| Title                       | Mobility improvement in nanowire junctionless transistors by uniaxial strain                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)                   | Raskin, Jean-Pierre; Colinge, Jean-Pierre; Ferain, Isabelle; Kranti,<br>Abhinav; Lee, Chi-Woo; Akhavan, Nima Dehdashti; Yan, Ran; Razavi,<br>Pedram; Yu, Ran                                                                                                                                                                                                                                                                                                                                                                 |

| Publication date            | 2010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Original citation           | Raskin, JP., Colinge, JP., Ferain, I., Kranti, A., Lee, CW., Akhavan, N. D., Yan, R., Razavi, P. and Yu, R. (2010) 'Mobility improvement in nanowire junctionless transistors by uniaxial strain', Applied Physics Letters, 97(4), pp. 042114. doi: 10.1063/1.3474608                                                                                                                                                                                                                                                        |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Link to publisher's version | http://aip.scitation.org/doi/abs/10.1063/1.3474608 http://dx.doi.org/10.1063/1.3474608 Access to the full text of the published version may require a subscription.                                                                                                                                                                                                                                                                                                                                                          |

| Rights                      | © 2010 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in Raskin, JP., Colinge, JP., Ferain, I., Kranti, A., Lee, CW., Akhavan, N. D., Yan, R., Razavi, P. and Yu, R. (2010) 'Mobility improvement in nanowire junctionless transistors by uniaxial strain', Applied Physics Letters, 97(4), pp. 042114 and may be found at http://aip.scitation.org/doi/abs/10.1063/1.3474608 |

| Item downloaded from        | http://hdl.handle.net/10468/4339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Downloaded on 2018-08-23T18:49:12Z

## Mobility improvement in nanowire junctionless transistors by uniaxial strain

Jean-Pierre Raskin', Jean-Pierre Colinge', Isabelle Ferain, Abhinav Kranti, Chi-Woo Lee, Nima Dehdashti Akhavan, Ran Yan, Pedram Razavi, and Ran Yu

Citation: Appl. Phys. Lett. 97, 042114 (2010); doi: 10.1063/1.3474608

View online: http://dx.doi.org/10.1063/1.3474608

View Table of Contents: http://aip.scitation.org/toc/apl/97/4

Published by the American Institute of Physics

## Articles you may be interested in

Reduced electric field in junctionless transistors

Applied Physics Letters 96, 073510 (2010); 10.1063/1.3299014

Low subthreshold slope in junctionless multigate transistors

Applied Physics Letters 96, 102106 (2010); 10.1063/1.3358131

Junctionless multigate field-effect transistor

Applied Physics Letters 94, 053511 (2009); 10.1063/1.3079411

Mobility enhancement effect in heavily doped junctionless nanowire silicon-on-insulator metal-oxidesemiconductor field-effect transistors

Applied Physics Letters 101, 213502 (2012); 10.1063/1.4767353

Improvement of carrier ballisticity in junctionless nanowire transistors

Applied Physics Letters 98, 103510 (2011); 10.1063/1.3559625

Simulation of junctionless Si nanowire transistors with 3 nm gate length

Applied Physics Letters 97, 062105 (2010); 10.1063/1.3478012

## Mobility improvement in nanowire junctionless transistors by uniaxial strain

Jean-Pierre Raskin, <sup>1,a)</sup> Jean-Pierre Colinge, <sup>2,b)</sup> Isabelle Ferain, <sup>2</sup> Abhinav Kranti, <sup>2</sup> Chi-Woo Lee, <sup>2</sup> Nima Dehdashti Akhavan, <sup>2</sup> Ran Yan, <sup>2</sup> Pedram Razavi, <sup>2</sup> and Ran Yu <sup>2</sup> <sup>1</sup> Information and Communication Technologies, Electronics and Applied Mathematics, Université catholique de Louvain, Place du Levant, 3, Maxwell Building, B-1348 Louvain-la-Neuve, Belgium <sup>2</sup> Tyndall National Institute, University College Cork, Dyke Parade, Cork, Ireland

(Received 15 May 2010; accepted 9 July 2010; published online 30 July 2010)

Improvement of current drive in n- and p-type silicon junctionless metal-oxide-semiconductor-field-effect-transistors (MOSFETs) using strain is demonstrated. Junctionless transistors have heavily doped channels with doping concentrations in excess of  $10^{19}~\rm cm^{-3}$  and feature bulk conduction, as opposed to surface channel conduction. The extracted piezoresistance coefficients are in good agreement with the piezoresistive theory and the published coefficients for bulk silicon even for 10 nm thick silicon nanowires as narrow as 20 nm. These experimental results demonstrate the possibility of enhancing mobility in heavily doped silicon junctionless MOSFETs using strain technology. © 2010 American Institute of Physics.

[doi:10.1063/1.3474608]

Mechanical strain is a widely used technique to increase carrier mobility in the channel of silicon metal-oxidesemiconductor-field-effect-transistors (MOSFETs). The technique has been applied to bulk MOSFETs, silicon-oninsulator (SOI) transistors, <sup>2-4</sup> as well as to multigate FETs (MuGFETs). These studies demonstrate the great interest of strain engineering to boost up the performance of those advanced MOS devices with extensive industrial applications. As mentioned by Chu et al. in Ref. 6, the viability of novel transistor architectures or channel materials will depend on their ability to provide device enhancement comparable to strained-Si planar MOSFETs. Recently, the fabrication of silicon nanowire transistors with no junctions has been reported. In these devices, the channel doping concentration is high with typical values ranging from 10<sup>19</sup> to over 5  $\times 10^{19}$  cm<sup>-3</sup>. n- and p-channel devices are uniformly doped with donor and acceptor impurities, respectively. The doping type and concentration are the same in the source and drain extensions as in the channel. The absence of doping concentration gradients greatly simplifies fabrication and relaxes thermal budget requirement, especially in ultrashort-channel devices. Those original devices have demonstrated near-ideal subthreshold slope, extremely low leakage current, and less degradation of mobility with gate voltage and temperature than classical transistors. Since the channel of junctionless transistors is heavily doped, one might wonder if straininduced mobility enhancement techniques can be effectively used in these devices. The aim of the present article is to experimentally analyze the impact of mechanical strain on drive current for n- and p-type junctionless Si nanowire MOSFETs.

The piezoresistance coefficients ( $\pi$ ) of doped bulk silicon can be found in the literature. The piezoresistance factor in silicon decreases when the doping concentration is in-

creased above  $5 \times 10^{17}~{\rm cm^{-3}}$  in n-type silicon and when it is increased above  $2 \times 10^{17}~{\rm cm^{-3}}$  in p-type silicon. The reduction of piezoresistance coefficients in n- and p-type silicon is shown in Table I for some typical doping concentrations used in the channel of junctionless transistors. To the reduction of piezoresistance coefficients corresponds a reduction in strain-induced mobility enhancement. Indeed, the piezoresistance coefficient is defined as the normalized change in resistivity with stress,  $\pi = \Delta \rho/(\rho \cdot \sigma)$ , where  $\sigma$  is the applied stress and  $\rho$  is the resistivity which is directly related to the carrier mobility by  $\rho = 1/(q\mu_n n + q\mu_n p)$ .

The strain-induced mobility enhancement ( $\pi_L$ ) can readily be calculated using the data supplied in Ref. 8 and one finds  $\pi_L$ =35.2 cm²/dyne=352×10<sup>-6</sup> MPa<sup>-1</sup> for p-type silicon and  $\pi_L$ =31.2 cm²/dyne=312×10<sup>-6</sup> MPa<sup>-1</sup> for n-type silicon at a doping concentration of 2×10<sup>19</sup> cm<sup>-3</sup>.

The devices were fabricated on standard (100) Unibond SOI wafers with a 340 nm top silicon layer and a 400 nm buried oxide. The starting SOI film was p-type with a resistivity of  $10-20~\Omega$  cm. The SOI layer was thinned down to 10-15~ nm and patterned to form silicon nanowires using e-beam lithography. Nanowires with different widths were patterned, in order to obtain devices with a width ranging between 20 and 40 nm. A 10 nm gate oxide was grown and ion implantation was used to dope the devices *uniformly* n<sup>+</sup> and p<sup>+</sup> with a concentration of  $2\times10^{19}~$  cm<sup>-3</sup> to realize n-channel and p-channel devices, respectively. A 50 nm thick polysilicon layer was deposited by low-pressure chemical vapor deposition on the gate oxide and doped either p<sup>++</sup> for

TABLE I. Reduction of piezoresistance coefficient (in percents) in n-type and p-type silicon for some values of doping concentration used in the channel of junctionless transistors.

| Doping concentration                | n-type | p-type |

|-------------------------------------|--------|--------|

| $1 \times 10^{19} \text{ cm}^{-3}$  | 14%    | 30%    |

| $2 \times 10^{19}$ cm <sup>-3</sup> | 26%    | 51%    |

| $5 \times 10^{19} \text{ cm}^{-3}$  | 46%    | 71%    |

<sup>&</sup>lt;sup>a)</sup>Electronic mail: jean-pierre.raskin@uclouvain.be. Tel.: +32 10 47 23 09, FAX: +32 10 47 87 05.

b) Electronic mail: jean-pierre.colinge@tyndall.ie. Tel.: +353 21 490 48 65, FAX: +353 21 420 57 03.

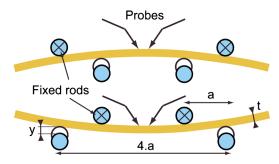

FIG. 1. (Color online) Four-point bending measurement setup and relationship between the induced stress  $(\sigma)$  and vertical displacement (y) of the bottom movable rods. For all measurements, the spacing "a" was equal to 20 mm

nMOS devices or n<sup>++</sup> for pMOS devices. The devices studied here have a gate length of 1  $\,\mu m$ . No source or drain implant was performed on the junctionless MuGFETs. Oxide was deposited and etched to form contact holes, and TiW +aluminum metallization completed the process. The channel of the devices follows the  $\langle 110 \rangle$  crystal direction. Mobility measurements made using the maximum of transconductance method yield mobility values in the range  $80{\text -}100~\text{cm}^2/\text{V}$  s for both electrons in n-channel devices and holes in p-channel device. Unlike inversion-mode and accumulation-mode MuGFETs, junctionless transistors in the on-state operate by bulk conduction (i.e., not surface channel conduction). Thus, their piezoresistance coefficients and mobility enhancement effects must be compared to bulk silicon values.

The devices were measured using a wafer probe system equipped with a four-point bending setup that allows for bending the wafers in order to generate uniaxial strain in the transistors. Bending the center of the wafer upwards creates a tensile stress on the top fiber of the wafer, and bending it downwards creates a compressive stress (Fig. 1). The transfer and output characteristics were measured for various devices geometries and applied stress values. The maximum stress is limited to 150 MPa to avoid breaking the wafers. This experimental setup provides a simple way to gain confidence in the effect of strain on transistor performance without modifying the process flow. This is quite important since many process flow parameters are changed when fabricating strained MOSFETs, there is thus uncertainly as to whether

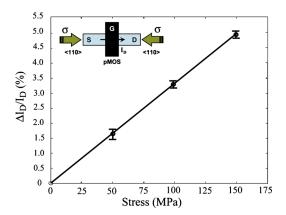

FIG. 2. (Color online) The variation in drain current,  $\Delta I_D/I_D$ , as a function of applied compression stress in a p-type junctionless MuGFET with a fin width of 30 nm.

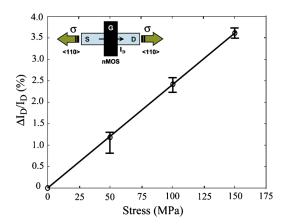

FIG. 3. (Color online) The variation in drain current,  $\Delta I_D/I_D$ , as a function of applied tensile stress in a n-type junctionless MuGFET with a fin width of 30 nm.

strain is the unique responsible for performance enhancement.

The stress is applied in  $\langle 110 \rangle$  crystalline direction, i.e., parallel to the current flow in the devices. Compression and traction stresses are, respectively, applied to p- and n-type junctionless MuGFETs. The devices were measured for a gate voltage ranging from 0.4 to 1.1 V (n-channel,  $V_{\rm TH}$ = -0.8 V) and -0.6 to -1.8 V (p-channel,  $V_{\text{TH}}$ =+0.2 V). The variation in drain current,  $\Delta I_D/I_D$ , as a function of the applied stress is plotted for p-(compression) and n-(traction) type junctionless MuGFETs in Figs. 2 and 3, respectively. The fin width of those devices is 30 nm and the gate voltage overdrive,  $V_{\rm GS}$ - $V_{\rm TH}$ , considered for the current extraction is 0.5 V. At least five devices for each stress level were measured. The characteristic fluctuation between devices is represented by a vertical bar in the graphs for each stress level. This fluctuation is pretty low, especially for p-type junctionless MuGFETs. The origin of this scattering might be of course related to the variability between devices but also to the measurement accuracy in terms of actual applied stress. The bars are more important for low level of applied stress. In fact, the main source of inaccuracy comes from the operator ability to define the zero point,  $\sigma$ =0 MPa. For this particular measurement point, the pressure applied between the two bottom metallic rods and the metallic back side of the Si wafer must be sufficient to assure a good ground contact but cannot induce bending of the wafer.

In both cases, we observe a linear increase in the drain current relative change as a function of stress. From the slope of represented straight lines in Figs. 2 and 3, the longitudinal piezoresistance factors,  $\pi_L$ , are extracted for, respectively, p-and n-type junctionless MuGFETs. The results are summarized in Table II and are found to be in excellent agreement with the theoretical values proposed by Kanda. 8

TABLE II. Piezoresistance coefficients in n-type and p-type devices. The calculated values are taken from Ref. 8 for a doping concentration of 2  $\times\,10^{19}$  cm $^{-3}$ .

|        | $\pi_L$ measured (MPa <sup>-1</sup> ) | $\pi_L$ calculated (MPa <sup>-1</sup> ) |

|--------|---------------------------------------|-----------------------------------------|

| n-type | $233 \pm 25 \times 10^{-6}$           | $230 \times 10^{-6}$                    |

| p-type | $333 \pm 10 \times 10^{-6}$           | $352 \times 10^{-6}$                    |

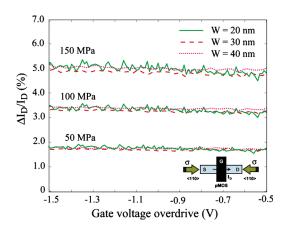

FIG. 4. (Color online) The variation in drain current,  $\Delta I_D/I_D$ , as a function of gate voltage overdrive,  $V_{\rm GS}$ - $V_{\rm TH}$ , in a p-type junctionless MuGFET characterized by fin width of 20, 30, or 40 nm for various applied compressive stresses

Figure 4 shows the variation in drain current,  $\Delta I_D/I_D$ , as a function of the gate voltage overdrive for p-type MuGFET characterized by fin width of 20, 30, or 40 nm and for applied compressive stress of 50, 100, or 150 MPa. No variations with the fin width demonstrate that there is no lateral geometry confinement on the piezoresistance effect. Contrary to classical planar or nonplanar MOSFETs working in inversion regime, the current relative change,  $\Delta I_D/I_D$ , is nearly independent on gate voltage overdrive for each recorded stress value. This beneficial behavior is directly related to the bulk conduction mode of junctionless MOSFETs. It means strain channel engineering improves carrier mobility over the whole gate bias range in on-state whereas for inversion mode strained-transistors the mobility enhancement degrades with gate voltage overdrive.

In conclusion, improvement of current drive using strain in junctionless n- and p-type nanowire MOSFETs is demonstrated. The extracted piezoresistance coefficients are in good agreement with the published piezoresistance coefficients for bulk silicon. A constant mobility enhancement factor is obtained over the whole gate bias range of interest in on-state. The combination of strained SOI and junctionless concept should lead to high-performance nanowire complementary MOS devices.

This work is supported by the Science Foundation Ireland under Grant No. 05/IN/I888, Advanced Scalable Silicon-on-Insulator Devices for Beyond-End-of-Roadmap Semiconductors. This work has also been enabled by the Programme for Research in Third-Level Institutions. This work was supported in part by the European Community (EC) Seventh Framework Program through the Networks of Excellence NANOSIL and EUROSOI+under Contract Nos. 216171 and 216373.

<sup>1</sup>S. E. Thompson, M. Armstrong, C. Auth, S. Cea, R. Chau, G. Glass, T. Hoffman, J. Klaus, Z. Ma, B. McIntyre, A. Murthy, B. Obradovic, L. Shifren, S. Sivakumar, S. Tyagi, T. Ghani, K. Mistry, M. Bohr, and Y. El-Mansy, IEEE Trans. Electron Devices **51–4**, 191 (2004).

<sup>2</sup>R. E. Belford, J. Electron. Mater. **30**, 807 (2001).

<sup>3</sup>S. Takagi, T. Mizuno, T. Tezuka, N. Sugiyama, T. Numata, K. Usuda, Y. Moriyama, S. Nakaharai, J. Koga, A. Tanabe, and T. Maeda, Appl. Surf. Sci. 224, 241 (2004).

<sup>4</sup>F. Rochette, M. Cassé, M. Mouis, A. Haziot, T. Pioger, G. Ghibaudo, and F. Boulanger, Solid-State Electronics **53**, 392 (2009).

<sup>5</sup>N. Serra, F. Conzatti, D. Esseni, M. De Michielis, P. Palestri, L. Selmi, S. Thomas, T. E. Whall, E. H. C. Parker, D. R. Leadley, L. Witters, A. Hikavyy, M. J. Hÿtch, F. Houdellier, E. Snoeck, T. J. Wang, W. C. Lee, G. Vellianitis, M. J. H. van Dal, B. Duriez, G. Doornbos, and R. J. P. Lander, Tech. Dig. - Int. Electron Devices Meet. **2009**, 71.

<sup>6</sup>M. Chu, Y. Sun, U. Aghoram, and S. E. Thompson, Annu. Rev. Mater. Res. **39**, 203 (2009).

<sup>7</sup>J.-P. Colinge, C. W. Lee, A. Afzalian, N. Dehdashti Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A. M. Kelleher, B. McCarthy, and R. Murphy, Nat. Nanotechnol. 5, 225 (2010).

<sup>8</sup>Y. Kanda, IEEE Trans. Electron Devices **29**, 64 (1982).

<sup>9</sup>C. W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. Dehdashti, and J.-P. Colinge, IEEE Trans. Electron Devices **57**, 620 (2010).