| Title                          | Simulation of junctionless Si nanowire transistors with 3 nm gate length                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)                      | Ansari, Lida; Feldman, Baruch; Fagas, Gíorgos; Colinge, Jean-Pierre;<br>Greer, James C.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Publication date               | 2010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Original citation              | Ansari, L., Feldman, B., Fagas, G., Colinge, JP. and Greer, J. C. (2010)<br>'Simulation of junctionless Si nanowire transistors with 3 nm gate<br>length', Applied Physics Letters, 97(6), pp. 062105. doi:<br>10.1063/1.3478012                                                                                                                                                                                                                                                                    |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Link to publisher's<br>version | http://aip.scitation.org/doi/abs/10.1063/1.3478012<br>http://dx.doi.org/10.1063/1.3478012<br>Access to the full text of the published version may require a<br>subscription.                                                                                                                                                                                                                                                                                                                        |

| Rights                         | © 2010 American Institute of Physics. This article may be<br>downloaded for personal use only. Any other use requires prior<br>permission of the author and AIP Publishing. The following article<br>appeared in Ansari, L., Feldman, B., Fagas, G., Colinge, JP. and<br>Greer, J. C. (2010) 'Simulation of junctionless Si nanowire<br>transistors with 3 nm gate length', Applied Physics Letters, 97(6),<br>pp. 062105 and may be found at<br>http://aip.scitation.org/doi/abs/10.1063/1.3478012 |

| Item downloaded<br>from        | http://hdl.handle.net/10468/4336                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Downloaded on 2018-08-23T18:51:06Z

Coláiste na hOllscoile Corcaigh

## Simulation of junctionless Si nanowire transistors with 3 nm gate length

Lida Ansari, Baruch Feldman, Giorgos Fagas, Jean-Pierre Colinge, and James C. Greer

Citation: Appl. Phys. Lett. **97**, 062105 (2010); doi: 10.1063/1.3478012 View online: http://dx.doi.org/10.1063/1.3478012 View Table of Contents: http://aip.scitation.org/toc/apl/97/6 Published by the American Institute of Physics

## Articles you may be interested in

Junctionless multigate field-effect transistor Applied Physics Letters **94**, 053511 (2009); 10.1063/1.3079411

Reduced electric field in junctionless transistors Applied Physics Letters **96**, 073510 (2010); 10.1063/1.3299014

Low subthreshold slope in junctionless multigate transistors Applied Physics Letters **96**, 102106 (2010); 10.1063/1.3358131

Gate-all-around junctionless silicon transistors with atomically thin nanosheet channel (0.65 nm) and record sub-threshold slope (43 mV/dec) Applied Physics Letters **110**, 032101 (2017); 10.1063/1.4974255

Analysis of the leakage current in junctionless nanowire transistors Applied Physics Letters **103**, 202103 (2013); 10.1063/1.4829465

Bipolar effects in unipolar junctionless transistors Applied Physics Letters **101**, 093507 (2012); 10.1063/1.4748909

## Simulation of junctionless Si nanowire transistors with 3 nm gate length

Lida Ansari, Baruch Feldman,<sup>a)</sup> Giorgos Fagas, Jean-Pierre Colinge, and James C. Greer *Tyndall National Institute, University College Cork, Cork, Ireland*

(Received 28 March 2010; accepted 3 July 2010; published online 10 August 2010)

Inspired by recent experimental realizations and theoretical simulations of thin silicon nanowire-based devices, we perform proof-of-concept simulations of junctionless gated Si nanowire transistors. Based on first-principles, our primary predictions are that Si-based transistors are physically possible without major changes in design philosophy at scales of  $\sim 1$  nm wire diameter and  $\sim 3$  nm gate length, and that the junctionless transistor avoids potentially serious difficulties affecting junctioned channels at these length scales. We also present investigations into atomic-level design factors such as dopant positioning and concentration. © 2010 American Institute of Physics. [doi:10.1063/1.3478012]

As the semiconductor technology roadmap nears its end, more and more fundamental changes are becoming necessary to design transistor devices. Short-channel effects<sup>1–3</sup> degrade subthreshold slope, aggravate drain-induced barrier lowering, and limit overall performance. In response, designs using more gates and thinner channels to enhance gating control and alleviate these effects are becoming popular.<sup>1–3</sup> Other proposals<sup>3,4</sup> for ultrashort-channel transistors include tunneling field-effect transistors (FETs) and impact ionization FETs, but all of these require precise control of dopant positioning to arrive at a profile that includes junctions, for example, p-i-p, p-i-n, etc.

However, *junctionless* nanowire transistors were recently fabricated with a trigate electrode structure.<sup>5</sup> These nanowire transistors have a thickness of a few nanometers and channel length of 1  $\mu$ m. This design, essentially a "gated resistor" that turns off by pinch-off when gate voltage is applied, avoids the difficulty and high thermal budget of fabricating ultrashallow junctions [as in standard metal oxide semiconductor FETs (MOSFETs)] at nanometer length scales.<sup>5,6</sup> Moreover, previous semiclassical simulations indicate it has better short-channel characteristics than comparable trigate MOSFETs.<sup>6</sup>

In this letter, we continue our previous efforts<sup>7,8</sup> to understand transport in Si nanowires by simulating an atomicscale device with a gating field and calculating its  $I-V_{ds}$ characteristics. Calculations of the response of doped junctionless silicon nanowire (SiNW) transistors to source-drain bias,  $V_{ds}$ , and gate voltage,  $V_g$ , are presented. By employing a first-principles approach for the electronic structure at small bias, our simulations provide a proof-of-concept, applying to devices both thinner and shorter than those currently achievable in the laboratory<sup>5</sup> or by effective-mass calculation.<sup>6</sup> At such small scales, standard two-junction transistor designs are difficult to fabricate, and (because of dopant de-localization, as we will discuss) may not be physically possible. Most importantly, we find the junctionless transistor device concept works at scales as small as wire diameter of ~1 nm and gate length of ~3 nm.

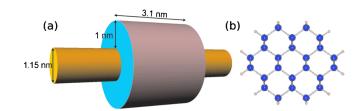

A typical structure of our simulated junctionless SiNW transistors is shown in Fig. 1. As the name implies, these devices are uniformly doped throughout the wire from a

macroscopic perspective. As shown, the SiNWs have a gateall-around (GAA) architecture. In the actual devices realized experimentally,<sup>5</sup> field effects from the work function of the gate cause the device to turn off at  $V_g=0$  V. But in principle, a junctionless device is a "gated resistor" that is *on* at  $V_g$ =0 V, as is the case in our simulations.

We used the [110]-oriented hydrogenated Si nanowire structures from previous work<sup>7</sup> (Fig. 1). The wire diameter is  $2R_{\rm NW}$ =1.15 nm. We found the electronic structure and Hamiltonian for all valence electrons in the doped SiNW device self-consistently in a full quantum-mechanical treatment using the density functional tight-binding<sup>9</sup> code, DFTB<sup>+</sup>. DFTB<sup>+</sup> performs self-consistent electronic structure calculations in a tight-binding framework using parameters calculated from first-principles density functional theory (DFT).<sup>9</sup> This enabled us to simulate ~800 atoms in our supercells.

We simulated the gating field from a GAA structure by using point charges (the positions and charges of these are held fixed within the electronic-structure calculation) to represent the gate. We assembled the point charges in rings of radius  $R_g$ =1.6 nm around the nanowire structure, typically containing 100 point charges per ring and spaced about 1 Å apart along the wire axis. We used a gate length  $L_g$ =3.1 nm. This approach yields a discrete approximation to the charge distribution of a gate with the required geometric characteristics. The values of the point charges were fixed by the desired gate voltage,  $V_g$ . To relate  $V_g$  to the gate charges, we modeled the oxide surrounding the nanowires by a continuum with hafnium oxide dielectric constant,  $\epsilon_{\rm HfO_2}$ =25.

To model doped nanowires, we inserted substitutional dopant atoms into the SiNW lattice. We used Ga for a p-type dopant, and As for n-type. Because of the relatively small supercells amenable to first-principles calculations, we used

FIG. 1. (Color online) (a) Geometry of junctionless GAA SiNW devices simulated. (b) Cross section of Si nanowire structures simulated.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: baruchf@alum.mit.edu.

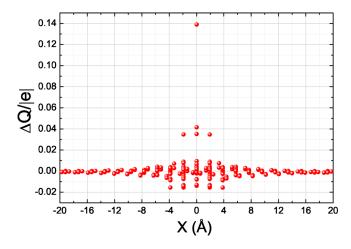

FIG. 2. (Color online) Mulliken charge differences (in units of |e|) for n-doped vs intrinsic Si nanowires as a function of position x along the wire axis. Shown here is a donor at the origin.

very high doping concentrations N in the leads, typically  $N = 8 \times 10^{20}$  cm<sup>-3</sup>, about ten times higher than in previous semiclassical simulations.<sup>6</sup> Nevertheless, this still gives just seven dopant atoms to be distributed within the ~800 atom supercell.

We used the electronic temperature  $T_e=300$  K. However, due to the high N, we found the dopant band displays a large curvature. Moreover, the Fermi levels and band structures in the leads were consistent with many free carriers,

$$|E_F - E_d| \approx 350 \text{ meV},\tag{1}$$

with  $E_d$  the edge of the dopant band. Taken together, these facts mean a high density of free carriers *independently* of whether the temperature is high enough for dopants to ionize. This can be explained by modeling a dopant atom as a hydrogenlike system with effective electron mass  $m^*$  and dielectric constant  $\epsilon$  from Si.<sup>10</sup> Then the typical localization radius of the dopant electron or hole is

$$R_{\rm loc} = \frac{m}{m^*} \epsilon \, a_0, \tag{2}$$

with  $a_0$  the Bohr radius. Using  $m^*/m=0.15$  for [110] SiNWs from our calculations<sup>8</sup> and the bulk value  $\epsilon_{\rm Si}=11.7$ , we find  $R_{\rm loc}=4$  nm, even at 0 K. This is to compare to a dopant spacing of  $\sim 1$  nm along the wire.

To understand this behavior better, we studied the Mulliken populations for our doped and undoped SiNWs. Mulliken population analysis<sup>11</sup> is a postprocessing step for localized-basis calculations yielding a charge associated with each atom. Figure 2 shows the Mulliken charge differences,  $\Delta Q_i^M \equiv Q_i^M - Q_i^{M,0}$ , where *i* is an atom index,  $Q_i^M$  is the Mulliken charge on atom *i* in the n-doped wire, and  $Q_i^{M,0}$  is the Mulliken charge in the intrinsic wire. As shown in the figure, the donated electron de-localizes around the dopant atom with an exponential localization distance  $R_{loc}=1.5$  nm (for the wave function), in rough agreement with Eq. (2). Further,  $Q_i^M$  differs from  $Q_i^{M,0}$  throughout our supercell, confirming that at high N and in a thin nanowire, dopants do not have to ionize to contribute to the channel's "on" conductivity. Since  $L_g \sim R_{\rm loc}$ , we predict that carriers are present in the channel region even when there are no dopant atoms there. This behavior, quite generally, makes standard junctioned nanowire transistors with small gate lengths difficult to achieve. By

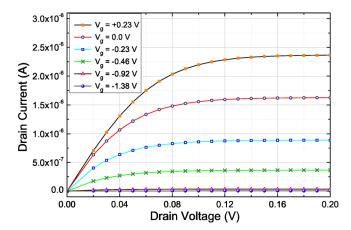

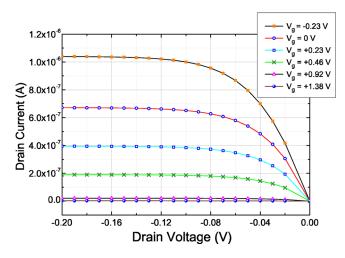

FIG. 3. (Color online) Room temperature I- $V_{ds}$  characteristic for SiNW junctionless transistor doped n-type by As atoms with dimensions shown in Fig. 1.

contrast, de-localization should make the junctionless design more robust against dopant fluctuations, a major design concern at these scales.

The calculations of Rurali *et al.*<sup>12</sup> show that dopant levels are very deep in thin SiNWs, making *isolated* dopants unlikely to ionize. However, for high *N*, this does not contradict our findings of Eq. (1) and the surrounding discussion. Furthermore, for n-doped [110] SiNWs of diameter  $2R_{\rm NW}=1$  nm, they found that a donated electron de-localizes significantly along the wire axis, consistent with our results. But for thicker wires, they found  $R_{\rm loc}$  increasing from  $R_{\rm loc}=2$  Å for  $2R_{\rm NW}=1.5$  nm to  $R_{\rm loc}=2$  nm in bulk. For slightly thicker wires than the ones we model, localization could thus pose a challenge.

For our transport calculations at fixed  $V_g$ , first we solved the DFT Kohn–Sham equations under the influence of the applied external gating potential (as described above). This yields the correct ground state charge distribution within the channel in a self-consistent manner. Then, we computed the linear response conductance by the Landauer formula. We used our in-house transport code, TIMES (Ref. 7) to solve for the transmission function T(E) from Green's functions for the DFT Hamiltonians. This nonself-consistent approach is valid as a linear response to  $V_{ds}$  but captures some non-Ohmic behavior because we integrate T(E) rather than assume<sup>13</sup> that  $dT/dE \leq 1/eV_{ds}$ .

Because the device we model is heavily doped, screening of the leads from the gate takes place over a short length scale. Moreover, we include 1.9-nm-long contact regions on each side between the gated region and the leads as part of our atomic-scale simulation, so the leads are suitably screened from the channel.

Figures 3 and 4 show the calculated  $I-V_{ds}$  characteristics for n- and p-type junctionless devices, respectively. Clearly, these devices are on for  $V_g=0$  V, and they turn off based on a pinch-off principle when  $V_g$  causes a sufficiently large barrier in the gating region. Short-channel effects are a serious issue at these length scales, as tunneling across the  $V_g$  barrier could undermine the device's effectiveness. To mitigate short-channel effects, a rule of thumb for GAA geometry requires gate length<sup>1,2</sup>

## $L_g > 2R_{\rm NW},$

a condition satisfied here by only a small margin.

FIG. 4. (Color online) Room temperature  $I-V_{ds}$  characteristic for SiNW junctionless transistor doped p-type by Ga atoms.

However, GAA geometries are well-known to have superior gate control.<sup>14,2</sup> Our results confirm this remains true in the junctionless design even for gate lengths  $\sim 3$  nm, enabling the devices to turn off. This is our most important finding.<sup>15</sup>

Nevertheless, our approximations limit our quantitative description of short-channel effects. For example, our prediction of the turnoff gate voltage  $V_{off}$  is an upper bound because of the lack of self-consistency in our non-equilibrium Green's function (NEGF) calculations and the limited supercell. Still, our calculations indicate a good subthreshold slope, and much better than for other nanoscale device designs.<sup>1,2</sup>

We found various effects of dopant positioning of relevance to prospective device design. First, as already mentioned, carrier delocalization blurs the junction boundary over a length scale  $R_{loc}$  comparable to the length  $L_g$  of the channel itself. This makes the junctionless transistor more robust against dopant fluctuations, while making a junctioned channel difficult to achieve.

We also found that the positioning of the dopant in the wire cross section makes a difference in the band structure of the device. A periodic array of dopants near the SiNW surface is found to create a dopant band that narrows the SiNW band gap, which is ordinarily about twice the band gap of bulk Si.<sup>7</sup> This narrowing leads to a steeper  $I-V_{ds}$  characteristic.

We have performed transport simulations on junctionless GAA SiNW devices of radius  $R_{\rm NW}$ =0.6 nm and gate length  $L_g$ =3.1 nm. We predict that the junctionless transistor continues to work well at this scale, turning off with sourcedrain leakage  $I_{\rm off} < 10^{-6}I_{\rm on}$ , and has good electrostatic control and a good subthreshold characteristic. By contrast, standard junctioned MOSFET designs are very difficult to fabricate at this scale. And, more importantly, the distribution of charge carriers around the dopant blurs the boundaries of a junction over a distance comparable to the channel length, so junctions at these scales would likely fail to keep carriers out of the channel.

We would like to thank J. Andreas Larsson for useful discussions. This research was funded by Science Foundation Ireland under Grant No. 06/IN.1/I857.

- <sup>1</sup>J.-P. Colinge, Solid-State Electron. **48**, 897 (2004); C.-W. Lee, S.-R.-N. Yun, C.-G. Yu, J.-T.-Park, and J.-P. Colinge, *ibid.* **51**, 505 (2007).

- <sup>2</sup>*FinFETs and Other Multi-Gate Transistors*, edited by J. P. Colinge (Springer, New York, 2007).

- <sup>3</sup>N. Singh, K. D. Buddharaju, S. K. Manhas, A. Agarwal, S. C. Rustagi, G. Q. Lo, N. Balasubramanian, and D.-L. Kwong, IEEE Trans. Electron Devices **55**, 3107 (2008).

- <sup>4</sup>M. T. Björk, J. Knoch, H. Schmid, H. Riel, and W. Riess, Appl. Phys. Lett. **92**, 193504 (2008).

- <sup>5</sup>J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Keleher, B. McCarthy, and R. Murphy, Nat. Nanotechnol. **5**, 225 (2010).

- <sup>6</sup>C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J.-P. Colinge, Appl. Phys. Lett. **94**, 053511 (2009).

- <sup>7</sup>G. Fagas and J. C. Greer, Nano Lett. 9, 1856 (2009).

- <sup>8</sup>F. Murphy-Armando, G. Fagas, and J. C. Greer, Nano Lett. **10**, 869 (2010).

- <sup>9</sup>M. Elstner, D. Porezag, G. Jungnickel, J. Elsner, M. Haugk, T. Frauenheim, S. Suhai, and G. Seifert, Phys. Rev. B 58, 7260 (1998).

- <sup>10</sup>N. W. Ashcroft and N. D. Mermin, *Solid State Physics* (Holt, Rinehart, and Winston, New York, 1976).

- <sup>11</sup>R. S. Mulliken, J. Chem. Phys. 23, 1833 (1955).

- <sup>12</sup>R. Rurali, B. Aradi, T. Frauenheim, and Á. Gali, Phys. Rev. B **79**, 115303 (2009).

- <sup>13</sup>S. Datta, *Electronic Transport in Mesoscopic Systems* (Cambridge University Press, Cambridge, 1997).

- <sup>14</sup>S. Miyano, M. Hirose, and F. Masuoka, IEEE Trans. Electron Devices 39, 1876 (1992).

- <sup>15</sup>We validated this by using  $V_g=0$  V but introducing a uniform energy shift to the NEGF Hamiltonian in the gated region. This neglects capacitance and screening in the oxide and SiNW but enables us to quantify the tunneling current through the channel.