## Desarrollo de una herramienta para la generación de circuitos aritméticos aproximados

#### Informe de Proyecto de Graduación

en cumplimiento de los requerimientos para optar por el título de Ingeniero en Electrónica con el grado académico de Licenciatura

Deykel Hernández Araya

# INSTITUTO TECNOLÓGICO DE COSTA RICA ESCUELA DE INGENIERÍA ELECTRÓNICA PROYECTO DE GRADUACIÓN ACTA DE APROBACIÓN

Defensa de Proyecto de Graduación Requisito para optar por el título de Ingeniero en Electrónica Grado Académico de Licenciatura Instituto Tecnológico de Costa Rica

El Tribunal Evaluador aprueba la defensa del proyecto de graduación denominado Desarrollo de una herramienta para la generación de circuitos aritméticos aproximados, realizado por el señor Deykel Israel Hernández Araya y, hace constar que cumple con las normas establecidas por la Escuela de Ingeniería Electrónica del Instituto Tecnológico de Costa Rica.

Miembros del Tribunal Evaluador

M.Sc. Jorge Castro Godinez

M.Sc Miguel Hernández Rivera

Profesor lector

Profesor lector

Dr. Roberto Pereira Arroyo

Profesor asesor

Cartago, 12 de junio de 2017

Declaro que el presente documento de tesis ha sido realizado enteramente por mi persona, utilizando y aplicando literatura referente al tema e introduciendo conocimientos y resultados experimentales propios.

En los casos en que he utilizado bibliografía he procedido a indicar las fuentes mediante las respectivas citas bibliográficas. En consecuencia, asumo la responsabilidad total por el trabajo de tesis realizado y por el contenido del presente documento.

Deykel Hernández Araya

Cartago. 5 de junio de 2017

Céd.: 7 0226 0295

#### **Agradecimientos**

Primeramente agradezco a Dios por darme vida, salud y sabiduría para superar todos los retos que se me han presentado a lo largo de este camino permitíendome llegar a este punto, el inicio de mi carrera profesional.

A mi familia, que han sido mis mayores cómplices en muchos de los proyectos e ideas que se me han ocurrido, en los que nunca he encontrado un no como respuesta y con los que he aprendido los valores importantes que rígen mi vida convirtiéndome en la persona que soy hoy.

A mi madre en especial, por ser la persona que se esfuerza y sacrifica cada día por brindarnos lo mejor tanto a mi hermano como a mi, por ser mi mayor ejemplo de que se debe trabajar duro para alcanzar metas y cumplir sueños.

A la familia Castro-Solano, por hacerme sentir a gusto y brindarme el calor de una segunda familia durante el desarrollo de este proyecto en un país completamente diferente, también por el apoyo, ejemplos de vida y consejos brindados durante mi estancia.

Al profesor Jorge Castro Godínez por darme la oportunidad y responsabilidad de asumir este proyecto, por los consejos, confianza y paciencia brindada. Y por permitirme vivir una experiencia con la cual a parte de abrir mi mente en el campo profesional, también se da una apertura de ella hacia el intercambio cultural y social por el cual el mundo atraviesa.

A mis profesores lectores y mi profesor asesor por la formación académica y apoyo brindado no solo en este punto de mi carrera sino a lo largo de ella.

En fin, a las personas que siempre estuvieron apoyándome directa o inderectamente, a las que siempre han esperado lo mejor de mí y a las que aún esperan más.

Deykel Hernández Araya Cartago, 20 de junio de 2017

#### Resumen

Computación aproximada se presenta como un nuevo paradigma que entre muchas capas de aplicación permite el diseño de circuitos energéticamente eficientes, esto aprovechando que muchas aplicaciones tienen cierta tolerancia a pérdidas en la precisión de sus cálculos, lo que admite variar las estructuras y a su vez el comportamiento lógico de las unidades aritméticas que realizan estos cómputos.

Este proyecto desarrolla una herramienta que es capaz de generar descripciones en hardware de unidades aritméticas aproximadas propuestas en la comunidad, además de ejecutar diversos procesos en herramientas externas de simulación y síntesis que brindan información relvante para el diseño de un circuito donde se desee introducir aproximaciones.

Es entonces como este documento proporciona primeramente las características de estructura y comportamiento lógico de las unidades aritméticas desarrolladas, seguido del proceso de diseño de la herramienta que incluye las consideraciones y restricciones tomadas para las descripción en hardware, escritura de scripts hacia herramientas externas y estructura de programación. Por último se presentan varios de los casos para lo que la herramienta puede ser usada comprobando a su vez el comportamiento correcto de las unidaes descritas.

Palabras clave: Circuitos aritméticos aproximados, Computación aproximada, Eficiencia energética, Sumadores aproximados, Multiplicadores aproximados, Divisores aproximados

#### **Abstract**

Approximate computing is presented as a new paradigm that among many application layers, allows the design of energy efficient circuits. This taking advantage of that many applications have some tolerance to losses in the precision of their calculations, which allows to vary the structures and in turn the logical behavior of the arithmetic units that perform these computations.

This project develops a tool that is capable of generating approximate arithmetic units hardware descriptions proposed in the community, in addition to execute various processes in external simulation and synthesis tools that provide relevant information for the design of a circuit in which is desired to introduce approximations.

It is then as this document first provides the characteristics of structure and logical behavior of the developed arithmetic units, followed by the process of design of the tool that includes the considerations and restrictions taken for the description in hardware, script writing towards external tools and structure programming. Finally, several of the cases are presented for which the tool can be used while checking the correct behavior of the described units.

**Keywords:** Approximate Arithmetic Circuits, Approximate Computing, Energy Efficiency, Approximate Adders, Approximate Multipliers, Approximate Dividers.

## Índice general

| In | dice  | de figu | ıras       |                                                          | V   |

|----|-------|---------|------------|----------------------------------------------------------|-----|

| Ín | dice  | de tab  | las        |                                                          | VII |

| Al | orevi | acione  | S          |                                                          | IX  |

| 1. | Intr  | oducci  | ión        |                                                          | 1   |

|    | 1.1.  | Comp    | utación A  | proximada                                                | 2   |

|    | 1.2.  | Unida   | des aritmé | éticas aproximadas                                       | 3   |

|    | 1.3.  | Genera  | ación de u | ınidades aritméticas aproximadas                         | 4   |

|    | 1.4.  | Contri  | bución de  | el proyecto                                              | 4   |

| 2. | Fun   | damen   | ıtos teóri | icos y estado del arte                                   | 7   |

|    | 2.1.  | Disipa  | ción de po | otencia en circuitos                                     | 7   |

|    | 2.2.  | Sumac   | dores      |                                                          | 8   |

|    | 2.3.  | Sumac   | dores apro | ximados                                                  | 9   |

|    |       | 2.3.1.  | Sumador    | res de baja Potencia                                     | 9   |

|    |       |         | 2.3.1.1.   | Sumador Aproximado Espejo (AMA, por sus siglas en        |     |

|    |       |         |            | inglés)                                                  | 10  |

|    |       |         | 2.3.1.2.   | Sumador de parte baja OR (LOA, por sus siglas en inglés) | 11  |

|    |       |         | 2.3.1.3.   | Approximate XOR/XNOR-based Adder (AXA)                   | 11  |

|    |       |         | 2.3.1.4.   | Sumador aproximado basado en compuertas de transmi-      |     |

|    |       |         |            | sion (TGA, por sus siglas en inglés)                     | 13  |

|    |       |         | 2.3.1.5.   | Sumador aproximado inexacto (InXA, por sus siglas en     |     |

|    |       |         |            | inglés)                                                  | 14  |

|    |       |         | 2.3.1.6.   | Sumador de acarreo libre (CFA, por sus siglas en inglés) | 15  |

|    |       | 2.3.2.  | Sumador    | res de alto rendimiento                                  | 16  |

|    |       |         | 2.3.2.1.   | Sumador de error tolerante II (ETAII, por sus siglas en  |     |

|    |       |         |            | inglés)                                                  | 16  |

|    |       |         | 2.3.2.2.   | Sumador casi correcto (ACAI, por sus siglas en inglés)   | 16  |

|    |       |         | 2.3.2.3.   | Sumador de precisión configurable (ACAII, por sus siglas |     |

|    |       |         |            | en inglés)                                               | 17  |

|    |       |         | 2.3.2.4.   | Sumador de precisión graciosamente-degradable (GDA)      | 17  |

|    |       |         | 2.3.2.5.   | Sumador Genérico de precisión configurable (GeAr, por    |     |

|    |       |         |            | sus siglas en inglés)                                    | 18  |

|    | 2.4.  | Multip  | olicadores |                                                          | 19  |

|    | 2.5   | Multir  | olicadores | Aproximados                                              | 19  |

Índice general

|    |      | 2.5.1.       | Multiplicador imparcial de rango dinamico para aplicaciones apro-                                                   | 1.0 |

|----|------|--------------|---------------------------------------------------------------------------------------------------------------------|-----|

|    |      | 0 <b>-</b> 0 | ( , , 1                                                                                                             | 19  |

|    |      | 2.5.2.       | Multiplicador aproximado redondeado a base (RoBa, por sus siglas                                                    | 01  |

|    | 2.0  | D            |                                                                                                                     | 21  |

|    | 2.6. |              |                                                                                                                     | 22  |

|    | 2.7. |              |                                                                                                                     | 22  |

|    |      | 2.7.1.       | Divisor aproximado sin restauración (AXDnr, por sus siglas en inglés)                                               | 22  |

|    |      | 2.7.2.       | Divisor aproximado con base redondeada de alta velocidad y eficiencia energética (SEERAD, por sus siglas en inglés) | 24  |

|    |      | 2.7.3.       | Divisor dinámico de baja potencia para aplicaciones aproximadas (DAC, por sus siglas en inglés)                     | 26  |

|    | 2.8. | Métric       | eas                                                                                                                 | 27  |

|    |      | 2.8.1.       | Producto retardo potencia (PDP, por sus siglas en inglés)                                                           | 27  |

|    |      | 2.8.2.       | Distancia de error (ED, por sus siglas en inglés)                                                                   | 28  |

|    |      | 2.8.3.       | Distancia media de error (MED, por sus siglas en inglés)                                                            | 28  |

|    |      | 2.8.4.       | · · · · · · · · · · · · · · · · · · ·                                                                               | 28  |

|    | 2.9. | Biblio       | tecas de circuitos aritméticos aproximados                                                                          | 28  |

|    |      | 2.9.1.       | EvoApprox8b: Biblioteca de sumadores y multiplicadores aproxi-                                                      |     |

|    |      |              | mados para diseño de circuito y evaluación comparativa de méto-                                                     |     |

|    |      |              |                                                                                                                     | 28  |

|    |      | 2.9.2.       | lpaclib: Biblioteca de multiplicadores y sumadores aproximados .                                                    | 29  |

|    |      |              |                                                                                                                     |     |

| 3. |      |              |                                                                                                                     | 31  |

|    | 3.1. | Estruc       | etura de la herramienta                                                                                             | 31  |

|    |      | 3.1.1.       | Generalidades                                                                                                       | 31  |

|    |      | 3.1.2.       | Archivos base                                                                                                       | 31  |

|    |      | 3.1.3.       | Organización de directorios                                                                                         | 32  |

|    |      | 3.1.4.       | Tipo de archivos                                                                                                    | 33  |

|    | 3.2. | Descri       |                                                                                                                     | 33  |

|    |      | 3.2.1.       | Sumadores                                                                                                           | 34  |

|    |      |              | 3.2.1.1. Sumadores de baja Potencia                                                                                 | 34  |

|    |      |              | 3.2.1.2. Sumadores de alto rendimiento                                                                              | 34  |

|    |      |              | 3.2.1.3. LOA                                                                                                        | 35  |

|    |      | 3.2.2.       | Multiplicadores                                                                                                     | 35  |

|    |      |              | 3.2.2.1. DRUM                                                                                                       | 36  |

|    |      |              | 3.2.2.2. RoBa                                                                                                       | 36  |

|    |      | 3.2.3.       | Divisores                                                                                                           | 37  |

|    |      |              | 3.2.3.1. AXDnr                                                                                                      | 37  |

|    |      |              | 3.2.3.2. DAC                                                                                                        | 37  |

|    |      |              | 3.2.3.3. SEERAD                                                                                                     | 38  |

|    | 3.3. | Archiv       |                                                                                                                     | 40  |

|    | 3.4. |              |                                                                                                                     | 40  |

|    |      | 3.4.1.       |                                                                                                                     | 40  |

|    |      | 3.4.2.       |                                                                                                                     | 41  |

|    |      | 3.4.3.       |                                                                                                                     | 43  |

|    |      |              | =                                                                                                                   |     |

Índice general iii

|           |       | 3.4.4.  | Script para estimación de potencia post-síntesis | 43        |

|-----------|-------|---------|--------------------------------------------------|-----------|

|           | 3.5.  | Núcleo  | de la herramienta                                | 43        |

|           |       | 3.5.1.  | Utilidades                                       | 44        |

|           |       | 3.5.2.  | Unidades aproximadas                             | 44        |

|           |       | 3.5.3.  | Funciones de Generación                          | 44        |

|           |       | 3.5.4.  | Funciones de ejecución                           | 45        |

|           |       | 3.5.5.  | Generador de unidades                            | 45        |

|           |       | 3.5.6.  | AAUG                                             | 46        |

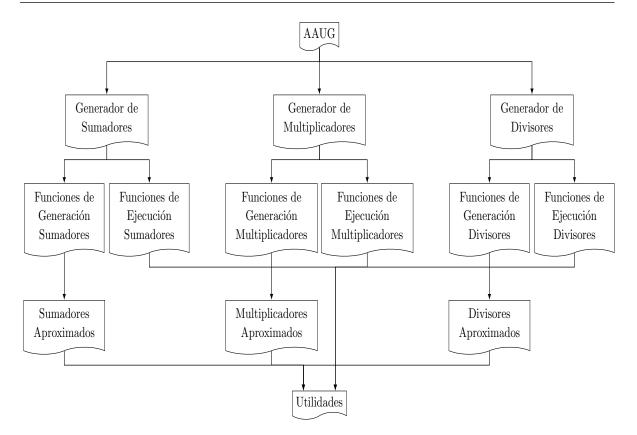

|           | 3.6.  | Flujo d | le la herramienta                                | 46        |

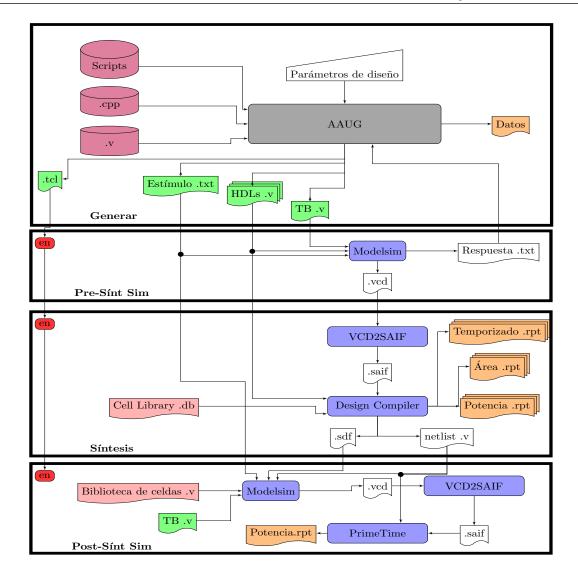

|           |       | 3.6.1.  | Generación                                       | 47        |

|           |       | 3.6.2.  | Simulación pre-síntesis                          | 47        |

|           |       | 3.6.3.  | Validación                                       | 47        |

|           |       | 3.6.4.  | Síntesis                                         | 47        |

|           |       | 3.6.5.  | Simulación Post-Síntesis                         | 47        |

| 4.        | Res   | ultados |                                                  | 49        |

|           |       |         | ación de datos para comparación                  | 49        |

|           |       | 4.1.1.  | Ejecución de herramienta                         | 49        |

|           |       | 4.1.2.  | Comparación entre procesos                       | 52        |

|           |       | 4.1.3.  | Múltiplies comparaciones                         | 54        |

|           |       | 4.1.4.  | Comparaciones derivadas                          | 55        |

|           | 4.2.  | Introdu | acción de optimizaciones                         | 56        |

|           | 4.3.  |         | ncias en Descripción                             | 57        |

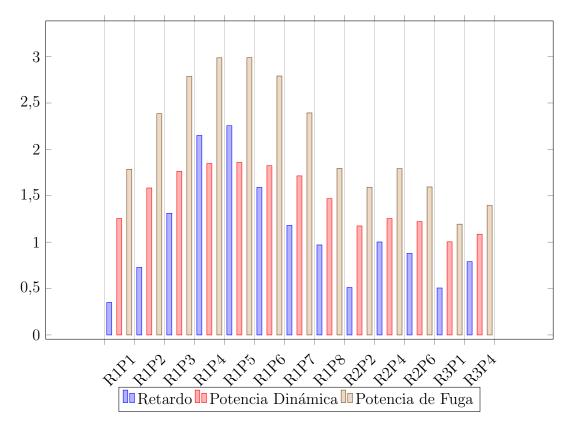

|           | 4.4.  |         | os en tecnología                                 | 59        |

|           | 4.5.  |         | ciones                                           | 61        |

|           | 4.6.  |         | ad de unidades                                   | 64        |

| <b>5.</b> | Con   | clusion | nes                                              | 69        |

| p;        | blion | rafía   |                                                  | 71        |

| וטו       | DIIO  | Jana    |                                                  | 11        |

| Α.        |       | nual de |                                                  | <b>75</b> |

|           |       |         | rimientos                                        | 75        |

|           | A.2.  | Config  | uración previa                                   | 75        |

|           | A.3.  | Ejecuc  | ión                                              | 76        |

iv Índice general

## Índice de figuras

| 1.1.  | Predicción de la tendencia de las mayores fuentes de disipación de poten-         |    |

|-------|-----------------------------------------------------------------------------------|----|

|       | cia                                                                               | 2  |

| 2.1.  | m-bit RCA adder                                                                   | 8  |

| 2.2.  | Implementación en compuertas lógicas de un FA, en rojo la ruta de retardo crítica | 8  |

| 2.3.  | Estructura de un Sumador de baja potencia                                         | 9  |

| 2.4.  | Estructura para la parte baja en un LOA                                           | 11 |

| 2.5.  | Diagrama lógico de InXA1                                                          | 14 |

| 2.6.  | Diagrama lógico de InXA2                                                          | 14 |

| 2.7.  | Diagrama lógico de InXA3                                                          | 15 |

| 2.8.  | Diagrama de bloques ETAII                                                         | 16 |

| 2.9.  | Ejemplo númerico de dos números enteros de 20 bits                                | 17 |

|       | Implementación general del ACAII, $k=\frac{l}{2}$                                 | 17 |

|       | Estructura de sumador GDA, (segmentos= $A_i, B_i; i = 0.,3$ )                     | 18 |

|       | Implementación general del GeAr: orden de derecha a izquierda                     | 19 |

|       | Diagrama de bloques de la implementación de DRUM                                  | 20 |

|       | Ejemplo númerico en el multiplicador DRUM. $(N=16, k=6)$ (a) Números              |    |

|       | de entrada (b) Entradas aproximadas (c) Resultado antes de corrimiento            |    |

|       | (d) Resultado Aproximado (e) Resultado Preciso                                    | 21 |

| 2.15. | Diagrama de bloques de la implementación de RoBa                                  | 22 |

|       | Implementación de un Divisor exacto sin restauración EXDnr: 8 bits di-            |    |

|       | videndo, 4 bits divisor                                                           | 23 |

| 2.17. | Posibles configuraciones para el divisor AXDnr: en rojo celdas exactas            |    |

|       | reemplazadas por celdas aproximadas. Sustitución (A) Vertical (B) Hori-           |    |

|       | zontal (C) Cuadrada (D) Triangular                                                | 24 |

| 2.18. | Diagrama de bloques de la implementación de SEERAD                                | 26 |

| 2.19. | Diagrama de bloques de la implementación de DAC                                   | 27 |

| 3.1.  | Estructura de carpeta general de la herramienta                                   | 32 |

| 3.2.  | Estructura de carpeta de unidades generadas                                       | 32 |

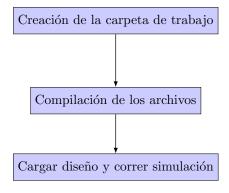

| 3.3.  | Flujo de simulación                                                               | 41 |

| 3.4.  | Flujo de Síntesis                                                                 | 42 |

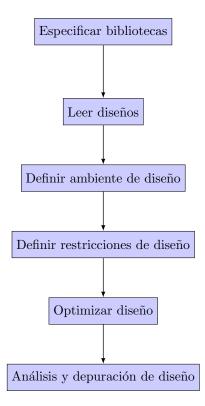

| 3.5.  | Estructura central de la herramienta                                              | 44 |

| 3.6.  | Flujo de herramienta                                                              | 48 |

| 4.1.  | Script para generación de sumadores de baja potencia                              | 50 |

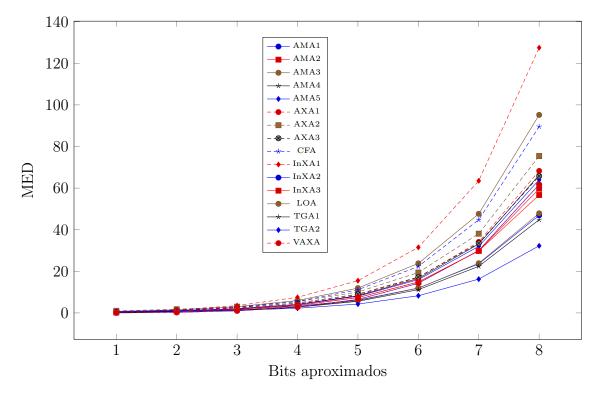

| 4.2.  | Distancia media del error en sumadores LPA de 10 bits                             | 50 |

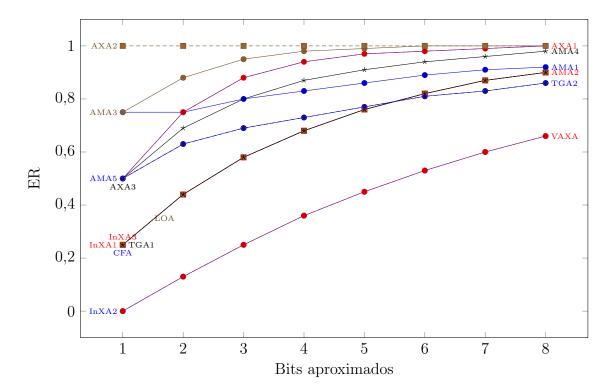

| 4.3.  | Tasa de error para sumadores LPA de 10 bits                                       | 1( |

|-------|-----------------------------------------------------------------------------------|----|

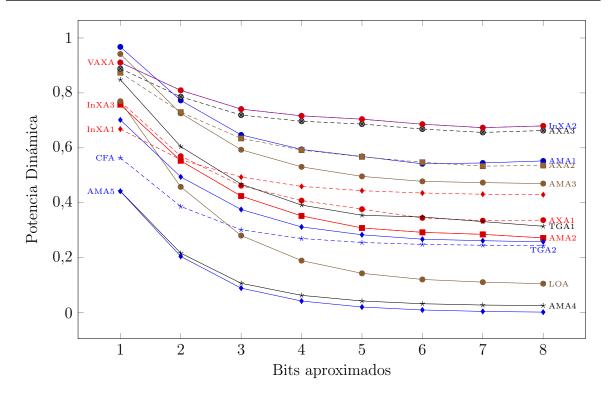

| 4.4.  | Potencia dinámica de sumadores de 10 bits tipo LPA sobre valor de refe-           |    |

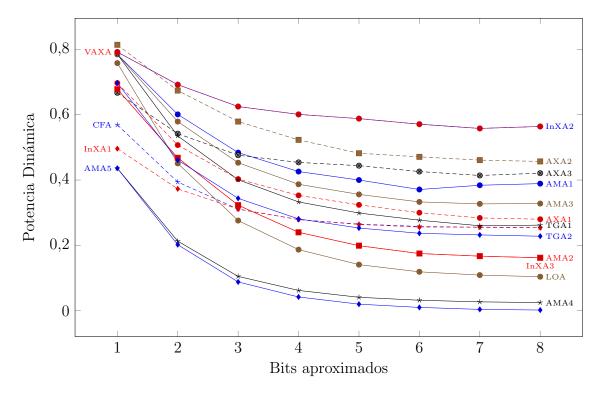

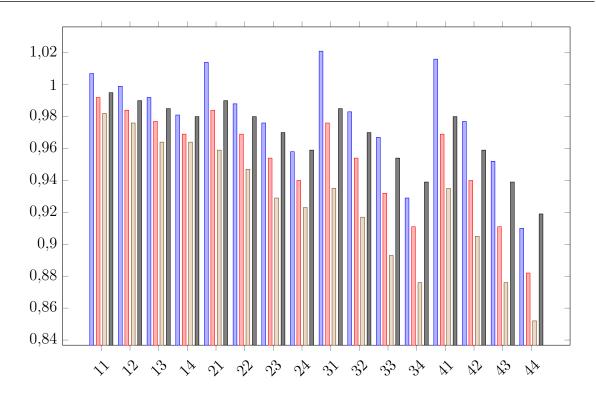

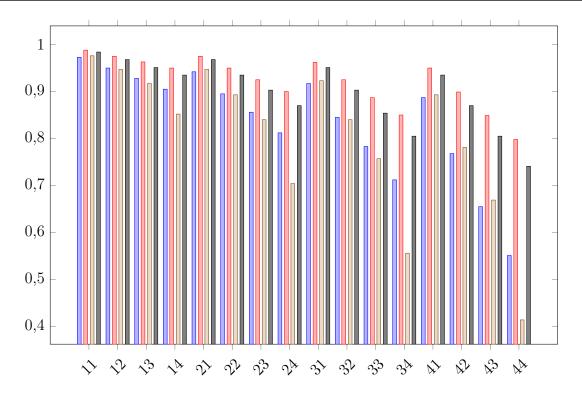

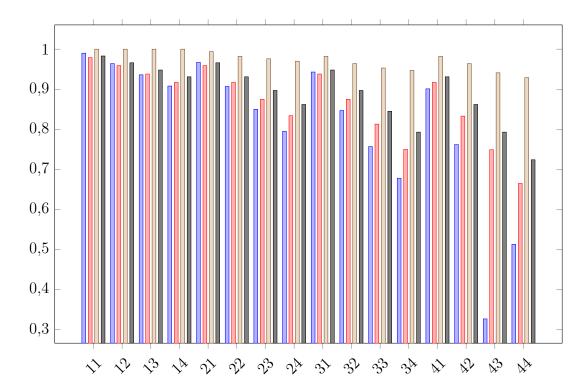

|       | rencia del sumador RCA 32.789 $\mu W$                                             | 52 |

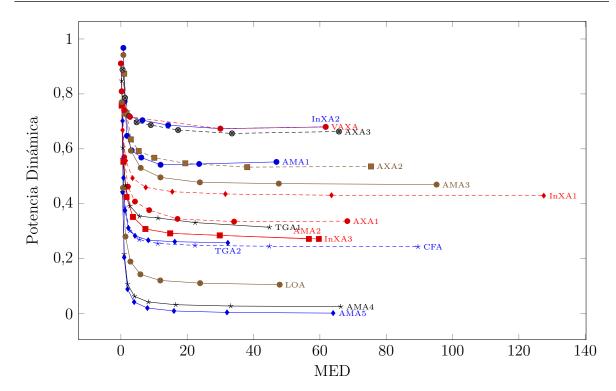

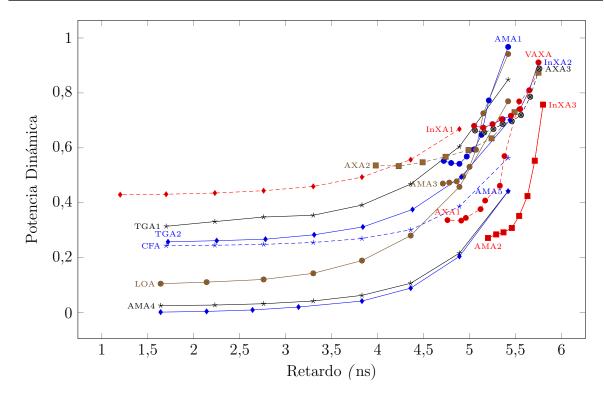

| 4.5.  | Potencia dinámica obtenida en síntesis contra valor medio de error 5              | 53 |

| 4.6.  | Potencia dinámica obtenida en post-síntesis contra valor medio de error 5         | 53 |

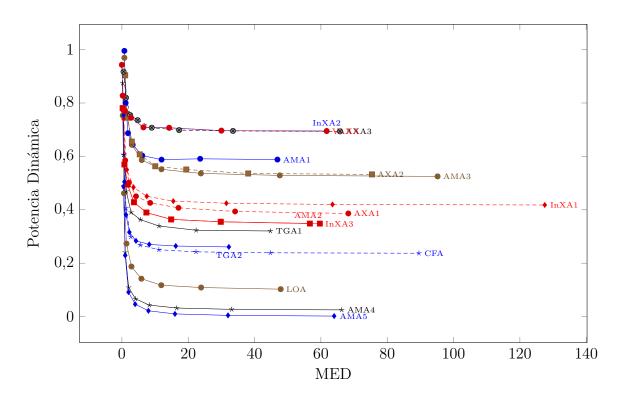

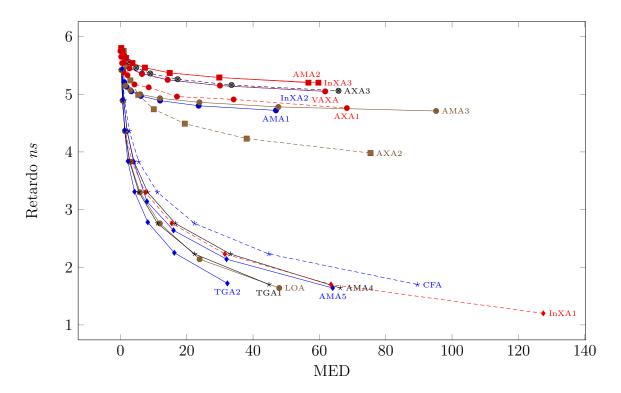

| 4.7.  | Ruta crítica o retardo contra el error medio de distancia                         | 54 |

| 4.8.  | Ruta Crítica contra Potencia                                                      | 55 |

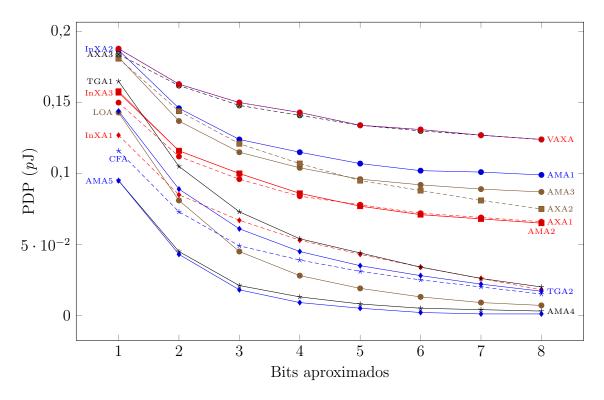

| 4.9.  | PDP para sumadores LPA de 10 bits, valor de sumador RCA $0.206~\mathrm{pJ}$ . $5$ | 55 |

| 4.10. | Línea modificada en plantilla de Síntesis de sumadores                            | 6  |

| 4.11. | Potencia dinámica de sumadores de 10 bits tipo LPA sobre valor de refe-           |    |

|       | rencia del sumador RCA 32.789 $\mu W$ con optimización                            | 56 |

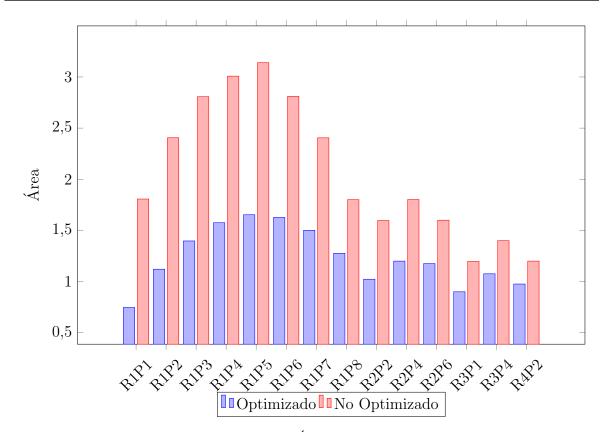

| 4.12. | Área en el GeAr                                                                   | 57 |

| 4.13. | Potencia GeAr 90nm                                                                | 58 |

| 4.14. | Potencia GeAr2 90nm                                                               | 58 |

| 4.15. | Potencia GeAr 65nm                                                                | 59 |

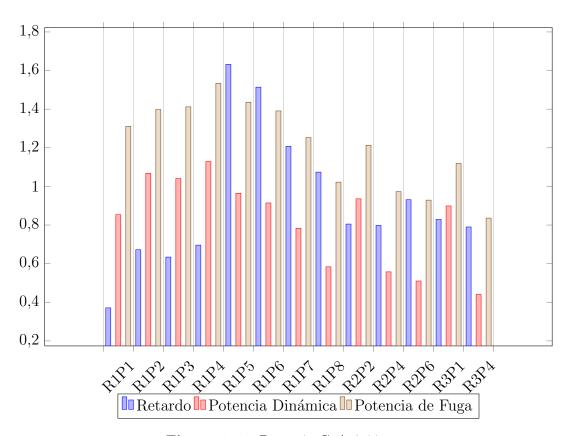

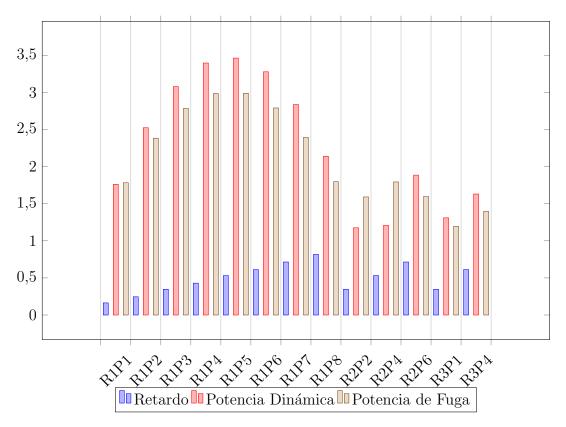

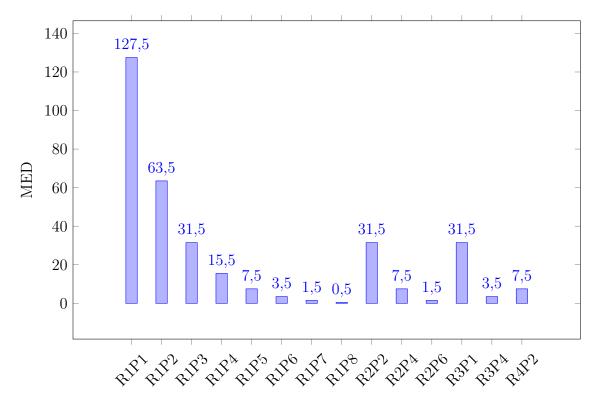

| 4.16. | MED para distintas combinaciones de R y P en el GeAr                              | 60 |

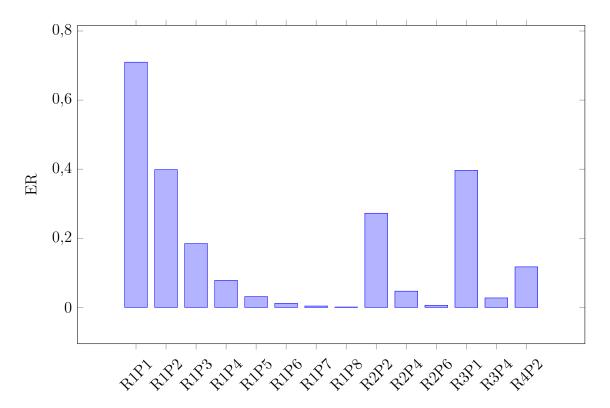

| 4.17. | ER para distintas combinaciones de R y P en el GeAr                               | 31 |

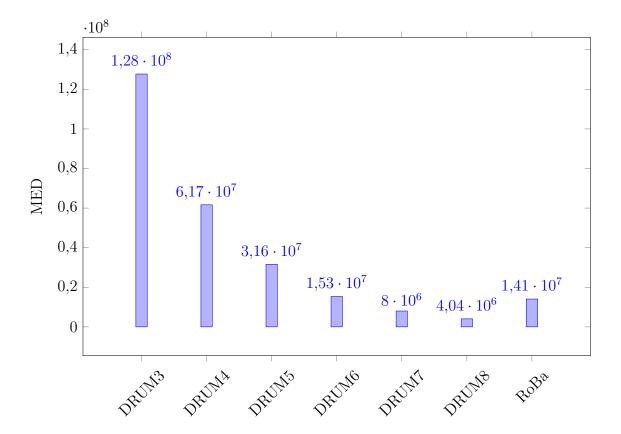

| 4.18. | MED para multiplicadores aproximados                                              | 32 |

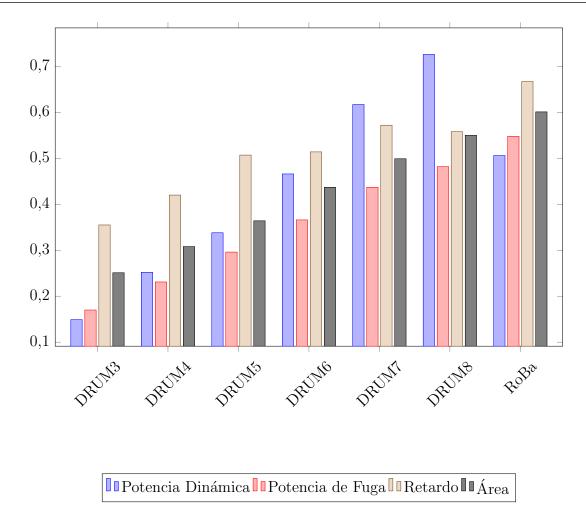

| 4.19. | Datos Multiplicadores                                                             | 3  |

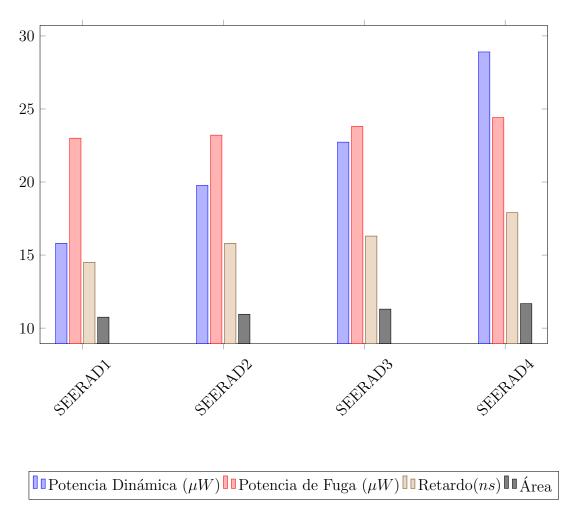

| 4.20. | Datos de divisor SEERAD                                                           | 64 |

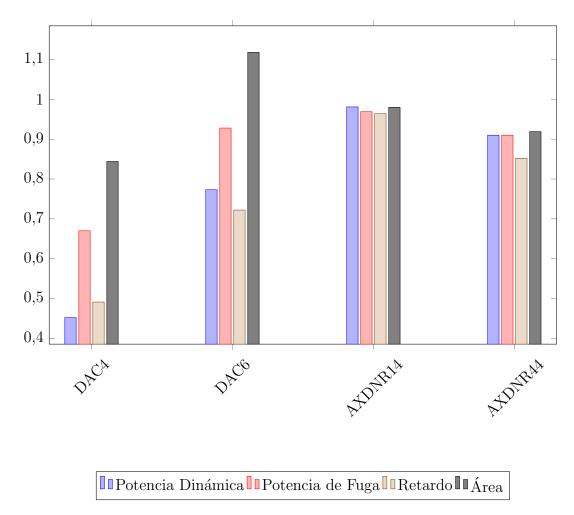

| 4.21. | Comparación divisores                                                             | 35 |

| 4.22. | Comparación para divisor AXDNR con celda AXSC1                                    | 66 |

| 4.23. | Comparación para divisor AXDNR con celda AXSC2                                    | 57 |

| 4.24. | Comparación para divisor AXDNR con celda AXSC3                                    | 8  |

## Índice de tablas

| 2.1.  | Tabla de verdad para sumador preciso                                    | Ć  |

|-------|-------------------------------------------------------------------------|----|

| 2.2.  | Tabla de verdad para sumador preciso                                    | 10 |

| 2.3.  | Tabla de verdad de las propuestas AMA ante las entradas de la tabla 2.2 | 11 |

| 2.4.  | Tabla de verdad de las propuestas AXA ante las entradas de la tabla 2.2 | 12 |

| 2.5.  | Tabla de verdad para VAXA                                               | 13 |

| 2.6.  | Tabla de verdad para TGA                                                | 14 |

| 2.7.  | Tabla de verdad para InXA                                               | 15 |

| 2.8.  | Funciones de una celdas exactas para suma y resta                       | 22 |

| 2.9.  | Funciones de celdas de resta aproximadas                                | 23 |

| 2.10. | Valores en cada grupo y su correspondiente parámetro D y L              | 25 |

| 3.1.  | Referencia a archivos generados                                         | 33 |

| 3.2.  | Biblioteca de Sumadores                                                 | 35 |

| 3.3.  | Biblioteca de Multiplicadores                                           | 36 |

| 3.4.  | Limitaciones de precisión en SEERAD                                     | 38 |

| 3.5.  | Biblioteca de divisores                                                 | 39 |

| A.1.  | Requerimientos de la herramienta                                        | 75 |

| A.2.  | Opciones de la herramienta                                              | 76 |

| A.3.  | Referencia a parámetros de unidades                                     | 77 |

viii Índice de tablas

#### Capítulo 1

#### Introducción

La eficiencia energética es actualmente un parámetro relevante en el diseño de sistemas computacionales [1]. Encontrar un equilibrio entre este parámetro y la capacidad o velocidad de procesamiento de información siempre será un desafío.

Hoy en día se ha dado un crecimiento acelerado de la cantidad de información que requiere ser procesada [2], por ejemplo el procesamiento de imágenes de muchos píxeles donde se encuentra una característica como la profundidad de bits (puede variar entre 1 bit, escala de blanco y negro, a 24 bits múltiples tonos) para cada píxel, lleva a que la información que se debe procesar aumente dependiendo de las dimensiones de la imagen, lo cual incide en el consumo de energía de los circuitos.

Aunado a esto, el fin práctico de la teoría de escalado de Dennard ha ocasionado un aumento significativo en la densidad de potencia de los chips actuales, dado que se ha incursionado rápidamente en tecnologías de fabricación de semiconductores muy pequeñas.

El nivel de integración que se ha logrado alcanzar gracias a esta reducción en tamaño trae consigo beneficios y perjuicios, por ejemplo en un procesador con más cantidad de transistores permite mejorar rendimiento pero a su vez implica mayor consumo de potencia tanto dinámica como estática [3].

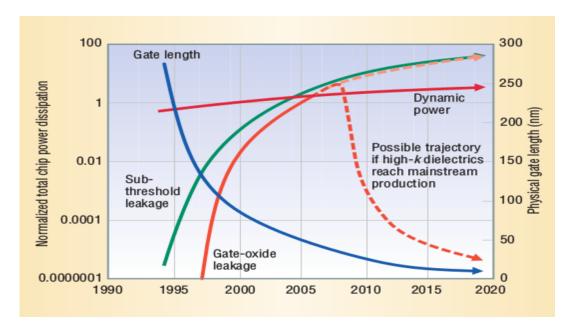

La predicción de la tendencia en disipación de potencia que tendrían los circuitos basados en tecnología CMOS se presentó hace varios años en la *International Technology Roadmap for Semiconductors*(ITRS), que es un grupo formado por expertos en el área de semiconductores[4]. Esta tendencia es creciente conforme se reduzca el tamaño en la tecnología de fabricación.

Figura 1.1: Predicción de la tendencia de las mayores fuentes de disipación de potencia

Al encontrarse la tecnología de semiconductores dentro del régimen nanométrico, el uso de cálculos precisos o libres de fallos se considera energéticamente ineficiente [5].

#### 1.1. Computación Aproximada

Recientemente se ha planteado un nuevo paradigma de diseño energéticamente eficiente [1, 5, 6, 7], debido a que aprovecha que un conjunto significativo de aplicaciones son capaces de tolerar ciertas pérdidas de precisión en los resultados de sus cálculos [6]. Existen diversas fuentes que permiten tener esta característica de tolerancia, entre ellas se pueden mencionar: limitaciones perceptuales humanas, datos de entrada redundantes y señales de entrada ruidosas [1]. Por ejemplo, debido a las limitaciones del ojo humano, en el procesamiento de una imagen, un cambio pequeño en la resolución o nítidez no afectará la percepción de la persona, de esta manera se permite un resultado aceptable en lugar de uno preciso.

Diversos trabajos alrededor de AC han propuesto múltiples técnicas a diferentes niveles de abstracción, desde el software hasta el hardware. Por ejemplo, a nivel de hardware se puede intencionalmente reducir la tensión de alimentación en algunos componentes para una compensación entre energía y precisión, a su vez en la capa del software se podrían ignorar selectivamente ciertos cálculos que no son críticos y que permiten que el sistema alcance un mismo objetivo, a lo largo de estas capas otras técnicas que se pueden encontrar son [2]:

- Programación: Loop perforation, code perforation, fusión de hilos, núcleos sintonizables, reducción de patrones.

- Arquitecura: almacenaje aproximado, extensiones ISA, aceleradores aproximados.

- Circuito: lógica imprecisa, voltage overscaling, cálculos analógicos, escalado de precisión.

1 Introducción 3

#### 1.2. Unidades aritméticas aproximadas

AC propone una solución para diseñar e implementar ciertas aplicaciones y sistemas de una manera energéticamente más eficiente, los circuitos aritméticos no han escapado de este nuevo paradigma de diseño, entre ellos el sumador presenta relevante importancia, pues, por ejemplo, en el procesamiento digital de señales los sumadores son fundamentales en la determinación de la velocidad y el consumo de potencia del sistema [8].

En la actualidad se encuentran disponibles muchas propuestas de sumadores aproximados, entre las que destacan diseños que basan su operación en especulación, segmentación y aproximación de un sumador completo. Además se encuentra una variación en los sumadores de segmentación donde para cada sub-sumador la entrada de su acarreo es seleccionada diferente. Una clasificación siguiendo esta línea de sumadores aproximados es propuesta en [8].

Para efectos de este proyecto los sumadores se dividen en dos grupos. El primer grupo cuenta con sumadores conocidos como sumadores aproximados de alto rendimiento (High-performance approximate adders, HPA) están compuestos por sub-sumadores, unidades de predicción de acarreo y/o unidades de corrección de errores [9]. El segundo grupo esta compuesto por los sumadores cuyo comportamiento se basa en aproximar al sumador completo y se conocerán a partir de aquí como sumadores aproximados de baja potencia (Low-power approximate Adders).

Como otra unidad básica en los circuitos aritméticos se encuentran los multiplicadores. Aunque han recibido menor atención que los sumadores, se pueden encontrar algunos diseños propuestos en la comunidad [5]. En [10] se mencionan tres metodologías aplicables para los multiplicadores aproximados: aproximación en la generación de productos parciales, aproximación (incluyendo truncado) en el árbol de producto parcial y usar diseños de sumadores (se señala como poco eficiente en la compensación entre precisión y energía [5]), contadores o compresores aproximados para acumular los errores parciales.

En el caso de los divisores, la atención es mucho menor debido posiblemente al bajo uso que se le da a estos en comparación con los sumadores o multiplicadores. En [11] se propone un divisor de baja potencia y bajo error, con un análisis teórico y una implementación, esta propuesta señala que puede alcanzar hasta un 70 % de ahorro de energía con la introducción de un error absoluto promedio de solo 3.08 %. Otra propuesta de divisor aproximado es SEERAD [12], donde se menciona que alcanza a ser de 14 a 300 veces menor en cuanto a consumo de energía en comparación con otros divisores.

Para algunos de estos diseños se han propuesto métricas que permiten evaluar su desempeño, entre ellas se puede mencionar la distancia de error (*Error Distance*, ED) y distancia media de error (*Mean Error Distance*, MED) propuestas en [13] y utilizadas tanto para sumadores como multiplicadores en [8] [10].

#### 1.3. Generación de unidades aritméticas aproximadas

Cuando se requiera para algún propósito específico alguna de estas unidades aritméticas, se podrían implementar de manera manual. Register-Transfer Level (RTL) es un nivel de abstracción de diseño donde se concentra en la descripción del flujo de las señales a través de registros y de operaciones lógicas sobre estas señales, permitiendo por ejemplo que el comportamiento de sumadores, multiplicadores así como divisores sea fácilmente especificado y que lenguajes de descripción de hardware (Hardware Description Language, HDL) que utilizan este nivel de abstracción puedan crear una representación del circuito descrito.

Parámetros como errores en cálculos, consumo de potencia, área o retardo, se pueden obtener de este modelo RTL siguiendo diversos procesos en herramientas especializadas en simulación y sintésis, estas herramientas a su vez requieren cierto tipo de archivos para funcionar correctamente, los cuales se deben de crear de manera manual. También una validación del correcto comportamiento de la unidad se podría realizar haciendo una comparación ante un modelo en un nivel de abstracción más alto por ejemplo C++, este modelo se realizaría de la misma manera.

En un proceso de diseño, cuando se requiera una de estas unidades aritméticas aproximadas, la etapa de elección de alguna de ellas implicaría su implementación, simulación y sintésis de manera manual para luego realizar una comparación con la que se pueda elegir la unidad que presenta mayores beneficios para la aplicación en la cual se desea utilizar, lo cual requiere bastante tiempo.

Una manera de ahorrarse este tiempo es que el proceso se realice de manera automática. Sin embargo en la actualidad no se cuenta con una herramienta que permita la exploración, elección y proporcione la respectiva implementación a nivel de RTL de unidades aritméticas aproximadas.

#### 1.4. Contribución del proyecto

Por lo anteriormente mencionado este proyecto desarrolla una herramienta capaz de generar componentes aritméticos aproximados, así como los archivos necesarios para su simulación, verificación y síntesis. La herramienta cuenta con una descripción en verilog de los componentes básicos necesarios para construir las unidades aritméticas aproximadas deseadas, así como los scripts que permiten a herramientas externas como Modelsim o Synopsys generar simulación y estimación de consumo (área, potencia) respectivamente.

Con la finalidad de que la herramienta propuesta sea de utilidad para una herramienta de *High-Level Synthesis* además de brindar a la comunidad un fácil acceso a las unidades aritméticas aproximadas, este proyecto debe de alcanzar lo siguiente:

Análisis e implementación de un conjunto de componentes aritméticos aproximados existentes en la comunidad. 1 Introducción 5

• Comparación de rendimiento de los componentes aritméticos aproximados según especificaciones dadas de diseño.

■ Creación a nivel RTL del componente aritmético aproximado deseado, así como sus respectivos modelos de simulación, verificación y sintésis.

#### Capítulo 2

#### Fundamentos teóricos y estado del arte

En este capítulo se muestran los circuitos aritméticos aproximados que se implementan en la herramienta, se detallan las características de su comportamiento y estructura. Además se introducen dos diferentes tipos de métricas sencillas que son utilizadas para determinar valores de error en las unidades aritméticas aproximadas. Por otra parte se presentan dos bibliotecas que buscan facilitar la selección de componentes que se ajusten a ciertas características al igual que la herramienta que en este trabajo se propone.

#### 2.1. Disipación de potencia en circuitos

El consumo de potencia en los circuitos CMOS proviene de dos fuentes, estático y dinámico. El primero se debe a corrientes de fuga que existen en los transistores aún así cuando el circuito esta inactivo. El consumo dinámico por su parte se debe a la carga y descarga de capacitancias de los transistores y conexiones, se da cuando hay transiciones de estado es decir cuando se da la conmutación [3].

$$P_{total} = P_{din} + P_{est}; (2.1)$$

$$P_{din} = P_{cambio} + P_{corto} + P_{compuerta}; (2.2)$$

En la ecuación 2.2  $P_{cambio}$  es debido al esfuerzo de realizar un cambio en la salida de una compuerta en la presencia de cargas de otras compuertas en el circuito,  $P_{corto}$  es la corriente de corto circuito que fluye durante las transiciones y  $P_{compuerta}$  es la corriente de túnel compuerta-óxido que fluye durante el periodo de transición. Una estimación de  $P_{cambio}$  se puede realizar asumiendo que el promedio de carga capacitiva por compuerta es  $C_L$  y calculando la potencia necesaria para cargar y descargar con una frecuencia de reloj de  $f_c$  [14],  $\alpha$  representa una estimación de la actividad de cambio (switching activity) del circuito .

$$P_{cambio} = \alpha \cdot V_{DD}^2 \cdot C_L \cdot f_c; \tag{2.3}$$

8 2.2 Sumadores

La parte estática es la suma acumulativa de todos los mecanismos de fuga [14].

#### 2.2. Sumadores

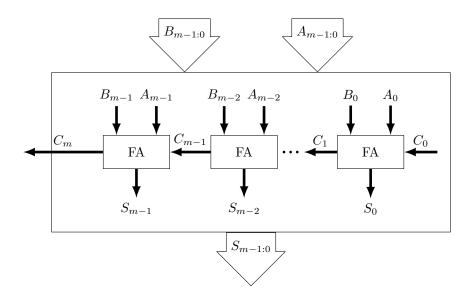

Los sumadores son ampliamente utilizados para realizar sumas binarias de dos números, un sumador comunmente usado es el  $ripple-carry\ adder\ (RCA)$ , el cual basa su operación en m 1-bit sumadores completos ( $full\ adder$ , FA) colocados en cascada, el acarreo se propaga a través de cada FA por lo que el retardo de propagación crece en proporción a m [8].

Figura 2.1: m-bit RCA adder

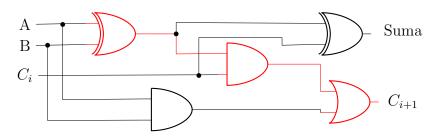

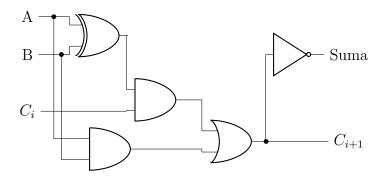

Figura 2.2: Implementación en compuertas lógicas de un FA, en rojo la ruta de retardo crítica

| En | trad | as       | Salidas |           |  |

|----|------|----------|---------|-----------|--|

| A  | В    | $C_{in}$ | Sum     | $C_{out}$ |  |

| 0  | 0    | 0        | 0       | 0         |  |

| 0  | 0    | 1        | 1       | 0         |  |

| 0  | 1    | 0        | 1       | 0         |  |

| 0  | 1    | 1        | 0       | 1         |  |

| 1  | 0    | 0        | 1       | 0         |  |

| 1  | 0    | 1        | 0       | 1         |  |

| 1  | 1    | 0        | 0       | 1         |  |

| 1  | 1    | 1        | 1       | 1         |  |

Tabla 2.1: Tabla de verdad para sumador preciso

#### 2.3. Sumadores aproximados

Se propone dos clasificaciones para los sumadores, Low Power Adder (LPA) para los que presentan mejor eficiencia enérgetica y High Performance Adder (HPA) para los que muestran mayor rapidez en cálculos.

#### 2.3.1. Sumadores de baja Potencia

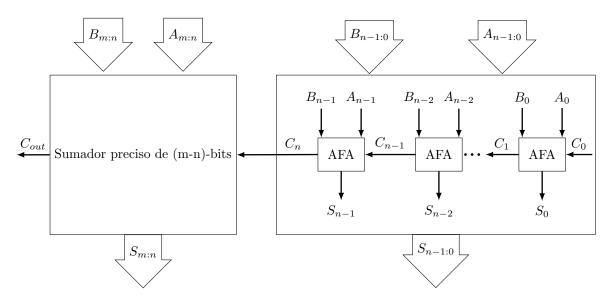

En este tipo de sumadores se busca aumentar la eficiencia energética mediante la reducción de área y en algunos casos de la ruta de retardo crítica como la mostrada en la figura 2.2, están compuestos por módulos que basan su operación en aproximar al sumador completo (approximate full adders, AFA). Para la implementación de estos sumadores se parte de un sumador común como el RCA de m-bits, la aproximación se da en los n-bits menos significativos, se modifica la estructura como la mostrada en la figura 2.1 cambiando n módulos FA por módulos AFA, mientras que los restantes (m-n)-bits más significativos se suman en FAs.

Figura 2.3: Estructura de un Sumador de baja potencia

Algunas propuestas que se pueden encontrar en la literatura son:

#### 2.3.1.1. Sumador Aproximado Espejo (AMA, por sus siglas en inglés)

Una manera convencional de implementar un FA es por medio de un sumador espejo (MA, por sus siglas en inglés) lo que lleva a que los AMA se generen mediante la modificación de la estructura básica de los MA removiendo algunos transistores. Al retirar estos transistores hay mejoras tales como el incremento de la carga y descarga de las capacitancias, menor disipación de energía y reducción de área [15]. Es importante destacar que no se pueden remover algunos transistores sin tener algún criterio, en [15] se toma en cuenta la introducción mínima de errores en la tabla de verdad del FA, asegurandose también de no generar circuitos abiertos o cortos. A continuación se muestra la tabla de verdad

| En | trad | as       | Salidas |           |  |

|----|------|----------|---------|-----------|--|

| A  | В    | $C_{in}$ | Sum     | $C_{out}$ |  |

| 0  | 0    | 0        | 0       | 0         |  |

| 0  | 0    | 1        | 1       | 0         |  |

| 0  | 1    | 0        | 1       | 0         |  |

| 0  | 1    | 1        | 0       | 1         |  |

| 1  | 0    | 0        | 1       | 0         |  |

| 1  | 0    | 1        | 0       | 1         |  |

| 1  | 1    | 0        | 0       | 1         |  |

| 1  | 1    | 1        | 1       | 1         |  |

Tabla 2.2: Tabla de verdad para sumador preciso

Mediante los criterios anteriormente mencionados, [15] propone cinco diferentes configuraciones de AMA las cuales se muestran a continuación:

- AMA1:Este configuración cuenta con ocho transistores menos que un MA convencional y en la tabla de verdad se introduce un error en el acarreo de salida  $(C_{out}, \text{ por sus siglas en inglés})$  y dos errores en la suma.

- AMA2: Se hace la observación de que en la tabla de verdad del sumador completo (tabla 2.2) que sum= $C_{out}$  para seis de ocho casos, por lo que se establece esta relación introduciendo dos errores en la suma mientras que  $C_{out}$  es correcto en todos los casos.

- **AMA3**: Se combinan AMA1 y AMA2 con lo que se introduce un error en  $C_{out}$  y tres errores en la suma.

- AMA4: Se observa en la tabla 2.2 que  $C_{out}$ =A y  $C_{out}$ =B para seis de ocho casos, entonces se fija la condición  $C_{out}$ =A, de esta manera se generan tres errores en la suma y dos en  $C_{out}$ , así también se rompe el retardo de propagación.

■ AMA5: Se hace una extención de AMA4 introduciendo un error más en la suma, el resultado de la suma se fija independiente del acarreo de entrada ( $C_{in}$ , por sus siglas en inglés) estableciendo sum=B y  $C_{out}$ =A.

| Precis | О       | AMA | 1       | AMA | 2       | AMA | 3       | AMA | 4       | AMA | 5       |

|--------|---------|-----|---------|-----|---------|-----|---------|-----|---------|-----|---------|

| Sum    | $C_out$ | Sum | $C_out$ | Sum | $C_out$ | Sum | $C_out$ | Sum | $C_out$ | Sum | $C_out$ |

| 0      | 0       | 0   | 0       | 1   | 0       | 1   | 0       | 0   | 0       | 0   | 0       |

| 1      | 0       | 1   | 0       | 1   | 0       | 1   | 0       | 1   | 0       | 0   | 0       |

| 1      | 0       | 0   | 1       | 1   | 0       | 0   | 1       | 0   | 0       | 1   | 0       |

| 0      | 1       | 0   | 1       | 0   | 1       | 0   | 1       | 1   | 0       | 1   | 0       |

| 1      | 0       | 0   | 0       | 1   | 0       | 1   | 0       | 0   | 1       | 0   | 1       |

| 0      | 1       | 0   | 1       | 0   | 1       | 0   | 1       | 0   | 1       | 0   | 1       |

| 0      | 1       | 0   | 1       | 0   | 1       | 0   | 1       | 0   | 1       | 1   | 1       |

| 1      | 1       | 1   | 1       | 0   | 1       | 0   | 1       | 1   | 1       | 1   | 1       |

Tabla 2.3: Tabla de verdad de las propuestas AMA ante las entradas de la tabla 2.2

#### 2.3.1.2. Sumador de parte baja OR (LOA, por sus siglas en inglés)

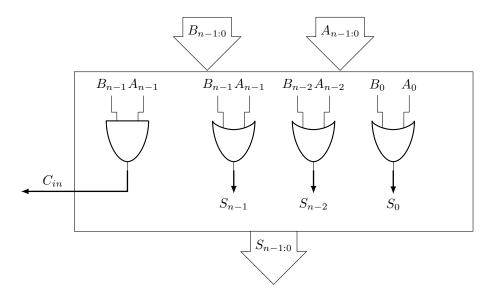

Los AFA en este caso son compuertas OR con lo que se corta la propagación del acarreo, una compuerta AND extra se encarga de generar el bit de acarreo para la parte superior lo que hace que disminuya la imprecisión del sumador aproximado [16].

Figura 2.4: Estructura para la parte baja en un LOA

#### 2.3.1.3. Approximate XOR/XNOR-based Adder (AXA)

Este tipo de sumadores se basan en compuertas XOR o NOR con multiplexores implementados por transistores de paso, tres propuestas son presentadas en [17] y se resumen a continuación:

■ **AXA1**: Esta estructura se basa en la operación XOR y se compone por ocho transistores e introduce 4 errores tanto en  $C_out$  como en la suma, las ecuaciones que representan su comportamiento son las siguientes:

$$Sum = C_{in} (2.4)$$

$$C_{out} = \overline{(A \oplus B) C_{in} + \overline{A} \cdot \overline{B}}$$

(2.5)

■ **AXA2**: Cuenta con seis transistores, que consisten en una compuerta XNOR de cuatro transistores y un bloque de transistores de paso, sus ecuaciones son las siguientes:

$$Sum = \overline{(A \oplus B)} \tag{2.6}$$

$$C_{out} = (A \oplus B) C_{in} + AB \tag{2.7}$$

■ AXA3: Es una extensión de AXA2 donde se utilizan dos transistores más en una configuración de transistor de paso con lo que se tiene una mejor precisión en la suma, sus ecuaciones se presentan a continuación:

$$Sum = \overline{(A \oplus B) C_{in}} \tag{2.8}$$

$$C_{out} = (A \oplus B) C_{in} + AB \tag{2.9}$$

Tabla 2.4: Tabla de verdad de las propuestas AXA ante las entradas de la tabla 2.2

| Precis | О       | $AXA_1$ |         | $AXA_2$ | 2       | $AXA_3$ | 3       |

|--------|---------|---------|---------|---------|---------|---------|---------|

| Sum    | $C_out$ | Sum     | $C_out$ | Sum     | $C_out$ | Sum     | $C_out$ |

| 0      | 0       | 0       | 0       | 1       | 0       | 0       | 0       |

| 1      | 0       | 1       | 0       | 1       | 0       | 1       | 0       |

| 1      | 0       | 0       | 1       | 0       | 0       | 0       | 0       |

| 0      | 1       | 1       | 0       | 0       | 1       | 0       | 1       |

| 1      | 0       | 0       | 1       | 0       | 0       | 0       | 0       |

| 0      | 1       | 1       | 0       | 0       | 1       | 0       | 1       |

| 0      | 1       | 0       | 1       | 1       | 1       | 0       | 1       |

| 1      | 1       | 1       | 1       | 1       | 1       | 1       | 1       |

Una propuesta basada en AXA es presentanda en [18] bajo el nombre Vdd-connected 1-bit AXA-based adder (VAXA), lo que busca es generar resultados correctos cuando  $C_{in}$  es '0', su tabla de verdad se muestra a continuación.

VAXA Preciso Sum  $C_{out}$ Sum  $C_{out}$

Tabla 2.5: Tabla de verdad para VAXA

## 2.3.1.4. Sumador aproximado basado en compuertas de transmision (TGA, por sus siglas en inglés)

Al igual que en algunas de las propuestas mencionadas anteriormente, las dos propuestas de TGA presentadas en [19] buscan reducir la complejidad de circuito en cuanto al número de transistores removiendo algunas compuertas del sumador completo.

■ TGA1: En este caso se establece  $C_{out}$ =B mediante la observación que seis de los ocho casos presentes en la tabla 2.2 presentan esta condición, así la propagación del acarreo es reducida, la suma también es modificada resultando en dos errores de ocho casos posibles, a continuación las ecuaciones para el TGA1:

$$Sum = (A \overline{\oplus} B) C_{in} + A \overline{B}$$

(2.10)

$$C_{out} = B (2.11)$$

■ TGA2: La observación en este caso es que existen cautro casos de seis donde si A o B son '1'  $C_{out}$  también es '1', de esta manera para calcular el  $C_{out}$  se utiliza una solo compuerta OR. Al igual que en el TGA1 no hay propagación de acarreo debido a que el  $C_{out}$  depende únicamente de las entradas A y B, sus ecuaciones son las siguientes:

$$Sum = (A \overline{\oplus} B) C_{in} \tag{2.12}$$

$$C_{out} = A + B \tag{2.13}$$

| Preciso |           | TGA1 |           | TGA2 |           |

|---------|-----------|------|-----------|------|-----------|

| Sum     | $C_{out}$ | Sum  | $C_{out}$ | Sum  | $C_{out}$ |

| 0       | 0         | 0    | 0         | 0    | 0         |

| 1       | 0         | 1    | 0         | 1    | 0         |

| 1       | 0         | 0    | 1         | 0    | 1         |

| 0       | 1         | 0    | 1         | 0    | 1         |

| 1       | 0         | 1    | 0         | 0    | 1         |

| 0       | 1         | 1    | 0         | 0    | 1         |

| 0       | 1         | 0    | 1         | 0    | 1         |

| 1       | 1         | 1    | 1         | 1    | 1         |

Tabla 2.6: Tabla de verdad para TGA

#### 2.3.1.5. Sumador aproximado inexacto (InXA, por sus siglas en inglés)

Se presentan en [20] tres propuestas de sumadores aproximados que como características se mencionan un número menor de transistores que los diseños de AXA y AMA así como menos resultados incorrectos tanto en la suma como en el  $C_{out}$ .

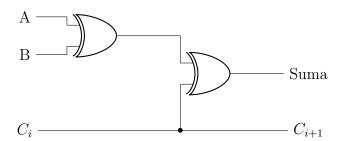

■ InXA1: La aproximación se da en el acarreo mientras se mantiene la suma de manera precisa, el diagrama en compuertas lógicas de la estructura del InXA1 se muestra a continuación:

Figura 2.5: Diagrama lógico de InXA1

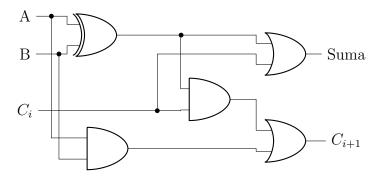

■ InXA2: En este caso se mantiene el acarreo preciso mientras que se aproxima la suma, su diagrama es el siguiente:

Figura 2.6: Diagrama lógico de InXA2

■ InXA3: Al igual que el InXA2 esta configuración cuenta con un acarreo preciso y una suma aproximada, los errores son introducidos en diferentes resultados.

Figura 2.7: Diagrama lógico de InXA3

| Pre | ciso      | InX | A1        | InX | A2        | InX | A3        |

|-----|-----------|-----|-----------|-----|-----------|-----|-----------|

| Sum | $C_{out}$ | Sum | $C_{out}$ | Sum | $C_{out}$ | Sum | $C_{out}$ |

| 0   | 0         | 0   | 0         | 0   | 0         | 1   | 0         |

| 1   | 0         | 1   | 1         | 1   | 0         | 1   | 0         |

| 1   | 0         | 1   | 0         | 1   | 0         | 1   | 0         |

| 0   | 1         | 0   | 1         | 1   | 1         | 0   | 1         |

| 1   | 0         | 1   | 0         | 1   | 0         | 1   | 0         |

| 0   | 1         | 0   | 1         | 1   | 1         | 0   | 1         |

| 0   | 1         | 0   | 0         | 0   | 1         | 0   | 1         |

| 1   | 1         | 1   | 1         | 1   | 1         | 0   | 1         |

Tabla 2.7: Tabla de verdad para InXA

#### 2.3.1.6. Sumador de acarreo libre (CFA, por sus siglas en inglés)

En [21] se propone un sumador aproximado con el nombre de AFA, debido a la generalidad de este nombre se le asigna CFA según una de las características con las que cuenta esta propuesta. La observación que se hace en este caso es que al minimizar el número de literales se reduce la complejidad del circuito en cuanto a ruta crítica, conmutación de capacitancia y área [21], se puede minimizar este número mediante complemento de minterminos y/o maxterminos. Siguiendo estos enfoques se llega a la propuesta presentada mediante las siguientes ecuaciones:

$$Sum_i = A_i \oplus B_i \oplus A_{i-1} \tag{2.14}$$

$$C_{out} = A_i (2.15)$$

De la ecuación 2.15 se extrae el nombre, ya que el  $C_{in_i}$  de cada módulo no depende del acarreo anterior  $C_{out_{i-1}}$ .

#### 2.3.2. Sumadores de alto rendimiento

Este tipo de sumadores le apuestan a reducir la ruta de retardo crítico mediante la segmentación de la suma completa en sub-sumadores, cada uno de estos ejecuta la suma de manera precisa en el segmento de bits correspondientes, lo que hace que la ruta de retardo se reduzca al tamaño de cada sub-sumador. La contra parte en esta reducción en el retardo es que estos sumadores suelen tener una mayor área.

#### 2.3.2.1. Sumador de error tolerante II (ETAII, por sus siglas en inglés)

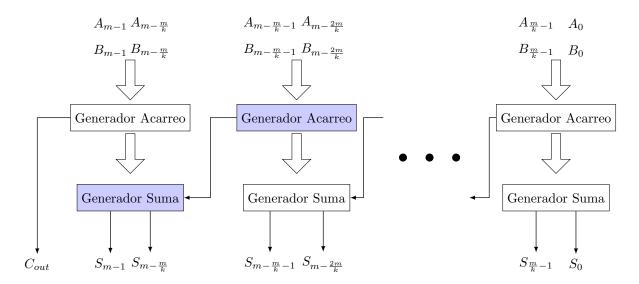

Una primera propuesta de este tipo de sumador es Error-Tolerant Adder I (ETA I) el cual tenía problemas calculando la suma para números pequeños, ETAII se propone en [22] con el fin de resolver este problema. Para obtener la estructura del ETAII, se divide un sumador de m bits en k sub-sumadores (k>=2), cada uno de estos bloques contiene m/k bits, por lo que m tiene que ser divisible entre k. Cada sub-sumador se compone de un generador de acarreo y un generador de suma, características importantes a mencionar de esta estructura es que el generador de acarreo no toma en cuenta el acarreo proveniente del sub-sumador anterior, mas sin embargo el generador de suma si lo considera. De esta forma la propagación del acarreo solo se da entre dos bloques consecutivos.

Figura 2.8: Diagrama de bloques ETAII

#### 2.3.2.2. Sumador casi correcto (ACAI, por sus siglas en inglés)

En este caso los sub-sumadores están compuestos por l bits de los cuales se utilizan l-1 bits para producir el bit de suma en la en la posición l de cada sub-sumador, en otras palabras a partir del bit en la posición l de un sumador de m bits, se toman los l-1 bits anteriores para generar el acarreo necesario, lo que reduce la propagación del acarreo a la misma que tendría un sumador de l bits [23], en este tipo de sumador existe un traslape entre los sub-sumadores.

| 101100 | $0\ 1\ 1\ 0\ 0\ 0$    | $\begin{smallmatrix} & & \\ 0 & 1 & 0 & 1 & 0 & 1 \end{smallmatrix}$ | 101011 |

|--------|-----------------------|----------------------------------------------------------------------|--------|

|        |                       |                                                                      |        |

|        | 0 1 1 0 1 1 0 1 1 1 0 | 101011101                                                            |        |

|        | 10110001100           | $1\; 1\; 0\; 1\; 0\; 1\; 0\; 1\; 1$                                  |        |

Figura 2.9: Ejemplo númerico de dos números enteros de 20 bits

#### 2.3.2.3. Sumador de precisión configurable (ACAII, por sus siglas en inglés)

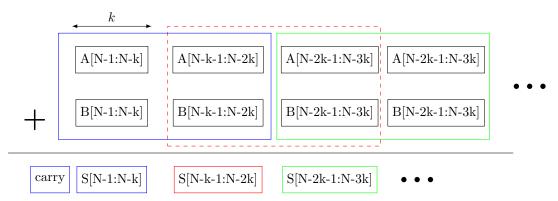

El comportamiento de este sumador es similar al del ETAII, lo que lo diferencia es la estructura, en este caso existe un traslape entre los segmentos de bits que son sumados por cada sub-sumador, lo que incrementa la precisión según [24]. En este caso cada sub-sumador se compone por l bits con los cuales se realiza una sub-suma de donde se toman los l/2 bits más significativos de su resultado para completar la suma general, la excepción es para el primer sub-sumador donde se toman completamente el resultado de l bits.

Figura 2.10: Implementación general del ACAII,  $k=\frac{l}{2}$

#### 2.3.2.4. Sumador de precisión graciosamente-degradable (GDA)

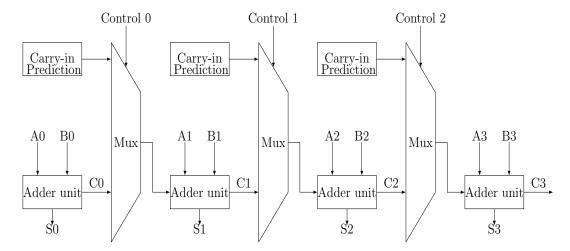

Este sumador propuesto en [25] apuesta por ser reconfigurable para lograr una mejor precisión, uno de los mecanismos que utiliza es que la longitud de cada sub-sumador sea reconfigurable. Para esto se segmenta una suma de m bits en sub-sumadores de l bits, cada uno de estos sub-sumadores esta conectado mediante multiplexadores que seleccionan el acarreo de entrada entre el sub-sumador anterior o una unidad de predicción.

Figura 2.11: Estructura de sumador GDA, (segmentos= $A_i, B_i; i = 0.,3$ )

## 2.3.2.5. Sumador Genérico de precisión configurable (GeAr, por sus siglas en inglés)

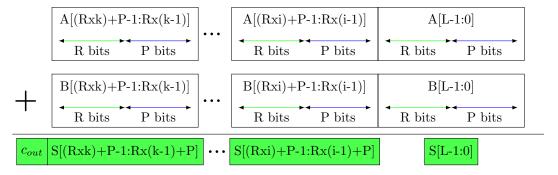

En [9] se propone un sumador genérico con precisión configurable (GeAr, por sus siglas en inglés), el mismo segmenta como los anteriores una suma de m bits en sumas de l bits realizadas por k sub-sumadores, además se define R como bits resultantes y P como bits previos. R son los bits que contribuyen con la suma final y P son utilizados para predecir el acarreo en cada sub-sumador. Solo el primer sub-sumador presenta una excepción aportando l bits a la suma final, relaciones importantes entre estos parámetros son presentadas a continuación.

$$l = R + P \tag{2.16}$$

$$k = ((m - l)/R) + 1 (2.17)$$

Para el primer sub-sumador se cumple:

$$Sum[l-1:0] = A[l-1:0] + B[l-1:0]$$

(2.18)

El resultado de los siguientes sub-sumadores se pueden obtener mediante:

$$Sum[(R*i) + P - 1 : R*(i-1) + P] = A[R*i) + P - 1 : R*(i-1)] + B[R*i) + P - 1 : R*(i-1)]$$

(2.19)

donde 1 < i < = k.

Figura 2.12: Implementación general del GeAr: orden de derecha a izquierda

# 2.4. Multiplicadores

Esta operación suele ser más compleja que la suma, en su proceso incluye tres elementos: multiplicador, multiplicador y producto. El procedimiento general es recorrer el multiplicador desde el bit menos significativo al más significativo. Se generan productos parciales los cuales, para cada bit del multiplicador, es el multiplicando si el bit del multiplicador es 1 y 0s si el bit es 0. Luego cada producto parcial es desplazado hacia la izquierda un espacio relativo a su previo producto parcial. Cuando se obtienen todos los productos parciales los mismos se suman. Para una multiplicación donde el multiplicando y multiplicador esten compuestos por N bits el producto será 2N bits. Existen varios métodos para realizar la multiplicación entre ellos: algoritmo de Booth, sequencia de suma-corrimiento y multiplicador en arreglo.

# 2.5. Multiplicadores Aproximados

# 2.5.1. Multiplicador imparcial de rango dinámico para aplicaciones aproximadas (DRUM, por sus siglas en inglés)

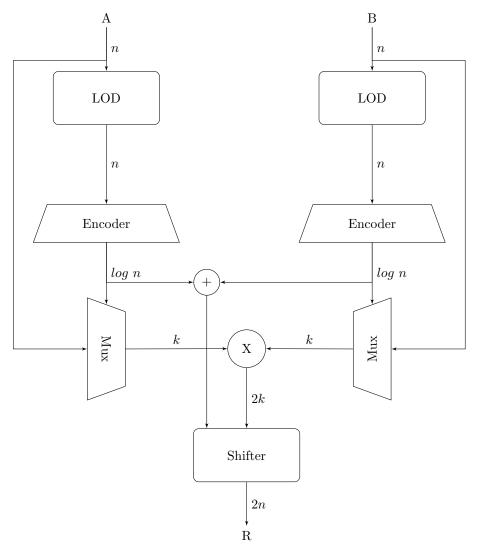

La premisa con la que trabaja esta propuesta en [26] es que no todos los bits de un número son igualmente importantes, por lo que se limita la cantidad de bits que se aplican a un multiplicador central preciso seleccionando cuidadosamente un rango para cada uno de los operandos.

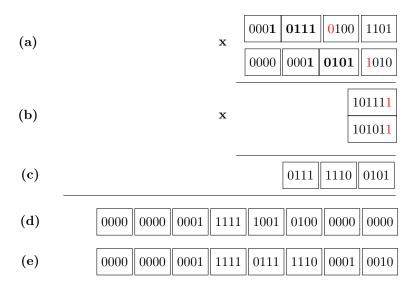

El modo de operación que sigue DRUM es el siguiente, asumiendo que ambos operandos son de N bits, primero se obtiene la posición del bit 1 más significativo mediante módulos que detectan este bit llamados detector de uno conductor (LOD, por sus siglas en inglés), luego a partir de la posición del bit más significativo se seleccionan los k-2 bits consecutivos basados en la precisión requerida, donde k es definido en etapa de diseño y especifica el ancho de bits que utilizará el multiplicador central.

Para reducir el error se aproximan los bits menos significativos restantes, para esto sea t la posición donde se encuentra el bit 1 más significativo con 0 <= t <= N-1, así el valor de los t-k+2 bit menos significativos restantes esta entre 0 y  $2^{t-k+2} - 1$ , si

se asume una distribucion uniforme para los valores de los operandos, el valor esperado es casi igual a  $2^{t-k+1}$ , de esta manera se aproximan los t-k+2 bits colocando un 1 en la posición t-k+1 y 0 desde la posición t-k a 0, luego estos ceros son truncados y se opera en el multiplicador central los operandos de k bits formados [26].

Figura 2.13: Diagrama de bloques de la implementación de DRUM

**Figura 2.14:** Ejemplo númerico en el multiplicador DRUM. ( $N=16,\ k=6$ ) (a) Números de entrada (b) Entradas aproximadas (c) Resultado antes de corrimiento (d) Resultado Aproximado (e) Resultado Preciso

# 2.5.2. Multiplicador aproximado redondeado a base (RoBa, por sus siglas en inglés)

El algoritmo propuesto en [27] para este multiplicador aprovecha que al tener números redondeados en potencia de 2 las multiplicaciones se pueden realizar mediante corrimientos. Sea A y B multiplicando y multiplicador respectivamente, sus representaciones redondeadas serán  $A_r$  y  $B_r$ . La operación de multiplicación puede ser escrita como:

$$A \cdot B = (A_r - A) \cdot (B_r - B) + A_r \cdot B + B_r \cdot A - A_r \cdot B_r$$

(2.20)

De esta expresión es la que se observa que hay tres términos que se pueden realizar mediante corrimiento,  $A_r \cdot B$ ,  $B_r \cdot A$ ,  $A_r \cdot B_r$ . El término restante  $(A_r - A) \cdot (B_r - B)$  es omitido con la observación de que su implementación en hardware es compleja y que el peso en el resultado final suele ser pequeño, de esta forma la aproximación propuesta de la ecuación 2.20 es :

$$A \cdot B \approx A_r \cdot B + B_r \cdot A - A_r \cdot B_r \tag{2.21}$$

2.6 Divisores

Figura 2.15: Diagrama de bloques de la implementación de RoBa

## 2.6. Divisores

Proceso más lento que el de la multiplicación, incluye cuatro elementos: dividendo, divisor, cociente y residuo. Existen varias técnicas para realizar la división entre ellas: secuencia de corrimiento-sumar/restar, método SRT, división multiplicativa y división en arreglo.

# 2.7. Divisores Aproximados

A pesar de que cuentan con un menor uso, en la literatura se encuentran propuestas interesantes, de las cuales se presentan a continuación tres, SEERAD, DAC y AXDNR, estos últimos dos presentan características similares en cuanto a la estructura de sus resultados mas no de su operación.

# 2.7.1. Divisor aproximado sin restauración (AXDnr, por sus siglas en inglés)

El diseño de este divisor toma como ventaja el hecho que la operación básica de la división es la resta. Una celda exacta de resta es muy similar a una celda exacta de suma como se puede apreciar en la siguiente tabla tomada de [28] que muestra sus respectivos comportamientos lógicos.

Tabla 2.8: Funciones de una celdas exactas para suma y resta

|       | Suma o Diferencia          | $C_{out} \circ B_{out}$                                        |

|-------|----------------------------|----------------------------------------------------------------|

| Suma  | $S=X\oplus Y\oplus C_{in}$ | $C_{out} = X \oplus Y \cdot C_{in} + XY$                       |

| Resta | $D=X\oplus Y\oplus B_{in}$ | $B_{out} = \overline{X \oplus Y} \cdot B_{in} + \overline{X}Y$ |

En las relaciones anteriores  $B_{in}$  y  $B_{out}$  se refieren a los bit que se toman prestados de

la parte baja y parte alta respectivamente. Al igual que para los sumadores un restador de N bits se puede formar colocando en cascada N celdas de resta exactas.

Para generar un divisor exacto sin restauración (EXDnr, por sus siglas en inglés) [28] presenta la celda básica con la que se compone EXDCnr, la misma esta compuesta por una compuerta XOR y una celda de resta exacta (EXSC, por sus siglas en inglés). Una señal de control Q es introducida, esta permite que la celda se pueda configurar como un restador exacto o un sumador exacto Q=0 y Q=1 respectivamente, las relaciones de su comportamiento se muestran a continuación.

$$R = X \oplus (Y \oplus Q) \oplus B_{in}$$

$$B_{out} = \overline{X \oplus Y \oplus Q} \cdot B_{in} + \overline{X}(Y \oplus Q)$$

(2.22)

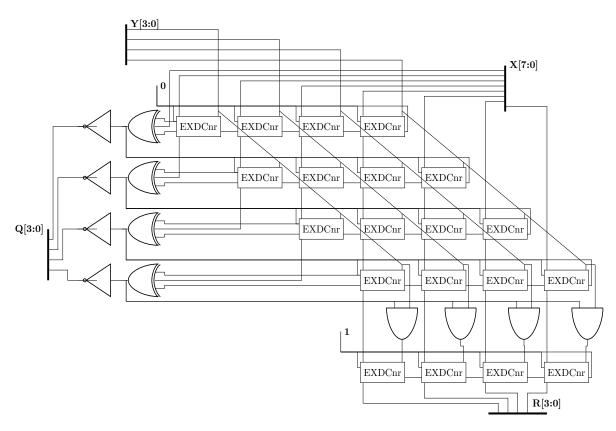

**Figura 2.16:** Implementación de un Divisor exacto sin restauración EXDnr: 8 bits dividendo, 4 bits divisor

Tres celdas de restadores aproximados (AXSC, por sus siglas en inglés) son propuestos en [28], las funciones lógicas que representan su comportamiento se muestran en la siguiente tabla.

Tabla 2.9: Funciones de celdas de resta aproximadas

|       | Diferencia                 | $B_{out}$                                                     |

|-------|----------------------------|---------------------------------------------------------------|

| AXSC1 | $X \oplus Y + B_{in}$      | $\overline{X \oplus Y} \cdot B_{in} + \overline{X}Y$          |

| AXSC2 | $X \oplus Y \oplus B_{in}$ | $B_{in}$ o D                                                  |

| AXSC3 | $B_{out}$                  | $\overline{X \oplus Y} \cdot \mathbf{B}_{in} + \overline{X}Y$ |

Teniendo en cuentas las celdas anteriormente presentadas se puede hacer una modificación en la celda EXDCnr para obtener una versión aproximada AXDCnr mediante la sustitución de la celda de resta exacta EXSC por una de las celdas de resta aproximadas AXSC.

Sustitución similar se hace en el divisor exacto sin restauración para obtener la versión aproximada AXDnr, sustituyendo la celda exacta EXDCnr por la aproximación AXD-Cnr.

Cuatro configuraciones pueden ser obtenidas mediante la sustitución de estas celdas en el divisor exacto, sustitución vertical, horizontal, en cuadrado y triangular.

**Figura 2.17:** Posibles configuraciones para el divisor AXDnr: en rojo celdas exactas reemplazadas por celdas aproximadas. Sustitución (A) Vertical (B) Horizontal (C) Cuadrada (D) Triangular

# 2.7.2. Divisor aproximado con base redondeada de alta velocidad y eficiencia energética (SEERAD, por sus siglas en inglés)

La propuesta de [29] es un divisor de alta velocidad y aún así energéticamente eficiente. A su vez la precisión de SEERAD es configurable en etapa de diseño, esta característica hace que el área de hardware requerido y el retardo del componente puedan aumentar o disminuir según la precisión con la que se elija trabajar. La síntesis del algoritmo que implementa este divisor es cambiar el divisor a su valor redondeando más cercano y operar con este nuevo número.

Sea A el dividendo y B el divisor, el número más cercano se expresa de la siguiente manera  $B_r = \frac{2^{K+L}}{D}$  donde  $2^K$  es la base del logaritmo de B que se representará como  $B_f$ , de esta manera se aproxima la división mediante la siguiente ecuación.

$$\frac{A}{B} \approx \frac{A}{B_r} = \frac{A}{\frac{2^{K+L}}{D}} = \frac{D \cdot A}{2^{K+L}} = \frac{D \cdot A}{2^L \cdot B_f}$$

(2.23)

En la ecuación 2.23 se muestran dos parámetros importantes en la determinación de la precisión con la que se puede contar para este divisor, D y L (Tupla). Para determinar cual es la mejor tupla para la cantidad de bits con las que se quiere trabajar se debe realizar una búsqueda exahustiva, la cual consiste en cambiar el valor de A desde 0 hasta el máximo y luego el error de dividir A con  $B_f$  es comparado al hacer la división con B, así la tupla con el menor error relativo será la elegida.

Si se utiliza la tupla encontrada para todos los anchos de bits, se optiene una implementación con menor retardo pero a un costo de imprecisión mayor. Para mejorar la precisión se pueden considerar diferentes tuplas para cierta cantidad de bits dada, para lograrlo se forman diferentes grupos dependiendo de la combinación de los bitse más significativos de B, esto incrementa el retardo.

En [29] bajo la búsqueda exahustiva se muestran cuatro niveles de precisión dados por la relación  $log_2|Group|+1$ , cabe destacar que al aumentar la cantidad de grupos se incrementa la precisión pero a su vez sobrecalentamiento [29]. En estos grupos propuestos el valor de D es seleccionado tal que el error relativo sea mínimo, a su vez para poder alcanzar una implementación en hardware más simple y con menor retardo se selecciona un valor de L para todos los grupos en cada nivel de precisión. Toda esta clasificación de grupos y niveles se muestran en la siguiente tabla.

| Tabla 2.10: | Valores en | cada grupo | y su correspon | diente | parámetro D | vΙ | , |

|-------------|------------|------------|----------------|--------|-------------|----|---|

|-------------|------------|------------|----------------|--------|-------------|----|---|

| Grupo | Nivel de precisión | Índíce | В        | D   | L |

|-------|--------------------|--------|----------|-----|---|

| 1     | 1                  | 0      | 001XX    | 5   | 3 |

|       |                    |        |          |     |   |

| 2     | 2                  | 0      | 0010XX   | 12  | 4 |

|       |                    | 1      | 0011XX   | 9   |   |

|       |                    |        |          |     |   |

| 4     | 3                  | 0      | 00100XX  | 28  | 5 |

|       |                    | 1      | 00101XX  | 24  |   |

|       |                    | 2      | 00110XX  | 20  |   |

|       |                    | 3      | 00111XX  | 17  |   |

|       |                    |        |          |     |   |

| 8     | 4                  | 0      | 001000XX | 120 | 7 |

|       |                    | 1      | 001001XX | 108 |   |

|       |                    | 2      | 001010XX | 97  |   |

|       |                    | 3      | 001011XX | 88  |   |

|       |                    | 4      | 001100XX | 82  |   |

|       |                    | 5      | 001101XX | 76  |   |

|       |                    | 6      | 001110XX | 70  |   |

|       |                    | 7      | 001111XX | 66  |   |

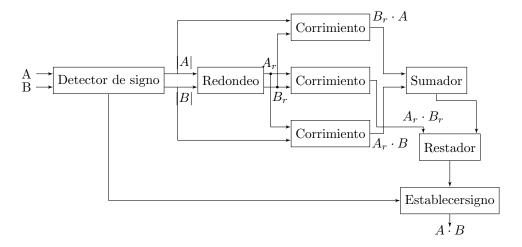

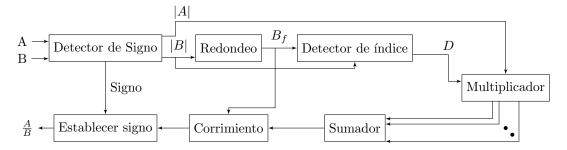

El procedimiento generado por esta estructura es como sigue, sea A y B números de N bits, se determina el signo tanto del divisor como del dividendo (se asume que ambos números se encuentren en complemento a dos), en el bloque de redondedo se determina la base de B en la forma de  $2^K = B_f$ , luego  $B_f$  es usado para determinar los valores D y L según el nivel de precisión elegido. Una vez que se tenga el valor de D se procede a realizar la multiplicación, para esta se utiliza unidades de corrimiento y un sumador.

Importante característica de este divisor es el tamaño de bits con los se realizan sus operaciones, la multiplicación generará un resultado de 2N bits, la unidad de corrimiento se encarga de correr la entrada K+L bits hacia la derecha, al realizar este corrimiento no se desechan bits por lo que la salida de este será de 2N+L, donde N son los bits de la parte entera y N+L representan la parte fraccionaria del número, por último se determina el signo del resultado [29].

Figura 2.18: Diagrama de bloques de la implementación de SEERAD

# 2.7.3. Divisor dinámico de baja potencia para aplicaciones aproximadas (DAC, por sus siglas en inglés)

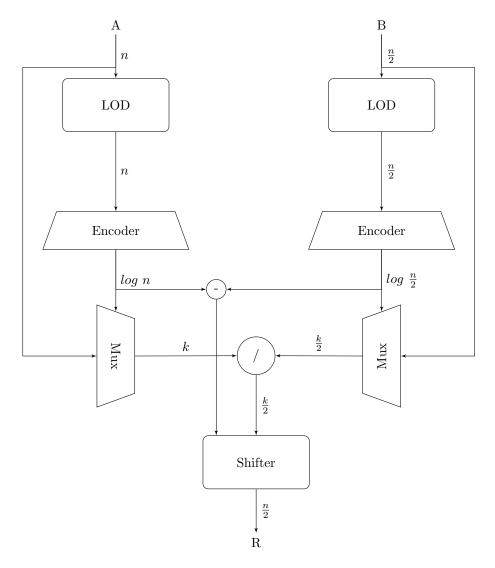

Similar a como trabaja el DRUM, toma como ventaja la importancia de algunos bits sobre otros en una representación númerica, con estos bits que cuentan con mayor peso se hace la operación de división en un divisor exacto central y utiliza algunos módulos extra para determinar cuales son estos bits más significativos. Entre estos elementos adicionales se encuentran detectores de uno conductor, multiplexadores y decodificadores al igual que los utilizados para el DRUM.

El primer paso del algoritmo que este propuesta utiliza es identificar el uno conductor en cada operando, seguido se define el parámetro k como el rango del divisor exacto, con este se pueden tener diversos intercambios entre precisión y otras métricas de diseño. A partir del uno conductor se eligen los siguientes k-1 bits, este conjunto es el que se dirige hacia el divisor exacto, los bits restantes son truncados [30].

Figura 2.19: Diagrama de bloques de la implementación de DAC

Cabe destacar ciertas características, DAC esta diseñado para mantener un radio de 2/1 entre el dividendo y el divisor por lo cual ante dos operandos de n bits y de n/2 respectivamente la salida será de n/2 bits. Si el uno conductor se encuentra entre los k bits no se necesita truncado y este se traslada directamente al divisor exacto central [30].

## 2.8. Métricas

# 2.8.1. Producto retardo potencia (PDP, por sus siglas en inglés)

Al igual que la energía la unidad de medida es el Julio, se considera cuando se quiere optimizar tanto rendimiento cocmo consumo de potencia. Se define por:

$$PDP = P_{promedio} \cdot T_{cp}; \qquad (2.24)$$

Donde  $T_{cp}$  es el retardo dado por la ruta de retardo crítica y  $P_{promedio}$  es la potencia promedia disipada por un circuito durante un período [14].

## 2.8.2. Distancia de error (ED, por sus siglas en inglés)

Se define básicamente por la distancia aritmética entre dos números es decir el valor absoluto de la diferencia en este caso del resultado aproximado y el resultado preciso de la suma [13].

$$ED = |a - b| = \left| \sum_{i} a[i] * 2^{i} - \sum_{j} b[j] * 2^{j} \right|$$

(2.25)

Donde a denota el resultado del sumador preciso y b el del sumador aproximado.

## 2.8.3. Distancia media de error (MED, por sus siglas en inglés)

Se define distancia media de error como el promedio de ED para un conjunto dado de vectores de entrada siempre y cuando se trabaje con entradas de distribución uniforme [31].

$$MED = E[ED] = \sum_{i} ED_{i} * P(ED_{i})$$

(2.26)

donde  $P(ED_i)$  es la probabilidad de  $ED_i$ .

# 2.8.4. Tasa de error (ER, por sus siglas en inglés)

Porcentaje de todas las salidas erróneas ante todas las salidas [31].

$$ER = \sum_{i} P(ED_i), si \ ED_i \neq 0$$

(2.27)

## 2.9. Bibliotecas de circuitos aritméticos aproximados

# 2.9.1. EvoApprox8b: Biblioteca de sumadores y multiplicadores aproximados para diseño de circuito y evaluación comparativa de métodos de aproximación

En [32] una biblioteca con componentes aritméticos aproximados es propuesta, se compone por 430 sumadores y 471 multiplicadores aproximados de 8 bits, incluye modelos en verilog, Matlab y C para cada componente.

Párametros como área, potencia y retardo son estimados con bibliotecas de TSMC de

180 y 45 nm. Algunas métricas relativas al comportamiento del error también son generadas para cada componente, con todos estos parámetros una búsqueda bajo ciertas restricciones de diseño se puede realizar permitiendo obtener rápidamente el modelo del componente que mejor se ajuste. Esta biblioteca se encuentra disponible en la web señalada en [32].

# 2.9.2. Ipaclib: Biblioteca de multiplicadores y sumadores aproximados

Una metodología para generar y explorar el espacio estructural de un multiplicador aproximado usando variantes de módulos elementales como multiplicadores o sumadores tanto aproximados como precisos es presentada en [33]. Se generan varios diseños los cuales también se sintetizan y se verifican utilizando herramientas como Synopsys Design Compiler y Modelsim respectivamente.

Varios sumadores y multiplicadores componen esta biblioteca que se puede encontrar en la web señalada en [33], en esta se pueden encontrar tanto la descripción en VHDL así como un modelo de comportamieto en C.

# Capítulo 3

# Diseño

En este capítulo se presenta la metodología para el diseño de la estructura de la herramienta y de los archivos que la componen. Estos archivos incluyen código fuente, archivo de configuración y bibliotecas de plantillas. También se muestra las consideraciones para la descripción de las unidades aritméticas, para la elaboración de archivos de prueba y para la creación de scripts, así como sus debidas restricciones.

### 3.1. Estructura de la herramienta

#### 3.1.1. Generalidades

Es importante conocer el ambiente donde se desarrolla la herramienta. El sistema operativo utilizado es la distribución Ubuntu 14.04 de LINUX, se utiliza el lenguaje de programación C++ para el desarrollo del código fuente, este código es editado mediante el entorno de desarrollo integrado (IDE, por sus siglas en inglés) Eclipse el cual es de fuente abierta.

#### 3.1.2. Archivos base

Se crean dos archivos necesarios para el correcto funcionamiento, el primero es un archivo "makefile" con el cual se puede compilar o recompilar (dado el caso de modificación o inserción de código) el código fuente y generar un ejecutable. El segundo documento es un archivo de configuración el cual posteriormente será leído por la herramienta para conocer las rutas de las herramientas externas así como de las bibliotecas de celdas necesarias para distintos procesos. Este archivo de configuración es el que el usuario modificaría para establecer lo anteriormente mencionado.

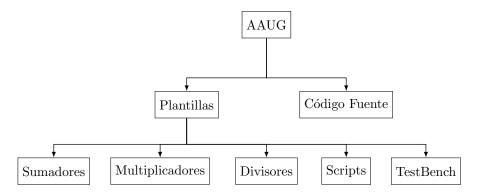

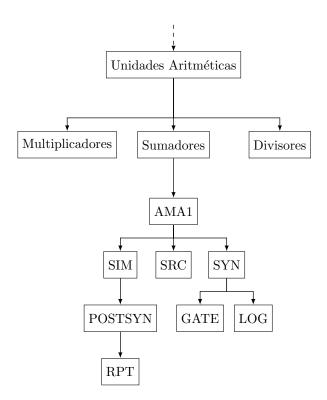

## 3.1.3. Organización de directorios

La carpeta principal de la herramienta contiene dos subcarpetas. La primera es donde se almacena el código fuente y modelos en C++ de los circuitos aritméticos desarrollados. La segunda contiene plantillas de los archivos que son modificables por la herramienta estos incluyen modelos en verilog, scripts y archivos de pruebas (testbenchs).

Figura 3.1: Estructura de carpeta general de la herramienta

Una carpeta extra es generada cuando se ejecuta la herramienta, esta incluye las unidades aritméticas solicitadas, reportes de área, potencia y retardo, así como sus respectivos archivos para simulación, síntesis y simulación post-síntesis. La ruta de esta carpeta por defecto es en la carpeta principal pero esto también es modificable en el archivo de configuración. Esta carpeta presenta una estructura jerárquica que facilita el intercambio y búsqueda de archivos para los procesos que se deseen realizar.

Figura 3.2: Estructura de carpeta de unidades generadas

## 3.1.4. Tipo de archivos