# **INSTITUTO SUPERIOR DE ENGENHARIA DO PORTO**

# Sistema de armazenamento e geração de energia para locais de consumo remotos

DIEGO HENRIQUE SCHECHTEL

novembro de 2016

# SISTEMA DE ARMAZENAMENTO E GERAÇÃO DE ENERGIA PARA LOCAIS DE CONSUMO REMOTOS

DIEGO HENRIQUE SCHECHTEL

Departamento de Engenharia Electrotécnica

Mestrado em Engenharia Electrotécnica e de Computadores

Área de Especialização em Automação e Sistemas

Relatório elaborado para satisfação parcial dos requisitos da Unidade Curricular de Tese/Dissertação do Mestrado em Engenharia Electrotécnica e de Computadores

Candidato: Diego Henrique Schechtel, № 1151478, 1151478@isep.ipp.pt

Orientação científica: Doutor Rui Miguel Monteiro de Brito, rmb@isep.ipp.pt

Coorientação científica: Doutora Fernanda Cristina Corrêa, fernandacorrea@utfpr.edu.br

Departamento de Engenharia Electrotécnica

Mestrado em Engenharia Electrotécnica e de Computadores

Área de Especialização em Automação e Sistemas

| Dedico este tra | abalho a minha famí | lia, em especial a | aos meus pais, que | não mediram |

|-----------------|---------------------|--------------------|--------------------|-------------|

|                 |                     |                    | udesse alcançar os |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

|                 |                     |                    |                    |             |

# Agradecimentos

Agradeço, primeiramente, a Deus por me dar força para persistir nas horas difíceis.

Agradeço aos meus pais, pelo amor, incentivo e dedicação que tiveram comigo ao longo de toda a minha vida. Vocês sempre serão meus exemplos de vida, amo vocês do fundo do meu coração.

Ao meu orientador, professor Doutor Rui Miguel Monteiro de Brito, pela paciência e orientações dadas ao longo do desenvolvimento desta dissertação.

A minha coorientadora, professora Doutora Fernanda Cristina Corrêa, pela ajuda e disponibilidade oferecida mesmo estando tão longe.

Agradeço também aos meus amigos Denis e Guilherme, que compartilharam comigo a experiência de estudar e morar em outro país, pela amizade e companheirismo neste ano que se mostrou um grande desafio a todos nós. Sem essa amizade o caminho trilhado seria mais difícil.

E agradeço as instituições UTFPR e ISEP, por terem me oferecido essa grande oportunidade.

# Resumo

Este trabalho propõe o uso do conversor *Back to Back* para manter a tensão constante na carga em situações em que a rede sofre com oscilações ou quedas de tensão. Para isso o conversor terá em seu barramento CC um sistema de armazenamento baseado em baterias que será capaz de alimentar a carga por um período de tempo até que a situação da rede se normalize. A escolha do conversor *Back to Back* partiu do princípio de que este é capaz de fornecer à carga a energia armazenada na bateria independentemente da situação em que a rede elétrica se encontra. O trabalho apresenta um estudo geral das componentes necessários para a implementação do conversor. É feito um estudo do fluxo de potência entre a rede e o conversor para que a fator de potência visto pela rede seja unitário. É apresentado um método de sincronismo com a rede para que o conversor possa trabalhar com o fluxo bidirecional de potência.

As análises são feitas através de simulação em duas situações diferentes, primeiro o conversor é analisado sobre as condições normais de funcionamento da rede. Para isto são utilizados tipos de cargas diferentes. A segunda analise é feita sobre as falhas da rede, onde é analisado o comportamento da tensão e da corrente sobre a carga.

Para colocar em prática os conceitos estudados neste trabalho, é implementado um inversor que utiliza o ângulo estimado da rede para gerar sua frequência de trabalho.

### Plavras-Chave

Retificador PWM, Inversor PWM, Conversores de potência, *Back to Back*, Qualidade de energia.

# Abstract

This work proposes the use of the converter Back to Back to maintain constant the voltage in the load on situations when the grid suffers from fluctuations or voltage drops. For this, the converter will have on your DC bus a storage system based on batterys that will able to supply the load for a period of time until the grid situation return to normal. The Back to Back converter choice came from this converter is able to provide to the load the energy stored in the battery regardless of the situation grid is. The work presents a general survey of components required to implement the converter. It made a study of the power flow between the grid and the converter to the power factor seen by the grid to be unitary. It is presented a synchronization method whit the grid to able the converter to work with the bidirectional power flow.

Analyses are done using simulation in two different situations, the first analyses are make with the converter working under a normal grid operation. To this we are used different types of load. The second analysis was made regarding the network failures, where the behavior of the voltage and current on the load is analysed.

To put into particle the concepts studied, an inverter is implemented that uses the estimated angle of the grid to generate its working frequency.

### Keywords

PWM rectifier, PWM inverter, Power converters, Back to Back, Power quality.

# Índice

| A  | GRADECIMENTOS                                      | I    |

|----|----------------------------------------------------|------|

| R  | ESUMO                                              | III  |

| A  | BSTRACT                                            | V    |

| ÍN | NDICE DE FIGURAS                                   | IX   |

| ÍN | NDICE DE TABELAS                                   | XV   |

| A  | CRÓNIMOS                                           | XVII |

| 1. | INTRODUÇÃO                                         | 1    |

|    | 1.1.Contextualização                               | 2    |

|    | 1.2.Objetivo                                       | 3    |

|    | 1.3.Calendarização                                 | 4    |

|    | 1.4.Organização do trabalho                        | 4    |

| 2. | ESTADO DA ARTE                                     | 7    |

|    | 2.1.Filtros Passivos                               | 7    |

|    | 2.2.Filtros Ativos                                 | 8    |

|    | 2.3.Fontes Ininterruptas de Potência               | 13   |

|    | 2.4.Conversores CA-CC-CA                           | 16   |

|    | 2.5.ESCOLHA DO SISTEMA UTILIZADO                   | 19   |

| 3. | TRANSFORMADAS DE CLARKE E PARK                     | 21   |

|    | 3.1.Transformada de Clarke                         | 23   |

|    | 3.2.Transformada de Park                           | 26   |

| 4. | FUNCIONAMENTO DOS CONVERSORES CA-CC-CA             | 33   |

|    | 4.1.Conversores CA-CC                              | 34   |

|    | 4.2.Controle do fluxo de potência                  | 46   |

| 5. | SINCRONISMO COM A REDE                             | 53   |

|    | 5.1. PLL                                           | 54   |

|    | 5.2.SRF PLL NO PSIM                                | 58   |

| 6. | TÉCNICAS DE MODULAÇÃO                              | 63   |

|    | 6.1.Modulação Senoidal por Largura de Pulso (SPWM) | 64   |

|    | 6.2.MODULAÇÃO POR VETOR DE ESPAÇO                  |      |

| 6.3.MODULAÇÃO POR INJEÇÃO DE HARMÔNICO ÍMPAR DE TERCEIRA ORDEM | 75  |

|----------------------------------------------------------------|-----|

| 6.4.Escolha do método de modulação                             | 77  |

| 7. ANÁLISE DE RESULTADOS                                       | 79  |

| 7.1.Simulações                                                 | 79  |

| 7.2. PLL                                                       | 88  |

| 7.3.Inversor                                                   | 93  |

| 7.4.Conversor Back to Back                                     | 101 |

| 7.5.Falhas da rede                                             | 107 |

| 7.6.Modelo discreto                                            | 114 |

| 7.7.SRF PLL IMPLEMENTAÇÃO PRÁTICA                              | 119 |

| 7.8.Implementação do inversor                                  | 125 |

| 8. CONCLUSÃO E TRABALHOS FUTUROS                               | 145 |

| 8.1.Trabalhos futuros                                          | 147 |

| REFERÊNCIAS DOCUMENTAIS                                        | 149 |

| ANEXO A. CÓDIGO C PSIM                                         | 155 |

# Índice de Figuras

| Figura 1 Filtros passivos, (a) primeira ordem, (b) segunda ordem,                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| (c) terceira ordem [5].                                                                                                                           | 8  |

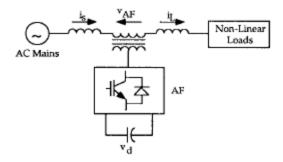

| Figura 2 Esquema simplificado de um filtro ativo série [7].                                                                                       | 10 |

| Figura 3 Funcionamento de um filtro ativo série. Imagem modificada de [4].                                                                        | 10 |

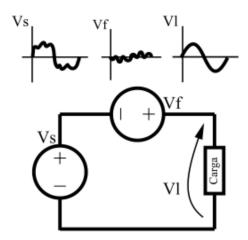

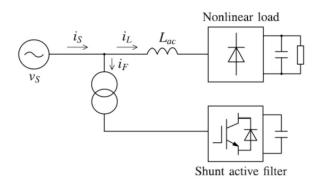

| Figura 4 Esquema simplificado de um filtro ativo paralelo (shunt) [5].                                                                            | 11 |

| Figura 5 Funcionamento de um filtro ativo paralelo. Imagem modificada de [4].                                                                     | 11 |

| Figura 6 Condicionador Universal de Qualidade de Energia [7].                                                                                     | 12 |

| Figura 7 Filtro híbrido [7].                                                                                                                      | 12 |

| Figura 8 Diagrama de blocos de uma UPS on-line [4].                                                                                               | 14 |

| Figura 9 Diagrama de blocos de uma UPS off-line [9].                                                                                              | 15 |

| Figura 10 Diagrama de blocos de uma UPS interativa [9].                                                                                           | 16 |

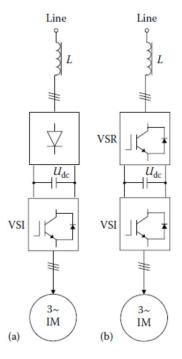

| Figura 11 Diagrama de blocos de conversores CA-CC-CA, (a) retificação a diodo, (b) retificação por chaves eletrônicas. Imagem modificada de [12]. | 16 |

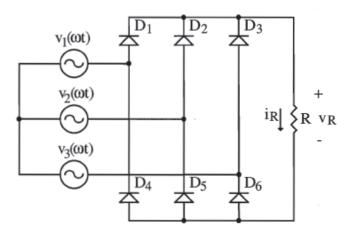

| Figura 12 Conversor trifásico a diodo em ponte completa, ponte de Greatz [13].                                                                    | 17 |

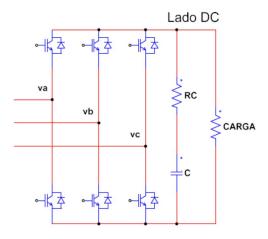

| Figura 13 Voltage Source Retifeir trifásico.                                                                                                      | 18 |

| Figura 14 VSR utilizados como método de redução de harmônicos na rede [12].                                                                       | 18 |

| Figura 15 Inversor VSI Voltage Source Inverter [16].                                                                                              | 19 |

| Figura 16 Sistema trifásico abc. Imagem modificada de [15].                                                                                       | 22 |

| Figura 17 Tensões no sistema trifásico.                                                                                                           | 22 |

| Figura 18 Representação dos sistemas abc trifásico e αβ bifásico [15].                            | 23 |

|---------------------------------------------------------------------------------------------------|----|

| Figura 19 (a) Transformada de Clarke. (b) Transformada inversa de Clarke.                         | 25 |

| Figura 20 Circuito de transformações.                                                             | 25 |

| Figura 21 Sinais das transformações.                                                              | 26 |

| Figura 22 Sistemas abc em preto, $\alpha\beta$ em vermelho e dq em azul [15].                     | 27 |

| Figura 23 Transformação do sistema abc para dq. Imagem modificada de [15].                        | 27 |

| Figura 24 Transformada de Park a partir do sistema $\alpha\beta$ . Imagem modificada de [15].     | 28 |

| Figura 25 (a) abc para dq. (b) dq para abc. (c) $\alpha\beta$ para dq (d) dq para $\alpha\beta$ . | 29 |

| Figura 26 Circuito para a transformada de Park.                                                   | 30 |

| Figura 27 Bloco que estima o ângulo <b>\theta e</b> no programa PSIM.                             | 30 |

| Figura 28 Sinais de tensão em cada sistema.                                                       | 31 |

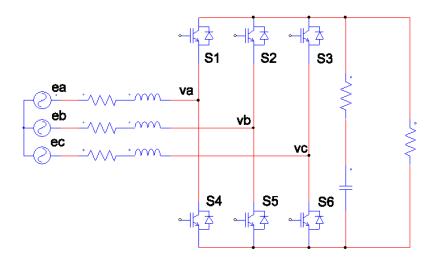

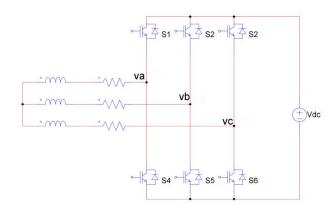

| Figura 29 Configuração do retificador ativo com seis IGBTs.                                       | 35 |

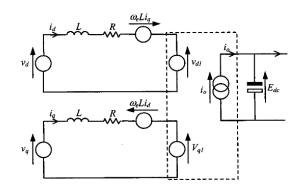

| Figura 30 Modelagem do AC do conversor.                                                           | 36 |

| Figura 31 Sistema para análise de transferência de potência entre fontes.                         | 36 |

| Figura 32 (a) Potência ativa sendo entregue pela rede, (b) potência ativa sendo                   |    |

| entregue pelo conversor. Imagem modificada de [15].                                               | 39 |

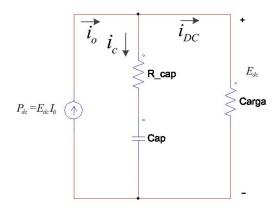

| Figura 33 Acoplamento CA/DC do conversor [27].                                                    | 45 |

| Figura 34 Lado CC do conversor.                                                                   | 45 |

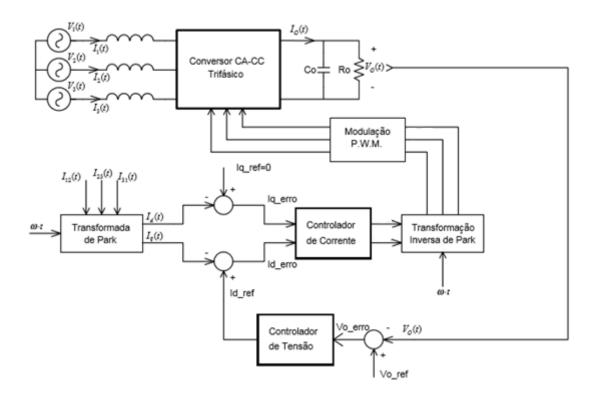

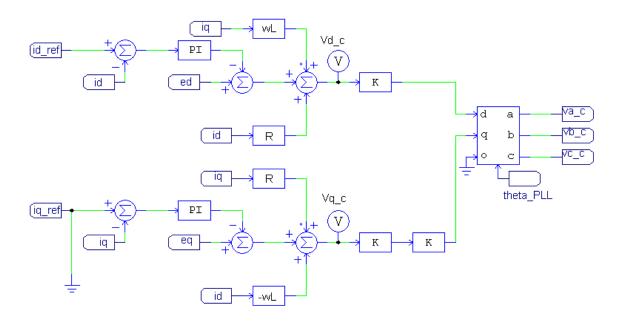

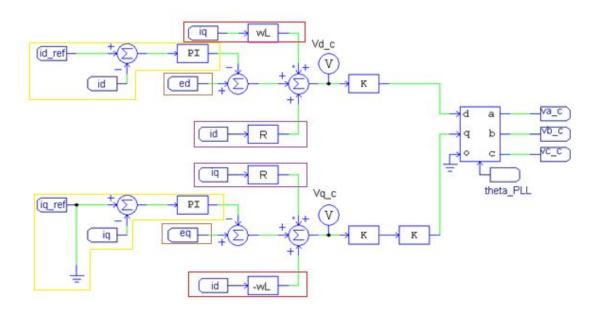

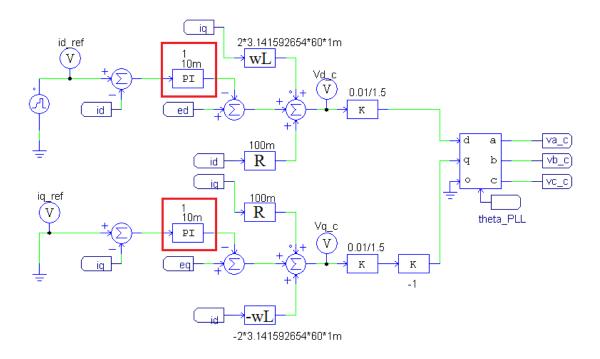

| Figura 35 Diagrama de controle do conversor VSC. Imagem modificada de [24].                       | 47 |

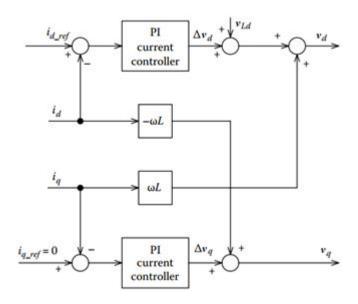

| Figura 36 Desacoplamento das tensões <b>vd</b> e <b>vq</b> . Imagem alterada de [12].             | 49 |

| Figura 37 Modelo elétrico para o controle do conversor. Imagem modificada de [15].                | 49 |

| Figura 38 Imagem explicativa do circuito elétrico.                                      | 50   |

|-----------------------------------------------------------------------------------------|------|

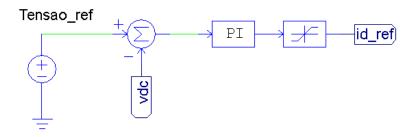

| Figura 39 Controlador da tensão do barramento CC.                                       | 51   |

| Figura 40 Comparação entre os métodos de PLL existentes [15].                           | 54   |

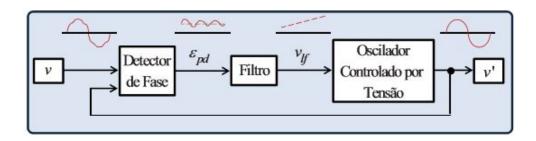

| Figura 41 Estrutura básica de uma PLL [29].                                             | 55   |

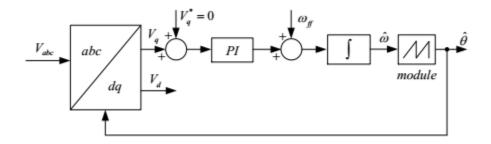

| Figura 42 Estrutura básica da SRF PLL [15].                                             | 56   |

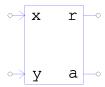

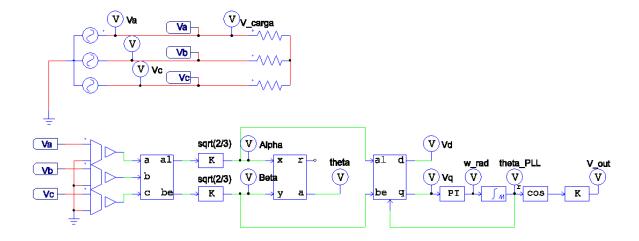

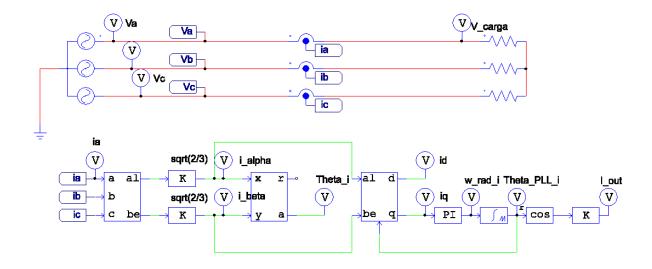

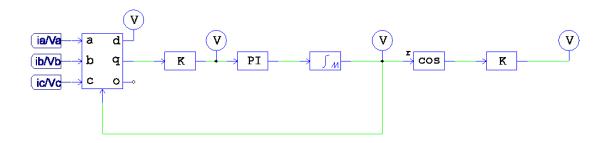

| Figura 43 Modelo SRF PLL PSIM.                                                          | 58   |

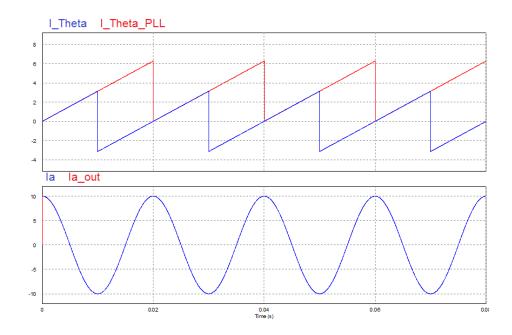

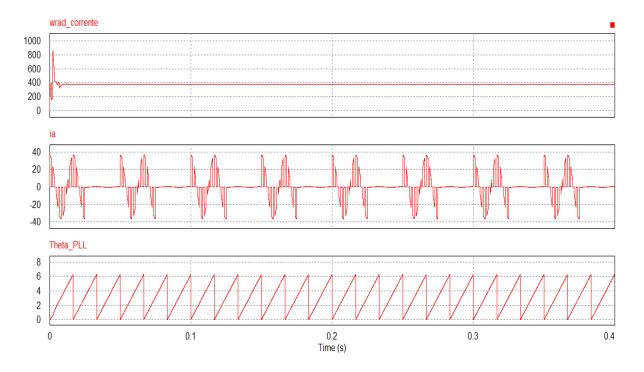

| Figura 44 Resultados da SRF PLL.                                                        | 59   |

| Figura 45 SRF PLL por corrente.                                                         | 60   |

| Figura 46 Resultados apresentados pela SRF PLL.                                         | 60   |

| Figura 47 Circuito simplificado SRF PLL.                                                | 61   |

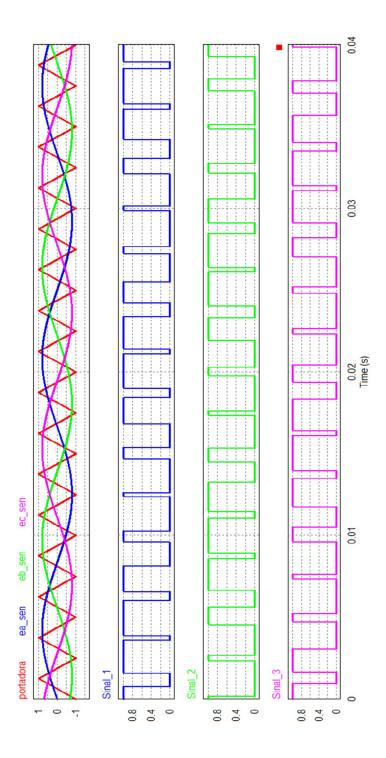

| Figura 48 Circuito de comparação para geração de sinal de disparo dos IGBTs.            | 65   |

| Figura 49 Sinais de disparo dos IGBTs usando a modulação SPWM.                          | 66   |

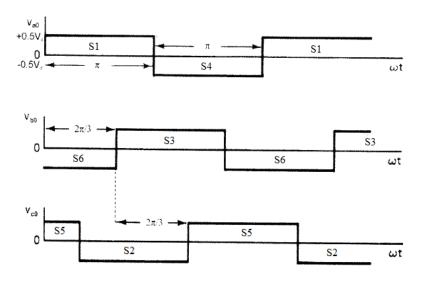

| Figura 50 Condução em funcionamento six-step. Imagem modificada de [37].                | 68   |

| Figura 51 Inversor trifásico.                                                           | 69   |

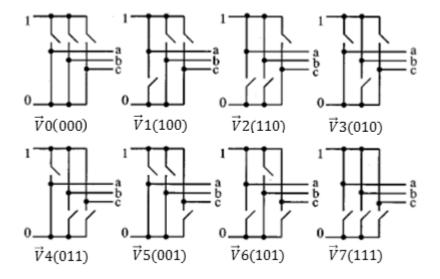

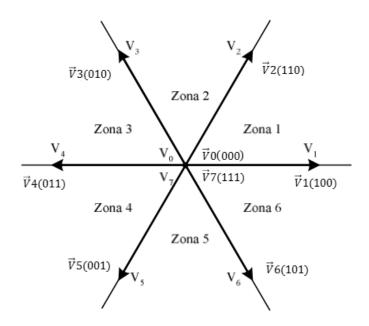

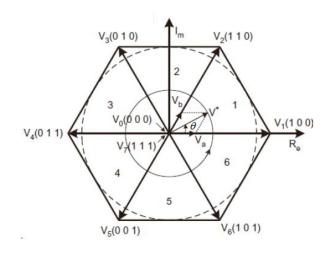

| Figura 52 Oito possíveis estados das chaves. Imagem modificada de [42].                 | 70   |

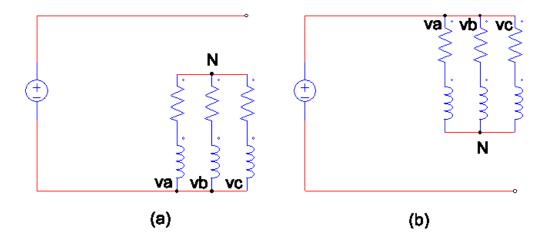

| Figura 53 Vetores nulos, (a) <b>V0</b> , (b) <b>V7</b> .                                | 70   |

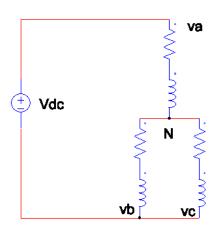

| Figura 54 Vetor <b>V1</b> =100.                                                         | 71   |

| Figura 55 Divisão do plano complexos pelos vetores <b>Vn</b> . Imagem modificada de [39 | ].73 |

| Figura 56 Vetor <b>V</b> * na zona 1 [15].                                              | 73   |

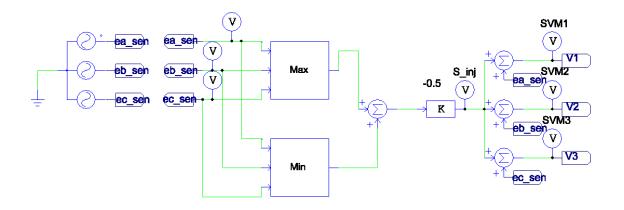

| Figura 57 Estrutura do SVM para o PSIM.                                                 | 75   |

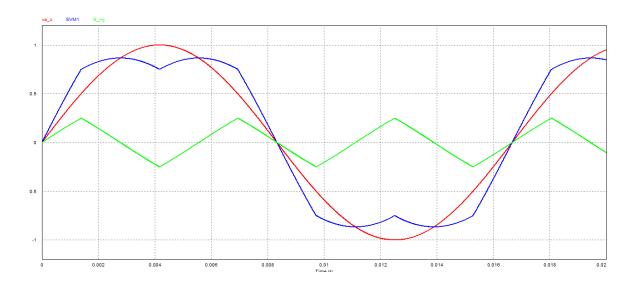

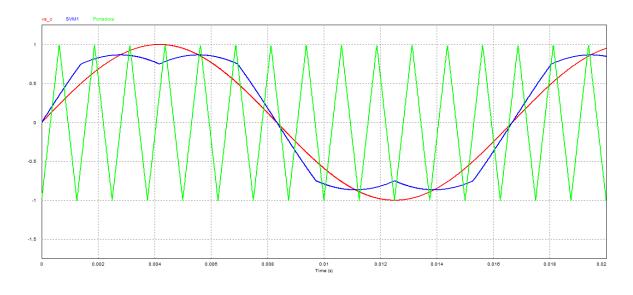

| Figura 58 Sinais de formação da SVM.                                                    | 76   |

| Figura 59 Comparação da modulação SVM e PWM em relação à portadora.                                        | 76 |

|------------------------------------------------------------------------------------------------------------|----|

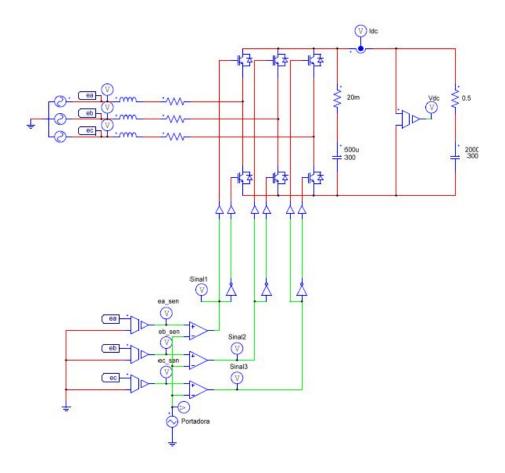

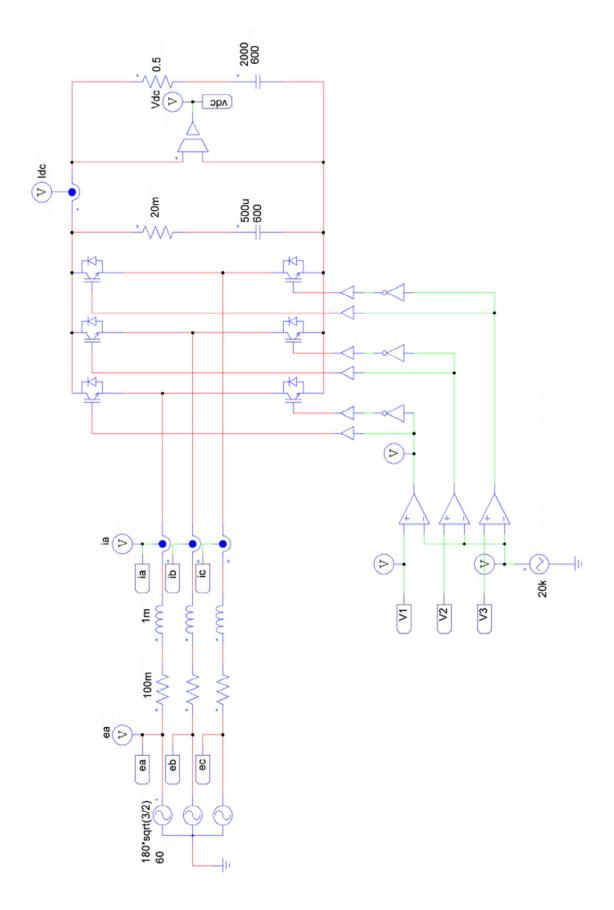

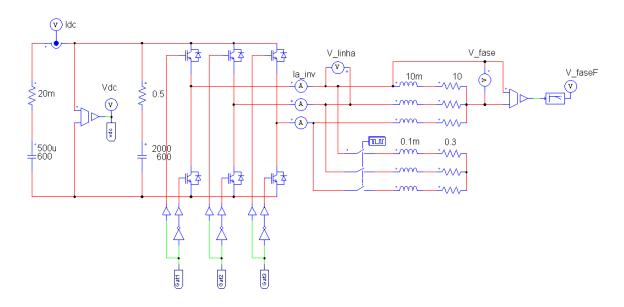

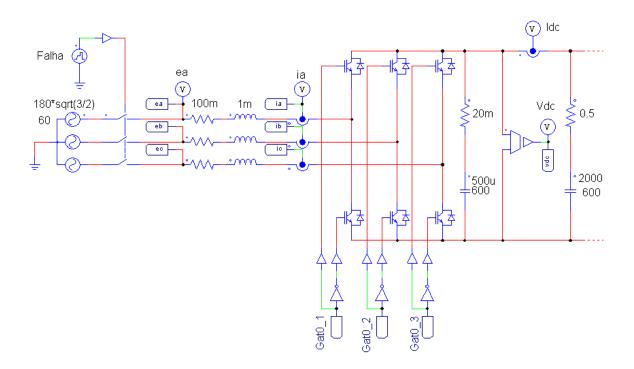

| Figura 60 Esquema elétrico para simulação.                                                                 | 80 |

| Figura 61 Modelo elétrico com fonte de referência para a corrente.                                         | 82 |

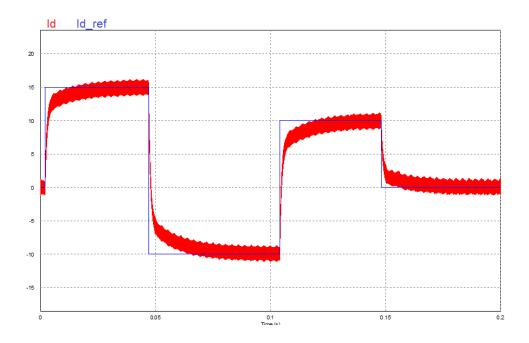

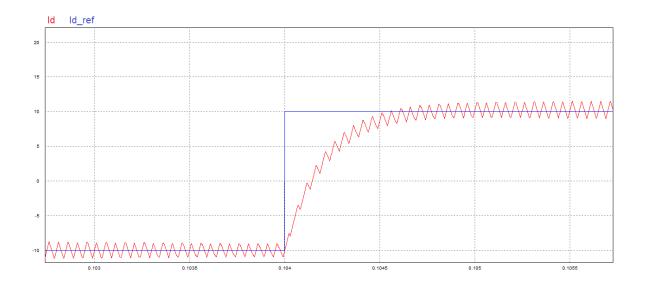

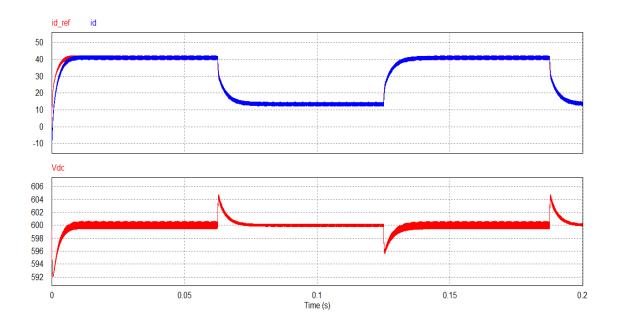

| Figura 62 Teste do controle de corrente.                                                                   | 83 |

| Figura 63 Resultado dentro dos parâmetros de projeto.                                                      | 84 |

| Figura 64 Potência ativa controlada pela corrente id.                                                      | 85 |

| Figura 65 Modificação no barramento CC para o teste do controlador de tensão                               | 86 |

| Figura 66 Teste do controlador de tensão, sem bateria.                                                     | 87 |

| Figura 67 Teste do controlador de tensão, com bateria.                                                     | 88 |

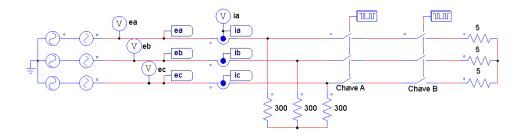

| Figura 68 Circuito para teste da SRF PLL.                                                                  | 89 |

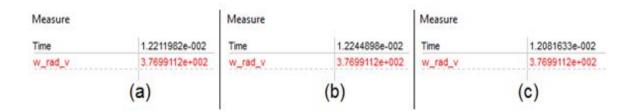

| Figura 69 Tempo de sincronismo (a) 180 Hz, (b) 300 Hz, (c) 420 Hz.                                         | 89 |

| Figura 70 Sinal sincronizado com harmônico de 20 kHz. Autoria própria.                                     | 90 |

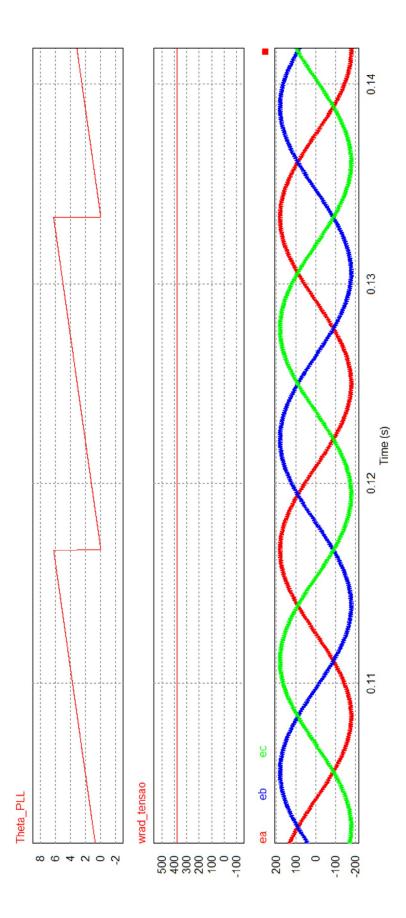

| Figura 71 Teste de robustez da SRF PLL.                                                                    | 91 |

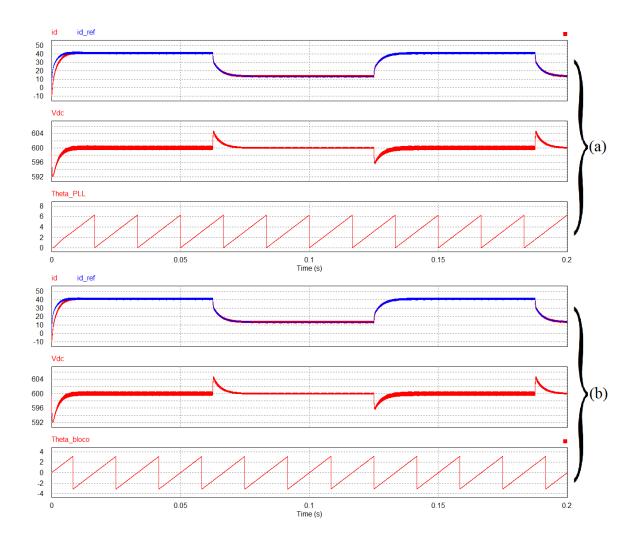

| Figura 72 Comparação do conversor. (a) $\theta$ gerado pela SRF PLL, (b) $\theta$ gerado pelo bloco xy/ra. | 92 |

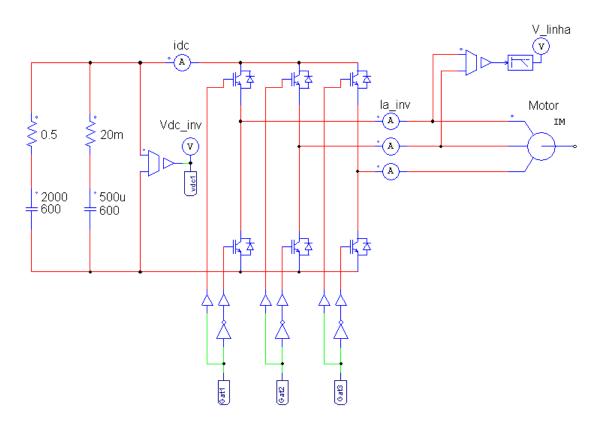

| Figura 73 Configuração do inversor que alimenta um motor a indução.                                        | 93 |

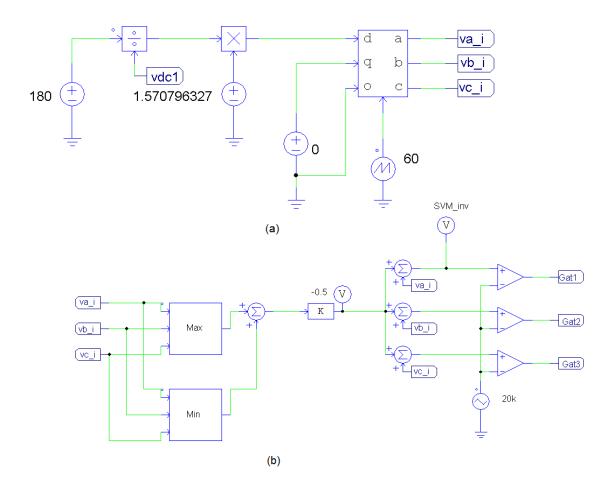

| Figura 74 (a) Controle de tensão de saída da inversora, (b) sistema de geração do SVM.                     | 95 |

| Figura 75 Inversor alimentando uma carga variável.                                                         | 96 |

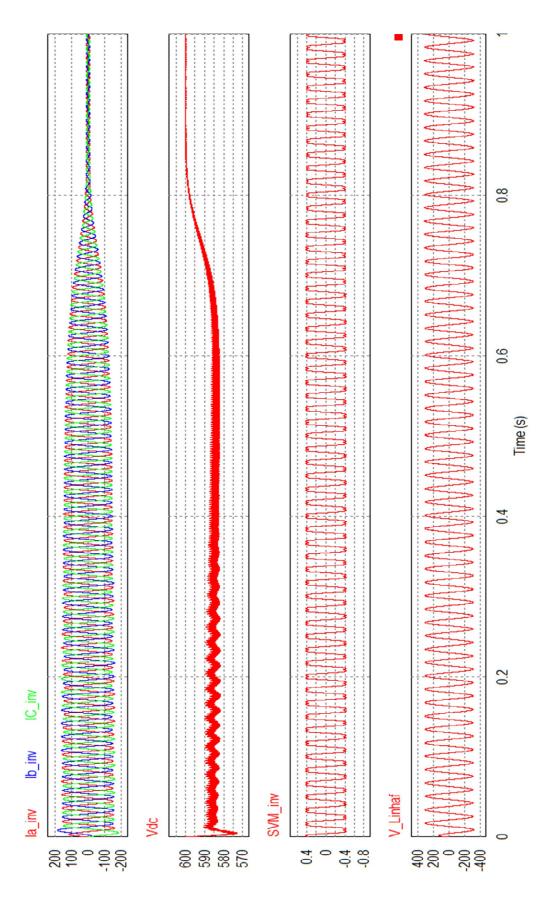

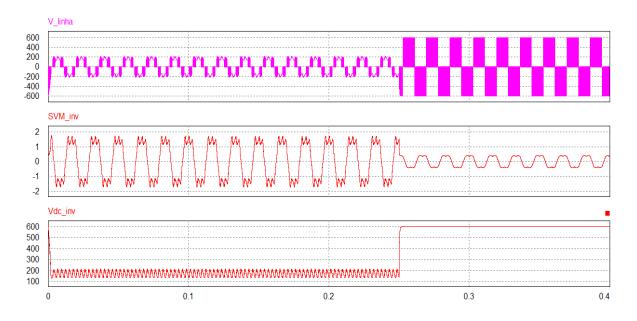

| Figura 76 Resultados apresentados para experiência um.                                                     | 97 |

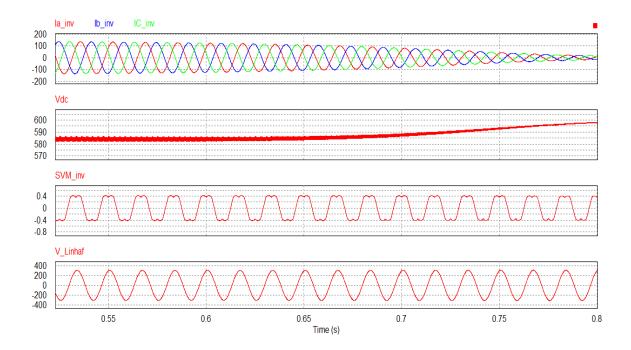

| Figura 77 Detalhe dos sinais da experiência um.                                                            | 98 |

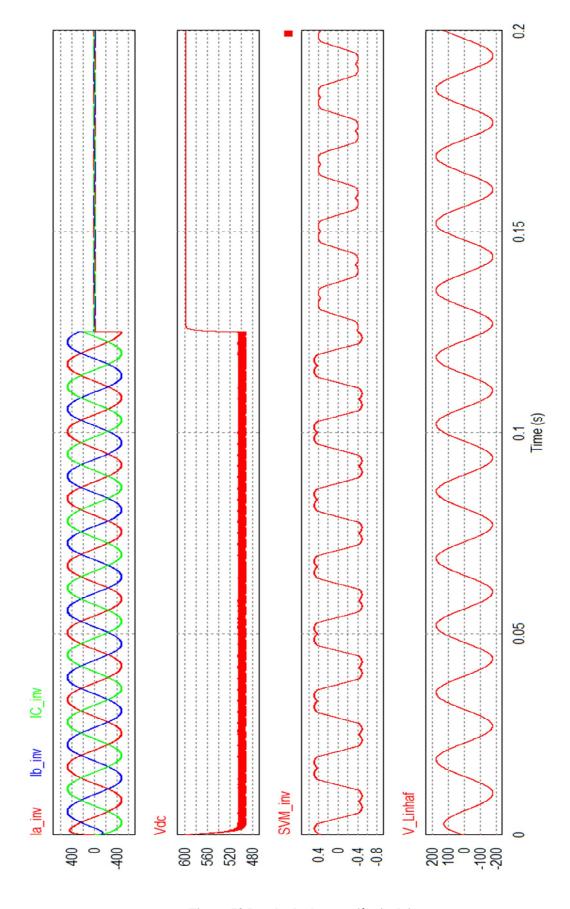

| Figura 78 Resultado da experiência dois.                                                                   | 99 |

| Figura 79 Funcionamento em sobre modulação até 0.25 segundos.                           | 100 |

|-----------------------------------------------------------------------------------------|-----|

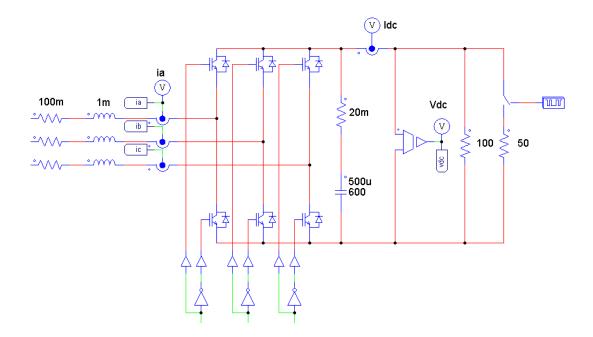

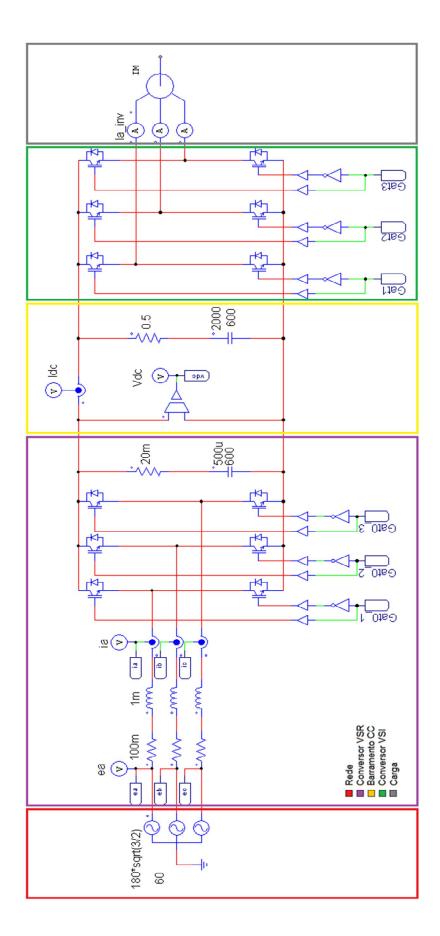

| Figura 80 Conversor Back to Back, planta de simulação.                                  | 102 |

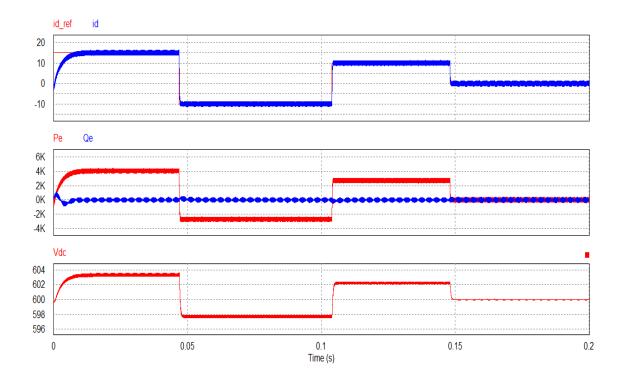

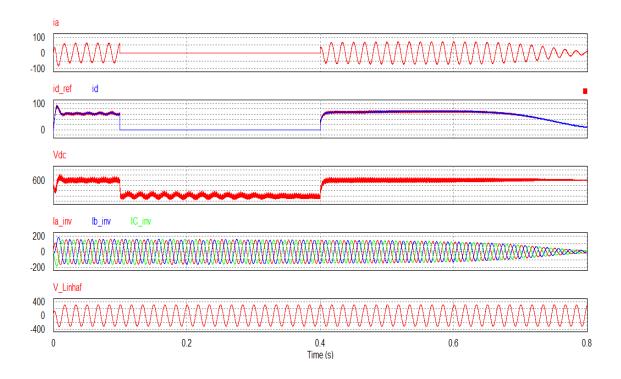

| Figura 81 Comportamento do conversor Back to Back com motor a indução como carga.       | 103 |

| Figura 82 Carga apresentada para a segunda experiência usando o conversor Back to Back. | 104 |

| Figura 83 Comportamento do conversor Back to Back com variação abrupta da carga.        | 105 |

| Figura 84 Tensão e corrente da rede em fase.                                            | 107 |

| Figura 85 Falha de sobre tensão.                                                        | 108 |

| Figura 86 Falha de afundamento de tensão.                                               | 109 |

| Figura 87 Circuito usado para simular a queda de tensão da rede.                        | 110 |

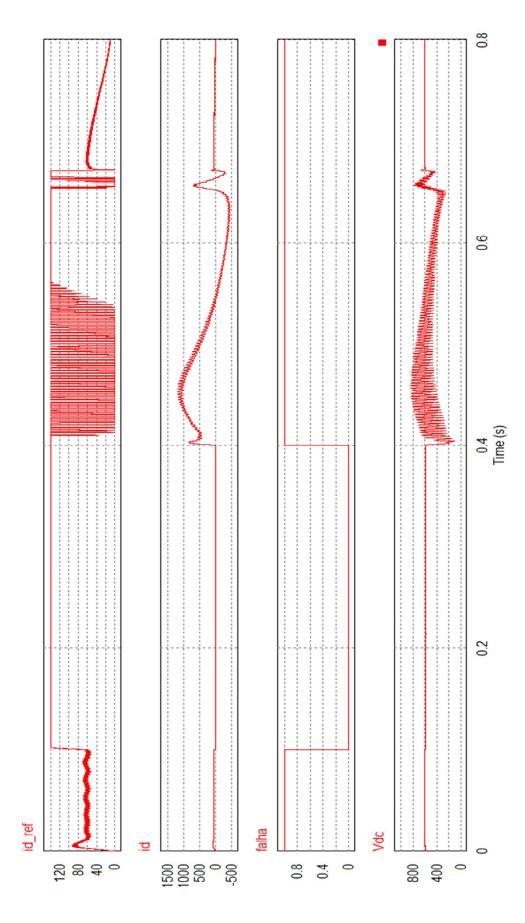

| Figura 88 Saturação da referência de corrente na queda de tensão da rede.               | 112 |

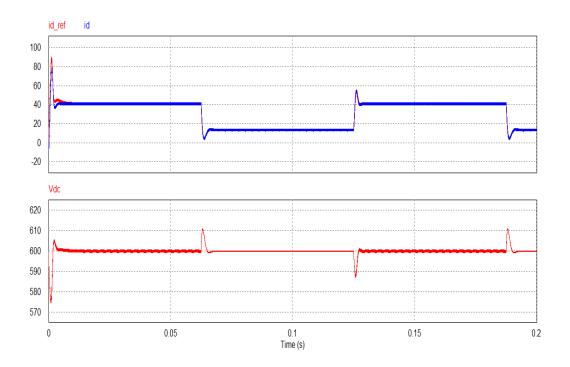

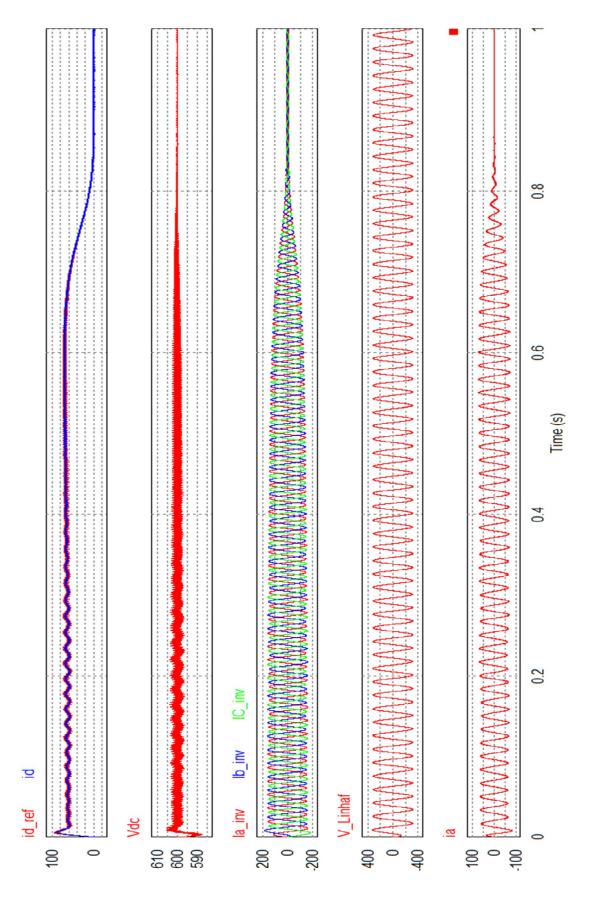

| Figura 89 Resultados apresentados após modificações propóstas.                          | 114 |

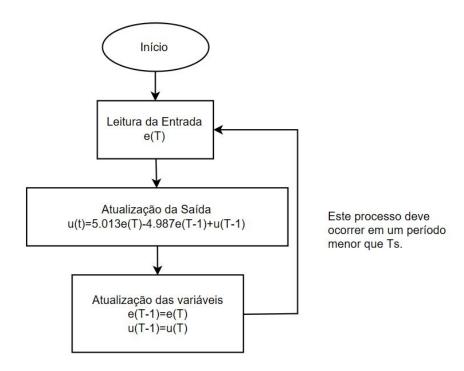

| Figura 90 Fluxograma do controlador PI da SRF PLL por tensão.                           | 117 |

| Figura 91 Resposta do conversor usando controladores digitais.                          | 119 |

| Figura 92 XMC 4500 Relax Lite Kit.                                                      | 120 |

| Figura 93 Circuito de condicionamento de sinal.                                         | 121 |

| Figura 94 Teste de sincronização SRF PLL.                                               | 124 |

| Figura 95 Sinal de sincronização da SRF PLL com a Fase A do transformador trifásico.    | 125 |

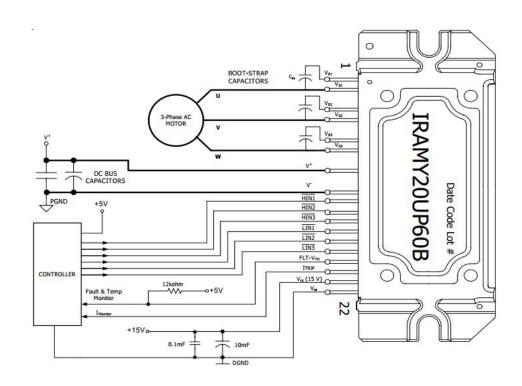

| Figura 96 Esquema de ligação do CI IRAMY20P60B [46].                                    | 127 |

| Figura 97 Circuito de alimentação do CI.                                | 127 |

|-------------------------------------------------------------------------|-----|

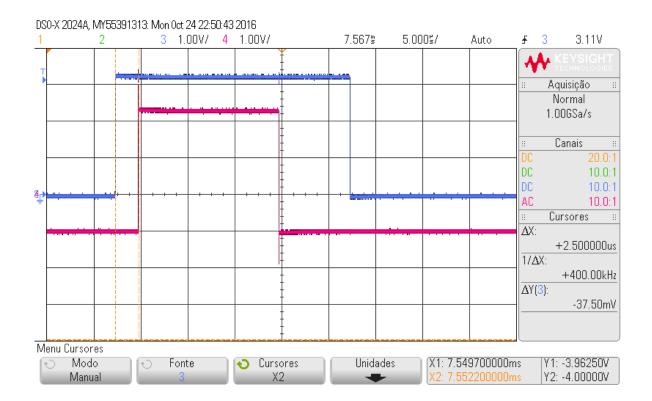

| Figura 98 Tempo de execução do código.                                  | 130 |

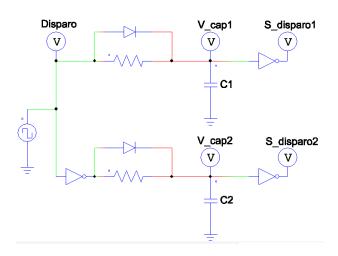

| Figura 99 Circuito para produção de tempo morto.                        | 131 |

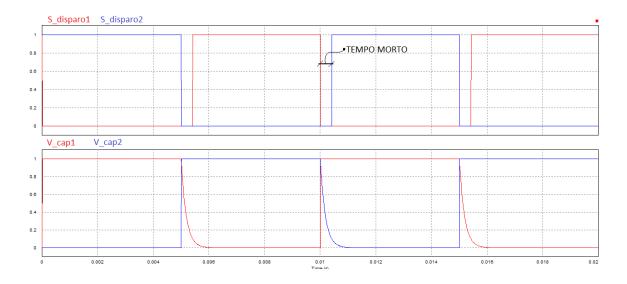

| Figura 100 Sinal de disparo com o tempo morto.                          | 131 |

| Figura 101 Tempo morto.                                                 | 133 |

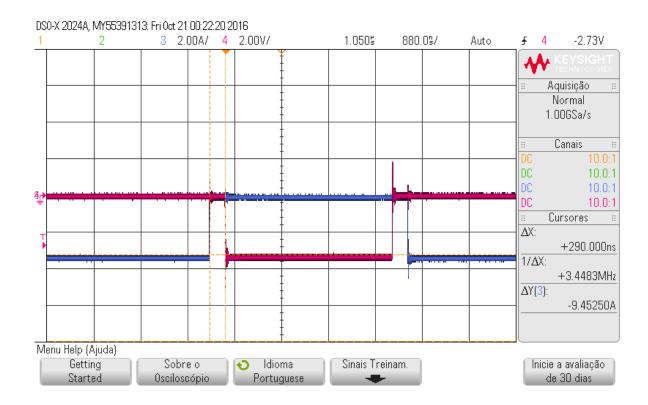

| Figura 102 Sinal de disparo em sincronia com a rede.                    | 134 |

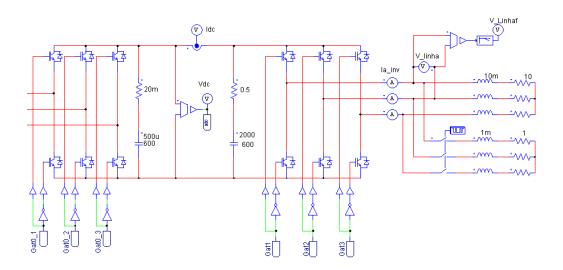

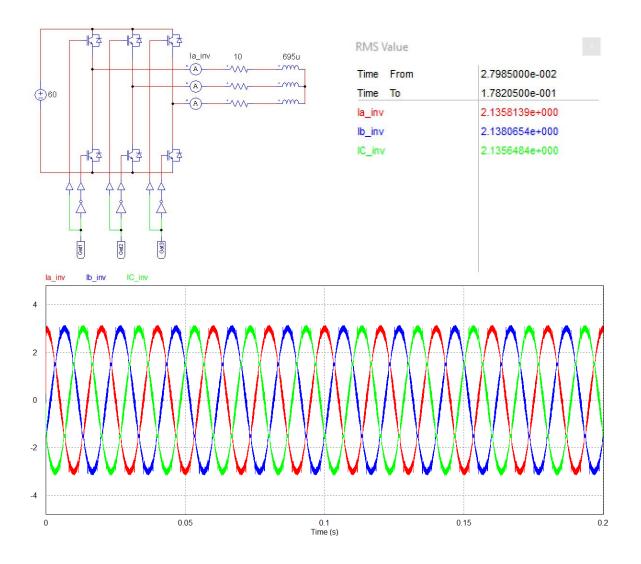

| Figura 103 Inversor simulado.                                           | 135 |

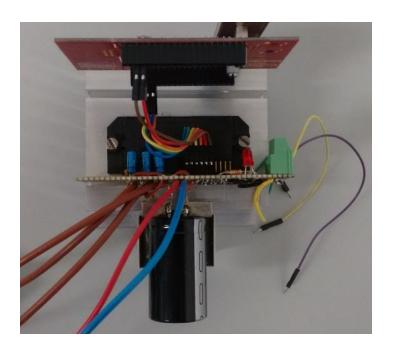

| Figura 104 Esquema de ligação para o funcionamento do inversor.         | 136 |

| Figura 105 Sistema de controle e aquisição de sinal.                    | 136 |

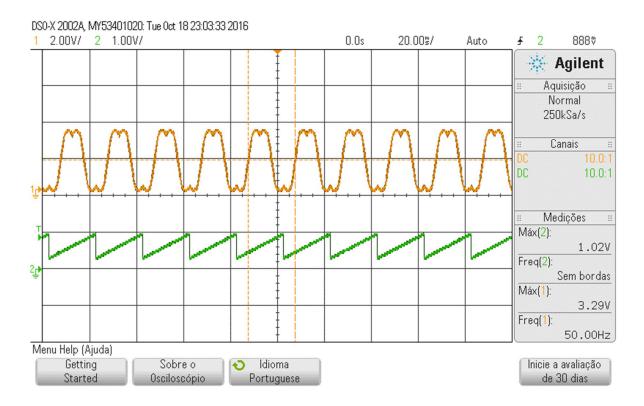

| Figura 106 Correntes do inversor e sinal de ângulo da SRF PLL.          | 137 |

| Figura 107 Tensão do barramento CC.                                     | 138 |

| Figura 108 Simulação, tensão de fase e de linha do conversor da fase A. | 139 |

| Figura 109 Tensão rms de linha do conversor.                            | 139 |

| Figura 110 Tensão rms de fase do conversor.                             | 140 |

| Figura 111 FFT dos sinais de tensão e corrente da simulação.            | 142 |

# Índice de Tabelas

| Tabela 1 Calendarização.                                        | 5   |

|-----------------------------------------------------------------|-----|

| Tabela 2 Tensão da carga por vetor de espaço.                   | 71  |

| Tabela 3 Corrente de referência.                                | 82  |

| Tabela 4 Parâmetros de configuração da APP ADC_MEASUREMENT_ADV. | 123 |

| Tabela 5 Parâmetros de configuração da APP PWM.                 | 124 |

| Tabela 6 Parâmetros de configuração da modulação SVM.           | 128 |

| Tabela 7 Parâmetros de configuração da interrupção da SVM.      | 128 |

| Tabela 8 Comparação de resultdos.                               | 141 |

# Acrónimos

AD – Analógico Digital

Aneel – Agência Nacional de Energia Elétrica

APPs – Aplications

CA – Corrente Alternada

CC – Corrente Contínua

CI – Circuito Integrado

CSI – Current Source Inverters

DAC – Digital-to-Analog Converter

DSP – Digital Signal Processor

Fas – Filtros Ativos

IGBT – Insulated Gate Bipolar Transistor

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

PI – Proporcional Integral

PLL – Phase-Locked Loop

PWM – Pulse-Width Modulation

SO – Symmetrical optimum

SPWM – Sinusoidal Pulse-Width Modulation

SRF PLL - Synchronous Reference Frame Phase-Locked Loop

SVM – Space Vector Modulation

THUPWM - Third Harmonic Uniform Pulse Width Modulation

UPQC – Unifield Power Quality Conditiner

UPS – Uninterruptible Power Supply

VSC – Voltage Source Converter

VSI – Voltage Source Inverter

VSR – Voltage Source Retifier

# 1. Introdução

Há vários estudos que apontam que o desenvolvimento de uma região está diretamente ligado ao acesso à energia elétrica, tanto o desenvolvimento econômico como a qualidade de vida é aprimorada com a disponibilidade da energia elétrica.

Por outro lado, é muito importante que essa energia seja entregue com qualidade ao consumidor. Para o desenvolvimento das atividades humanas na atualidade a qualidade de energia elétrica é indispensável.

O termo qualidade de energia é um termo que abrange muitas variáveis, porém de forma geral é usado para identificar as condições em que a energia é entregue para o consumidor pelas concessionárias de distribuição, ou ainda quão bem o consumidor pode aproveitar o uso desta energia. A qualidade de energia entregue ao consumidor tem alguns pontos fundamentais como a conformidade com parâmetros considerados desejáveis e a continuidade da distribuição [1].

Entre os problemas apresentados na distribuição pode-se citar:

Distorções;

- Flutuação de Tensão;

- Variação de tensão de curta duração;

- Desequilíbrio de sistemas trifásicos;

- Transitórios rápidos;

- Interrupção do fornecimento durante um período de tempo.

Os problemas causados pela falta de qualidade de energia vão desde o incomodo visual devido à cintilação da luz até perdas de produção por interrupções da distribuição [1].

Atualmente os equipamentos instalados nas redes de distribuição são sensíveis a distúrbios e muitas vezes são também os causadores destes distúrbios.

# 1.1. CONTEXTUALIZAÇÃO

A dimensão territorial brasileira é um dos problemas enfrentados na distribuição de energia elétrica. Como é baixo o consumo das zonas rurais em relação aos centros urbanos e industriais, os consumidores rurais ainda enfrentem problemas com a entrega de energia em suas regiões.

As zonas rurais que em geral são muito afastas dos grandes centros de distribuição de energia, acabam sofrendo com a baixa qualidade da energia elétrica que são gerados pelas longas distâncias. Entre os distúrbios estão a tensão em níveis não adequados, oscilações e presença de harmônicos [2].

Na região sul do Brasil o aumento da agroindústria trouxe uma nova categoria de consumidores para as zonas rurais, consumidores que necessitam de uma energia de qualidade. As cargas instaladas pela agroindústria nas redes rurais agora são sensíveis a distúrbios. Essas cargas instaladas nas agroindústrias em geral são bombas de agua, refrigeradores, compressores e esteiras. Essas cargas são basicamente motores em diferentes funções.

Assim como nas indústrias a baixa qualidade de energia entregue nas zonas rurais causa problemas nos equipamentos instalados na rede, tanto nas residências como nas atividades produtivas rurais.

Outro problema que aparece nas redes rurais com frequência são os desligamentos e oscilações causados por descargas elétricas nas proximidades ou diretamente na rede de transmissão.

Todas estas perturbações geram problemas para os consumidores, como mau funcionamento dos equipamentos, queima e perdas de produção. De acordo com a resolução 360/2009 da Agência Nacional de Energia Elétrica (Aneel), os danos causados em equipamentos devido a problemas nas redes elétricas devem ser ressarcidos ao consumidor [3], mas os danos relativos a perdas de produção entre outros não cabem à prestadora do serviço o ressarcimento.

Visto os problemas enfrentados pelos consumidores rurais, a pergunta que fica é se seria possível a utilização da eletrônica de potência para corrigir ou amenizar os problemas citados?

# **1.2. OBJETIVO**

### 1.2.1. OBJETIVO GERAL

O objetivo fundamental deste trabalho é simular o uso de um conversor de potência *Back* to *Back* para atenuar os problemas que são apresentados nas redes rurais, nomeadamente sobre tensão e afundamentos (ocilações) e interrupções momentaneas.

### 1.2.2. OBJETIVO ESPECÍFICO

Os objetivos específicos são:

- Simular um conversor *Back to Back*;

- Simular as falhas na rede rural;

- Analisar o resultado das simulações das falhas no conversor Back to Back sobre o ponto de vista da carga;

- Caso haja recursos, implementar um conversor de potência *Voltage Source Converter* (VSC).

# 1.3. CALENDARIZAÇÃO

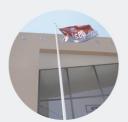

Para a execução deste trabalho foram definidas algumas atividades como, estudo de conversores de potência; estudo do conversor *Back to Back*; familiarização com o programa PSIM entre outras, os desenvolvimentos das atividades geraram a calendarização apresentada na tabela 1.

# 1.4. ORGANIZAÇÃO DO TRABALHO

No capítulo 1 são apresentados os motivos que levaram a execução deste trabalho, bem com os objetivos a serem atingidos com o mesmo, no capitulo 2 é apresentado o estado da arte, onde são apresentados os conceitos dos equipamentos que abrangem a maior parte das funções buscadas pela implementação do conversor *Back to Back*, no capítulo 3 é apresentado as transformadas de Clarke e Park que serão utilizadas na execução deste trabalho, no capítulo 4 é apresentado a modelagem e a forma de controle dos conversores utilizados no *Back to Back*, no capítulo 5 é apresentado o método de sincronização SRF PLL que é utilizado para sincronizar o conversor com a rede, no capítulo 6 são apresentados os dois métodos mais utilizados de modulação PWM, no capítulo 7 são feitas as simulações e apresentações de resultados, bem como a apresentação da atividade prática, e por último o capítulo 8 apresenta as conclusões gerais do trabalho, e as possíveis implementações futuras.

Tabela 1 Calendarização.

# 2. ESTADO DA ARTE

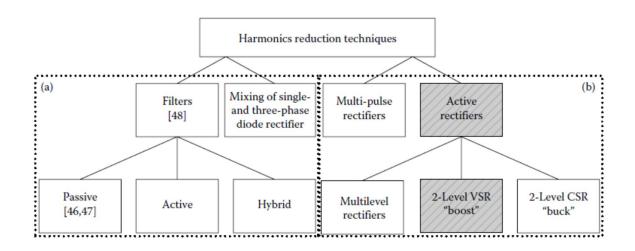

Diante de oscilações de tensão na rede, seja ela devido a condições climáticas, excesso de cargas não lineares ligadas à rede ou outra fonte de perturbação, para amenizar ou suprimir estes problemas existem classes de equipamentos que podem corrigir e evitar introduzir mais perturbações na rede. Entre estes equipamentos podemos citar como mais comuns as fontes de energia ininterruptas ou do inglês *Uninterruptible Power Supply* (UPS), e os filtros passivos e ativos.

Especificamente os filtros passivos e ativos são empregados para correção de fator de potência, eliminação de harmônicos e balanceamento de linhas. Já as UPS são utilizadas onde a necessidade de fornecimento de energia é constante e a falta da mesma pode gerar problemas de ordem material ou física [4].

## 2.1. FILTROS PASSIVOS

A qualidade de energia está diretamente ligada as cargas que a rede alimenta, cargas capazes de armazenar energia como capacitores e indutores geram baixos fatores de potência. Cargas não lineares como fontes de computadores, reatores de lâmpadas

fluorescentes e dispositivos para o acionamento de motores geram um grande conteúdo harmônico e também baixo fator de potência na rede.

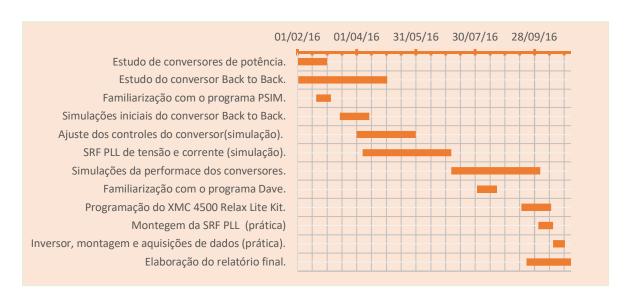

Quando se fala em correção de fator de potência, eliminação de harmônicos de corrente ou tensão na rede elétrica os filtros são os primeiros dispositivos a serem usados. Os filtros passivos são instalados em paralelo as cargas não lineares, em resumo são caminhos de baixa impedância para os harmônicos que se deseja filtrar [5]. A figura 1 mostra filtros passivos de primeira a terceira ordem.

Estes filtros em geral são filtros passa baixa e são configurados para atenuar harmônicos específicos, como os de terceira e quinta ordem [5]. Os filtros passivos são amplamente utilizados, mas possui reveses que dificultam sua instalação e uso. Em geral os problemas vêm com o redimensionamento dos filtros todas as vezes que a carga é modificada, significando uma baixa flexibilidade, além de ser necessário um grande estudo sobre a planta em que se pretende instalar o filtro a fim de evitar efeitos de ressonância em outras frequências que não estariam presentes sem o filtro [6]. Porem na década de 70 surgiu os primeiros trabalhos sobre um novo tipo de filtro, conhecido como filtro ativo.

Figura 1 Filtros passivos, (a) primeira ordem, (b) segunda ordem, (c) terceira ordem [5].

# 2.2. FILTROS ATIVOS

Filtros ativos em geral são compostos por VSI, *Voltage Source Inverters*, ou CSI, *Current Source Inverters*, que basicamente são formados por chaves eletrônicas, que são disparadas

para gerarem sinais específicos de tensão ou corrente para eliminarem, entre outras funções, harmônicos de corrente ou tensão. Tratados como um assunto já bem consolidado por [7] em 1999, foi com o aumento das taxas de chaveamento das chaves eletrônicas, IGBTs (insulated-gated bipolar transistors) e MOSFETs de potência (metal-oxide-semiconductor field-effect transistors), juntamente com a evolução dos processadores de sinais digitais e conversores analógicos digitais (AD) que o números de pesquisas voltadas para a área de filtros ativos começou a aumentar [5] [7].

As grandes vantagens dos filtros ativos sobre os passivos são o tamanho reduzido, a flexibilidade e o não aparecimento do problema de ressonância, além de possuir uma maior capacidade de filtragem [5] [7].

Entre as aplicações possíveis dos filtros ativos (FAs) estão, a eliminação de harmônicos de tensão/corrente, correção do fator de potência, regular tensão nos terminais da carga ou da fonte, eliminar oscilações de tensões, balanceamento de tensão em sistemas trifásico.

Atuar em uma ou mais aplicações citadas anteriormente depende inicialmente dos requisitos e necessidades do projeto, além do tipo de topologia utilizada e da estratégia de controle [6] [7]. Entre as classificações possíveis dos filtros ativos a mais conhecida é a divisão entre filtros ativos série, filtros ativo paralelo (*shunt*) e misto, mais conhecido por universal ou ainda por condicionador universal de qualidade de energia ou do inglês *Unified Power Quality Conditioner* (UPQC) [5] [6] [7].

# 2.2.1 Filtros Ativos Série

São utilizados na correção de problemas relacionados a tensão, nomeadamente harmônicos de tensão, regulação de tensão e balanceamento de tensão em redes trifásicas. Em geral usa-se um transformador para o acoplamento a carga nessa topologia de FAs [7] [8], o que acaba por limitar o seu uso, pois o transformador deve aguentar a corrente total da carga, existem outras topologias que dispensam o uso do transformado [8]. A figura 2 mostra um esquema simplificado de um filtro ativo série.

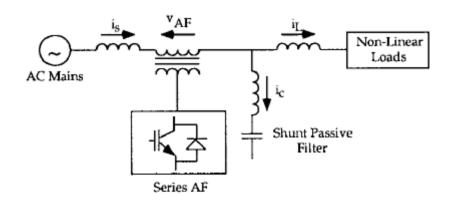

Figura 2 Esquema simplificado de um filtro ativo série [7].

A figura 3 mostras de forma simplificada o funcionamento de um filtro ativo série, basicamente uma fonte de tensão em série injeta uma tensão de mesma amplitude do conteúdo harmônica indesejado em oposição de fase para eliminar o conteúdo harmônico.

Figura 3 Funcionamento de um filtro ativo série. Imagem modificada de [4].

Na figura 3 Vs é a fonte de alimentação da carga que apresenta conteúdos harmônicos indesejados, a fonte Vf representa o filtro ativo que após ler o sinal da Vs e separar o conteúdo harmônico indesejado, injeta um sinal de tensão para a correção, assim a tensão vista pela carga é puramente senoidal.

### 2.2.2 Filtros Ativos Paralelo

Filtros ativos paralelo são os FAs mais utilizados, em geral são empregados para corrigir os harmônicos que as cargas não lineares introduzem na corrente e que acabam aparecendo no ponto de acoplamento entre a fonte e a carga. Apresentam como principais

funcionalidades a correção do fator de potência, redução ou eliminação dos harmônicos de corrente e o ajuste de correntes desbalanceadas [4] [7] [8]. A figura 4 mostra um esquema simplificado de um filtro ativo paralelo.

Figura 4 Esquema simplificado de um filtro ativo paralelo (shunt) [5].

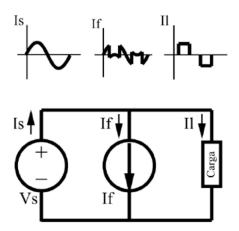

A figura 4 mostra um esquema simplificado do filtro ativo paralelo. A figura 5 Mostra o funcionamento do filtro ativo paralelo, usando uma analogia a uma fonte de corrente alocada em paralelo com a carga.

Figura 5 Funcionamento de um filtro ativo paralelo. Imagem modificada de [4].

A corrente I1 mostrada na figura 5 representa a corrente distorcida e carregada de harmônicos devido à presença de uma carga não linear, If de forma análoga a Vf do filtro ativo série é a fonte de corrente que fornecerá a corrente de correção de If, para deixa-la puramente senoidal. Após a correção da corrente a fonte Vs enxerga a carga como uma carga linear, puramente resistiva.

# 2.2.3 Condicionador Universal de Qualidade de Energia

Considerado por [7] como o filtro ativo ideal, corrige problemas de harmônicos de corrente e tensão, geralmente é empregado em equipamentos médicos, pois estes tipos de equipamentos necessitam de energia livre de perturbações. A figura 6 mostra um esquema simplificado do condicionador universal de qualidade de energia. Este filtro ativo tem no custo a sua principal desvantagem.

Figura 6 Condicionador Universal de Qualidade de Energia [7].

Uma saída mais barata para utilizar os benificios dos filtros serie e paralelo juntos, é o filtro híbrido, que é composto por um filtro ativo série e um filtro parelelo passivo [7]. A figura 7 mostra um esquema simplificado de um filtro híbrido.

Figura 7 Filtro híbrido [7].

### 2.2.4 Controle de Filtros Ativos

Considerado na literatura com parte principal do processo de filtragem ativa [4] [7] [8], a estratégia de controle dos FAs pode ser dividido em três etapas para sua implementeação.

A primeira etapa consiste no condicionamento do sinal de corrente ou tensão, nesta etapa é feita a leitura do sinal de tensão ou de corrente. O emprego de sensores de efeito Hall é comum para as duas medições porem há outros métodos de medição tanto de corrente como de tensão [7]. Ainda os sinais podem ser tratados analogicamente ou digitalmente para evitar problemas de leitura.

A segunda etapa tem efeito direto no transitório bem como no regime permanete do filtro, pois cria os sinais de compensação. Esta etapa é conhecida como derivação dos sinais de compensação [4] [7] [8], onde é comum usar ou o domínio do tempo ou da frequência para desenvolver os sinais de compensação. No dominio da frequência faz-se uso da tranformada de Fourier para isolar os harmônicos indesejados. Já no domínio do tempo existem outras estratégias a se aplicar, como por exemplo, o método da potência ativa e reativa instantanea "p-q", ou o metodo da refência sincrona "d-q" que transforma as variáveis lidas em grandezas de valores contínuos [7].

A terceira e útima etapa consiste na geração dos pulsos de *gate* nas chaves eletrônicas. Esta etapa pode ser controlada por controle PWM de corrente ou tensão, PWM do inglês *Pulse Width Modulation*, lógica difusa entre outras que podem ser implementadas em hardware dedicado como os DSP, também do inglês *Digital Signal Processor* [4] [7] [8].

### 2.3. FONTES ININTERRUPTAS DE POTÊNCIA

São conhecidos também por *Uninterruptible Power Supply* (UPS). A UPS já é uma tecnologia que vem sendo estudada e usada há bastante tempo, podem ser categorizadas conforme a sua atuação em relação à carga. Em [4] as UPS são divididas em 3 categorias, *Nobreaks on-line, Nobreaks off-line* e *Nobreaks* interativos, *Nobreaks* é a nomenclatura comumente utilizada no Brasil para fontes ininterruptas de potência [4]. Em [9] a classificação é feita em três categorias distintas, UPS estáticas (*static*), UPS rotativas (*Rotary*) e a junção das duas UPS híbridas (*Hybrid*), Todas as apresentadas em [4] se encaixam na categoria de UPS estáticas, pois possuem somente elementos estáticos na sua topologia para fazer a conversão de energia.

A categoria de UPS estática será descrita em seguida, as outras duas UPS rotativa e híbrida não fazem parte do interesse deste trabalho.

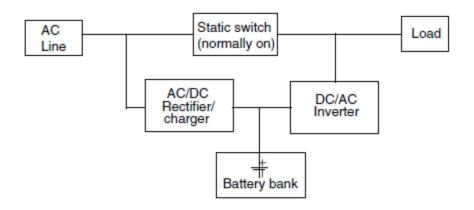

### 2.3.1 UPS on-line

Basicamente é formada por um retificador, um banco de baterias e um inversor, são chamadas de UPS *on-line* por que o retificador esta continuamente alimentando o barremanto DC, o retificador deve prover a potência total necessária para suprir as necessidades da carga, bem como o carregamento do banco de baterias [9]. A figura 8 apresenta um diagrama de blocos com as principais que formam a UPS *on-line*.

Figura 8 Diagrama de blocos de uma UPS on-line [4].

A carga recebe a tensão com boa quaidade por existir um barramento de corrente contínua (CC). Este barramento permite que as tensões entregue a carga sejam independentes das tensões ou da frequência da rede.

Apesar da figura 8 apresentar um bloco com um diodo na parte da retificação, muitos trabalhos apresentam outras topologia para retificação, aumentando a performace e a qualidade da energia [10] inclusive topologia *multilevel* para os conversores [11].

O modo de operação das UPS *on-line* divide-se em três partes, funcinamento normal que ocorre quando a retificação alimenta a bateria e a bateria fornece energia para o inversor, funcionamento e falta de tensão na rede, quando há falta de alimentação por parte da rede o banco de baterias encarrega-se de suprir a energia para a carga, até que a rede volte a alimentar o retificador. E por último o modo *baypass* que cumpre a função de ignorar a UPS, caso a mesma apresente funcionamento inadequado [9].

### 2.3.2 UPS off-line

As UPS *off-line* são formadas por um retificador, um banco de bateria, um inversor e uma chave estática. Agora o retificador é usado para carregar a bateria, não existe mais um barramento CC entre a rede e a carga, a carga está ligada diretamente à rede através de uma chave estática. A figura 9 mostra um diagrama de blocos de uma UPS *off-line*.

Figura 9 Diagrama de blocos de uma UPS off-line [9].

Essa configuração não permite nenhum processamento eletrônico da tensão entregue à carga pela rede, em alguns casos o inversor é usado como filtro ativo paralelo para retirar harmônicos de corrente da carga e melhorar o fator de potência, mas é mais comum que o inversor esteja desligado quando o sistema está operando com a tensão da rede [9].

No modo de funcionamento normal a chave estática liga à rede a carga e o retificador carrega a bateria. Quando a rede não está operando normalmente a chave estática abre e o inversor passa a fornecer a energia da bateria para a carga. Esta configuração não precisa de um modo de *bypass* [4] [9].

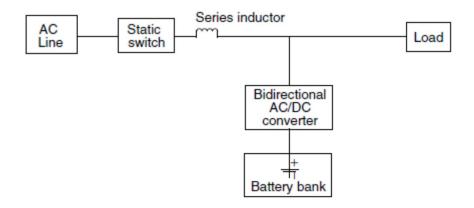

### 2.3.3 UPS Interativa

Com uma estrutura diferenciada é formada por uma chave estática, um indutor, um conversor bidirecional e um banco de bateria [9]. A figura 10 apresenta um diagrama de blocos com as partes que formam a UPS interativa.

No modo de funcionamento normal a fonte alimenta a carga e o conversor carrega o banco de bateria além de promover a filtragem do sinal da rede como um filtro ativo, quando a rede falha o conversor passa a trabalhar como um inversor e alimenta a carga com a energia do banco de bateria [9].

Figura 10 Diagrama de blocos de uma UPS interativa [9].

# 2.4. CONVERSORES CA-CC-CA

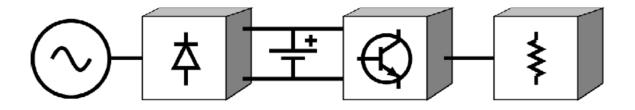

Conversores CA-CC-CA são formados por um estágio de retificação, um barramento CC e um estágio de inversão. São de grande utilidade na indústria, grande parte da sua aplicação é direcionada para sistemas de ajuste de velocidade de motores e geradores [12]. A figura 11 mostra o diagrama de blocos de diferentes tipos topologia para conversores CA-CC-CA.

Figura 11 Diagrama de blocos de conversores CA-CC-CA, (a) retificação a diodo, (b) retificação por chaves eletrônicas. Imagem modificada de [12].

Na figura 11 (a), entre inúmeras formas de conversão de energia os conversores a diodo mono ou trifásicos são comumente utilizados por suas robustez e baixo custo, porem produzem um conteúdo harmônico nas correntes de entrada que são indesejáveis para a rede [12]. Conhecida como ponte de Greatz, a retificação a diodo trifásica é a estrutura apresentada na figura 12.

Figura 12 Conversor trifásico a diodo em ponte completa, ponte de Greatz [13].

Fazem parte dos conversores não controlados [13], são muito comuns em equipamentos eletrônicos como fontes de computadores, reatores de lâmpadas fluorescentes e outros.

A estrutura da figura 11 (b) possui um retificador formado por chaves eletrônicas, é comum o uso de IGBTs nestes casos. Conhecidos VSC *Voltage Source Converters*, que opera como um retificador também conhecido como VSR *Voltage Source Retifeirs*, é uma estrutura que e possui vantagens sobre outras estruturas de conversão devido à possibilidade de fluxo bidirecional de potência e baixo conteúdo harmônico [12].

Figura 13 Voltage Source Rectifeir trifásico.

Para que haja um controle do fluxo de potência, o barramento CC deve ter tensão maior que a tensão de linha da rede [14], por isso este tipo de configuração de conversor é visto com um conversor elevador (*boost*) na retificação e um conversor rebaixador (*buck*) na inversão [15].

Os VSR juntamente com os filtros ativos, são considerados uma forma de reduzir a poluição harmônica na rede, este tipo de retificação também consegue um fator de potência unitário, que o torna um modelo de retificação muito procurado. Os grandes reveses dessa configuração são o preço das chaves eletrônicas, especialmente as que são destinadas a potências mais elevadas. Outro problema dos VSR são as perdas por comutação [12].

Figura 14 VSR utilizados como método de redução de harmônicos na rede [12].

No outro lado do barramento CC existe um VSC operando como um inversor, também conhecido como VSI, *Voltage Soure Inverte*. O inversor é responsável por transforma a tensão continua do barramento CC em uma tensão alternada. A tensão entregue a carga não necessariamente terá fase ou frequência da tensão da rede, isso torna o inversor um equipamento muito utilizado para controle de velocidade de motores de corrente alternada [12].

Figura 15 Inversor VSI Voltage Source Inverter [16].

A junção de um VSR a um VSI através de um barramento CC da origem a uma configuração chamada de *Back to Back*. Esta configuração de conversor é muito utilizada em diversas aplicações, nomeadamente em geração de energia eólica [14] [17], controle de velocidade de motores [12] entre outras aplicações.

O nome Back to Back é muitas vezes abreviado para BTB ou ainda B2B.

### 2.5. ESCOLHA DO SISTEMA UTILIZADO

Após uma pesquisa na literatura, fica evidente a versatilidade do conversor *Back to Back*. Este está presente em inúmeras aplicações e dos mais variados tipos.

Com o crescente aumento dos sistemas descentralizados de produção de energia como, por exemplo, energia eólica, solar entre outras, não é difícil de pensar que esta forma de produção de energia seja um meio de vencer as barreiras dimensionais para o território brasileiro.

É importante pensar em sistemas que possam se adaptar a novas situações. Por exemplo, um empresário do meio rural pode instalar um sistema de geração de energia eólica na

localidade da sua propriedade para consumo próprio, isso por si só já faria o *Back to Back* um conversor útil, mas o excedente da produção pode ser armazenado em baterias, supercapacitores ou simplesmente entregues a rede elétrica, neste caso o uso do conversor *Back to Back* também é possível.

Outra aplicação possível é o uso da energia reativa como forma de ajudar a estabilizar a tensão da rede, o VSC pode controlar a injeção de potência reativa na rede quando existir a necessidade da estabilização da tensão da mesma [18].

Assim visto as inúmeras aplicações e sua característica perante as condições de qualidade no ponto de acoplamento da rede, além de que o conversor *Back to Back* possui a capacidade de realizar as funções dos filtros e das UPS, a escolha deste sistema se tornou natural.

# 3. TRANSFORMADAS DE CLARKE E PARK

As transformações são comumente utilizadas para facilitar os cálculos ou o entendimento do sistema que está sendo utilizado. Pode-se citar como exemplo a transformada de Laplace que é utilizada para mudar o domínio do tempo para o domínio da frequência, assim facilitando alguns cálculos e ajudando na compreensão de sistemas de controle. As transformações que serão apresentadas nesta seção do trabalho não são diferentes, possuem o mesmo intuito de facilitar a modelagem matemática, a compreensão do sistema e facilitar o sistema de controle.

O Sistema trifásico ou abc é representado por três fasores estacionários que estão separados por um angulo de 120 graus ou  $\frac{2\pi}{3}$  radianos. A figura 16 mostra a representação de um sistema trifásico.

Figura 16 Sistema trifásico abc. Imagem modificada de [15].

O sistema de distribuição de energia elétrica, na sua grande maioria, é feito através de um sistema trifásico de tensão. A soma vetorial do sistema trifásico é igual a zero, o mesmo ocorre em um sistema balanceado de distribuição de energia elétrica [19].

O sistema apresentado na figura 16 pode ser representado pela equação (1).

$$\begin{cases} a = \cos(\theta) \\ b = \cos\left(\theta - \frac{2\pi}{3}\right) \\ c = \cos\left(\theta + \frac{2\pi}{3}\right) \end{cases}$$

(1)

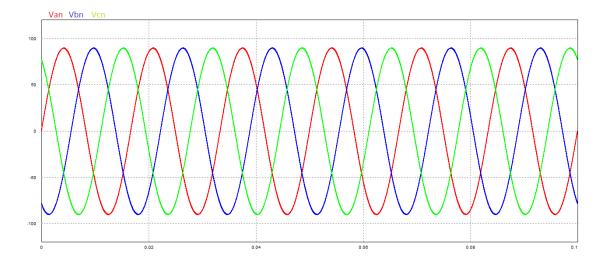

No sistema trifásico de distribuição de energia os sinais de tensão da rede são representados como na figura 17.

Figura 17 Tensões no sistema trifásico.

As tensões do sistema são representadas pela equação (2).

$$\begin{cases} V_a = V \cos(\omega t); \\ V_b = V \cos\left(\omega t - \frac{2\pi}{3}\right); \\ V_c = V \cos\left(\omega t + \frac{2\pi}{3}\right). \end{cases}$$

(2)

Onde V é a tensão de pico de fase e  $\omega$  é a frequência angular da rede.

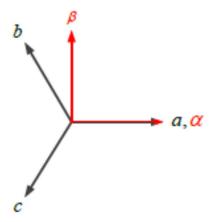

# 3.1. TRANSFORMADA DE CLARKE

A transformada de Clarke é aplicada para a transformação de sistemas trifásicos em um sistema de duas fases ortogonais chamadas de  $\alpha$  e  $\beta$  [15], as fases estão representadas na figura 18.

Figura 18 Representação dos sistemas abc trifásico e αβ bifásico [15].

A transformada de Clarke representa o sistema trifásico em um sistema  $\alpha\beta$  através da decomposição de cada fase do sistema abc em apenas duas fases. A decomposição do sistema abc em  $\alpha$  fica;

$$\alpha = a + b\cos(\frac{2\pi}{3}) + c\cos(\frac{4\pi}{3}). \tag{3}$$

A mesma decomposição feita na fase  $\beta$  é representada na equação (4).

$$\beta = b \cos(\frac{\pi}{6}) - c \cos(\frac{\pi}{6}). \tag{4}$$

Simplificando as equações (3) e (4) tem-se;

$$\alpha = a - \frac{1}{2}b - \frac{1}{2}c. {(5)}$$

$$\beta = \frac{\sqrt{3}}{2}b - \frac{\sqrt{3}}{2}c. \tag{6}$$

Como o conversor *Back to Back* que será utilizado nesse trabalho não possui neutro, as componentes homopolares não aparecem no sistema [20], por esse motivo não estão sendo consideradas na transformada de Clarke. Assim a transformada de Clarke é dada por;

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = N \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}. \tag{7}$$

Onde N é uma constante usada para manter a potência do sistema constante e é dada por [21];

$$N = \sqrt{\frac{2}{3}}. (8)$$

Assim o sistema completo é dado pela equação (9).

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}. \tag{9}$$

Em algumas literaturas manter a amplitude do sinal (tensão ou corrente) nos diferentes sistemas de coordenadas é o principal interesse, assim N assume o valor de  $\frac{2}{3}$  [15]. Para esse trabalho usou-se a constante que mantém a tensão de pico igual nos dois sistemas de coordenadas, a transformada de Clarke é apresentada na equação (10);

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}. \tag{10}$$

A transformada inversa de Clarke é dada por [15];

$$\begin{bmatrix} a \\ b \\ c \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \frac{1}{2} & \frac{\sqrt{3}}{2} \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \end{bmatrix}.$$

(11)

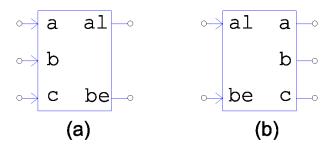

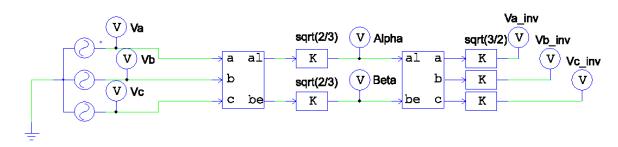

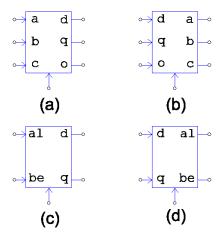

No programa *PSIM*, o qual será utilizado para fazer as simulações nesta dissertação, existem blocos para fazer a transformação de Clarke e sua inversa. A figura 19 mostra os blocos do *PSIM* responsáveis pelas transformações.

Figura 19 (a) Transformada de Clarke. (b) Transformada inversa de Clarke.

O circuito para a transformação do sistema abc para  $\alpha\beta$  é mostrado na figura 20. O *PSIM* apresenta no bloco da transformada Clarke a equação (9), em [15] uma constante de multiplicação é proposta para corrigir a diferença. O valor dessa constante é igual  $\sqrt{\frac{2}{3}}$ , para a transformada inversa uma nova constante deve ser usada para manter as tensões de pico equivalentes  $\sqrt{\frac{3}{2}}$ .

Figura 20 Circuito de transformações.

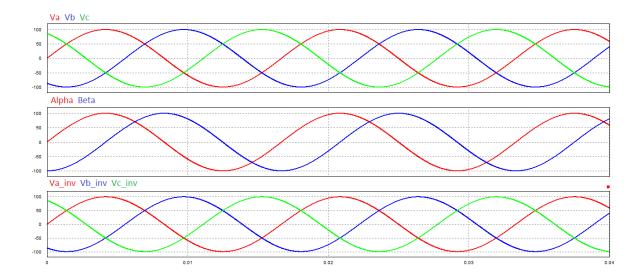

Os sinais resultantes das transformadas são apresentados na figura 21.

Figura 21 Sinais das transformações.

As tensões no sistema αβ é representada pela equação (12).

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{a} \\ V_{b} \\ V_{c} \end{bmatrix}.$$

(12)

O mesmo vale para as correntes em  $\alpha\beta$ . A vantagem da troca do sistema abc para a  $\alpha\beta$  é a redução do número de variáveis além de ser possível encontrar o módulo e o ângulo  $\theta_e$  da rede.

$$M\acute{o}dulo = \sqrt{V_{\alpha}^2 + V_{\beta}^2}. \tag{13}$$

$$\theta_e = \tan^{-1} \left( \frac{V_\alpha}{V_\beta} \right). \tag{14}$$

O ângulo  $\theta_e$  será importante para a obtenção da transformada de Park.

# 3.2. TRANSFORMADA DE PARK

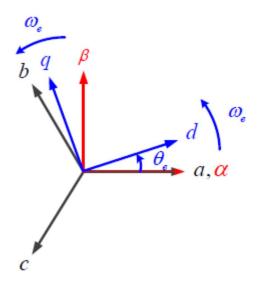

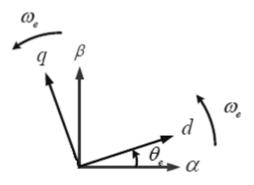

Diferente dos sistemas abc e  $\alpha\beta$ , o sistema dq não é estacionário, este sistema rotaciona na mesma frequência da rede. A figura 22 mostra os três sistemas sobrepostos.

Figura 22 Sistemas abc em preto, αβ em vermelho e dq em azul [15].

O sistema dq pode ser obtido diretamente do sistema abc através da transformada de Park ou faz-se primeiro a transformada de Clarke para o sistema αβ e depois a transformada de Park para o sistema dq [15]. Primeiramente será feito a transformação abc para dq.

Figura 23 Transformação do sistema abc para dq. Imagem modificada de [15].

Assim como apresentado na transformada de Clarke as componentes homopolares não serão levas em conta para a transformação. De forma semelhante à transformada de Clarke, a transformada de Park também é feita através da decomposição das fases abc só que agora para o sistema dq [21]. Depois da decomposição das três fases em d, chamada de em inglês de *direct axis*, d é representado pela equação (15);

$$d = a\cos(\theta_e) + b\cos\left(\theta_e - \frac{2\pi}{3}\right) + c\cos\left(\theta_e + \frac{2\pi}{3}\right). \tag{15}$$

A mesma decomposição para q, chamado em inglês de *quadrature-axis*, é apresentada em (16);

$$q = -a \operatorname{sen}(\theta_e) - b \operatorname{sen}\left(\theta_e - \frac{2\pi}{3}\right) - c \operatorname{sen}\left(\theta_e + \frac{2\pi}{3}\right). \tag{16}$$

Juntando as duas decomposições, tem-se a transformada de Park;

$$\begin{bmatrix} d \\ q \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos \theta_e & \cos \left(\theta_e - \frac{2\pi}{3}\right) & \cos \left(\theta_e + \frac{2\pi}{3}\right) \\ -\sin \theta_e & -\sin \left(\theta_e - \frac{2\pi}{3}\right) & -\sin \left(\theta_e + \frac{2\pi}{3}\right) \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}.$$

(17)

É importante notar a necessidade do ângulo  $\theta_e$ , isso se deve a característica rotacional do sistema dq.

A transformada inversa de Park para o sistema abc é dada pela equação (18) [15];

$$\begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} \cos \theta_e & -\sin \theta_e \\ \cos \left(\theta_e - \frac{2\pi}{3}\right) & -\sin \left(\theta_e - \frac{2\pi}{3}\right) \\ \cos \left(\theta_e + \frac{2\pi}{3}\right) & -\sin \left(\theta_e + \frac{2\pi}{3}\right) \end{bmatrix} \begin{bmatrix} d \\ q \end{bmatrix}.$$

(18)

Agora será feita a transformada de Park a partir do sistema  $\alpha\beta$ . Assim como feito anteriormente os fasores  $\alpha$  e  $\beta$  serão decompostos em dq.

Figura 24 Transformada de Park a partir do sistema αβ. Imagem modificada de [15].

Seguindo a mesma ideia das outras transformações, α e β serão decompostos para d e q. Após as decomposições a equação (19) mostra a transformada de Park [15];

$$\begin{bmatrix} d \\ q \end{bmatrix} = \begin{bmatrix} \cos(\theta_e) & \sin(\theta_e) \\ -\sin(\theta_e) & \cos(\theta_e) \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \end{bmatrix}.$$

(19)

Novamente o ângulo  $\theta_e$  mostra-se necessário para a transformada de Park. Para achar a transformada inversa de Park basta isolar os termos de  $\alpha$  e  $\beta$  da equação (20);

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \begin{bmatrix} \cos(\theta_e) & -\sin(\theta_e) \\ \sin(\theta_e) & \cos(\theta_e) \end{bmatrix}^{-1} \begin{bmatrix} d \\ q \end{bmatrix}. \tag{20}$$

Resolver a matriz inversa a transformada inversa é dada pela equação (21) [15].

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \begin{bmatrix} \cos(\theta_e) & \sin(\theta_e) \\ -\sin(\theta_e) & \cos(\theta_e) \end{bmatrix} \begin{bmatrix} d \\ q \end{bmatrix}. \tag{21}$$

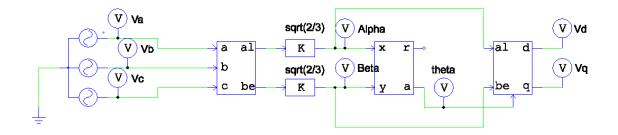

O programa *PSIM* possui bloco para a transformada de Park, tanto partindo do sistema abc quanto do sistema αβ. A figura 25 mostra os blocos responsáveis pelas transformadas de Park no programa *PSIM*.

Figura 25 (a) abc para dq. (b) dq para abc. (c) αβ para dq (d) dq para αβ.

O circuito mostrado na figura 26 apresenta as transformações de abc para  $\alpha\beta$  em seguida para dq no programa *PSIM*.

Figura 26 Circuito para a transformada de Park.

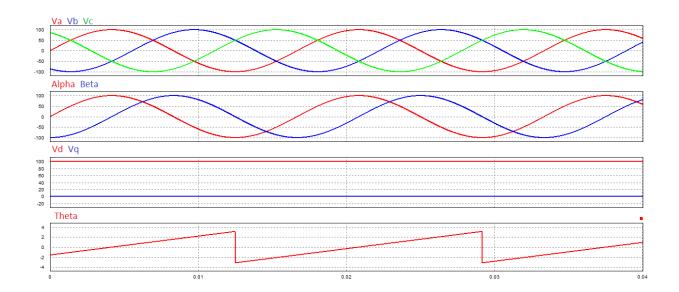

O bloco de transformação de xy/ra mostrado na figura 27 é usado para estimar o ângulo  $\theta_e$ , onde a saída r apresenta o módulo entre entradas x e y dado pela equação (22) e a saída a dá o ângulo  $\theta_e$ , dado pela equação (23).

Figura 27 Bloco que estima o ângulo  $\theta_e$  no programa PSIM.

$$r = \sqrt{x^2 + y^2};\tag{22}$$

$$a = \theta = \tan^{-1}\left(\frac{y}{x}\right). \tag{23}$$

A figura 28 mostra os sinais de tensão para todos os sistemas, mostra também o ângulo estimado pelo bloco *xy/ra* mostrado na figura 27.

Figura 28 Sinais de tensão em cada sistema.

A grande vantagem de usar o sistema dq é de que sinais anteriormente senoidais agora tornaram-se constantes [15], esse fato facilita muito o controle e a modelagem do VSC utilizado neste trabalho.

# 4. FUNCIONAMENTO DOS CONVERSORES CA-CCCA

Formado por dois conversores de tensão VSC (*Voltage source* converter) que estão unidos por um barramento CC, a melhor palavra para definir o conversor *back-to-back* é flexibilidade devido ao número de aplicações em que esse tipo de conversor é utilizado. Entre as possíveis aplicações o controle ajustável da velocidade de motores e geradores [12], geração de energia eólica [17], entre outras [22] [23].

Por existir um barramento CC o controle de cada conversor é feito separadamente, ambos podem ser vistos como VSR, *Voltage Source Retifeirs*, ou VSI, *Voltage Source Inverter*, isso possibilita o fluxo bidirecional da potência, outra vantagem é que o estudo de cada conversor é praticamente feito da mesma forma e separadamente [17] [14].

# 4.1. CONVERSORES CA-CC

Retificador controlado é o nome dado ao conversor que transforma tensão e corrente alternada em tensão e corrente continua com controle da tensão média de saída [24]. Portando os retificadores controlados são conversores CA-CC, VSC, que fazem a interface entre a rede e a carga. São conhecidos como retificadores ativos e podem ser mono ou trifásicos [12].

Retificadores ativos são conversores que aumentam a qualidade da energia no ponto de acoplamento com a rede, pois são capazes de controlar o fluxo de potência ativa entre a rede e o barramento CC e controlar o fluxo de potência reativa entre a rede e o lado CA do retificador [12] [15].

Buscando melhorar a utilização da energia, o controle do fluxo de potência reativa é extremamente importante, pois o fluxo de potência reativa definirá se o conversor trabalhará com fator de potência unitário. Será visto na seção 6 de técnicas de modulação que o conversor VSC possui harmônicos nas bandas laterais da frequência de comutação das chaves eletrônicas, que em geral são elevadas facilitando a filtragem destes harmônicos.

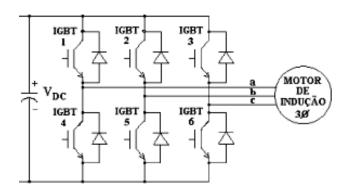

O controle do fluxo de potência ativa ainda define o sentido da potência, ou seja, o conversor pode extrair potência da rede ou fornecer potência a ela. Entre as inúmeras topologias a mais utilizada para o trânsito bidirecional de potência é a trifásica, que possui seis chaves eletrônicas [12]. Atualmente IGBTs são usados como as chaves eletrônicas, a estrutura do VSC pode ser visto na figura 29.

Figura 29 Configuração do retificador ativo com seis IGBTs.

Alguns elementos são muito importantes para o bom funcionamento deste conversor, entre eles estão o indutor de entrada e o capacitor no barramento CC. O indutor se faz importante por filtrar as oscilações de corrente (*ripples*) e servir como um armazenador de energia, isso para quando o VSC estiver na função de retificação, assim o conversor trabalha como um conversor elevador (*boost*). Por outro lado quando o conversor está fornecendo energia para a rede, trabalhando como um inversor, ele funciona como um conversor rebaixador (*buck*) [15]. O capacitor no barramento CC ajuda a estabilizar a tensão no mesmo.

Ambos, capacitor e indutor, influenciam a dinâmica do conversor e serão utilizados na modelagem [15].

### 4.1.1. MODELAGEM DO CONVERSOR VSC

A função de um modelo matemático é fornecer uma representação precisa do sistema modelado, este se faz útil para desenvolvimento de um controle e para que o mesmo tenha boa resposta. O modelo matemático ainda pode ser utilizado para avaliações do sistema, bem como analise das características dinâmicas além de analisar e selecionar parâmetros do sistema [12].

Para a modelagem que será feita do conversor serão assumidos alguns parâmetros, a tensão de lado CA do conversor é representada somente por sua frequência fundamental, não

utilizar as altas frequências implica em ignorar qualquer fenômeno de indução que possa ser causado pela alta frequência, o que reflete em não haver credibilidade para analises de compatibilidade eletromagnética. Mas como é um método rápido, é recomendado para estudos universitários [12]. Outra consideração é que não há perdas nas chaves semicondutoras, ou seja, elas são consideradas ideais, as únicas perdas estarão presentes na resistência da indutância da rede e na resistência do capacitor localizado no barramento CC.

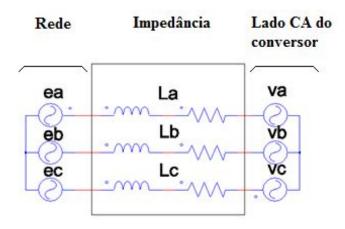

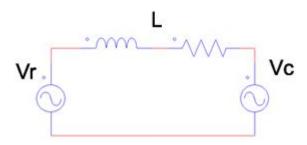

Para controlar o fluxo de potência deve-se controlar o sentido da corrente que flui pela impedância RL mostrada da figura 30. Esta impedância separa a rede do lado CA do conversor. A figura 31 mostra um modelo simplificado da rede e do lado CA do conversor [24] [12].

Figura 30 Modelagem do AC do conversor.

Onde *ea*, *eb* e *ec* são as tensões trifásicas da rede e *va*, *vb* e *vc* são as tensões geradas pelo conversor. Para a análise de transferência de potência entre duas fontes simplifica-se o sistema da figura 30 para o apresentado na figura 31 [24] [12].

Figura 31 Sistema para análise de transferência de potência entre fontes.

Tem-se então Vr que representa a tensão da rede (ea, eb e ec) e Vc representando a tensão AC produzida pelo conversor (va, vb e vc). Para encontrar o fluxo de potência deve-se analisar qual é a influência que as fontes têm sobre ele. As fontes de tensão podem ser equacionadas como em (24) e (25) [25]:

Tensão Vr;

$$Vr = Vre^{j\theta_1}. (24)$$

Tensão Vc;

$$Vc = Vce^{j\theta_2}. (25)$$

A potência aparente vista pela rede é representada por;

$$S_r = P_r + jQ_r = VrI_r^*. (26)$$

Onde  $I_r^*$  é o conjugado da corrente, que é dado por;

$$I_r^* = \frac{V_r^* - V_c^*}{Z^*}. (27)$$

$Z^*$  é a impedância L entre a rede o conversor, substituindo (27) em (26) tem-se;

$$S_r = Vr\left(\frac{V_r^* - V_c^*}{Z^*}\right) = \frac{V_r^2 - V_r V_c e^{-j(\varphi)}}{R - jX}.$$

(28)

Onde  $\varphi = \theta_2 - \theta_1$ , manipulando a equação (28);

$$S_r = \frac{(R+jX)}{(R+jX)} \left( \frac{V_r^2 - V_r V_c e^{-j(\varphi)}}{R-jX} \right).$$

(29)

Expandindo o termo  $e^{-j(\varphi)}$ ;

$$S_r = (R + JX) \left( \frac{V_r^2 - V_r V_c \cos(-\varphi) - j V_r V_c \sin(-\varphi)}{R^2 + X^2} \right).$$

(30)

Considerando que a função cosseno é par e a seno ímpar pode-se simplificar a equação (30);

$$S_r = (R + JX) \left( \frac{V_r^2 - V_r V_c \cos(\varphi) + j V_r V_c \sin(\varphi)}{R^2 + X^2} \right).$$

(31)

Efetuando a multiplicação, e separando em parte real e imaginária;

$$S_r = \left(\frac{RV_r^2 - RV_rV_c\cos(\varphi) - XV_rV_c\sin(\varphi)}{R^2 + X^2}\right) + j\left(\frac{XV_r^2 - XV_rV_c\cos(\varphi) - RV_rV_c\sin(\varphi)}{R^2 + X^2}\right). \tag{32}$$

Assim a potencial real vista pela rede é igual a;

$$P_r = \left(\frac{RV_r^2 - RV_r V_c \cos(\varphi) - XV_r V_c \sin(\varphi)}{R^2 + X^2}\right). \tag{33}$$

E a potência reativa é igual;

$$Q_r = j \left( \frac{XV_r^2 - XV_r V_c \cos(\varphi) - RV_r V_c \sin(\varphi)}{R^2 + X^2} \right). \tag{34}$$

Usando a mesma análise para o a potência vista pela fonte  $V_c$ ;

$$P_c = \left(\frac{RV_c^2 - RV_rV_c\cos(\varphi) + XV_rV_c\sin(\varphi)}{R^2 + X^2}\right). \tag{35}$$

E a potência reativa vista pela  $V_c$  fonte fica;

$$Q_c = j \left( \frac{XV_c^2 - XV_r V_c \cos(\varphi) - RV_r V_c \sin(\varphi)}{R^2 + X^2} \right). \tag{36}$$

Considereando que a resistência R é bem inferior a reatância X, pode-se então despresar os efeitos da resistência na analise, então a potência vista por  $V_r$  é igual a;

$$P_r = \left(\frac{-V_r V_c \sin(\varphi)}{X}\right),\tag{37}$$

$$Q_r = j\left(\frac{V_r^2 - V_r V_c \cos(\varphi)}{X}\right). \tag{38}$$

E para  $V_c$ ;

$$P_c = \left(\frac{V_r V_c \sin(\varphi)}{X}\right),\tag{39}$$

$$Q_c = j \left( \frac{V_c^2 - V_r V_c \cos(\varphi)}{X} \right). \tag{40}$$

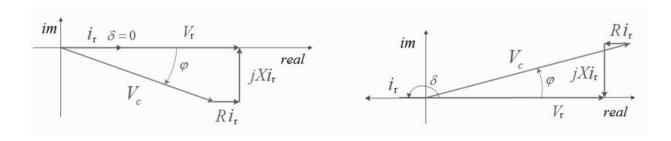

Para a potência ativa da fonte, a variação do ângulo  $\varphi$  define se a fonte está a receber ou a fornecer potência ativa. Se o ângulo  $\varphi$  é positivo a fonte estará recebendo potência do conversor, caso contrário estará fornecendo potência, a equação (41) sintetiza o fluxo de potência ativa [25].

$$P_r = \begin{cases} Fornecendo \ potência \ ativa, \ \varphi < 0; \\ Recebendo \ potência \ ativa, \ \varphi > 0. \end{cases} \tag{41}$$

A potência reativa tem seu fluxo regulado pela tensão da rede  $V_r$ , se a tensão da rede for maior que a tensão do conversor  $V_c \cos(\varphi)$  a potência reativa estará sendo fornecida pela rede, caso contrário está recebendo potência reativa. Na equação (42) essa relação sintetiza o fluxo de potência reativa [25].

$$Q_r = \begin{cases} Fornecendo \ potência \ reativa, \ V_r > V_c \cos(\varphi); \\ Recebendo \ potência \ reativa, \ V_r < V_c \cos(\varphi). \end{cases}$$

(42)

Analisando a potência ativa vista pela rede e pelo conversor, percebe-se que elas são opostas, isso significa basicamente que se uma fonte está fornecendo potência a outra está necessariamente recebendo, e que a soma das potências vista pelos dois pontos é igual a zero, isto desconsiderando a potência dissipada na resistência de linha.

A análise fasorial mostrada na figura 32 apresenta a relação do ângulo  $\varphi$  com a direção da corrente  $I_r$ .

Figura 32 (a) Potência ativa sendo entregue pela rede, (b) potência ativa sendo entregue pelo conversor. Imagem modificada de [15].

Considerando a tensão da rede como um valor fixo, gerar as tensões do conversor (va, vb e vc) conforme a necessidade é a única forma de variar o fluxo de potência ativa e reativa entre a rede e o conversor. Porém analisando as potências ativa e reativa apresentadas nas equações (39) e (40) é visível que a variação de uma potência interfere diretamente na outra.

O controle separado da potência ativa e reativa fica prejudicado pelos termos  $V_c$  e  $\varphi$  que são comuns às duas equações. Este acoplamento presente entre as potências impediria, por exemplo, que o conversor trabalhasse sempre com fator de potência unitário, pois a variação da demanda da potência ativa interfere na potência reativa.

Assim a mudança de sistemas de coordenadas das tensões e das correntes é proposta para corrigir este problema [12] [15] [25]. Usando as transformadas de Clarke e Park, como visto na seção 3, todo o conversor será modelado para o sistema de referência dq.

A modelagem da parte CA do conversor começa pela definição da fonte trifásica na referência abc, que pode ser escrita como;

$$e_a = E\cos(\omega t);$$

$$e_b = E\cos\left(\omega t + \frac{2\pi}{3}\right);$$

$$e_c = E\cos\left(\omega t - \frac{2\pi}{3}\right).$$

(43)

Usando a lei de Kirchhoff das tensões, um sistema balanceado trifásico sem neutro como apresentado na figura 29 pode ser representado pela equação (44) [26];

$$\begin{cases} e_{a} = Ri_{la} + L\frac{di_{la}}{dt} + v_{a}; \\ e_{b} = Ri_{lb} + L\frac{di_{lb}}{dt} + v_{b}; \\ e_{c} = Ri_{lc} + L\frac{di_{lc}}{dt} + v_{c}. \end{cases}$$

(44)

Usando a transformada de Clarke dada pela equação (11), as tensões da rede são transferidas para o sistema de coordenadas αβ. As tensões da rede são representadas pela equação (45) [12];

$$e_{\alpha} = E \cos(\omega t);$$

(45)

$e_{\beta} = E \sin(\omega t).$

Agora aplicando a transformada de Park, equação (19), na equação (45) a tensão da rede é dada pela equação (46), é interessante lembrar que agora os eixos ortogonais d e q estão a rotacionar com a velocidade angular da rede [12].

$$e_d = E;$$

$$e_a = 0.$$

$$(46)$$

A grande vantagem de trabalhar com a transformada de Park é que as variáveis que nos sistemas estacionários eram senoidais agora são constantes, como pode ser visto na equação (46). É importante ressaltar que *E* tem a amplitude do pico de fase do sistema trifásico [15].

No sistema αβ a equações do circuito da figura 30 são apresentadas pela equação (47) [15] [12].

$$\begin{cases} e_{\alpha} = Ri_{\alpha} + L\frac{di_{\alpha}}{dt} + v_{\alpha}; \\ e_{\beta} = Ri_{\beta} + L\frac{di_{\beta}}{dt} + v_{\beta}. \end{cases}$$

$$(47)$$

Usando a transformada de Park do sistema de coordenada αβ para dq dado pela equação (19), pode-se achar a equação do circuito do lado CA do conversor [15]. A tensão e a corrente da rede são dadas por (48) e (49) respectivamente;

$$\begin{bmatrix} e_d \\ e_q \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} e_\alpha \\ e_\beta \end{bmatrix}. \tag{48}$$

$$\begin{bmatrix} i_d \\ i_q \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} i_\alpha \\ i_\beta \end{bmatrix}. \tag{49}$$

Substituindo (47) em (48);

$$\begin{bmatrix} e_d \\ e_q \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} Ri_\alpha + L \frac{di_\alpha}{dt} + v_\alpha \\ Ri_\beta + L \frac{di_\beta}{dt} + v_\beta \end{bmatrix}.$$

(50)

Isolando  $i_{\alpha}$  e  $i_{\beta}$  da equação (49);

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix}^{-1} \begin{bmatrix} i_d \\ i_q \end{bmatrix}. \tag{51}$$

A matriz inversa da equação (49) é dada por;

$$\begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix}^{-1} = \begin{bmatrix} \cos \theta_e & -\sin \theta_e \\ \sin \theta_e & \cos \theta_e \end{bmatrix}. \tag{52}$$

Assim (51) fica;

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} = \begin{bmatrix} \cos \theta_e & -\sin \theta_e \\ \sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} i_d \\ i_q \end{bmatrix}. \tag{53}$$

Expandindo a equação (50);

$$\begin{bmatrix} e_d \\ e_q \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} L \frac{d}{dt} \begin{bmatrix} i_\alpha \\ i_\beta \end{bmatrix} + R \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} i_\alpha \\ i_\beta \end{bmatrix} + \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} v_\alpha \\ v_\beta \end{bmatrix}. \tag{54}$$

Substituindo (53) em (54) e fazendo;

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} v_\alpha \\ v_\beta \end{bmatrix}. \tag{55}$$

tem-se;

$$\begin{bmatrix} e_d \\ e_q \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} L \frac{d}{dt} \begin{bmatrix} i_\alpha \\ i_\beta \end{bmatrix} + R \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \begin{bmatrix} v_d \\ v_q \end{bmatrix}.$$

(56)

Substituindo (53) em (56);

$$\begin{bmatrix} e_d \\ e_g \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} L \frac{d}{dt} \begin{pmatrix} [\cos \theta_e & -\sin \theta_e \\ \sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} i_d \\ i_g \end{bmatrix} + R \begin{bmatrix} i_d \\ i_g \end{bmatrix} + \begin{bmatrix} v_d \\ v_g \end{bmatrix}. \tag{57}$$

Usando a derivada da multiplicação e considerando que;

$$\theta_e = \omega_e t, \ \omega_e = \frac{d\theta_e}{dt}.$$

(58)

$$\begin{bmatrix} e_d \\ e_q \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} L \begin{pmatrix} \begin{bmatrix} -\omega_e \sin \theta_e & -\omega_e \cos \theta_e \\ \omega_e \cos \theta_e & -\omega_e \sin \theta_e \end{bmatrix} \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \begin{bmatrix} \cos \theta_e & -\sin \theta_e \\ \sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} \frac{di_d}{dt} \\ \frac{di_q}{dt} \end{bmatrix} \end{pmatrix}$$

(59)

$$+R\begin{bmatrix}i_d\\i_q\end{bmatrix}+\begin{bmatrix}v_d\\v_q\end{bmatrix}.$$

Desenvolvendo as multiplicações em (59);

$$\begin{bmatrix} e_d \\ e_q \end{bmatrix} = L \begin{bmatrix} 0 & -\omega_e \\ \omega_e & 0 \end{bmatrix} \begin{bmatrix} i_d \\ i_q \end{bmatrix} + L \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \begin{bmatrix} \frac{di_d}{dt} \\ \frac{di_q}{dt} \end{bmatrix} + R \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \begin{bmatrix} v_d \\ v_q \end{bmatrix}.$$

(60)

Por fim tem-se a equação (61), a representação do conversor da figura 29 no sistema de coordenadas dq.

$$\begin{cases} e_d = Ri_d + L\frac{di_d}{dt} - \omega Li_q + v_d; \\ e_q = Ri_q + L\frac{di_q}{dt} + \omega Li_d + v_q. \end{cases}$$

$$(61)$$

Agora  $e_d$  e  $e_q$  são as tensões da rede,  $i_d$  e  $i_q$  são as correntes que passam pela impedância de entrada e  $v_d$  e  $v_q$  são as tensões geradas pelo conversor. Na equação (61) nota-se que a tensão  $e_d$  e  $e_q$  estão acopladas pelos termos  $-\omega Li_q$  e  $+\omega Li_d$  respectivamente. Esse acoplamento torna as tensões dependentes um da outra [15].

Segundo [26] a potências de um sistema balanceado trifásico podem ser escritas com;

$$P = e_a i_a + e_b i_b + e_c i_c. (62)$$

$$Q = j \frac{1}{\sqrt{3}} (e_{bc} i_a + e_{ca} i_b + e_{ab} i_c).$$

(63)

No sistema de coordenadas  $\alpha\beta$ ;

$$P_r = e_{\alpha} i_{\alpha +} e_{\beta} i_{\beta}. \tag{64}$$

$$Q_r = e_\beta i_\alpha - e_\alpha i_\beta. \tag{65}$$

No sistema de coordenadas dq, [15] apresentam as seguintes equações;

$$P = e_d i_d + e_q i_q. (66)$$

$$Q = j(e_a i_d - e_d i_a). \tag{67}$$

Levando em conta a equação (46) a potência aparente em dq fica;

$$S = \frac{3}{2} (e_d i_d - j e_d i_q). \tag{68}$$

Como referido anteriormente  $e_d$  = E, assim a potência ativa e reativa no sistema de coordenadas dq é escrita como;

$$\begin{cases} P = \frac{3}{2}Ei_d; \\ Q = -j\frac{3}{2}Ei_q. \end{cases}$$

$$(69)$$

Analisando a equação (69) é possível verificar que as potências, ativa e reativa agora estão desacopladas, o que torna possível fazer o controle de cada uma separadamente. Segundo a equação (69) igualando a corrente  $i_q$  a zero não haverá transferência de potência reativa, então o fator de potência será unitário [15], essa informação será importante para o controle do fator de potência. A potência vista pelo lado CA do conversor é dada por;

$$S_c = \frac{3}{2} (v_d i_d + v_q i_q + j(v_q i_d - v_d i_q)). \tag{70}$$

$$\begin{cases} P_c = \frac{3}{2} (v_d i_d + v_q i_q); \\ Q_c = j \frac{3}{2} (v_q i_d - v_d i_q). \end{cases}$$

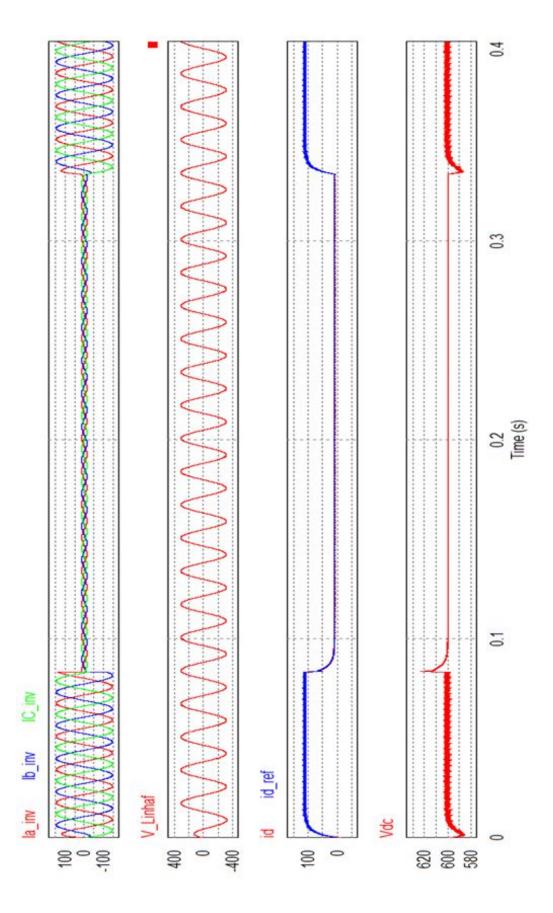

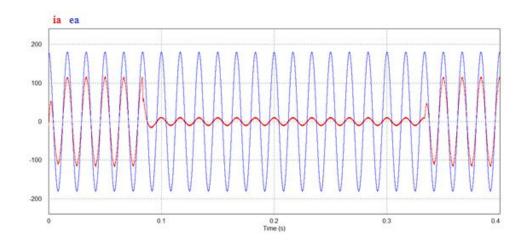

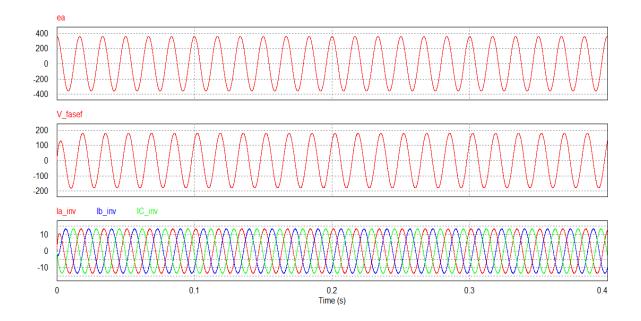

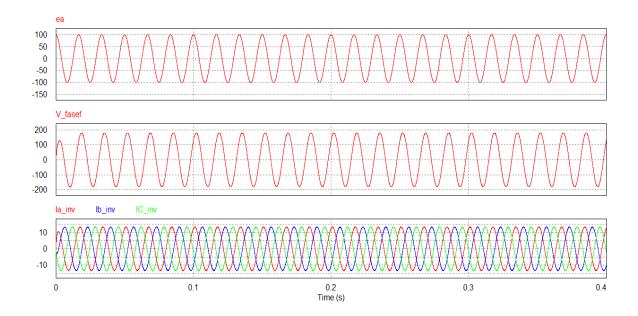

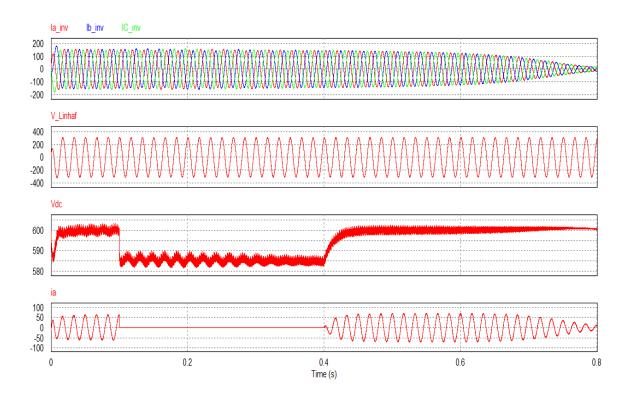

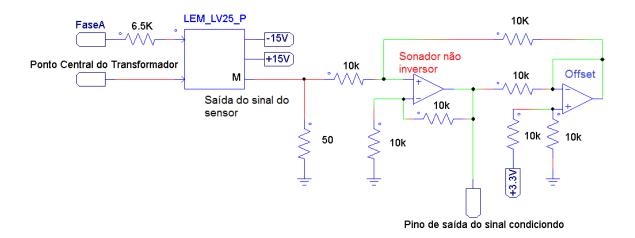

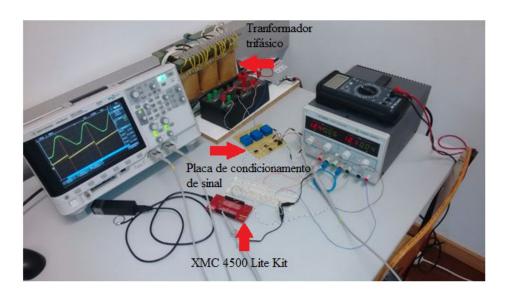

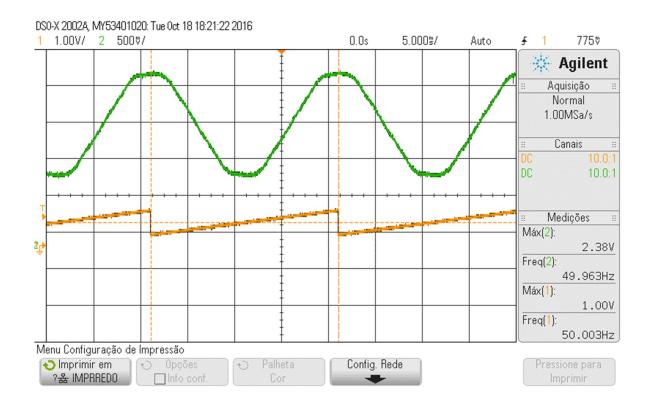

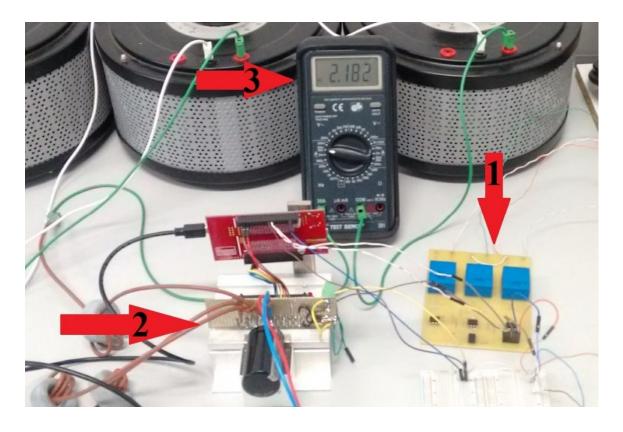

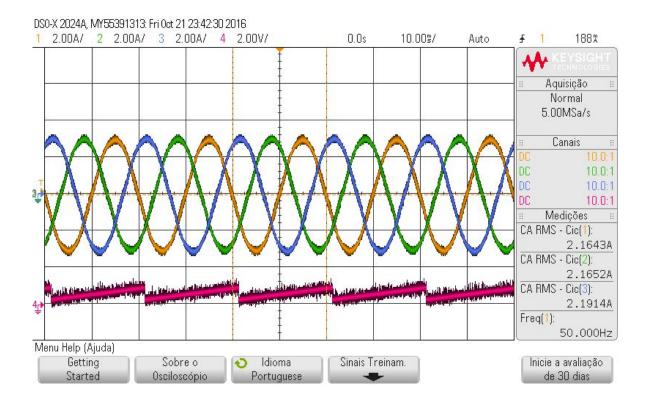

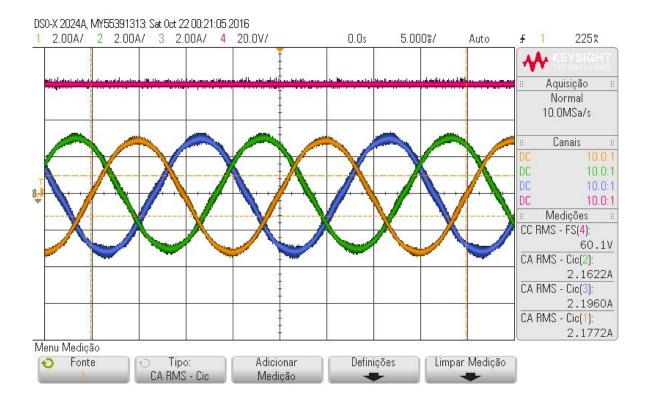

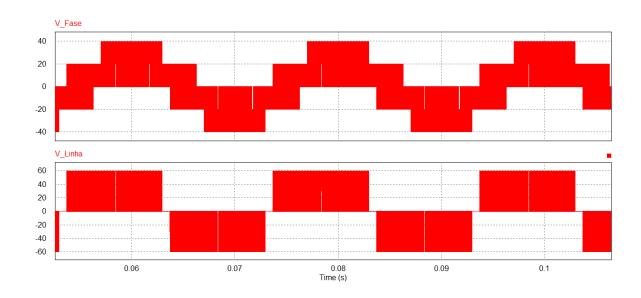

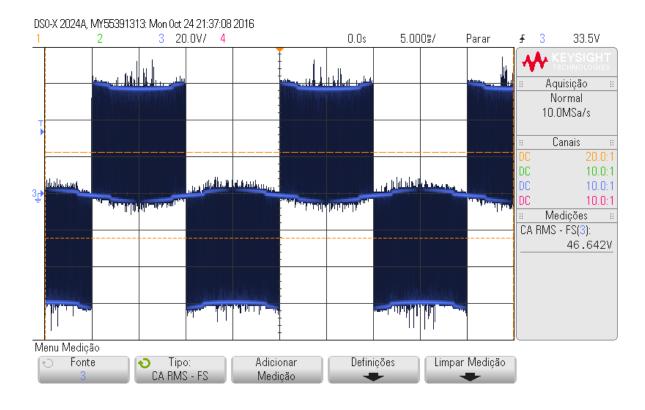

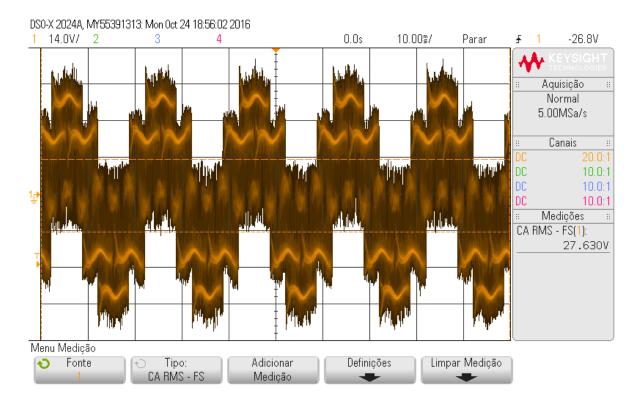

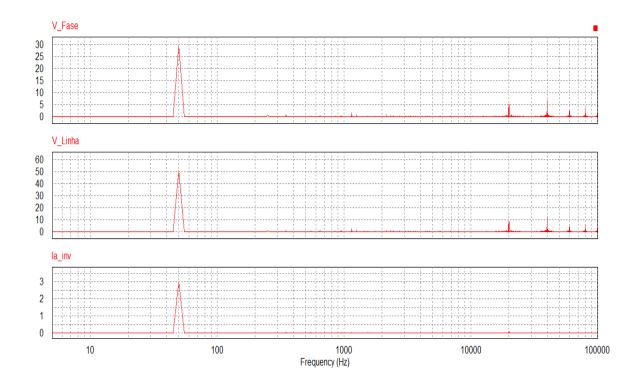

(71)