# ABSTRACT

| Title of Dissertation: | MODELING AND SOFTWARE SYNTHESIS<br>FOR MULTIPROCESSOR IMPLEMENTATION<br>OF WIRELESS COMMUNICATION SYSTEMS |

|------------------------|-----------------------------------------------------------------------------------------------------------|

|                        | Shuoxin Lin, Doctor of Philosophy, 2016                                                                   |

| Directed by:           | Professor Shuvra Bhattacharyya<br>Department of Electrical and Computer Engineering                       |

In recent years, the complexity of designing embedded signal processing systems for wireless communications has increased significantly based on the need to support increasing levels of operational flexibility and adaptivity, while also supporting increasing data rates and bandwidths. These trends pose important design and implementation challenges to meet the required demands on communication system performance, real-time operation, energy efficiency, and reconfigurability.

Dataflow models of computation provide a useful framework that can be built upon to address these challenges. Dataflow models provide high-level abstractions for specifying, analyzing and implementing a wide range of embedded signal processing applications. They allow designers to specify an application using high-level, platform-independent representations, and synthesize optimized embedded software that is targeted to specific types of hardware resources and design constraints.

The growing complexity of wireless communication systems, as motivated above, along with the complexity of system-on-chip platforms for embedded signal processing result in new problems that must be addressed in developing effective dataflow-based design methodologies. First, significant improvements to dataflowbased models and methods are needed to effectively utilize heterogeneous computing platforms and multiple forms of parallelism under stringent constraints on realtime performance and energy consumption. Second, effective modeling and analysis methods for handling dynamic parameters within dataflow graph components are needed for reliable and efficient management of system-level adaptivity and reconfiguration.

In this thesis, we address these problems by developing an integrated framework that exploits pipeline, data and task-level parallelism in dataflow models under memory constraints, and proposing novel dataflow modeling concepts and performance optimization techniques for design and implementation of dynamically parameterized communication systems. The main contributions of the thesis are summarized as follows:

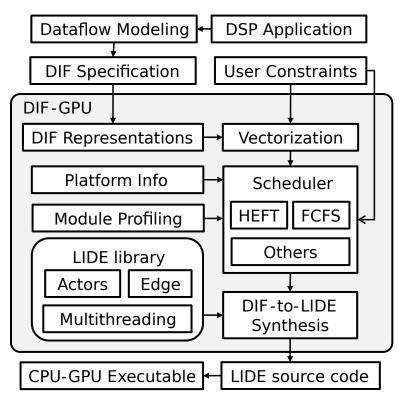

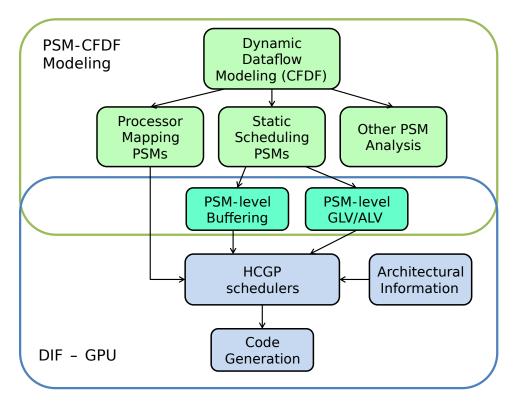

(1) Software synthesis framework for heterogeneous signal processing platforms. We have developed an integrated dataflow-based design framework called *DIF-GPU*, which provides a toolset for specification, optimization and software synthesis of embedded software targeted to heterogeneous CPU-GPU platforms. DIF-GPU incorporates novel models and methods in the dataflow interchange format (DIF) that are geared toward design optimization of signal processing systems on heterogeneous architectures composed of multicore CPUs and GPUs. DIF-GPU helps to free developers from low-level, platform-specific fine-tuning, and allows them to focus on higher-level aspects of communication system design. (2) Vectorization in DIF-GPU. In the context of dataflow models for embedded signal processing, vectorization is an important transformation for exploiting data parallelism. We have developed new techniques for integrated dataflow graph vectorization and scheduling on heterogeneous platforms. These techniques are developed in the DIF-GPU framework to provide optimized vectorization and scheduling capabilities for hybrid CPU-GPU platforms under memory constraints. For the targeted class of platforms, these techniques are shown to provide significantly better processing throughput compared to previous methods for a given memory constraint. We demonstrate our integrated vectorization and scheduling techniques by applying them to an Orthogonal Frequency Division Multiplexing (OFDM) receiver system.

(3) Modeling parameterized, dynamic dataflow behavior. We introduce a novel modeling method, called *parameterized sets of modes* (*PSMs*), that enables efficient representation and analysis of adaptive and dynamically reconfigurable signal processing functionality. PSMs can be viewed as high-level abstractions that model parameterized functionality involving groups of related regimes of operation ("modes") for dynamic dataflow models. We develop formal foundations for PSM-based modeling, and demonstrate the utility of this form of modeling by using it to develop efficient methods for scheduling dynamically parameterized dataflow graphs on different types of relevant platforms.

# Modeling and Software Synthesis for Multiprocessor Implementation of Wireless Communication Systems

by

# Shuoxin Lin

# Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2016

Advisory Committee: Professor Shuvra S. Bhattacharyya, Chair/Advisor Professor Manoj Franklin Professor William Levine Professor Ankur Srivastava Professor Yang Tao, Dean's Representative © Copyright by Shuoxin Lin 2016 Dedication

To my wife, son and parents

#### Acknowledgments

I sincerely thank Prof. Shuvra Bhattacharyya for his invaluable support, guidance and encouragement throughout the years of my PhD study. His continuous support from all aspects of my work and life has allowed me to complete this study, and overcome difficulties of all kinds. His generous and insightful guidance is indispensable for my successful completion of my study. I am truly grateful to have him as my advisor.

I also want to thank my committee members, Professor Levine, Professor Franklin, Professor Srivastava and Professor Tao for providing insightful and valuable feedbacks.

I am grateful to Dr. William Plishker, Dr. Chung-Ching Shen, Dr. Lai-huei Wang, Dr. George Zaki, Ms. Yanzhou Liu, and other colleagues and collaborators for their generous help. I would also like to thank Marshall Plan Foundation and Fachhochschule Salzburg for providing a great opportunity for collaborative research.

Finally I give my special thanks to my wonderful parents, my wife and my son for their love and understanding.

The research underlying this thesis was supported in part by the Laboratory for Telecommunication Sciences, U.S. National Science Foundation, and Tekes — The Finnish Funding Agency For Innovation.

# Table of Contents

| List of Figures vi |                                        |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                             |

|--------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1                  | Intro<br>1.1<br>1.2                    | oduction         Contributions         1.1.1       Design Framework for Heterogeneous Platforms         1.1.2       Memory-Constrained Vectorization and Scheduling         1.1.3       Modeling Parameterized Dynamic Dataflow         Outline of Thesis                                                                                                                                             | $     \begin{array}{c}       1 \\       4 \\       5 \\       7 \\       8 \\       10     \end{array} $                    |

| 2                  | Bacl<br>2.1<br>2.2<br>2.3              | kground<br>Synchronous Dataflow                                                                                                                                                                                                                                                                                                                                                                       | 12<br>12<br>13<br>15                                                                                                        |

| 3                  | DIF<br>3.1<br>3.2<br>3.3<br>3.4        | -GPU Design FrameworkIntroductionRelated WorkDIF-GPU Framework3.3.1 Dataflow Graph Specification3.3.2 Implementation of Actors and Edges3.3.3 Vectorization3.3.4 Scheduling3.3.5 Managing Interprocessor Data Transfers3.3.6 Runtime3.3.7 Code GenerationSteperiments3.4.1 Benchmarks3.4.2 Evaluation of Actor Performance and Data Transfer Cost3.4.3 System-Level Evaluation3.4.4 SchedulingSummary | $\begin{array}{c} 17 \\ 18 \\ 19 \\ 22 \\ 25 \\ 26 \\ 29 \\ 31 \\ 33 \\ 34 \\ 35 \\ 37 \\ 39 \\ 41 \\ 48 \\ 49 \end{array}$ |

| 4                  | Men<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | nory-Constrained Vectorization and SchedulingIntroductionRelated WorkBackgroundOperationBackgroundProblem FormulationVectorization and Scheduling with Memory Constraints4.5.1Incremental Actor Vectorization4.5.2N-Candidates IAV4.5.3Mapping-Based Devectorization4.5.4Mapping Actors onto HCGPs4.5.5Throughput Estimation                                                                          | 51<br>53<br>56<br>59<br>67<br>67<br>72<br>75<br>78<br>79                                                                    |

|    |        | 4.5.6 Summary                                                | 80  |

|----|--------|--------------------------------------------------------------|-----|

|    | 4.6    | Experiments using Synthetic Graphs                           | 81  |

|    |        | 4.6.1 Experimental Setup                                     |     |

|    |        | 4.6.2 Synthetic Graph Generation                             |     |

|    |        | 4.6.3 IAR Scheduling                                         |     |

|    |        | 4.6.4 Vectorization                                          | 87  |

|    |        | 4.6.5 Runtime                                                |     |

|    | 4.7    | Case Study: OFDM                                             |     |

|    |        | 4.7.1 System Implementation and Profiling                    |     |

|    |        | 4.7.2 Software Synthesis with GLV-HEFT                       |     |

|    |        | 4.7.3 Software Synthesis with ALV-IAR                        |     |

|    | 4.8    | Summary                                                      |     |

| 5  | Para   | ameterized Sets of Modes                                     | 106 |

|    | 5.1    | Introduction                                                 | 106 |

|    | 5.2    | Related Work                                                 | 109 |

|    | 5.3    | Formulation of PSMs                                          |     |

|    |        | 5.3.1 Notation                                               |     |

|    |        | 5.3.2 Motivation for Parameterized Sets of Modes             |     |

|    |        | 5.3.3 Formal Definition of PSM-CFDF                          |     |

|    |        | 5.3.4 PSM Transition Graph                                   |     |

|    |        | 5.3.5 Implementation Considerations                          |     |

|    |        | 5.3.6 Application Example                                    |     |

|    |        | 5.3.7 Summary                                                |     |

|    | 5.4    | PSM-level Static Scheduling for CFDF Graphs                  |     |

|    |        | 5.4.1 Statically Schedulable Regions                         |     |

|    |        | 5.4.2 PSM-level Static Scheduling                            |     |

|    |        | 5.4.3 Construction of SDF Scheduling PSMs                    |     |

|    |        | 5.4.4 Synthetic Example                                      |     |

|    |        | 5.4.5 Application Example                                    |     |

|    |        | 5.4.6 Summary of PSM-level Static Scheduling                 |     |

|    | 5.5    | PSM-level Processor Selection for Heterogeneous Platforms    |     |

|    |        | 5.5.1 Overview                                               |     |

|    |        | 5.5.2 PSM-level Processor Selection                          |     |

|    |        | 5.5.3 Profile-based Selection                                |     |

|    |        | 5.5.4 OFDM Demodulation                                      |     |

|    |        | 5.5.5 Application of PAPPS to the OFDM Demodulation System . |     |

|    |        | 5.5.6 Experimental Results                                   |     |

|    | 5.6    | Summary                                                      |     |

| 6  | Con    | clusions and Future Work                                     | 148 |

|    | 6.1    | Conclusions                                                  | 148 |

|    | 6.2    | Future Work                                                  |     |

| Bi | bliogr | caphy                                                        | 154 |

# List of Figures

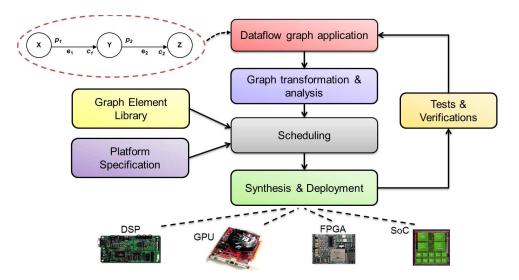

| 1.1<br>1.2 | Overview of dataflow-based design framework                                                                                                                        | 2<br>3 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

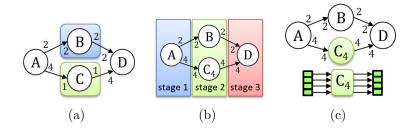

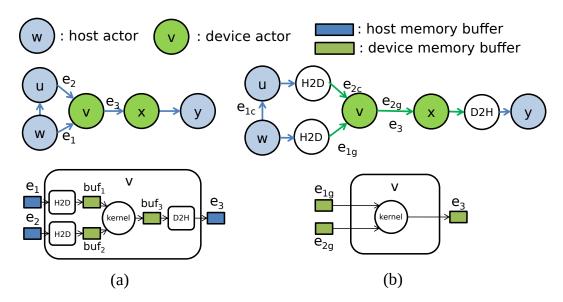

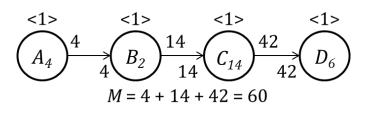

| 3.1        | An example dataflow application graph. (a) Original SDF graph. (b)<br>Vectorized SDF graph $\nu_b(G)$ . (c) $\nu_b(G)$ after insertion of data transfer<br>actors. | 20     |

| 2.0        |                                                                                                                                                                    | 20     |

| 3.2        |                                                                                                                                                                    | 23     |

| 3.3        |                                                                                                                                                                    | 24     |

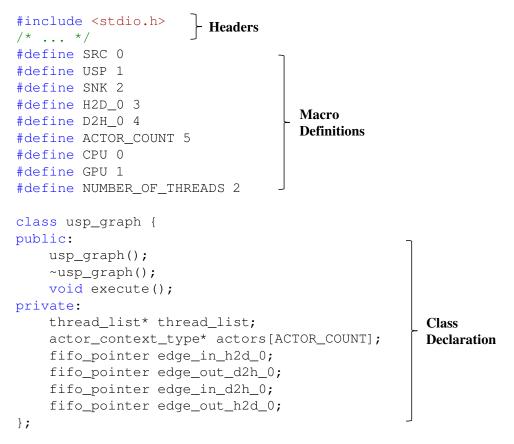

| 3.4        | Dataflow Structure and interface method declarations of LIDE-CUDA                                                                                                  | 07     |

| 0 5        |                                                                                                                                                                    | 27     |

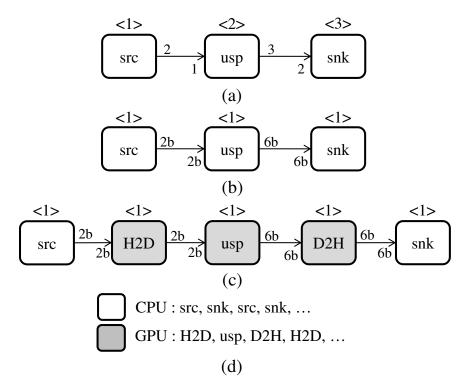

| 3.5        | Illustration of methods for handling CPU-GPU data transfers in dataflow                                                                                            |        |

|            | schedules. (a) Host-centered FIFO allocation. (b) Mapping-dependent                                                                                                |        |

|            |                                                                                                                                                                    | 31     |

| 3.6        | Generated header file code for the example of Figure $3.1(a)$                                                                                                      | 35     |

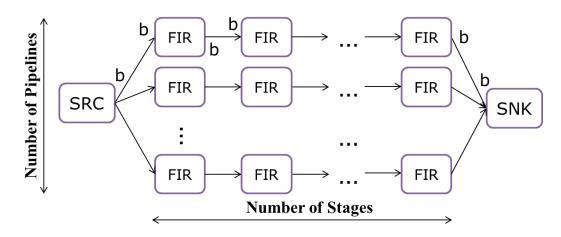

| 3.7        |                                                                                                                                                                    | 36     |

| 3.8        |                                                                                                                                                                    | 37     |

| 3.9        |                                                                                                                                                                    | 40     |

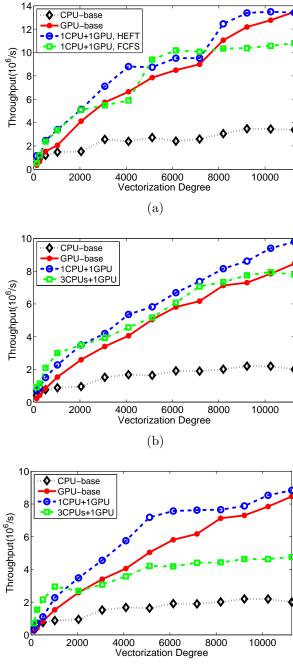

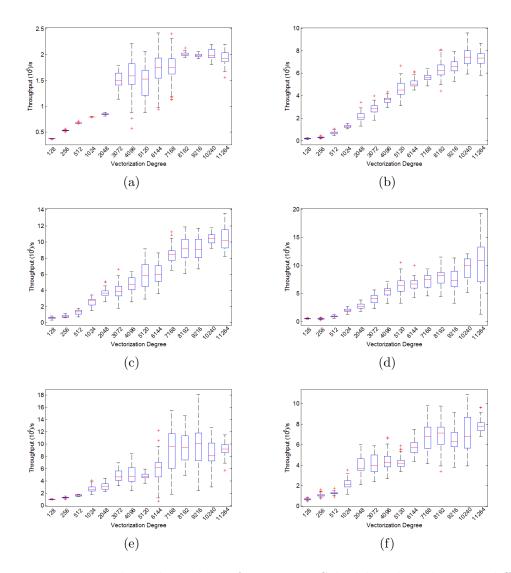

| 3.10       | Throughput of $M \times N$ MP-Sched benchmarks for different platform                                                                                              |        |

|            | configurations and schedulers. (a) $2x5$ with FCFS and HEFT; (b)                                                                                                   |        |

|            | 4x4 with HEFT; (c) $4x4$ with FCFS; (d) $6x3$ with HEFT; (e) $6x3$                                                                                                 |        |

|            |                                                                                                                                                                    | 44     |

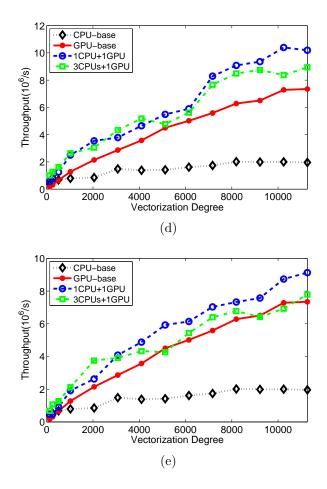

| 3.11       | Throughput box plots of $2 \times 5$ MP-Sched benchmarks with different                                                                                            |        |

|            | platform configurations and schedulers: (a) CPU-base; (b) GPU-base;                                                                                                |        |

|            | (c) $1 \text{ CPU} + 1 \text{ GPU}$ , HEFT scheduler; (d) $1 \text{ CPU} + 1 \text{ GPU}$ , FCFS                                                                   |        |

|            | scheduler                                                                                                                                                          | 45     |

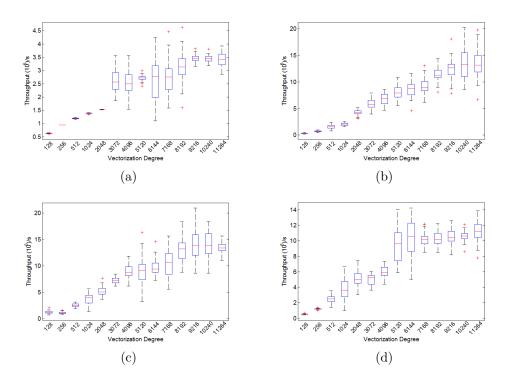

| 3.12       | Throughput box plots of $4 \times 4$ MP-Sched benchmarks with different                                                                                            |        |

|            | platform configurations and schedulers: (a) CPU-base; (b) GPU-base;                                                                                                |        |

|            | (c) $1 \text{ CPU core} + 1 \text{ GPU}$ , HEFT scheduler; (d) $1 \text{ CPU core} + 1 \text{ GPU}$ ,                                                              |        |

|            | FCFS scheduler; (e) 3 CPU cores + 1 GPU, HEFT scheduler; (e) 3                                                                                                     |        |

|            | CPU cores $+ 1$ GPU, FCFS scheduler                                                                                                                                | 46     |

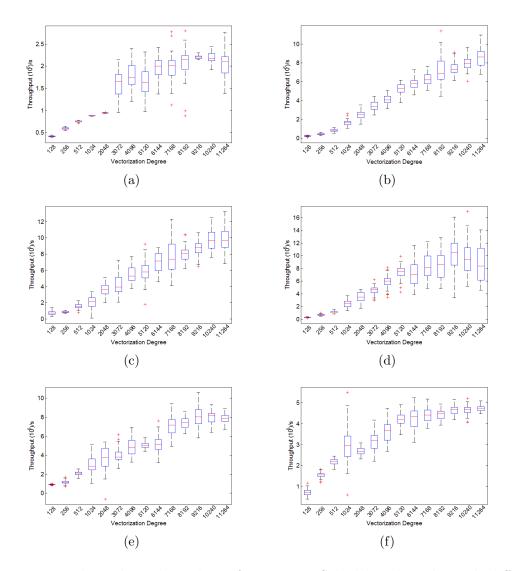

| 3.13       | Throughput box plots of $6 \times 3$ MP-Sched benchmarks with different                                                                                            |        |

|            | platform configurations and schedulers: (a) CPU-base; (b) GPU-base;                                                                                                |        |

|            | (c) $1 \text{ CPU core} + 1 \text{ GPU}$ , HEFT scheduler; (d) $1 \text{ CPU core} + 1 \text{ GPU}$ ,                                                              |        |

|            | FCFS scheduler; (e) 3 CPU cores + 1 GPU, HEFT scheduler; (e) 3                                                                                                     |        |

|            | CPU cores + 1 GPU, FCFS scheduler.                                                                                                                                 | 47     |

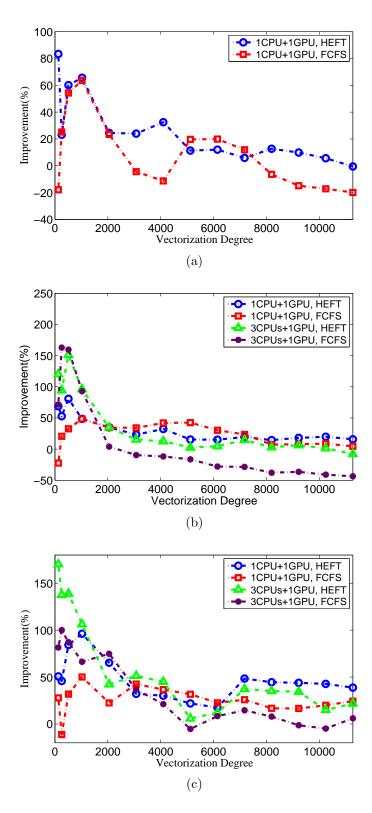

| 3.14       | Speedup of MP-Sched benchmarks using the HEFT and FCFS sched-                                                                                                      |        |

|            |                                                                                                                                                                    | 50     |

|            |                                                                                                                                                                    |        |

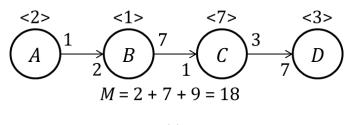

| 4.1        | Example of vectorization and minimum buffer requirements. (a) Orig-                                                                                                |        |

|            | inal graph. (b) Vectorization of $A$ by 2. (c) Vectorization of all actors                                                                                         |        |

|            | by 2. (d) Vectorization of $B$ by 2                                                                                                                                | 62     |

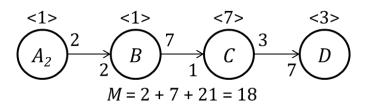

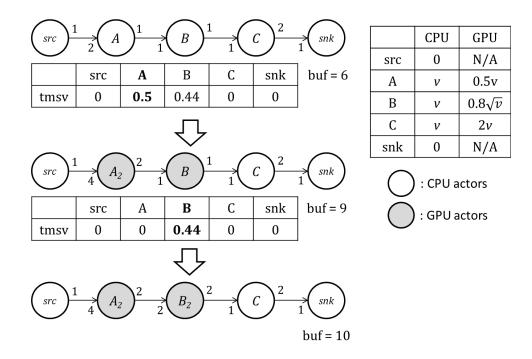

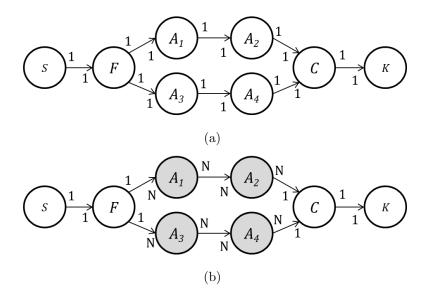

| 4.2<br>4.3 | A simple example to illustrate $\Sigma$ -IAV using the TMSV score function.<br>An example that illustrates the utility of devectorization. (a) The original graph. (b) The graph with GVD = $N$ and devectorization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

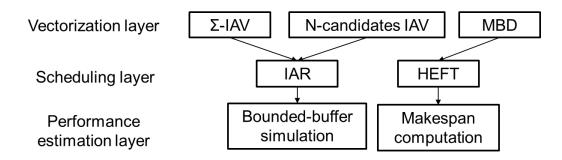

| 4.4        | applied to all CPU-mapped actors $-C, F, K, S. \ldots \ldots \ldots$<br>Layered structure of vectorization, scheduling, and performance esti-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76               |

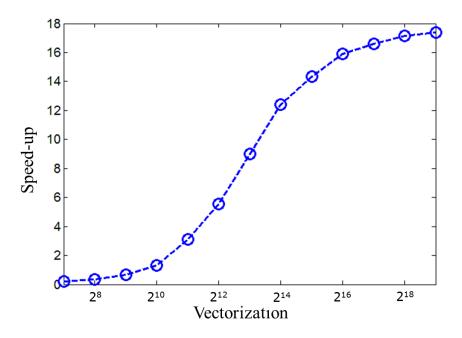

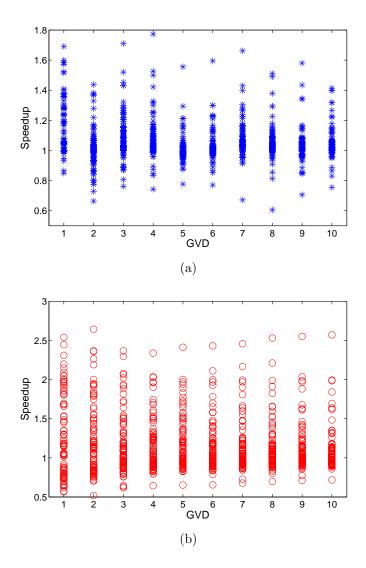

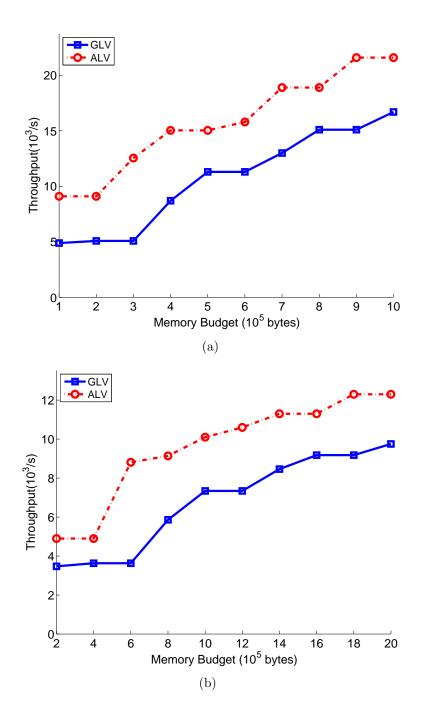

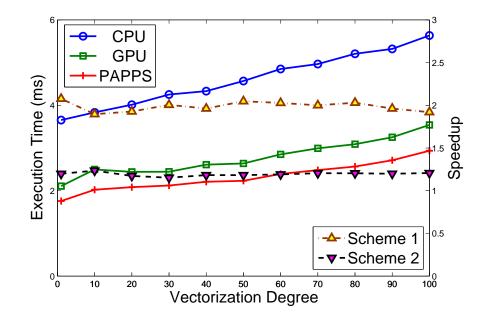

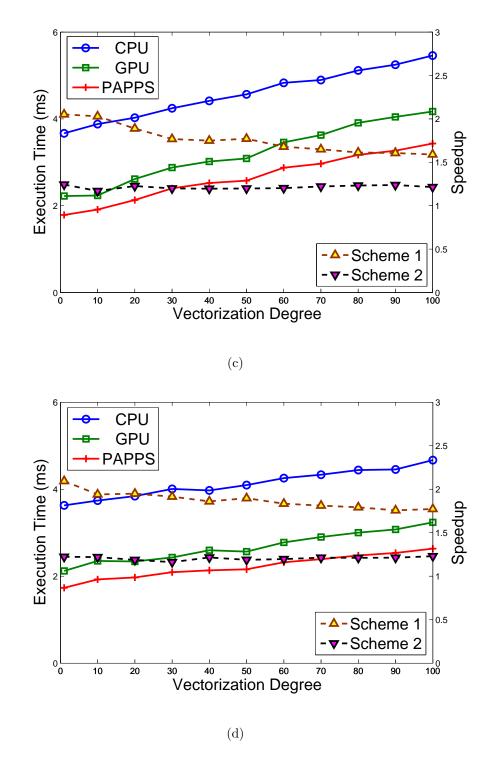

| 4.5        | mation in the proposed design optimization framework Simulated speedup compared between the vectorized schedules generated by GLV-IAR and GLV-HEFT. Two target platform configurations are considered in this evaluation: (a) 1 CPU core + 1 GPU, and (b) 3 CPU cores + 1 GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81               |

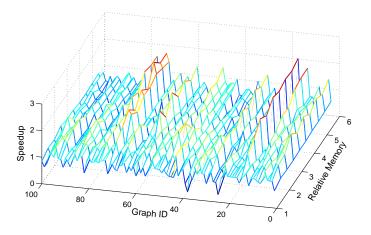

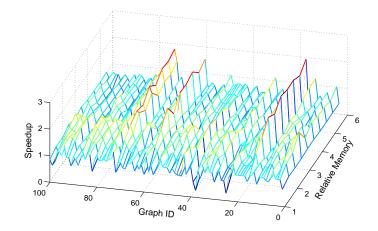

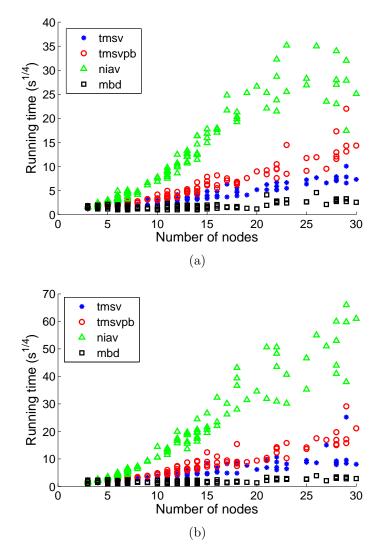

| 4.6        | Speedups measured for four different ALV techniques that were in-<br>troduced in Section 4.5: (a) TMSV $\Sigma$ -IAV, (b) TMSVPB $\Sigma$ -IAV, (c)<br>N-candidate IAV, and (d) MBD. The target platform configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86               |

| 4.7        | consists of 1 CPU core and 1 GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89               |

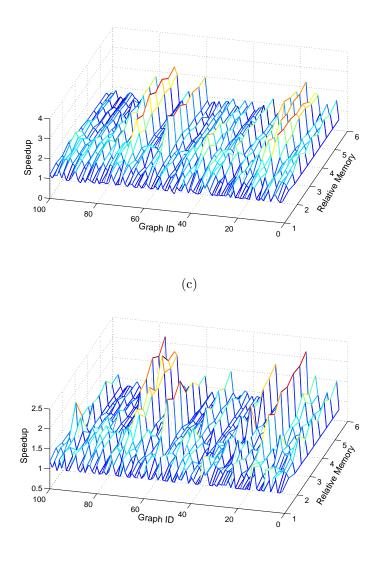

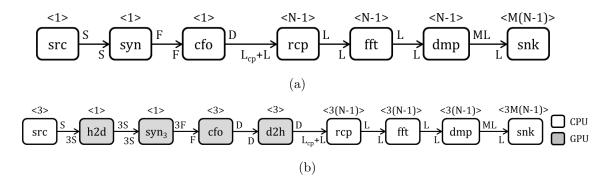

| 4.8        | $M = 2M_0$ , and (b) $M = 4M_0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92               |

|            | The transformed graph that results from vectorization of $syn$ by a factor of 3, and insertion of the actors $h2d$ and $d2h$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 94               |

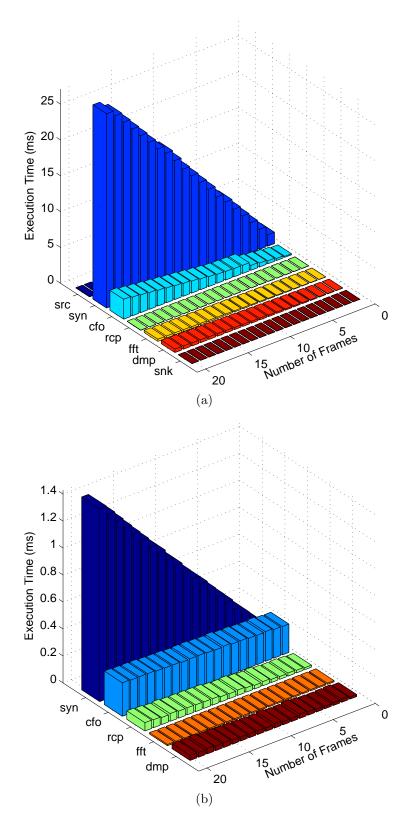

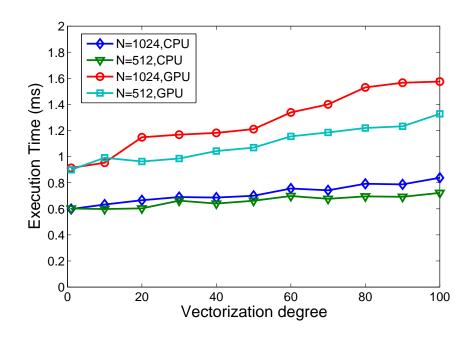

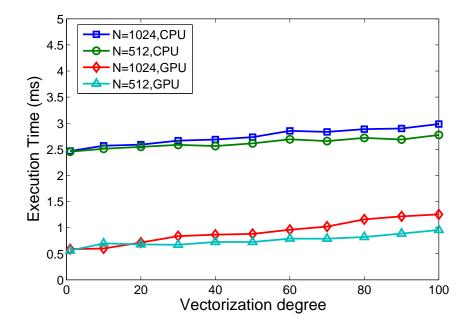

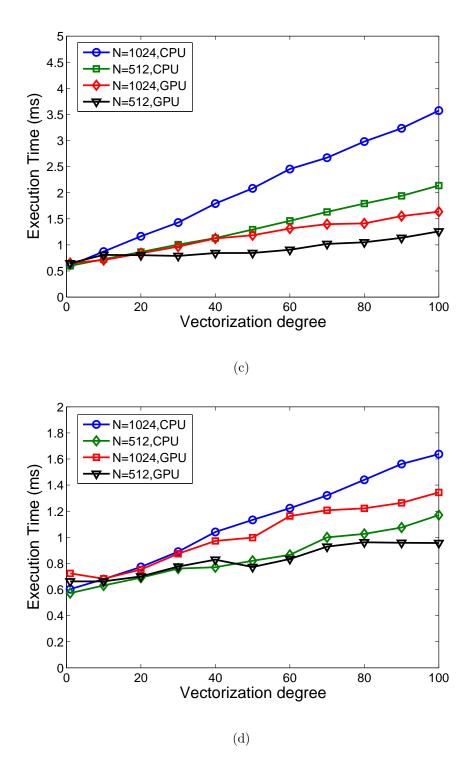

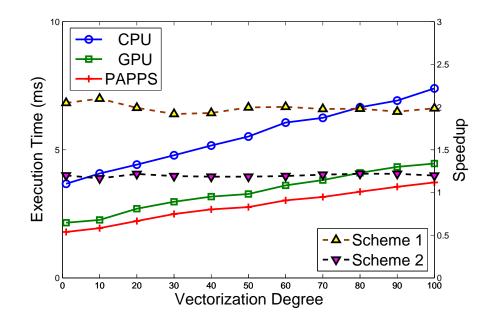

| 4.9        | ATSIs on the CPU and GPU when actors are vectorized to process<br>multiple frames in each firing. (a) CPU. (b) GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 97               |

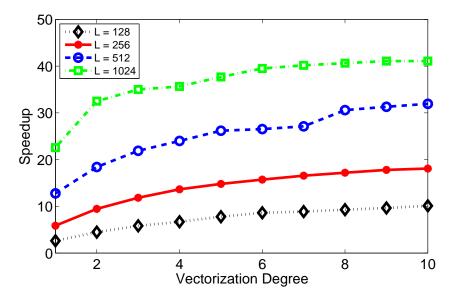

| 4.10       | Speedup of the OFDM-RX application over a single CPU implemen-<br>tation for different GVD values and different values of the bandwidth<br>parameter $I$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00               |

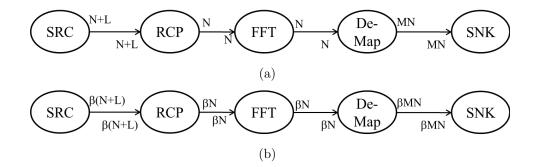

| 4.11       | parameter $L$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99<br>103        |

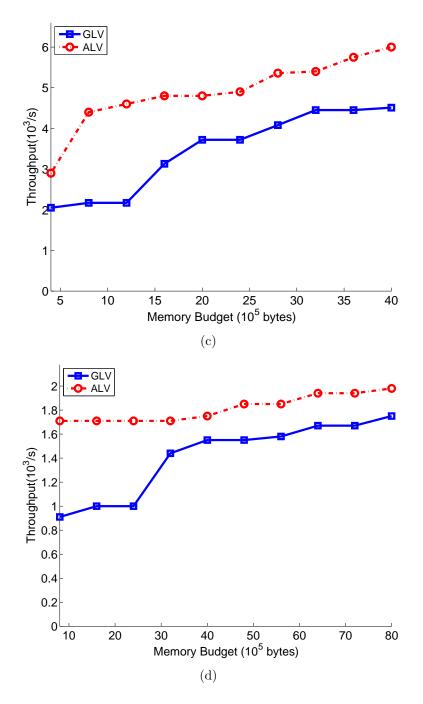

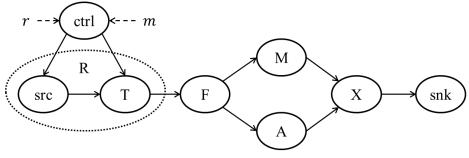

| 5.1        | An example of a PSM-CFDF actor: OFDM demapper example. (a)<br>Actor interface. (b) PSM transition graph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 118              |

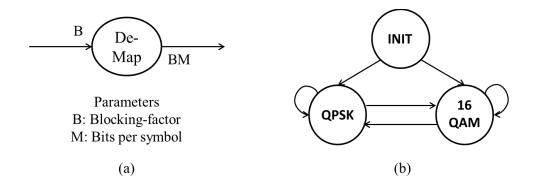

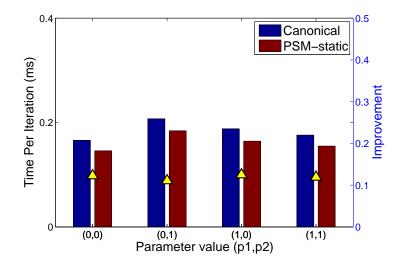

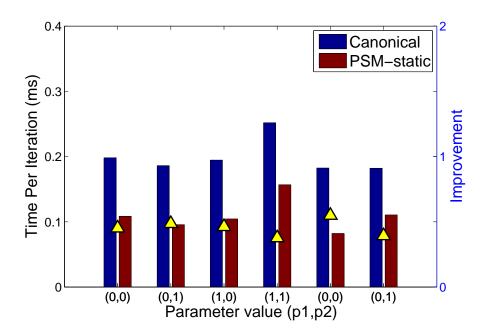

| 5.2        | A synthetic CFDF graph that is used to illustrate PSM-level static                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| 5.3        | scheduling concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |