## University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2014

## Thermal Analysis, Parasitic Extraction, and Wirebond Reliability Studies of Power Electronic Modules

Shilpa Prabhudeva University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd Part of the <u>Power and Energy Commons</u>

**Recommended** Citation

Prabhudeva, Shilpa, "Thermal Analysis, Parasitic Extraction, and Wirebond Reliability Studies of Power Electronic Modules" (2014). *Theses and Dissertations*. 2096. http://scholarworks.uark.edu/etd/2096

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

Thermal Analysis, Parasitic Extraction, and Wirebond Reliability Studies of

Power Electronic Modules

# Thermal Analysis, Parasitic Extraction, and Wirebond Reliability Studies of Power Electronic Modules.

A thesis submitted in partial fulfillment of the requirements of the degree of Master of Science in Electrical Engineering

By

Shilpa Prabhudeva Visveswaraya Technological University Bachelor of Engineering, 2011

> December 2014 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

Dr. Simon S. Ang Thesis Director

Dr. Juan C. Balda Committee Member Dr. Roy A. McCann Committee Member

#### ABSTRACT

This investigates thermal performance, parasitic thesis research extraction and wirebond/encapsulation reliability of power electronic modules. Thermal performance is critical to the power electronic modules. As such, thermal analysis is an important part of the power electronic module design process. Several cases are studied on generalized power modules with a full bridge layout. A database is built based on these results. The studies are performed using SolidWorks thermal simulation tool. The database involves several parameters such as power dissipation, maximum junction temperature, ambient temperature, convection coefficient required to cool the module, size of the baseplate, heat-sink size, substrate size, spacing between dies, and different materials that can be used for the power electronic module. Using this database, procedures to select appropriate parameters in a thermally efficient layout for the power electronic modules are illustrated using examples. It was found that, for optimum performance,  $\Delta T$  (maximum junction temperature – ambient temperature) should be greater than 125°C for power modules with medium and high power dissipation. Also, for a low  $\Delta T$  and high power dissipation, baseplate acts more like a thermal resistance than a heat-spreader. Hence, it is ineffective to employ base-plates for these cases. Increasing substrate size to bring down maximum junction temperature is more effective in higher power dissipation cases than those for medium or low power dissipation.

Parasitic extraction for an electronic power module using a time domain reflectometry (TDR) method in the form of differential inductance waveforms was developed. These measured parasitic inductance and parasitic capacitance are compared with the parasitic parameters extracted using a Q3D extractor software. The accuracy of the measurement results from these two different approaches is studied in detail.

Reliability of wirebonds in the case of encapsulated and un-encapsulated power modules were investigated by subjecting them temperature cycling from -55°C to 250°C. It was found that the solder flux affected the reliability of the wirebonds. As such, it is recommended that the power connectors on the power substrate should be free of flux, as the residual solder flux can affect the nearby wirebonds in the power modules. As expected, the differences in the coefficients of thermal expansion between the power substrate bond wires and encapsulation affect the reliability of the wirebonds. Large diameter wirebonds tend to be stronger and can withstand the stress and strain created by the different material systems in the power electronic modules.

#### ACKNOWLEDGEMENTS

I would like to thank god for providing me an opportunity to study at the University of Arkansas. It was a lifetime dream come true to do Master's Degree in Electrical Engineering from this prestigious university.

I would like to thank my teachers, parents, friends and colleagues for their constant support and encouragement throughout my whole studies. I would especially like to thank Dr. Simon S. Ang for accepting me as his student, and providing me with valuable knowledge to achieve this degree and also for providing me with a graduate assistantship. Thanks to his support and encouragement, I was able to successfully complete my degree. I would also like to thank all my colleagues, who were also my friends, for their support and helping me in learning all the fabrication processes. Thank you Hao Zhang, Atanu Dutta, and Marwan Abu-Mahaimed. Also thanks to the HiDEC staff members, Mike Steger, Dr. Michael Glover, Errol Porter, Kaoru Porter, and Tom Cannon, for their support and guidance in using instruments and HiDEC facilities.

Also, a million thanks to my parents, sister, and brother-in-law for their unconditional support throughout my studies.

## TABLE OF CONTENTS

| CHAPT | ER 1. INTRODUCTION                                             | 1  |

|-------|----------------------------------------------------------------|----|

| 1.1   | Thermal Analysis                                               | 2  |

| 1.2   | Parasitic extraction of power modules                          |    |

| 1.3   | Reliability of wire bonds                                      |    |

| 1.3   | Chapter Organization                                           |    |

| CHAPT | ER 2. BACKGROUND CONCEPTS                                      |    |

| 2.1   | Heat transfer in power modules                                 |    |

| 2.2   | Encapsulation                                                  | 7  |

| 2.3   | Wirebonding                                                    | 9  |

| 2.3   | .1 Bond wire material                                          | 9  |

| 2.3   | .2 Wirebonders                                                 |    |

| 2.3   | .3 Failure mechanism                                           |    |

| CHAPT | ER 3. THERMAL ANALYSIS OF POWER MODULES                        |    |

| 3.1   | Introduction                                                   |    |

| 3.2   | Full bridge circuit                                            |    |

| 3.3   | Full bridge layout                                             |    |

| 3.4   | Parameter constraints applied on power module for simulations  |    |

| 3.5   | Material selection                                             |    |

| 3.5   | .1 Insulating material in DBC substrates                       |    |

| 3.5   | .2 Different heat-sink materials                               |    |

| 3.6   | Study on ambient temperature variations                        |    |

| 3.7   | Study on power dissipation (heat generated by dies) variations |    |

| 3.8   | Study on varying baseplate size                                |    |

| 3.9   | Study on varying heat-sink size                                |    |

| 3.10  | Study on varying substrate (DBC) size                          |    |

| 3.11  | Discussions on results                                         | 58 |

| 3.1   | 1.1 Application examples                                       |    |

| 3.12  | Summary                                                        |    |

| 3.1   | 2.1 Significance of the results                                |    |

| 3.12             | .2 Limitations                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| CHAPTE           | R 4. PARASITIC EXTRACTION OF A POWER MODULE                                                                                       |

| 4.1              | Introduction:                                                                                                                     |

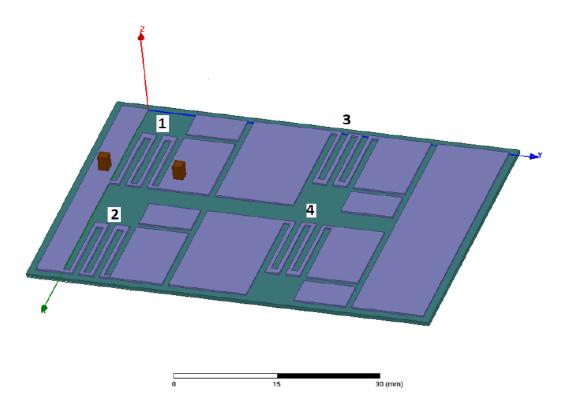

| 4.2              | Test vehicle description                                                                                                          |

| 4.2.1            | Test vehicle A                                                                                                                    |

| 4.2.2            | 2 Test vehicle B                                                                                                                  |

| 4.3              | Experimental setup for Time-domain-reflectometry70                                                                                |

| 4.4              | Initial verification for impedance measurements using TDR method:                                                                 |

| 4.5              | Results and discussions:                                                                                                          |

| 4.6              | Summary                                                                                                                           |

| 4.6.1            | Applications                                                                                                                      |

| 4.6.2            | 2 Limitations                                                                                                                     |

| CHAPTE<br>PARAMI | ER 5. INVESTIGATION OF WIREBOND RELIABILITY FOR VARIOUS                                                                           |

| 5.1              | Introduction                                                                                                                      |

| 5.1.1            | Materials used to fabricate                                                                                                       |

| 5.2              | Theoretical Stress calculations on wirebonds due to thermal cycling                                                               |

| 5.3              | Experimentation and Testing                                                                                                       |

| 5.3.1<br>conr    | Experimentation on un-encapsulated and encapsulated modules having power<br>nectors and solder paste without cleaning solder flux |

| 5.3.2<br>paste   | 2 Experimentation on encapsulated modules having power connectors and solder<br>e; steps were taken to clean solder flux          |

| 5.3.3<br>relia   | B Experimentation on un-encapsulated and encapsulated modules for wirebond bility                                                 |

| 5.4              | Discussions and conclusion                                                                                                        |

| CHAPTE           | R 6. CONCLUSION                                                                                                                   |

| 6.1              | Conclusions and discussions 105                                                                                                   |

| 6.2              | Future works                                                                                                                      |

| REFERE           | NCES:                                                                                                                             |

## LIST OF TABLES

| Table 3.1:    | Al2O3 and AlN material properties comparison                       | 25   |

|---------------|--------------------------------------------------------------------|------|

| Table 3.2:    | 1050A, 6061, 6063, Copper material properties comparison table     | 27   |

| Table 4.1:    | Comparison of results obtained from Q3D simulations and TDR method | 77   |

| Table 5.1:    | DBC substrate material properties                                  | 82   |

| Table 5.2:    | Solder paste material properties                                   | 83   |

| Table 5.3:    | Aluminum wire material properties                                  | 83   |

| Table 5.4(a): | Wirebonded trace/path connectivity test before thermal cycling     | .94  |

| Table 5.4(b): | Wirebonded trace/path connectivity test after thermal cycling      | 94   |

| Table 5.5:    | Wirebond pull strength                                             | 95   |

| Table 5.6:    | Wire-bonded trace/path connectivity test after thermal cycling     | .101 |

## LIST OF FIGURES

| Figure 2.1:    | Layers in power module                                                                                |

|----------------|-------------------------------------------------------------------------------------------------------|

| Figure 2.2:    | Air bubble in encapsulated power electronic module                                                    |

| Figure 2.3:    | Wedge wirebond11                                                                                      |

| Figure 2.4:    | Orthodyne ultrasonic wedge bonder11                                                                   |

| Figure 2.5:    | Failure modes of an integrated circuit12                                                              |

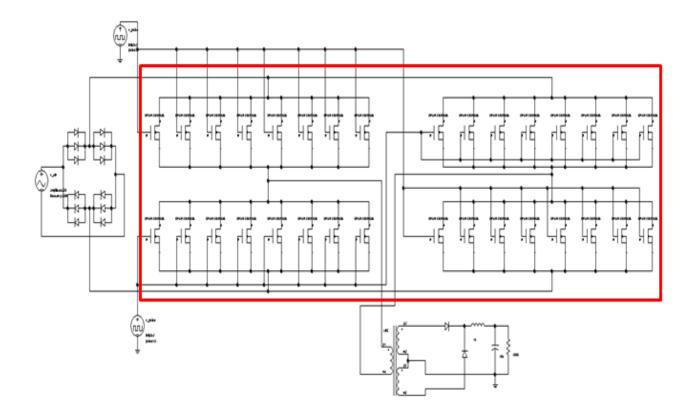

| Figure 3.1:    | Full bridge circuit15                                                                                 |

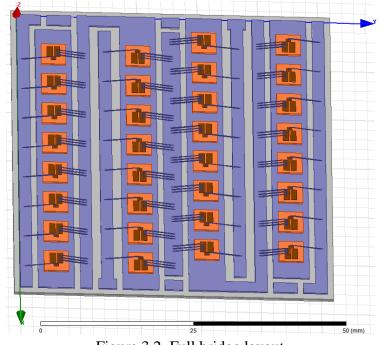

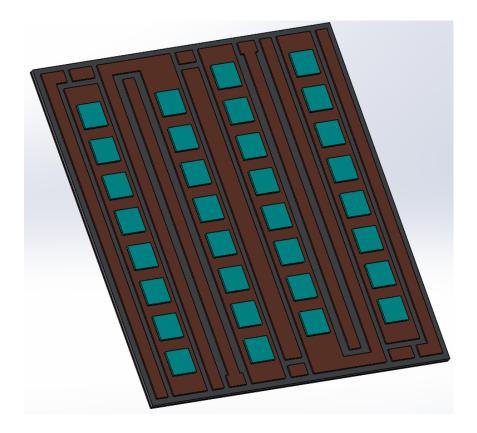

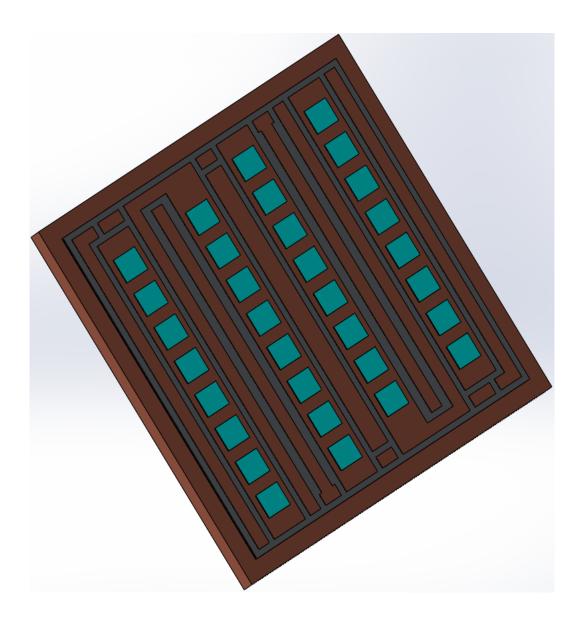

| Figure 3.2:    | Full bridge layout16                                                                                  |

| Figure 3.3:    | DBC substrate designed in SolidWorks18                                                                |

| Figure 3.4:    | DBC substrate with baseplate designed in SolidWorks19                                                 |

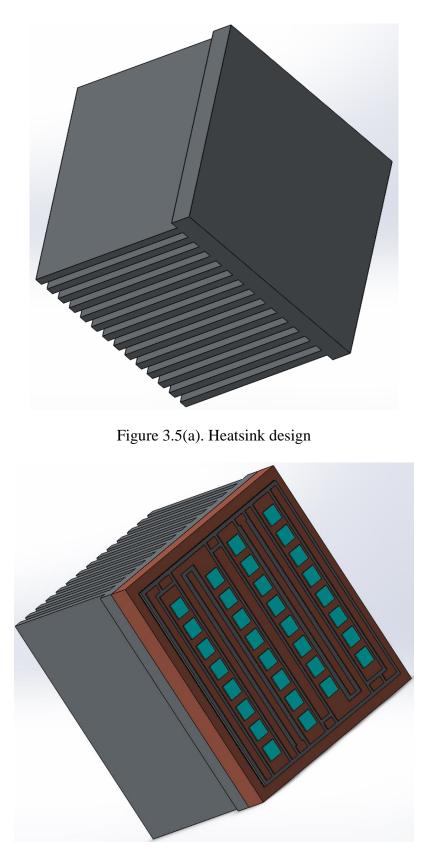

| Figure 3.5(a): | Heatsink design                                                                                       |

| Figure 3.5(b): | DBC substrate with baseplate and heatsink designed in SolidWorks20                                    |

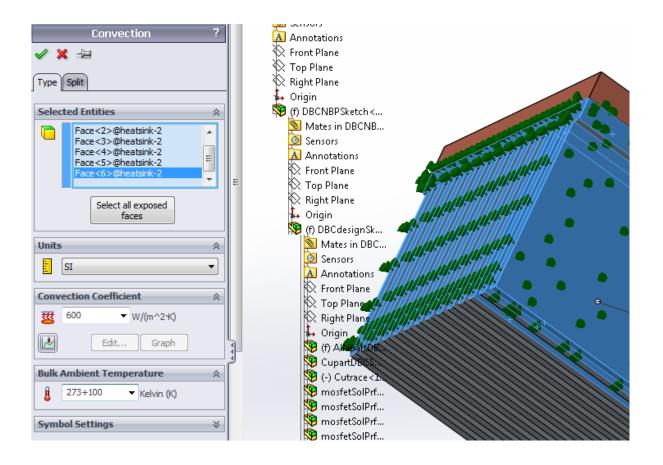

| Figure 3.6(a): | Assigning some of the parameters for simulations in SolidWorks21                                      |

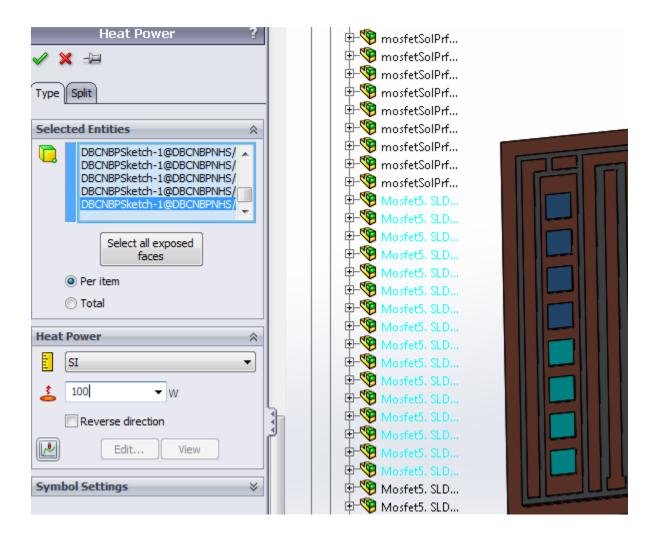

| Figure 3.6(b): | Assigning some of the parameters for simulations in SolidWorks22                                      |

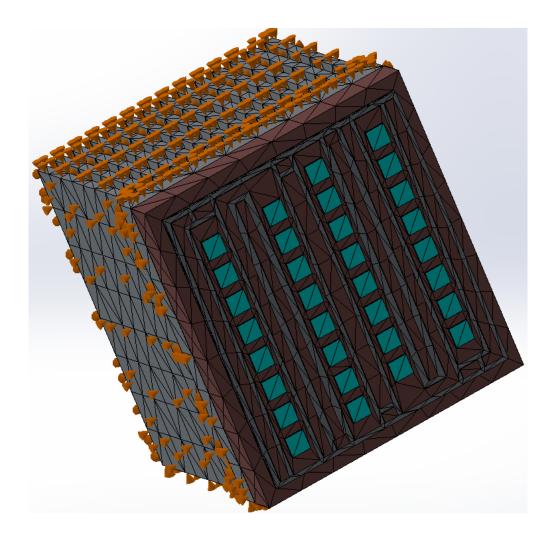

| Figure 3.6(c): | Meshed power module                                                                                   |

| Figure 3.6(d): | Simulated results                                                                                     |

| Figure 3.7:    | Convection coefficient versus maximum junction temperature for Al <sub>2</sub> O <sub>3</sub> and AlN |

|                | materials                                                                                             |

| Figure 3.8:    | Convection coefficient versus maximum junction temperature for four material.27                       |

| Figure 3.9:    | Convection coefficient required by each material to maintain a maximum junction                       |

|                | temperature of 250°C                                                                                  |

| Figure 3.10:   | Convection coefficient versus maximum junction temperature for different                              |

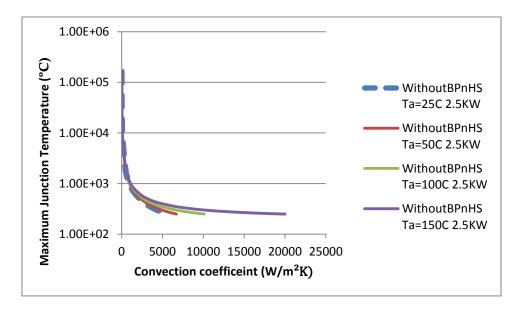

|                | ambient temperature and 2.5KW power dissipation (without BP or HS)29                                  |

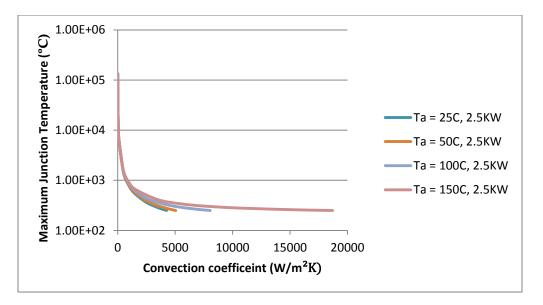

- Figure 3.11: Convection coefficient versus maximum junction temperature for different ambient temperatures and 2.5KW power dissipation (with BP and without HS).29

- Figure 3.13: Convection coefficient versus maximum junction temperature for different ambient temperatures and 1.6KW power dissipation (without BP or HS)......31

- Figure 3.14: Convection coefficient versus maximum junction temperature for different ambient temperatures and 1.6KW power dissipation (with BP and without HS).32

- Figure 3.15: Convection coefficient versus maximum junction temperature for different ambient temperatures and 1.6KW power dissipation (with BP and HS)......32

- Figure 3.16: Convection coefficient versus maximum junction temperature for different ambient temperatures and 4.0KW power dissipation (without BP or HS)......33

- Figure 3.17: Convection coefficient versus maximum junction temperature for different ambient temperatures and 4.0KW power dissipation (with BP and without HS).33

- Figure 3.18: Convection coefficient versus maximum junction temperature for different ambient temperatures and 4.0KW power dissipation (with BP and HS)......34

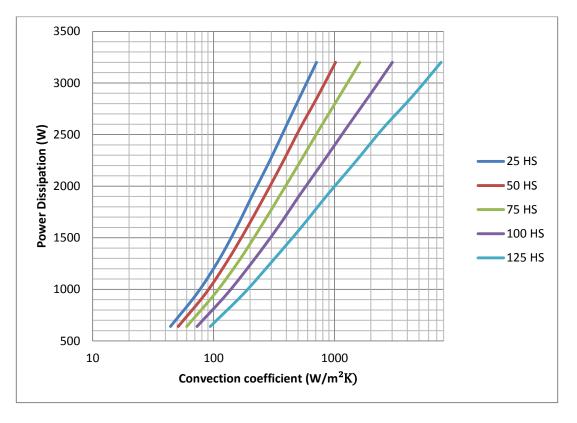

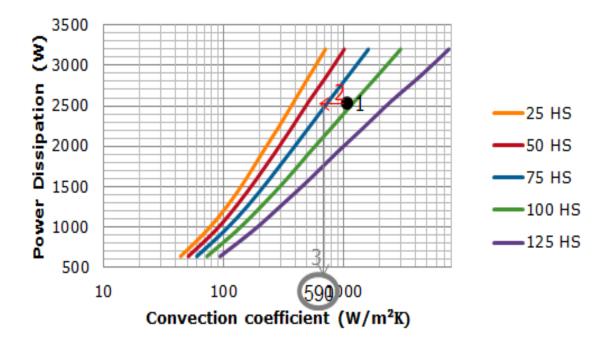

| Figure 3.22:   | Power dissipation versus convection coefficient for various ambient temperatures, |

|----------------|-----------------------------------------------------------------------------------|

|                | and Tj of 250°C (all three cases for comparison)                                  |

| Figure 3.23:   | Power dissipation versus convection coefficient for various ambient temperatures, |

|                | and Tj of 200°C (without BP or HS)                                                |

| Figure 3.24:   | Power dissipation versus convection coefficient for various ambient temperatures, |

|                | and Tj of 200°C (with BP and without HS)                                          |

| Figure 3.25:   | Power dissipation versus convection coefficient for various ambient temperatures, |

|                | and Tj of 200°C (with BP and HS)                                                  |

| Figure 3.26:   | Power dissipation versus convection coefficient for various ambient temperatures, |

|                | and Tj of 200°C (all three cases for comparison)                                  |

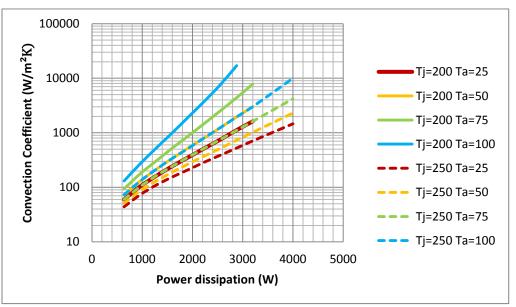

| Figure 3.27:   | Convection versus power dissipation for few cases40                               |

| Figure 3.28(a) | Convection versus power dissipation with different ambient temperatures41         |

| Figure 3.28(b) | Convection versus ambient temperatures for different power dissipations 41        |

| Figure 3.28(c) | Semi-logarithmic plot for power dissipation versus convection coefficient with    |

|                | different ambient temperatures (with HS)42                                        |

| Figure 3.29:   | Baseplate size versus power dissipation and convection coefficient for Ta of      |

|                | 100°C and Tj of 250°C43                                                           |

| Figure 3.30:   | Baseplate size versus power dissipation and convection coefficient for different  |

|                | Ta of 100°C, 125°C and Tj of 250°C44                                              |

| Figure 3.31:   | Convection coefficient versus maximum junction temperature for different          |

|                | baseplate sizes, and for 2.5KW power dissipation, Ta of 100°C44                   |

| Figure 3.32:   | Convection coefficient versus maximum junction temperature for different          |

|                | baseplate sizes, and for 1.6KW power dissipation Ta of 100°C45                    |

| Figure 3.33: | Convection coefficient versus maximum junction temperature for different         |

|--------------|----------------------------------------------------------------------------------|

|              | baseplate sizes, and for 2.5KW power dissipation, Ta of 125°C45                  |

| Figure 3.34: | Convection coefficient versus maximum junction temperature for different         |

|              | baseplate sizes, and for 1.6KW power dissipation Ta of 125°C46                   |

| Figure 3.35: | Baseplate size increase versus convection coefficient for 2.5KW and 1.6KW        |

|              | power dissipation, and 100°C and 125°C Ta47                                      |

| Figure 3.36: | Heat-sink size variation versus power dissipation and convection coefficient for |

|              | Ta of 100°C and Tj of 250°C48                                                    |

| Figure 3.37: | Heat-sink size variation versus power dissipation and convection coefficient for |

|              | Ta of 100°C, 125°C and Tj of 250°C48                                             |

| Figure 3.38: | Convection coefficient versus Tj for different heat-sink sizes, for 2.5KW power  |

|              | dissipation, Ta of 100°C49                                                       |

| Figure 3.39: | Convection coefficient versus Tj for different heat-sink sizes, for 1.6KW power  |

|              | dissipation, Ta of 100°C49                                                       |

| Figure 3.40: | Convection coefficient versus Tj for different heat-sink sizes, for 2.5KW power  |

|              | dissipation, Ta of 125°C50                                                       |

| Figure 3.41: | Convection coefficient versus Tj for different heat-sink sizes, for 1.6KW power  |

|              | dissipation, Ta of 125°C50                                                       |

| Figure 3.42: | Convection coefficient versus heat-sink increase                                 |

| Figure 3.43: | Convection coefficient versus power dissipation and substrate size for Tj 250°C  |

|              | (without BP or HS)                                                               |

| Figure 3.44: | Convection coefficient versus power dissipation and substrate size for Tj 250°C  |

|              | (with BP and without HS)                                                         |

| Figure 3.45:   | Convection coefficient versus power dissipation and substrate size for Tj 250°C    |

|----------------|------------------------------------------------------------------------------------|

|                | (with BP and HS)                                                                   |

| Figure 3.46:   | Convection coefficient versus power dissipation and substrate size for Tj 250°C    |

|                | (All three cases)                                                                  |

| Figure 3.47:   | Convection coefficient versus Tj for various substrate sizes, power dissipation of |

|                | 1.6KW (without BP or HS)                                                           |

| Figure 3.48:   | Convection coefficient versus Tj for various substrate sizes, power dissipation of |

|                | 1.6KW (with BP and HS)54                                                           |

| Figure 3.49:   | Convection coefficient versus Tj for various substrate sizes, power dissipation of |

|                | 1.6KW (with BP and HS)55                                                           |

| Figure 3.50:   | Convection coefficient versus Tj for various substrate sizes, power dissipation of |

|                | 2.5KW (without BP or HS)                                                           |

| Figure 3.51:   | Convection coefficient versus Tj for various substrate sizes, power dissipation of |

|                | 2.5KW (with BP and HS)                                                             |

| Figure 3.52:   | Convection coefficient versus Tj for various substrate sizes, power dissipation of |

|                | 2.5KW (with BP and HS)                                                             |

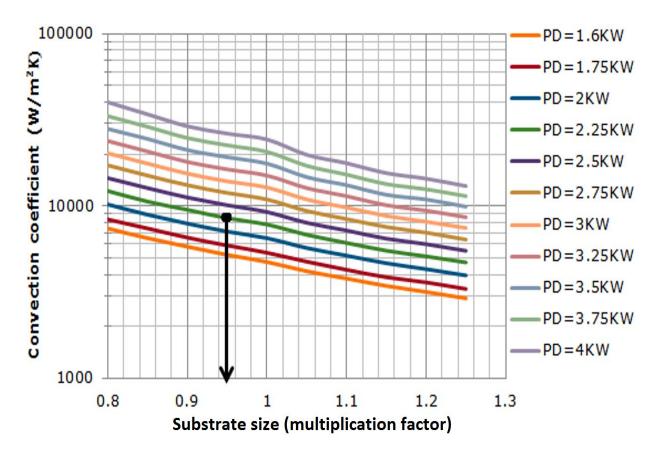

| Figure 3.53(a) | Convection coefficient versus substrate size increase (linear plot)                |

| Figure 3.53(b) | Convection coefficient versus substrate size increase (semilog plot)               |

| Figure 3.54:   | Find y-axis (convection coefficient) with respect to 1.1 on x-axis (substrate size |

|                | increase); for 2.5KW power dissipation                                             |

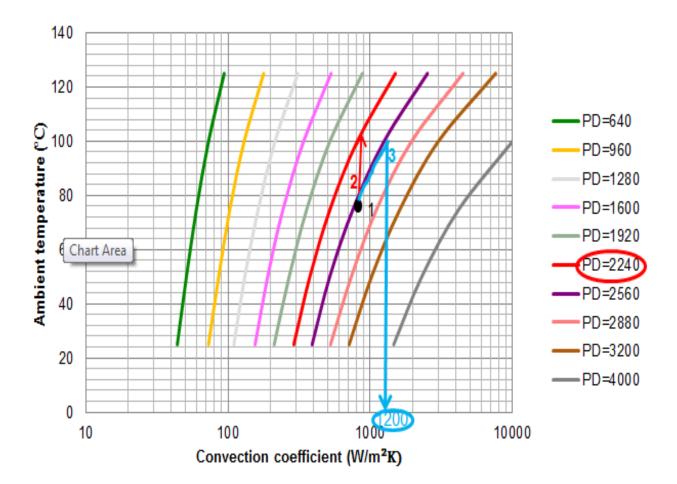

| Figure 3.55(a) | Semi-logarithmic plot of Figure 3.28 for better reading values                     |

| Figure 3.55(b) | ):Obtaining convection coefficient for Ta = 75°C61                                 |

| Figure 3.56(a) | Ta versus convection coefficient for different power dissipations                  |

| Figure 3.56(b) | Convection coefficient versus substrate size plot to find the optimum size | .63 |

|----------------|----------------------------------------------------------------------------|-----|

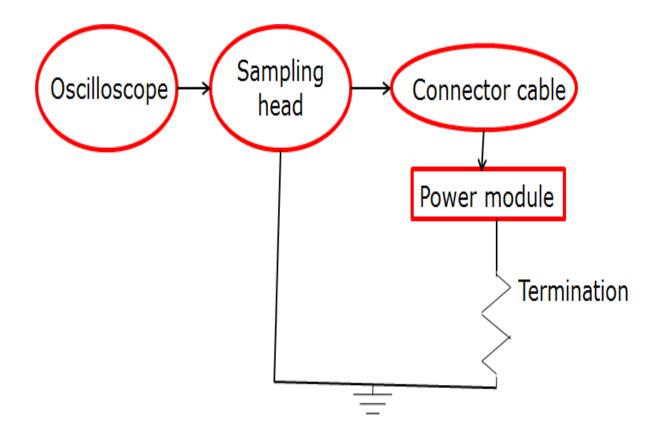

| Figure 4.1:    | Basic block diagram representation of TDR method                           | .67 |

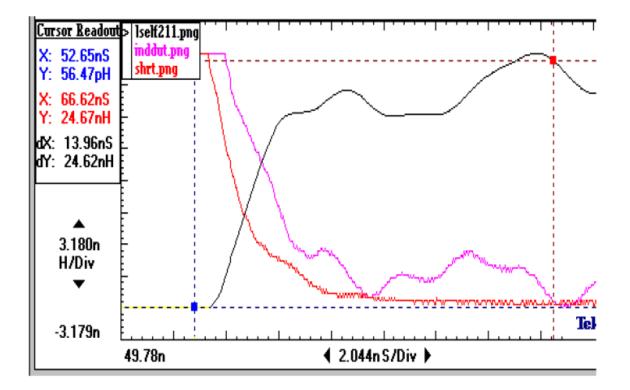

| Figure 4.2:    | TDR waveforms example of test vehicle in parasitic inductance measurement  | .68 |

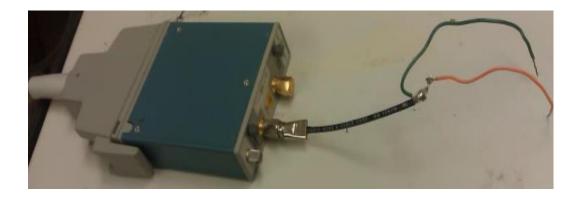

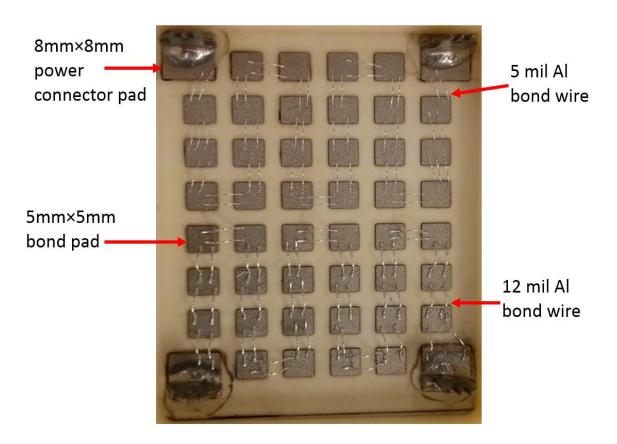

| Figure 4.3:    | Test vehicle B, designed to measure parasitics                             | .69 |

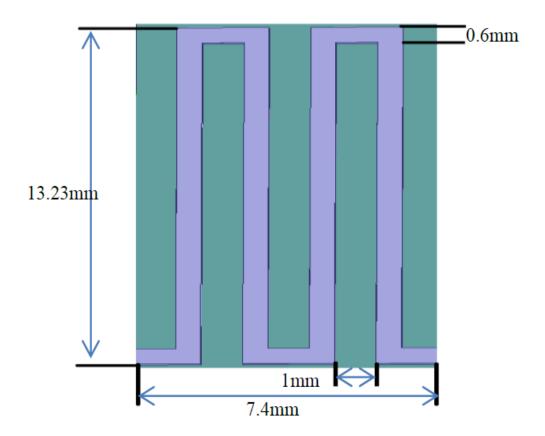

| Figure 4.4:    | Trace dimensions                                                           | .70 |

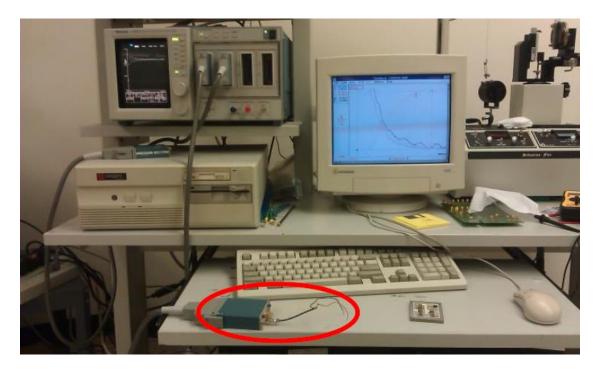

| Figure 4.5(a): | Experimental setup for TDR                                                 | .71 |

| Figure 4.5(b): | Focused on the sampling head                                               | .71 |

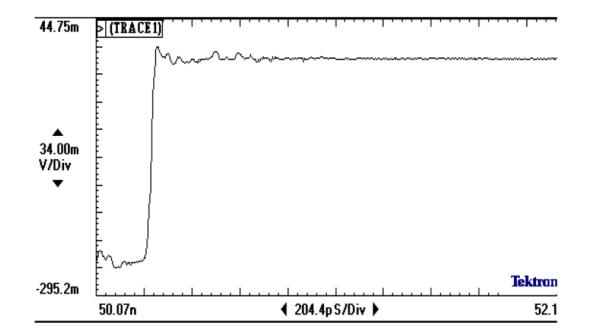

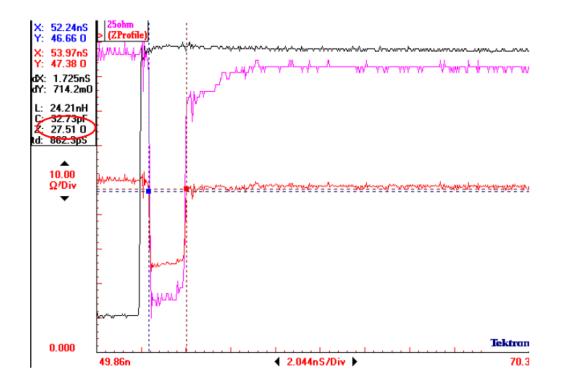

| Figure 4.6:    | Incident step signal or waveform incident on micro-strips                  | .72 |

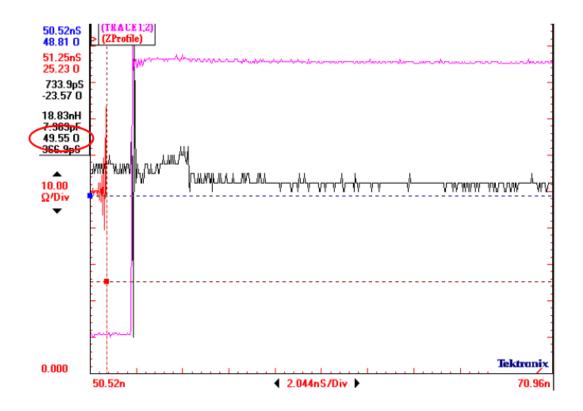

| Figure 4.7:    | Impedance waveform for 25 ohms                                             | .73 |

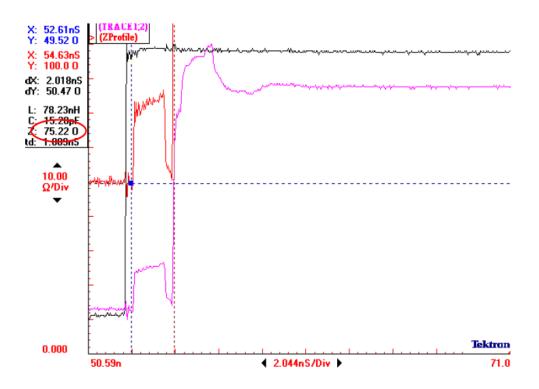

| Figure 4.8:    | Impedance waveform for 50 ohms                                             | .73 |

| Figure 4.9:    | Impedance waveform for 75 ohms                                             | .74 |

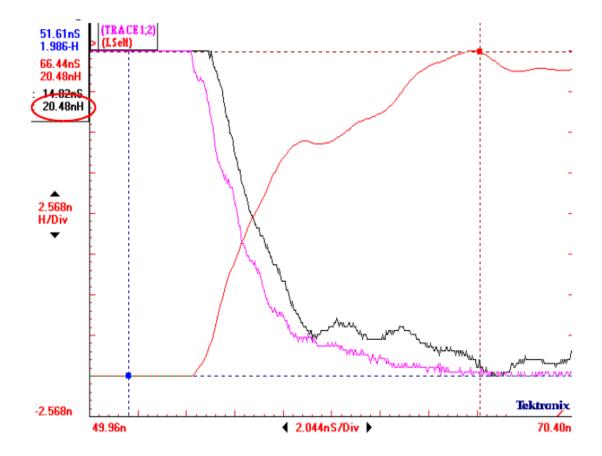

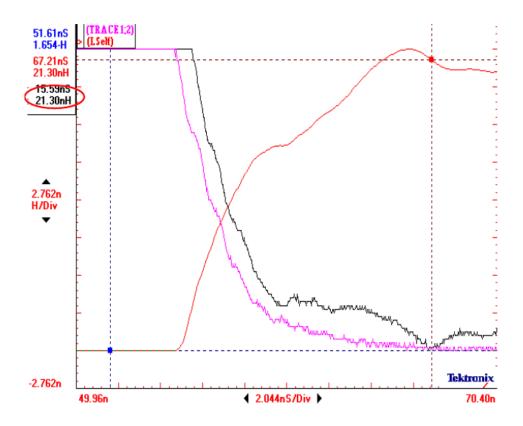

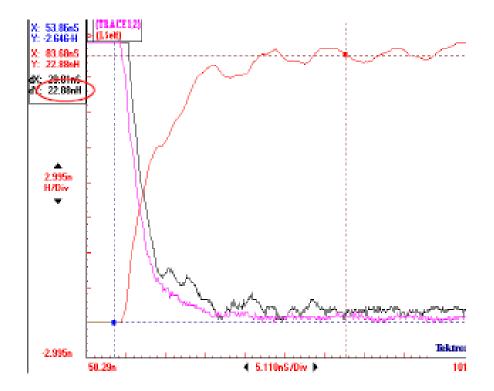

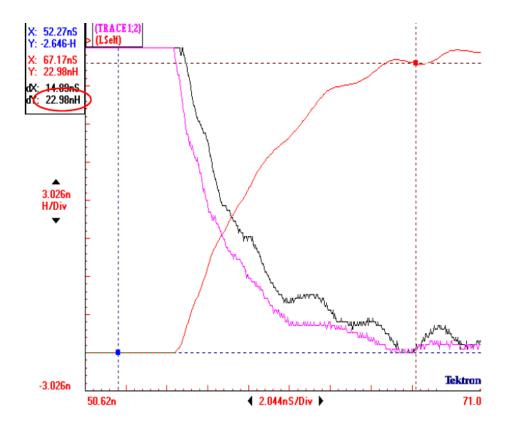

| Figure 4.10:   | Reflected, shorted and inductance waveforms for trace 1                    | .75 |

| Figure 4.11:   | Reflected, shorted and inductance waveforms for trace 2                    | .76 |

| Figure 4.12:   | Reflected, shorted and inductance waveforms for trace 3                    | .76 |

| Figure 4.13:   | Reflected, shorted and inductance waveforms for trace 4                    | .77 |

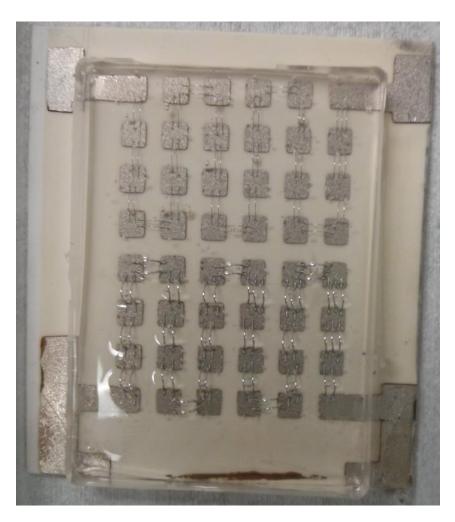

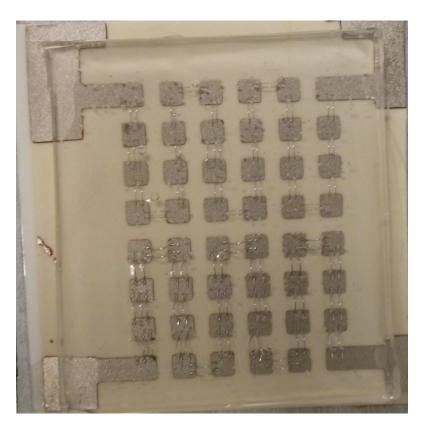

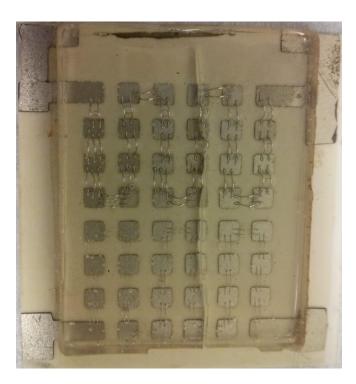

| Figure 5.1:    | Layout according to daisy chain design (with power connectors)             | .80 |

| Figure 5.2:    | Layout according to daisy chain design (without power connectors)          | .81 |

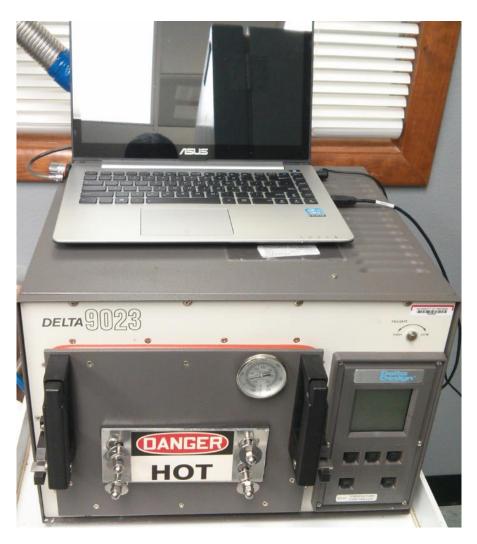

| Figure 5.3:    | Thermal cycling furnace                                                    | .86 |

| Figure 5.4(a): | Un-encapsulated test structure after thermal cycling                       | .87 |

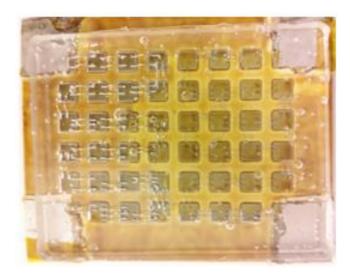

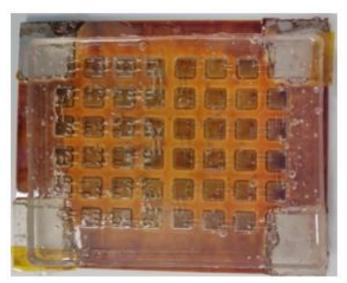

| Figure 5.4(b): | Encapsulated test structure after thermal cycling                          | .87 |

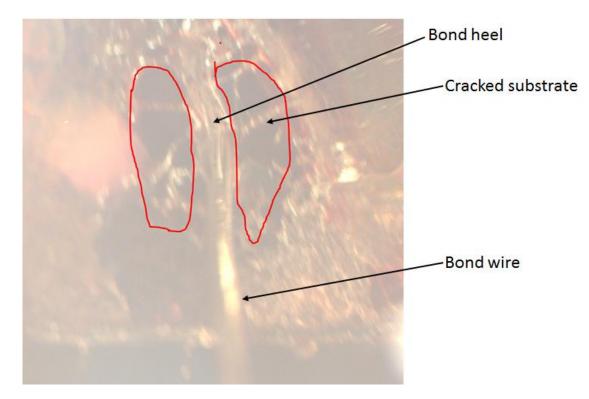

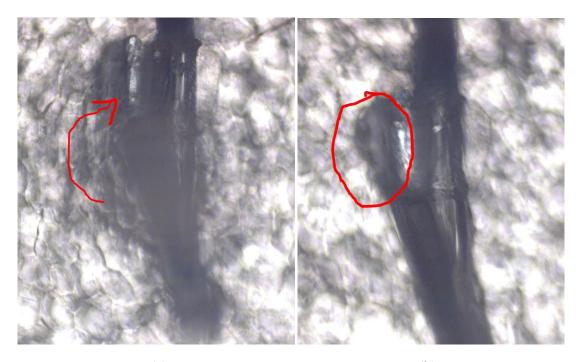

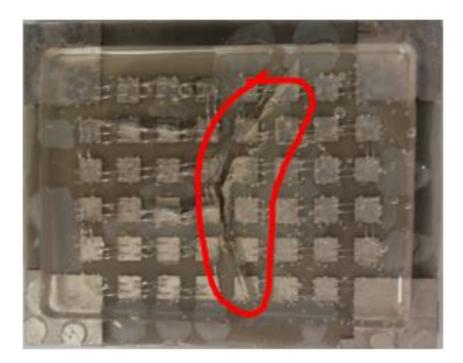

| Figure 5.5:    | Cracks developed in encapsulated test structure                            | .88 |

| Figure 5.6(a): | Faulty wirebonds observed in test structure                                | 89  |

| Figure 5.6(b): | Faulty wirebonds observed in test structure                                | 90  |

| Figure 5.7:    | Flux cleaned and encapsulated test structure after thermal cycling          | 91  |

|----------------|-----------------------------------------------------------------------------|-----|

| Figure 5.8:    | No cracks at critical points                                                | 92  |

| Figure 5.9:    | Layout of test structure                                                    | 93  |

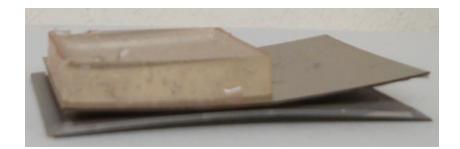

| Figure 5.10:   | De-lamination of copper layer from Al <sub>2</sub> O <sub>3</sub> substrate | 95  |

| Figure 5.11:   | De-lamination of encapsulate from DBC substrate decreases                   | 97  |

| Figure 5.12:   | De-lamination of encapsulate from DBC substrate                             | 97  |

| Figure 5.13:   | Horizontal crack developed on the one of the test structure                 | 98  |

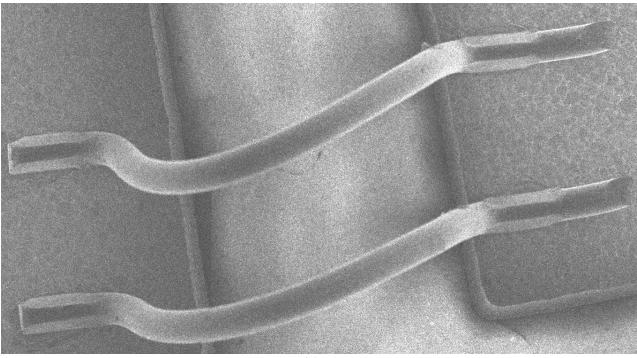

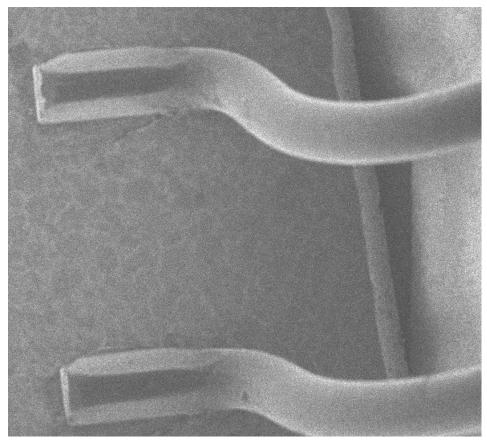

| Figure 5.14:   | Faulty 5 mil wirebonds                                                      | 99  |

| Figure 5.15:   | 12 mil wirebonds                                                            | 100 |

| Figure 5.16(a) | PAI coated test structure before thermal cycling                            | 102 |

| Figure 5.16(b) | ):PAI coated test structure after thermal cycling                           | 102 |

| Figure 5.17:   | Non PAI coated test structure                                               | 103 |

#### **CHAPTER 1. INTRODUCTION**

Power electronic module is an optimal compact package of a circuit which includes multiple power semiconductor devices (MOSFETs, diodes, IGBTs etc.), and sometimes along with passives (resistors, and capacitors etc.) and their control circuitries. These power modules are later integrated into a corresponding power electronic system which performs a specific function. Power electronic modules are widely used in various home and industrial applications like automobiles, motor controllers, power supplies, robotics, air conditioners, refrigerators, continuous power distribution systems, etc.

A power module design is optimized before fabrication; to provide for size and weight reduction, lower parasitic, thermally optimum, higher efficiency and improved performance. Trade-off between cost and reliability is the major factor that affects designing of power electronic systems. Since individual packages are not required for power semiconductor devices; and all power semiconductor devices can be incorporated into a single package, power electronic modules should provide for high reliability with lower cost and smaller size.

The first step in the power electronic module design is to choose an appropriate topology. Once this is done, the module is designed using Q3D software manually or using a layout designing software tool. This designed virtual module is subjected to thermal and parasitic simulations to optimize the design.

Thermal simulations can be performed using the SolidWorks software. These simulations provide the maximum junction temperature for module designed for certain parameters. The operating parameters and design are varied until a maximum junction temperature (for example, 250°C) is achieved. This thermally optimized design is later subjected to parasitic simulations

1

using Q3D software to re-optimize the module with respect to parasitics. This design for layout is later fabricated using several fabrication processes and tested.

#### **1.1** Thermal Analysis

Several design parameters such as power dissipation, maximum junction temperature, and convection coefficient affect the performance of a power electronic module. Hence, it is very crucial in selecting appropriate parameters while designing a layout. Usually trial and error methods are employed when layout is designed manually. This is a very tedious and time-consuming process. Even when a layout is designed using computer aided design tools, most of these parameters should be provided by the designer initially to the designing software.

This thesis aims to provide a "rough" database that predicts the thermal behaviors of the module for several different parameters. When designers use this database to select their parameters, module behavior becomes predictable to a good extent. Thermal analysis is performed on a generalized module using SolidWorks software, and their results are represented in a way that helps in choosing parameters. This is shown in Chapter 3. Chapter 3 also provides a few examples which demonstrate the parameter selection procedure.

#### **1.2** Parasitic extraction of power modules

Parasitic analysis is performed on a virtual power module before fabrication for electrical characterization. However for verification purposes, it is also required to extract parasitic from a fabricated module. Chapter 4 develops the physical extraction of parasitic inductances using a time domain reflectometry (TDR) method.

2

#### **1.3** Reliability of wirebonds

Temperature cycling can reveal failures associated with the mismatches of coefficients of thermal expansion of different material systems in the power electronic modules. Thermal cycling of power electronic module is performed from -55°C to 250°C using a daisy-chain wirebond and results/behavior of the modules with encapsulation and without encapsulation is compared.

#### **1.3** Chapter Organization

This thesis is organized into six chapters. Chapter 1 introduces the objectives and rationales behind research work. Chapter 2 discusses the background concepts. Chapter 3 discusses results from the thermal analysis of a power electronic modules. Chapter 4 develops the parasitic extraction measurements using the time domain reflectometry method. Chapter 5 presents the thermal cycling results of power electronic modules with and without encapsulation. Chapter 6 concludes the thesis.

#### **CHAPTER 2. BACKGROUND CONCEPTS**

#### 2.1 Heat transfer in power modules

Heat transfers between solids when they are in contact. As heat transfers through several layers in series thermal resistivity increases, thus decreasing the heat-transfer rate. Similarly, as heat transfers through layers in parallel, thermal resistivity decreases, thus increasing the heat-transfer rate.

In a power electronic module, there are several layers in series – like die, direct bonded copper substrate, solder, baseplate – and heat-sink is normally considered to be in parallel due to fins. Hence, a complex structure of several layers in series and parallel need to be considered to calculate the total thermal resistance of the complete structure.

Heat is dissipated by power semiconductor dies in the power electronic module and in a multiple chip module where several power semiconductor dies dissipate power, thermal coupling takes place. This further increases maximum junction temperature of the power electronic module. This in-turn demands a better cooling system. To increase the efficiency by increasing heattransfer rate would place the power semiconductor dies far apart that heat-dissipated by one power semiconductor die does not couple with that of the other.

The calculation shown below is an example for a minimum distance between two power semiconductor dies to avoid thermal coupling completely before a heat-sink is attached. Figure 2.1 shows the several layers of a typical power electronic module.

4

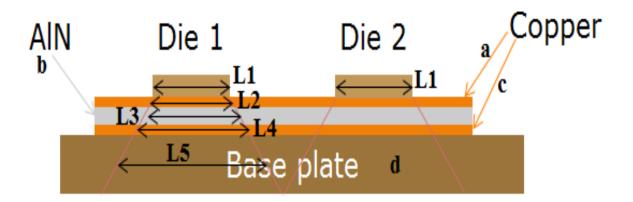

Figure 2.1: Layers in power module (solder layer is neglected)

Power semiconductor die is placed on the DBC substrate (copper, AlN, copper) and baseplate. Since the solder layer is very thin and when an ideal case is considered, solder layers can be ignored. The red lines in Figure 2.1 indicate the heat-spreading as it passes through various layers. The heat-spreading angle ( $\alpha$ ) changes as it passes through each layer. In Figure 2.1, L1, L2, L3, L4, and L5 indicate the power semiconductor, the top copper layer, the DBC dielectric layer, the bottom copper layer, and the baseplate layer, respectively. The following symbols are used:

'K' defines thermal conductivity of each material.

$K_{Cu} = Ka = Kc = Kd = 393W/m-K$

$K_{AlN} = Kb = 170 \text{ W/m-K}$

$K_{Al}$  (baseplate is usually followed by Al heat-sink) = 240W/m-K

'T' indicates thickness of each layer.

Ta = Tc = 0.3mm

Tb = 0.65mm

Td = 6.35mm

The angle of spreading ' $\alpha$ ' is given by [1]:

From equation (2.1), we have

$$\alpha_{a} = \tan^{-1} \left(\frac{\text{Ka}}{\text{Kb}}\right) = \tan^{-1} \left(\frac{393}{170}\right) = 66.6^{\circ}$$

$$\alpha_{b} = \tan^{-1} \left(\frac{\text{Kb}}{\text{Kc}}\right) = \tan^{-1} \left(\frac{170}{393}\right) = 23.4^{\circ}$$

$$\alpha_{c} = \tan^{-1} \left(\frac{\text{Kc}}{\text{Kd}}\right) = \tan^{-1} \left(\frac{393}{393}\right) = 45^{\circ}$$

$$\alpha_{d} = \tan^{-1} \left(\frac{\text{Kd}}{\text{Ke}}\right) = \tan^{-1} \left(\frac{393}{240}\right) = 58.6^{\circ}$$

where  $\alpha_a$  is the angle of spreading at the interface of the power semiconductor die and the top copper layer,  $\alpha_b$  is angle of spreading at the top copper layer and the DBC dielectric layer,  $\alpha_c$  is angle of spreading at the DBC dielectric layer and the bottom copper layer,  $\alpha_d$  is angle of spreading at the interface of the bottom copper layer and the baseplate layer. The surface length of thermal effect for one dimensional model is given by [1]:

$$L(of next layer) = 2 t_x tan(\alpha_x) + L(of previous layer).....(2.2)$$

L1 is the length of the power semiconductor die, 4.08mm for the 50A CREE MOSFETs. Then,

L2=2 t<sub>a</sub> tan(

$$\alpha_a$$

)+L1= 2 (0.3 × 10<sup>-3</sup>)tan(66.6)+4.08×10<sup>-3</sup>=5.47 ×10<sup>-3</sup>m

$$L3=2 t_{b} \tan(\alpha_{b})+L2=2 (0.65 \times 10^{-3})\tan(23.4)+5.47 \times 10^{-3}=6.0326 \times 10^{-3}m$$

$$L4=2 t_{c} \tan(\alpha_{c})+L3=2 (0.3 \times 10^{-3})\tan(45)+6.0326 \times 10^{-3}=6.6326 \times 10^{-3}m$$

$$L5=2 t_{d} \tan(\alpha_{d})+L4=2 (6.35 \times 10^{-3})\tan(58.6)+6.6326 \times 10^{-3}=27.43 \times 10^{-3}m$$

From the above analysis, the minimum distance between the two 50A CREE SiC power MOSFETs in order to have a complete heat spreading without any thermal coupling is 27.43mm -4.08mm = 23.35mm.

This distance is not practical to achieve between the two power semiconductor dies in a multiple chip module as the size of the module becomes very large. Hence, power semiconductor dies are placed close to each other due to size constraint. In this case, thermal coupling needs to be considered as well. Maximum junction temperature increases due to thermal coupling, and hence, a more effective cooling system needs to be employed to cool the module. Using software which incorporates finite element analysis and iterative methods for thermal simulations, it is possible to evaluate the maximum junction temperature of the power electronic modules, and hence, the convection coefficient required to cool the power electronic module.

#### 2.2 Encapsulation

Encapsulation is an insulating layer applied on the power electronic modules to protect their underlying components. These components can be chips/dies, wire connections and substrate, etc. These encapsulations need to be electrically insulating to avoid shorting of the components due to high voltage/current surges. Since heat dissipation occurs at chips and encapsulation is in contact with them, it would be ideal if encapsulation also aids in uniform heat distribution over the module. Also, there should be good adhesion between substrate and encapsulation after curing. Encapsulation must be chosen in such a way that the difference in coefficient of thermal expansion (CTE) between the substrate and encapsulation must be as low as possible. This is required in order to mitigate any sort of undesirable thermal and mechanical stress [2]. Gel form is preferred for encapsulation under pre-cured condition. This is because applying or coating encapsulation on the power electronic module becomes easier. Once applied, encapsulation needs to solidify after curing and still retain its adhesion and insulating properties.

When encapsulation is applied on the power electronic module, care must be taken to prevent air bubbles within the encapsulation layer. If curing needs to be performed at high temperature, temperature must be increased in a rate low enough to avoid air bubbles. Air bubbles needs to be avoided as the trapped moisture or gases might induce corrosion in the power components.

Nusil R-2187 silicone elastomer encapsulation needs to be cured at 80°C for an hour. Temperature of the oven is first increased to 40°C and left there for an hour, and then increased to 60°C and left for another hour, before finally increasing it to 80°C at which the actual curing happens. Also, rate of temperature increases must be kept low enough to achieve effective encapsulation. An air bubble in power electronic module is shown in Figure 2.2.

Figure 2.2. Air bubble in encapsulated power electronic module

#### 2.3 Wirebonding

Most of the interconnections in power electronic modules are usually achieved using wirebonds. Some of these interconnections are

- Connecting two different traces

- To make connections with/between dies (source/drain/gate) and traces of interest.

- Make connection to power connectors which in turn act for external connections.

#### 2.3.1 Bond wire material

Several materials for wires have been investigated for the power electronic module packaging. Some of them are mentioned below:

- Gold and Gold-alloys. This material is preferred in thermo-compression or thermo-sonic bonding. It has good electrical properties and high reliability. [3]

- Copper wire is a good substitute for Au wires as it costs less and has similar electrical properties. [4]

- Beryllium-doped Au wires have strong wire properties, and hence, can bear high stress.

They are mainly used for automated bonding which adds a lot of mechanical stress on wires. [5]

- Aluminum wires are used as bond wires in this thesis. Al bond wires are preferred for high current density and weigh relatively low. They are available in both thin/fine (< 3mil wire diameter) and thick/heavy wires (> 3mil wire diameter). 5mil and 12mil aluminum bond wires are used to make interconnections in the wirebond reliability test structures in Chapter 5. Al wires are usually 99% pure and the other 1% is usually silicon or magnesium. Magnesium doping provides a better fatigue resistance [6]. Al 1%Si wire is precipitation strengthened and Al 1%Mg is solution strengthened. Both have similar

break and yield strength for a wide range of annealing temperature. According to Hongwei Liu, elongation increases with annealing temperature for 1%Mg Al wires and reaches its highest around  $250^{\circ}$ C –  $300^{\circ}$ C. Whereas for 1%Si Al wires, two high peaks and another low peaks were recorded between  $200^{\circ}$ C and  $300^{\circ}$ C [7].

#### 2.3.2 Wirebonders

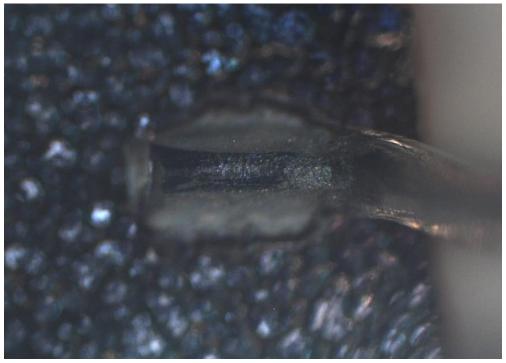

Different types of bonders are available for both automated and manual wirebondings. Wedge bonder is discussed here as this is the bonder used to make wirebonds for the wirebond reliability test modules as reported in Chapter 5.

Ultrasonic wedge bonder:

Ultrasonic wedge bonder attaches/welds wire to a substrate using ultrasonic energy at room temperature. The bonder has a capillary through which bond wire is fed. The capillary is pointed at the first bonding position and wire is bonded using ultrasonic energy. This is called the head of the wirebond. The voltage and time to weld the wire should be calibrated according to the wirebond diameter. Once head connection is made, the wedge bonder's capillary is lifted to a loop height (this needs to be set based on the module design) and steps back (step back needs to be set according to the module design as well) to the second position. The bonder now makes second bond at this position using its ultrasonic energy. This is the tail of the bond. Bonds are made at room temperature. Once the second bond is made, the wire following second bond is cut. Figure 2.3 shows a wedge bond. An orthodyne ultrasonic wedge bonder shown in Figure 2.4 was used to create the aluminum wedge bond shown in Figure 2.3.

Figure 2.3. Wedge wirebond

Figure 2.4. Orthodyne ultrasonic wedge bonder

#### 2.3.3 Failure mechanisms

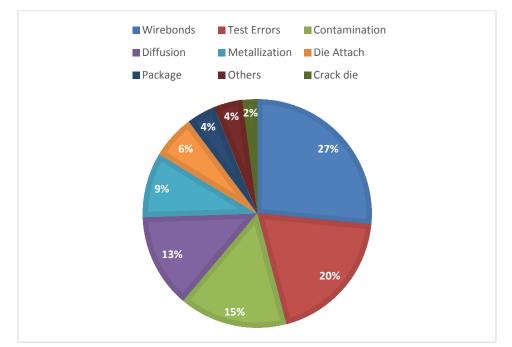

A power electronic module houses several interconnections using wirebonds. The number of wirebonds in a single power electronic module can vary from 10s to 10000's. Sometimes a single wirebond failure in critical spots like gate connections can cause failure of the entire power electronic module. Hence study of wirebond failure is very important to assess the reliability of power electronic modules. Wirebond failure is the largest failure mode for an integrated circuit as shown in Figure 2.5.

Figure 2.5: Failure modes of an integrated circuit [Source: Solid state technology ICE "Road maps of packaging technology"] [8]

Some of the failure mechanisms for wirebonds are:

- Insufficient energy (ultrasonic energy in case of ultrasonic wedge bonder) applied on the bond wire while welding it to the substrate. This causes weak bonds, and hence, a small amount of stress can cause failure.

- When energy more than the required levels is applied while bonding, it can cause extra stress, and hence deform the bond heel.

- Improper tool calibration like wirefeed length, step back, loop height.

- Wirebonds are subjected to mechanical stress due to other materials in power electronic modules like encapsulation. If mechanical stress is big enough, it may cause wirebond failure as well.

- Wirebonds may corrode due to moisture and gases at bonding points.

- Contamination of the substrate or un-clean substrate lead to thermo-oxidative degradation, and hence, corrosion in aluminum bond wires at its heel.

- Breakage of bonds when handled roughly.

- In a case where wirebonds jump over a trace, shorting of the middle undesirable trace with other traces can occur.

- Thermal cycling of the module can add thermal stress on the wirebonds and cause lift-off of wirebond at it heals.

- When hard or thick wires are welded to fragile surfaces like gate pad of a power semiconductor die, the surface damage can occur.

- Even if the wire is well bonded, due to intermetallic failures and formation of Kirkindall voids, a high electrical resistance region at the bonding area can fail interconnections.

#### **CHAPTER 3. THERMAL ANALYSIS OF POWER ELECTRONIC MODULES**

#### 3.1 Introduction

When designing a layout for any circuit, it is easier if there is a database from which one can select certain parameters. Like choosing the right size of the substrate from the efficiency at which the power module is supposed to work, or choosing the type of cooling required (convection coefficient that specifies if free/forced air/liquid cooling) to maintain a particular maximum junction temperature for a given ambient temperature etc.

This chapter includes:

- Study of how different parameters like power dissipation, maximum junction temperature, ambient temperature, convection coefficient required to cool the module, size of the baseplate, heat-sink size, substrate size, spacing between dies, different materials that can be used for module – affect each other in a layout.

- To provide a rough database that aids in choosing parameters like convection coefficient or optimum substrate size for a layout.

The layout of power electronic module can be designed in many ways for the same circuit. To provide for more generalized database, a full bridge circuit is considered. As this is one of the most common topologies used in power electronic modules. For this full bridge circuit, a generalized layout is designed; on which thermal simulations are performed using Solidworks thermal simulator. This layout is later subjected to various conditions virtually; similar to what power electronic modules would experience in actual operation situation. Thermal behavior of this power electronic module in simulated conditions for various parameters is recorded to prepare a database, and to further study them.

#### **3.2** Full bridge circuit

The most common topology used in power module packaging is the full bridge topology since it can deliver a large amount of energy transfer. A half-bridge topology is used in many cases too, but since the full bridge is larger and can accommodate more power semiconductor dies, the full bridge is considered here. A complete full bridge circuit is given in Figure 3.1.

Figure 3.1. Full bridge circuit

For a 50KW power electronic module and 92% efficient, the total power dissipation by the module is 4KW. For a 50KW power module that is 95% efficient, the total power dissipation by the module is 2.5KW. Hence power dissipation by the module depends on the efficiency and how much power the module is capable to output from the given input without being damaged. The maximum power dissipation case by module considered in this thesis is 4KW (higher power dissipation cases are possible but is not considered here). This needs to be distributed between all

the MOSFETs equally. For this extreme case, it's best to consider 32 MOSFETs. This gives 8 MOSFETs on each leg and 125W of power dissipation by each MOSFET rated at 20A.

Since a generalized layout is to be designed for simulation purpose; a layout is designed only for part of a circuit shown in the Figure 3.1 which is inside the red box.

#### **3.3 Full bridge layout**

Several layouts were designed and the most optimized layout was chosen. Size of this substrate is 53mm X 58mm. Of-course the MOSFETs can be rotated to better aid wire-bond connections. In this layout, dies are distributed evenly throughout the substrate, thus providing for good thermal balance. As shown, 8 power MOSFET dies are arranged in a linear array with a common drain on the power substrate. Also, silicon carbide (SiC) MOSFETs are used in this power electronic module as they can operate under high temperature conditions. Figure 3.2 shows the layout on which thermal analysis is performed and results of the same are shown later in this chapter.

Figure 3.2. Full bridge layout.

#### **3.4** Parameter constraints applied on power module for simulations

- *Power dissipation (PD):* As mentioned in section 3.2, maximum limit to power dissipation by module is considered to be 4KW. For analysis, total power dissipation by module is considered to vary from 640W to 4000W. However, three main cases considered are; low 1.6KW, medium 2.5KW and high 4KW.

- *Maximum junction temperature (Tjmax):* It is the maximum temperature allowed on the power electronic module and is usually at the center of the die. Two cases of maximum junction temperature are considered for analysis 250°C and 200°C.

- Ambient temperatures (Ta): This is the temperature at which the module is placed and provides data on the external environment of the working module. Several cases of ambient temperatures are considered like 25°C, 50°C, 75°C, 100°C and 125°C. However, 100°C is considered is most cases unless specified otherwise.

- *Size of DBC or substrate:* Original (smallest) size of the module considered based on the layout design is 53mm X 58mm. This is the substrate size on which thermal analysis is performed until specified otherwise.

- *Convection coefficient (CC):* This value gives us the required cooling system/technique that is needed to be employed, to bring the maximum junction temperature of the module to desired levels. It varies significantly depending on the above parameters. The smaller is the convection coefficient; the more favorable it is to the thermal management system.

Thermal simulations are performed on a DBC substrate with the above parameters individually and the results are plotted. Figure 3.3 shows the SolidWorks designed DBC substrate model on which simulations are performed.

Figure 3.3. DBC substrate designed in SolidWorks

In some layout design software (PowerSynt), baseplate feature attachment option is made available and the convection coefficient assigned to the baseplate would be equivalent to both heat-sink attached to baseplate and the convection coefficient given to this heatsink. For this purpose, thermal simulations are performed on the DBC substrate with baseplate attached to it. Baseplate provides for mechanical strength of the power electronic module and also helps in balanced heat-spreading over the substrate. Baseplate is slightly bigger than the DBC substrate (5mm increase on x and y directions). SolidWorks model for the same is given in Figure 3.4. Baseplate material used is copper. This is because the DBC substrate's copper comes in contact with the baseplate via solder preform/paste hence; to facilitate best thermal distribution and to achieve good heat spreading copper baseplates are preferred. Also it provides best coefficient of thermal expansion match (CTE for copper is 16.7ppm/°C).

Figure 3.4. DBC substrate with baseplate designed in SolidWorks

In all cases, heatsinks are attached to the power electronic modules to increase the cooling surface area. Hence, heatsink is also designed in SolidWorks and is attached to the baseplate. A general design of heat-sink is considered with each fin of 2mm wide, and spacing between each fin is 2mm as shown in Figure 3.5(a). Finally, the heatsink attached to the power electronic module (along with baseplate) is given in Figure 3.5(b).

Figure 3.5(b). DBC substrate with baseplate and heatsink designed in SolidWorks

*Thermal Study* is chosen in SolidWorks simulator to perform steady state thermal analysis. Figure 3.6 shows some of the steps in assigning parameters for simulations. Convection coefficient and ambient temperatures are applied for the power module in SolidWorks on the backside of the substrate (for no baseplate or heatsink condition) or on the backside of the baseplate (for baseplate and no heatsink condition) or to all the exposed faces of the heatsink (for heatsink condition) using *Convection* in *Thermal Load* as illustrated in Figure 3.6(a).

Figure 3.6(a). Assigning convection for power module in SolidWorks (heatsink condition)

Although not all MOSFETs are functioning at the same time; in steady state thermal analysis, due to high switching speeds of the dies, off-time of the dies does not make much difference thermally (NOT electrically) due to thermal mass and slow heat-spreading. Hence it can be considered that power is dissipated equally by all the MOSFETs at a time as an average. From

this assumption, power dissipation is given to the power module by assigning power dissipation for each device (MOSFET, JFET, diodes etc.). Suppose the total power dissipated by the module is 3.2KW, and then equally divide the power between all the dies. In this case since there are 32 MOSFETs, each MOSFET is given 100W of power dissipation (3200/32 = 100W). This power dissipation is assigned using *Heat Power* in *Thermal Loads* and choosing every single MOSFET as shown in Figure 3.6(b).

Figure 3.6(b). Assigning power dissipation for power module in SolidWorks

When all the parameters are applied to the power module, mesh is chosen and the simulation is performed to obtain the simulated results (meshing parameters are chosen depending on the design and size of the module). Simulated results are normally the maximum junction temperature of the module. Parameters are varied using *Convection* and *Heat Power* thermal loads to obtain different/desired junction temperatures.

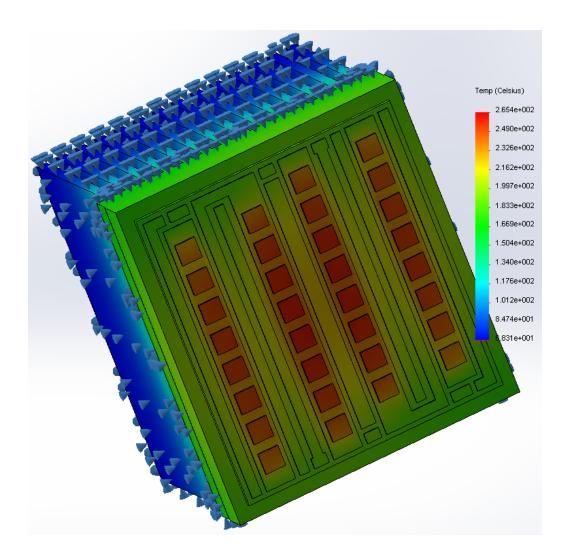

Curvature based mesh is chosen for the simulations of the power electronic module. Figure 3.6(c) shows the meshed power module (after Convection is assigned). Figure 3.6(d) shows the thermally simulated module. Maximum temperature is usually at the center of the die (usually on the die which is placed at the center of the module). Red areas indicate corresponding high temperatures and blue indicates corresponding low temperatures.

Figure 3.6(c). Meshed power module

Figure 3.6(d). Simulated result

## 3.5 Material selection

Properties of different materials that can be used in fabrication are studied. Thermal simulations are performed on these different materials to discuss which materials are best suited for thermal analysis in later section.

# 3.5.1 Insulating material in DBC substrates

AlN and  $Al_2O_3$  are the two mainly used insulating substrates for the DBC. Table 3.1 compares the thermal properties of these two materials.

| Properties                                                          | Al <sub>2</sub> O <sub>3</sub> | AIN |

|---------------------------------------------------------------------|--------------------------------|-----|

| Thermal conductivity (W/m. K at 20°C)                               | 24                             | 170 |

| Coefficient of thermal expansion (ppm/K at 20 to 200°C)             | 6.8                            | 4.7 |

| Specific heat (J/Kg. K)                                             | 880                            | 740 |

| Dielectric strength (KV/mm)                                         | 16.7                           | 20  |

| <b>Relative price per DBC</b> (Al <sub>2</sub> O <sub>3</sub> base) | 1                              | 2.5 |

Table 3.1. Al<sub>2</sub>O<sub>3</sub> and AlN material properties comparison [accuratus.com, remtec.com]

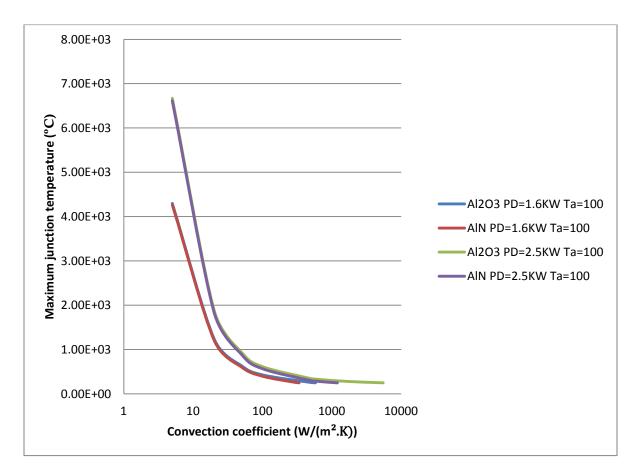

Next, simulations are performed using both materials on model shown in Figure 3.6. The simulation results are shown in Figure 3.7.

Figure 3.7. Convection coefficient versus maximum junction temperature for Al<sub>2</sub>O<sub>3</sub> and AlN materials

Figure 3.7 shows the plot for convection coefficient (CC) versus maximum junction temperature (Tjmax) for Al<sub>2</sub>O<sub>3</sub> and AlN substrate materials under 100°C ambient temperature and different power dissipations (1.6KW and 2.5KW).

It can be seen from Figure 3.7 that although  $Al_2O_3$  and AlN follow the same curve for similar power dissipations, maximum junction temperature of 250°C is reached quicker (lower convection coefficient) in the case for AlN. That is, for 2.5KW (and 1.6KW) of power dissipation,  $Al_2O_3$  based substrate needs around 5500W/m<sup>2</sup>K (and 580W/m<sup>2</sup>K) to reach 250°C of Tjmax whereas AlN requires only 1200W/m<sup>2</sup>K. Also, for 1.6KW of power dissipation,  $Al_2O_3$ based substrate needs around 580W/m<sup>2</sup>K to reach a 250°C Tjmax whereas AlN requires only 340W/m<sup>2</sup>K.

From Table 3.1, thermal conductivity of AlN is much higher than that of  $Al_2O_3$ . Hence, AlN conducts or transfers heat better than the  $Al_2O_3$  dielectric. So, when performance is the main factor in designing the layout, it is always better to choose AlN as the insulating material for the DBC substrate. However if price is the main factor and performance takes second place, then  $Al_2O_3$  is the better option.

#### 3.5.2 Different heat-sink materials

As discussed in Chapter 2, heatsink reduces the temperature of the power module by a significant value by increasing the surface area that is exposed to the external environment (ambient temperature).

Varieties of heatsink materials are available in the market today. Some of the most commonly used heat-sink materials are: Al alloys 1050A, 6061, 6063 and copper. Properties of these metals are given in the Table 3.2.

| Property                                 | 1050A                 | 6061                      | 6063                 | Cu                    |

|------------------------------------------|-----------------------|---------------------------|----------------------|-----------------------|

| Density (g/cm <sup>3</sup> )             | 2.71                  | 2.7                       | 2.7                  | 8.92                  |

| Melting Point (°C)                       | 650                   | 650                       | 600                  | 1083                  |

| Modulus of Elasticity (GPa)              | 71                    | 70                        | 69.5                 | 117                   |

| Electrical Resistivity (Ω.cm)            | 2.82x10 <sup>-6</sup> | 3.7–4.0 x10 <sup>-6</sup> | 3.5x10 <sup>-6</sup> | 1.71x10 <sup>-6</sup> |

| Thermal Conductivity (W/m.K)             | 222                   | 173                       | 200                  | 391.1                 |

| Thermal Expansion (x10 <sup>-6</sup> /K) | 24                    | 23.5                      | 23.5                 | 16.9                  |

Table 3.2. 1050A, 6061, 6063, Cu material properties comparison table [Datasheets from www.aalco.co.uk]

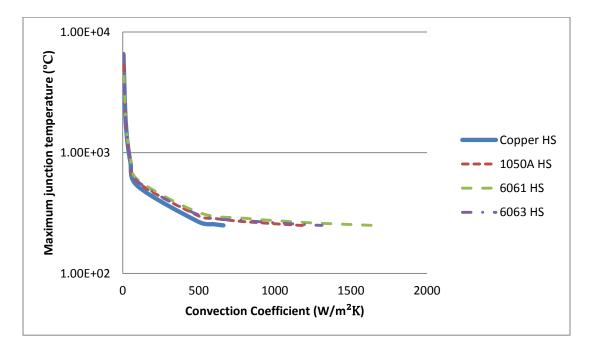

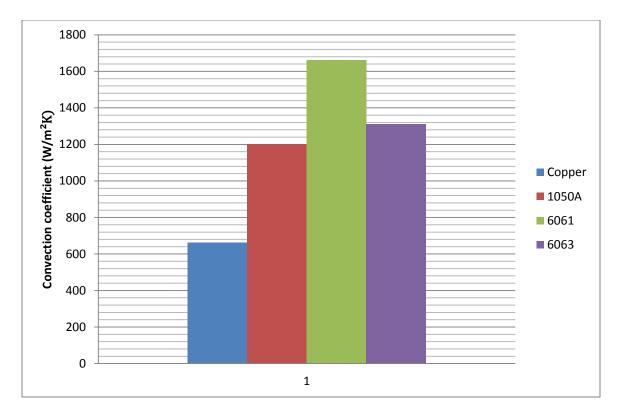

Simulations are performed for all the four heatsink materials (for the model shown in Figure 3.6), for 2.5KW power dissipation and 100°C ambient temperature. The plot obtained for maximum junction temperature versus convection coefficient is shown in Figure 3.8 for the four materials. Also, Figure 3.9 shows the convection coefficient required by each of these materials to maintain a 250°C maximum junction temperature.

Figure 3.8. Convection coefficient versus maximum junction temperature for four materials

Figure 3.9. Convection coefficient required by each material to maintain a maximum junction temperature of 250°C

Copper and 1050A Al alloy produce best results as seen in Figures 3.8 and 3.9. Based on the plots above, copper is the best material for heat-sink since it requires almost only half the convection coefficient to cool the substrate when compared to that of the 1050A Al alloy. But, from Table 3.2, the density of copper (8.92g/cm<sup>3</sup>) is much higher than that of 1050A (2.71g/cm<sup>3</sup>). Hence if copper is used as a heatsink material the power electronic module becomes heavy. Due to this trade-off, Al alloy 1050A is used for heatsinks when a reduced weight is important. Therefore for thermal simulations later in this chapter, Al alloy 1050A material is used as the heatsinks.

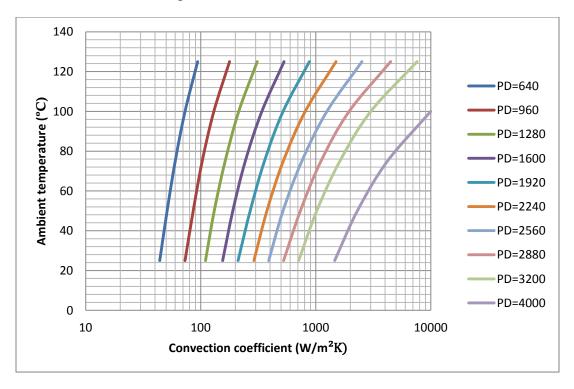

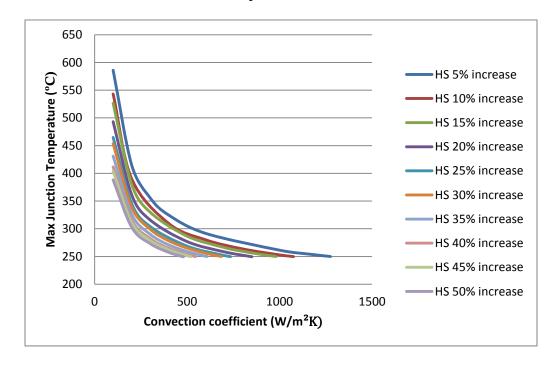

#### **3.6** Study on ambient temperature variations

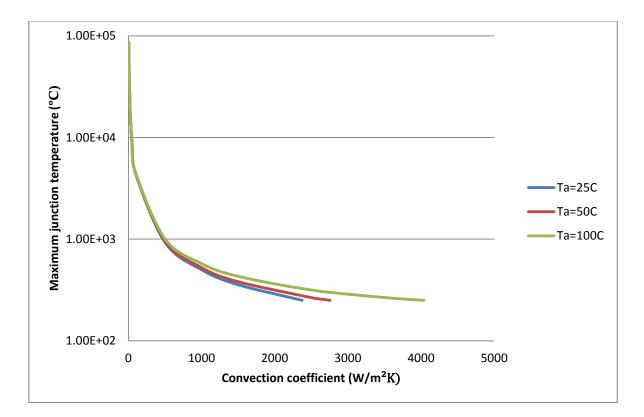

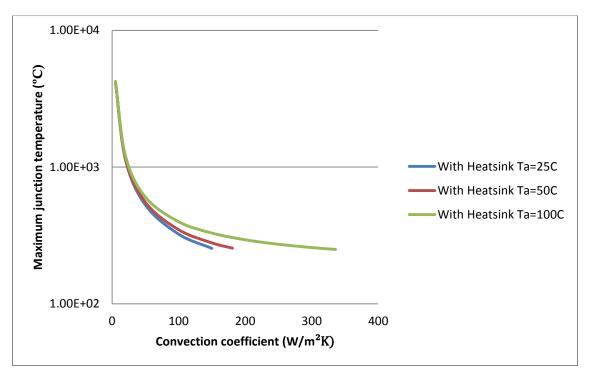

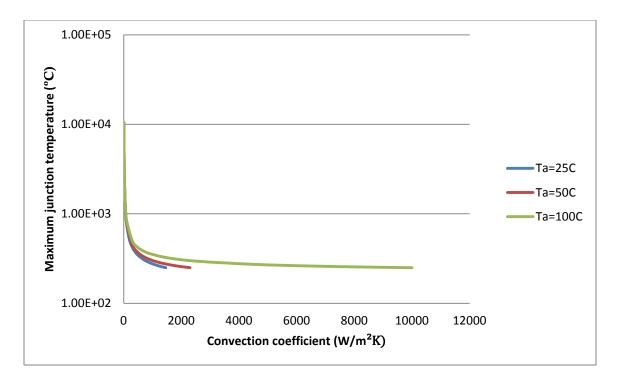

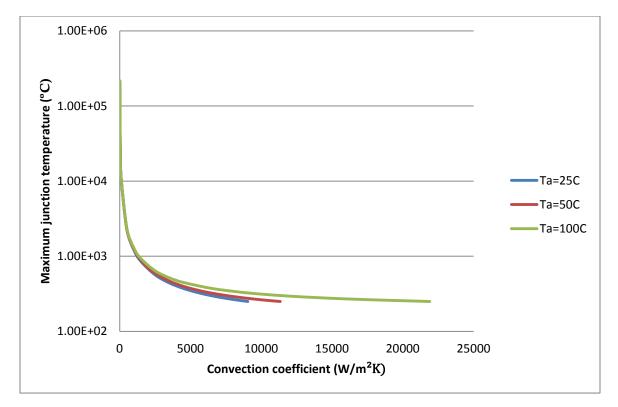

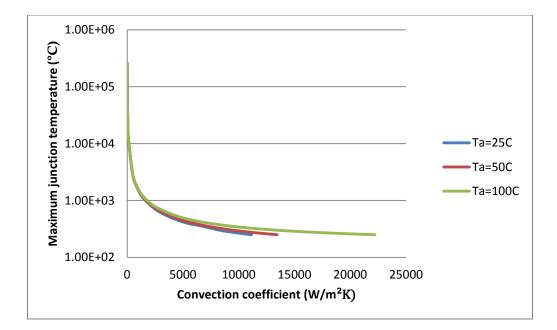

To study the effect of ambient temperature on the power electronic module, maximum junction temperature versus convection coefficient is plotted for different ambient temperatures at 25°C,

50°C, 100°C, and 150°C for 2.5KW power dissipation. Figure 3.10 is for model shown in Figure 3.3 with no baseplate and no heat-sink condition.

Figure 3.10. Convection coefficient versus maximum junction temperature (without BP or HS) for different ambient temperature and 2.5KW power dissipation

Similarly, Figures 3.11 and 3.12 are for models shown in Figures 3.4 and 3.5, respectively (with base plate, and with baseplate and heatsink, respectively).

Figure 3.11. Convection coefficient versus maximum junction temperature (with BP and without HS) for different ambient temperature and 2.5KW power dissipation

Figure 3.12. Convection coefficient versus maximum junction temperature (with BP and HS) for different ambient temperatures and 2.5KW power dissipation

As seen in Figures 3.10, 3.11, and 3.12, convection coefficient versus Tjmax plots show exponential behaviors. Also, Tjmax in most of the power electronic module does not exceed 250°C or 300°C. Hence, the power electronic module with heatsink and convection coefficient larger than 260W/m<sup>2</sup>K is of importance.

Three main cases considered are:

- No heatsink and no baseplate: baseplates are not used to improve power cycling capability in some cases. To provide equivalent convection coefficient to heatsink and cooling system given to this heatsink, this case is considered.

- With baseplate and without heatsink: there are several software that provide for only baseplate while layout is generated (for example: PowerSynt [9]), to provide the equivalent convection coefficient to heatsink and cooling applied to this heatsink case two is considered.

- With baseplate and heatsink: most power modules design includes both baseplate and heatsink.

Similarly for 1.6KW and 4KW power dissipations, data collected is shown in Figures 3.13, 3.16 (no baseplate and no heat-sink condition), 3.14, 3.17 (with base plate and without heat-sink) and 3.15, 3.18 (with baseplate and heat-sink conditions). From these plots, the type of cooling required for a particular ambient temperature and power dissipation conditions can be determined.

Figure 3.13. Convection coefficient versus maximum junction temperature (without BP or HS) for different ambient temperatures and 1.6KW power dissipation

Figure 3.14. Convection coefficient versus maximum junction temperature (with BP and without HS) for different ambient temperatures and 1.6KW power dissipation

Figure 3.15. Convection coefficient versus maximum junction temperature (with BP and HS) for different ambient temperatures and 1.6KW power dissipation

Figure 3.16. Convection coefficient versus maximum junction temperature (without BP or HS) for different ambient temperatures and 4KW power dissipation

Figure 3.17. Convection coefficient versus maximum junction temperature (with BP and without HS) for different ambient temperatures and 4KW power dissipation

Figure 3.18. Convection coefficient versus maximum junction temperature (with BP and HS) for different ambient temperatures and 4KW power dissipation

From these plots, it is obvious that the lower the ambient temperature, the lower is the convection coefficient required to achieve a similar junction temperature. The greater is the difference between ambient temperature and junction temperature ( $\Delta T = Tjmax \sim Ta$ ), the lower is the convection coefficient, and hence, a lower cost cooling system can be employed for good performance.

#### 3.7 Study on power dissipation (heat generated by dies) variations

This section is to study the type of cooling needed to be employed for the power electronic module with changes in power dissipated by them. Different power devices (power semiconductor dies) have different thermal resistance and drain-to-source resistance. Hence, for the same current (or different currents) passes through the device, heat/power dissipation changes. In this section, total power dissipated by the module is varied from 640W to 3.2KW and the results are plotted. Another parameter considered here along with varying power is the ambient temperature (variation from 20°C to 100°C).

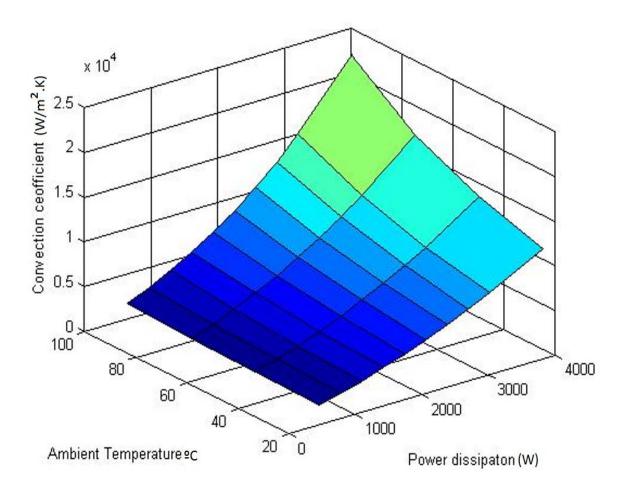

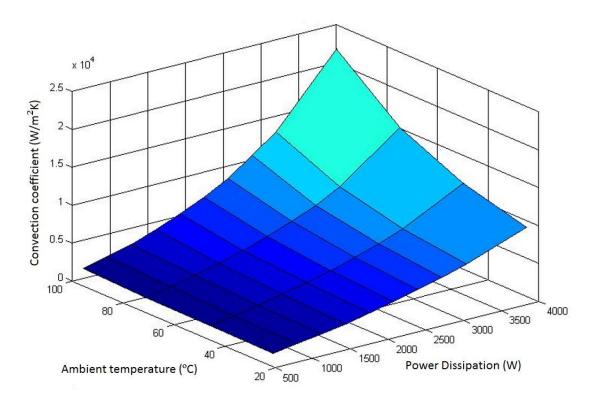

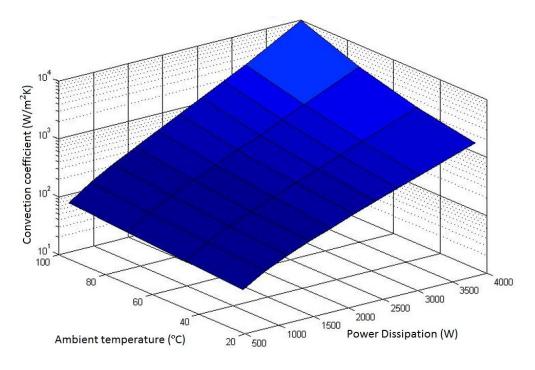

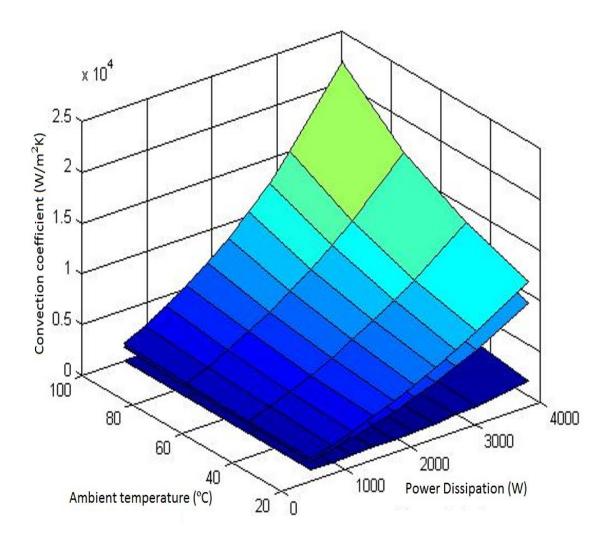

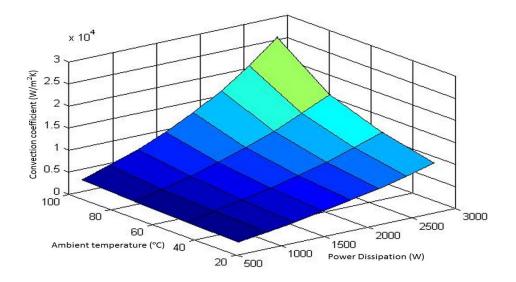

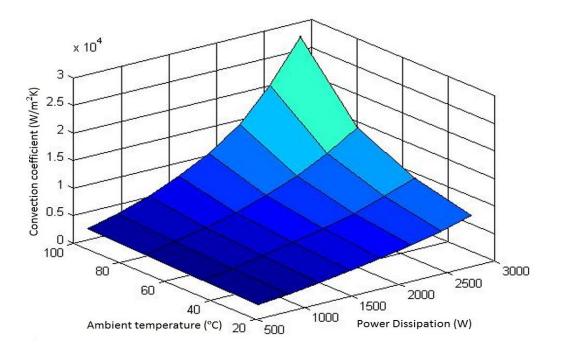

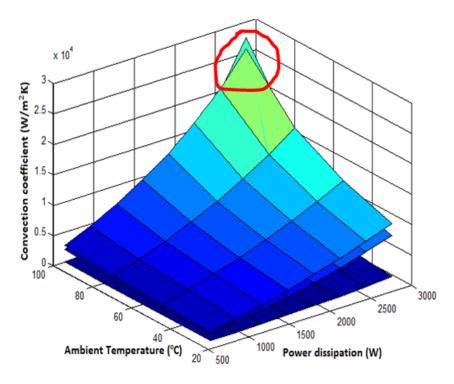

3D graphs are shown below which include power dissipation versus convection coefficient for various ambient temperatures and  $Tj = 250^{\circ}C$ :

- Without baseplate or heatsink (Figure 3.19)

- With baseplate (Figure 3.20)

- With heatsink (Figure 3.21)

- All the above three cases for comparision (Figure 3.22)

Figure 3.19. Power dissipation versus convection coefficient for various ambient temperatures, and Tj of 250°C (without BP or HS condition)

Figure 3.20. Power dissipation versus convection coefficient for various ambient temperatures, and Tj of 250°C (with BP condition)

Figure 3.21. Power dissipation versus convection coefficient for various ambient temperatures, and Tj of 250°C (with BP and HS condition)

Figure 3.22. Power dissipation versus convection coefficient for various ambient temperatures, and Tj of 250°C (all three cases for comparision)

3D graphs are shown which include power dissipation versus convection coefficient for various ambient temperatures and  $Tj = 200^{\circ}C$  for:

- Without baseplate or heat-sink (Figure 3.23)

- With baseplate (Figure 3.24)

- With heatsink (Figure 3.25)

- All the above three cases for comparision (Figure 3.26)

Figure 3.23. Power dissipation versus convection coefficient for various ambient temperatures, and Tj of 200°C (without BP or HS condition)

From these figures, it is self-explanatory that the lower the power dissipated by the module, the lower convection coefficient is required to achieve the same junction temperature.

Figure 3.24. Power dissipation versus convection coefficient for various ambient temperatures, and Tj of 200°C (with BP condition)

Figure 3.25. Power dissipation versus convection coefficient for various ambient temperatures, and Tj of 200°C (with BP or HS condition)

Figure 3.26. Power dissipation versus convection coefficient for various ambient temperatures, and Tj of 200°C (all three cases for comparision)

Figure 3.26 shows that, for most range of ambient temperature, and power dissipation conditions, the convection coefficient required to maintain the maximum junction temperature of 200°C is lower when baseplate is attached when compared to when baseplate is not attached to the substrate. However after a certain range, that is, at high power dissipation and high ambient temperature conditions, the convection coefficient required to maintain 200°C is more when baseplate is attached to substrate than when baseplate is not attached to the substrate. This is because for high power dissipation and low  $\Delta T$ , baseplate acts more like a thermal resistor than a heat-spreader. This inceases the convection coefficient, and hence, decreasing the ease at which excess heat is removed from the substrate. Thus a designer needs to take precautions or decide whether it is advantageous or disadvantageous to employ baseplate in a design for certain parameters.

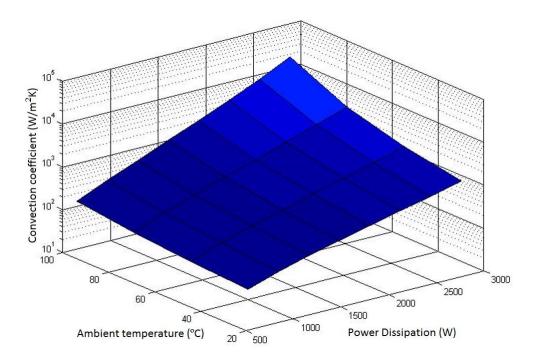

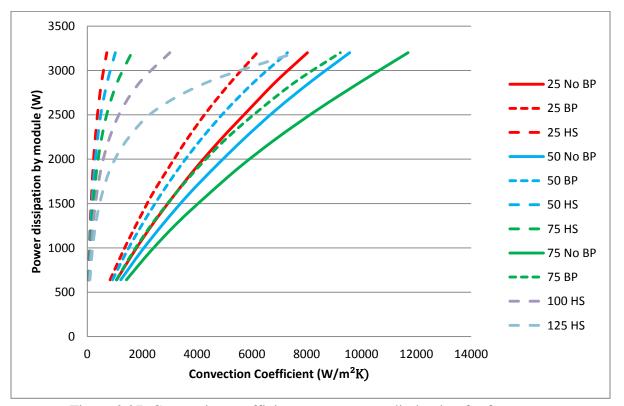

Two dimensional representations for some of the results are shown in Figure 3.27 and 3.28.

Figure 3.27. Convection coefficient versus power dissipation for few cases.

Figure 3.28(a). Convection coefficient versus power dissipation with different ambient temperatures (with BP and HS condition)

Figure 3.28(b). Convection coefficient versus ambient temperature for different power dissipations.

The results from Figure 3.28(a) are used to plot Figure 3.28(b) but with a different axis. This plot is used later in this chapter to help in choosing the optimum substrate size for an example.

Figure 3.28(c). Semilog plot for power dissipation versus convection coefficient with different ambient temperatures (with BP and HS condition)

Since  $\Delta T = Tjmax - Ta$ , so as the  $\Delta T$  increases, the convection coefficient decreases for same power dissipation. This  $\Delta T$  can be increased by using lower ambient temperatures. As seen in the above plots - despite employing heatsinks, for the case of 3.2KW power dissipation, 250°C maximum junction temperature, and ambient temperatures of 25°C, 50°C, 75°C, 100°C, 125°C; the convection coefficients required are 710, 1020, 1620, 3010, and 7600 W/m<sup>2</sup>K, respectively. Also for 2.5KW power dissipation and 200°C maximum junction temperature, and ambient temperatures of 25°C, 50°C, 75°C, 100°C; the convection coefficients required are 750, 1250, 2550, 7700 W/m<sup>2</sup>K, respectively. That is, as it reaches  $\Delta T$  of 125°C, convection coefficient values double. Hence for optimum functioning, it is best to maintain  $\Delta T > 125°$ C. This is observed in all cases in the above Figure 3.28(c). However as power dissipation increases (beyond 4KW), convection coefficient doubles much earlier. Then the  $\Delta T$  increases correspondingly. That range is not investigated in this thesis work.

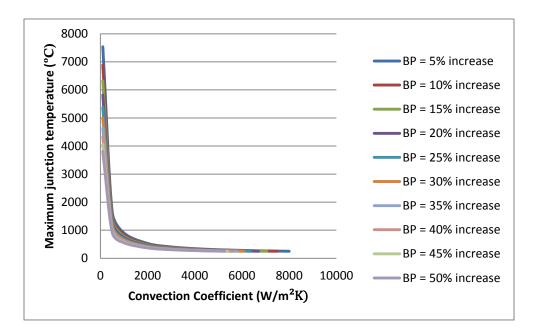

### 3.8 Study on varying baseplate size

Baseplate, as mention in Section 3.4, provides mechanical strength and balanced thermal distribution over the power substrate. As discussed in Section 3.4, copper metal is used for baseplate. Simulations are performed for a constant substrate size as well as for increase in size of baseplate from 5% to 50% without the heatsink.

Figures 3.29, 3.30, 3.31, 3.32, 3.33, and 3.34 are shown below to illustrate the variation of baseplate and its corresponding effect on other parameters.

• Parameters Ta = 100°C, Power dissipation = 1.6KW, 2.5KW, 4KW. Tj = 250°C

Figure 3.29. Baseplate size versus power dissipation and convection coefficient for Ta of 100°C and Tjmax of 250°C

• Parameters  $Ta = 100^{\circ}C$ , 125°C. Power dissipation = 1.6KW, 2.5KW. Tj = 250°C

Figure 3.30. Baseplate size versus power dissipation and convection coefficient for different ambient temperatures of 100°C, 125°C and Tjmax of 250°C. Two cases of ambient temperatures are plotted to show comparison

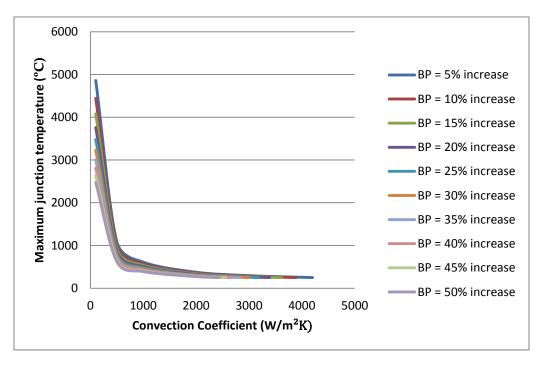

• Parameters  $Ta = 100^{\circ}C$ , Power dissipation = 2.5KW.

Figure 3.31. Convection coefficient versus maximum junction temperature for different baseplate sizes, and for 2.5KW power dissipation

Figure 3.32. Convection coefficient versus maximum junction temperature for different baseplate sizes, and for 1.6KW power dissipation

• Parameters  $Ta = 125^{\circ}C$ , Power dissipation = 2.5KW.

Parameters  $Ta = 100^{\circ}C$ , Power dissipation = 1.6KW.

•

Figure 3.33. Convection coefficient versus maximum junction temperature for different baseplate sizes, and for 2.5KW power dissipation

• Parameters  $Ta = 125^{\circ}C$ , Power dissipation = 1.6KW.

Figure 3.34. Convection coefficient versus maximum junction temperature for different baseplate sizes, and for 1.6KW power dissipation

As can be seen from Figures 3.31 to 3.34, Tjmax varies rapidly with increase in convection coefficient until 1000W/m<sup>2</sup>K is reached. After this, the plots take sharp turn and continue to behave almost constant (varying only by a little).

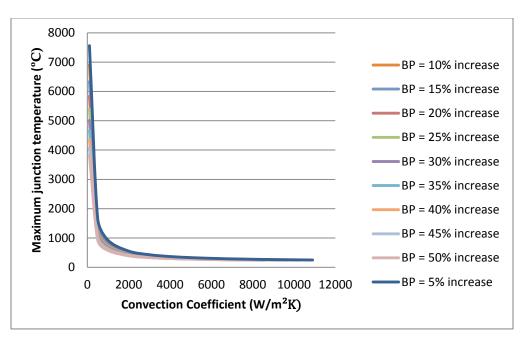

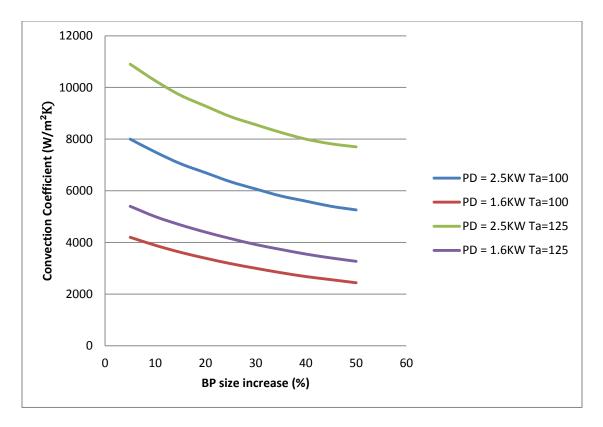

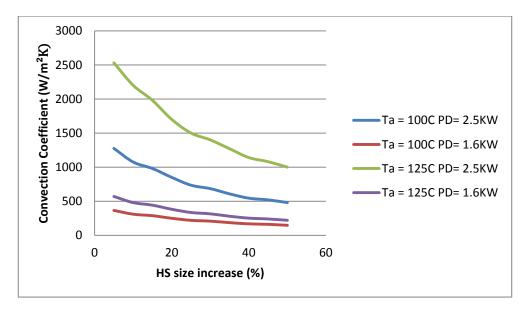

For Tjmax = 250°C, the convection coefficient versus baseplate percentage size increase is plotted in Figure 3.35 for various parameters of power dissipation of 2.5KW, 1.6KW and ambient temperature of 100°C, 125°C.

Figure 3.35. Baseplate size increase versus convection coefficient for 2.5KW and 1.6KW power dissipation, and 100°C and 125°C ambient temperatures

It is straight forward to see from the graph that the larger the baseplate the better would be the heat spreading, and hence, a better heat removal aid for the module provided the thickness of the baseplate remains constant.

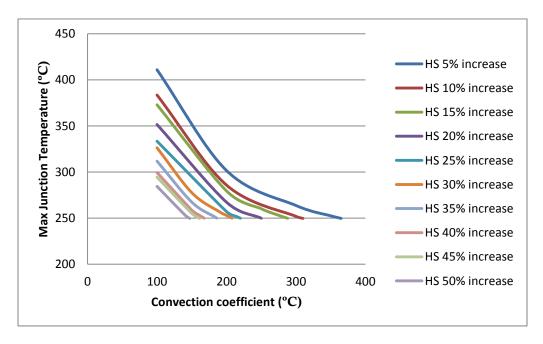

#### 3.9 Study on varying heat-sink size

As discussed in Section 3.5.2, 1050A Al alloy is chosen for the heatsink material. Simulations are performed for a constant substrate size; increase the size of both baseplate and heatsink - thus increasing the exposed surface area - from 5% to 50%. When size of the heatsink is increased, it may be possible to add a fin to the heatsink thus adding a thermal resistance in parallel.

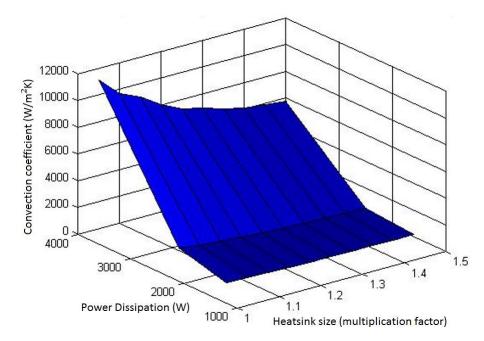

Plots in this section provide study on variation of the size of heatsink and its corresponding effect on other parameters. Figures 3.36 and 3.37 show the three dimensional plots.

• Parameters Ta = 100°C, Power dissipation = 1.6KW, 2.5KW, 4KW. Tj = 250°C

Figure 3.36. Heatsink size variation versus power dissipation and convection coefficient for ambient temperature of 100°C and Tjmax of 250°C

• Parameters Ta = 100°C, 125°C. Power dissipation = 1.6KW, 2.5KW. Tj = 250°C

Figure 3.37. Heatsink size variation versus power dissipation and convection coefficient for ambient temperatures 100°C, 125°C (to show the comparison) and Tjmax 250°C

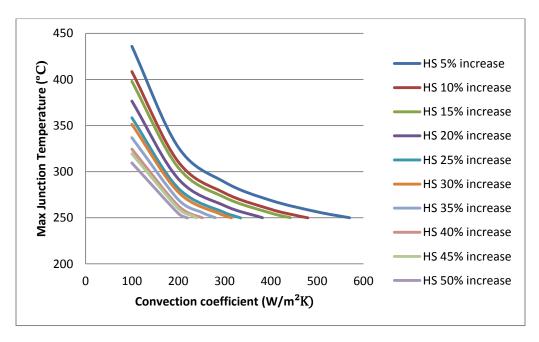

Figure 3.38. Convection coefficient versus maximum junction temperature for different heatsink sizes for 2.5KW power dissipation

• Parameters  $Ta = 100^{\circ}C$ , Power dissipation = 1.6KW.

Parameters  $Ta = 100^{\circ}C$ , Power dissipation = 2.5KW.

•

Figure 3.39. Convection coefficient versus maximum junction temperature for different heatsink sizes for 1.6KW power dissipation

• Parameters Ta = 125°C, Power dissipation = 2.5KW.

Figure 3.40. Convection coefficient versus maximum junction temperature for different heatsink sizes for 2.5KW power dissipation

• Parameters Ta = 125°C, Power dissipation = 1.6KW.

Figure 3.41. Convection coefficient versus maximum junction temperature for different heatsink sizes for 1.6KW power dissipation

• To obtain Tjmax = 250°C, the convection coefficient versus heatsink size increase for various parameters is given in Figure 3.42.

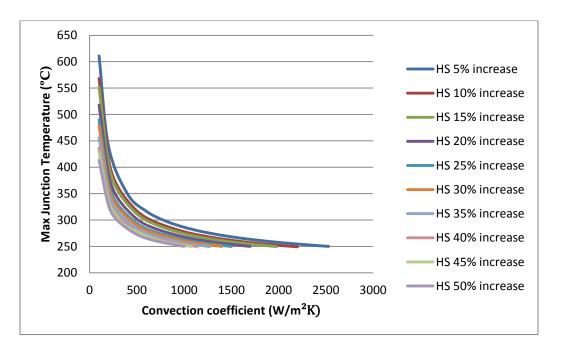

Figure 3.42. Convection coefficient versus heatsink size increase

As can be seen in Figure 3.42, for power dissipation=2.5KW and Ta=125°C, the change in convection coefficient is from 2500W/m<sup>2</sup>K to 1000W/m<sup>2</sup>K, whereas, for power dissipation=1.6KW and Ta=100°C, the change in convection coefficient is only from around 360 W/m<sup>2</sup>K to 150 W/m<sup>2</sup>K. That is, there is a significant change in convection coefficient when increasing the size of heatsink for higher power (dissipation) modules than for low power dissipation modules.

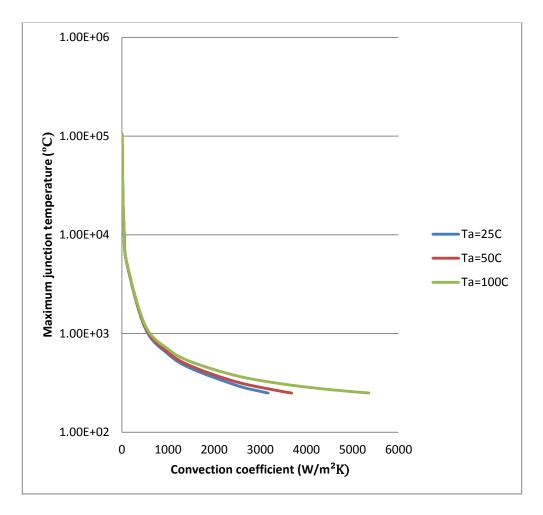

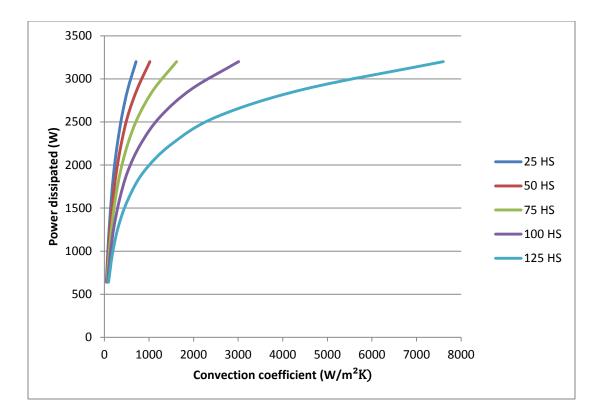

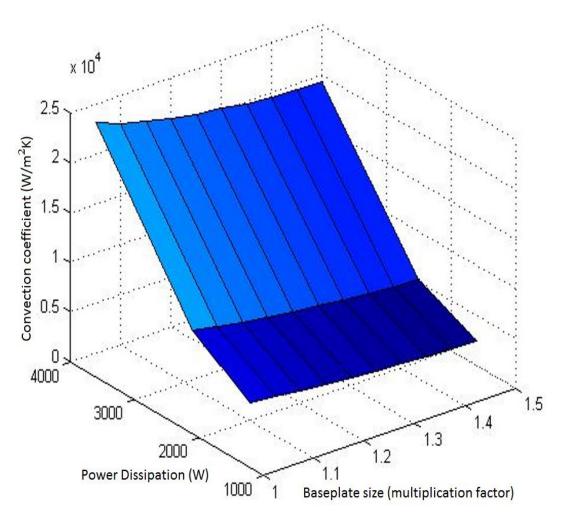

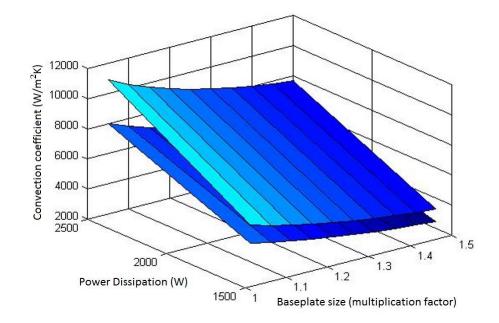

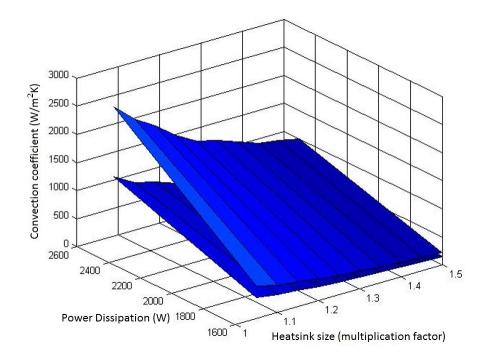

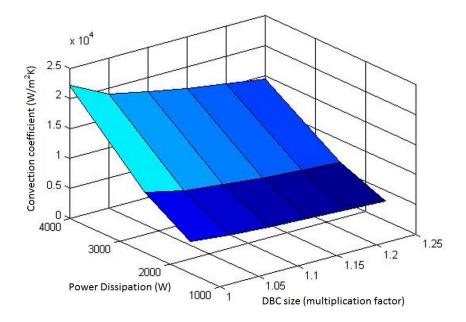

#### 3.10 Study on varying substrate (DBC) size

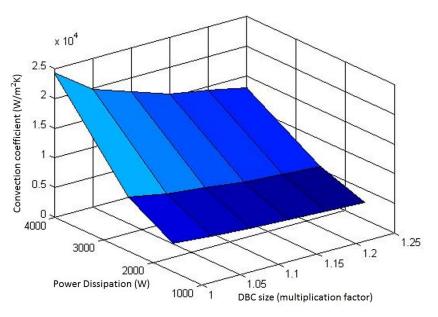

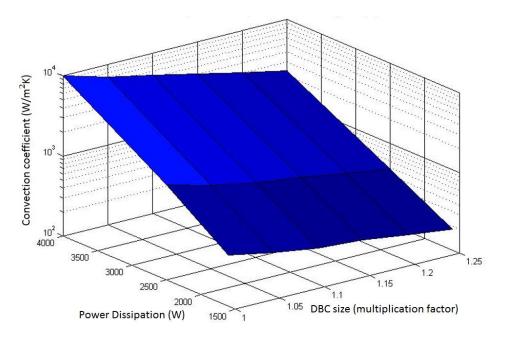

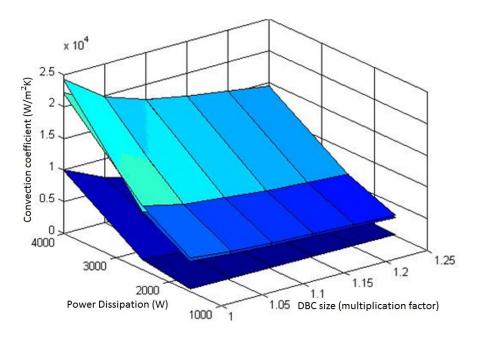

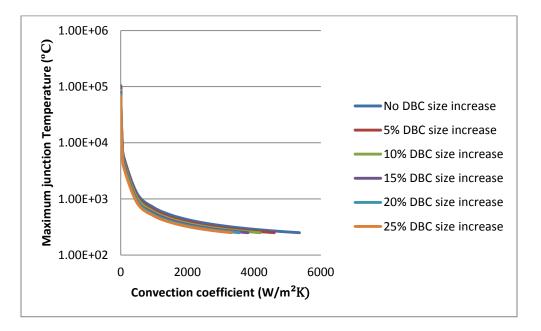

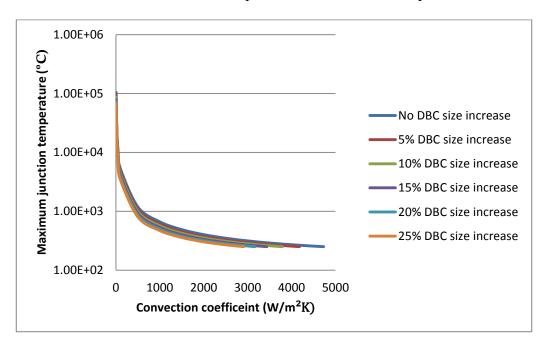

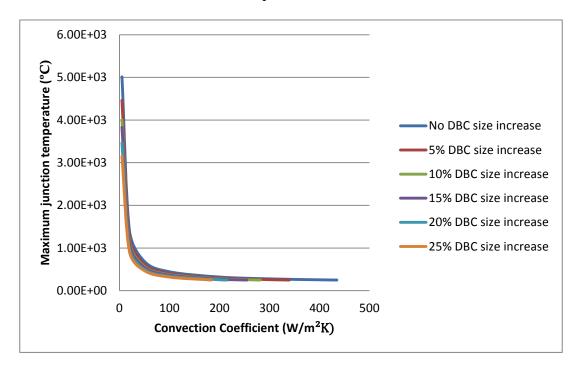

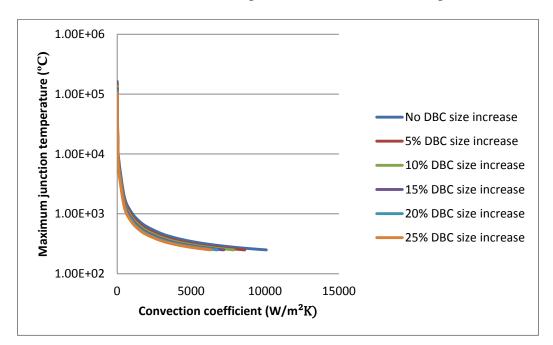

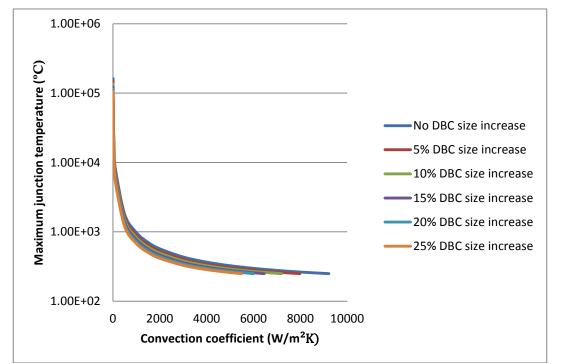

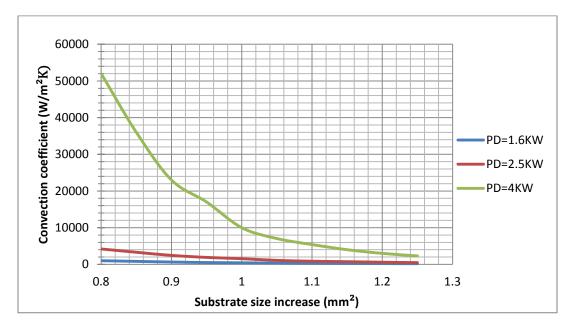

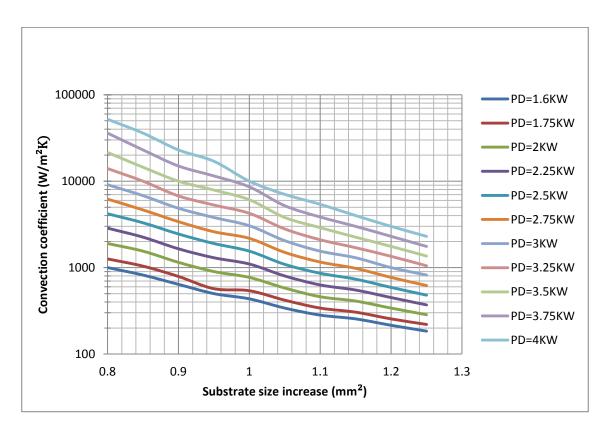

Increasing the substrate size increases the surface area and helps in better heat spreading. Also, the spacing between the dies increases thus reducing thermal coupling in the layout. So theoretically, increasing the substrate size would need a lower convection coefficient for the same Tj according to Newton's cooling law. Figures 3.44, 3.45, 3.46, 3.47, 3.48, 3.49, 3.50, 3.51, 3.52, and 3.53 show the effects of increasing the substrate size on other parameters.

• Parameters Ta = 100°C, Power dissipation = 1.6KW, 2.5KW, 4KW. Tjmax = 250°C, without baseplate condition.

Figure 3.43. Convection coefficient versus power dissipation and substrate size for Tjmax=250°C (no BP or HS condition)

• Parameters Ta = 100°C, Power dissipation = 1.6KW, 2.5KW, 4KW. Tjmax = 250°C, with baseplate condition

Figure 3.44. Convection coefficient versus power dissipation and DBC size for Tjmax=250°C (with BP condition)

• Parameters Ta = 100°C, Power dissipation = 1.6KW, 2.5KW, 4KW. Tjmax = 250°C, with heatsink condition

Figure 3.45. Convection coefficient versus power dissipation and DBC size for Tjmax=250°C; (with HS condition)

• Parameters Ta = 100°C, Power dissipation = 1.6KW, 2.5KW, 4KW. Tjmax = 250°C

Figure 3.46. Convection coefficient versus power dissipation and DBC size for Tjmax=250°C; all three cases

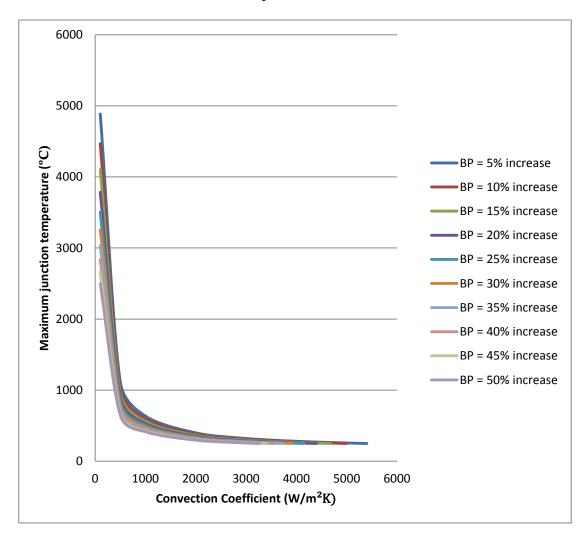

• Parameters: Ta = 100°C, Power dissipation = 1.6KW, without baseplate or heat-sink condition

Figure 3.47. Convection coefficient versus maximum junction temperature for various DBC sizes, Power dissipation 1.6KW (without BP or HS condition)

• Parameters:  $Ta = 100^{\circ}C$ , Power dissipation = 1.6KW, with baseplate but no heatsink

Figure 3.48. Convection coefficient versus maximum junction temperature for various DBC sizes Power dissipation 1.6KW (with BP condition)

• Parameters:  $Ta = 100^{\circ}C$ , Power dissipation = 1.6KW with heatsink

Figure 3.49. Convection coefficient versus maximum junction temperature for various DBC sizes Power dissipation 1.6KW (with HS condition)

• Parameters: Ta = 100°C, Power dissipation = 2.5KW without baseplate and heatsink

Figure 3.50. Convection coefficient versus maximum junction temperature for various DBC sizes Power dissipation 2.5KW (without BP or HS condition)

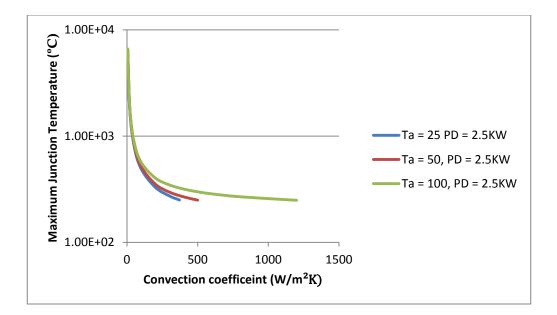

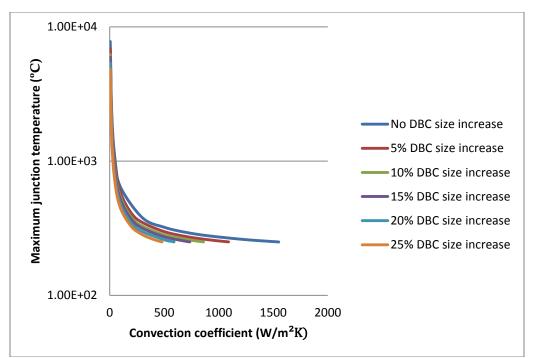

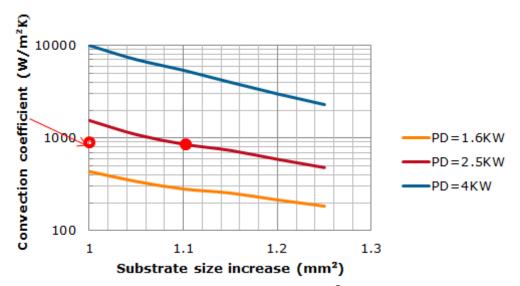

• Parameters: Ta =100°C, Power dissipation = 2.5KW, with baseplate and without heatsink