# Interleaved Buck Converter Based Shunt Active Power Filter with Shoot-through elimination for Power Quality Improvement

Dissertation submitted in partial fulfillment

of the requirements of the degree of

#### **Doctor of Philosophy**

in

#### Electrical Engineering

by

#### Ranjeeta Patel

(Roll Number: 512EE8011)

based on research carried out

under the supervision of

Prof. Anup Kumar Panda

January, 2017

Department of Electrical Engineering National Institute of Technology Rourkela

January 4, 2017

#### **Certificate of Examination**

Roll Number: 512EE8011

Name: Ranjeeta Patel

Title of Dissertation: Interleaved Buck Converter Based Shunt Active Power Filter with Shoot-through elimination for Power Quality Improvement

We the below signed, after checking the dissertation mentioned above and the official record book (s) of the student, hereby state our approval of the dissertation submitted in partial fulfillment of the requirements of the degree of *Doctor of Philosophy* in *Electrical Engineering* at *National Institute of Technology Rourkela*. We are satisfied with the volume, quality, correctness, and originality of the work.

-----Anup Kumar Panda

Principal Supervisor

------Sulta day Mahan

Sukadev Meher Member, DSC

Sanjeeb Mohanty Member, DSC

\_\_\_\_\_

Umesh Chandra Pati Member, DSC

Bansidhar Majhi Chairperson, DSC Debapriya Das External Examiner

Jitendriya Kumar Satpathy Head of the Department

**Prof. Anup Kumar Panda** Professor

January 4, 2017

#### Supervisor's Certificate

This is to certify that the work presented in this dissertation entitled *Interleaved Buck Converter Based Shunt Active Power Filter with Shoot-through elimination for Power Quality Improvement* by *Ranjeeta Patel*, Roll Number 512EE8011, is a record of original research carried out by her under my supervision and guidance in partial fulfillment of the requirements of the degree of *Doctor of Philosophy* in *Electrical Engineering*. Neither this dissertation nor any part of it has been submitted earlier for any degree or diploma to any institute or university in India or abroad.

-----

Anup Kumar Panda Professor

# Dedicated

to

## my son

# Zinith Patel

... Ranjeeta Patel

## **Declaration of Originality**

I, *Ranjeeta Patel*, Roll Number *512EE8011* hereby declare that this dissertation entitled *Interleaved Buck Converter Based Shunt Active Power Filter with Shoot-through elimination for Power Quality Improvement* presents my original work carried out as a doctoral student of NIT Rourkela and, to the best of my knowledge, contains no material previously published or written by another person, nor any material presented by me for the award of any other degree or diploma of NIT Rourkela or any other institution. Any contribution made to this research by others, with whom I have worked at NIT Rourkela or elsewhere, is explicitly acknowledged in the dissertation. Works of other authors cited in this dissertation have been duly acknowledged under the sections "Reference" "Bibliography". I have also submitted my original research records to the scrutiny committee for evaluation of my dissertation.

I am fully aware that in case of any non-compliance detected in future, the Senate of NIT Rourkela may withdraw the degree awarded to me on the basis of the present dissertation.

January 4, 2017 NIT Rourkela

Ranjeeta Patel

## Acknowledgment

I would like to express my most sincere gratitude and appreciation to my esteemed supervisor, **Prof. Anup Kumar Panda**, for his constant support, guidance and suggestion throughout the studies and research. It has been an honour to work under him, whose expertise and discernment was the key for the completion of this dissertation

I am grateful to the past Director **Prof. S. K. Sarangi** and present Director **Prof. Animesh Biswas**, NIT Rourkela for his kind support and concern regarding my academic requirements. I would like to give special thanks to **Prof B. Majhi**, Dean Academic, who graciously agreed to serve as my Doctoral Scrutiny Committee chairman. I am also very much grateful to the Doctoral Scrutiny Members **Prof. S. Meher**, **Prof. S. Mohanty** and **Prof. U. C. Pati** for their valuable suggestion during the research period.

I am very much thankful to present Head of the Department, **Prof. J. K. Satpathy** and past Head of the Department, **Prof. Anup Kumar Panda** for providing me with all the official and laboratory facilities.

I would also like to thank my senior colleagues Dr. S. Mikkili and Dr. T. Ramesh for the wonderful company and technical support. Also I am thankful to my friends, Mr. Nishant Patnaik, Mr. Ashish Kumar Dash, Mr. S. Shiva Kumar, Mr. Pratap Mohanty, Mr. Joseph Sanam, Mr. Mrutyunjay Mangaraj, Mr. Trilochan Penthia, for extending their personal support.

This section would remain incomplete if I don't thank the lab assistant **Mr. Rabindra Kumar Nayak**, without him the research work would not have been completed.

My heartfelt thanks to **Silicon Institute of Technology, Sambalpur** for allowing me to pursue Ph. D studies and gives a sense of happiness to be associated with National Institute of Technology Rourkela.

I wish to thank my spouse **Mr. Susanta Kumar Patel** for sharing all the good and bad moments and for his love, sacrifice and understanding during this course.

This thesis is dedicated to my beloved son **Zinith.** I love him more than I express.

With my deepest love, I would be grateful to my beloved family members for their positive encouragement that they showered on me throughout this research work.

January 4, 2017 NIT Rourkela *Ranjeeta Patel* Roll Number: 512EE8011

## Abstract

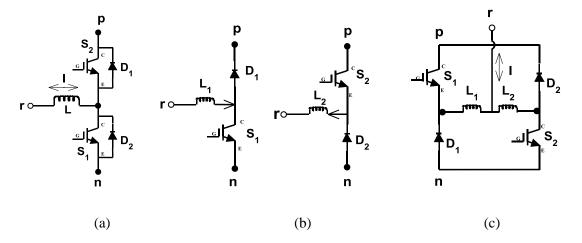

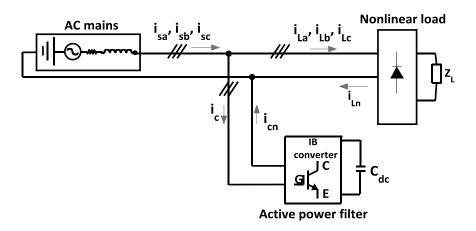

The "shoot-through" phenomenon defined as the rush of current that occurs while both the devices are ON at the same time of a particular limb is one of the most perilous failure modes encountered in conventional inverter circuits of active power filter (APF). Shoot-through phenomenon has few distinct disadvantages like; it introduces typical ringing, increases temperature rise in power switches, causes higher Electromagnetic Interference (EMI) and reduces the efficiency of the circuit. To avert the "shoot-through", dead time control could be added, but it deteriorates the harmonic compensation level. This dissertation presents active power filters (APFs) based on interleaved buck (IB) converter. Compared to traditional shunt active power filters, the presented IB APFs have enhanced reliability with no shoot-through phenomenon.

The instantaneous active and reactive power (p-q) scheme and instantaneous active and reactive current component  $(i_d-i_q)$  control scheme has been implemented to mitigate the source current harmonics. Type-1 and Type-2 fuzzy logic controller with different membership functions (MFs) viz. Triangular, Trapezoidal and Gaussian have been implemented for the optimal harmonic compensation by controlling the dc-link voltage and minimizing the undesirable losses occurred inside the APF. Additionally, the adaptive hysteresis band current controller (AHBCC) is being implemented to get the nearly constant switching frequency. The performance of the control strategies and controllers for the presented IB APF topologies has been evaluated in terms of harmonic mitigation and dc-link voltage regulation under sinusoidal, unbalanced sinusoidal and non-sinusoidal voltage source condition.

This dissertation is concerned with the different topologies of 3-phase 4-wire IB APFs viz. split capacitor (2C) topology, 4-leg (4L) topology, transformer based full-bridge IB APF or single capacitor based FB IB APF (1C 3 FB IB APF) and full-bridge IB APF (FB IB APF) for low to medium power application. Moreover, APF topology is now being

expanded to multilevel VSIs for high power application. Thanks to flexible modular design, transformerless connection, extended voltage and power output, less maintenance and higher fault tolerance, the cascade inverters are good candidates for active power filters with the utility of high power application. The cascaded FB IB APF is modelled with no shoot-through phenomenon by using multicarrier phase shifted PWM scheme.

Extensive simulations have been carried out in the MATLAB / Simulink environment and also verified in the OPAL-RT LAB using OP5142-Spartan 3 FPGA to support the feasibility of presented IB APF topologies, control strategies and controllers during steady and dynamic condition. The performance shows that IB-APF topologies bring the THD of the source current well below 5% adhering to IEEE-519 standard. A comparison has also been made, based on SDP (switch device power) between the IB-APF topologies.

Keywords: Shoot-through phenomenon; IB APF; p-q and  $i_d$ - $i_q$  control strategy; Fuzzy1, Fuzzy2, SDP rating, OPAL-RT

## Contents

| Certificate of Examination | ii     |

|----------------------------|--------|

| Supervisor's Certificate   | iii    |

| Dedication                 | iv     |

| Declaration of Originality | v      |

| Acknowledgement            | vi     |

| Abstract                   | viii   |

| List of Figures            | XV     |

| List of Tables             | xxviii |

| 1 | Int | roduction                                                            | 1  |

|---|-----|----------------------------------------------------------------------|----|

|   | 1.1 | Research Background.                                                 | 3  |

|   | 1.2 | Electrical Power System Quality.                                     | 3  |

|   |     | 1.2.1 Harmonics.                                                     | 6  |

|   |     | 1.2.2 Harmonic Sources.                                              | 7  |

|   |     | 1.2.3 Effects of Harmonic Distortion.                                | 8  |

|   |     | 1.2.4 Standard of Harmonics                                          | 9  |

|   | 1.3 | Devices for controlling Harmonic Distortion                          | 10 |

|   |     | 1.3.1 Passive Power Filter.                                          | 10 |

|   |     | 1.3.2 Active Power Filter                                            | 12 |

|   | 1.4 | Shunt Active Power Filter configurations.                            | 16 |

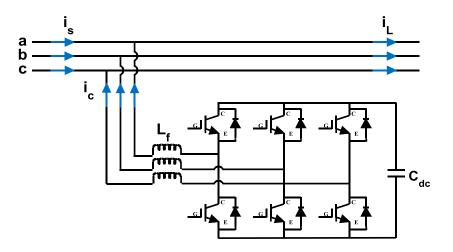

|   |     | 1.4.1 Three-phase four-wire capacitor midpoint APF (2C APF) topology | 17 |

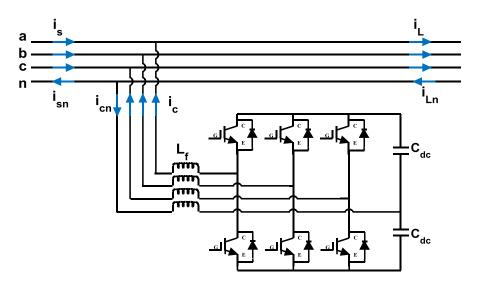

|   |     | 1.4.2 Three-phase 4- leg APF (4L APF) topology                       | 18 |

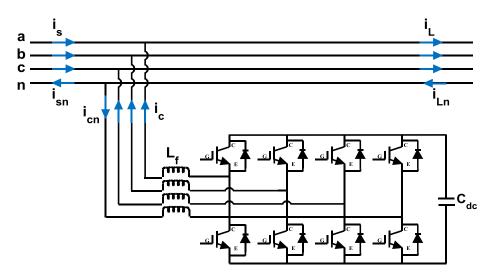

|   |     | 1.4.3 1-C, 3 H-Bridge/Full-Bridge APF topology                       | 19 |

|   |     | 1.4.4 Three-phase four-wire H-bridge/Full-Bridge APF topology        | 20 |

|   | 1.5 Multilevel Inverter based Shunt Active Power Filter                               | 20 |

|---|---------------------------------------------------------------------------------------|----|

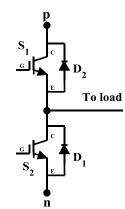

|   | 1.6 Shoot-through phenomenon                                                          | 22 |

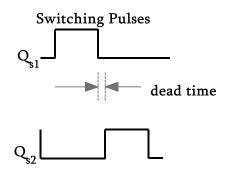

|   | 1.6.1 Dead time                                                                       | 23 |

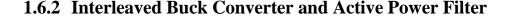

|   | 1.6.2 Interleaved Buck Converter and Active Power Filter                              | 24 |

|   | 1.7 Control Schemes of APF                                                            | 25 |

|   | 1.7.1 Conventional PI controller for dc-link voltage regulation                       | 26 |

|   | 1.7.2 Implementation of Fuzzy controller for dc-link voltage regulation               | 26 |

|   | 1.8 Research Motivations and objectives                                               | 27 |

|   | 1.8.1 Motivations                                                                     | 27 |

|   | 1.8.2 Objectives                                                                      | 29 |

|   | 1.9 Dissertation Layout                                                               | 30 |

| 2 | Performance Analysis of Interleaved Buck Shunt Active Power Filter with               | 33 |

|   | p-q and i <sub>d</sub> -i <sub>q</sub> control schemes                                |    |

|   | 2.1 Introduction                                                                      | 33 |

|   | 2.2 Half Bridge Interleaved Buck converter based Active Power Filter                  | 34 |

|   | 2.2.1 Half Bridge Interleaved Buck converter.                                         | 35 |

|   | 2.2.2 Three-phase four-wire Interleaved Buck converter based Active Power             | 07 |

|   | Filter                                                                                | 37 |

|   | 2.3 Control Schemes for three-phase four-wire Interleaved Buick Active Power          | 40 |

|   | Filter                                                                                | 40 |

|   | 2.3.1 Instantaneous Active and Reactive Power $(p - q)$ Control Scheme                | 41 |

|   | 2.3.2 Instantaneous Active and Reactive Current Component $(i_d - i_q)$               |    |

|   | Control Scheme.                                                                       | 43 |

|   | 2.4 DC-link voltage regulator using PI controller                                     | 47 |

|   | 2.5 Conventional and Adaptive Hysteresis Band Current Controller                      | 49 |

|   | 2.6 Analysis Tools                                                                    | 51 |

|   | 2.7 System performance of p-q and $i_d$ - $i_q$ control strategies with PI controller |    |

|   | using Hysteresis PWM                                                                  | 55 |

|   | 2.7.1 Steady State performance discussion with MATLAB and OPAL-RT                     |    |

|   | Results                                                                               | 55 |

|   | 2.7.2 Dynamic State performance discussion with MATLAB and OPAL-RT                    |    |

|   |     | Results                                                                    | 66  |

|---|-----|----------------------------------------------------------------------------|-----|

|   | 2.8 | Summary                                                                    | 73  |

| 3 | Per | formance Analysis of Interleaved Buck Shunt Active Power Filter with       | 75  |

|   | Тур | pe-1 and Type-2 Fuzzy Logic controller                                     |     |

|   | 3.1 | Introduction                                                               | 75  |

|   | 3.2 | Type-1 Fuzzy Logic controller (T1FLC)                                      | 76  |

|   |     | 3.2.1 Fuzzification                                                        | 78  |

|   |     | 3.2.2 Fuzzy Inference System                                               | 78  |

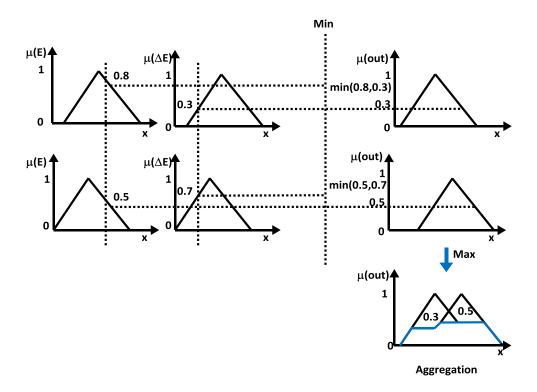

|   |     | 3.2.2.1 Mamdani max-min Inferencing Composition method                     | 80  |

|   |     | 3.2.2.2 Mamdani max-prod Inferencing Composition method                    | 80  |

|   |     | 3.2.2.3 Aggregation                                                        | 81  |

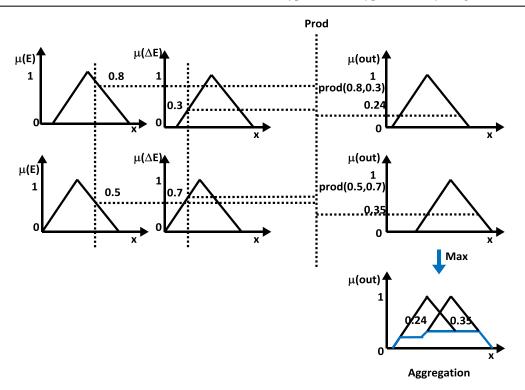

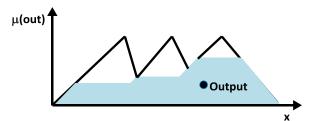

|   |     | 3.2.3 Defuzzification.                                                     | 81  |

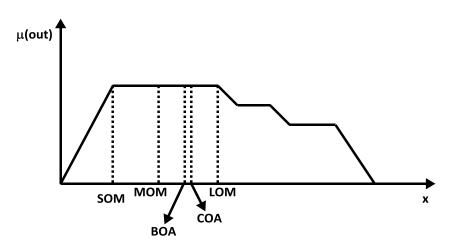

|   |     | 3.2.3.1 Center of Area method                                              | 82  |

|   |     | 3.2.3.2 Bisector of Area method                                            | 83  |

|   |     | 3.2.3.3 Mean, Smallest and Largest of Maximum methods                      | 83  |

|   |     | 3.2.4 Design of Control Rules.                                             | 84  |

|   |     | 3.2.4.1 Trapezoidal Membership Function                                    | 84  |

|   |     | 3.2.4.2 Triangular Membership Function                                     | 86  |

|   |     | 3.2.4.3 Gaussian Membership Function                                       | 87  |

|   |     | 3.2.4.4 Rule Base                                                          | 88  |

|   | 3.3 | Type-2 Fuzzy Logic Controller                                              | 91  |

|   |     | 3.3.1 Structure of Type-2 Fuzzy Logic Controller (T2FLC)                   | 92  |

|   |     | 3.3.2 Fuzzy Inference System of Type 2 FLC                                 | 95  |

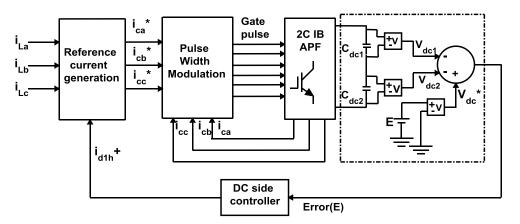

|   | 3.4 | 2C IB APF using FLC based $i_d$ - $i_q$ control strategy                   | 98  |

|   | 3.5 | System performance of Type-1 FLC based $i_d$ - $i_q$ control strategy with |     |

|   |     | different fuzzy MFs.                                                       | 101 |

|   |     | 3.5.1 Results Discussion.                                                  | 107 |

|   | 3.6 | System performance of Type-2 FLC based $i_d$ - $i_q$ control strategy with |     |

|   |     | different fuzzy MFs                                                        | 108 |

|   |     | 3.6.1 Results Discussion.                                                  | 114 |

|   | 3.7 | Summary                                                                    | 116 |

| 4 | Per | formance Analysis of 4 Leg IB APF, 1C 3FB IB APF and FB IB APF            | 118 |

|---|-----|---------------------------------------------------------------------------|-----|

|   | top | ologies for 3-phase 4-wire system                                         |     |

|   | 4.1 | Introduction                                                              | 118 |

|   | 4.2 | Split Capacitor Interleaved Buck Active Power Filter (2C IB APF)          | 119 |

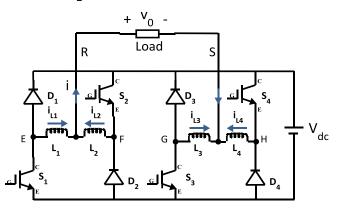

|   | 4.3 | Four-Leg Interleaved Buck Active Power Filter (4-L IB APF)                | 121 |

|   | 4.4 | Full-bridge Interleaved Buck Converter based Active Power Filter          | 123 |

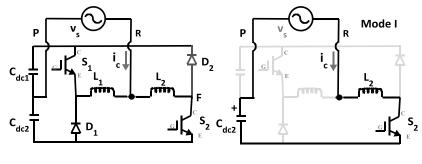

|   |     | 4.4.1 Working modes of Full-bridge Interleaved Buck Active Power Filter   | 124 |

|   | 4.5 | Single Capacitor three Full-Bridge Interleaved Buck Active Power Filter   |     |

|   |     | (1C 3FB IB APF)                                                           | 126 |

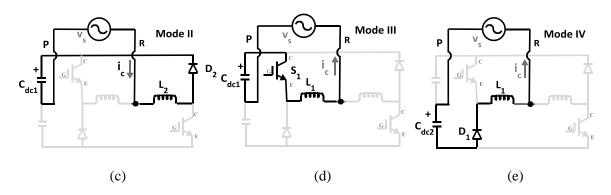

|   | 4.6 | Three-phase four-wire Full-Bridge Interleaved Buck Active Power Filter    |     |

|   |     | (FB IB APF) topology                                                      | 129 |

|   | 4.7 | System Performance of 2C IB APF, 4-Leg IB APF, 1C 3FB IB APF and FB       |     |

|   |     | IB APF topologies by $i_d$ - $i_q$ control strategy with PI and T1FLC for |     |

|   |     | sinusoidal, unbalanced sinusoidal and non-sinusoidal voltage source       |     |

|   |     | condition                                                                 | 132 |

|   |     | 4.7.1 Results Discussion.                                                 | 148 |

|   | 4.8 | SDP (Switch Device Power) of IB APFs.                                     | 152 |

|   | 4.9 | Summary                                                                   | 153 |

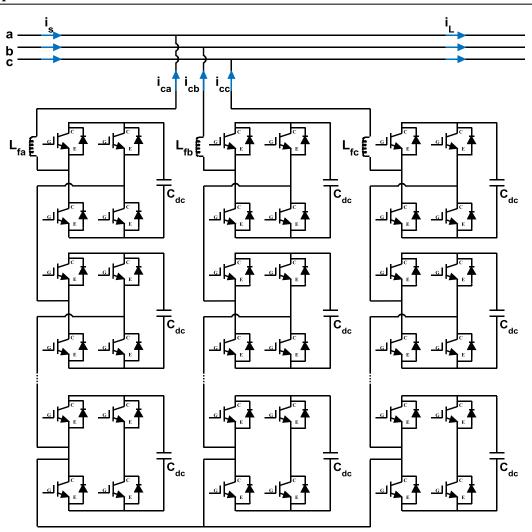

| 5 | Per | formance Analysis of Cascaded Full-Bridge Interleaved Buck Shunt          | 155 |

|   | Act | ive Power Filter                                                          |     |

|   | 5.1 | Introduction                                                              | 155 |

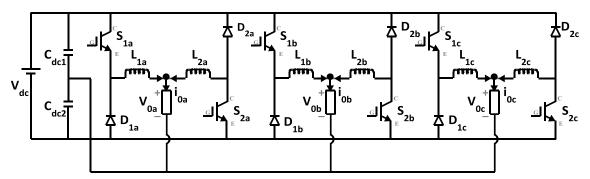

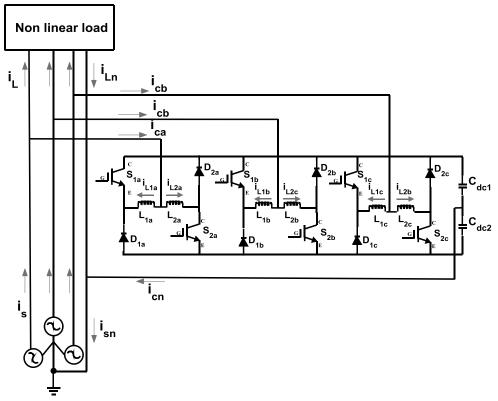

|   | 5.2 | Cascaded Full-Bridge Interleaved Buck Active Power converter              | 156 |

|   | 5.3 | Control Analysis of Cascaded Full-Bridge Interleaved Buck converter       | 158 |

|   |     | 5.3.1 Space Vector Modulation (SVM)                                       | 159 |

|   |     | 5.3.2 Selective Harmonic Elimination (SHE)                                | 159 |

|   |     | 5.3.3 Multicarrier based Pulse width Modulation (PWM)                     | 160 |

|   |     | 5.3.3.1 Phase Shifted PWM scheme.                                         | 160 |

|   |     | 5.3.3.2 Level Shifted PWM scheme                                          | 161 |

|   | 5.4 | Cascaded Full-Bridge Interleaved Buck Converter based Active Power        |     |

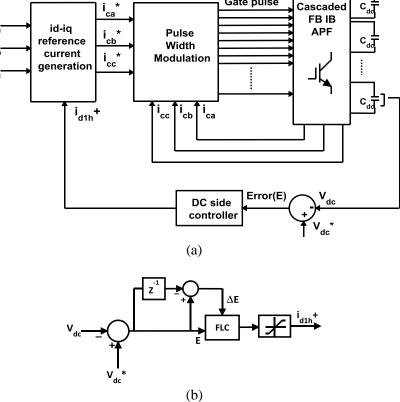

|   |     | Filter with i <sub>d</sub> -i <sub>q</sub> control strategy               | 164 |

|   | 5.5 System performance of Cascaded Full-Bridge Interleaved Buck converter | 166 |

|---|---------------------------------------------------------------------------|-----|

|   | 5.6 System performance of Cascaded Full-Bridge Interleaved Buck Converter |     |

|   | based Active Power Filter                                                 | 171 |

|   | 5.7 Results Discussion                                                    | 172 |

|   | 5.8 Summary                                                               | 173 |

|   |                                                                           |     |

| 6 | Major Contributions, General Conclusions and Scope for Future Research    | 174 |

|   | 6.1 Major Contribution                                                    | 174 |

|   | 6.2 General Conclusion                                                    | 175 |

|   | 6.3 Scope for Future Research                                             | 176 |

|   |                                                                           |     |

#### Bibliography

#### Dissemination

## **List of Figures**

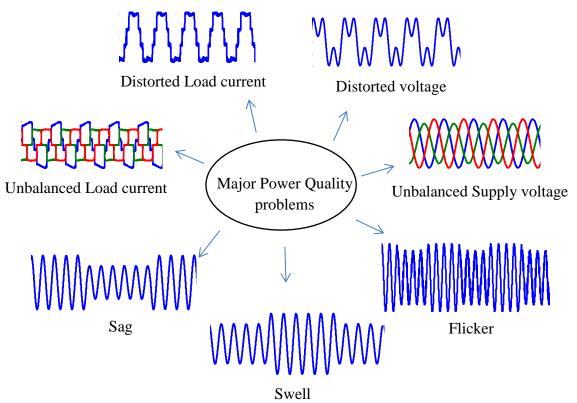

| 1.1  | Major power quality problems.                                                                    | 4  |

|------|--------------------------------------------------------------------------------------------------|----|

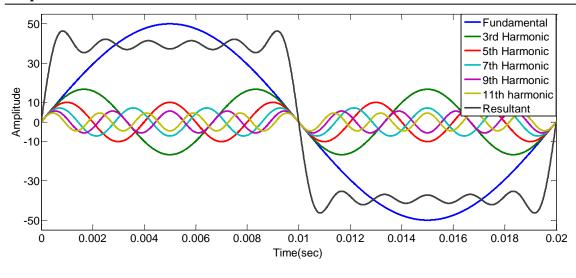

| 1.2  | Harmonics                                                                                        | 7  |

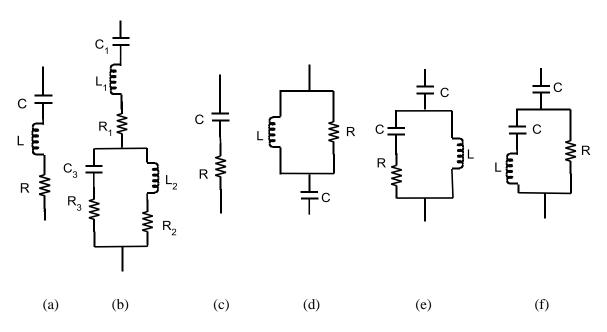

| 1.3  | Common Shunt passive filter configurations (a) Single tuned (b) Double                           |    |

|      | tuned (c) $1^{st}$ order high pass filter (d) $2^{nd}$ order high pass filter (e) $3^{rd}$ order |    |

|      | high pass filter (f) C-type filter                                                               | 11 |

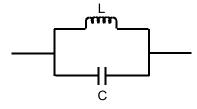

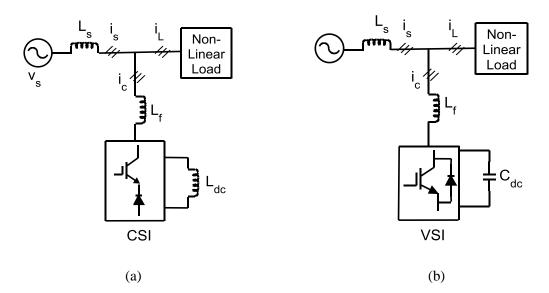

| 1.4  | (a) Series passive filter configuration (b) Low pass broadband filter                            | 11 |

| 1.5  | (a) Current source inverter (CSI) based APF (b) Voltage source inverter                          |    |

|      | (VSI) based APF                                                                                  | 13 |

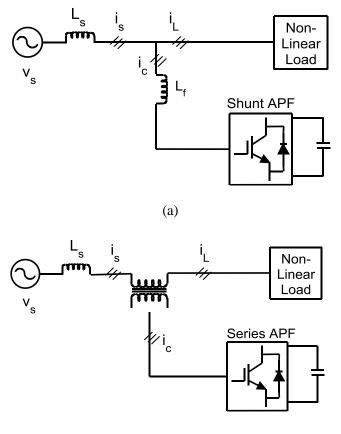

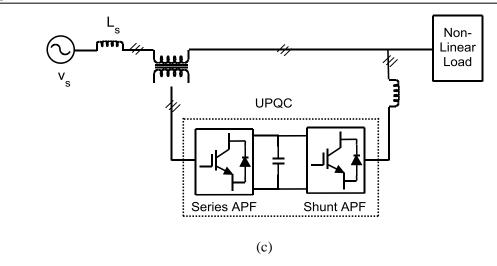

| 1.6  | (a) Shunt active power filter (b) Series active power filter (c) Unified power                   |    |

|      | quality conditioner (UPQC).                                                                      | 14 |

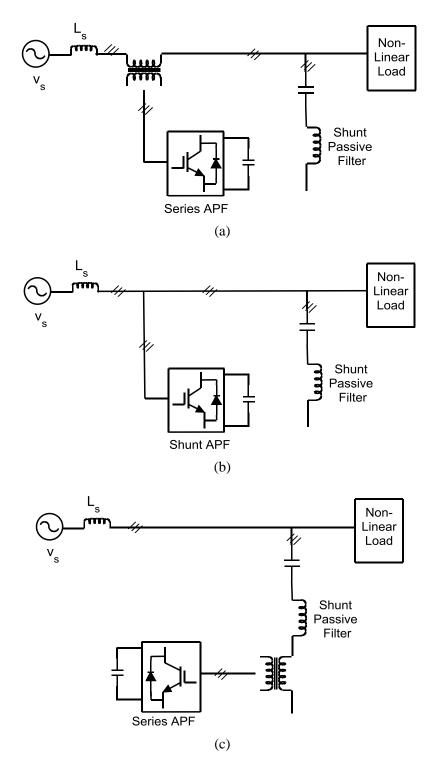

| 1.7  | Hybrid filters (a) Series active power filter and shunt passive filter (b) Shunt                 |    |

|      | active power filter and shunt passive filter (c) Series active power filter and                  |    |

|      | shunt passive filter                                                                             | 15 |

| 1.8  | Three-phase three-wire shunt active power filter                                                 | 16 |

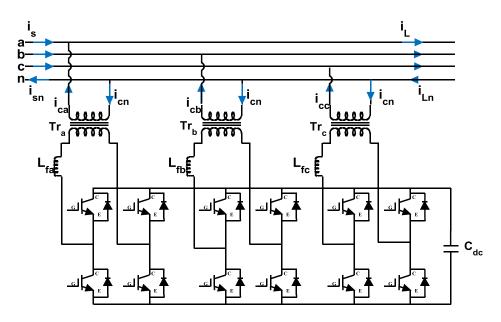

| 1.9  | Three-phase four-wire capacitor midpoint shunt active power filter                               | 18 |

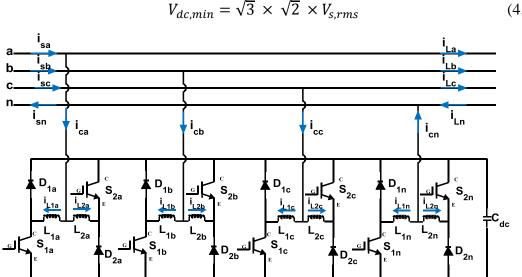

| 1.10 | Three-phase four-leg shunt active power filter                                                   | 18 |

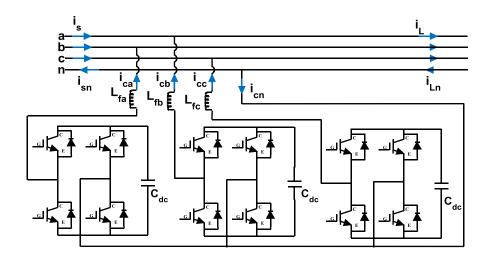

| 1.11 | Three-phase four-wire 3 H-bridge/Full-bridge active power filter with single                     |    |

|      | dc-link capacitor                                                                                | 19 |

| 1.12 | Three-phase four-wire full-bridge active power filter                                            | 20 |

| 1.13 | Multilevel cascaded H-bridge/Full-bridge active power filter.                                    | 21 |

| 1.14 | Generic phase leg of voltage source inverter.                                                    | 22 |

| 1.15 | Dead time in the normal gate switching signal                                                    | 23 |

| 1.16 | (a) Conventional inverter phase (b) Equivalent circuit cells of conventional                     |    |

|      | inverter phase limb (c) Interleaved buck bridge cell                                             | 24 |

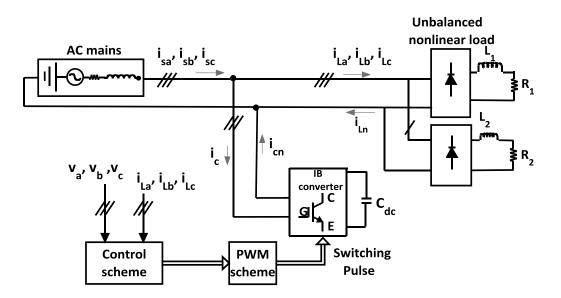

| 2.1  | Basic configuration of Shunt IB APF system.                                                      | 34 |

| 2.2  | (a) Conventional half-bridge converter (b) Half bridge interleaved buck                          |    |

|      | converter                                                                                                          | 35 |

|------|--------------------------------------------------------------------------------------------------------------------|----|

| 2.3  | Three-phase half bridge interleaved buck converter                                                                 | 36 |

| 2.4  | Single phase half bridge interleaved buck converter based APF and its                                              |    |

|      | working modes                                                                                                      | 38 |

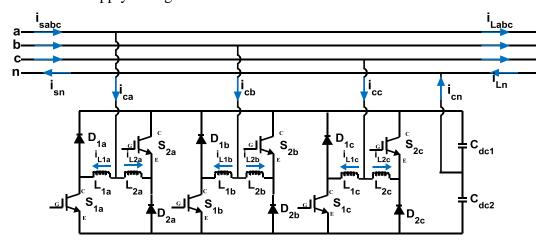

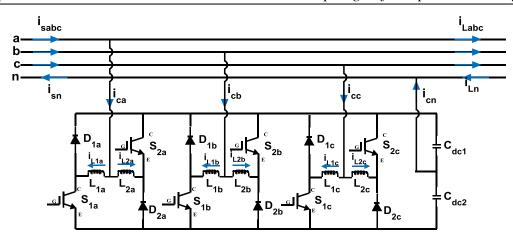

| 2.5  | 3-phase 4-wire split capacitor interleaved buck active power filter                                                | 39 |

| 2.6  | Basic harmonic compensation principle of interleaved buck shunt active                                             |    |

|      | power filters                                                                                                      | 40 |

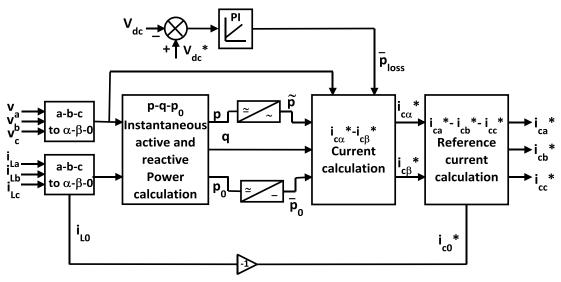

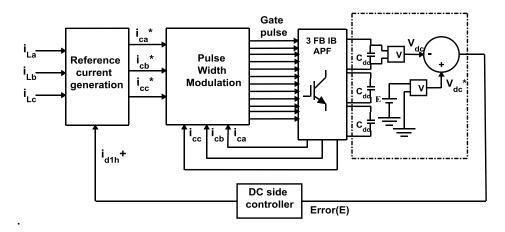

| 2.7  | Control block diagram of p-q control strategy used for 2C IB APF                                                   | 42 |

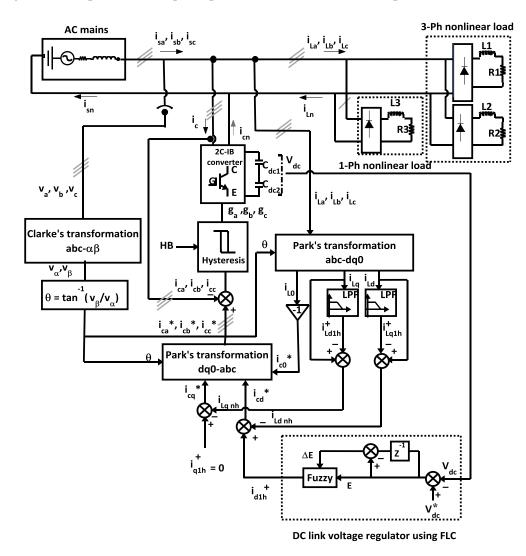

| 2.8  | Control block diagram of $i_d$ - $i_q$ control strategy used for 2C IB APF                                         | 43 |

| 2.9  | Instantaneous voltage and current vectors                                                                          | 44 |

| 2.10 | Harmonic compensation scheme of 2C IB APF using $i_d\mathchar`-i_q$ control strategy                               | 46 |

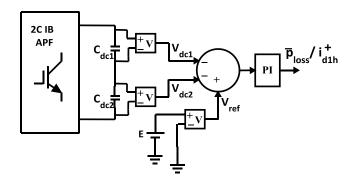

| 2.11 | DC-link voltage controller block diagram using PI controller                                                       | 48 |

| 2.12 | Hysteresis band current controller PWM scheme for the generation of                                                |    |

|      | switching pulses                                                                                                   | 50 |

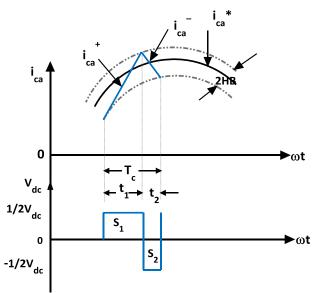

| 2.13 | Hysteresis band current controller PWM scheme current and voltage                                                  |    |

|      | waveforms                                                                                                          | 50 |

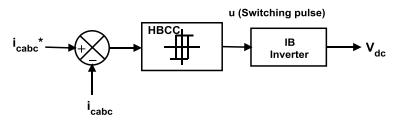

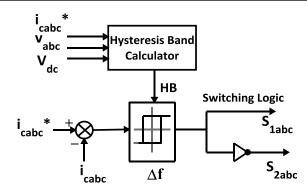

| 2.14 | Adaptive hysteresis band current controller (AHBCC)                                                                | 51 |

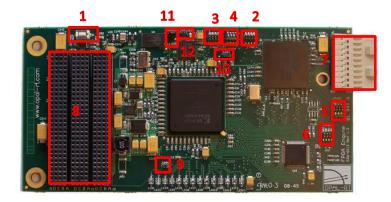

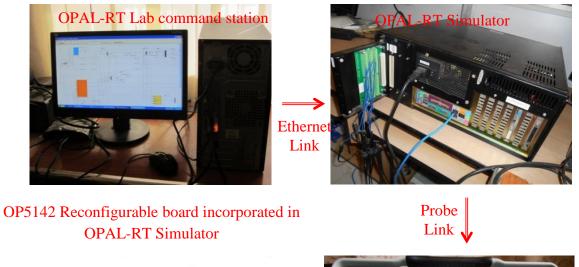

| 2.15 | OP5142 Reconfigurable Board indicating components                                                                  | 51 |

| 2.16 | OPAL-RT LAB Setup                                                                                                  | 52 |

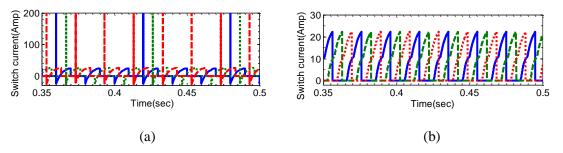

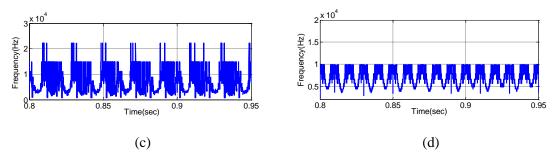

| 2.17 | Switch current for R-L load in (a) conventional 3 -phase half- bridge                                              |    |

|      | inverter with shoot-through current (b) 3-phase half-bridge inverter with no                                       |    |

|      | shoot-through current                                                                                              | 56 |

| 2.18 | Switching frequency of the power switches using (c) conventional hysteresis                                        |    |

|      | band current controller (b) adaptive hysteresis band current controller based                                      |    |

|      | i <sub>d</sub> -i <sub>q</sub> control strategy during steady state condition                                      | 56 |

| 2.19 | Steady state simulation results of 2C IB APF with unbalanced load using                                            |    |

|      | HBCC p-q control strategy for load current $(i_L)$ , filter current $(i_c)$ , source                               |    |

|      | current $(i_s)$ , load neutral current $(i_{Ln})$ , source neutral current $(i_{sn})$ , and                        |    |

|      | capacitor voltage ( $V_{dc}$ ), under (a) ideal sinusoidal voltage supply, (b)                                     |    |

|      | unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.                                       | 57 |

| 2.20 | Steady state OPAL-RT results of 2C IB APF with unbalanced load using                                               |    |

|      | HBCC p-q control strategy for load current (i <sub>L</sub> ), filter current (i <sub>c</sub> ), source             |    |

|      | current (i <sub>s</sub> ), load neutral current (i <sub>Ln</sub> ), source neutral current (i <sub>sn</sub> ), and |    |

capacitor voltage ( $V_{dc}$ ), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

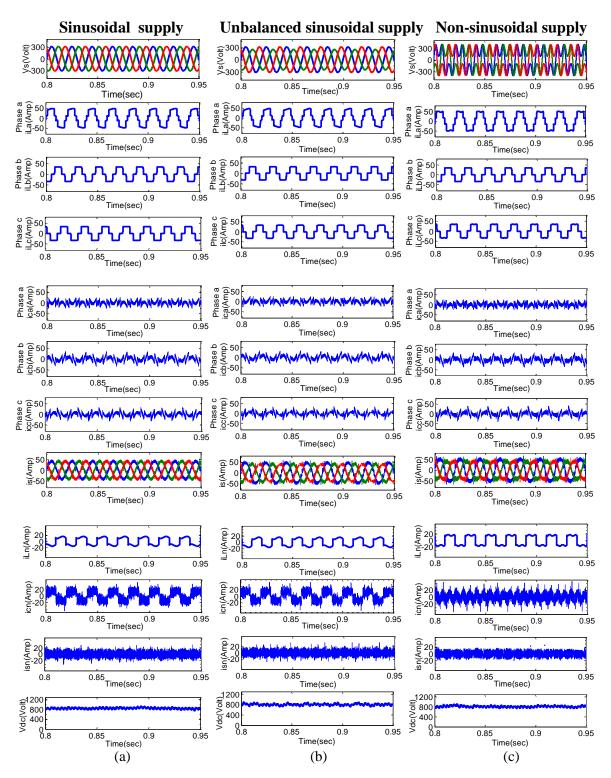

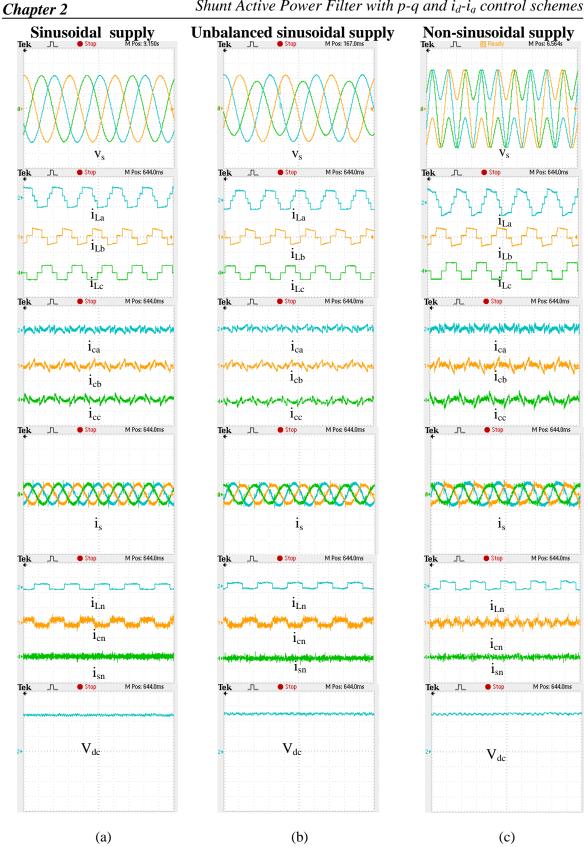

- 2.21 Steady state simulation results of 2C IB APF with unbalanced load using HBCC i<sub>d</sub>-i<sub>q</sub> control strategy for load current (i<sub>L</sub>), filter current (i<sub>c</sub>), source current (i<sub>s</sub>), load neutral current (i<sub>Ln</sub>), source neutral current (i<sub>sn</sub>), and capacitor voltage (V<sub>dc</sub>), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

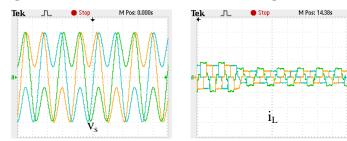

- 2.22 Steady state OPAL-RT results of 2C IB APF with unbalanced load using HBCC  $i_d$ - $i_q$  control strategy for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage ( $V_{dc}$ ), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

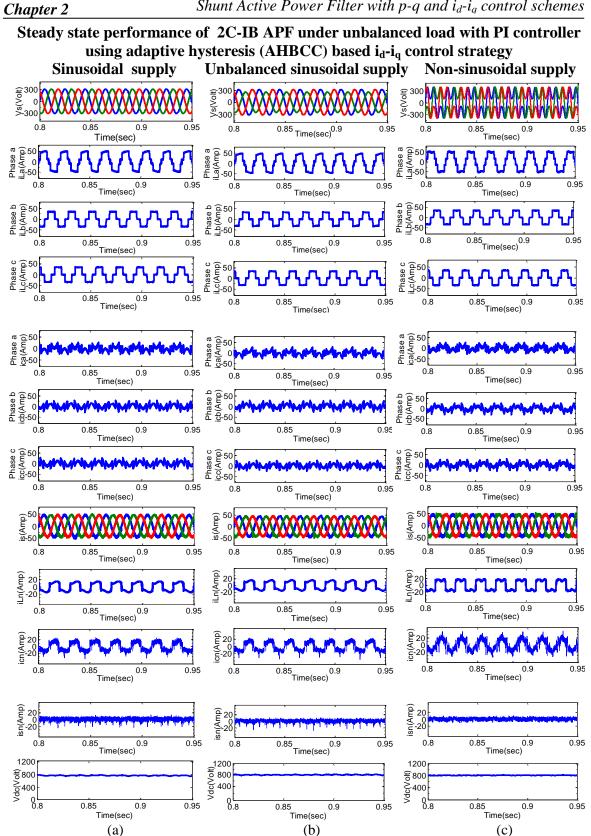

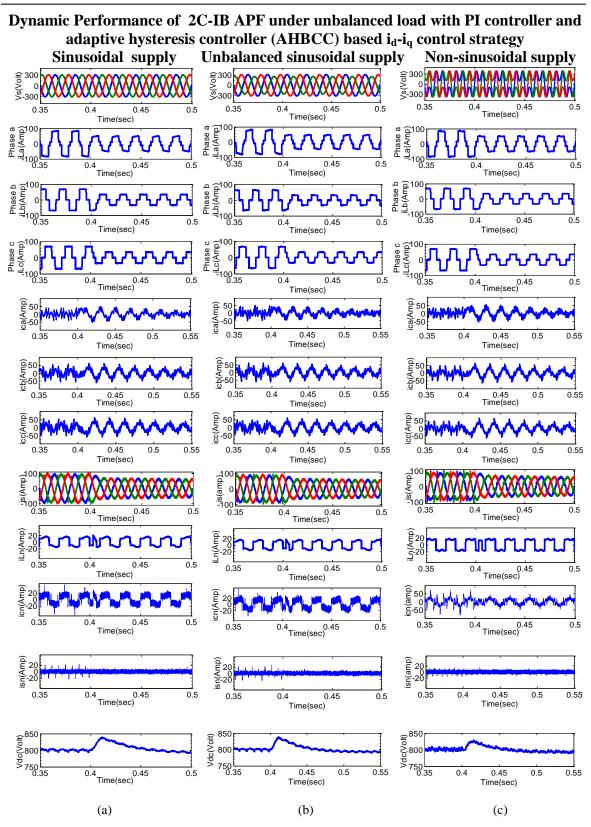

- 2.23 Steady state simulation results of 2C IB APF with unbalanced load using AHBCC  $i_d$ - $i_q$  control strategy for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage ( $V_{dc}$ ), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

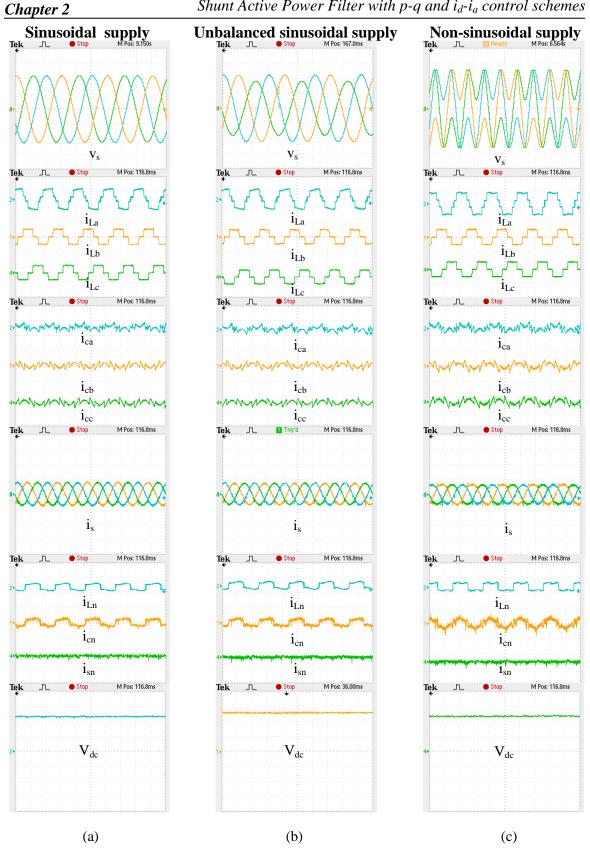

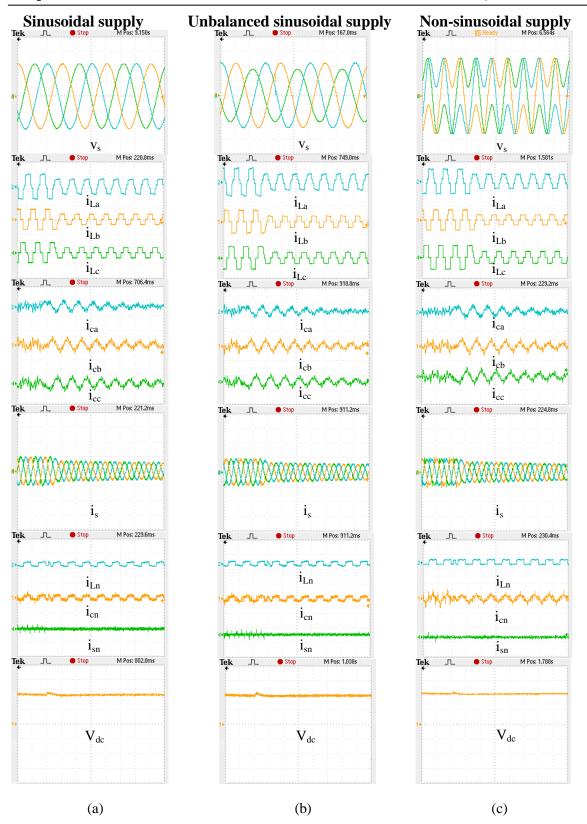

- 2.24 Steady state OPAL-RT results of 2C IB APF with unbalanced load using AHBCC  $i_d$ - $i_q$  control strategy for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage ( $V_{dc}$ ), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

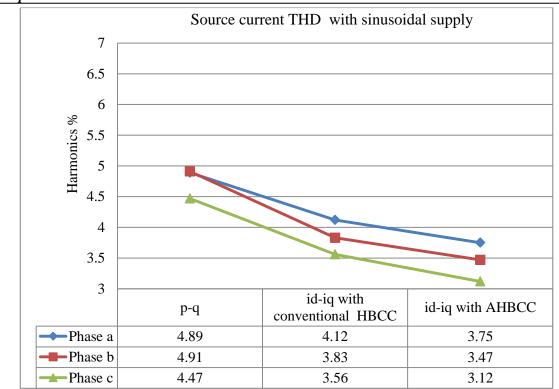

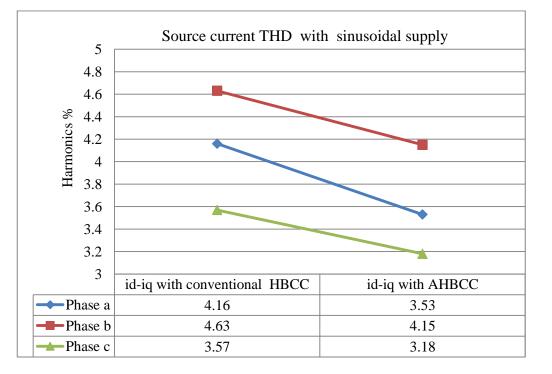

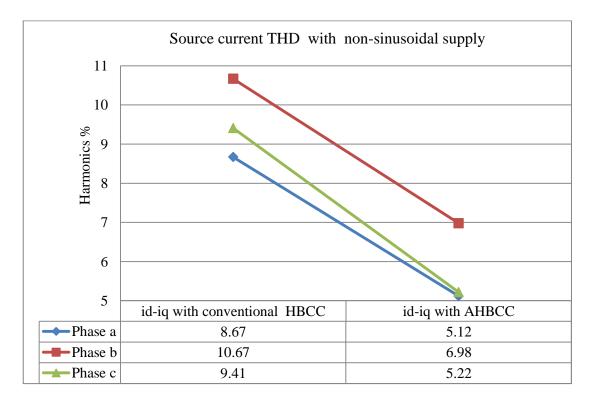

# 2.25 Chart showing the THD comparison of source current for p-q, $i_d$ - $i_q$ with conventional HBCC and $i_d$ - $i_q$ with AHBCC for sinusoidal voltage source condition.

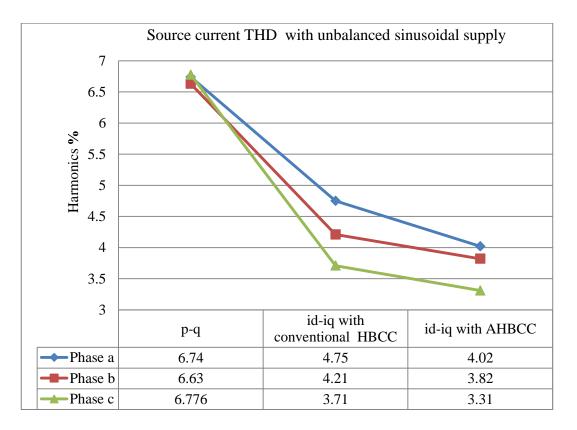

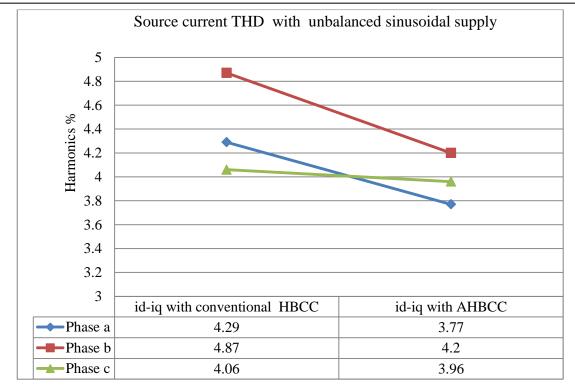

- 2.26 Chart showing the THD comparison of source current for p-q, i<sub>d</sub>-i<sub>q</sub> with conventional HBCC and i<sub>d</sub>-i<sub>q</sub> with AHBCC for unbalanced sinusoidal voltage source condition.

64

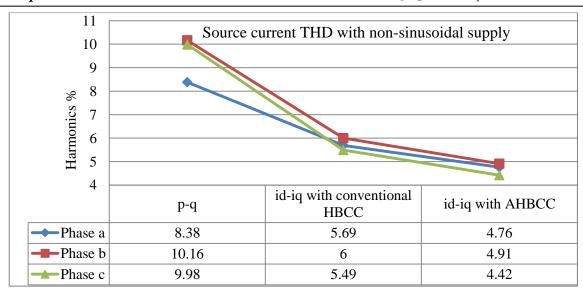

- 2.27 Chart showing the THD comparison of source current for p-q,  $i_d$ - $i_q$  with conventional HBCC and  $i_d$ - $i_q$  with AHBCC for non-sinusoidal voltage source condition.

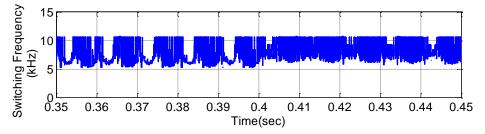

- 2.28 Switching frequency of the power switches using adaptive hysteresis band current controller based i<sub>d</sub>-i<sub>q</sub> control strategy during dynamic state condition.

66

xvii

58

59

62

64

65

2.29 Dynamic State simulation results of 2C IB APF with unbalanced load using HBCC i<sub>d</sub>-i<sub>q</sub> control strategy for load current (i<sub>L</sub>), filter current (i<sub>c</sub>), source current (i<sub>s</sub>), load neutral current (i<sub>Ln</sub>), source neutral current (i<sub>sn</sub>), and capacitor voltage (V<sub>dc</sub>), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

67

68

69

70

- 2.30 Dynamic state OPAL-RT results of 2C IB APF with unbalanced load using HBCC i<sub>d</sub>-i<sub>q</sub> control strategy for load current (i<sub>L</sub>), filter current (i<sub>c</sub>), source current (i<sub>s</sub>), load neutral current (i<sub>Ln</sub>), source neutral current (i<sub>sn</sub>), and capacitor voltage (V<sub>dc</sub>), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

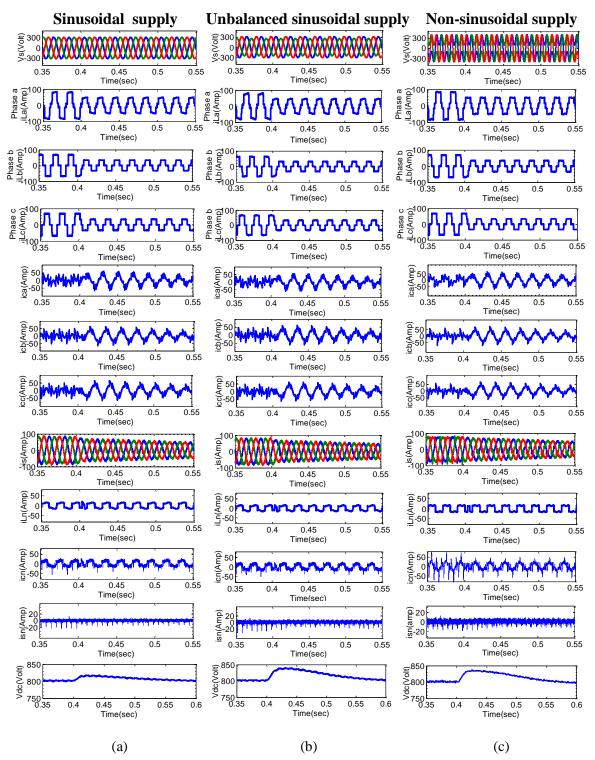

- 2.31 Dynamic state simulation results of 2C IB APF with unbalanced load using AHBCC  $i_d$ - $i_q$  control strategy for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage ( $V_{dc}$ ), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

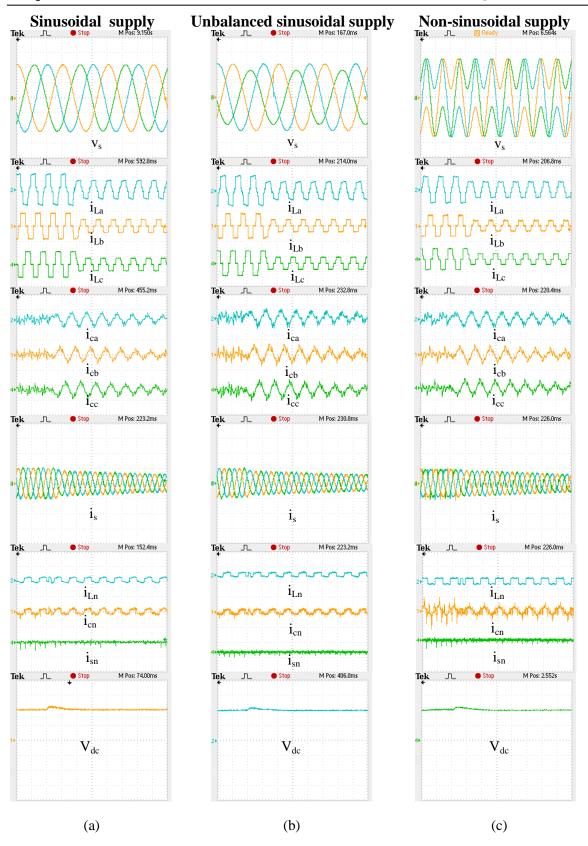

- 2.32 Dynamic state OPAL-RT results of 2C IB APF with unbalanced load using AHBCC  $i_d$ - $i_q$  control strategy for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage ( $V_{dc}$ ), under (a) ideal sinusoidal voltage supply, (b) unbalanced sinusoidal voltage supply, and (c) non-sinusoidal voltage supply.

- 2.33 Chart showing the THD comparison of source current for  $i_d$ - $i_q$  with conventional HBCC and  $i_d$ - $i_q$  with AHBCC for sinusoidal voltage source condition.

- 2.34 Chart showing the THD comparison of source current for i<sub>d</sub>-i<sub>q</sub> with conventional HBCC and i<sub>d</sub>-i<sub>q</sub> with AHBCC for unbalanced sinusoidal voltage source condition.

72

- 2.35 Chart showing the THD comparison of source current for i<sub>d</sub>-i<sub>q</sub> with conventional HBCC and i<sub>d</sub>-i<sub>q</sub> with AHBCC for unbalanced nonsinusoidal voltage source condition.

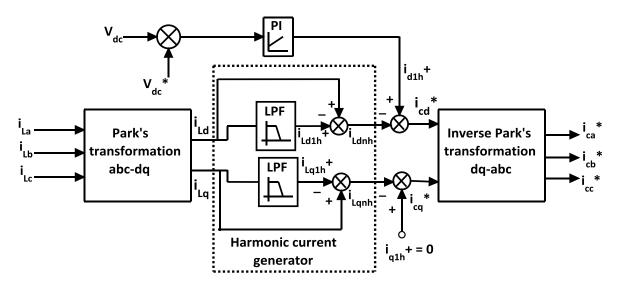

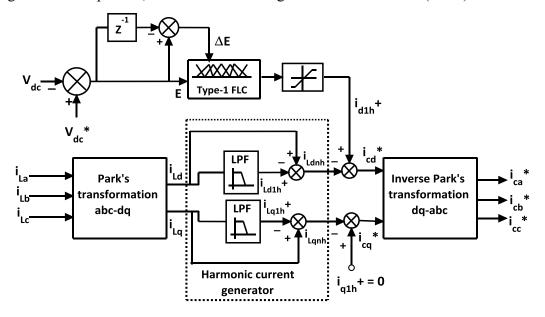

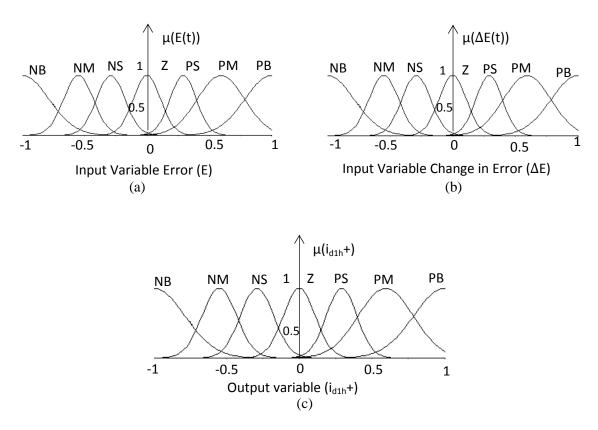

3.1 Reference current extractions with i<sub>d</sub>-i<sub>q</sub> method with Type-1 Fuzzy Logic

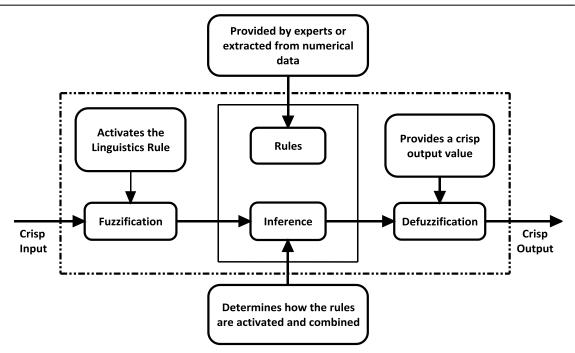

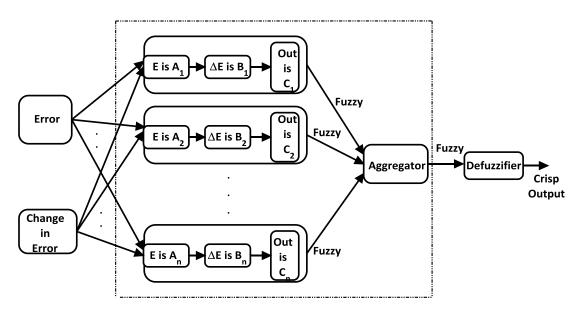

- controller.773.2Fuzzy logic controller block diagram.783.3A two input Mamdani Fuzzy inference system.79

| 3.4  | A two input Mamdani Fuzzy max-min Inference system                                |

|------|-----------------------------------------------------------------------------------|

| 3.5  | A two input Mamdani Fuzzy max-prod Inference system                               |

| 3.6  | Defuzzification                                                                   |

| 3.7  | Defuzzification methods                                                           |

| 3.8  | Trapezoidal membership function.                                                  |

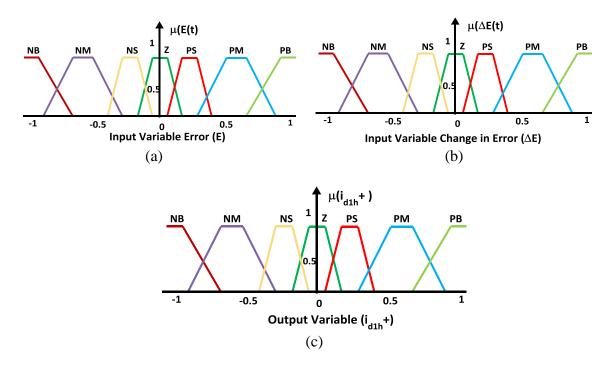

| 3.9  | Normalized trapezoidal membership function for dc-link voltage control (a)        |

|      | Input variable error, E (b) Input variable change in error, $\Delta E$ (c) Output |

|      | variable, $i_{d1h}^+$                                                             |

| 3.10 | Triangular membership function                                                    |

| 3.11 | Normalized triangular membership function for dc-link voltage control (a)         |

|      | Input variable error, E (b) Input variable change in error, $\Delta E$ (c) Output |

|      | variable, $i_{d1h}^+$                                                             |

| 3.12 | Gaussian membership function.                                                     |

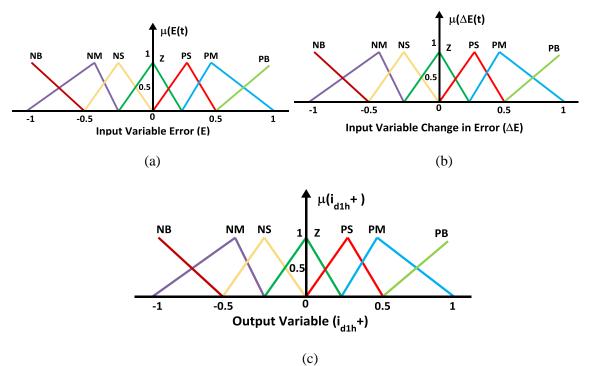

| 3.13 | Normalized Gaussian membership function for dc-link voltage control (a)           |

|      | Input variable error, E (b) Input variable change in error, $\Delta E$ (c) Output |

|      | variable, $i_{d1h}^+$                                                             |

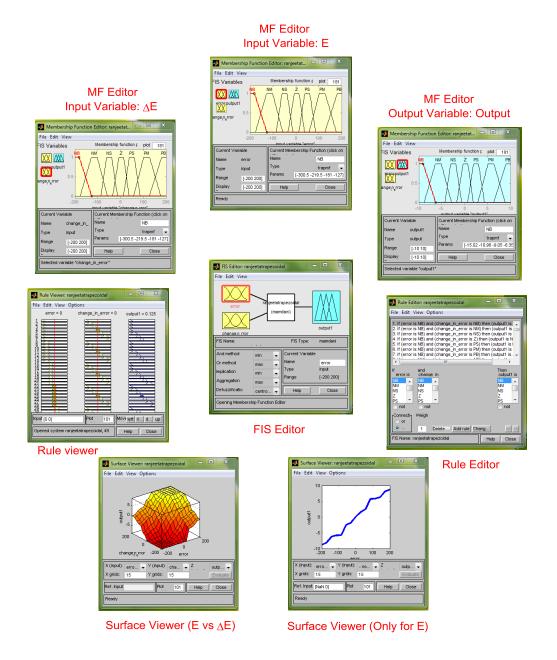

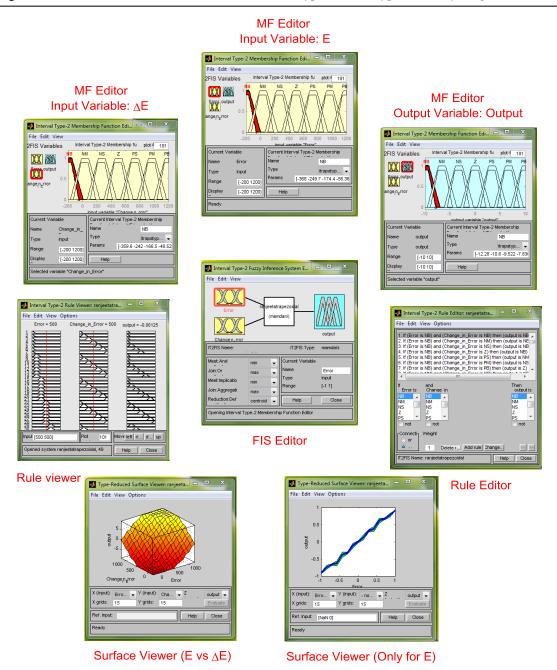

| 3.14 | Matlab based Type-1 fuzzy inference system with trapezoidal membership            |

|      | function.                                                                         |

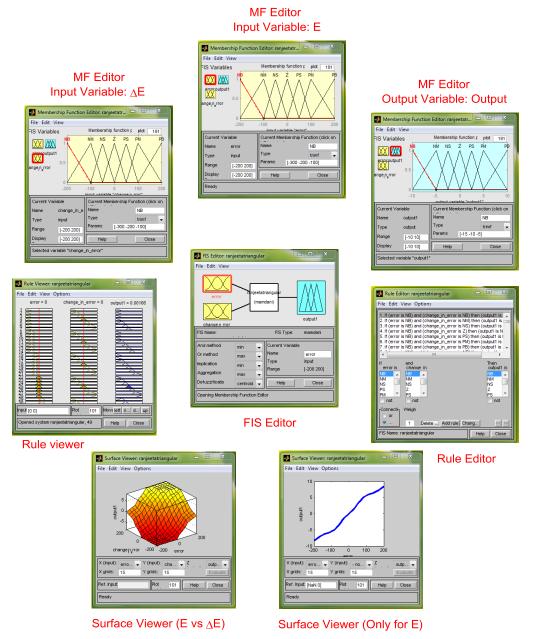

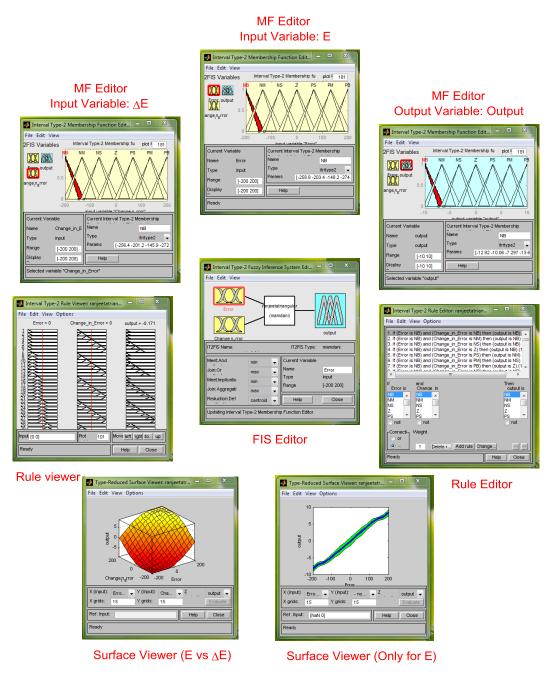

| 3.15 | Matlab based Type-1 fuzzy inference system with triangular membership             |

|      | function.                                                                         |

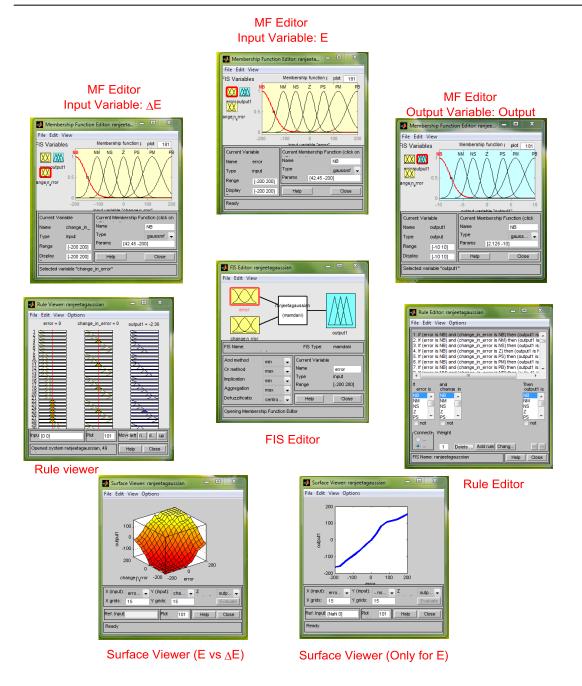

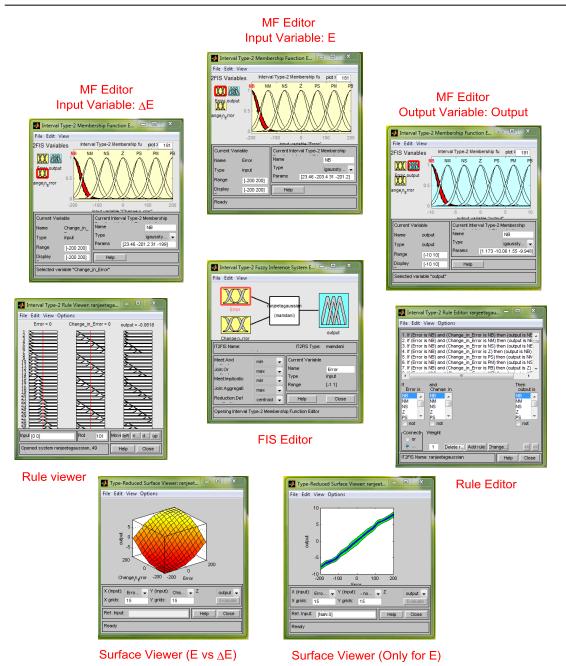

| 3.16 | Matlab based Type-1 fuzzy inference system with Gaussian membership               |

|      | function                                                                          |

| 3.17 | Type-1 fuzzy logic controller architecture.                                       |

| 3.18 | Type-2 fuzzy logic controller architecture.                                       |

| 3.19 | (a) Type-1 fuzzy logic membership function (b) Type-2 fuzzy logic                 |

|      | membership function.                                                              |

| 3.20 | Reference current extractions with $i_d$ - $i_q$ method using Type-2 Fuzzy Logic  |

|      | controller                                                                        |

| 3.21 | Matlab based Type-2 fuzzy inference system with trapezoidal membership            |

|      | function.                                                                         |

| 3.22 | Matlab based Type-2 fuzzy inference system with triangular membership             |

|      | function.                                                                         |

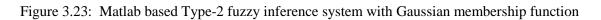

| 3.23 | Matlab based Type-2 fuzzy inference system with Gaussian membership               |

|      | function                                                                                                             | 98  |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

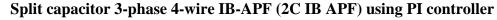

| 3.24 | 3-phase 4-wire split capacitor interleaved buck active power filter (2C IB                                           |     |

|      | APF)                                                                                                                 | 99  |

| 3.25 | 3-phase 4-wire split capacitor interleaved buck active power filter (2C IB                                           |     |

|      | APF) using fuzzy and adaptive hysteresis based $i_d$ - $i_q$ control strategy                                        | 99  |

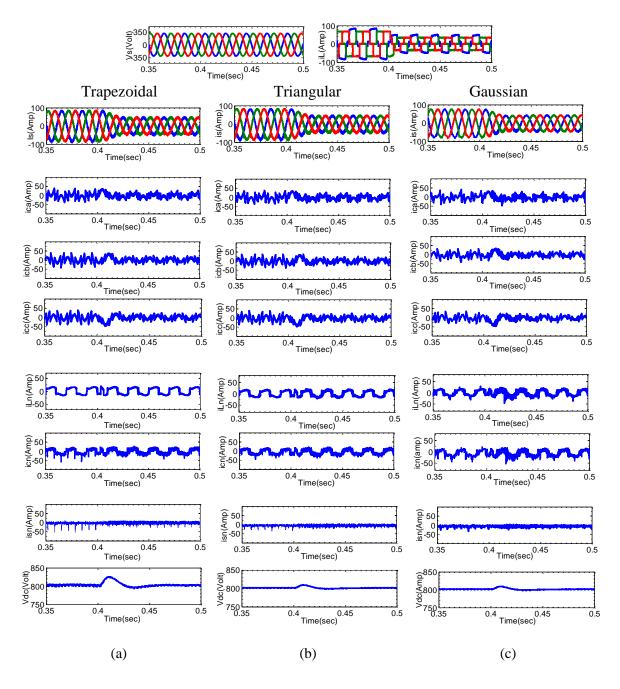

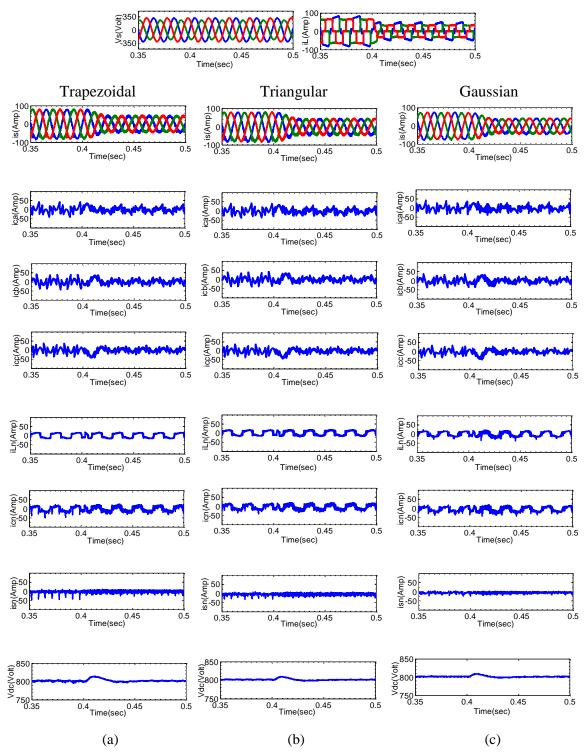

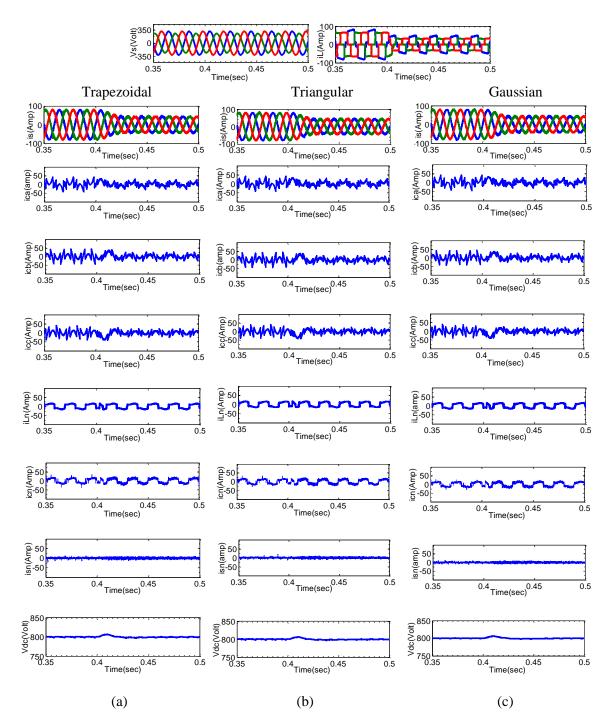

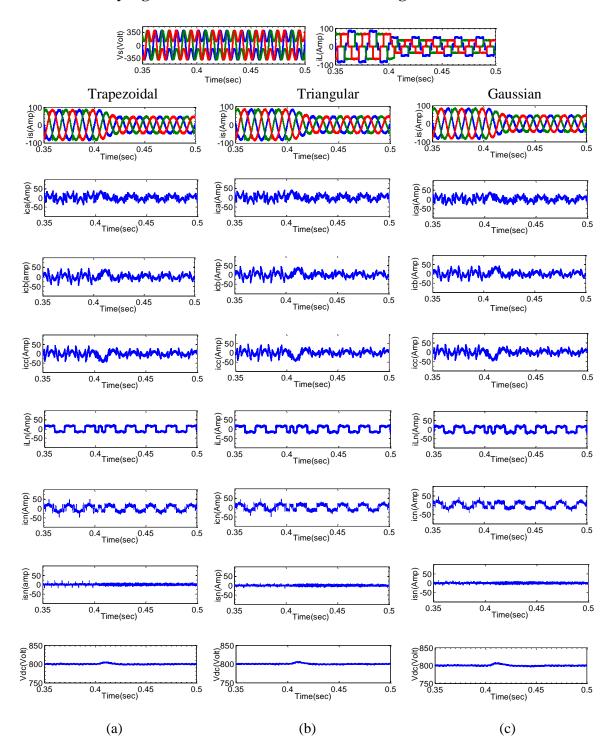

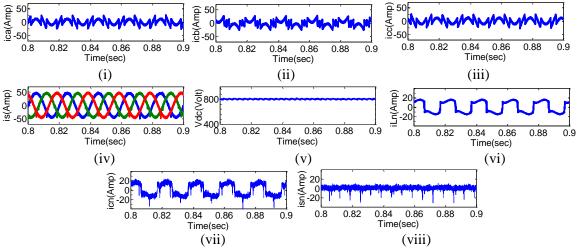

| 3.26 | Simulation results of 2C IB APF with unbalanced load using Type-1 fuzzy                                              |     |

|      | logic controller for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ),                     |     |

|      | load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ) and capacitor voltage                         |     |

|      | $\left(V_{dc}\right)$ by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian MF under                            |     |

|      | sinusoidal voltage source condition.                                                                                 | 101 |

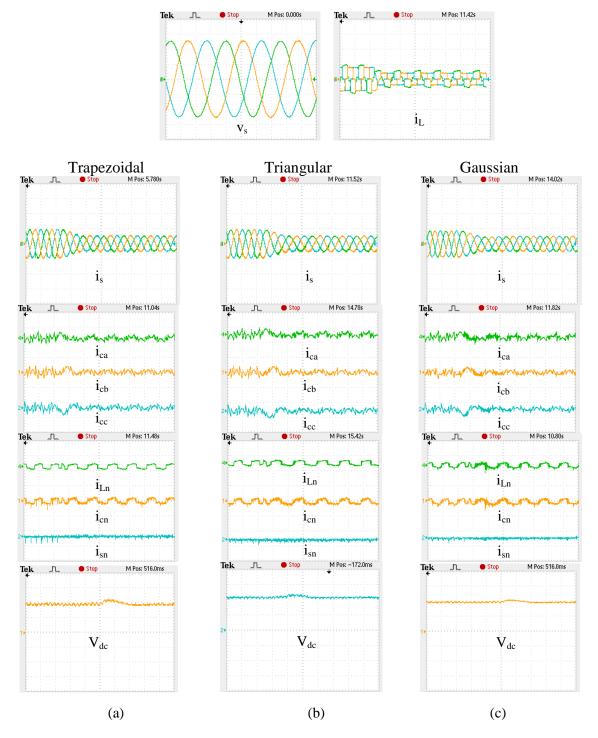

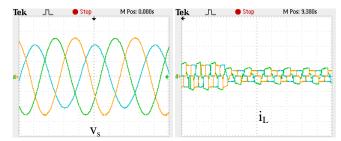

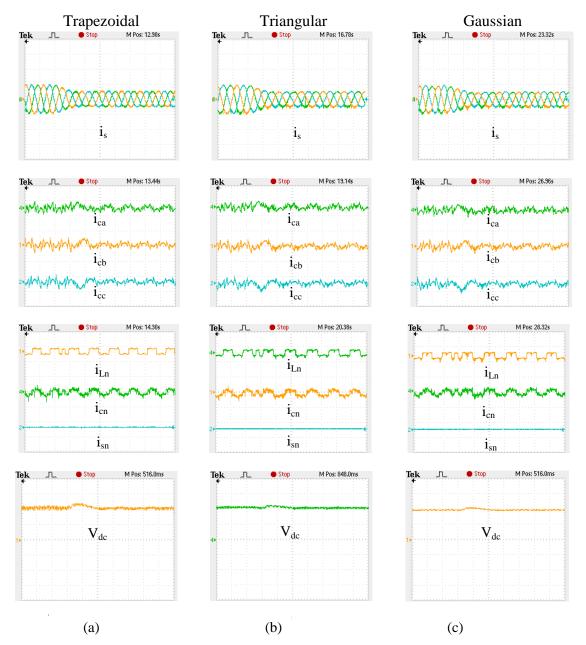

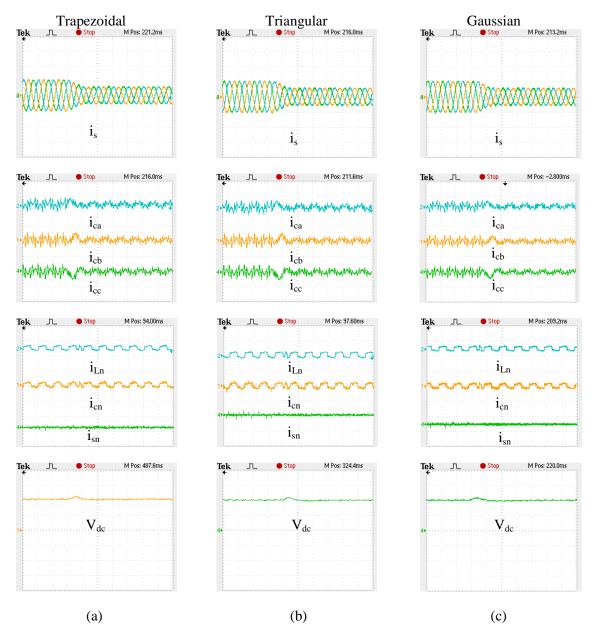

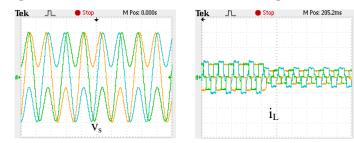

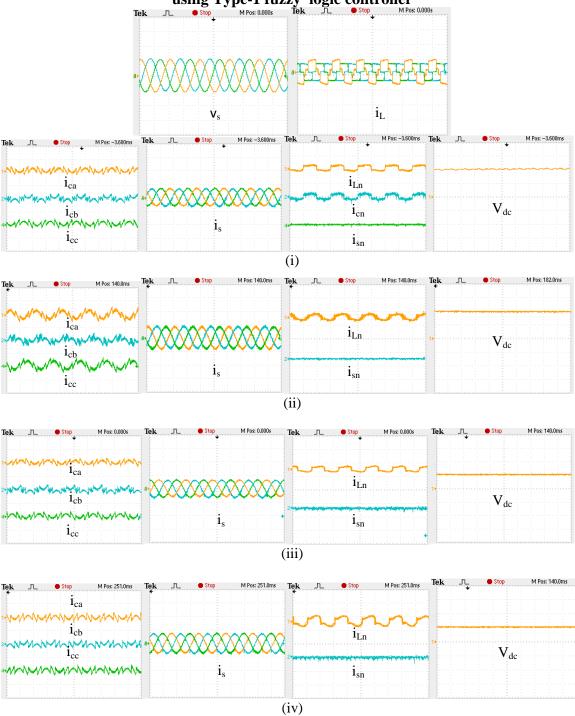

| 3.27 | OPAL-RT lab results of 2C IB APF with unbalanced load using Type-1                                                   |     |

|      | fuzzy logic controller for load current ( $i_L$ ), filter current ( $i_c$ ), source current                          |     |

|      | (i <sub>s</sub> ), load neutral current (i <sub>Ln</sub> ), source neutral current (i <sub>sn</sub> ), and capacitor |     |

|      | voltage( $V_{dc}$ ) by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian                                       |     |

|      | MF under sinusoidal voltage source condition.                                                                        | 102 |

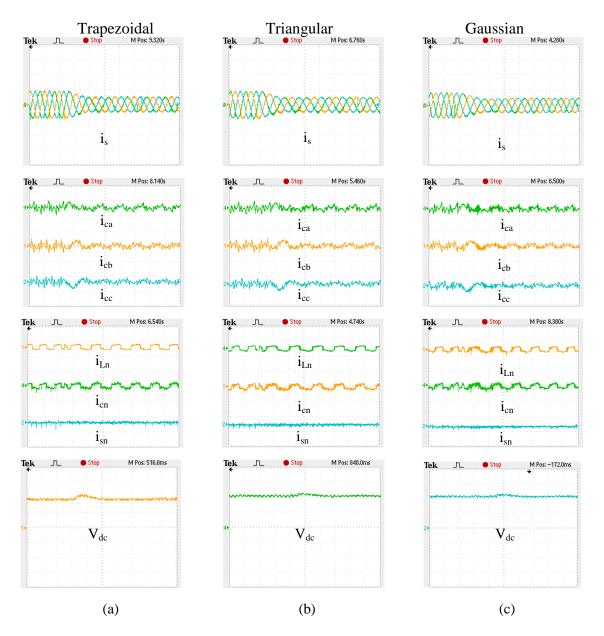

| 3.28 | Simulation results of 2C IB APF with unbalanced load using Type-1fuzzy                                               |     |

|      | logic controller for load current ( $i_L$ ), filter current ( $i_c$ ), source current (is),                          |     |

|      | load neutral current (i $_{\text{Ln}}$ ), source neutral current (i $_{\text{sn}}$ ) ), and capacitor                |     |

|      | voltage( $V_{dc}$ ) by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian                                       |     |

|      | MF under unbalanced sinusoidal voltage source condition                                                              | 103 |

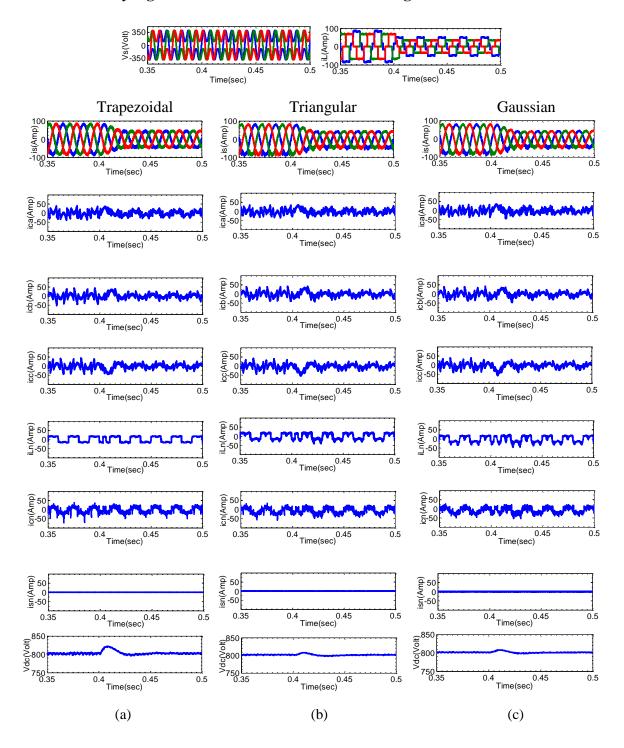

| 3.29 | OPAL-RT results of 2C IB APF with unbalanced load using Type-1 fuzzy                                                 |     |

|      | logic controller for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ),                     |     |

|      | load neutral current $(i_{Ln})$ , source neutral current $(i_{sn})$ and capacitor                                    |     |

|      | voltage( $V_{dc}$ ) by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian                                       |     |

|      | MF under unbalanced sinusoidal voltage source condition                                                              | 104 |

| 3.30 | Simulation results of 2C IB APF with unbalanced load using Type-1 fuzzy                                              |     |

|      | logic controller for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ),                     |     |

|      | load neutral current $(i_{Ln})$ , source neutral current $(i_{sn})$ , and capacitor                                  |     |

|      | voltage( $V_{dc}$ ) by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian                                       |     |

|      | MF under nonsinusoidal voltage source condition.                                                                     | 105 |

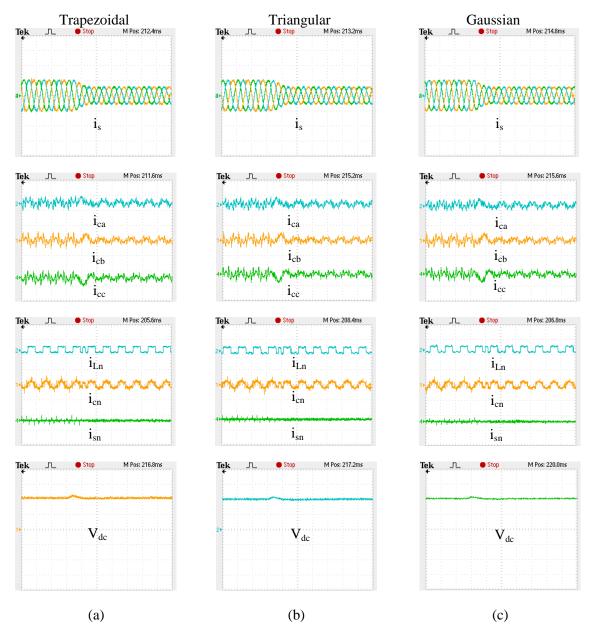

| 3.31 | OPAL-RT results of 2C IB APF with unbalanced load using Type-1 fuzzy                                                 |     |

|      | logic controller for load current $(i_L)$ , filter current $(i_c)$ , source current $(i_s)$ ,                        |     |

|      | load neutral current (i $_{Ln}$ ), source neutral current (i $_{sn}$ ) and capacitor voltage                         |     |

| 3.32 | $(V_{dc})$ by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian MF under<br>nonsinusoidal voltage source condition                                                                                                                                                                                                                                                                                                                                                                                                                 | 106 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.33 | $(V_{dc})$ by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian MF under<br>sinusoidal voltage source condition                                                                                                                                                                                                                                                                                                                                                                                                                    | 108 |

| 3.34 | sinusoidal voltage source condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 109 |

| 3.35 | voltage( $V_{dc}$ ) by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian MF under unbalanced sinusoidal voltage source condition<br>OPAL-RT results of 2C IB APF with unbalanced load using Type-2 fuzzy logic controller for load current (i <sub>L</sub> ), filter current (i <sub>c</sub> ), source current (i <sub>s</sub> ), load neutral current (i <sub>Ln</sub> ), source neutral current (i <sub>sn</sub> ), and capacitor voltage (V <sub>dc</sub> ) by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian MF under | 110 |

| 3.36 | unbalanced sinusoidal voltage source condition<br>Simulation results of 2C IB APF with unbalanced load using Type-2 fuzzy<br>logic controller for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ),<br>load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor                                                                                                                                                                                                                   | 111 |

| 3.37 | voltage( $V_{dc}$ ) by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian MF under non-sinusoidal voltage source condition<br>OPAL-RT results of 2C IB APF with unbalanced load using Type-2 fuzzy logic controller for load current ( $i_L$ ), filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage                                                                                                                                   | 112 |

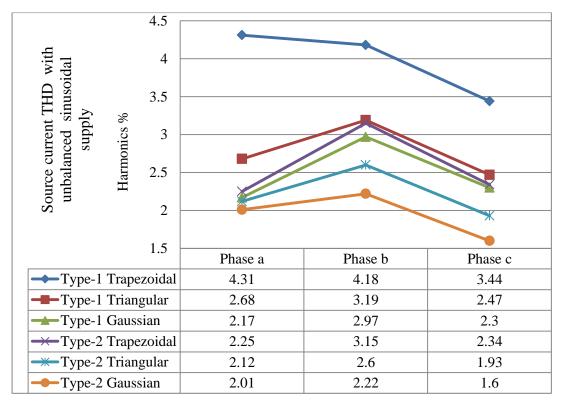

| 3.38 | $(V_{dc})$ by (a) Trapezoidal MF, (b) Triangular MF, and (c) Gaussian MF under<br>non-sinusoidal voltage source condition                                                                                                                                                                                                                                                                                                                                                                                                                | 113 |

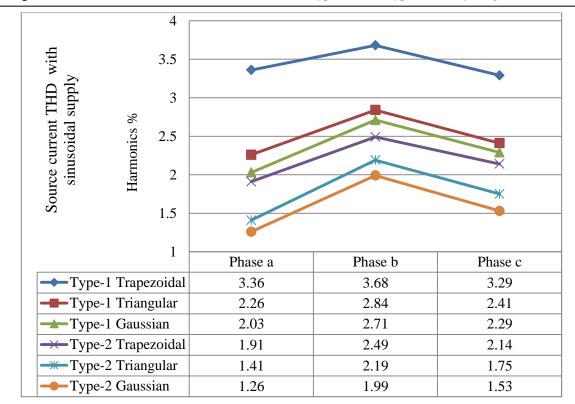

|      | Type-2 trapezoidal, triangular, and Gaussian membership function for                              |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | sinusoidal voltage source condition.                                                              | 115 |

| 3.39 | Chart showing the THD comparison of source current using Type-1 and                               |     |

|      | Type-2 trapezoidal, triangular, and Gaussian membership function for                              |     |

|      | unbalanced sinusoidal voltage source condition                                                    | 115 |

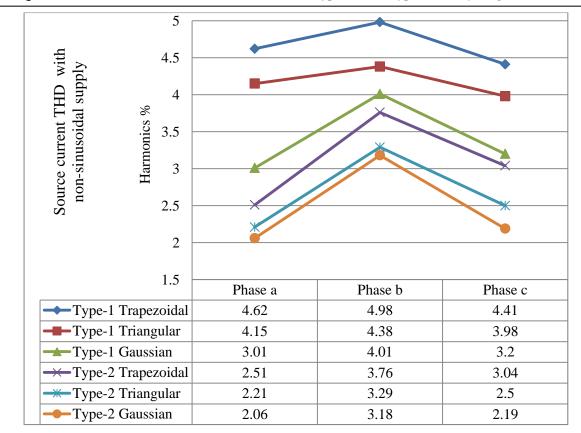

| 3.40 | Chart showing the THD comparison of source current using Type-1 and                               |     |

|      | Type-2 trapezoidal, triangular, and Gaussian membership function for non-                         |     |

|      | sinusoidal voltage source condition.                                                              | 116 |

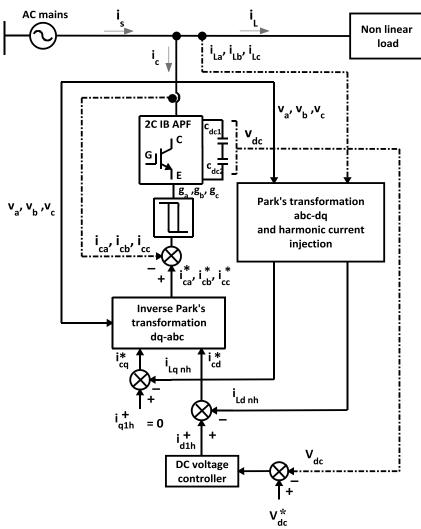

| 4.1  | Split capacitor interleaved buck active power filter (2C IB APF)                                  | 120 |

| 4.2  | Block diagram of dc-link voltage regulation in 2C IB APF                                          | 120 |

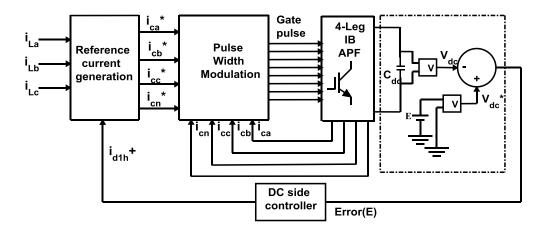

| 4.3  | Four-leg interleaved buck active power filter (4L IB APF)                                         | 122 |

| 4.4  | Block diagram of dc-link voltage regulation in four-leg interleaved buck                          |     |

|      | active power filter (4L IB APF)                                                                   | 123 |

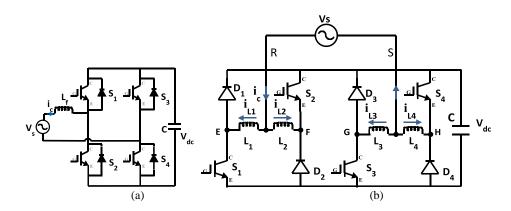

| 4.5  | (a) Single phase conventional full-bridge converter (b) Single phase full-                        |     |

|      | bridge interleaved buck (IB) converter                                                            | 124 |

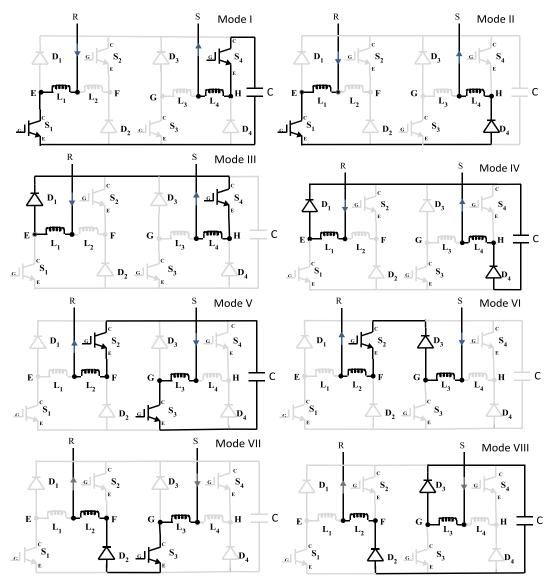

| 4.6  | Working stages of full-bridge interleaved buck converter based active power                       |     |

|      | filter                                                                                            | 125 |

| 4.7  | Single capacitor, three full-bridge interleaved buck active power filter (1C                      |     |

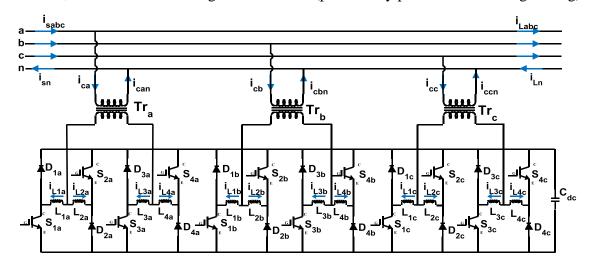

|      | 3FB IB APF)                                                                                       | 126 |

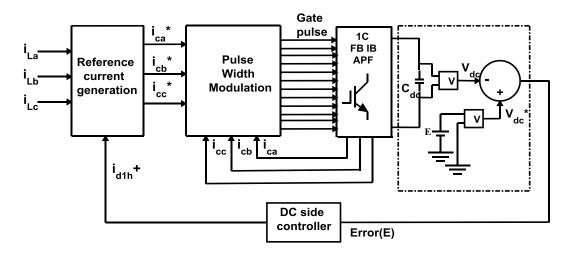

| 4.8  | Block diagram of dc-link voltage regulation in single capacitor, three full-                      |     |

|      | bridge interleaved buck active power filter (1C 3FB IB APF)                                       | 127 |

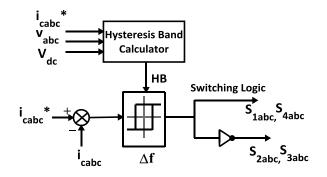

| 4.9  | Switching pulse generation.                                                                       | 127 |

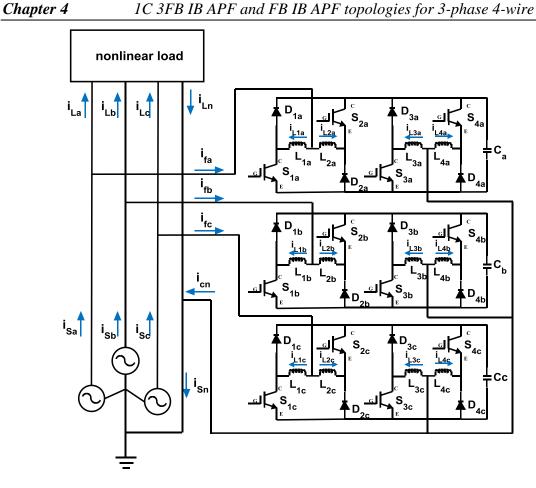

| 4.10 | 3-phase 4-wire full-bridge interleaved buck active power filter (FB IB APF).                      | 130 |

| 4.11 | Block diagram of dc-link voltage regulation in 3-phase 4-wire full-bridge                         |     |

|      | interleaved buck active power filter (3-phase 4-wire FB IB APF)                                   | 130 |

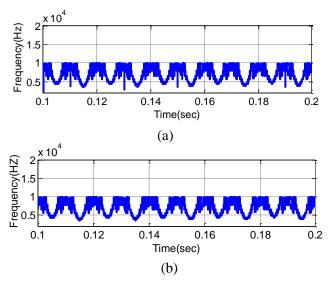

| 4.12 | Simulation result of switching frequency for (a) adaptive hysteresis current                      |     |

|      | controller with PI controller (b) adaptive hysteresis current controller with                     |     |

|      | Type-1 fuzzy controller.                                                                          | 132 |

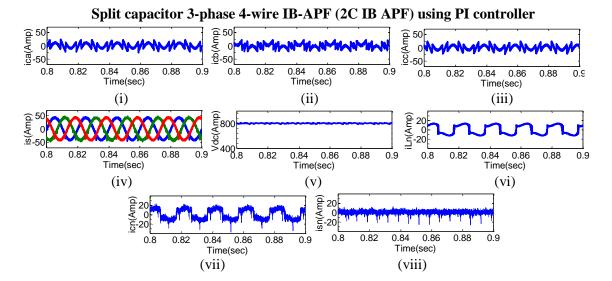

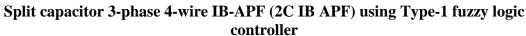

| 4.13 | Simulation results of (i) phase $a$ filter current, $i_{ca}$ (ii) phase $b$ filter current,       |     |

|      | $i_{cb}$ (iii) phase c filter current, $i_{cc}$ (iv) source current, $i_s$ (v) capacitor voltage, |     |

|      | $V_{dc}$ (vi) load neutral current, $i_{Ln}$ (vii) filter neutral current, $i_{cn}$ and (viii)    |     |

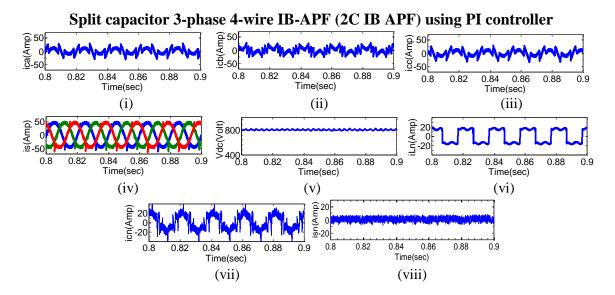

|      | source neutral current $i_{sn}$ for 2C IB APF using PI and Type-1 fuzzy logic                     |     |

|      | controller (T1FLC) under sinusoidal volatge source condition.                                     | 133 |

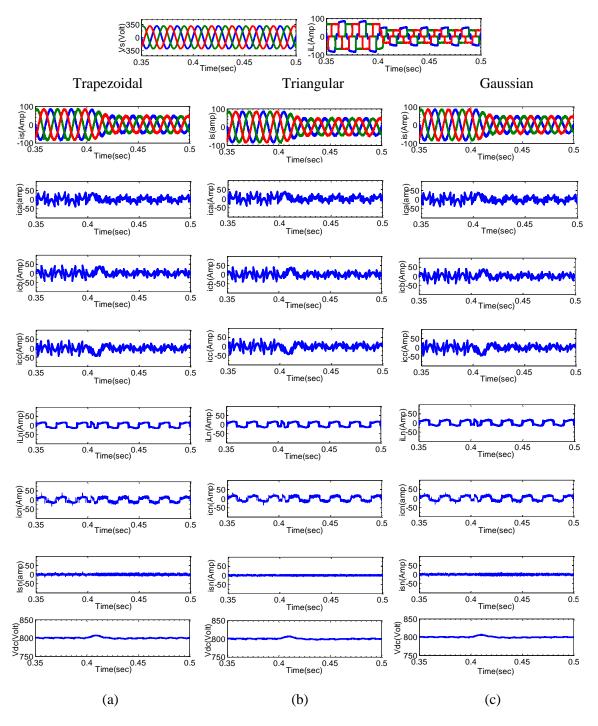

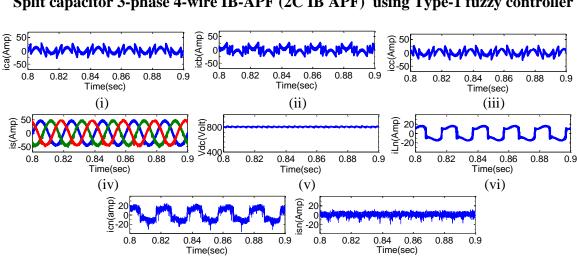

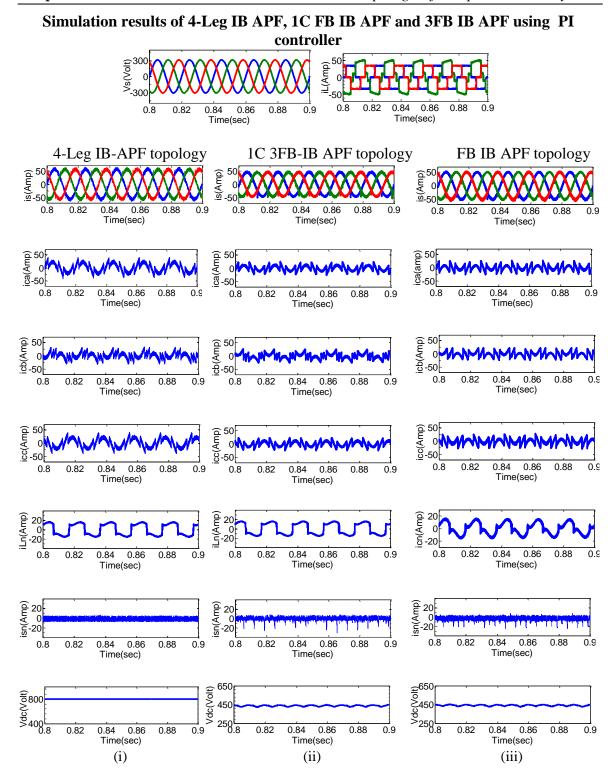

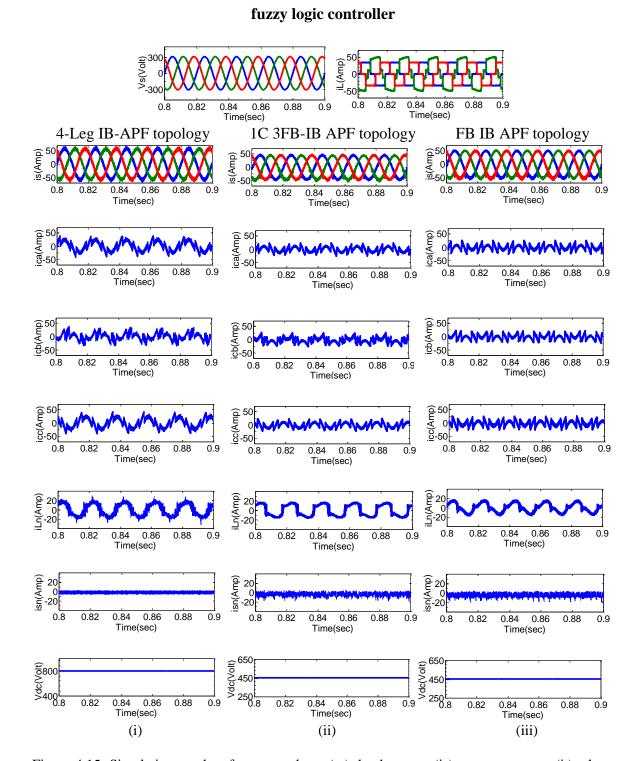

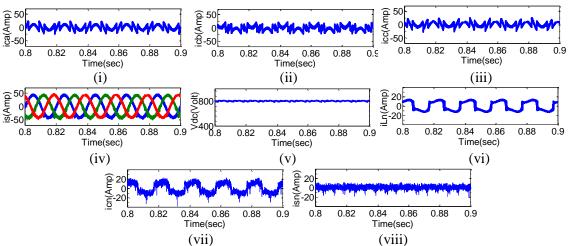

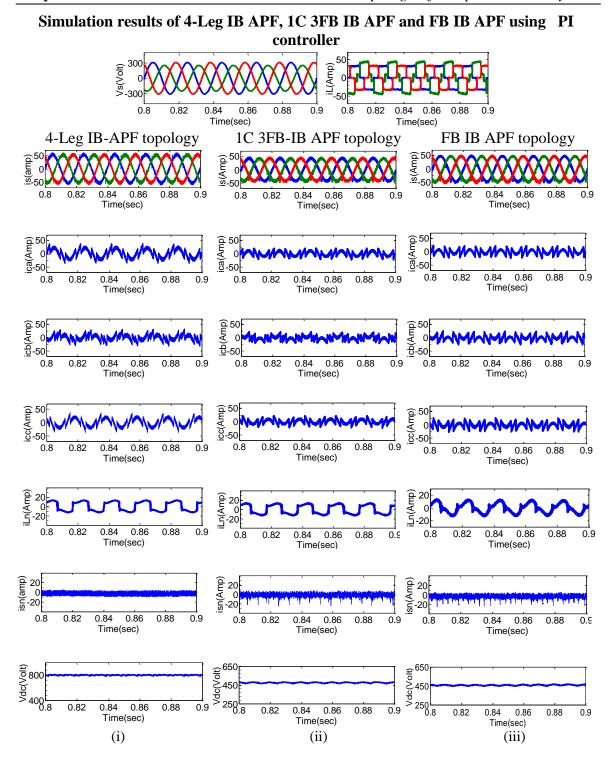

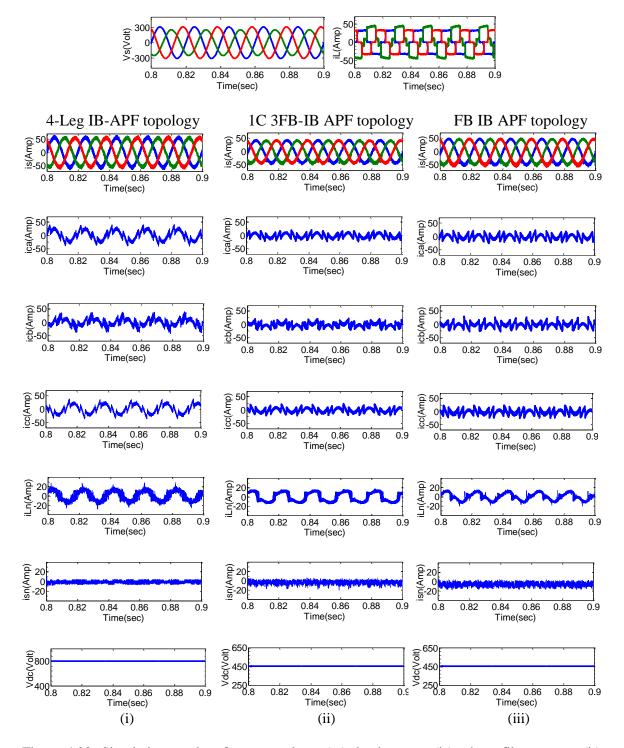

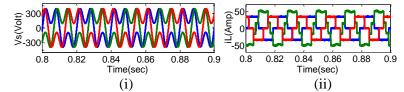

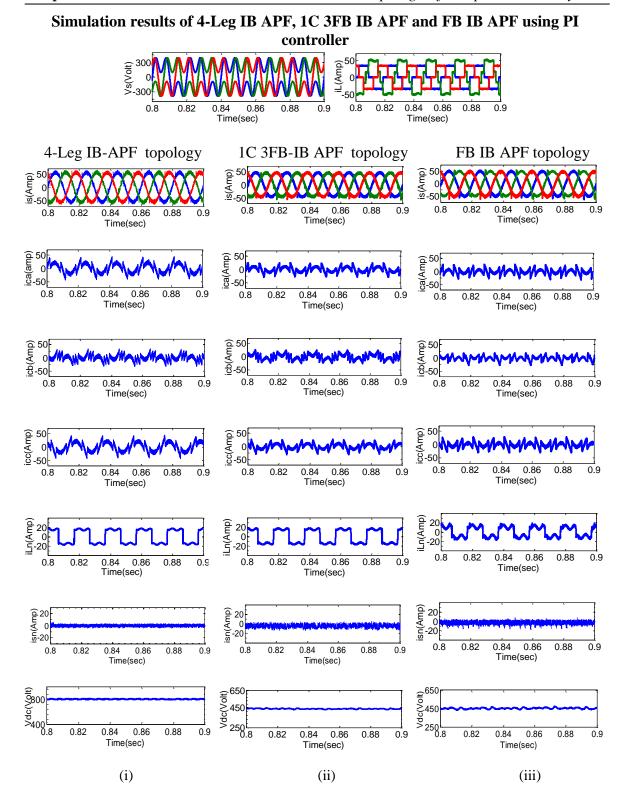

- 4.14 Simulation results of source voltage (v<sub>s</sub>), load current (i<sub>L</sub>), phase filter current (i<sub>c</sub>), source current (i<sub>s</sub>), load neutral current (i<sub>Ln</sub>), source neutral current (i<sub>sn</sub>), and capacitor voltage (V<sub>dc</sub>) using PI controller under sinusoidal voltage source condition for (i) four-leg interleaved buck active power filter, 4L IB APF (ii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iii) 3-phase 4-wire full bridge interleaved buck active power filter, FB IB APF.

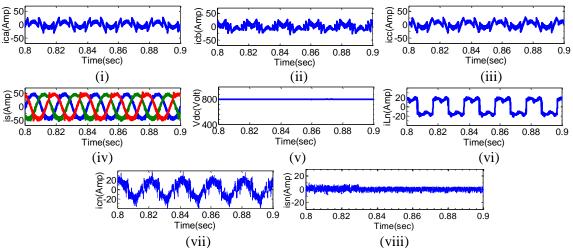

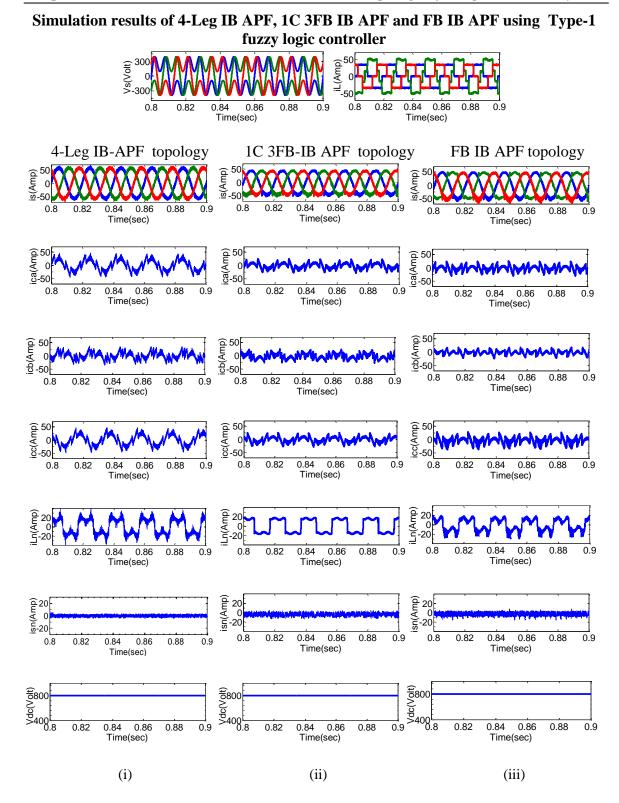

- 4.15 Simulation results of source current (i<sub>s</sub>), phase filter current (i<sub>c</sub>), load neutral current (i<sub>Ln</sub>), source neutral current (i<sub>sn</sub>), and capacitor voltage (V<sub>dc</sub>) using Type-1 fuzzy logic controller (T1FLC) under sinusoidal voltage source condition for (i) four-leg interleaved buck active power filter, 4L IB APF (ii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iii) 3-phase 4-wire full bridge interleaved buck active power filter, FB IB APF.

134

135

136

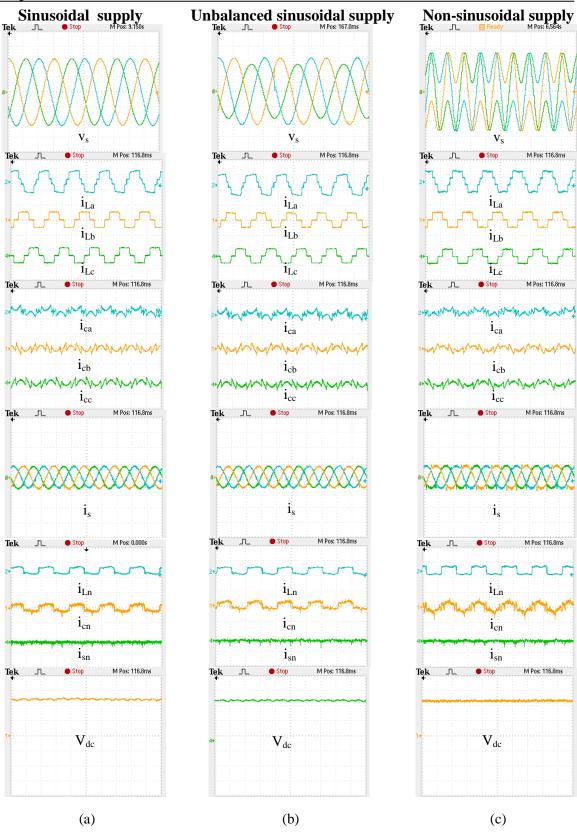

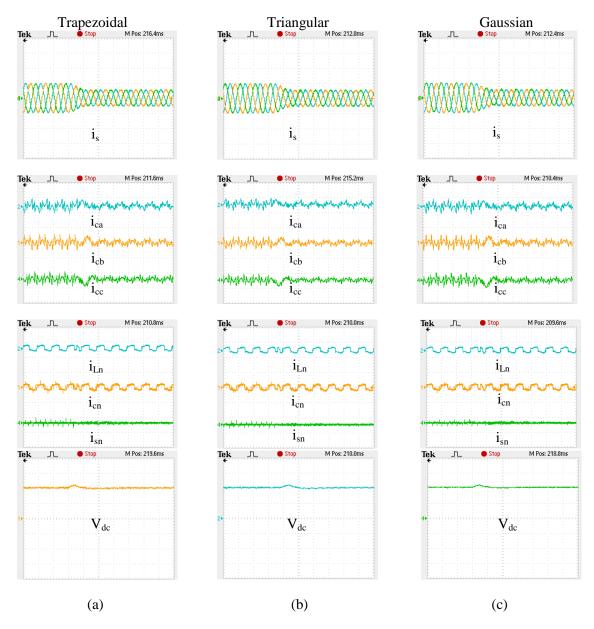

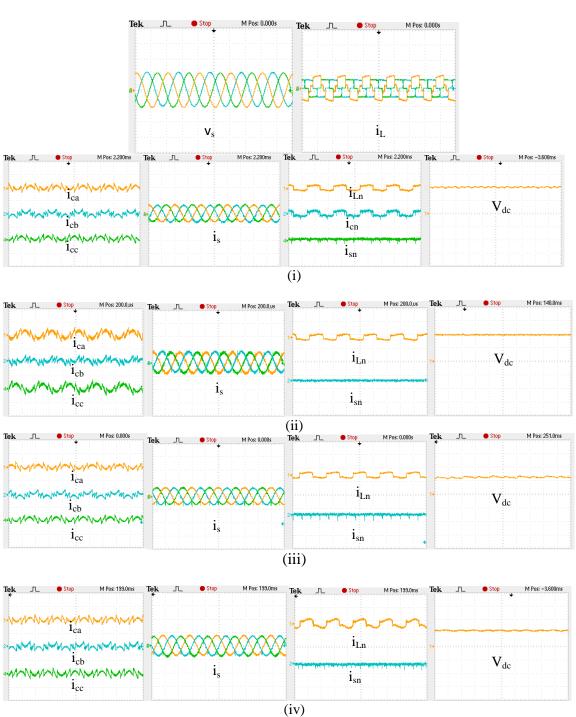

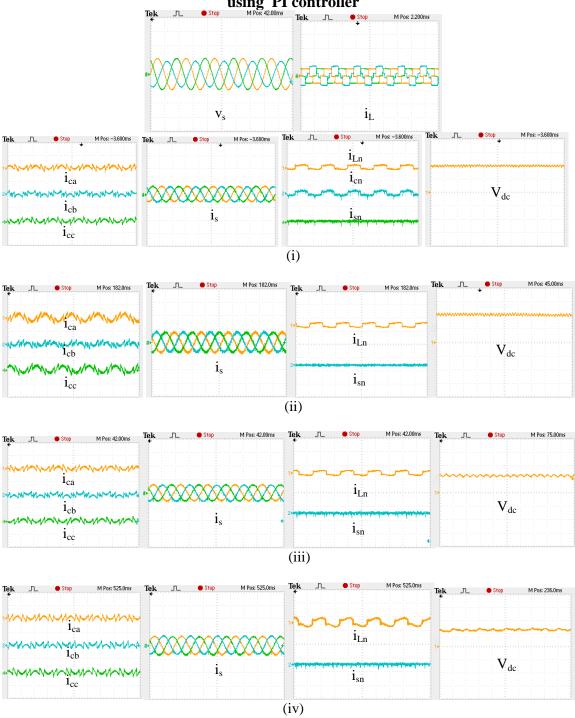

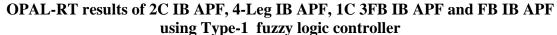

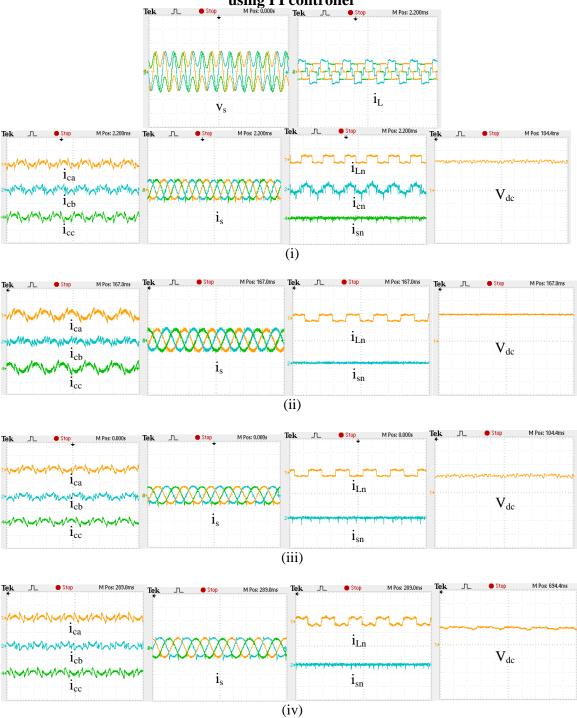

- 4.16 OPAL-RT results of source voltage (v<sub>s</sub>), load current (i<sub>L</sub>), phase filter current (i<sub>c</sub>), source current (i<sub>s</sub>), load neutral current (i<sub>Ln</sub>), source neutral current (i<sub>sn</sub>), and capacitor voltage (V<sub>dc</sub>) using PI controller under sinusoidal voltage source condition for (i) split capacitor interleaved buck active power filter, 2C IB APF (ii) four-leg interleaved buck active power filter, 4L IB APF (iii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iv) 3-phase 4-wire full bridge interleaved buck active power filter, FB IB APF.

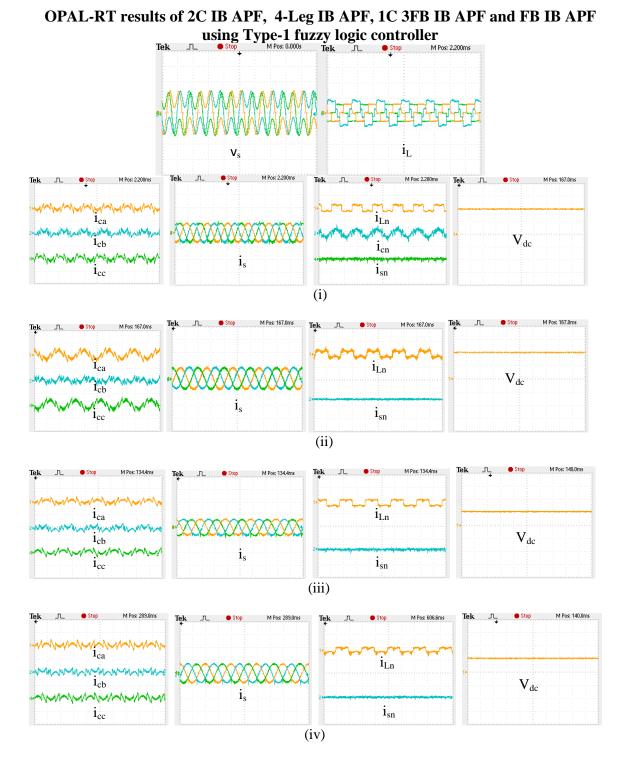

- 4.17 OPAL-RT results of source voltage ( $v_s$ ), load current ( $i_L$ ), phase filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage ( $V_{dc}$ ) using Type-1 fuzzy logic controller (T1FLC) under sinusoidal voltage source condition for (i) split capacitor interleaved buck active power filter, 2C IB APF (ii) four-leg interleaved buck active power filter, 4L IB APF (iii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iv) 3-phase 4-wire full bridge interleaved buck active power filter, FB IB APF.

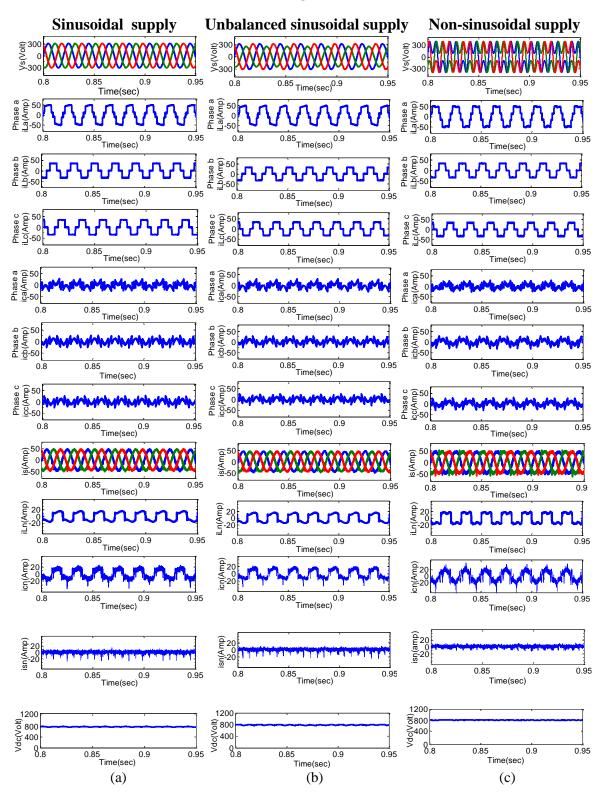

- 4.18 Simulation results of (i) phase *a* filter current, i<sub>ca</sub> (ii) phase *b* filter current, i<sub>cb</sub>

(iii) phase *c* filter current, i<sub>cc</sub> (iv) source current, i<sub>s</sub> (v) capacitor voltage, V<sub>dc</sub>

(vi) load neutral current, i<sub>Ln</sub> (vii) filter neutral current, i<sub>cn</sub> and (viii) source

neutral current i<sub>sn</sub> for 2C IB APF using PI and Type-1 fuzzy logic controller (T1FLC) under unbalanced sinusoidal volatge source condition.

- 4.19 Simulation results of source voltage  $(v_s)$ , load current  $(i_L)$ , phase filter current  $(i_c)$ , source current  $(i_s)$ , load neutral current  $(i_{Ln})$ , source neutral current  $(i_{sn})$ , and capacitor voltage  $(V_{dc})$  using PI controller under unbalanced sinusoidal voltage source condition for (i) four-leg interleaved buck active power filter, 4L IB APF (ii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iii) 3-phase 4-wire full bridge interleaved buck active power filter, FB IB APF....

- 4.20 Simulation results of source voltage ( $v_s$ ), load current ( $i_L$ ), phase filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage ( $V_{dc}$ ) using Type-1 fuzzy logic controller (T1FLC) under unbalanced sinusoidal voltage source condition for (i) fourleg interleaved buck active power filter, 4L IB APF (ii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iii) 3phase 4-wire full bridge interleaved buck active power filter, FB IB APF....

- 4.21 OPAL-RT results of source voltage (v<sub>s</sub>), load current (i<sub>L</sub>), phase filter current (i<sub>c</sub>), source current (i<sub>s</sub>), load neutral current (i<sub>Ln</sub>), source neutral current (i<sub>sn</sub>), and capacitor voltage (V<sub>dc</sub>) using PI controller under unbalanced sinusoidal voltage source condition for (i) split capacitor interleaved buck active power filter, 2C IB APF (ii) four-leg interleaved buck active power filter, 4L IB APF (iii) single capacitor, three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iv) 3-phase 4-wire full bridge interleaved buck active power 141

- 4.23 Simulation results of (i) phase a filter current,  $i_{ca}$  (ii) phase b filter current,

139

138

$i_{cb}$  (iii) phase *c* filter current,  $i_{cc}$  (iv) source current,  $i_s$  (v) capacitor voltage,  $V_{dc}$  (vi) Load neutral current,  $i_{Ln}$  (vii) filter neutral current,  $i_{cn}$  and (viii) source neutral current  $i_{sn}$  for 2C IB APF using PI and Type-1 fuzzy logic controller (T1FLC) under non-sinusoidal voltage source condition....

- 4.24 Simulation results of source voltage  $(v_s)$ , load current  $(i_L)$ , phase filter current  $(i_c)$ , source current  $(i_s)$ , load neutral current  $(i_{Ln})$ , source neutral current  $(i_{sn})$ , and capacitor voltage  $(V_{dc})$  using PI controller under non sinusoidal voltage source condition for (i) four-leg interleaved buck active power filter, 4L IB APF (ii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iii) 3-phase 4-wire full bridge interleaved buck active power filter, FB IB APF.....

- 4.25 Simulation results of source voltage (v<sub>s</sub>), load current (i<sub>L</sub>), phase filter current (i<sub>c</sub>), source current (i<sub>s</sub>), load neutral current (i<sub>Ln</sub>), source neutral current (i<sub>sn</sub>), and capacitor voltage (V<sub>dc</sub>) using Type-1 fuzzy logic controller (T1FLC) under non sinusoidal voltage source condition for (i) four-leg interleaved buck active power filter, 4L IB APF (ii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iii) 3-phase 4-wire full bridge interleaved buck active power filter, FB IB APF....

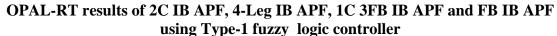

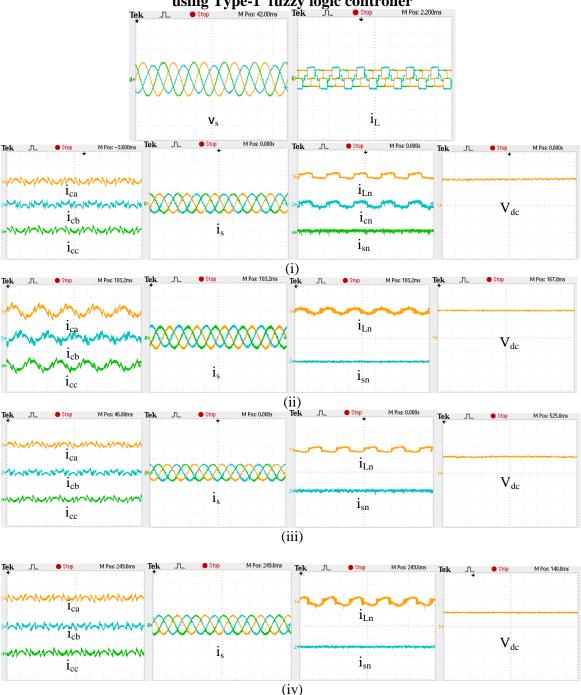

- 4.26 OPAL-RT results of source voltage  $(v_s)$ , load current  $(i_L)$ , phase filter current  $(i_c)$ , source current  $(i_s)$ , load neutral current  $(i_{Ln})$ , source neutral current  $(i_{sn})$ , and capacitor voltage  $(V_{dc})$  using PI controller under nonsinusoidal voltage source condition for (i) split capacitor interleaved buck active power filter, 2C IB APF (ii) four-leg interleaved buck active power filter, 4L IB APF (iii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iv) 3-phase 4-wire full bridge interleaved buck active power filter, FB IB APF.....

- 4.27 OPAL-RT results of source voltage( $v_s$ ), load current ( $i_L$ ), phase filter current ( $i_c$ ), source current ( $i_s$ ), load neutral current ( $i_{Ln}$ ), source neutral current ( $i_{sn}$ ), and capacitor voltage ( $V_{dc}$ ) using Type-1 fuzzy logic controller (T1FLC) under non sinusoidal voltage source condition for (i) split capacitor interleaved buck active power filter, 2C IB APF (ii) four-leg interleaved buck active power filter, 4L IB APF (iii) single capacitor three full bridge interleaved buck active power filter, 1C 3FB IB APF and (iv) 3-phase 4-wire

145

144

143

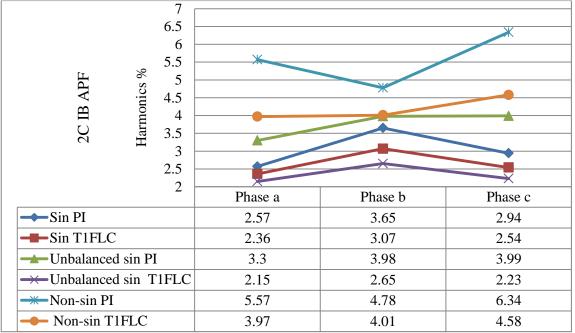

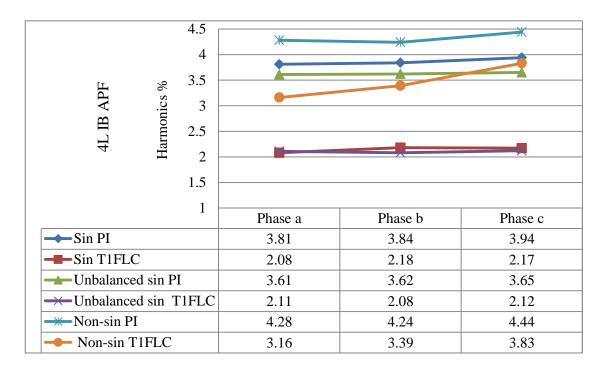

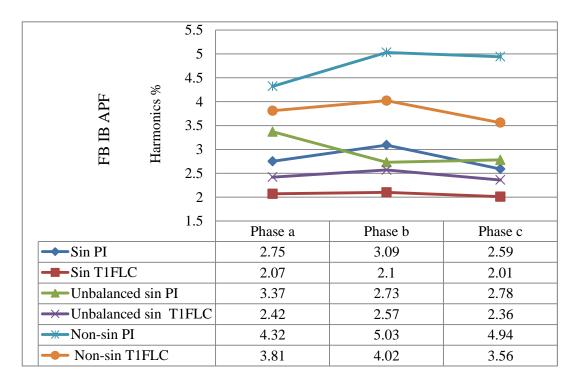

| 4.28 | Chart showing the source current THD comparison after compensation using   |     |

|------|----------------------------------------------------------------------------|-----|

|      | 2C IB APF topology with PI and Type-1 fuzzy logic controller (T1FLC) for   |     |

|      | sinusoidal, unbalanced sinusoidal and non-sinusoidal voltage source        |     |

|      | condition                                                                  | 150 |

| 4.29 | Chart showing the source current THD comparison after compensation using   |     |

|      | 4L IB APF topology with PI and Type-1 fuzzy logic controller (T1FLC) for   |     |

|      | sinusoidal, unbalanced sinusoidal and non-sinusoidal voltage source        |     |

|      | condition                                                                  | 150 |

| 4.30 | Chart showing the source current THD comparison after compensation using   |     |

|      | 1C 3 FB IB APF topology with PI and Type-1 fuzzy logic controller          |     |

|      | (T1FLC) for sinusoidal, unbalanced sinusoidal and non-sinusoidal voltage   |     |

|      | source condition.                                                          | 151 |

| 4.31 | Chart showing the source current THD comparison after compensation using   |     |

|      | FB IB APF topology with PI and Type-1 fuzzy logic controller (T1FLC) for   |     |

|      | sinusoidal, unbalanced sinusoidal and non-sinusoidal voltage source        |     |

|      | condition.                                                                 | 151 |

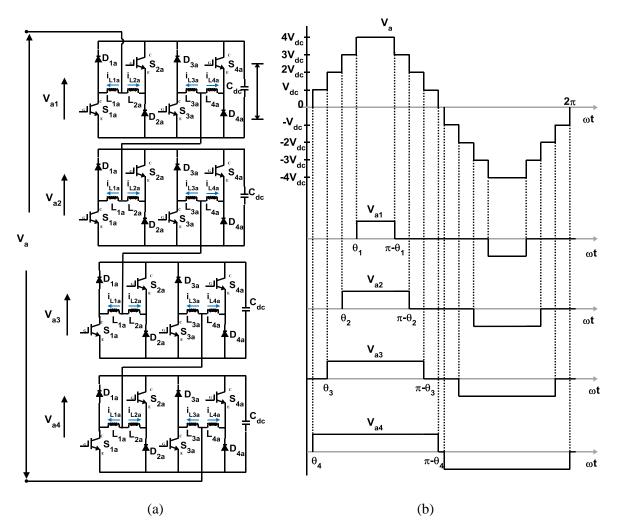

| 5.1  | Circuit diagram of full bridge interleaved buck converter                  | 157 |

| 5.2  | (a) Circuit diagram and (b) Output phase voltage of 9-level cascaded full- |     |

|      | bridge interleaved buck inverter                                           | 157 |

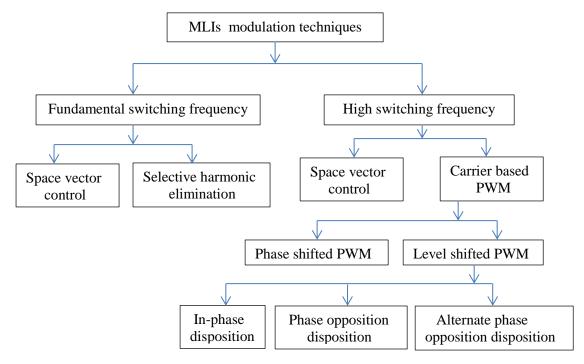

| 5.3  | Classification of multilevel inverter (MLI) modulation techniques          | 158 |

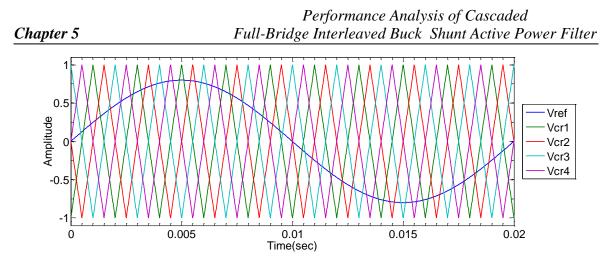

| 5.4  | Phase shifted PWM scheme for 5-level multilevel cascaded inverter          | 161 |

full bridge interleaved buck active power filter, FB IB APF.....

147

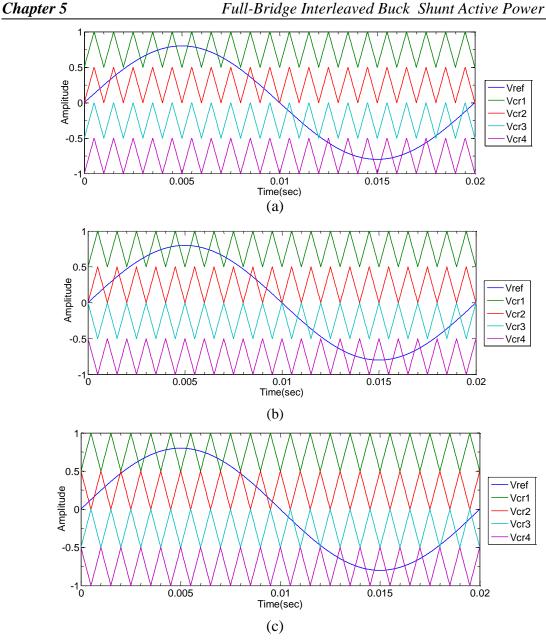

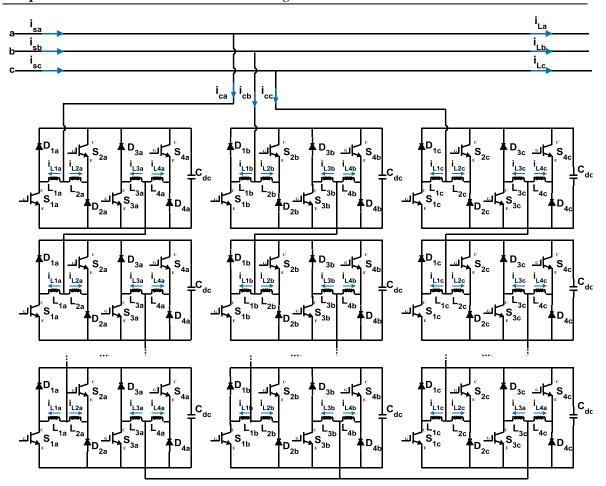

- (a) In-phase disposition PWM (IPD PWM) (b) Phase opposition disposition 5.5 PWM (POD PWM) (c) Alternate phase opposition disposition PWM scheme for 5-level multilevel cascaded inverter. 162 5.6 Multilevel m-level cascaded full bridge interleaved buck active power filter. 165

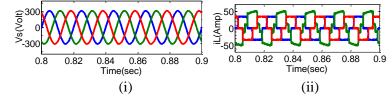

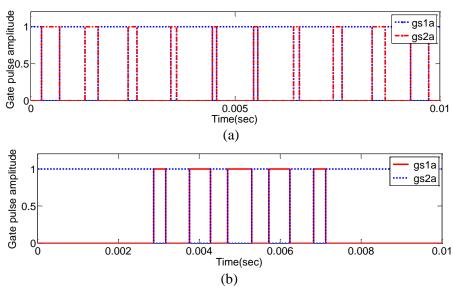

- (a) Block diagram of reference current generation using  $i_d$ - $i_a$  control scheme 5.7 for m-level interleaved buck active power filter (b) dc- link voltage 166 Switching pulse for the same leg power devices by (a) phase shift PWM (b) 5.8 level shifted PWM. 166

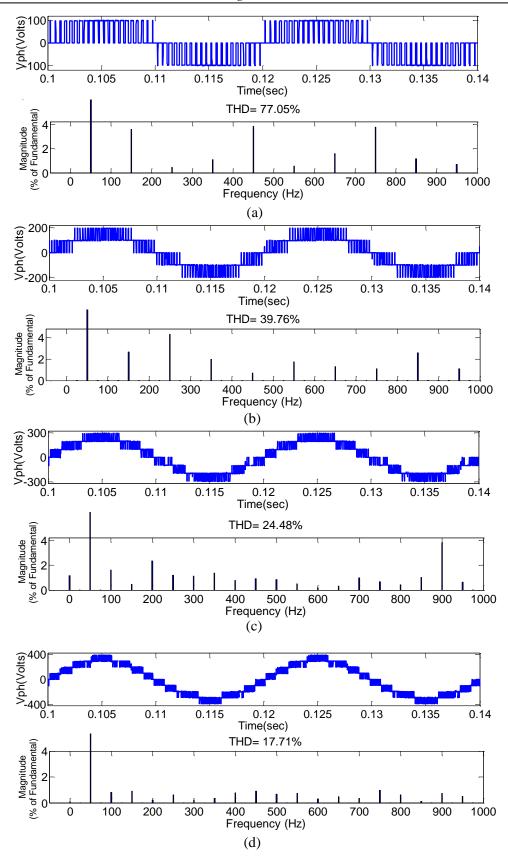

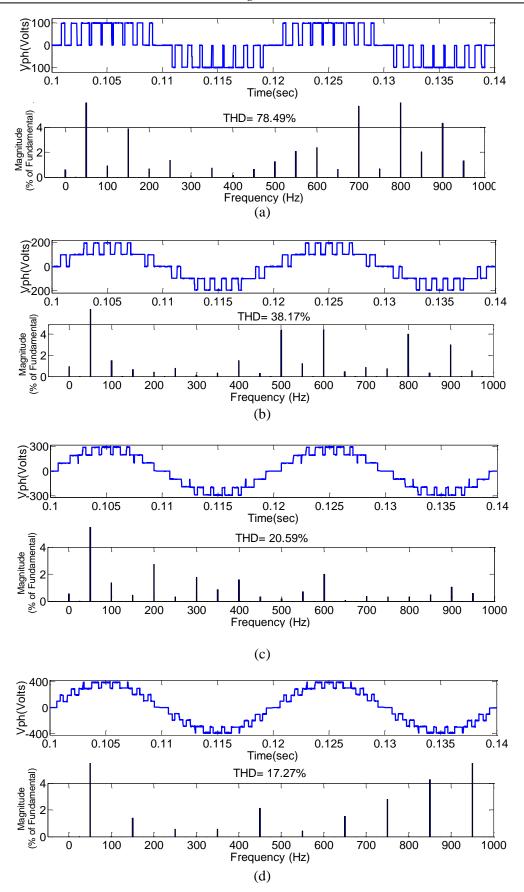

- Phase voltage and THDs for (a) Level-3 (b) Level-5 (c) Level-7 (d) Level-9 5.9 cascaded full-bridge IB inverter using Phase shifted PWM scheme..... 167

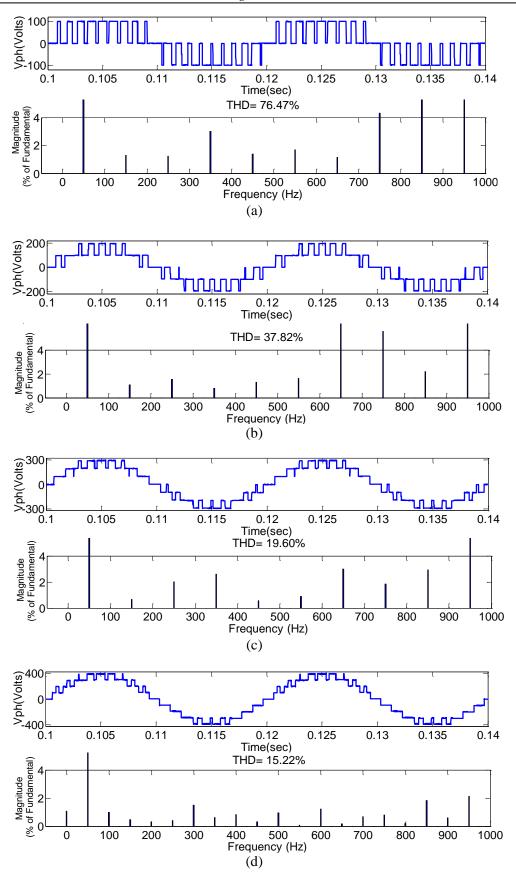

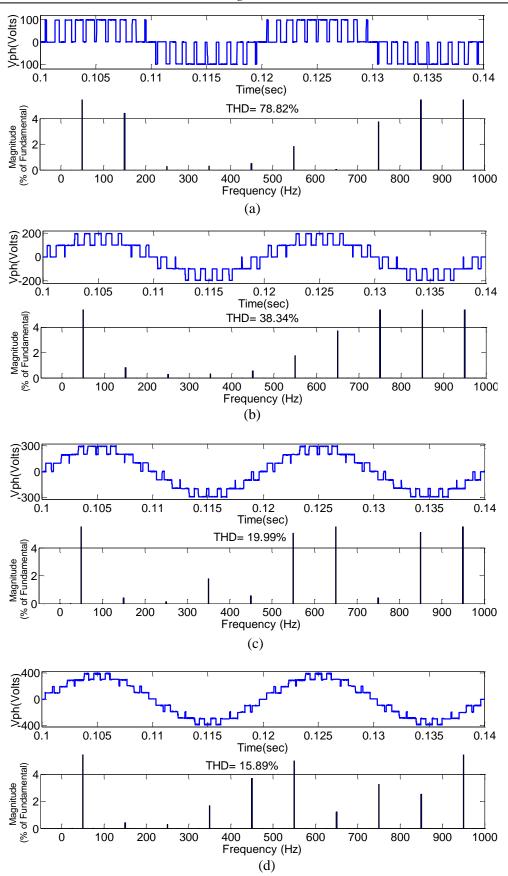

| 5.10 | Phase voltage and THDs for (a) Level-3 (b)Level-5 (c) Level-7 (d) Level-9          |     |

|------|------------------------------------------------------------------------------------|-----|

|      | cascaded full-bridge IB inverter using In phase Disposition (IPD) PWM              |     |

|      | scheme                                                                             | 168 |

| 5.11 | Phase voltage and THDs for (a) Level-3 (b) Level-5 (c) Level-7 (d) Level-9         |     |

|      | cascaded full-bridge IB inverter using Phase Opposition Disposition (POD)          |     |

|      | PWM scheme                                                                         | 169 |

| 5.12 | Phase voltage and THDs for (a) Level-3 (b) Level-5 (c) Level-7 (d) Level-9         |     |

|      | cascaded full-bridge IB inverter using Alternate Phase Opposition                  |     |

|      | Disposition (APOD) PWM scheme.                                                     | 170 |

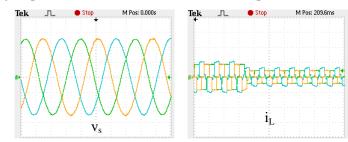

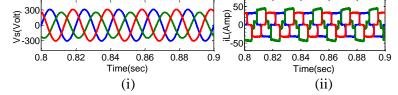

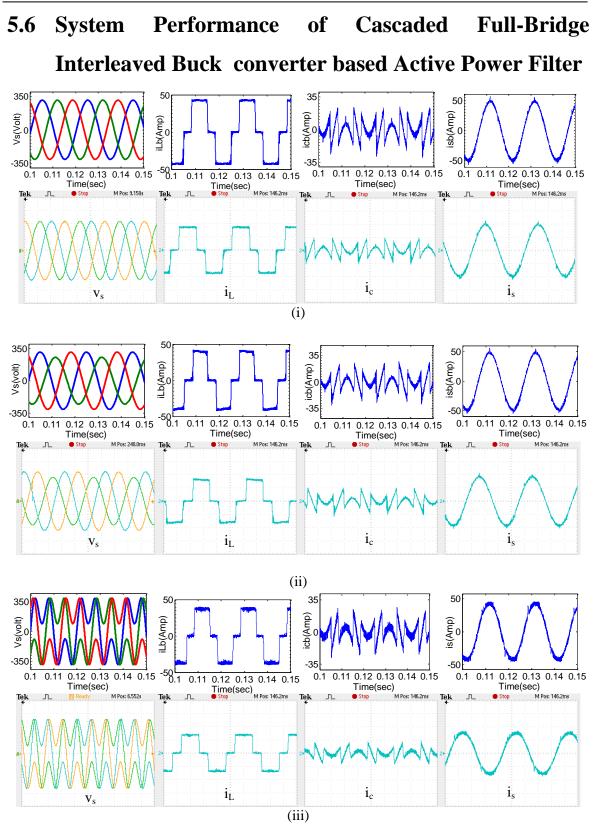

| 5.13 | Simulation and OPAL-RT results of source voltage $(v_s)$ , load current $(i_L)$ ,  |     |

|      | compensating current $(i_c)$ and source current $(i_s)$ for 5-level cascaded full- |     |

|      | bridge interleaved buck active power filter under (i) sinusoidal (ii)              |     |

|      | unbalanced sinusoidal (iii) non-sinusoidal voltage source condition                | 171 |

| 5.14 | THDs of the source current after compensation using cascaded 5-level FB IB         |     |

|      | converter based APF for (a) sinusoidal (b) unbalanced sinusoidal and (c) non-      |     |

|      | sinusoidal voltage source condition                                                | 172 |

## **List of Tables**

| 1.1 | IEEE 519-2014 Standard for harmonic current limits for general distribution |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | systems (120–69,000 V)                                                      | 9   |

| 2.1 | Comparison of conventional and interleaved buck converter                   | 37  |

| 2.2 | Components description of OP5142 Reconfigurable Board                       | 52  |

| 2.3 | Simulation condition parameters for steady state analysis of 2C IB APF      | 56  |

| 2.4 | Source current THD using HBCC p-q control strategy                          | 63  |

| 2.5 | Source current THD using conventional hysteresis band current controller    |     |

|     | ( HBCC) based $i_d$ - $i_q$ control strategy                                | 63  |

| 2.6 | Source current THD using adaptive hysteresis band current controller        |     |

|     | (AHBCC) based $i_d$ - $i_q$ control strategy                                | 63  |

| 2.7 | Simulation condition parameters for dynamic state analysis of 2C IB APF     | 66  |

| 2.8 | Source current THD using conventional hysteresis band current controller    |     |

|     | (HBCC) based $i_d$ - $i_q$ control strategy during dynamic condition        | 71  |

| 2.9 | Source current THD using adaptive hysteresis band current controller based  |     |

|     | (AHBCC) $i_d$ - $i_q$ control strategy during dynamic condition             | 71  |

| 3.1 | Rule Base                                                                   | 88  |

| 3.2 | Parameters value for simulation and real time implementation                | 100 |

| 3.3 | Mamdani fuzzy design parameters                                             | 100 |

| 3.4 | Source current THD using Fuzzy Type-1 different MFs                         | 107 |

| 3.5 | Source current THD using Fuzzy Type-2 different MFs                         | 114 |

| 4.1 | Brief description of the single-phase full-bridge IB APF working modes      | 126 |

| 4.2 | Comparison of various features of 3-phase 4-wire IB APFs topologies         | 132 |

| 4.3 | Parameters value used for various 3-phase 4-wire IB APFs                    | 148 |

| 4.4 | Source current THD before and after compensation using 2C IB APF            | 149 |

| 4.5 | Source current THD before and after compensation using 4-leg IB APF         | 149 |

| 4.6 | Source current THD before and after compensation using 1C 3FB IB APF        | 149 |

| 4.7 | Source current THD before and after compensation FB IB APF            | 149 |

|-----|-----------------------------------------------------------------------|-----|

| 4.8 | Comparative study of 2C IB APF and FB IB-APF for various parameters   | 152 |

| 4.9 | Comparative study of SDP rating for 2C IB APF and FB IB-APF           | 153 |

| 5.1 | THD of the phase voltage of the Level-3, Level-5, Level-7 and Level-9 |     |

|     | cascaded interleaved buck full-bridge inverter.                       | 172 |

## Acronyms

| PQ                                    | Power Quality                                              |

|---------------------------------------|------------------------------------------------------------|

| IEEE                                  | Institute of Electrical and Electronics Engineers          |

| THD                                   | Total Harmonic Distortion                                  |

| IGBT                                  | Insulated Gate Bipolar Transistor                          |

| MOSFET                                | Metal Oxide Semiconductor Field Effect Transistor          |

| CSI                                   | Current Source Inverter                                    |

| VSI                                   | Voltage Source Inverter                                    |

| APF                                   | Active Power Filter                                        |

| UPQC                                  | Unified Power Quality Conditioner                          |

| IB                                    | Interleaved Buck                                           |

| IB APF                                | Interleaved Buck Active Power Filter                       |

| HB IB APF                             | Half Bridge Interleaved Buck Active Power Filter           |

| FB IB APF                             | Full Bridge Interleaved Buck Active Power Filter           |

| 2C IB APF                             | Capacitor Midpoint Split Capacitor Interleaved Buck Active |

|                                       | Power Filter                                               |

| p-q theory                            | Instantaneous Active and Reactive Power Theory             |

| i <sub>d</sub> -i <sub>q</sub> theory | Instantaneous Active and Reactive Current Theory           |

| LPF                                   | Low Pass Filter                                            |

| HPF                                   | High Pass Filter                                           |

| PI                                    | Proportional Integral Controller                           |

| FLC                                   | Fuzzy Logic Controller                                     |

| T1FLC                                 | Type-1 Fuzzy Logic Controller                              |

| T2FLC                                 | Type-2 Fuzzy Logic Controller                              |

| MF                                    | Membership Function                                        |

| UMF                                   | Upper Membership Function                                  |

| LMF                                   | Lower Membership Function                                  |

| LOM              | Largest (Absolute) Value of Maximum                              |

|------------------|------------------------------------------------------------------|

|                  |                                                                  |

| MOM              | Mean value of Maximum                                            |

| FIS              | Fuzzy Inference System                                           |

| BOA              | Bisector of Area                                                 |

| COA              | Centroid of Area                                                 |

| FOU              | Foot Point of Uncertainty                                        |

| NB               | Negative Big                                                     |

| NM               | Negative Medium                                                  |

| NS               | Negative Small                                                   |

| ZE               | Zero                                                             |

| PB               | Positive Big                                                     |

| PM               | Positive Medium                                                  |

| PS               | Positive Small                                                   |

| 4L IB APF        | 4-Leg Interleaved Buck Active Power Filter                       |

| 1C 3FB IB APF    | Single Capacitor Three Full Bridge Interleaved Buck Active Power |

|                  | Filter                                                           |

| FB IB APF        | Full Bridge Interleaved Buck Active Power Filter                 |

| PWM              | Pulse Width Modulation                                           |

| IPD PWM          | In-phase Disposition Pulse Width Modulation                      |

| POD PWM          | Phase Opposition Disposition Pulse Width Modulation              |

| APOD PWM         | Alternate Phase Opposition Disposition Pulse Width Modulation    |

| PS PWM           | Phase Shifted Pulse Width Modulation                             |

| RTDS             | Real Time Digital Simulator                                      |

| HDL              | Hardware Description Language                                    |

| HIL              | Hardware-in-the-Loop                                             |

| FPGA             | Field-Programmable Gate Array                                    |

| JTAG             | Joint Test Action Group                                          |

| CPLD             | Complex Programmable Logic Device                                |

| PCIe             | Peripheral Component Interconnect Express                        |

| I <sup>2</sup> C | Inter Integrated Circuit                                         |

| EEPROM           | Electrically Erasable Programmable Read Only Memory              |

| DSO              | Data Storage Oscilloscope                                        |

| RT-XSG           | Real-Time Xilinx System Generator                                |

|                  |                                                                  |

## Notations

| A                                                   | Type-1 fuzzy set                                                       |

|-----------------------------------------------------|------------------------------------------------------------------------|

| Ã                                                   | Type-2 fuzzy set                                                       |

| $v_a$ , $v_b$ , $v_c$                               | Source voltage (Phase)                                                 |

| $v_0$                                               | Zero-axis reference voltage                                            |

| i <sub>a</sub> , i <sub>b</sub> , i <sub>c</sub>    | Source current (Phase)                                                 |

| i <sub>n</sub>                                      | Source neutral current                                                 |

| $i_{\it La}$ , $i_{\it Lb}$ , $i_{\it Lc}$          | Load current of phase a,b and c                                        |

| i <sub>Ln</sub>                                     | Load neutral current                                                   |

| $i_{\ Llpha}$ , $i_{Leta}$                          | $\alpha$ and $\beta$ -axis reference load current                      |

| i <sub>Ld</sub> , i <sub>Lq</sub>                   | d and $q$ -axis reference load current                                 |

| $\overline{\iota}_{Ld}$ , $\overline{\iota}_{Lq}$   | dc component of $d$ and $q$ -axis load current                         |

| ${	ilde \iota}_{Ld}$ , ${	ilde \iota}_{Lq}$         | ac component of $d$ and $q$ axis load current                          |

| $i^+_{Ld1h}$ , $i^+_{Lq1h}$                         | Transformed dc quantity of first harmonic current of positive sequence |

| i <sub>Ldnh</sub> , i <sub>Lqnh</sub>               | ac component of current must be injected by the active power filter    |

| i <sub>L0</sub>                                     | Zero-axis load current                                                 |

| i <sub>ca</sub> , i <sub>cb</sub> , i <sub>cc</sub> | Compensating current/filter current of phase a, b and c                |

| i <sub>cn</sub>                                     | Neutral compensating current                                           |

| $i^*_{ca}$ , $i^*_{cb}$ , $i^*_{cc}$                | Reference compensating current of phase a, b and c                     |

| i <sup>*</sup> <sub>c0</sub>                        | Zero-axis compensating current                                         |

| ${v}_{lpha}$ , ${v}_{eta}$                          | $\alpha$ and $\beta$ - axis reference phase voltage                    |

| $i^*_{clpha}$ , $i^*_{ceta}$                        | $\alpha$ and $\beta$ - axis reference compensating current             |

| $i_{c0}^*$                                          | Zero-axis reference compensating current                               |

| p,q                                                 | Instantaneous active and reactive power                                |

| $p_0$                                               | Zero-axis instantaneous active power                                   |

|                                                     |                                                                        |

| $ar{p}$ , $ar{p}$    | Average and oscillating component of instantaneous active power |

|----------------------|-----------------------------------------------------------------|

| $\Delta ar{p}$       | Additional average power                                        |

| $ar{p}_0$            | Average zero sequence power                                     |

| $ar{p}_{loss}$       | Losses occurred inside the voltage source inverter              |

| V <sub>dc</sub>      | dc-link voltage                                                 |

| $V_{dc}^*$           | Reference dc-link voltage                                       |

| Ε                    | Error                                                           |

| $\Delta E$           | Change in error                                                 |

| σ                    | Width                                                           |

| $\mu_A(x)$           | Type-1 membership function                                      |

| $\tilde{\mu}_A(x,u)$ | Type-2 membership function                                      |

| Χ                    | Universe of discourse                                           |

### Chapter 1

## Introduction

The advances in power electronics have increased the harmonic contamination in the line current which has encouraged the development of active power filter that are intended to block all non-fundamental current. One of the main concerns in the research of active power filter is reliability. The "shoot-through" phenomenon occurs in the conventional inverter circuit decreases the reliability of the active power filter. To overcome shoot-through, various investigations have been done, out of which, interleaved buck (IB) inverter topology is exceptional and suits to be utilized in the application with the requirement of high reliability and harmonic compensation.