# DEVELOPMENT OF EFFICIENT SOFT SWITCHING SYNCHRONOUS BUCK CONVERTER TOPOLOGIES FOR LOW VOLTAGE HIGH CURRENT APPLICATIONS

Dissertation submitted to the

#### National Institute of Technology Rourkela

in partial fulfilment of the requirements

for the degree of

**Doctor of Philosophy**

in

Electrical Engineering

by

S. Shiva Kumar

(Roll Number: 512EE1014)

Under the supervision of

Prof. Anup Kumar Panda

October, 2016

Department of Electrical Engineering

**National Institute of Technology Rourkela**

February, 2016

#### **Certificate of Examination**

Roll Number: 512EE1014 Name: S.Shiva Kumar

Title of Dissertation: Development of Efficient Soft Switching Synchronous Buck Converter

Topologies for low voltage high current applications

We the below signed, after checking the dissertation mentioned above and the official record book(s) of the student, hereby state our approval of the dissertation submitted in partial fulfillment of the requirements of the degree of Doctor of Philosophy in Electrical Engineering at National Institute of Technology Rourkela. We are satisfied with the volume, quality, correctness, and originality of the work.

Anup Kumar Panda Principal Supervisor

S.Gopalakrishna Member (DSC) S.K.Behera Member (DSC)

N.Islam Member (DSC)

Examiner

K.B.Mohanty Chairman (DSC) Prof. Dr. Anup Kumar Panda

Professor

October, 2016

#### **Supervisor's Certificate**

This is to certify that the work presented in this dissertation entitled "Development of efficient soft switching synchronous buck converter topologies for low voltage high current applications" by "S.Shiva Kumar", Roll Number: 512EE1014, is a record of original research carried out by him under my supervision and guidance in partial fulfilment of the requirements of the degree of Doctor of Philosophy in Electrical Engineering. Neither this dissertation nor any part of it has been submitted for any degree or diploma to any institute or university in India or abroad.

Prof. Anup Kumar Panda

# **Declaration of Originality**

I, S. Shiva Kumar, Roll Number 512EE1014 hereby declare that this dissertation entitled "Development of efficient soft switching synchronous buck converter topologies for low voltage high current applications" represents my original work carried out as a doctoral student of NIT Rourkela and, to the best of my knowledge, it contains no material previously published or written by another person, nor any material presented for the award of any other degree or diploma of NIT Rourkela or any other institution. Any contribution made to this research by others, with whom I have worked at NIT Rourkela or elsewhere, is explicitly acknowledged in the dissertation. The works of other authors cited in this dissertation have been duly acknowledged under the section "Bibliography". I have also submitted my original research records to the doctoral scrutiny committee for evaluation of my dissertation.

I am fully aware that in case of any non-compliance detected in the future, the Senate of NIT Rourkela may withdraw the degree awarded to me on the basis of the present dissertation.

October, 2016 NIT Rourkela

S. Shiva Kumar

## **Acknowledgement**

I express my profound gratitude to Prof. Anup Kumar Panda, Professor, Department of Electrical Engineering for accepting as a student in the Power Electronics group and suggesting me the research topic. I am deeply indebted for his continuous support and encouragement given during the research work. I consider myself fortunate to have worked under his guidance. I am indebted to him for providing all official and laboratory facilities.

I am grateful to the Director, Prof. S.K. Sarangi and Prof. Jitendriya Kumar Satpathy, Head of Electrical Engineering Department, National Institute of Technology, Rourkela, for their kind support and concern regarding my academic requirements.

I gratefully thank to my Doctoral Scrutiny Committee members, Prof. Kanungo Barada Mohanty, Prof. S. Gopala Krishna and Prof. S.K. Behera, for their valuable suggestions and contributions of this dissertation. I express my thankfulness to the faculty and staff members of the Electrical Engineering Department for their continuous encouragement and suggestions.

At this point, I wish to specifically emphasize my gratitude for all the help and encouragement I received from my supervisor Prof. Anup Kumar Panda. During communication of the journal publications, his guidance and insight gave me encouragement to proceed with confidence towards publishing in the reputed journals of this work. Also, personally at hard times my supervisor provided great moral support.

I am especially indebted to all my colleagues in the power electronics group. I would like to thank my seniors Dr. Y Suresh, Dr. N. Rajendra Prasad and Dr. Tejavathu Ramesh for their help and support throughout my research work.

I am especially grateful to Power Electronics Laboratory staff Mr. Rabindra Nayak without him the work would have not progressed.

I would also like to thank my friends, Mr. D Koteswarao, Mr. Kishore Ragi, Mr. K. Vinay Sagar, Mr. G. Kiran Kumar, Mr. Muralidhar Killi, Mr. Prasanth Rajam, Mr. K. Pavan, Mr. D.Dinesh, Mr. J. Naresh, Ms. Sushree Sangitha Patnaik, Mr. Nishanth Patnaik, Ms. Ranjeeta Patel, Ms. Richa Patnaik, Mr. Joseph Sanam, Mr. Mrutyunjay, Mr. Trilochan, Mr. Pratap, Mr. Ashish, Mr. Kishore thakre, Ms. C. Aditi, Mr. Ashwini Nayak for extending their technical and personal support.

vi Acknowledgement

I express my deep sense of gratitude and reverence to my beloved father Sri. Sarode

Rajeshwar, Mother Smt. S. Vijaya Laxmi, brothers Mr.S.Krishna and Mr. S. Raju, brother-in-

law Dr. C. Srinivas and sister Mrs. C. Indira who supported and encouraged me all the

time, no matter what difficulties I encountered. I especially thank my wife S. Chitra, her

support, encouragement, patience and unwavering love, provided strength to focus on the

work. I would like to express my greatest admiration to all my family members and relatives

for their positive encouragement that they showered on me throughout this research work.

Without my family's sacrifice and support, this research work would not have been possible.

It is a great pleasure for me to acknowledge and express my appreciation to all my well-

wishers for their understanding, relentless supports, and encouragement during my research

work. Last but not the least, I wish to express my sincere thanks to all those who helped me

directly or indirectly at various stages of this work.

Above all, I would like to thank The Almighty God for the wisdom and perseverance that

he has been bestowed upon me during this research work, and indeed, throughout my life.

October, 2016

NIT Rourkela

S. Shiva Kumar

Roll Number: 512EE1014

### **Abstract**

Switched mode power supplies (SMPS) have emerged as the popular candidate in all the power processing applications. The demand is soaring to design high power density converters. For reducing the size, weight, it is imperative to channelize the power at high switching frequency. High switching frequency converters insist upon soft switching techniques to curtail the switching losses. Several soft switching topologies have been evolved in the recent years.

Nowadays, the soft switching converters are vastly applied modules and the demand is increasing for high power density and high efficiency modules by minimizing the conduction and switching losses. These modules are generally observed in many applications such as laptops, desktop processors for the enhancement of the battery life time. Apart from these applications, solar and spacecraft applications demand is increasing progressively for stressless and more efficient modules for maximizing the storage capacity which inturn enhances the power density that improves the battery life to supply in the uneven times.

Modern trends in the consumer electronic market focus increases in the demand of lower voltage supplies. Conduction losses are significantly reduced by synchronous rectifiers i.e., MOSFET's are essentially used in many of the low voltage power supplies. Active and passive auxiliary circuits are used in tandem with synchronous rectifier to diminish the crucial loss i.e., switching loss and also it minimizes the voltage and current stresses of the semiconductor devices.

The rapid progress in the technology and emerging portable applications poses serious challenges to power supply design engineers for an efficient power converter design at high power density. The primary aim is to design and develop high efficiency, high power density topologies like: buck, synchronous buck and multiphase buck converters with the integration of soft switching techniques to minimize conduction and switching losses sustaining the voltage and current stresses within the tolerable range.

In this work, two ZVT-ZCT PWM synchronous buck converters are introduced, one with active auxiliary circuit and the other one with passive auxiliary circuit. The operating principle and comprehensive steady state analysis of the ZVT-ZCT PWM synchronous buck converters are presented. The converters are designed to have high efficiency and low voltage that is suitable for high power density application. The semiconductor devices used in the topologies in addition to the main switch operate with soft switching conditions. The

viii Abstract

topologies proposed render a large overall efficiency in contrast to the contemporary topologies. In addition the circuit's size is less, reliable and have high performance-cost ratio.

The new generation microprocessor demands the features such as low voltage, high current, high power density and high efficiency etc., in the design of power supplies. The supply voltage for the future generation microprocessors must be low, in order to decrease the power consumption. The voltage levels are dripping to a level even less than 0.7V, and the power consumption increases as there is an increase in the current requirement for the processor. In order to meet the demands of the new generation microprocessor power supply, a soft switching multiphase PWM synchronous buck converter is proposed. The losses in the proposed topology due to increasing components are pared down by the proposed soft switching technique.

The proposed converters in this research work are precisely described by the mathematical modelling and their operational modes. The practicality of the proposed converters for different applications is authenticated by their simulation and experimental results.

Keywords: Soft switching; Zero Voltage Transition; Zero Current Transition; Pulse-width modulation; Synchronous Buck Converter; Multphase Buck Converter.

## **Notations**

$R_{dson}$  -On resistance of MOSFET

Coss -MOSFET Output Capacitance

v<sub>phase</sub> -Instantaneous voltage at output

I<sub>L</sub> -Load current

V<sub>D</sub> -Drain to source voltage in MOSFET

P<sub>c</sub> -Conduction loss

P<sub>BD</sub> -Body diode power loss

$I_{SD}$  -Body diode current

$t_D$  -Body diode on time

$T_{Fall}$  -Fall time  $T_{rise}$  -Rise time

f<sub>SW</sub> -Switching frequency

Q<sub>oss</sub> -Output charge of MOSFET

Q<sub>rr</sub> -Reverse recovery charge

P<sub>MOSFET</sub> -Total loss in MOSFET

P<sub>Switching</sub> -Switching loss in MOSFET

$P_{conduction} \qquad \quad -Conduction \ loss$

$L_r \qquad \quad -Resonant \ Inductor$

$C_r$  -Resonant Capacitor

L<sub>b</sub> -Auxiliary Inductor

$C_{s1}$  -Auxiliary Capacitor

$L_0 \qquad \quad \text{-Filter Inductor} \quad$

C<sub>0</sub> -Filter Capacitor

D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub> -Auxiliary circuit diodes

V<sub>in</sub> -Input Voltage

V<sub>0</sub> -Output Voltage

I<sub>0</sub> -Output Load current

R<sub>0</sub> -Output load resistance

V<sub>g</sub> -Gate pulse voltage

$V_{g(aux)}$  -Gate pulse voltage for auxiliary switch

$I_{Lr}$  -Current through resonant inductor

List of Symbols x

$V_{Cs1}$  -Voltage across the capacitor  $C_{s1}$

$V_{cr}$  -Voltage across the resonant capacitor  $C_r$

D<sub>min</sub> -Minimum duty cycle

I<sub>0max</sub> -Maximum current of inductor L

$\Delta p$  -Energy stored in each cycle in the resonant capacitor  $C_r$

L<sub>b</sub> -Auxiliary circuit buffer inductor

C<sub>b</sub> -Auxiliary circuit buffer capacitor

$D_1, D_2$  -Schottky diodes in the auxiliary circuit

$D_{s1}$ ,  $D_{s2}$  -Body diodes of the MOSFET switches  $S_1$ ,  $S_2$ .

$t_{01}$ ,  $t_{12}$ , etc -Time interval between modes

$I_{0(avg)}$  -Average output current

au -Time period of one switching cycle

I<sub>Lrmax</sub> -Maximum inductor current

$V_{Crmax}$  -Maximum voltage across capacitor  $C_r$

ω -Resonant frequency

Z -Characteristic Impedance

$t_1, t_2$ , etc. -Instants of Time in different modes

$L_1, L_2, L_3$  -Filter Inductors

$i_{resonant}$  -Resonant current

S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub> etc., -MOSFET switches

$C_{s1}$ ,  $C_{s3}$ ,  $C_{s5}$  -Auxiliary circuit capacitors

R -Body diode resistance

## **Abbreviations**

SMPS -Switch mode power supplies

BJT -Bipolar junction transistor

IGBT -Insulated -gate bipolar transistor

MOSFET -Metal-Oxide-Semiconductor Field-Effect-Transistor

PWM - Pulse Width Modulation

AMD - Advanced Micro Devices

VR - Voltage Regulator

VRM - Voltage Regulator Module

POL - Point of load

DC-DC - Direct Current - Direct Current

RR - Reverse recovery

SR - Synchronous Rectifier

ZVT - Zero Voltage Transition

ZCT - Zero Current TransitionZCZV - Zero current Zero voltageZVS - Zero Voltage Switching

ZCS - Zero Current Switching

EMI - Electromagnetic Interference

MRC -Multi-resonant converter

QRC - Quasi Resonant Converter

QSC - Quasi-Square-wave Converters

DSP - Digital Signal Processors

PSIM - Power Simulation

SBC - Synchronous Buck Converter

PCB - Printed Circuit Board

# **Contents**

| Supe | ervisor's | Certificate                                                              | iii |

|------|-----------|--------------------------------------------------------------------------|-----|

| Decl | aration o | of Originality                                                           | iv  |

| Ack  | nowledg   | ement                                                                    | v   |

| Abst | ract      |                                                                          | vii |

| Nota | tions     |                                                                          | ix  |

| Abb  | reviation | is                                                                       | xi  |

| Con  | ents      |                                                                          | xii |

| List | of Figur  | es                                                                       | xv  |

| List | of Table  | s                                                                        | xix |

| CHA  | APTER     | 1: INTRODUCTION                                                          | 1   |

| 1.1  | Introdu   | action                                                                   | 1   |

| 1.2  | Losses    | in converters                                                            | 4   |

| 1.3  | Contra    | st between different resonant converters                                 | 6   |

| 1.4  | Motiva    | ntion                                                                    | 7   |

| 1.5  | Object    | ives                                                                     | 8   |

| 1.6  | Organi    | sation of the thesis                                                     | 9   |

| (    | CHAPT     | ER 2: PERFORMANCE ENHANCEMENT OF SYNCHRONOUS BUCK                        |     |

|      |           | CONVERTER WITH INTEGRATION OF ACTIVE AUXILIARY                           |     |

|      |           | CIRCUIT                                                                  | 10  |

| 2.1  | Introdu   | action                                                                   | 10  |

| 2.2  | -         | ogy description                                                          |     |

| 2.3  | -         | ional modes                                                              |     |

| 2.4  | Design    | Procedure                                                                |     |

|      | 2.4.1     | Snubber Capacitor $C_{s1}$ , Resonant Capacitor $C_r$ and Inductor $L_r$ |     |

|      | 2.4.2     | Inductor L <sub>b</sub>                                                  | 26  |

| 2.5  | Simula    | ation and Experimental Results                                           | 26  |

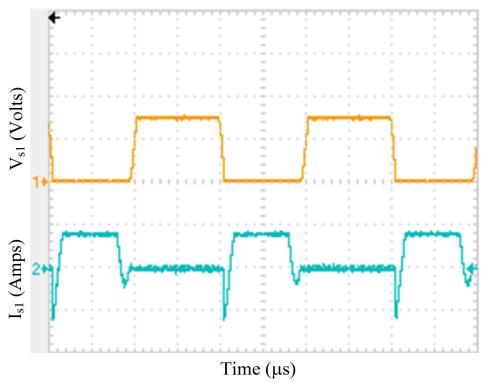

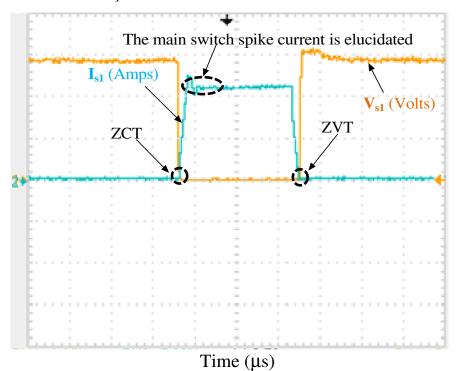

|      | 2.5.1     | Main switch S <sub>1</sub>                                               | 34  |

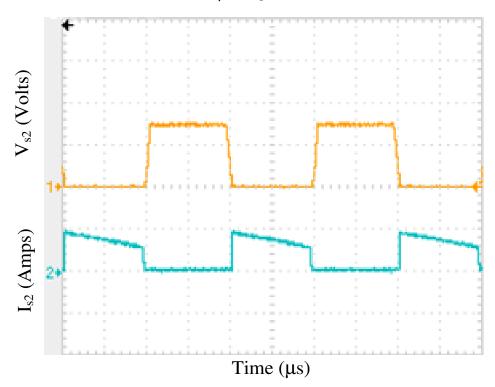

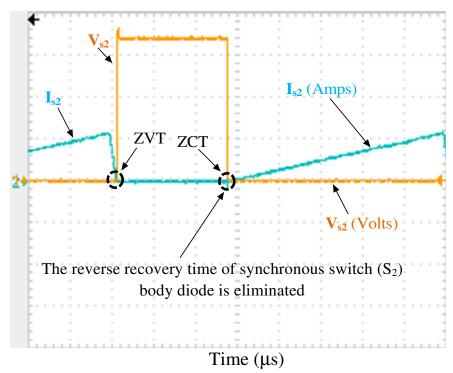

|      | 2.5.2     | Synchronous switch S <sub>2</sub>                                        | 34  |

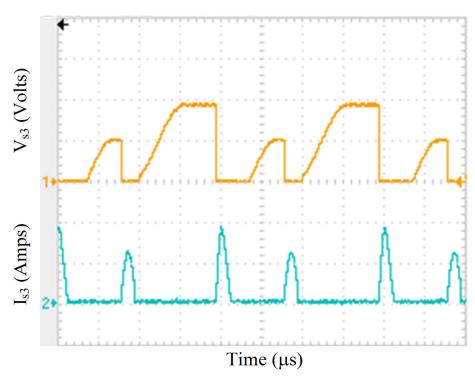

|      | 2.5.3     | Auxiliary switch S <sub>3</sub>                                          | 34  |

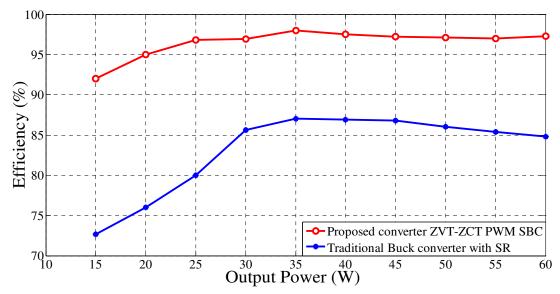

| 2.6  | Efficie   | ncy curve                                                                | 34  |

|      | 2.6.1     | Contrast with contemporary topologies                                    | 35  |

|      | 2.6.2     | Overview of the contemporary topologies                                  | 36  |

| 27   | Summ      | O.W.                                                                     | 38  |

| CHA  | APTER 3: A PASSIVE AUXILIARY CIRCUIT INTEGRATED WITH SYNO  | CHRONOUS |

|------|------------------------------------------------------------|----------|

|      | BUCK CONVERTER FOR HIGH CURRENT APPLICATION                | 39       |

| 3.1  | Introduction                                               | 39       |

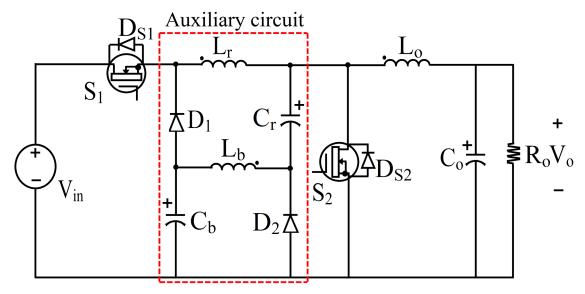

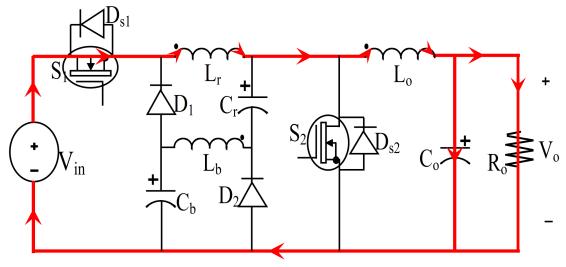

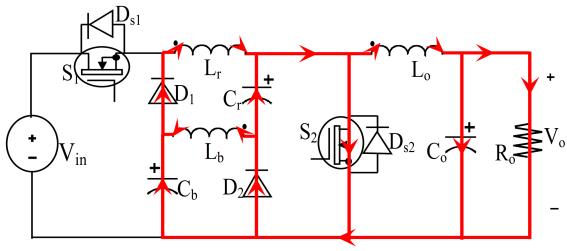

| 3.2  | Topology description                                       | 40       |

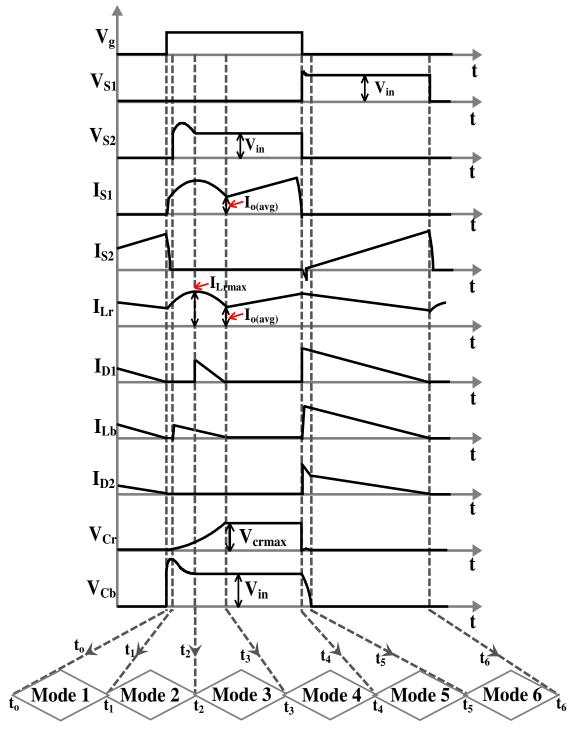

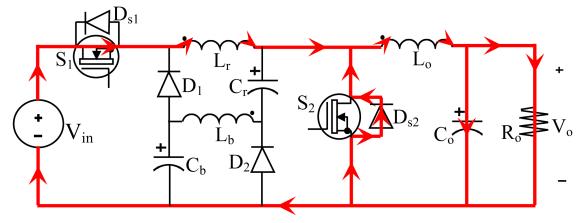

| 3.3  | Operational modes                                          | 41       |

| 3.4  | Output voltage                                             | 47       |

| 3.5  | Design Procedure                                           | 48       |

|      | 3.5.1 Resonant Inductor L <sub>r</sub>                     | 48       |

|      | 3.5.2 Buffer Inductor L <sub>b</sub>                       | 48       |

|      | 3.5.3 Snubber Capacitor C <sub>b</sub>                     | 48       |

|      | 3.5.4 Resonant Capacitor C <sub>r</sub>                    | 49       |

| 3.6  | Simulation and Experimental Results                        | 49       |

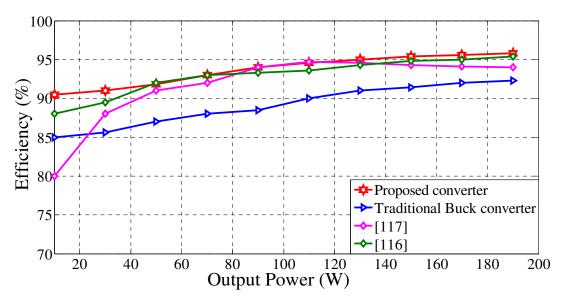

| 3.7  | Efficiency curve                                           | 57       |

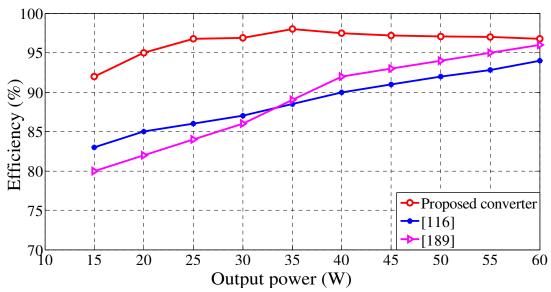

|      | 3.7.1 Contrast with contemporary topologies                | 57       |

|      | 3.7.2 Overview of the contemporary topologies              | 58       |

| 3.8  | Summary                                                    | 61       |

| CHA  | APTER 4: A NEW MULTIPHASE SYNCHRONOUS BUCK CONVERTER       |          |

|      | INTEGRATED WITH ACTIVE AUXILIARY CIRCUIT FOR PO            | RTABLE   |

|      | APPLICATIONS                                               | 62       |

| 4.1  | Introduction                                               | 62       |

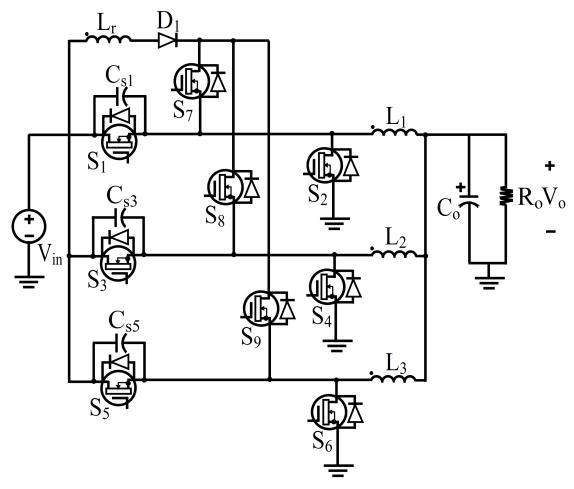

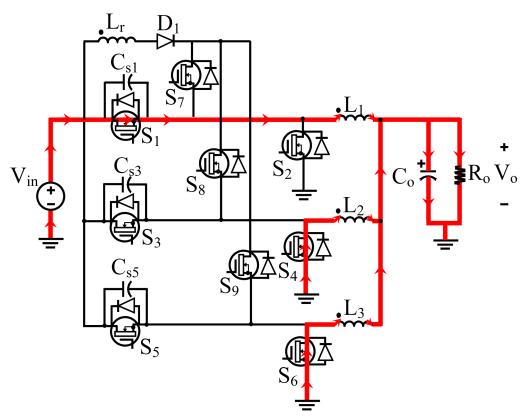

| 4.2  | Topology description                                       | 63       |

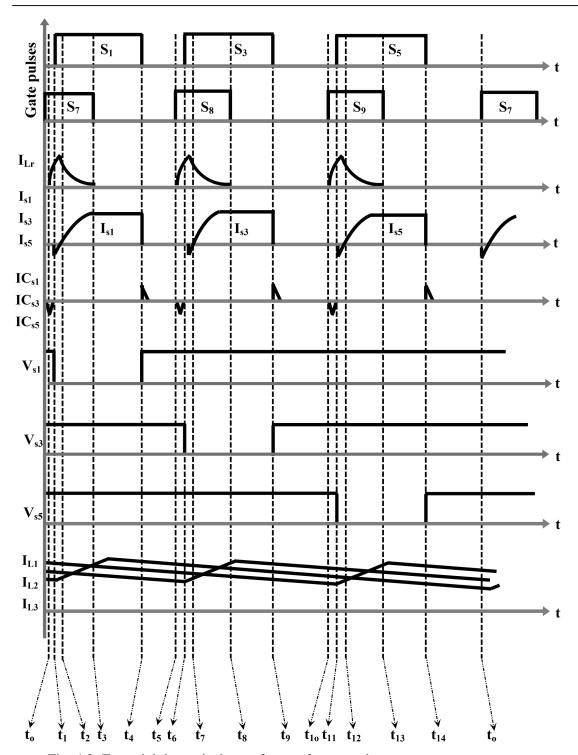

| 4.3  | Operational modes                                          | 65       |

| 4.4  | Output voltage                                             | 71       |

| 4.5  | Design Procedure                                           | 72       |

|      | 4.5.1 Resonant Capacitor C <sub>s1</sub>                   | 72       |

|      | 4.5.2 Resonant Inductor L <sub>r</sub>                     | 72       |

| 4.6  | Simulation and Experimental Results                        | 72       |

| 4.7  | Efficiency curve                                           | 87       |

|      | 4.7.1 Contrast between proposed converters                 | 87       |

| 4.8  | Summary                                                    | 88       |

| CHA  | APTER 5: CONCLUSIONS AND FUTURE SCOPE                      | 89       |

| 5.1  | Conclusions                                                | 89       |

| 5.2  | Scope for Future Work                                      | 90       |

|      | 5.2.1 Control issues:                                      | 91       |

|      | 5.2.2 Parasitic effects in the components:                 | 91       |

|      | 5.2.3 Designing the converter at high switching frequency: | 91       |

| Bibl | liography                                                  | 93       |

| Diss | semination                                                 | 109      |

# **List of Figures**

| 1.1     | Basic Resonant switches                                                                                                   |

|---------|---------------------------------------------------------------------------------------------------------------------------|

| 1.1 (a) | Zero current resonant switch                                                                                              |

| 1.1 (b) | Zero voltage resonant switch                                                                                              |

| 1.2     | Intel's road map for the processors required current and voltage4                                                         |

| 1.3     | Switching losses in the conventional and resonant converter6                                                              |

| 2.1     | Proposed ZVT-ZCT PWM Synchronous buck converter with active auxiliary circuit12                                           |

| 2.2     | Essential theoretical waveforms of proposed converter                                                                     |

| 2.3 (a) | Modes of operation: Mode 1 ( $t_0 - t_1$ )                                                                                |

| 2.3 (b) | Modes of operation: Mode 2 $(t_1 - t_2)$                                                                                  |

| 2.3 (c) | Modes of operation: Mode 3 $(t_2-t_3)$                                                                                    |

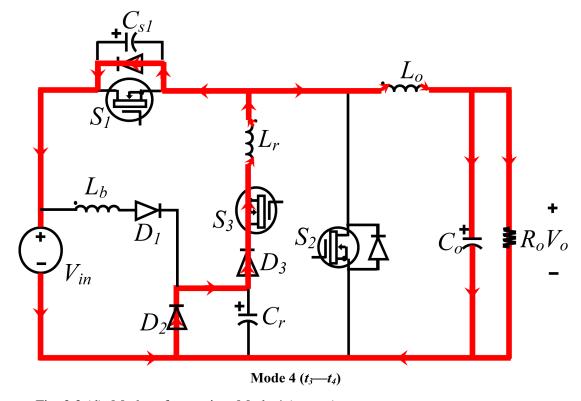

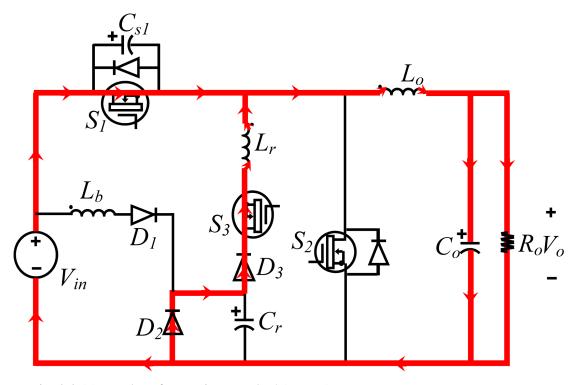

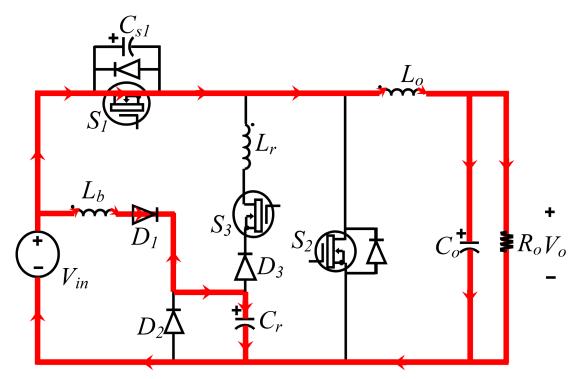

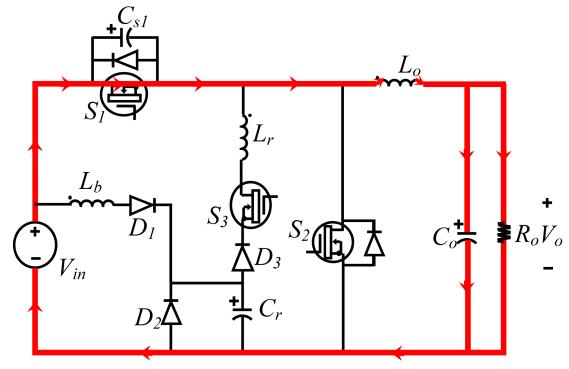

| 2.3 (d) | Modes of operation: Mode 4 $(t_3 - t_4)$                                                                                  |

| 2.3 (e) | Modes of operation: Mode 5 (t <sub>4</sub> —t <sub>5</sub> )18                                                            |

| 2.3 (f) | Modes of operation: Mode 6 (t <sub>5</sub> —t <sub>6</sub> )19                                                            |

| 2.3 (g) | Modes of operation: Mode 7 ( $t_6$ — $t_7$ )                                                                              |

| 2.3 (h) | Modes of operation: Mode 8 (t <sub>7</sub> — t <sub>8</sub> )                                                             |

| 2.3 (i) | Modes of operation: Mode 9 (t <sub>8</sub> —t <sub>9</sub> )21                                                            |

| 2.3 (j) | Modes of operation: Mode 10 ( $t_9$ — $t_{10}$ )                                                                          |

| 2.3 (k) | Modes of operation: Mode 11 (t <sub>10</sub> —t <sub>11</sub> )23                                                         |

| 2.3 (1) | Modes of operation: Mode 12 (t <sub>11</sub> — t <sub>12</sub> )24                                                        |

| 2.3 (m) | Modes of operation: Mode 13 (t <sub>12</sub> —t <sub>13</sub> )24                                                         |

| 2.3 (n) | Modes of operation: Mode 14 (t <sub>13</sub> —t <sub>14</sub> )25                                                         |

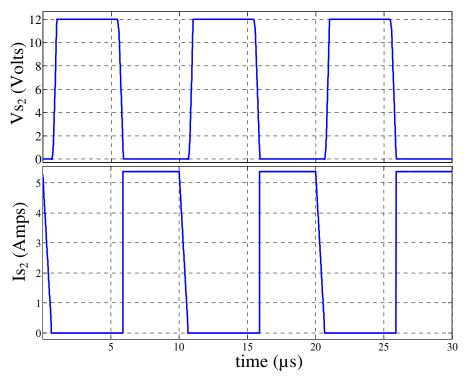

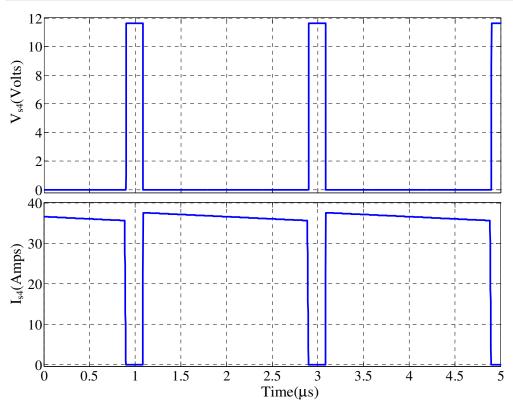

| 2.4 (a) | Simulated voltage and current waveforms of main switch $S_1$ : $V_{s1}$ in Volts and $I_{s1}$ in                          |

|         | Amps27                                                                                                                    |

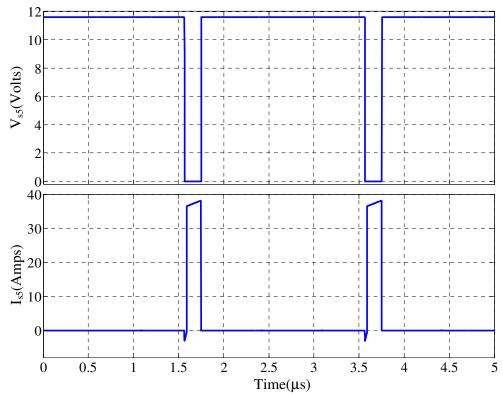

| 2.4 (b) | Simulated voltage and current waveforms of synchronous switch $S_2$ : $V_{s2}$ in Volts and                               |

|         | I <sub>s2</sub> in Amps                                                                                                   |

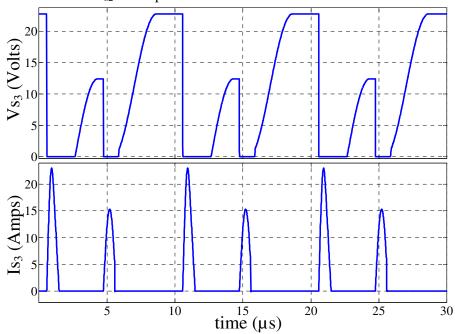

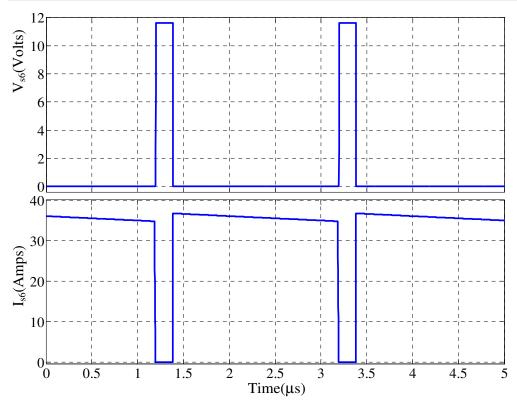

| 2.4 (c) | Simulated voltage and current waveforms of auxiliary switch S <sub>3</sub> : V <sub>s3</sub> in Volts and I <sub>s3</sub> |

| . ,     | in Amps                                                                                                                   |

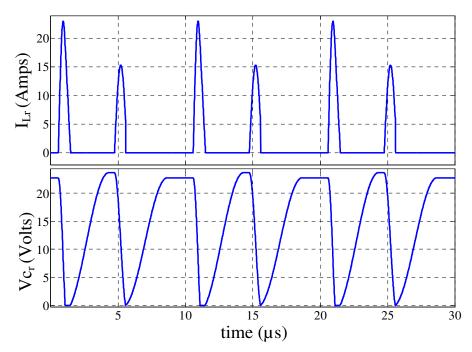

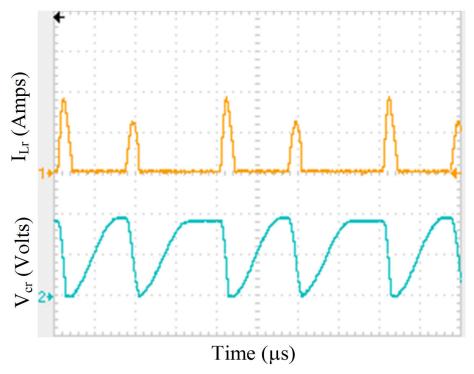

| 2.4 (d) | Simulated current and voltage waveforms of inductor $L_r$ and resonant capacitor $C_r$ : $I_{Lr}$                         |

| · /     | in Amps and V <sub>Cr</sub> in Volts.                                                                                     |

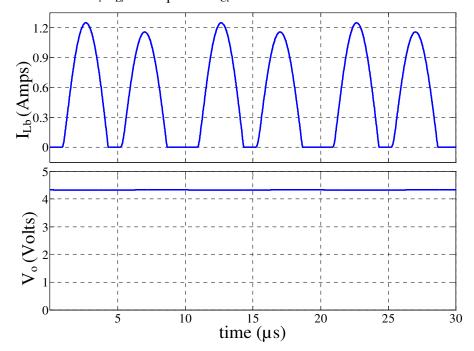

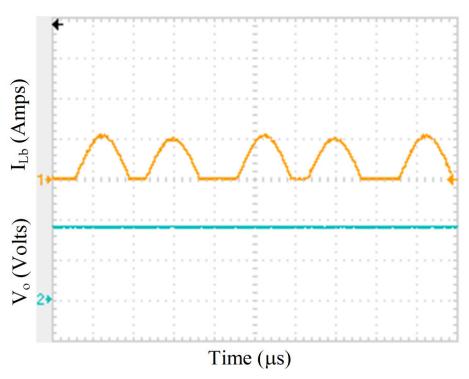

| 2.4 (e) | Simulated current and voltage waveforms of inductor L <sub>b</sub> and output capacitor C <sub>o</sub> : I <sub>Lb</sub>  |

| (-)     | in Amps and V <sub>o</sub> in Volts.                                                                                      |

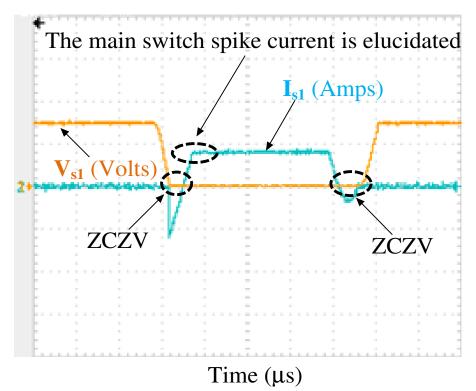

| 2.5 (a) | Experimental voltage and current waveform of Main switch S <sub>1</sub> : [Vs <sub>1</sub> : 60V/Div; Is <sub>1</sub> :   |

| ()      | 5A/Div: time: 2.5us/Divl                                                                                                  |

xvii List of figures

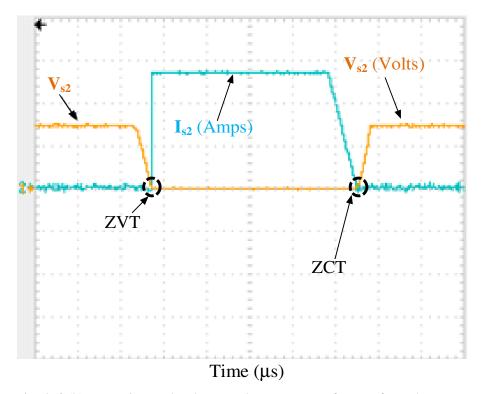

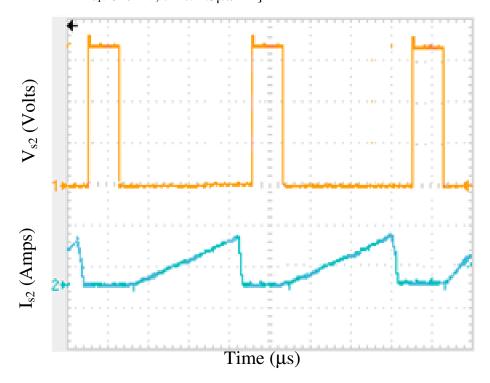

| 2.5 (b) | Experimental voltage and current waveform of synchronous switch S <sub>2</sub> : [Vs <sub>2</sub> : 60V/Div; Is <sub>2</sub> : 5A/Div; time: 2.5µs/Div] | 30 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

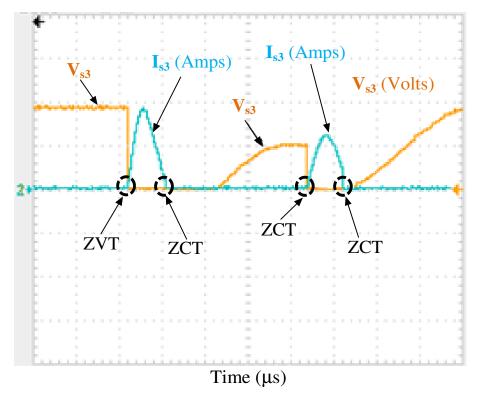

| 2.5 (a) | Experimental voltage and current waveforms of auxiliary switch $S_3$ exemplifying soft                                                                  | 30 |

| 2.3 (C) | switching conditions [Vs <sub>3</sub> :90V/Div; Is <sub>3</sub> :6A/Div; time:0.1µs/Div]                                                                | 31 |

| 2.5 (d) | Experimental current and voltage waveform of inductor $L_r$ and resonant capacitor $C_r$ :                                                              |    |

| , ,     | [I <sub>Lr</sub> : 6A/Div; V <sub>cr</sub> : 100V/Div; time: 2.5µs/Div]                                                                                 | 31 |

| 2.5 (e) | Experimental current and voltage waveform of inductor $L_b$ and output capacitor $C_o$ :                                                                |    |

| ( )     | [I <sub>Lb</sub> : 1.5A/Div; V <sub>o</sub> : 20V/Div; time: 2.5us/Div]                                                                                 | 32 |

| 2.6 (a) | Experimental voltage and current waveforms of main switch $S_1$ exhibits soft                                                                           |    |

| ,       | switching conditions [Vs <sub>1</sub> :50 V/Div; Is <sub>1</sub> : 5A/Div; time: 0.1µs/Div]                                                             | 32 |

| 2.6 (b) | Experimental voltage and current waveforms of synchronous switch $S_2$ exhibits soft                                                                    |    |

| . ,     | switching conditions [Vs <sub>2</sub> :50V/Div; Is <sub>2</sub> :5A/Div; time: 0.1µs/Div]                                                               | 33 |

| 2.6 (c) | Experimental voltage and current waveforms of auxiliary switch S <sub>3</sub> exemplifying soft                                                         |    |

|         | switching conditions [Vs <sub>3</sub> :90V/Div; Is <sub>3</sub> :6A/Div; time: 0.1µs/Div]                                                               | 33 |

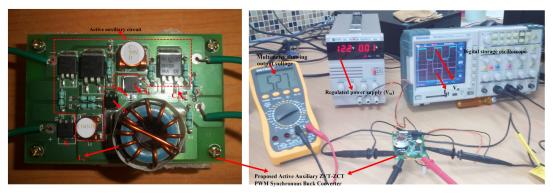

| 2.7     | Experimental setup of Proposed ZVT-ZCT PWM synchronous Buck Converter                                                                                   |    |

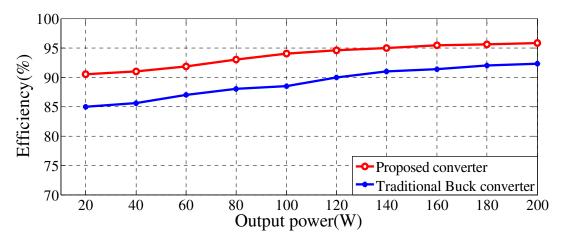

| 2.8     | Efficiency curve of the proposed converter in comparison with traditional buck                                                                          |    |

|         | converter                                                                                                                                               | 35 |

| 2.9     | Circuit diagram of the topology proposed by S. Urgun [116]                                                                                              | 36 |

| 2.10    | Circuit diagram of the topology proposed by Hong Tzer Yang [117                                                                                         | 37 |

| 2.11    | Efficiency curve of the proposed converter in contrast with contemporary topologies                                                                     | 37 |

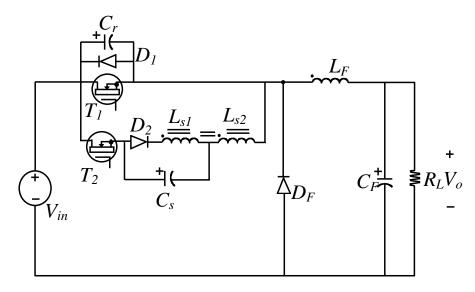

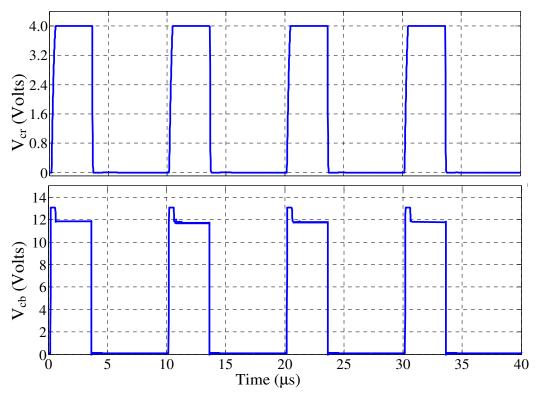

| 3.1     | Proposed ZVT-ZCT PWM Synchronous buck converter with passive auxiliary circuit                                                                          | 40 |

| 3.2     | Essential theoretical waveforms of proposed converter                                                                                                   | 41 |

| 3.3 (a) | Modes of operation: Mode 1 (t <sub>0</sub> —t <sub>1</sub> )                                                                                            | 42 |

| 3.3 (b) | Modes of operation: Mode 2 (t <sub>1</sub> — t <sub>2</sub> )                                                                                           | 43 |

| 3.3 (c) | Modes of operation: Mode 3 (t <sub>2</sub> — t <sub>3</sub> )                                                                                           | 43 |

| 3.3 (d) | Modes of operation: Mode 4 (t <sub>3</sub> — t <sub>4</sub> )                                                                                           | 44 |

| 3.3 (e) | Modes of operation: Mode 5 (t <sub>4</sub> — t <sub>5</sub> )                                                                                           | 45 |

| 3.3 (f) | Modes of operation: Mode 6 (t <sub>5</sub> —t <sub>6</sub> )                                                                                            | 46 |

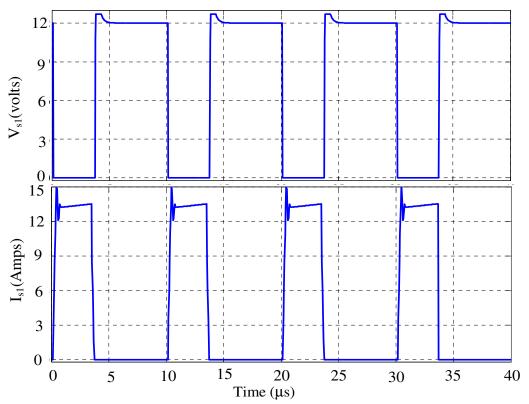

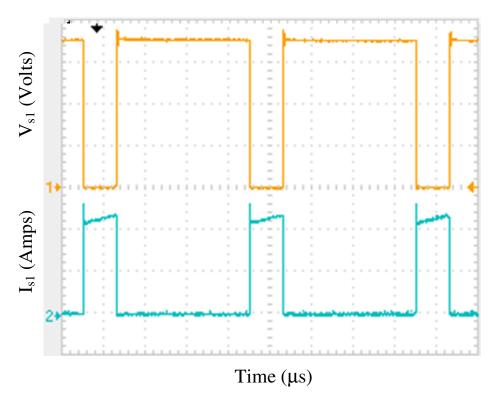

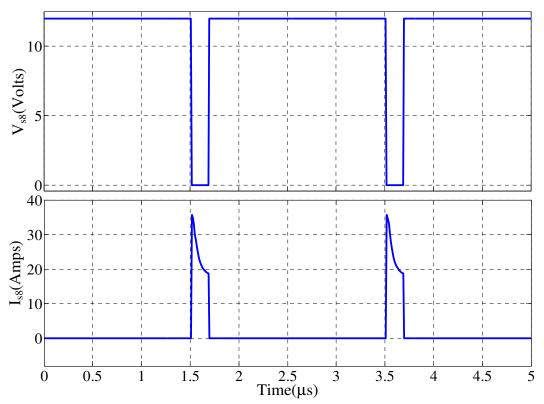

| 3.4 (a) | Simulated voltage and current waveforms of synchronous switch $S_1$ : $V_{s1}$ in Volts and                                                             |    |

|         | I <sub>s1</sub> in Amps.                                                                                                                                | 50 |

| 3.4 (b) | Simulated voltage and current waveforms of synchronous switch S2: Vs2 in Volts and                                                                      |    |

|         | I <sub>s2</sub> in Amps.                                                                                                                                | 50 |

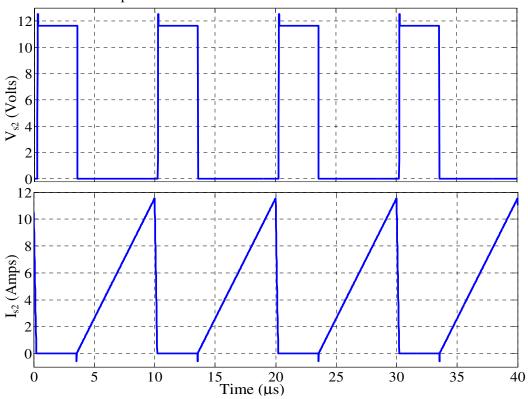

| 3.4 (c) | Simulated voltage waveforms of resonant capacitor and snubber capacitor C <sub>r</sub> and C <sub>b</sub> :                                             |    |

|         | V <sub>cr</sub> and V <sub>cb</sub> in Volts                                                                                                            | 51 |

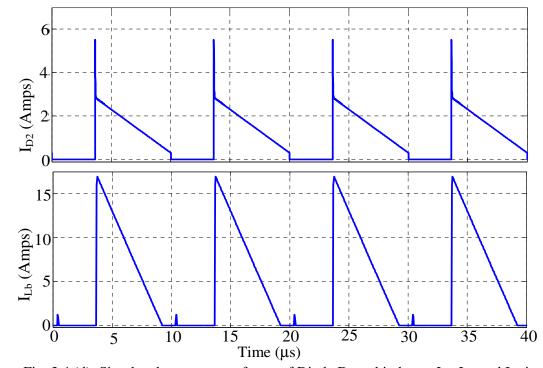

| 3.4 (d) | Simulated current waveforms of Diode D <sub>2</sub> and inductor L <sub>b</sub> : I <sub>D2</sub> and I <sub>Lb</sub> in Amps                           | 51 |

| 3.4 (e) | Simulated current waveform of resonant inductor L <sub>T</sub> : I <sub>LT</sub> in Amps                                                                | 52 |

<u>List of figures</u> xviii

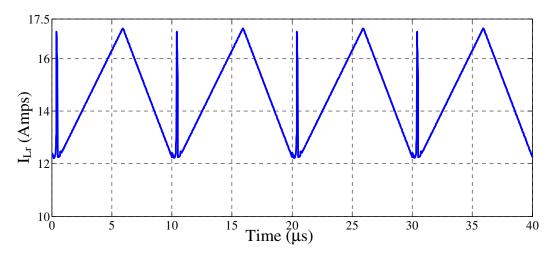

| 3.5     | Experimental setup of Proposed ZVT-ZCT PWM synchronous Buck Converter52                                          |

|---------|------------------------------------------------------------------------------------------------------------------|

| 3.6 (a) | Experimental voltage and current waveform of Main switch $S_1$ : [Vs <sub>1</sub> : 3.42V/Div; Is <sub>1</sub> : |

|         | 6A/Div; time: 2.5μs/Div]53                                                                                       |

| 3.6 (b) | Experimental voltage and current waveform of synchronous switch $S_2$ : $[Vs_2:$                                 |

|         | 3.42V/Div; Is <sub>2</sub> : 8A/Div; time: 2.5µs/Div]53                                                          |

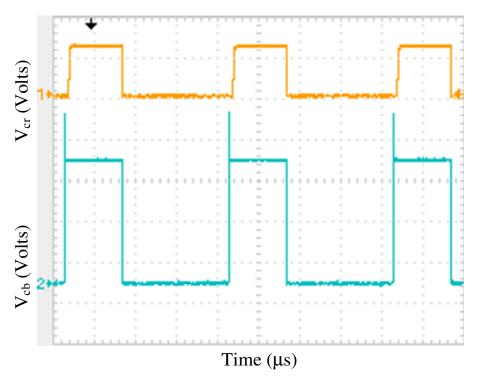

| 3.6 (c) | Experimental voltage waveforms of resonant capacitor $C_r$ and buffer capacitor $C_b  S_3$ :                     |

|         | [V <sub>cr</sub> : 3V/Div; V <sub>cb</sub> : 4V/Div; time: 2.5µs/Div]54                                          |

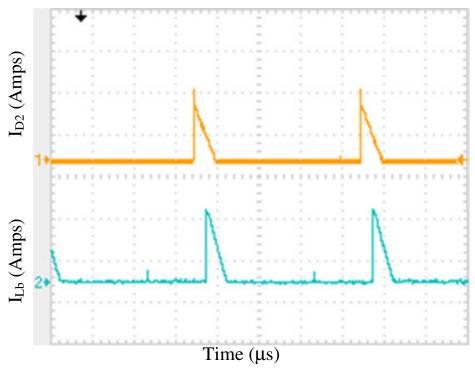

| 3.6 (d) | Experimental current waveforms of diode $D_2$ and inductor $L_b$ : $[I_{Lb}$ : $10A/Div; I_{D2}$ :               |

|         | 3.5A/Div; time: 2.5us/Div]54                                                                                     |

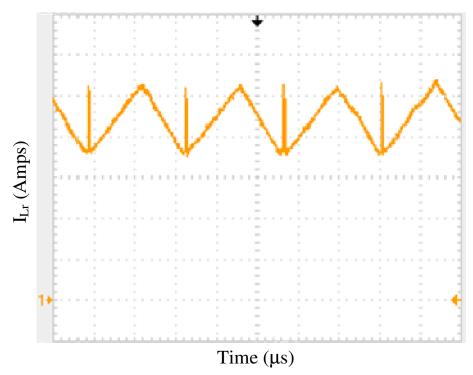

| 3.6 (e) | Experimental current waveform of resonant inductor L <sub>r</sub> : [I <sub>Lr</sub> : 3.5A/Div; time:           |

|         | 2.5us/Div]55                                                                                                     |

| 3.7 (a) | Experimental voltage and current waveforms of main switch $S_1$ exhibits soft                                    |

|         | switching conditions [Vs $_1$ : 3.42V/Div; Is $_1$ : 6A/Div; time:0. 1 $\mu$ s/Div]55                            |

| 3.7 (b) | Experimental voltage and current waveforms of synchronous switch S2 exhibits soft                                |

|         | switching conditions [Vs <sub>2</sub> : 3.42V/Div; Is <sub>2</sub> : 10A/Div; time: 0.1µs/Div]56                 |

| 3.8     | Efficiency curve of proposed converter in comparison with traditional buck converter                             |

|         | 57                                                                                                               |

| 3.9     | Circuit diagram of the topology proposed by S Urgun[116]                                                         |

| 3.10    | Circuit diagram of the topology proposed by Hyun Lark Do[189]59                                                  |

| 3.11    | Efficiency curve of proposed converter in contrast with contemporary topologies61                                |

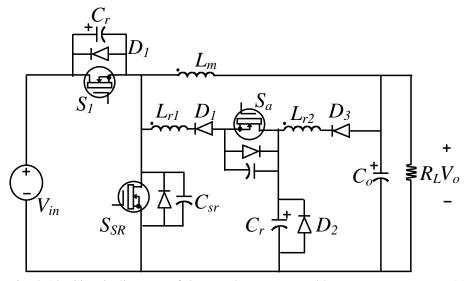

| 4.1     | Proposed multiphase ZVT-ZCT PWM Synchronous buck converter with active auxiliary                                 |

|         | circuit                                                                                                          |

| 4.2     | Essential theoretical waveforms of proposed converter                                                            |

|         | Modes of operation: Mode 1 $(t_0 - t_1)$                                                                         |

|         | Modes of operation: Mode 2 $(t_1 - t_2)$                                                                         |

| 4.3 (c) | Modes of operation: Mode 3 (t <sub>2</sub> — t <sub>3</sub> )67                                                  |

|         | Modes of operation: Mode 4 $(t_3 - t_4)$                                                                         |

| 4.3 (e) | Modes of operation: Mode 5 (t <sub>4</sub> —t <sub>5</sub> )69                                                   |

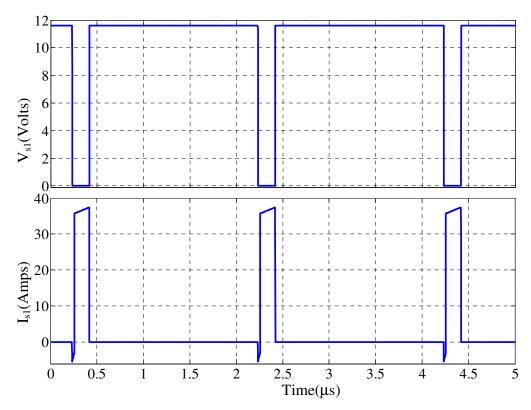

| 4.4 (a) | Simulated voltage and current waveforms of main switch $S_1$ : $V_{s1}$ in Volts and $I_{s1}$ in                 |

|         | Amps                                                                                                             |

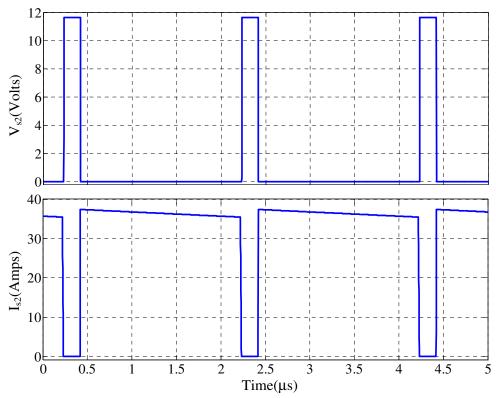

| 4.4 (b) | Simulated voltage and current waveforms of synchronous switch $S_2$ : $V_{s2}$ in Volts and                      |

|         | I <sub>s2</sub> in Amps73                                                                                        |

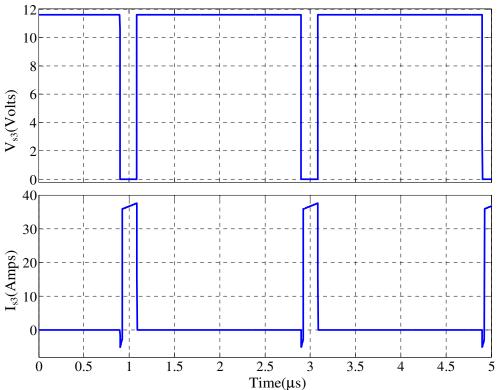

| 4.4 (c) | Simulated voltage and current waveforms of synchronous switch $S_3$ : $V_{s3}$ in Volts and                      |

|         | I <sub>s3</sub> in Amps                                                                                          |

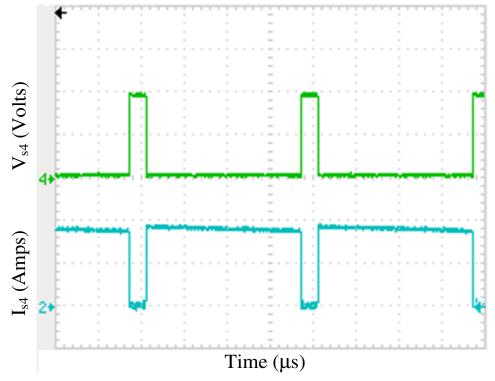

| 4.4 (d) | Simulated voltage and current waveforms of synchronous switch $S_4$ : $V_{s4}$ in Volts and                      |

|         | I <sub>s4</sub> in Amps                                                                                          |

xvii List of figures

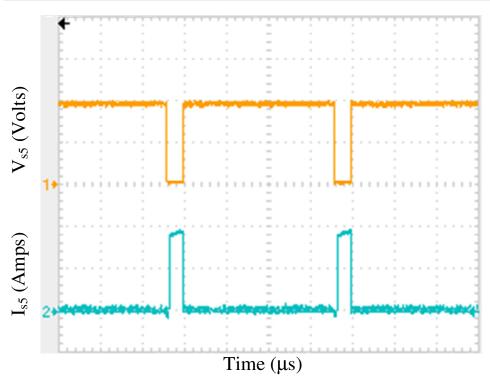

| 4.4 (e) | Simulated voltage and current waveforms of synchronous switch $S_5$ : $V_{s5}$ in Volts and                                                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | I <sub>s5</sub> in Amps74                                                                                                                                           |

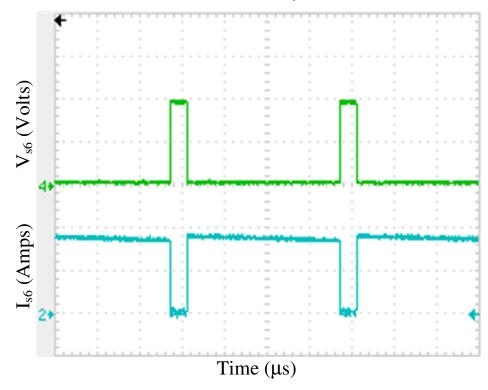

| 4.4 (f) | Simulated voltage and current waveforms of synchronous switch $S_6$ : $V_{s6}$ in Volts and                                                                         |

|         | I <sub>s6</sub> in Amps75                                                                                                                                           |

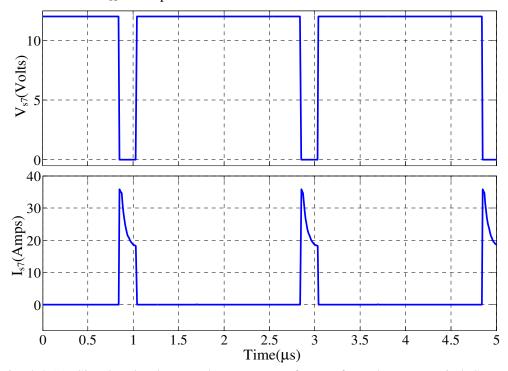

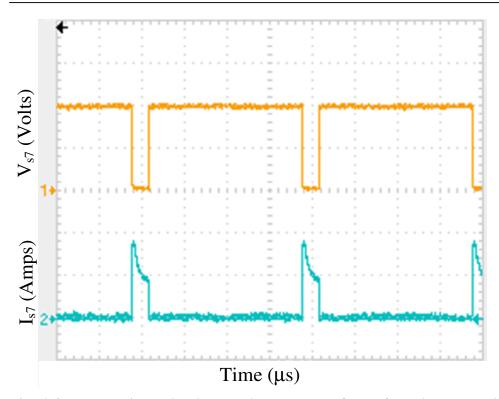

| 4.4 (g) | Simulated voltage and current waveforms of synchronous switch $S_7$ : $V_{s7}$ in Volts and                                                                         |

|         | I <sub>s7</sub> in Amps75                                                                                                                                           |

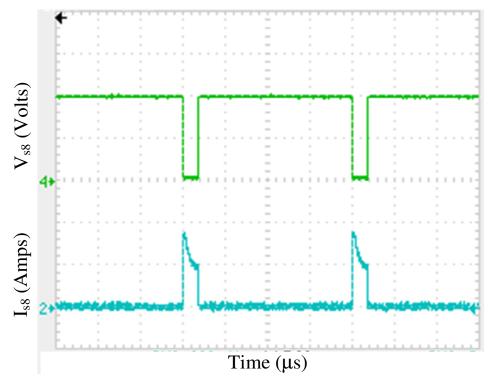

| 4.4 (h) | Simulated voltage and current waveforms of synchronous switch $S_8$ : $V_{s8}$ in Volts and                                                                         |

|         | I <sub>s8</sub> in Amps76                                                                                                                                           |

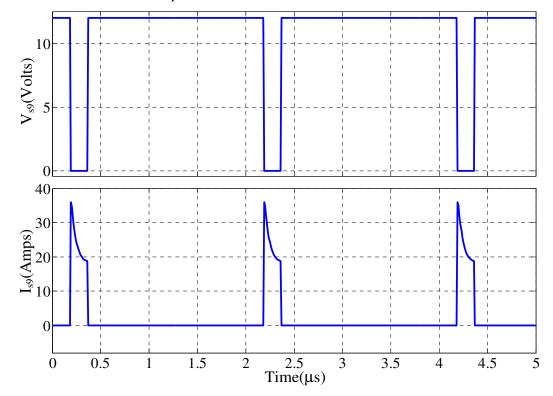

| 4.4 (i) | Simulated voltage and current waveforms of synchronous switch S9: Vs9 in Volts and                                                                                  |

|         | I <sub>s9</sub> in Amps76                                                                                                                                           |

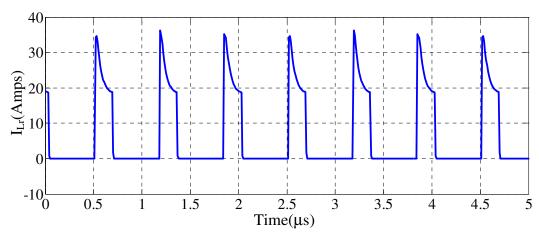

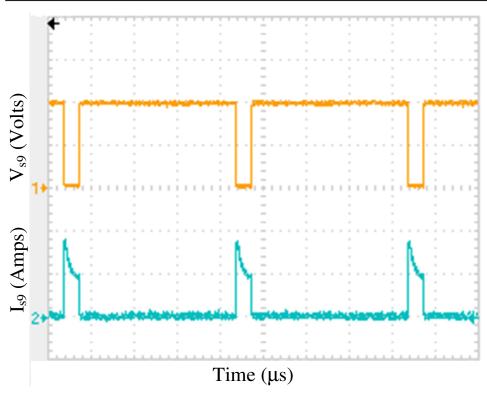

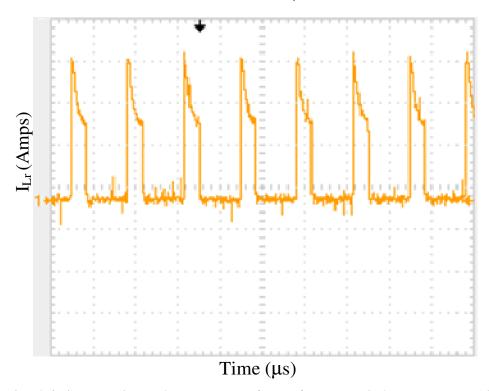

| 4.4 (j) | Simulated current waveform of resonant inductor: $I_{Lr}$ in Amps                                                                                                   |

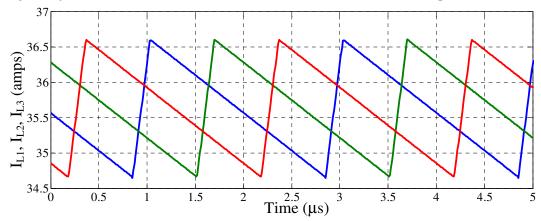

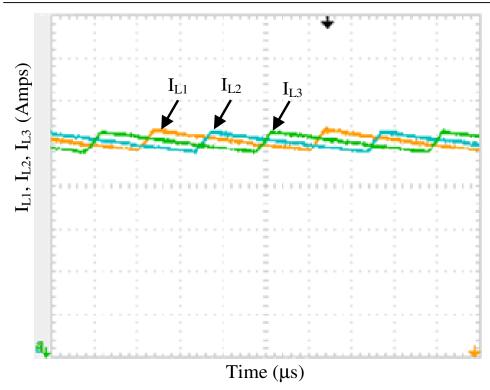

| 4.4 (k) | Simulated current waveforms of filter inductors: $I_{L1}$ , $I_{L2}$ , $I_{L3}$ in Amps77                                                                           |

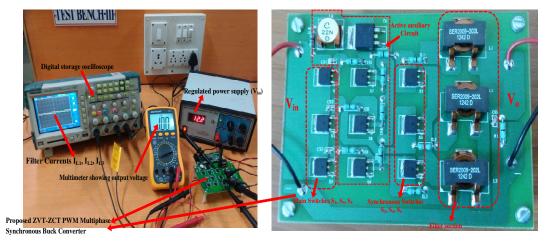

| 4.5     | Experimental setup of proposed multiphase ZVT-ZCT PWM synchronous Buck                                                                                              |

|         | Converter                                                                                                                                                           |

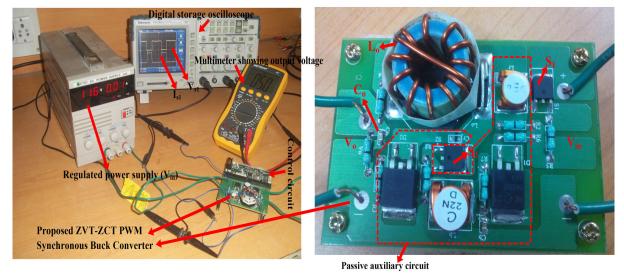

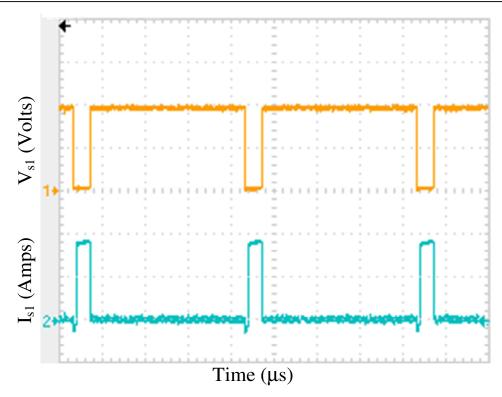

| 4.6 (a) | Experimental voltage and current waveform of Main switch $S_1$ : [Vs <sub>1</sub> : 6V/Div; Is <sub>1</sub> :                                                       |

|         | 17.5A/Div; time: 0.5µs/Div]                                                                                                                                         |

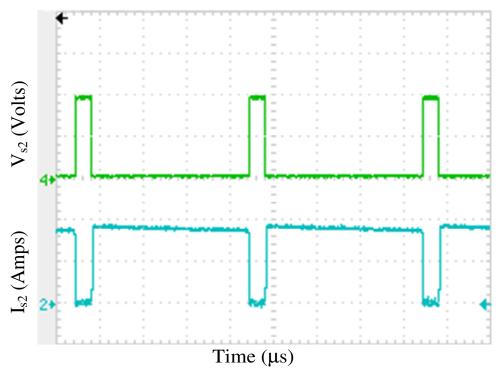

| 4.6 (b) | Experimental voltage and current waveform of synchronous switch S2: [Vs2: 6V/Div;                                                                                   |

|         | Is <sub>2</sub> : 17.5A/Div; time: 0.5μs/Div]78                                                                                                                     |

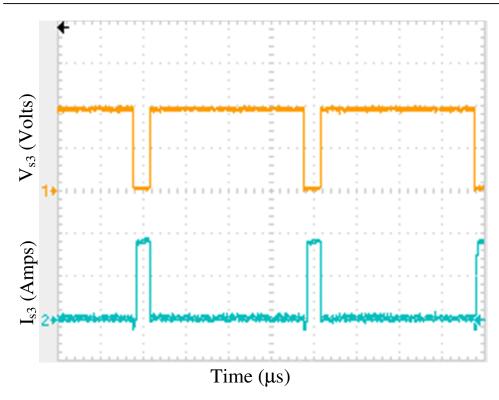

| 4.6 (c) | Experimental voltage and current waveform of synchronous switch S <sub>3</sub> : [Vs <sub>3</sub> : 6V/Div;                                                         |

|         | Is <sub>3</sub> : 17.5A/Div; time: 0.5μs/Div]79                                                                                                                     |

| 4.6 (d) | Experimental voltage and current waveform of synchronous switch S <sub>4</sub> : [Vs <sub>4</sub> : 6V/Div;                                                         |

|         | Is <sub>4</sub> : 17.5A/Div; time: 0.5μs/Div]79                                                                                                                     |

| 4.6 (e) | Experimental voltage and current waveform of synchronous switch S <sub>5</sub> : [Vs <sub>5</sub> : 6V/Div;                                                         |

|         | Is <sub>5</sub> : 17.5A/Div; time: 0.5μs/Div]80                                                                                                                     |

|         | 4.6 (f) Experimental voltage and current waveform of synchronous switch $S_6$ : [Vs <sub>6</sub> : 6V/Div;                                                          |

|         | Is <sub>6</sub> : 17.5A/Div; time: 0.5µs/Div]80                                                                                                                     |

| 4.6 (g) | Experimental voltage and current waveform of synchronous switch S7: [Vs7: 6V/Div;                                                                                   |

|         | Is <sub>7</sub> : 17.5A/Div; time: 0.5μs/Div]81                                                                                                                     |

| 4.6 (h) | Experimental voltage and current waveform of synchronous switch S <sub>8</sub> : [Vs <sub>8</sub> : 6V/Div;                                                         |

|         | Is <sub>8</sub> : 17.5A/Div; time: 0.5μs/Div]81                                                                                                                     |

| 4.6 (i) | Experimental voltage and current waveform of synchronous switch S <sub>9</sub> : [Vs <sub>9</sub> : 6V/Div;                                                         |

|         | Is <sub>9</sub> : 17.5A/Div; time: 0.5μs/Div]82                                                                                                                     |

| 4.6 (j) | Experimental current waveform of resonant inductor L <sub>r</sub> : [I <sub>Lr</sub> : 10A/Div; time:                                                               |

|         | 0.5µs/Div]82                                                                                                                                                        |

| 4.6 (k) | Experimental current waveform of filter inductors L <sub>1</sub> , L <sub>2</sub> , L <sub>3</sub> : [I <sub>L1</sub> , I <sub>L2</sub> , I <sub>L3</sub> : 7A/Div; |

|         | time: 0.5µs/Div]83                                                                                                                                                  |

<u>List of figures</u> xviii

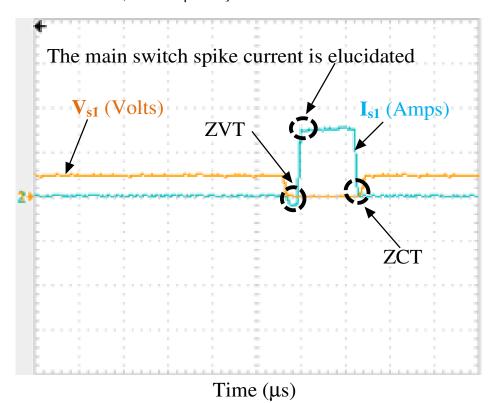

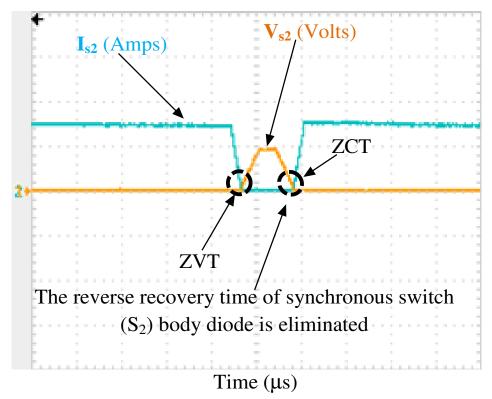

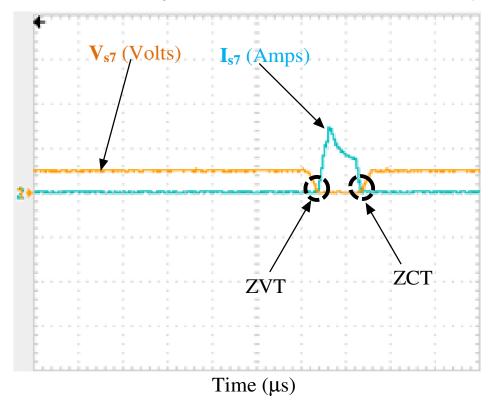

| 4.7 (a) | Experimental voltage and current waveforms of main switch $S_1$ exhibits soft        |

|---------|--------------------------------------------------------------------------------------|

|         | switching conditions [Vs $_1$ :24V/Div; Is $_1$ : 20A/Div; time:0. 2 $\mu$ s/Div]83  |

| 4.7 (b) | Experimental voltage and current waveforms of synchronous switch $S_2$ exhibits soft |

|         | switching conditions [Vs2: 24V/Div; Is2: 20A/Div; time: 0.2 $\mu$ s/Div]84           |

| 4.7 (c) | Experimental voltage and current waveforms of auxiliary switch $S_7$ exhibits soft   |

|         | switching conditions [Vs7: 24V/Div; Is7: 20A/Div; time: $0.2\mu s/Div$ ]84           |

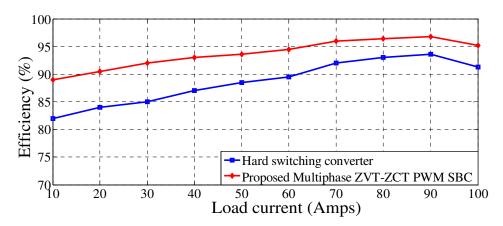

| 4.8     | Efficiency curve of the proposed converter in comparison with traditional buck       |

|         | converter85                                                                          |

# **List of Tables**

| 1.1 | Comparison between the soft switching techniques | 6  |

|-----|--------------------------------------------------|----|

| 2.1 | Components used for proposed converter           | 27 |

| 2.2 | Contrast with contemporary topologies            | 38 |

| 3.1 | Components used for proposed converter           | 50 |

| 3.2 | Contrast with contemporary topologies            | 60 |

| 4.1 | Components used for proposed converter           | 73 |

| 4.2 | Comparison among the proposed converters         | 87 |

# Chapter 1

INTRODUCTION

#### **CHAPTER 1: INTRODUCTION**

#### 1.1 Introduction

Switched mode power supplies (SMPS) have become standard candidate in most of the power processing applications. The design demand is forever moving towards higher power densities. The designer has to find the right tradeoff among efficiency, size, weight, thermal design, EMI issues and cost. Higher power density requires higher switching frequency. Higher switching frequency leads to high switching loss and associated problems. The concept of soft switching addresses these issues. The analysis and design methodologies of hard switched converters matured in 1970's and 1980's [1]. Good analytical circuit models have come into use out of these efforts [2] - [5]. In contrast to hard switching converters, the soft switching converters offer several advantages. Several families of soft switching converters emerged in the past few decades [6] - [44]. Analysis and modelling methods have been proposed in relation with these topologies [45] - [48]. Different degrees of efficiency improvement and increase in switching frequency have been obtained. As a result, there has been a constant increase in the power density of SMPS in the past few decades.

Resonant switching techniques reduce the switching losses to practically zero; the switching frequency then may be increased to hundreds of kHz to achieve higher power densities. Such converters in general are classified as `Soft switching converters' [6]. In these converters, the switching transitions occur with zero loss. Exploitation of resonant transitions in power conversion is not new. Resonant circuits were used to provide forced commutation in the thyristor era. The use of such techniques diminished with the introduction of fully controlled switches such as BJTs, MOSFETS and IGBTs. With the demand for higher power density and lower switching loss, there is a renewed interest in the resonant switching techniques. The switching techniques in the resonant converter employ zero voltage switching and/or zero current switching. Soft switching is also referred to as Zero current switching (ZCS) or Zero voltage switching (ZVS) in the literature [6]. In zero current switching, the device turns-on with zero current and turns-off after the current drops to zero. In zero voltage switching, the switch turns-off at zero voltage and turns-on after the device voltage drops to zero.

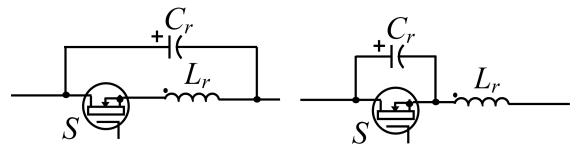

The concept of resonant switch was first proposed in [12]. The basic resonant switches are `Zero current switch' and `Zero voltage switch', shown in fig. 1.1. The `Resonant switch converters' are obtained by replacing the controllable switches in PWM converters with the 'Resonant Switch'. The resonant switch is the combination of a switch and reactance's. The switch has a series inductance to achieve ZCS or a shunt capacitance to achieve ZVS. The

family of DC-DC converters with resonant switches are known as `Quasi-resonant converters' (QRC's) [12] - [14].

Fig. 1.1: Basic resonant switches (a) Zero current resonant switch (b) Zero voltage resonant switch Resonant switch converters, employing fig. 1.1 (a) are ZCS QRC's - The current in the switch starts from zero at turn-on. The turn-off of the device is when the current through the device has come down to zero. The devices are designed for high peak current. Conduction loss is high and practically independent of the load current. The loss due to the discharge of the parasitic junction capacitance of the device during turn-on is significant at switching frequencies above 1MHz. Hence, at higher switching frequencies, resonant switch converters employing fig. 1.1 (a) is preferred to ZCS QRC's. Resonant switch converters, employing fig. 1.1 (b) are ZVS QRC's - The turn-on of the device is while the body diode is conducting. During turn-off, the shunt capacitor constraints the device voltage to increase slowly. The active switch in ZVS QRC's is subjected to relatively low current stress. However, the active switch suffers from excessive voltage stress. Quasi-resonant converters are available in a wide variety of topologies [15].

New families of converters called multi-resonant converters (MRC's) were reported in [16]-[17]. The ZVS multi-resonant converter technique uses all parasitics of the power stage. All devices operate with ZVS. This substantially reduces the switching losses. Both active and passive switches suffer from voltage and current stress, higher than in PWM counterparts. This leads to a substantial increase in the conduction loss. A new family of converters called 'Quasi-Square-wave Converters' (QSC) were reported in [18]. QSC's had reduced voltage stresses and operated with improved efficiency. However, the switches suffered from higher current stress, twice that in the PWM counterpart. In resonant load and resonant switch converters, switching losses are reduced at the cost of conduction losses of the main switch. The output voltage is controlled by varying the switching frequency. When the switching frequency varies, the EMI filters become heavier; this puts additional size penalty on the converter.

In the above converters, the resonant elements handle many times the load current and the circuit voltage. This may be overcome if the resonant elements are not in the direct path of the power flow. Later developments in ZVS/ZCS converters adopted a different strategy- the

resonant elements were away from the main path of the power flow. The resonant elements shaped the switch voltage/current only during the switch transitions. When the switching transitions are over, the circuit reverts back to the PWM mode. The converter achieves soft switching while preserving the characteristics of the PWM converter. In recent years, various soft transition techniques have been proposed to reduce the switching losses. The converters employing soft transition techniques (Zero voltage transition (ZVT) or Zero current transition (ZCT)) are called `Soft transition converters [19]. These converters achieve soft switching (ZVS or ZCS) through an active auxiliary circuit. This auxiliary circuit becomes active only during the switching transitions. The ZVT technique forces the switch voltage to zero, before the switch is driven on. The ZCT forces the current through the switch to zero, before the switch is driven off.

The main power is not processed in the auxiliary circuit. A good soft transition scheme will have the following features:

- ➤ Lower switching losses

- ➤ Reduction of switch Current/Voltage

- > Soft recovery for the freewheeling diode

These features contribute to higher power density and improvement in the efficiency.

A number of soft transition converters employing ZVT/ZCT have been reported [20] - [34]. All these converters employ an auxiliary network to obtain soft switching for the main switch. These converters achieve ZVS for both the active and the passive switches. The VA ratings of the main switch are same as that of the source voltage and load current. In these converters, the main switch transitions are lossless; auxiliary switch turn-off transition is lossy.

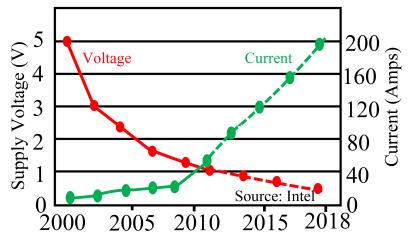

The demands for processing power have been observed in the companies such as Intel and AMD repeatedly self—obsolete themselves with powerful and faster processor chips. These advancements have been made by the increase in the transistor density, which can be fabricated in a particular area of silicon. The processor current requirement increases exponentially over a few decades and in future it may exceed 100A in the different processor applications. The Moore's law which state, "transistor density doubles every twelve months" is successful in the prediction of evolution of microprocessors. Currently, there are millions of transistors and by 2018 there will be billions of transistors on a particular chip. A converter that supplies 120A/0.8V is in need by the year 2018 [185-186].

The power management techniques are introduced in a microprocessor, for modules of transistors in the recent years. The decline of microprocessor supply voltage is one of the solutions. Many company's microprocessors including Intel uses a non-standard power

supply of less than 5V and these voltages is continuously getting decreased. Furthermore, the transistors number increases in the microprocessor that leads to increase in the microprocessor current demand. The low voltage, high current and tight voltage regulation inflict challenges for power supply design of microprocessors. Fig. 1.2 shows the voltage and current variation as per the current demands of the Intel's processors.

Fig. 1.2: Intel's road map for the processors required current and voltage

#### 1.2 Losses in converters

In general losses are bound to be present in the elements of the converter. The loss of each element depends on its operational characteristics. The loss distribution varies widely, but the switching elements play a significant role. The other component losses also cannot be neglected. MOSFET's are well- known switching elements which are the cause for switching and conduction loss. The power loss of the MOSFET is categorized as conduction and switching losses. The calculations applied are approximate, as the losses are neglected during the operation. Conduction loss is the product of current square times the resistance in the switch during conduction, whereas the switching loss is considered to be the overlap of the current and voltage of the switching element. Switching loss is obtained as the product of half the drain voltage and the inductor current during the switching transition time (fall and rise times) [81-83]. Output capacitance C<sub>oss</sub>, body diode conduction loss is also other elements which cause the losses in the converter. Output capacitance Coss loss is calculated as the product of half the Coss times the square of the input voltage and multiplied by the switching frequency [84-88]. Calculation of output capacitor Coss loss has been introduced on the basis of a basic energy concept in [87-89]. The output capacitor Coss is located in between the drain-source and drain- gate, its value is obtained from the datasheet of the MOSFET. Calculation of each element loss is required in order to minimize the respective losses to enhance the overall efficiency. The usage of synchronous rectifier results in the reduction of

the conduction loss, but develops supplemental switching losses. This effect is reduced by the addition of the resonant tank in the converter.

The two basic terms, overlap VI loss and  $C_{oss}$  loss have a relation between  $C_{oss}$  and switching loss obtained as a ratio that can't be segregated. Switching loss is the combination of total switching and  $C_{oss}$  losses i.e.,  $0.5I_L.V_D.$  ( $T_{fall} + T_{rise}$ ) [45].  $C_{oss}$  loss has an indirect effect as it affects the rise and fall time period, which inturn affects the switching loss.

The power loss of the MOSFET is given by:

$$P_{MOSFET} = P_{Switching} + P_{Conduction}$$

Conduction losses are calculated as

$$P_{Conduction} = I_{rms}^2 . R_{dsON}$$

Where  $I_{rms}$  is the current through the MOSFET,

$R_{dsON}$  is ON state resistance,

A specific dead time is allowed between two synchronous MOSFET's to avoid current shoot through. This results in the current commutation from MOSFET channel to its body diode, where a negative voltage drop develops between drain-source channels. This time is considered as body diode ON time  $t_D$ . The calculation of body diode loss is obtained by the parameters as follows; the forward voltage drop of body diode  $V_D$ , source to drain body diode current  $I_{SD}$ , the body diode ON time  $t_D$  and the switching frequency  $f_{SW}$ .

$$P_{BD} = V_D I_{sD} t_D f_{sw}$$

The switching loss at the instant of OFF time is calculated by the output charge  $Q_{oss}$  and the reverse recovery charge  $Q_{rr}$  that build the losses during the transition of turning OFF the synchronous rectifier MOSFET. It is given by

$$P_s = V_T \left( \frac{1}{2} Q_{oss} + Q_{rr} \right) f_{sw}$$

$V_T$  is the instantaneous voltage of MOSFET.

Therefore, the losses of the synchronous rectifier are expressed as:

$$P_{SR} = P_C + P_S + P_{BD}$$

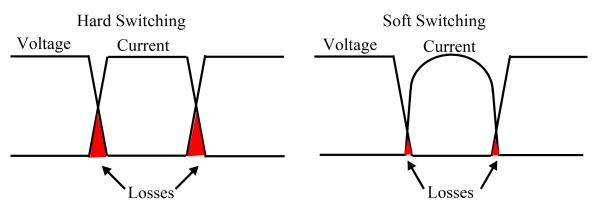

Application of soft switching enhances the overall efficiency by the reduction of inevitable losses as shown in fig. 1.3. Many converter topologies are proposed for enhancing the efficiency [91-95].

Fig. 1.3: Switching losses in the conventional and resonant converter

#### 1.3 Contrast between different resonant converters

Table 1.1 Comparison between the soft switching techniques

| Switching technique | Advantage         | Drawback                     | Operating condition         |

|---------------------|-------------------|------------------------------|-----------------------------|

| Quasi resonant      | decrease the      | Current is                   | Works with variable         |

|                     | switching stress  | discontinuous                | frequency                   |

| Resonant            | Operates at zero  | High voltage and             | Applicable for converters   |

|                     | voltage and zero  | current peaks with           | operating under 100 kHz     |

|                     | current to        | greater complexity           | frequency.                  |

|                     | minimize the      |                              |                             |

|                     | losses            |                              |                             |

| Zero voltage        | Operates at high  | Losses occur due to          | During the transition times |

| Transition (ZVT)    | frequency and     | $C \frac{dv}{dt}$ across the | it works as a resonant      |

|                     | minimizes the     | gate are not minimized       | converter and rest it       |

|                     | parasitic effects |                              | operates as a conventional  |

|                     |                   | mmmized                      | PWM converter.              |

|                     |                   |                              |                             |

| Zero Current        | Minimizes the     | Losses in the                | Operates at the instant of  |

| Transition (ZCT)    | turn-OFF loss     | junction capacitance         | switch, turn-OFF time.      |

|                     |                   |                              |                             |

| Zero voltage        | Eliminates both   |                              | Operates on both the        |

| Transition (ZVT) -  | turn-ON and turn- |                              | instances of turn-ON and    |

| Zero Current        | OFF losses        |                              | turn-OFF; acts as a         |

| Transition (ZVT)    |                   |                              | traditional PWM converter   |

|                     |                   |                              | for the remaining period.   |

Research is still in demand to introduce novel topologies, in the recent years the converters embedded with quasi-resonant, resonant and ZVT-ZCT technique is in use [96].

Each soft switching technique has its own significance as per the application. In a resonant converter, a regular PWM converter is added by a resonant element switch network. The converter which emerges has both the properties of the resonant switch network and PWM converter.

#### 1.4 Motivation

The huge demand of power converters for portable electronic circuitry under various power ratings constitutes solid tests for power supply designers. Increased current demand, low operating voltages and the state of the microprocessor based or microcontroller based systems develops new opportunities for power distribution and management. High power density, high efficiency and proper voltage regulation are the issues which become critical if conventional converters are used for low operating voltage. Due to advances in power electronics converter design and control methods, the electrical energy conversion from one form to another with enhancing efficiency and low cost is being made possible. But a tradeoff is considered for some issues such as size, cost, weight and power density, etc., in modern day power electronic circuitry. The advantages in cost, size and performance endorses the power electronic applications broadly in many fields like industrial, residential, aerospace and military in the recent years. According to Moore's law, the number of transistors on an IC has doubled every year. To attain high power density with a large rate of increase in the number of transistors appeals rise in the switching frequency that induces the switching losses.

The increase in the acclaim of low power portable equipment asserts for efficient and high power density converter. The power density of a converter is enhanced by reducing the losses of size of components. The switching frequency is a prime factor for the reduction of the size of the components. The switching frequency is a prime factor for the reduction of the size of the components to a certain extend. Quasi-resonant, resonant, ZVT-PWM, ZCT-PWM, ZVT-ZCT-PWM converter topologies have been proposed in the recent years, in order to reduce the losses. The resonant converter experiences the high current peaks and high voltage across the switching devices. ZVT-ZCT PWM converters are in huge demand since they provide lower voltage and current stresses. This inturn affects the ratings of the device to be higher than the conventional converters. The enhanced efficiency can be accomplished by using the proper topology that alleviates the conduction and switching loss. The modern power electronic converter topologies insist on high efficiency, low cost power supply, high power density for portable applications motivate to design and develop ZVT-ZCT PWM

synchronous buck converters with the addition of active and passive auxiliary circuits at different operating conditions. ZVT-ZCT PWM synchronous buck converters attains high efficiency by the reduction of losses. They also attain low cost and low power rating elements in the converter by reducing voltage and current stresses.

Programmable devices such as microprocessors and DSP's are extensively used in many commercial and industrial applications. In order to meet the demands of these programmable devices, there should be declined in the operating voltage without changing the power consumption, while sustaining the higher operating switching frequency. These demands can be achieved by the use of multiphase synchronous buck converter. Increase in the number of components and switches results in the lower efficiency. Reduction of losses in the multiphase buck converter to accomplish the demand of high efficiency is now a challenging task. These demands motivate to employ the soft switching techniques into the synchronous buck converter to attain high power density with an enhanced efficiency.

#### 1.5 Objectives

From the above discussions the thesis objectives are as follows:

- ➤ To employ the soft switching techniques in the synchronous buck converter topology using an active auxiliary circuit. The proposed topology should enhance the efficiency for high power density applications. The main aim is to reduce the voltage and current stresses using the auxiliary circuit.

- ➤ To implement the soft switching into the synchronous buck converter embedding the passive snubber circuit. A passive auxiliary circuit in the synchronous buck converter should fulfill the demands of high efficiency, high power density maintaining high operating switching frequency. It will also accomplish the objective of reducing high voltage and current stresses.

- ➤ To design and develop multiphase synchronous buck converter for modern generation microprocessor power supply unit for point of load (POL) applications at low operating output voltage and high load current by reducing switching losses, voltage and current stresses.

#### 1.6 Organisation of the thesis

**Chapter I** presents the background of the work. The significance of loss analysis to measure the degree of performance of a topology is discussed. Comparisons between different soft switching techniques are included. Finally, factors for motivation and objectives have been discussed.

Chapter II includes the design and implementation of ZVT-ZCT soft switching technique in the synchronous buck converter to accomplish high efficiency for higher power density applications. An active auxiliary circuit is incorporated in the conventional PWM synchronous buck converter which makes the main switch to operate with ZVS at turn-ON and ZCS at turn OFF. The principle of operation and steady state analysis of the proposed converter has been discussed. The simulation and experimental results that validate the performance of the proposed converter have been presented. To mitigate the disadvantages of active auxiliary circuit such as surplus switching loss and its complex circuitry the active auxiliary circuit is substituted with a simple passive auxiliary circuit.

In **chapter III**, a passive auxiliary circuit introduced into the conventional synchronous buck converter is discussed. The detailed steady state analysis and operating principle are presented. The design details of the auxiliary circuit components are included and a prototype has been built in the laboratory. The performance of the proposed converter is verified by the simulation and experimental results.

**Chapter IV** introduces the implementation of the soft switching technique into the multiphase synchronous buck converter incorporated with an auxiliary circuit for reduction of switching losses. The steady state analysis of the proposed converter has been explained comprehensively. The design and fabrication of the proposed converter have been executed in the simulation and experimental results.

**Chapter V** deals with summary and future work of the buck converters.

# **Chapter 2**

PERFORMANCE ENHANCEMENT OF SYNCHRONOUS BUCK CONVERTER WITH INTEGRATION OF ACTIVE AUXILIARY CIRCUIT

# CHAPTER 2: PERFORMANCE ENHANCEMENT OF SYNCHRONOUS BUCK CONVERTER WITH INTEGRATION OF ACTIVE AUXILIARY CIRCUIT

#### 2.1 Introduction

In the recent times, the Zero Voltage Transition-Zero Current Transition (ZVT-ZCT) technique applied to the synchronous buck converter emanates as a prior converter that maintains voltage and current stresses within tolerable limits. These modules are found immensely in the high- power applications. In addition to that, the solar and spacecraft applications demanding efficient DC-DC modules for improving the storage capacity which is to be used in intermittent times.

The Zero Voltage Transition (ZVT) – Zero Current Transition (ZCT) technique applied to synchronous buck converter (SBC) reduces the conduction and switching losses which inturn enhances the efficiency. The voltage and current mode soft switching method that has drawn attention in the recent times is Zero Voltage Transition (ZVT) – Zero Current Transition (ZCT) [67, 100-108]. The demand boosts as its operation is close to the PWM converters and in addition to that, provides low conduction and switching losses. The auxiliary circuit of the Zero Voltage Transition (ZVT) – Zero Current Transition (ZCT) converters is activated just before the main switch is made active and culminates after it is accomplished. The ratings of auxiliary circuit components are lower than those in main power circuit as the auxiliary circuit is activated for a small fraction of the switching cycle; this makes a provision for the converter's to shrink its size and cost.

The converters proposed in [102, 105, 109-110]; suffer from hard switching turn OFF that leads to increase in switching losses. The auxiliary switch is turned-off while it is conducting that causes switching losses and electromagnetic inference (EMI) to appear that offsets the advantage of using the auxiliary circuit. The converters proposed in [108-111, 105] have very high current stresses on the main switch. The main converter switch operates with a higher peak current stress and with the more circulating current which results in the need for a higher current rated switch that increases conduction losses. Reduction of switching losses for low power circuits such as synchronous buck is not presented in the [112-127].

Switching losses are reduced by inculcating soft switching function into the standard PWM-converters utilizing the Zero Voltage Transition (ZVT) – Zero Current Transition (ZCT) technique. The auxiliary circuit proposed transfers energy from input voltage source to

output, suitable for high power applications. It also shares the output current stress between the main switch and auxiliary switch. There is no additional voltage and current stress on the main switch and the semiconductor devices used are soft switched.

The various other proposed ZVT-ZCT PWM converters have one of the following flaws:

- 1. During current conduction through the auxiliary switch, it is turned OFF. This leads to switching losses and EMI to occur that cancel out the advantages using the auxiliary switch. The converters proposed in [102, 110, 187, 188] experience hardswitching turn OFF.

- 2. The auxiliary circuit affects the main switch of the converter to operate at high peak current stress and more circulating current. This causes to use higher current rating switching device for the main switch that also increases the conduction losses. The converters that are proposed in [25, 32, 44, 49, 98, and 105] suffer with high current stress on the main switch.

- 3. The components used for auxiliary circuit in the proposed converters [102, 26, 29, 32] contain high voltage and current stresses. The converters proposed in [108, 111] have low current stress on the main switch, but the circuit is complex.

This chapter is organised as follows: section 2.2 describes about the proposed topology. Section 2.3 explains the principle of operation and its operating modes. Section 2.4 provides the design procedure of magnetic elements used. Section 2.5 includes the simulation and experimental results that exposes the features of the proposed converter. In section 2.6, efficiency curve is shown that explains the operation of the converter over wide range of load, also the efficiency curve is compared with conventional and contemporary topologies. Section 2.7 summarises the important features.

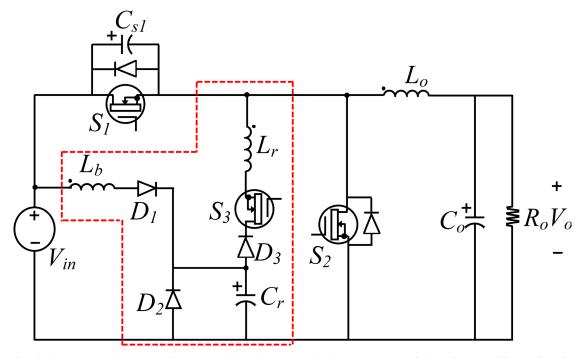

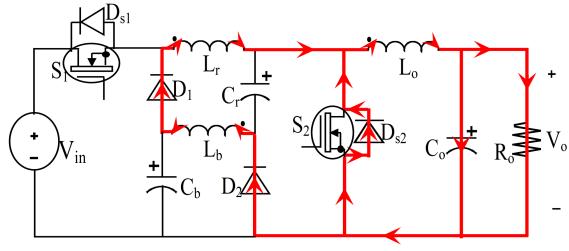

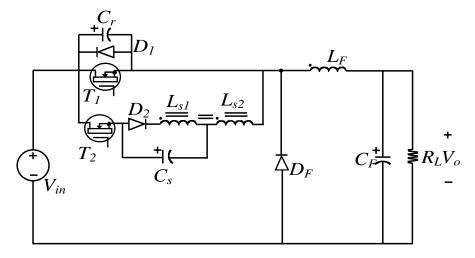

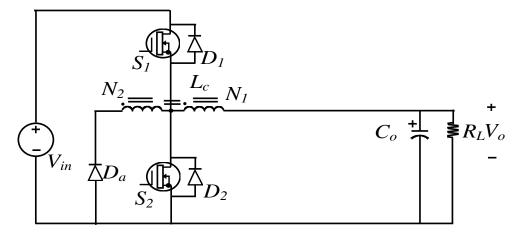

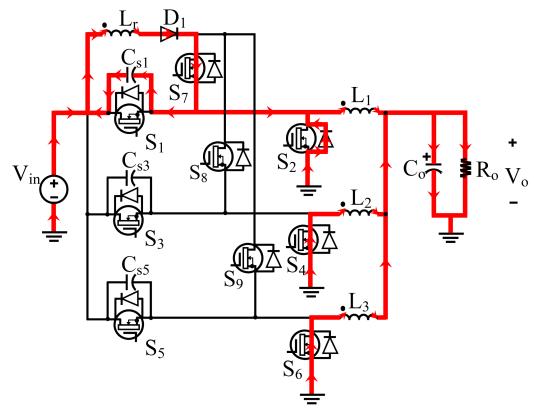

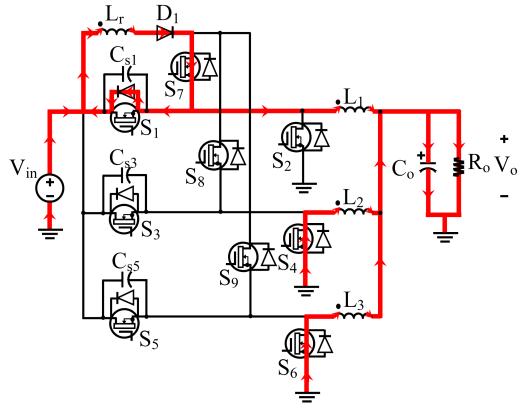

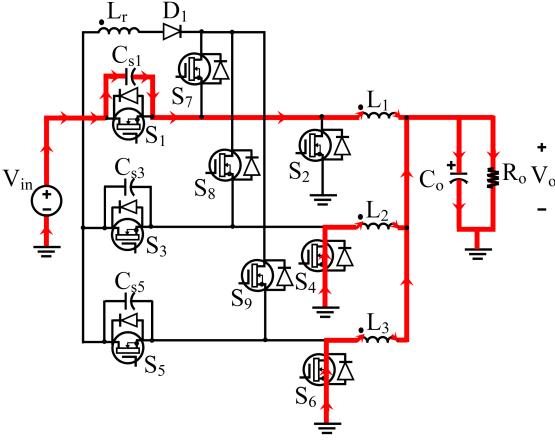

#### 2.2 Topology description

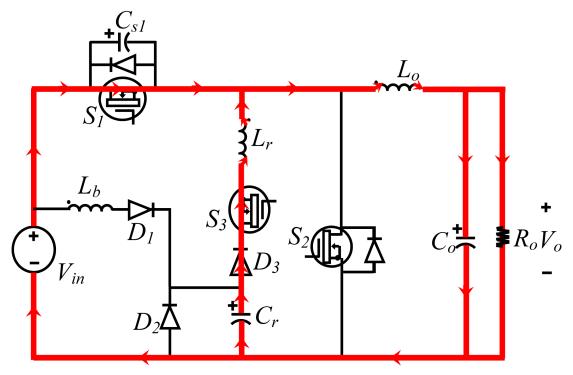

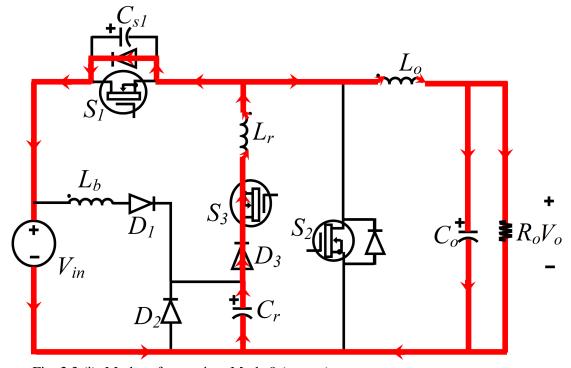

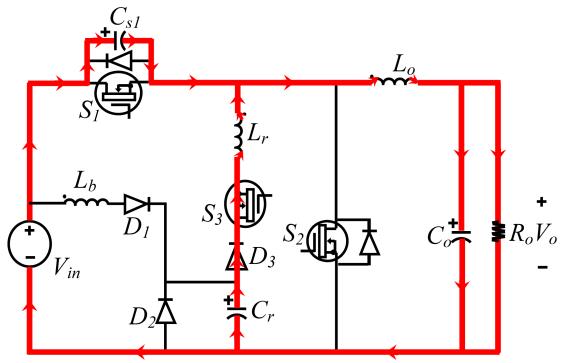

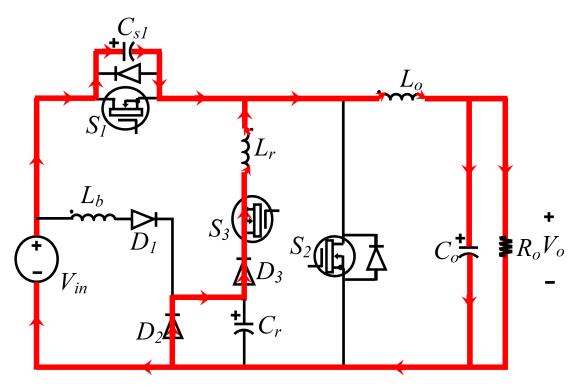

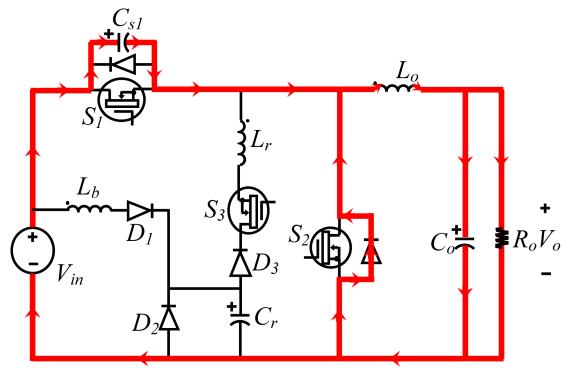

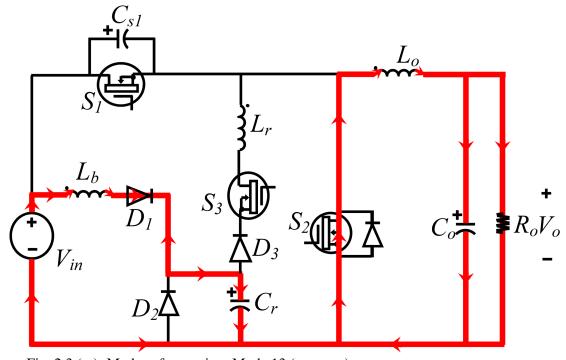

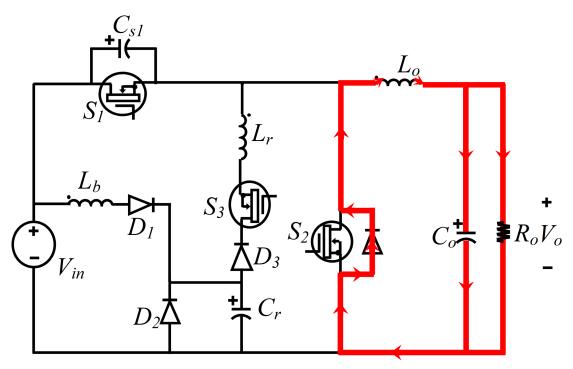

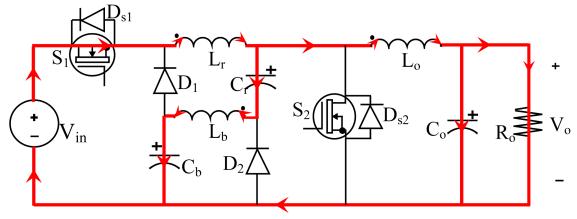

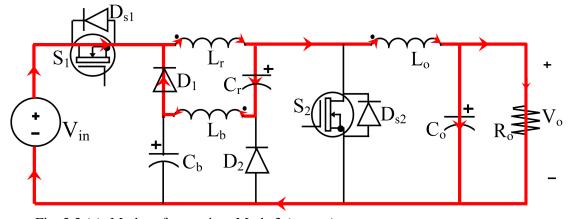

The circuit scheme of the proposed ZVT-ZCT synchronous buck converter with active auxiliary circuit is shown in Fig. 1. The converter comprises of main switch  $S_1$ , synchronous switch  $S_2$ , filter capacitor  $C_o$ , and filter inductor  $L_o$ . The proposed auxiliary circuit includes an auxiliary switch  $S_3$ , auxiliary inductors  $L_b$  and  $L_r$ , diodes  $D_1$ ,  $D_2$ ,  $D_3$  and a capacitor  $C_r$ .

To simplify the analysis the following conditions are assumed in a switching cycle.

- 1. The auxiliary capacitor is charged to  $2V_{in}$  and the synchronous switch is conducting before mode 1.

- 2. Inductor current I<sub>L0</sub> is constant and equal to I<sub>o</sub>

- 3.  $L_b$  is much larger than  $L_r$ .

#### 4. All circuit elements are ideal.

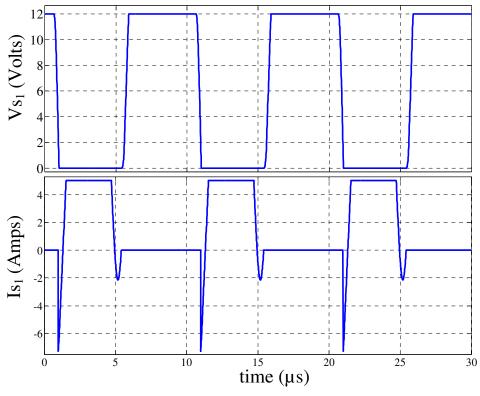

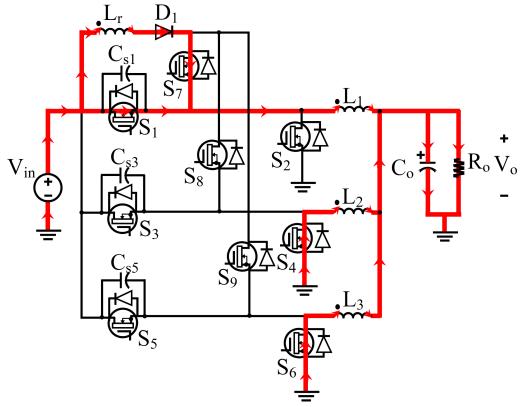

Fig. 2.1: Proposed ZVT-ZCT PWM Synchronous buck converter with active auxiliary circuit

#### 2.3 Operational modes

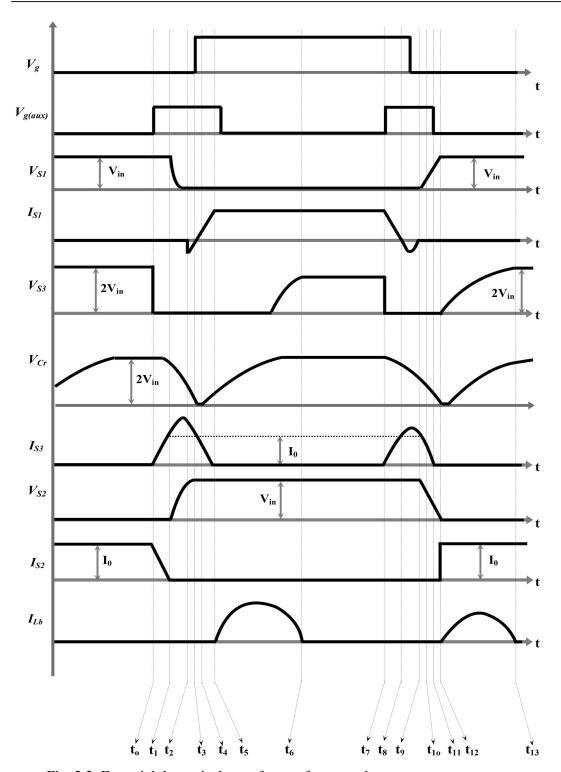

In this section, the operating modes of the proposed converter are comprised of 14 states, considering the different current paths of the elements and switch voltages. The waveforms are presented in fig. 2.2, and the operating mode analysis is explained by the current paths shown in fig. 2.3.

*Mode 1* ( $t_0 - t_1$ ): In mode 1 auxiliary switch is turned ON, that causes resonance between the auxiliary capacitor  $C_r$  and the auxiliary inductor  $L_r$ . The current of  $L_r$  increases during the resonant period. When  $L_r$  current becomes equal to the output current, the synchronous switch body diode turns OFF under ZCZV condition. Snubber capacitor voltage is constant that is charged to  $V_{in}$ , which causes ZV condition. The  $L_r$  current and  $C_r$  voltage expressions for this mode are:

$$I_{Lr} = \frac{2V_{in}}{z_1} \sin(\omega_1(t - t_0))$$

(2.1)

$$V_{Cr} = 2V_{in}\cos(\omega_1(t - t_0)) \tag{2.2}$$

Where

$$\omega_{l} = \frac{1}{\sqrt{L_{r}C_{r}}} \tag{2.3}$$

$$Z_1 = \sqrt{\frac{L_r}{C_r}} \tag{2.4}$$

This mode ends when  $L_r$  is equal to the output current. The duration of this mode and capacitor voltage  $C_r$  are given by

$$t_{1} - t_{0} = \frac{\sin^{-1}\left(\frac{I_{o}Z_{1}}{2V_{in}}\right)}{\omega_{1}} = \Delta t_{1}$$

(2.5)

$$V_{Cr} = 2V_{in}\cos(\omega_1 \Delta t_1) \tag{2.6}$$

*Mode* 2 ( $t_1 - t_2$ ): In this mode, resonance occurs between  $L_r$ ,  $C_r$  and  $C_{s1}$ . The snubber capacitor discharges during the resonance. In this mode, some part of the energy is transferred to the output. At the end of the mode voltage across Cr becomes equal to zero.

$$I_{L_{r}} = \left(I_{0} - \frac{I_{0}}{I_{L_{0}}C_{s1}\omega_{2}^{2}}\right)cos\left(\omega_{2}\left(t - t_{1}\right)\right) + \frac{V_{Cr}}{L_{r}\omega_{2}}sin\left(\omega_{2}\left(t - t_{1}\right)\right) + \frac{I_{0}}{I_{L_{0}}C_{s1}\omega_{2}^{2}}$$

(2.7)

$$V_{C_{S1}} = V_{in} - \frac{1}{C_{S1}} \int_{L_{r}}^{t_{2}} (I_{Lr} - I_{0}) dt$$

(2.8)

$$V_{Cr} = V_{Cr} - \frac{1}{C_{s1}} \int_{t_1}^{t_2} (I_{Lr}) dt$$

(2.9)

$$\omega_2 = \frac{1}{\sqrt{\frac{L_r C_{s1} C_r}{C_r + C_{s1}}}}$$

(2.10)

Calculation the time interval of this mode is complex from (7) and (8). In order to simplify the analysis, the auxiliary capacitor  $C_r$  and snubber capacitor  $C_{s1}$  are assumed to be equal. Therefore

$$C_r = C_{s1} = C (2.11)$$

$$\omega = \frac{1}{\sqrt{L_r C_r}} = \omega_1 = \frac{\omega_2}{\sqrt{2}} \tag{2.12}$$

$$Z = \sqrt{\frac{L_r}{C}} = Z_1 \tag{2.13}$$

$$L_r C \omega_2^2 = 2 \tag{2.14}$$

Fig. 2.2: Essential theoretical waveforms of proposed converter

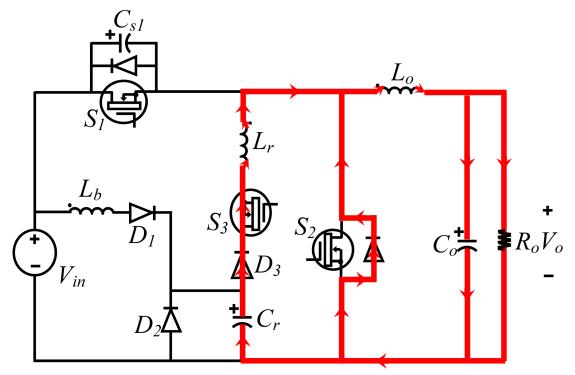

Fig. 2.3 (a): Modes of operation: Mode 1 ( $t_0$ — $t_1$ )

Fig. 2.3 (b): Modes of operation: Mode 2  $(t_1 - t_2)$

$$\frac{Z}{L_r \omega_2} = \frac{1}{\sqrt{2}} \tag{2.15}$$

$$\frac{I_0}{C\omega} = I_0 Z = \frac{V_{in}}{1.2} \tag{2.16}$$

The equations (6) and (7) are simplified as follows:

$$V_{Cr} = 1.82V_{in} (2.17)$$

$$I_{L_{r}} = \left(I_{0} - \frac{I_{0}}{2}\right) cos\left(\omega_{2}\left(t - t_{1}\right)\right) + \frac{1.82 * 1.2Z_{1}I_{0}}{L_{r}w_{2}} sin\left(\omega_{2}\left(t - t_{1}\right)\right) + \frac{I_{0}}{2}$$

(2.18)

$$= \left[\frac{1}{2}\cos\left(\omega_{2}\left(t-t_{1}\right)\right) + \frac{1.82*1.2}{\sqrt{2}}\sin\left(\omega_{2}\left(t-t_{1}\right)\right) + \frac{1}{2}\right]\left(I_{0}\right)$$

The duration of this interval is obtained as  $0.55\pi/\omega_2$  and also from (8) and (18), the inductor current  $L_r$  and the snubber capacitor  $C_r$  voltage  $1.96I_o$  and  $0.18V_{in}$  respectively. Another resonance between  $L_b$  and  $C_r$  occurs when the voltage of capacitor  $C_r$  falls below  $V_{in}$ .  $L_b$  is assumed to be larger than  $L_r$ ,  $L_b$  and  $C_r$  are under resonance which is very slow and hence its effect can be negligible until the sixth mode.

*Mode 3* ( $t_2 - t_3$ ): In this mode,  $D_1$  gets forward bias and the resonance between  $C_r$  and  $L_r$  will continue. This mode ends when  $C_r$  is discharged and due to this the main switch body diode conducts. The inductor  $L_r$  current and capacitor  $C_r$  voltage is given by:

$$I_{L_r} = (1.96 - 1)\cos(\omega_2(t - t_2)) + (0.18 - 1)\sin(\omega_2(t - t_2) + 1).I_0$$

(2.19)

$$V_{Cs1} = 0.18V_{in} - \frac{1}{C_{s1}} \int_{t2}^{t3} (I_{Lr} - I_0) dt$$

(2.20)

The resonant inductor  $L_r$  current at the end of this mode is  $1.65I_0$  and duration of this mode is given by  $0.99\pi/\omega$ .

*Mode 4* ( $t_3 - t_4$ ): When the snubber capacitor is discharged, the body diode of the main switch starts conducting and  $L_r$  current decreases linearly. The main switch turns ON at the ZCZV condition before the inductor  $L_r$  current becomes lesser than the output current. The duration of the mode is given by:

$$t_4 - t_3 = \frac{0.65L_r I_0}{V_{in}} = \Delta t_4 \tag{2.21}$$

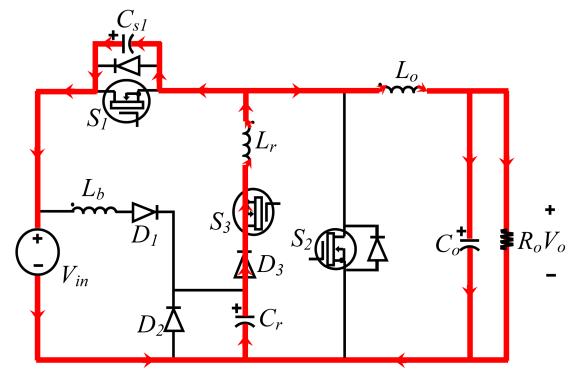

Fig. 2.3 (c): Modes of operation: Mode 3  $(t_2 - t_3)$

Fig. 2.3 (d): Modes of operation: Mode 4  $(t_3 - t_4)$

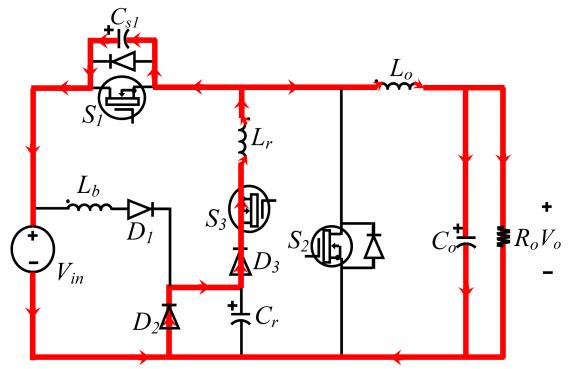

**Mode 5** ( $t_4 - t_5$ ): In this mode main switch is turned ON and the voltage across  $L_r$  is  $V_{in}$  and its current decreases linearly to zero. The main switch current increase linearly from

zero to output current  $I_0$ . At the end of this mode due to ZC condition the auxiliary switch is turned OFF as its current is reduces to zero. The duration of this mode is given by: