# The As-grown-Generation (AG) model: A reliable model for reliability prediction under real use conditions

J. F. Zhang\*, Z. Ji and W. Zhang Department of Electronics and Electrical Engineering, Liverpool John Moores University, Byrom Street, Liverpool L3 3AF, UK. \*Phone: +44-151-2312363 Email: j.f.zhang@ljmu.ac.uk

Abstract- Modeling the negative bias temperature instability (NBTI) can optimize circuit design. Several models have been proposed and all of them can fit test data well. These models are extracted typically by fitting short accelerated stress data. Their capability to predict NBTI aging outside the test range has not been fully demonstrated. This predictive capability for long term aging under low operation bias is what needed by circuit designers. In this work, we test the predictive capability of the well-known reaction-diffusion (RD) based framework for samples fabricated by a variety of processes. Results show that the RD model cannot make an acceptable generic prediction. The recently proposed As-grown-Generation (AG) model is then introduced. By dividing defects into two groups, as-grown and generated defects, and measuring the as-grown defects experimentally, we demonstrate that it can make reliable prediction for the same set of data where the RD model failed.

### I. INTRODUCTION

The gap between device models and real performance is one of the difficulties in optimizing circuit design. The inaccuracy in modeling aging can contribute to this gap [1, 2]. The negative bias temperature instability (NBTI) is a well-known reliability issue for both digital [3] and analog CMOS integrated circuits [4]. Although it was first reported in 1960s [5], it has become a serious aging issue only since 2000s or so, because the operation temperature and electrical field increase with downscaling [6] and nitrogen is routinely added to gate dielectric [7, 8].

Several NBTI models have been proposed, such as the two-stage model [9], reaction-diffusion (RD) based framework [10, 11], the composite model [12], and the as-grown-generation (AG) model [13-17]. In order to verify their correctness, a common practice is to demonstrate that they can fit the test data well. The tests were typically carried out at elevated Vg for a relatively short time (e.g. 1000 sec [10]) and there is little information on their capability to predict aging outside the test range used for the fitting. This predictive capability for long term aging under low operation bias is what needed by circuit designers.

The two-stage model has been extensively and critically reviewed recently [11,18]. In this paper, we will examine the predictive capability of the RD based framework and the AG models. The methodology is to test them under conditions as simple as possible, since if they do not work under the simplified test conditions, they cannot work when additional physical processes are involved. As a result, we only test the continuous stress (DC) with recovery process minimized here. It will be shown that both the RD based framework failed in the prediction assessment. In contrast, the As-grown-Generation (AG) model can predict the long-term degradation under low operation biases, based on the same set of test data.

### II. DEVICES AND EXPERIMENTS

# A. Devices

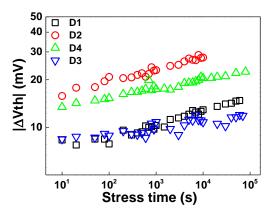

To test the generic predictive capability of the RD model, four processes were selected to represent different fabrication techniques (ALCVD, plasma nitridation, and thermal nitridation), dielectric materials/structures and (Al<sub>2</sub>O<sub>3</sub>-capped HfO<sub>2</sub>/SiON, HfSiON/SiON, SiON), and gate materials (TiN, p+ poly-Si) as listed in Table I. Both D1 and D2 have high-k stack and metal gates. Among the four processes, Fig. 1 shows that D2 has the highest NBTI under Vg=-1.1 V, representing a process under development. D3 is a plasma nitrided SiON and has the lowest NBTI, representing an industry-grade process. D4 is a thermally nitrided SiON and is used to give a high nitrogen density and high as-grown hole traps [19].

Fig. 1 A comparison of the aging of the four samples listed in table I under nominal operating bias, Vg, and 125 °C.

On device sizes, the NBTI models originally were proposed for large devices with a negligible statistical variation. There are efforts to adopt them for the nm-sized devices by introducing statistical distributions for the model parameters [14, 17, 20]. If the original model does not work for a large device, a revised model based on it will not work for nm-size devices. As the first step in testing their predictive capability, large devices were used in this work for simplicity with typical channel width of 10  $\mu$ m and length of either 1  $\mu$ m (D1) or 0.1  $\mu$ m (D2, D3, D4).

TABLE I SAMPLE LIST USED IN THIS WORK

| Device<br>number | Gate dielectrics                             | ЕОТ    |

|------------------|----------------------------------------------|--------|

| D1               | HfO2 with TiN gate                           | 1.45nm |

| D2               | HfSiON/SiON with TiN gate                    | 1.53nm |

| D3               | Plasma SiON with high N% and P+<br>poly gate | 2.0nm  |

| D4               | Thermal SiON with poly gate                  | 2.7nm  |

# B. Experiment

The test follows the commonly used stress-then-sense procedure and aging is monitored by pulse Id-Vg [21,22]. It starts by recording the reference Id-Vg from a 3  $\mu$ s gate pulse edge during which degradation is negligible [21]. The stress was carried out either under a constant Vg or a constant over-drive voltage, Vg\_ov=Vg-Vtho- $\Delta$ Vth. The threshold voltage shift, i.e.  $\Delta$ Vth, was monitored from the Vg shift at a constant sensing Id= 100 nA×W/L. The measurement delay is 3  $\mu$ s and the recovery is minimized [21]. All tests were carried out at the typical work temperature for modern CMOS technologies, i.e. 125 °C.

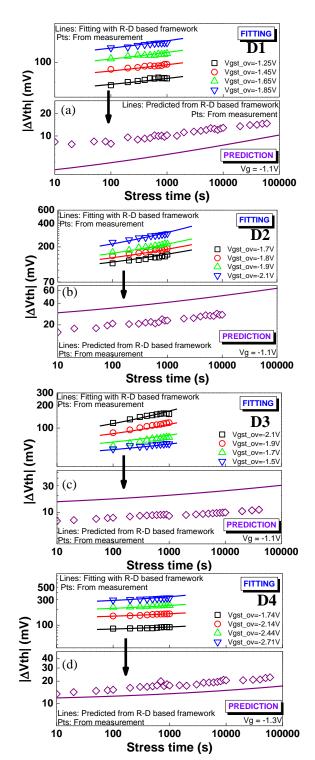

The constant Vg stressing was used in Fig. 1, since circuits operate under a fixed Vg. The NBTI, however, is believed to be driven by the oxide field at the interface, Eox, so that it is desirable to carry out tests under constant Eox. Under a constant stress Vg, |Eox| reduces as the positive charges built up with time. To maintain a constant Eox, the overdrive voltage, i.e. Vg\_ov=Vg-Vtho- $\Delta$ Vth, was kept as a constant through increasing the stress |Vg| by the  $|\Delta$ Vth| measured at the last step. The upper panels in Figs. 2(a)~(d) gives the  $\Delta$ Vth with Vg\_ov not changing with time.

#### III. FAILURE OF THE RD MODELS

The original RD model was proposed for NBTI on devices of thick SiO<sub>2</sub> (e.g. 95 nm) with the stress Eox low enough that hole injection was negligible [5,23]. For the thin dielectric (e.g. < 3 nm) used in current industry, however, hole injection and subsequent trapping is significant and the H/H<sub>2</sub> RD model has been revised [10, 11]. In the "RD based framework" [10, 11], RD process covers only the generation of interface states ( $\Delta V_{IT}$ ). Two other components have been added: i) As-grown hole traps ( $\Delta V_{HT}$ ), and ii) Generation of bulk traps ( $\Delta V_{\text{OT}}$ ). The filling of as-grown hole traps saturates generally within 10 sec and  $\Delta V_{HT}$  becomes time-independent for longer time. The formula of the simplest R-D based framework is given in eqns. (1)-(4), which is applicable to the stress phase for a stress time over 10 sec and should have the capability to predict the long term threshold voltage shift,  $\Delta V$ th, under operation Vg.

$$\Delta V_{IT} = \frac{q}{Cox} A \left( Vg - Vth0 - \Delta Vth \right)^{\Gamma_{IT}} e^{-\frac{L_{AIT}}{kT}} t^{1/6}$$

(1)

$$\Delta V_{HT} = \frac{q}{Cox} B \left( Vg - Vth0 - \Delta Vth \right)^{\Gamma_{HT}} e^{-\frac{E_{AHT}}{kT}}$$

(2)

$$\Delta V_{oT} = \frac{q}{Cox} C(1 - e^{\left(-\left(\frac{1}{n}\right)^{NOT}\right)})$$

(3)

where

$$n = \eta \cdot (Vg - Vth0 - \Delta Vth)^{-\frac{\Gamma_{oT}}{\beta_{oT}}} e^{(\frac{E_{AOT}}{kT\beta_{oT}})}$$

. (4)

**Fig. 2** Predictive capability assessment of the R-D based framework in eqns. (1)-(4). The symbols are test data. (a), (b), (c), and (d) are for the sample D1, D2, D3 and D4 given in table I, respectively. The upper panels of (a)-(d) give the  $\Delta$ Vth measured from short accelerated stresses and the lines are computed by using the fitted parameters in table II. The extracted model was then used to predict  $\Delta$ Vth under low operating Vg in the lower panels. The prediction (lines) does not agree with the test data.

Before testing the prediction capability, four parameters: A, B, C, and  $\Gamma_{\text{IT}} = \Gamma_{\text{HT}}$  must be fitted for the RD based framework. The other parameters in eqns. (1)-(4) are constant and given in ref. [10]. To verify the program we used for fitting the parameters, the test data given in ref. [10] were first used and the same values were obtained as those reported in ref. [10]. This RD based framework was then fitted with the NBTI data in the upper panels of Figs. 2(a)-(d) for the

processes given in table I. The model fits our test data well for all processes and the fitted values are given in table II.

When compared with the short accelerated stress for typical NBTI test, a device operates at lower Vg for longer time in real circuits. An extracted model is of value only if it can predict this long term NBTI at the low operation bias. The device should work for years, but the practical test time is typically only days. An extracted model should be able to predict two decades ahead at operation Vg, therefore.

To test the predictive capability of RD based framework, relatively long stresses at an operation Vg=-1.1 V were carried out and the results are given in the lower panels of Figs. 2(a)-(d).  $\Delta$ Vth predicted by RD based framework can be either higher or lower than the test data and we conclude that it does not have the required predictive capability.

**TABLE II** Extracted parameters from R-D based framework. To use these values, the unit for voltage is volts and for time is sec in eqns. (1)~(4).

|     | Device   |          |          |          |  |

|-----|----------|----------|----------|----------|--|

|     | D1       | D2       | D3       | D4       |  |

| Α   | 5.85E+11 | 1.41E+12 | 4.55E+11 | 1.21E+11 |  |

| В   | 2.07E+11 | 8.13E+11 | 4.62E+11 | 3.25E+11 |  |

| С   | 5.13E+14 | 3.84E+14 | 2.49E+14 | 8.73E+12 |  |

| ГІТ | 4.07     | 1.88     | 1.51     | 2.54     |  |

### IV. As-GROWN-GENERATION (AG) MODEL

Since modeling long term NBTI at operation bias is of importance to the circuit designers [24, 25] and the well-known models do not have the required predictive capability, there is a pressing need to develop a model with such capability. An As-grown-Generation model (AG) is proposed recently [13-17] and we now demonstrate its predictive capability. As this model is not well-known yet, we will introduce it first.

## A. The AG model and the two groups of defects

The AG model given in eqn. (7) is based on separating the defects into two groups: the as-grown hole traps (AHT), i.e. 'A', and the Generated defects (GD) represented by the second term.

$$\Delta Vth = A + G_0 \cdot (Vg - Vth0 - \Delta Vth)^m \cdot t^n \tag{7}$$

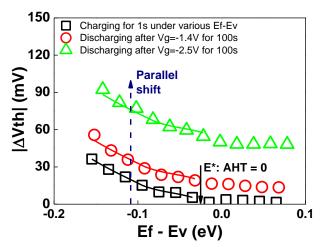

In 2001, it was shown that degradation is dominated by filling AHTs initially and new hole traps are generated, controlling the aging for longer time [26]. Generating new traps is an independent process from filling AHTs [27-30]. The AHTs are located below Si Ev, while the generated hole traps are above Ev [13, 31, 32]. The evidence for this framework was provided by the dependence of defects' energy distribution on stress levels. Based on the energy-probing technique in ref. [33], Fig. 3 shows that the AHT below Ev can be filled in ~1 sec and there are no hole traps above Ev in a fresh device. As stress level increases, trapping above Ev increases by generating new defects, but the trapping below Ev remains the same, as indicated by the parallel shift of the three curves.

# B. Experimental separation of the two components

A principle for developing a model is to minimize the number of fitting parameters, because this reduces the risk that a good agreement between a model and test data is just a result of 'curve-fitting' [34, 35]. The AG model in eqn. (7) potentially has four fitting parameters: A,  $G_o$ , m and n. Since Fig. 3 and early work [36] shows that filling AHTs completes  $\sim 1$  sec, it has been proposed to determine the 'A' experimentally [13] and the method is described below.

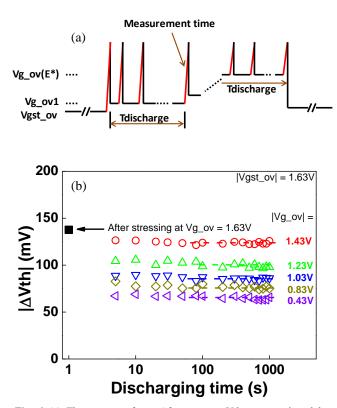

The Vg waveform used in this method is given in Fig. 4 (a) and the test consists of a stress phase, followed by a discharge phase. The early work [13] used constant Vg for both stress and discharge. The change in Fig. 3, however, is determined by Ef-Ev. For a commercial grade device with low  $|\Delta Vth|$ , the change in Ef-Ev is insignificant under a constant Vg. For a process under development, however,  $|\Delta Vth|$  can be large enough that the Ef-Ev may not be treated as a constant under a constant Vg. As a result, we carried out stress and discharge under а constant overdrive voltage, i.e. Vg\_ov=Vg-Vtho- $\Delta$ Vth, where  $\Delta$ Vth was measured and changed with time. The relation between Vg\_ov and Ef-Ev is determined by simulation [13, 33].

**Fig. 3** Energy distribution of positive charges in gate dielectric induced by NBTI. After only 1 sec charging, 'As-grown hole traps (AHTs)' were fully filled-up and will not increase further with stress levels, as shown by the three parallel-shifted curves. There are no AHTs above E\*. Above E\*, the increase of  $|\Delta Vth|$  with stress is caused by the generated defects (GD). The sample D1 was used here.

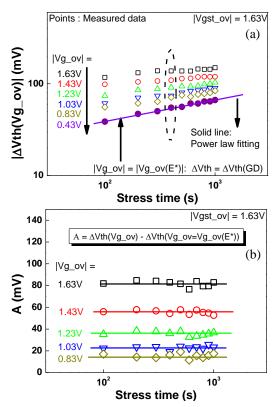

The E\* in Fig. 3 is the energy level above which AHT=0. Under typical stress Vgst\_ov, corresponding Ef is lower than E\* and some AHTs were filled and, together with the generated defects, gave the measured  $\Delta$ Vth ('**•**' in Fig. 4(b)). After stressing for a pre-specified time (e.g. 500 sec for Fig. 4(b)), the gate voltage was lowered towards positive to Vg\_ov1 to allow the AHT between Vgst\_ov and Vg\_ov1 discharging. The  $\Delta$ Vth during the discharge phase was monitored by the pulse Id-Vg, as shown by the waveform in Fig. 4(a). Fig. 4(b) shows that a discharge time of 100 sec is long enough for its completion.

After completing discharge at Vg\_ov1, Vg was stepped to Vg\_ov2 and the same procedure was followed to give the discharge data-sets for the lower  $|Vg_ov|$  in Fig. 4(b). The last discharge Vg\_ov used corresponds to (Ef-Ev)=E\*, where AHTs is completely discharged, i.e. AHT=0 (see Fig. 3). For the process D1, (Ef-Ev)=E\*=-0.03eV and the corresponding

Vg\_ov(E\*)=-0.8V. As 'A'=0 here, the measured  $\Delta V$ th contains only the generated defects (GD) that does not discharge for (Ef-Ev) $\leq$ E\*, i.e.,

$$\Delta Vth(GD) = \Delta Vth [Vg_ov(E^*)].$$

(8)

Once  $\Delta Vth(GD)$  is known, 'A' at a given Vg\_ov is evaluated from,

$$A = \Delta V th(Vg_ov) - \Delta V th (GD).$$

(9)

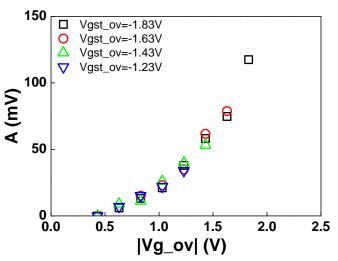

This experimentally determined 'A' is plotted against Vg\_ov in Fig. 5.

Fig. 4 (a) The test waveform. After stress,  $\Delta V$ th was monitored by applying a pulse to the gate (' $\bullet$ ' in (a)).  $|Vg_ov|$  was then lowered to discharge and  $\Delta V$ th are monitored periodically. The discharging  $|Vg_ov|$  was stepped lower until it reached  $|Vg_ov(E^*)|$ . (b) Typical discharge results under different  $|Vg_ov|$ , after stressing at Vgst\_ov = -1.63 V and 125 °C for 500 sec. Process D1 is used.

Fig. 4(b) was obtained after a stress time of 500 sec and the  $\Delta$ Vth at a discharge time of 200 sec is plotted as one data-set in Fig. 6 (a). In principle, other stress time can also be used to evaluate 'A', provided that it is long enough for the filling of AHTs to reach saturation. Fig. 6(a) shows the  $\Delta$ Vth(Vg\_ov) by repeating the measurement in Fig. 4 after different stress times and the evaluated 'A' by eqns (8) & (9) is given in Fig. 6(b). As expected, 'A' is insensitive to stress time, since it is 'as-grown'.

Once 'A'=0 at Vg\_ov(E\*), the  $\Delta$ Vth(GD) extracted by this method can be fitted well with a power law against stress time in Fig. 7. This strongly supports the AG model in eqn. (7).

**Fig. 5** The saturation level of as-grown hole traps, 'A', evaluated for different Vg\_ov by using the eqns. (8)-(9). The sample D1 was used.

**Fig. 6 (a)** A device was stressed under  $|Vg_ov|=1.63$  V for different time. After each stress time, the  $\Delta$ Vth at lower  $|Vg_ov|$  was measured by using the waveform in Fig. 4(a). The data-set in the dashed circle was the same as that in Fig. 4(b). (b) 'A' evaluated by using eqns. (8)-(9) under each Vg\_ov. It does not change with the stress time, because it saturated. It rises for higher  $|Vg_ov|$ , since a higher  $|Vg_ov|$  lowers Ef-Ev in Fig. 3.

It is worth of comparing the contributions of the 'A' and 'GD' by including the test data in short stress time, where 'A' has not reached its saturation. In Fig. 7,  $\Delta$ Vth(GD) was fitted by a power law and then subtracted from the measured  $\Delta$ Vth to give the  $\Delta$ Vth(AHT), i.e. the contribution from the AHT. Filling AHTs clearly dominates the NBTI initially, but then reached saturation around 1 sec. The GD becomes increasingly important as time increases.

**Fig. 7** A comparison of the contributions of as-grown hole traps (AHTs) and generated defects (GDs) to NBTI. The  $\Delta$ Vth(GD) was measured at Vg\_ov(E\*), where AHT=0, and fitted with a power law. The fitted dashed line was then subtracted from the measured  $\Delta$ Vth to evaluate  $\Delta$ Vth(AHT). AHTs clearly dominate NBTI initially, but saturates around 1 sec. The sample is D1.

# C. Differences of AG model from RD based framework

Differences of AG model from the RD based framework are (i) RD based framework fits the as-grown hole traps by equation (2), while AG uses the measured value; (ii) RD based framework separates hole trap generation in eqn. (3) from the creation of interface states in eqn. (1) and uses different kinetics for them. The AG combines them into the generated defect and uses the same kinetics as the second term in eqn. (7); (iii) R-D based framework fixes the time exponent at 1/6 for the generated interface state, while AG fits the time exponent; (iv) R-D based framework applies the same voltage exponent for generating interface states and filling the as-grown hole traps, but AG does not. (v) For fitting the stress phase with saturated AHTs, RD and AG uses four and three fitting parameters, respectively.

# D.Prediction capability of the AG model

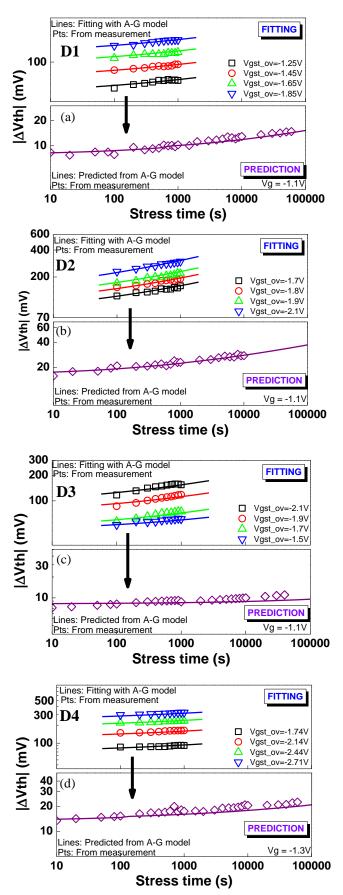

The AG model is tested by using the same data-sets as those for testing the RD based framework in Fig. 2. With the 'A' extracted using procedure described in section IV.B, the  $G_0$ , m, and n were fitted with the test data in the upper panels in Figs. 8(a)~(d) for each process and their values are listed in table III. Like the RD, the AG model fits the test data well.

The G<sub>o</sub>, m, and n were fitted from the short accelerated stresses and we now test whether this extracted AG model can predict the long term aging under low operation bias. By using the eqn. (7), together with the measured 'A', the predicted  $\Delta$ Vth are compared with the measured data in the lower panels of Figs. 8 (a) ~ (d). The agreement is good for all four processes. We conclude that the AG model has a generic predictive capability.

**TABLE III** Extracted parameters from A-G model. To use these values, the unit for voltage is volts and for time is sec in eqn. (7).

|    | Device   |          |          |          |  |

|----|----------|----------|----------|----------|--|

|    | D1       | D2       | D3       | D4       |  |

| Go | 1.80E-03 | 2.40E-03 | 5.93E-04 | 1.56E-03 |  |

| m  | 4.13     | 3.622    | 4.186    | 2.6434   |  |

| n  | 0.231    | 0.232    | 0.239    | 0.183    |  |

Fig. 8 Predictive capability assessment of the AG model. The test data (symbols) are the same as that in Fig. 2. (a), (b), (c), and (d) are for the sample D1, D2, D3 and D4 given in table I, respectively. The lines in the upper panels are computed by using the fitted parameters in table IV. The extracted model was then used to predict  $\Delta$ Vth under low operating Vg in the lower panels. The prediction (lines) agrees well with the test data for all processes.

## V.CONCLUSIONS

NBTI models are generally extracted by fitting the short accelerated stress data. This work tests their capability to predict the long term stress phase under low operation bias for a range of fabrication processes. The RD based framework failed, but the AG model succeeded, in making the required prediction. By separating degradation into As-grown and Generated defects and experimentally determining the saturation value of the as-grown hole traps, the aging kinetics is reduced to a power law with only three fitting parameters, allowing the reliable extraction of model parameters and, in turn, the prediction.

#### ACKNOWLEDGMENT

The authors thank B. Kaczer, D. Linten, and G. Groeseneken of IMEC, Belgium, for discussions and supply of test samples used in this work. This work is supported by the EPSRC of UK under the grant no. EP/L010607/1.

### REFERENCES

- E. Y. Wu, J. H. Stathis, and L. K. Han, "Ultra-thin oxide reliability for ULSI applications," *Semicond. Sci. Technol.*, vol. 15, no. 5, pp. 425, 2000.

- [2] F. Driussi, F. Widdershoven, D. Esseni, L. Selmi, and M. J. van Duuren, "Experimental characterization of statistically independent defects in gate dielectrics-part I: description and validation of the model," *IEEE Trans. Electron Devices*, vol. 52, no. 5, pp. 942, 2005.

- [3] V. Reddy, A. T. Krishnan, A. Marshall, J. Rodriguez, S. Natarajan, T. Rost, and S. Krishnan, "Impact of negative bias temperature instability on digital circuit reliability," in *Proc. Int. Rel. Phys. Symp.*, pp. 248, 2002.

- [4] N. K. Jha, P. S. Reddy, D. K. Sharma, and V. Ramgopal Rao, "NBTI degradation and its impact for analog circuit reliability," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2609, 2005.

- [5] B. E. Deal, M. Sklar, A. S. Grove, and E. H. Snow, "Characteristics of the Surface - State charge (Qss) of thermally oxided silicon," *J. Electrochem. Soc.*, vol. 114, no. 3, pp. 266, 1967.

- [6] G. Chen, M. F. Li, C. H. Ang, J. Z. Zheng, and D. L. Kwong, "Dynamic NBTI of p-MOS transistors and its impact on MOSFET scaling," *IEEE Electron Device Lett.*, vol. 23, no. 12, pp. 734, 2002.

- [7] S. S. Tan, T. P. Chen, J. M. Soon, K. P. Loh, C. H. Ang, and L. Chan, "Nitrogen-enhanced negative bias temperature instability: An insight by experiment and first-principle calculations," *Appl. Phys. Lett.*, vol. 82, no. 12, pp. 1881, Mar, 2003.

- [8] Y. Mitani, H. Satake, and A. Toriumi, "Influence of Nitrogen on Negative Bias Temperature Instability in Ultrathin SiON," *IEEE Trans. Device Mater. Rel.*, vol. 8, no. 1, pp. 6, 2008.

- [9] T. Grasser, B. Kaczer, W. Goes, T. Aichinger, P. Hehenberger, and M. Nelhiebel, "A two-stage model for negative bias temperature instability," in *Proc. Int. Rel. Phys. Symp.*, pp. 33-44, 2009.

- [10] K. Joshi, S. Mukhopadhyay, N. Goel, and S. Mahapatra, "A consistent physical framework for N and P BTI in HKMG MOSFETs," in *Proc. Int. Rel. Phys. Symp.*, pp. 5A.3.1, 2012.

- [11] S. Mahapatra, N. Goel, S. Desai, S. Gupta, B. Jose, S. Mukhopadhyay, K. Joshi, A. Jain, A. E. Islam, and M. A. Alam, "A Comparative Study of Different Physics-Based NBTI Models," *IEEE Trans. Electron Devices*, vol. 60, no. 3, pp. 901, 2013.

- [12] V. Huard, C. Parthasarathy, N. Rallet, C. Guerin, M. Mammase, D. Barge, and C. Ouvrard, "New characterization and modeling approach for NBTI degradation from transistor to product level," in *IEDM Tech. Dig.*, pp. 797, 2007.

- [13] Z. Ji, S. W. M. Hatta, J. F. Zhang, J. G. Ma, W. D. Zhang, N. Soin, B. Kaczer, S. De Gendt, and G. Groeseneken, "Negative Bias Temperature Instability lifetime prediction: Problems and Solutions," in *IEDM Tech. Dig.*, pp. 413-416, 2013.

- [14] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, A. Thean, G. Groeseneken, and A. Asenov, "Time-dependent variation: A new defect-based prediction methodology," in *Proc of IEEE VLSI Tech. Symp.*, pp.74-75, 2014.

- [15] J. Ma, W. Zhang, J. F. Zhang, B. Benbakhti, Z. Ji, J. Mitard, J. Franco, B. Kaczer, and G. Groeseneken, "NBTI of Ge pMOSFETs:

understanding defects and enabling lifetime prediction," in *IEDM Tech. Dig.*, pp. 820-823, 2014.

- [16] Z. Ji, J. F. Zhang, L. Lin, M. Duan, W. Zhang, X. Zhang, R. Gao, B. Kaczer, J. Franco, T. Schram, N. Horiguchi, S. De Gendt, and G. Groeseneken, "A test-proven As-grown-Generation (A-G) model for predicting NBTI under use-bias," in *Proc. IEEE VLSI Tech. Symp.*, pp.36-37, 2015.

- [17] R. Gao, Z. Ji, S. M. Hatta, J. F. Zhang, J. Franco, B. Kaczer, W. Zhang, M. Duan, S. De Gendt, D. Linten, G. Groeseneken, J. Bi and M. Liu, "Predictive As-grown-Generation (A-G) model for BTI-induced device/circuit level variations in nanoscale technology nodes," in *IEDM Tech. Dig.*, pp. 778-781, 2016.

- [18] V. Huard, "Two independent components modeling for Negative Bias Temperature Instability," in *Proc. Int. Rel. Phys. Symp.*, pp. 33, 2010.

- [19] K. Sakuma, D. Matsushita, K. Muraoka, and Y. Mitani, "Investigation of Nitrogen-Originated NBTI Mechanism in SiON with High-Nitrogen Concentration," in *Proc. Int. Rel. Phys. Symp.*, pp. 454, 2006.

- [20] P. Ren, R. Wang, Z. Ji, P. Hao, X. Jiang, S. Guo, M. Luo, M. Duan, J. F. Zhang, J. Wang, J. Liu, W. Bu, J. Wu, W. Wong, S. Yu, H. Wu, S. W. Lee, N. Xu, and R. Huang, "New Insights into the design for end-of-life variability of NBTI in scaled high-k/metal-gate technology for the nano-reliability era," in *IEDM Tech. Dig.*, pp. 816-819, 2014.

- [21] Z. Ji, J. F. Zhang, M. H. Chang, B. Kaczer, and G. Groeseneken, "An Analysis of the NBTI-Induced Threshold Voltage Shift Evaluated by Different Techniques," *IEEE Trans. Electron Devices*, vol. 56, no. 5, pp. 1086, 2009.

- [22] L. Lin, Z. Ji, J. F. Zhang, W. D. Zhang, B. Kaczer, S. De Gendt, and G. Groeseneken, "A single pulse charge pumping technique for fast measurements of interface states," *IEEE Trans. Electron Dev.*, vol. 58, No.5, pp. 1490, 2011.

- [23] K. O. Jeppson, and C. M. Svensson, "Negative Bias Stress of MOS devies at high electric-fields and degradation of MNOS devices," J. Appl. Phys., vol. 48, no. 5, pp. 2004, 1977.

- [24] B. Tudor, J. Wang, C. Sun, Z. P. Chen, Z. J. Liao, R. Tan, W. D. Liu, and F. Lee, "MOSRA: An efficient and versatile MOS aging modeling and reliability analysis solution for 45nm and below," in *ICSICT*, pp. 1645, 2010.

- [25] Z. H. Liu, B. W. McGaughy, and J. Z. Ma, "Design tools for reliability analysis," in *Design Automation Conference*, pp. 182, 2006.

- [26] J. F. Zhang, H. K. Sii, G. Groeseneken, and R. Degraeve, "Hole trapping and trap generation in the gate silicon dioxide," *IEEE Trans. Electron Devices*, vol. 48, no. 6, pp. 1127, Jun, 2001.

- [27] J. F. Zhang, C. Z. Zhao, A. H. Chen, G. Groeseneken, and R. Degraeve, "Hole traps in silicon dioxides Part I: Properties," *IEEE Trans. Electron Devices*, vol. 51, no. 8, pp. 1267, Aug, 2004.

- [28] C. Z. Zhao, J. F. Zhang, G. Groeseneken, and R. Degraeve, "Hole-traps in silicon dioxides - Part II: Generation mechanism," *IEEE Trans. Electron Devices*, vol. 51, no. 8, pp. 1274, Aug, 2004.

- [29] C. Z. Zhao, and J. F. Zhang, "Effects of hydrogen on positive charges in gate oxides," J. Appl. Phys., vol. 97, no. 7, Apr, 2005.

- [30] M. H. Chang, and J. F. Zhang, "On positive charge formed under negative bias temperature stress," J. Appl. Phys., vol. 101, no. 2, Jan, 2007.

- [31] C. Z. Zhao, J. F. Zhang, M. H. Chang, A. R. Peaker, S. Hall, G. Groeseneken, L. Pantisano, S. De Gendt, and M. Heyns, "Stress-induced positive charge in Hf-based gate dielectrics: Impact on device performance and a framework for the defect," *IEEE Trans. Electron Devices*, vol. 55, no. 7, pp. 1647, Jul, 2008.

- [32] J. F. Zhang, "Defects and instabilities in Hf-dielectric/SiON stacks (Invited Paper)," *Microelectron. Eng.*, vol. 86, no. 7, pp. 1883, 2009.

- [33] S. W. M. Hatta, Z. Ji, J. F. Zhang, M. Duan, W. D. Zhang, N. Soin, B. Kaczer, S. De Gendt, and G. Groeseneken, "Energy Distribution of Positive Charges in Gate Dielectric: Probing Technique and Impacts of Different Defects," *IEEE Trans. Electron Devices*, vol. 60, no. 5, pp. 1745, 2013.

- [34] C. Z. Zhao, J. F. Zhang, M. B. Zahid, B. Govoreanu, G. Groeseneken, and S. De Gendt, "Determination of capture cross sections for as-grown electron traps in HfO2/HfSiO stacks," J. Appl. Phys., vol. 100, no. 9, Nov, 2006.

- [35] M. H. Chang, J. F. Zhang, and W. D. Zhang, "Assessment of capture cross sections and effective density of electron traps generated in silicon dioxides," *IEEE Trans. Electron Devices*, vol. 53, no. 6, pp. 1347, Jun, 2006.

- [36] Z. Ji, L. Lin, J. F. Zhang, B. Kaczer, and G. Groeseneken, "NBTI Lifetime Prediction and Kinetics at Operation Bias Based on Ultrafast Pulse Measurement," *IEEE Trans. Electron Devices*, vol. 57, no. 1, pp. 228, Jan, 2010.