#### HIGHLY CONCURRENT VS. CONTROL FLOW COMPUTING MODELS

by

ROBERT CLARENCE MARSHALL

B.S., University of Rochester, 1972

#### A MASTER'S REPORT

submitted in partial fulfillment of the

requirements for the degree

MASTER OF SCIENCE

Department of Computer Science

KANSAS STATE UNIVERSITY Manhattan, Kansas

1982

Approved by:

Major Professor

#### **ACKNOWLEDGEMENTS**

Thanks are due to my major professor, Dr. David

Gustafson, for his guidance and encouragement. Although I am solely responsible for final form and

content, Dave suggested the general organization of

the report. I would also like to thank NCR Corporation

who contributed many resources during report preparation.

I would like to give special thanks to my wife, Mary Ann, for her patience, love, and understanding, and for typing the manuscript.

## TABLE OF CONTENTS

|            |                                              | PAGE |

|------------|----------------------------------------------|------|

| LIST OF    | TABLES                                       | iii  |

| LIST OF    | FIGURES                                      | iv   |

| 1.1<br>1.2 | Introductory Remarks                         | 1    |

| CHAPTER    | 2                                            | 16   |

| Abstrac    | ct Computing Models                          | 16   |

| 2.1        | Highly Concurrent Computing Models           | 16   |

|            | 2.1.1 The Data Flow Model                    | 30   |

| 2 2        | 2.1.2 The Functional Model                   | 54   |

| 2.2        | 2.2.1 The Structure of Conventional Programm | ing  |

|            | Languages                                    | 63   |

|            | 2.2.2 Synchronization Primitives             | 66   |

|            | 2.2.3 Monitors                               | 68   |

| 2.3        | Comparing Highly Concurrent and Control Flow |      |

| 2.5        | Models                                       | 70   |

|            | Model3                                       |      |

| CHAPTER    | R 3                                          |      |

| Impleme    | entations of Computing Models                | 76   |

| 3.1        | Data Flow Implementations                    | / 0  |

| 3.2        | A Functional Implementation                  | 86   |

| 3.3        | Parallel Taxonomies                          | 98   |

| 3.3        | 3.3.1 A Control Flow Taxonomy                | 98   |

|            | 3.3.2 An Extended Taxonomy                   | 99   |

| 3.4        | Comparing Highly Concurrent and Control Flow |      |

|            | Computing Implementations                    | 109  |

|            |                                              |      |

| CHAPTER    | R 4                                          |      |

| Conclus    | sion                                         | 113  |

| 4.1        | The Emperor's Old Clothes                    | 117  |

| DEEEDEN    | NCES                                         |      |

# **APPENDICES**

| ח | ٨ | $\boldsymbol{\mathcal{C}}$ | т |

|---|---|----------------------------|---|

| r | А | J.                         | Г |

| APPEN | NDIX A  |     |           |     |    |         |    |        |

|-------|---------|-----|-----------|-----|----|---------|----|--------|

| Some  | Details | of  | Operation | and | an | Example | of | Mago's |

| Funct | ional A | rch | itecture  |     |    |         |    |        |

| APPEND: | IX B                                              |

|---------|---------------------------------------------------|

| The Al  | gebra of Functional Programs                      |

| B.1     | Laws of the Algebra of Programs                   |

| B.2     | FoundationsB-4                                    |

|         | B.2.1 Expansion Theorem                           |

|         | B.2.2 Linear Expansion Theorem                    |

| B.3     | Recursion and IterationB-7                        |

|         | B.3.1 Recursion Theorem                           |

|         | B.3.2 Iteration Theorem                           |

| B.4     | Proofs for Functional Programs                    |

| B.5     | Example of a Recursive Program and its ProofB-8   |

|         | B.5.1 Recursive Factorial Function                |

|         | B.5.2 Proof for Recursive Factorial Function.B-10 |

#### LIST OF TABLES

| PA                                                                  | AGE        |

|---------------------------------------------------------------------|------------|

| Table 1 Some FP Functional Forms [BACK78]                           | 4 3        |

| Table 2 A Chart Illustrating Backus' Classification Scheme [BACK78] | 56         |

| Table 3 Basic Types of Global Control Units (Taxonomies) [KUCK78]10 | 00         |

| Table 4 Some Types of Array GCU's [KUCK78]1                         | 01         |

| Table 5 Example of (Partial) Highly Concurrent Taxonomy1            | 0 8        |

| Table 6 Speedup Factors (n Processors) [MEAD80]                     | 15         |

| Table B.1 Example of Application of Recursive Factorial Function    | <b>-</b> 9 |

## LIST OF FIGURES

| PAGE                                                                        |

|-----------------------------------------------------------------------------|

| Figure 1 Control Flow Design Hierarchy [SCHN79]15                           |

| Figure 2 VLSI Design Hierarchy [SCHN79]15                                   |

| Figure 3 Language-Based Design Hierarchy for Data Flow Computers [DENN80]18 |

| Figure 4 Segment of a Data Flow Program Graph20                             |

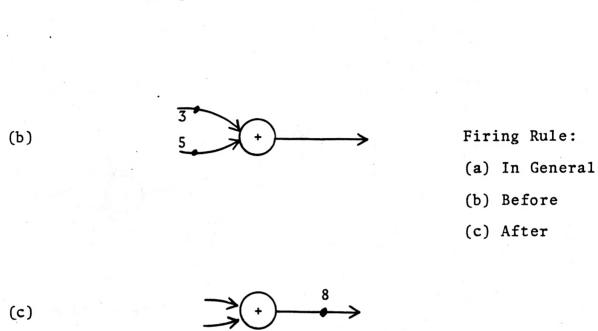

| Figure 5 Firing Rules [DENN80]21                                            |

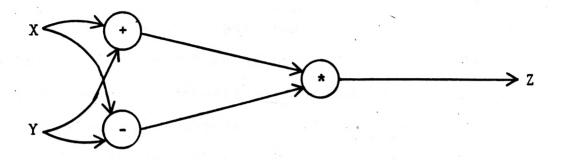

| Figure 6 Examples of Program Graphs22                                       |

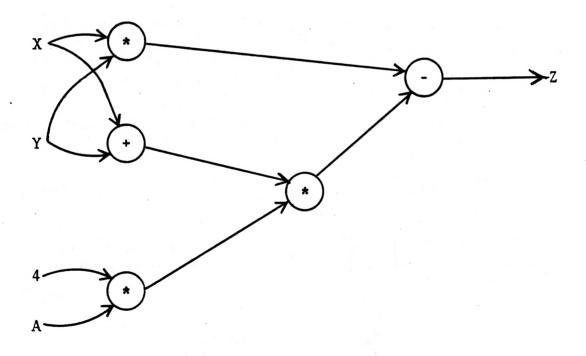

| Figure 7 Switch and Merge Actors [DENN80]23                                 |

| Figure 8 Multiply Activity Template24                                       |

| Figure 9 Composition of Operators Using Activity Templates [DENN80]25       |

| Figure 10 Example Data Flow Program Representation [TREL79]29               |

| Figure 11 Inner Product Functional Program Application [BACK78]53           |

| Figure 12 Typical Control Flow Assignment Statements57                      |

| Figure 13 Basic Structure of a Control Flow Computer [BACK78]59             |

| Figure 14 Example of Fork and Join Synchronization Primitives in [TREL79]   |

| Figure 15<br>Rumbaugh's Conceptual Data Flow Model [RUMB77]80            |

|--------------------------------------------------------------------------|

| Figure 16 Rumbaugh's Activation Processor [RUMB77]81                     |

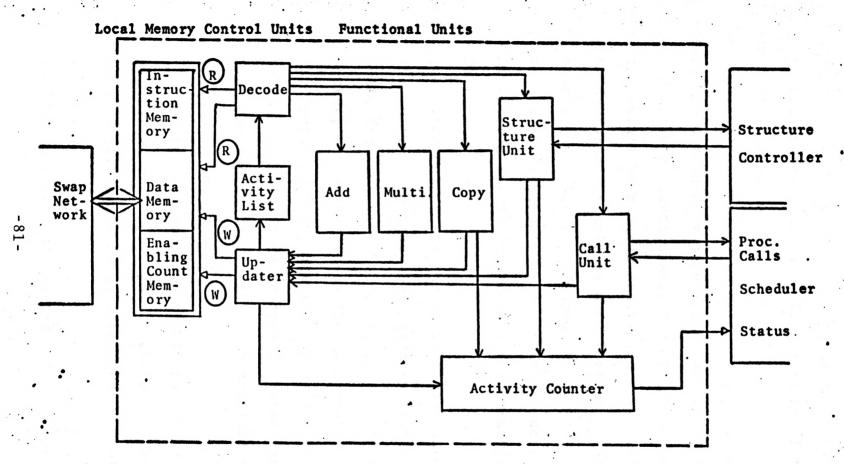

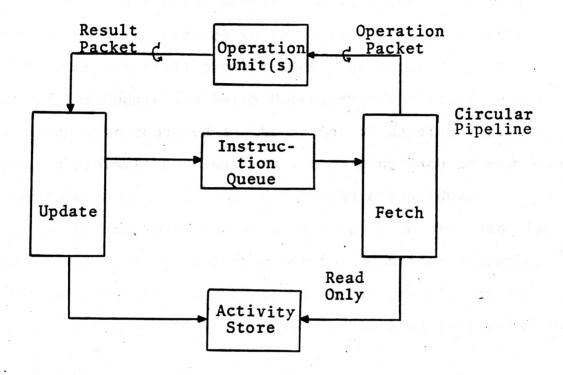

| Figure 17 Dennis' Instruction Execution Mechanism [DENN80]83             |

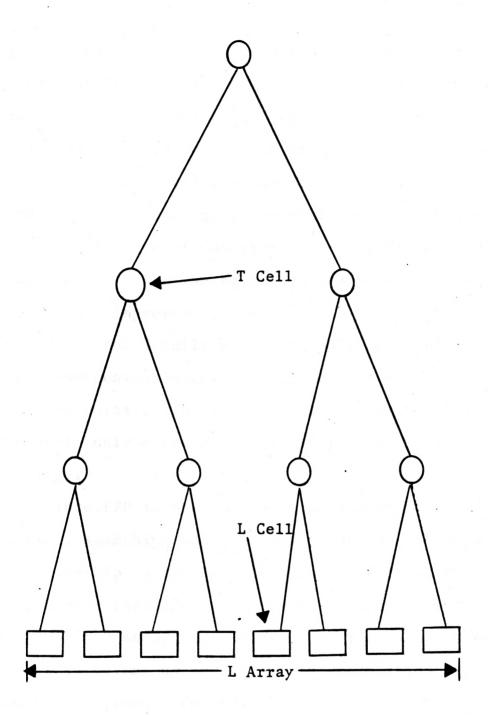

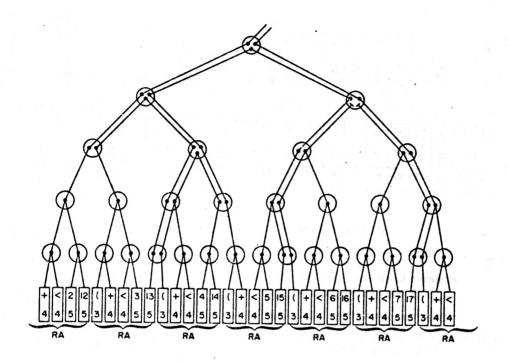

| Figure 18 Magó's Binary Tree Structure [MAGO80]89                        |

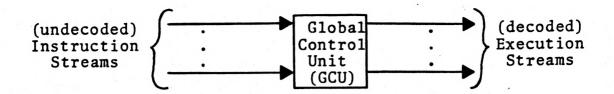

| Figure 19 Global Control Unit [KUCK78]99                                 |

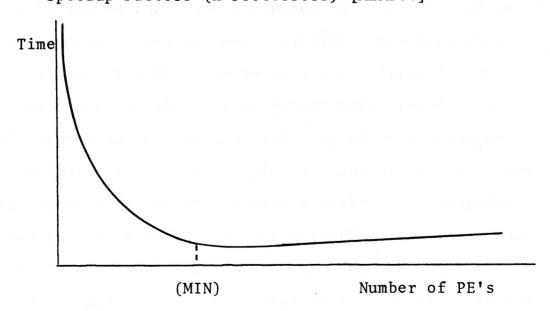

| Figure 20 Speedup Curve for Data Flow Speedup Experiments of [GOST80]115 |

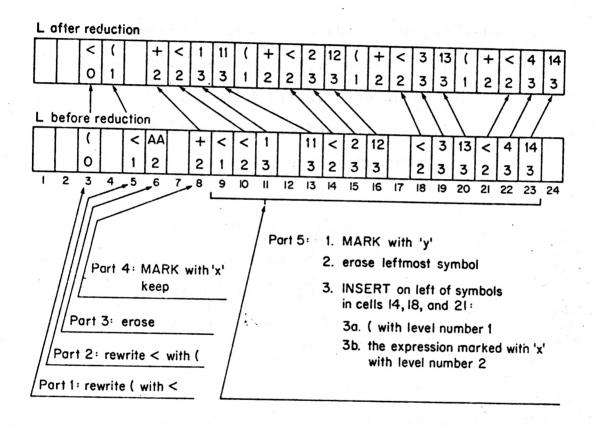

| Figure A.la Interconnection of Cells [MAGO80]A-14                        |

| Figure A.1b<br>A Possible Layout Scheme [MAGO80]                         |

| Figure A.2 Fragment of a Partitioned Network [MAGO80]A-15                |

| Figure A.3 Microprogram for AA (Apply to All) [MAGO80]A-16               |

#### CHAPTER 1

#### Introduction

This report reviews, contrasts, and compares two classes of computing models:

- highly concurrent models, in which concurrent operation is implicitly assumed;

- control flow models, in which sequential operation is implicitly assumed.

The highly concurrent class is represented in the report by two models: the data flow and functional models. Highly concurrent models are being made practical for commercial implementation by advancing technology.

The control flow model is represented by von Neumann computing principles. This model has been identified with digital computers since the inception of discrete computing machines.

The next section will summarize the organization of the report. Two key properties which significantly shape the form of the report will also be briefly introduced.

#### 1.1 Introductory Remarks

The control flow model has had a dominant influence on digital computers. Until the advent of Large Scale Integration and Very Large Scale Integration (LSI/VLSI), it had literally become synonomous with "computers."

Recently, the importance of formalizing the study of models has become more apparent as LSI/VLSI techniques have introduced technological and economic changes in design that favor non-control-flow models.

The data flow and functional models are different in two important respects from the control flow model:

- they are designed for implicitly concurrent operation;

- they are not history sensitive.

The first property has evolved as a natural consequence of the improving technology and is highly advantageous, but the second is more a product of our current scientific position and is not always a desirable property. History sensitivity is just the ability for data values to be stored internally for indefinite periods and utilized whenever desired.

History sensitivity is at once a strength and a weakness of the control flow model. Internal storage of data values enhances high-volume commercial and data file processing capabilities, but it also introduces the side effects so well known to commercial computing. These side effects result in unexpected, additional values of variables assigned to memory locations which are multiply named. The multiple naming occurs in global portions of procedures. Global and common storage areas require synchronization primitives to be used in multiprocessed

sections of code. This severely restricts the ability of the control flow model to be used well in the design of concurrent routines.

Models that eliminate unwanted side effects by restricting or eliminating history sensitivity allow easy and efficient concurrent design, but only at the expense of internal storage capabilities. Examples of such models include the data flow and functional models. Functional models have the capability of being extended to add a history-sensitive property (FFP model in Section 2.1.2).

Together, concurrency and history sensitivity present the best opportunity to compare and contrast the highly concurrent models with the control flow model. The report will return to considerations of these two properties frequently, particularly in Section 2.3.

Chapter 2 will present discussions of the abstract highly concurrent models and of the abstract control flow model. Some key points of comparison between the two types of models will be discussed in Section 2.3.

Chapter 3 will consider implementations of the data flow and functional models. A discussion of parallel taxonomies will close the chapter.

Chapter 4 concludes the report. Included is an allegory representing the fallacy of designing do-everything programming languages without due consideration for the attributes of programmer ease of use, algorithm complexity, and underlying technological advances. Complex

von Neumann designs may someday find it difficult to locate an architecture for implementation. Languages of the future must never lose sight of architectures upon which they can be realized.

A third significant area of difference between highly concurrent and control flow models is not so apparent until one attempts a comparison between them. concurrent models, such as the data flow and functional models, are much easier to consider apart from their implementations, simply because their abstract structures (i.e., their "models" as opposed to their "implementations") were developed separately from any fixed ideas about specific hardware realizations. During the early development years of control flow computing, the concept of "model" was rarely considered separately from implementation, and the development of hardware realizations drove the structure of the model. As a result, no separate theoretical structure now exists for the control flow "model" which can rival the comparable highly concurrent models. report considers the von Neumann "model" in Chapter 2, and many von Neumann concepts will be seen to require some reference to hardware concepts, such as "registers" and "memory locations". Since so much is known of von Neumann implementations, little would be gained by presenting one in Chapter 3; therefore, Chapter 3 concentrates on data flow

and functional implementations, while von Neumann implementations are discussed only during Sections 3.3 (on parallel taxonomies) and Section 3.4 (comparison of control flow and highly concurrent implementations).

The next section summarizes the impacts of LSI/

VLSI technology which are bringing highly concurrent

models to the forefront. Impacts on hardware, software,

and design will be discussed.

## 1.2 Structural Impacts of LSI/VLSI Technology

The control flow model was the model for almost all digital computers in the early 1970's, and few designers had given much thought to any other. The cost functions of computing included expensive (global) memory, expensive discrete components, and a "medium" scale of integration allowing chips fabricated with, perhaps, 1000 transistors per chip. Control flow models tended to minimize the total cost of computing. At about that time, techniques for Large Scale Integration (LSI) and Very Large Scale Integration (VLSI) began to emerge.

VLSI and LSI techniques were revolutionary and would offer the promise of fabricating chips containing  $10^5$  individual transistors by 1980 and  $10^7$  or  $10^8$  transistors by 1990 (NECH79], [SCHW80]). Meanwhile, the cost of memory was decreasing substantially. With VLSI

technology, it became easy to implement interconnecting networks of vast numbers of processing and memory elements on single silicon chips. The cost functions for these kinds of chips were dramatically changed from all that had gone before; now, cost (and efficiency) of a device was more dependent on the total lengths of interconnecting paths between elements than on the elements themselves ([MEAD80], [MAGO80], [SCHW80]). The global memory structures of control flow computing were no longer acceptable, since local memory with each processing element minimized interconnections and improved processing efficiency.

The primary problem posed to computer scientists and engineers by VLSI became one of how to best exploit this technology. Sugarman in [SUGA80] envisions VLSI design tasks falling into two categories:

- structuring control flow designs into VLSI;

- abandoning control flow designs totally to utilize the full power of VLSI.

Only in the latter category can the full promise of concurrency available in VLSI systems be tapped. However, as Rem notes in [SUGA80], computer scientists are only now mastering the theory of sequential programming, and they are currently ill-prepared to supply programming techniques to make VLSI structures a reality. Computer design engineers have discovered that design times of fifty man years could be required to design and fabricate

a 100K device chip without improved computer-aided design techniques [NECH79]. (Remember, a 100K device chip is feasible today; by 1990, 10<sup>5</sup>K device chips may be feasible!) The challenges inherent to VLSI design are many, but the rewards could be very great.

Section 1.2.1 discusses some impacts of LSI/VLSI technology on hardware structures, while section 1.2.2 discusses impacts on languages and software. Section 1.2.3 presents a change in viewpoint for total system design that is necessary for VLSI design.

## 1.2.1 Impact on Hardware Structures

How will VLSI affect conventional hardware structures? Mead and Conway [MEAD80] provide some interesting insights. This section is a summary of their findings.

Both processing and memory elements can easily be implemented in VLSI: "A human brings to an organization what VLSI brings to a circuit: both combine processing and memory effortlessly." Long interconnecting wires which impede communications are eliminated. The resultant systems support very high degrees of concurrent operations.

Mead reviews processor/memory architectures

(control flow machines) in terms of resource usage.

For large global memory systems most memory and memory wiring is idle most of the time. A four megabyte memory of 32 bits/word width, for example, may access only one

word of four million 32-bit words at one time. Many resources are expended by communication of data words over relatively large distances (buses, etc.). A discussion of memory locality and how it's implemented in a memory hierarchy illustrates an inverse relationship between memory size (M) and speed of access. The access time, T, is proportional to the square root of memory size, M. For register memory ( $M_T$ ), cache memory ( $M_C$ ), primary memory ( $M_D$ ), and secondary memory ( $M_S$ ) (i.e., disks), a model for memory access time is presented:  $M_T$   $M_T$

$T_{avg} = F_r (M_r)^{\frac{1}{2}} + F_c (M_c)^{\frac{1}{2}} + F_p (M_p)^{\frac{1}{2}} + 100 F_s (M_s)^{\frac{1}{2}}$ Typical frequency values are:

$$F_r = 0.6$$

$F_c = 0.38$

$F_p = 0.02$

$F_s = 5 \times 10^{-6}$

Access to secondary storage dominates.

Two other methods have been used to increase speed:

- pipeline structures;

- multiprocessor structures.

Pipeline structures with local memory increase processing power to a greater factor than just by the number of processors provided because each processor can have a smaller local memory. For example, a two-processor pipeline more than doubles available processing power:<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>[MEAD80], pp. 266-7.

<sup>&</sup>lt;sup>2</sup>[MEAD80], p. 267.

$$T_e = \frac{1}{2} (M/2)^{\frac{1}{2}}$$

$T_{e}$ , execution time, is about 1/3 the time for one processor (note that this formula ignores interconnection costs). This effect occurs as the result of two factors:

- doubling number of processors doubles speed;

- localizing memory to each processor and reducing memory size for each increases speed.

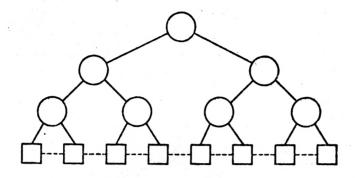

Effective multiprocessor systems in VLSI will probably be hierarchical structures, such as binary trees of processors (see section 3.2). Simple systems are combined into large, complex structures consisting of perhaps hundreds or thousands of elemental processor and memory combinations. The binary tree is a structure with some ability to utilize all processors concurrently. In general, trees also have other advantages:

- can be tested comparatively easily;

- general computing structures for a general class of problems are well-represented by trees.

On VLSI chips it is extremely important to minimize wire length to minimize both time delay and energy dissipation. There is a definite tradeoff between increasing processor/memory combinations and the resultant area required for wires:

hierarchical structures improve performance to a point;

if a hierarchical structure gets too large,

it begins to require too much interconnecting

wire area.

With the emergence of VLSI problems must be framed from the beginning in terms of concurrency. In this environment communication is expensive and computation is not. VLSI presents a challenge to computer science: "Develop a theory of computation that accommodates a more general model of the costs involved in computing. The current VLSI revolution has revealed weaknesses of a theory too solidly attached to the cost properties of a single sequential machine." [MEAD80]

Summarizing these considerations in [MEAD80] we can list some properties advantageous to VLSI hardware structures:

- large numbers of fairly simple processors connected together in complex hierarchies, such as binary tree structures;

- small amounts of local memory associated with each processor;

- pipeline structures;

- techniques to optimize wire area (minimum)

versus hierarchy size;

- concurrency implicit to the model;

- new theories of computation embracing concurrent rather than sequential operation.

Finally, the huge area of parallel algorithms is still in its early developmental stages. Kung ([KUNG80] and [MEAD80]) reviews this field. Because so many of these new algorithms will be implemented in hardware structures, there is going to be a major impact on computer scientists to interact with other disciplines during computer design. Lattin ([NECH79] and [SUGA80]) cites a growing crisis in VLSI design in which the sheer numbers of devices in a structure such as a microprocessor can require inordinate design times. This affects computer science in two ways:

- more must be known about parallel algorithms in general, so structures can be designed using standard devices and/or techniques, rather than custom-designed devices, etc.;<sup>3</sup>

- much more of the design process must be done by utilizing computers (computer-aided design CAD).

The area of parallel algorithms is so large it would require a separate report to cover it adequately.

$<sup>^{3}</sup>$ In [SUGA80] Lattin maintains the ratio D = DT/DC

Where DT = devices of all kinds, and DC = custom designed devices

for the intel 8086 was such that D = 4.4. He feels D = 20 must be attained to cut a 60 man-year effort to 5 man-years.

The ultimate impact upon conventional control flow computing will obviously be very large.

## 1.2.2 Impact on Software Structures

The impact on sequential programming languages consists in part of techniques to translate conventional high level language programs to equivalent parallel representations as in [ALLA76], or to compile conventional language programs into code for one of the parallel architectural models, as in ([JOHN80], [KUCK79]). Kuck discusses compiling techniques for structures consisting of arrays of microprocessors. This report will not examine these techniques in detail.

Newer highly concurrent languages and processing techniques are also appearing. Brock and Montz [BROC79], Gurd and Watson [GUR680], and Treleaven [TREL79] all discuss some of these language structures. Treleaven includes an example program written in a data flow language which will be examined in chapter 2 (Section 2.1.1). This kind of language will require programmers to alter their views of machine communications and structures to fit the highly concurrent models. Gurd and Watson contains an excellent discussion of some flow-graph techniques for structuring parallel software.

#### 1.2.3 Impact on Design

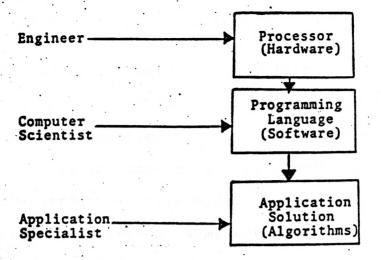

Section 1.2.1 ended with a discussion of parallel algorithms and the impact these would have on the design of software structures. An important additional consideration for these algorithms in the VLSI environment was that many would also affect hardware design In control flow computing the hardware structures. design activity was distinctly separate from both the language and application design activities. Hardware design actually drove the other two activity areas, and, to a great extent, language design drove application design. Thus, a design hierarchy with hardware design at the top and application design at the bottom was typical. In the era of expensive discrete hardware components, expensive banks of global memory, and the sequential emphasis on computing structures, this made In VLSI design it is becoming a much less some sense. relevant approach.

Schneck [SCHN79] outlines a new design approach in which the application, design, and implementation areas of algorithms, hardware, and software are very intertwined. In this approach the algorithm design activity for the application, not hardware design, drives the total effort. Hardware and software design activity areas will be at the same level in this hierarchy and will be nearly indistinguishable in some important ways. See Figures 1 and 2 for illustrations of the old and new design hierarchies.

In the control flow environment, computer scientists have unfortunately grown too accustomed to their niche in the old hierarchy. Feature laden, complex, von Neumann based "new" languages such as PL/1 and Ada are always appearing, while comparatively little has been done on the design of truly innovative languages which would fit other existing models more satisfactorily, or help to define new models. This design attitude will have to change, since the inputs of computer scientists will affect machine design much more directly in the VLSI era. Chapter 4 will return to this subject.

Figure 1

Control Flow Design Hierarchy

[SCHN79]

Figure 2

VLSI Design Hierarchy

[SCHN79]

-15-

#### CHAPTER 2

#### Abstract Computing Models

This chapter will examine two implicitly concurrent models: the data flow and functional models. Section 2.2 will examine some properties of the implicitly sequential control flow model, and some programming primitives necessary to realize concurrency in this model. Section 2.3 will then present a brief comparison of some key properties of highly concurrent and control flow models.

## 2.1 Highly Concurrent Computing Models

Section 2.1.1 will examine the data flow model, and Section 2.1.2 the functional model. Chapter 3 will discuss implementations for these abstract models.

## 2.1.1 The Data Flow Model

Dennis [DENN80] advocates language-based computer design, which ensures the programmability of a radical architecture. He describes a language-based design to be one in which the computer hardware serves as an interpreter for a specific base language. Programs written for the computer must be expressed in the base language.

Future supercomputers must support massive concurrency in order to achieve significant performance increases; therefore, a base language for such machines must necessarily allow simple, implicit expression of concurrency on a very large scale.

Dennis feels that conventional control flow languages have an intrinsic, fatal design flaw: they are based on a global state model of operation. In the next computer generation, at least for large scale scientific computation, he believes this flaw will force abandonment of control flow languages. At this time he recognizes only two alternatives: the functional (applicative) languages to be discussed in Section 2.1.2 and the data flow models.

Dennis' subsequent explanation of the data flow model is now reviewed. His discussion has a simplicity and precision which makes the topic easy to understand.

In data flow models machine-level programs present a new view of instruction execution which departs radically from the sequential one. An instruction is automatically ready for execution when all operands have arrived. Relative positions of instructions are irrelevant, and data flow computers do not have location counters. A direct consequence of data-activated instruction execution is that many instructions may be ready to execute at once. Therefore, highly concurrent operation is an integral part of the data flow concept.

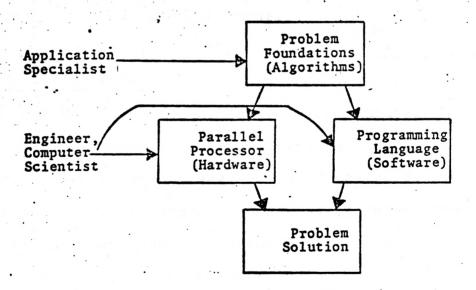

The base language for most data flow architectures is a representation called data flow program graphs. In most cases data flow computers are a form of language-based architecture in which these graphs are the base language. Thus, the language and the architectural concepts of data flow models are explicitly bound together

at design time, and architectural concepts do not force language representation as happened in control flow computing. Data flow program graphs-are a formally specified set of interfaces bridging system architecture and the user source programming language. Figure 3 illustrates the concept.

Figure 3

Language-Based Design Hierarchy for Data Flow Computers

[DENN80]

In the design environment implied by Figure 3, the computer architect and language implementor have sharply defined tasks:

- the architect must define a computing machine which implements the formal behavior of program graphs;

- the language implementor must devise translators for source language programs which translate source into equivalent data flow program graphs.

The cooperating nature of the design process is clear when the role of the program graphs in the scheme is understood.

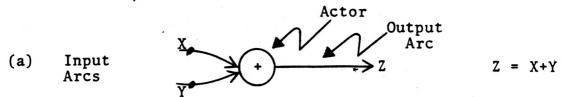

Data flow graphs are represented by collections of activity templates, which are information packets stored in memory. The role and structure of activity templates will become clear as the discussion proceeds. Basically, an activity template represents an action entity, such as an operator, which requires a finite number of operands in order to execute. The template records all operand fields and their readiness to be used in an operation. After execution, template fields are utilized to record and forward results to succeeding templates.

Data flow program graphs are composed of actors and arcs. Actors are connected by arcs and consist of both input and output arcs which carry data values in the form of tokens. Thus, arcs are communication paths between actors, and values travel upon these paths as tokens.

Figure 4 shows two actors connected by an arc upon which a token is being transmitted from actor 1 to actor 2.

Figure 4

Segment of a Data Flow Program Graph

Firing rules for tokens govern the placement onto and removal from input and output arcs of tokens and their associated values. For an actor to be enabled, a token must be present on each input arc, and no tokens can be present on any output arcs. An enabled actor may be fired. If the actor is an operator, firing entails applying the specified actor function to each input token value and placing the resultant tokens with computed values on the output arcs. Figure 5 illustrates the firing process.

Figure 5

Firing Rules

[DENN80]

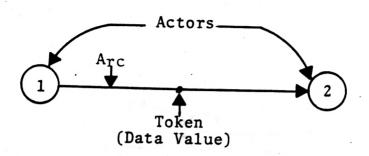

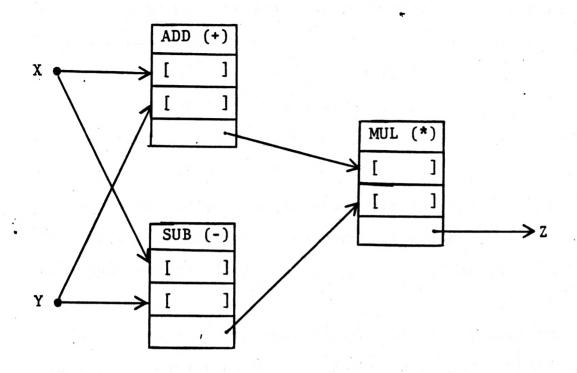

An arbitrary number of operators (or actors) may be connected to form program graphs. Figure 6 presents some examples of program graphs.

(a)

$$Z = (X+Y)*(X-Y)$$

[DENN 80]

## (b) Z = X\*Y - 4\*A\*(X+Y)

Figure 6

Examples of Program Graphs

There are many different types of actors: actors for each arithmetic operator, actors for copying data values to arbitrary numbers of output arcs, actors for merging data values, etc. The natures of these actors make conditional executions, iterations, and recursive computations fairly easy to implement. For a complete discussion of different types of actors, refer to [GUR680]. For the purposes of this report only simple switch and merge actors will be discussed.

Switch and merge actors control conditional executions and iterations. They do this by controlling the routing and selection of data values. An actor of one of these types operates by testing a boolean input value on one of its input arcs. The switch actor selects an output arc according to a true or false boolean control input value. The merge actor forwards one of two input data values according to an input (control) boolean. Figure 7 shows switch and merge actors and arcs.

Switch and Merge Actors

[DENN80]

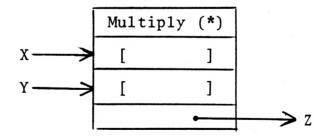

At the machine level, data flow programs are represented by activity templates. A program is a collection of these templates. Each activity template corresponds to one or more actors of a data flow program graph. An activity template consists of a collection of data value fields. For example a multiply template consists of four fields:

- an operation code (Multiply);

- two receiver fields to receive input operand values from previous operations;

- one destination field to store and forward the resultant product value to succeeding operations.

Figure 8 displays a multiply template. Figure 9 shows the corresponding composite structure of templates for one of the data flow program graphs in Figure 6.

Z = X\*Y

Figure 8

Multiply Activity Template

Figure 9

Composition of Operators using Activity Templates

[DENN80]

Activity templates control the execution of a machine program. Execution of a template is activated by the presence of an operand value in each receiver field. An operation packet of the form

<OPCODE,OPERANDS,DESTINATIONS>

is operated upon, and a result packet of the form <PVALUE, DESTINATION>

is passed on for each destination field. When the result packet is generated, each result value is placed into the receiver field designated by its destination field.

It is possible to analyze control flow programs and produce data flow machine object programs ([ALLA76], [JOHN80]). Indeed, conventional compilers with optimizing phases seem fairly easy to adapt in this way, since many of these compilers represent programs as directed graphs, and such representations are very close to the machine language of a data flow computer. A prototype computer of this kind has been successfully built, and the optimizing phase of a conventional compiler has been modified to generate code for it [JOHN80]. This approach holds much promise, since the underlying data flow model should be fairly transparent to the high level language programmer.

However, the semantics of data flow and control flow languages differ greatly [TREL79]. In data flow models

the order of assignment statements is irrelevant, and these are interchangeable since they are activated only by the availability of input data. To insure determinate operation, assignment statements must obey a single-assignment rule: an identifier can be assigned values at only one point in a program. This is necessary since an identifier is mapped to an arc, or data path, in data flow models and not to a memory location. History sensitivity is not a property of the model.

Side effects are not present in data flow languages. In the control flow model, mappings of multiple identifiers to the same storage location can cause unexpected results to occur. This happens ordinarily through subroutine parameter mappings and common storage shared by multiple modules. This phenomenon depends upon the property of history sensitivity, and thus it cannot occur in data flow languages. Because there is no necessity to coordinate common storage areas, side effects are absent from the data flow model and concurrency is highly enhanced. However, the price of eliminating history sensitivity from the model is not all positive; Chapter 4 will return to this subject.

One reason data flow is a popular research area is that textual data flow programming languages may be developed that share a few properties with control flow languages. For example, they can utilize assignment statements, arithmetic expressions, conditional statements, iteration, recursion, and function declaration [TREL79].

Representation in data flow languages is straightforward. Data identifiers are mapped to data paths and

operations to data flow instructions. The von Neumann

principle of program-data indistinguishability is lost,

since these mappings are not to memory locations. One

author reached the conclusion that this indistinguishability principle should be re-established in the data

flow model [SLEE80]. This would probably entail the

establishment of a history sensitivity property.

Since the data flow model supports concurrency at a low level, this model will support the optimal data flow language directly and allow individual operations to be initiated as soon as input data are avail-Studies of speed-up ratios show the best ones are linear in P, where P is the resource replication factor [STON73]. In a data flow model with large P (i.e., a very large number of processing units), the best way to achieve this speed-up is by supporting concurrency at as low a level as possible, since all higher level concurrency will then be automatically supported. Introduction of explicit statements, such as CALL and WAIT, to support concurrency will cause a negative effect on the linearity of P. When represented at a low enough level, there is the possibility of achieving a better increase in performance for a broad class of problems, since the system can then utilize the detailed representation of a program to maintain a very high overall resource utilization [TREL79].

Figure 10 illustrates a data flow representation of a quadratic roots program in a Pascal-like form [TREL79]. Recall that there is no relevance to the relative placements of the assignment statements in the QUAD-ROOTS function.

Due to time constraints, this report does not discuss many of the more advanced data flow concepts. Where appropriate, references are made to papers discussing recursion, acknowledge processing, and data flow multiprocessors. [DENN79] discusses another important concept: concurrent computation with streams. It is intended, here, only to discuss the basic concepts of the data flow model. The great potential for concurrent computation should be very clear.

Example Data Flow Program Representation

Figure 10

[TREL 79]

### 2.1.2 The Functional Model

Backus introduced a functional model of programming languages which is highly mathematical. He describes his functional structure in two different ways [BACK78]:

- informal discussion of functional programming,

or FP, systems;

- formal functional programming (FFP) systems.

The FFP systems can be studied in detail in [BACK78].

In general, this section concentrates on FP systems.

Backus recognizes two parts of a programming language:

- framework: defines the overall rules of the system;

- changeable parts: existence is provided for by language framework, but specific behavioral aspects are not specified.

An example of changeable parts portions of control flow languages is the CALL/RETURN procedure mechanism, which in many languages is used to invoke modules of arbitrary function. The language framework always describes its fixed features and provides the minimal features and environment for its changeable features.

Backus strives to define a minimal framework which could generate most other features as changeable parts. His exact quotation follows: "if a language had a small framework which could accommodate a great variety

of powerful features entirely as changeable parts, then such a framework could support many different features and styles without being changed itself."

According to Backus, von Neumann languages have large frameworks and limited changeable parts. Two properties of the von Neumann model seem to dictate this:

- word-at-a-time programming in which semantics are closely coupled to state, and every detail of computation changes the state;

- semantics closely coupled to state transitions implies every detail of every feature must be built into the state and its transition rules.

As an example of the rigidity of von Neumann languages, consider the primary techniques used for passing control to subroutines. The expression itself, "passing control," reveals the only real purpose of the techniques, which never evolved as expressive parts to alter the structure of a language to fit a problem. The purpose of such constructs are only to "modularize" large portions of program code. Typical CALL/RETURN mechanisms function as tying statements used only to glue sequentially-related but functionally independent portions of logic together. In themselves, they contribute little meaning to the language.

Functional techniques, such as the FORTRAN function defining and manipulating statements, are better in von Neumann computing than are their CALL/RETURN cousins. They can be utilized in a more expressive manner, since they can be embedded into complex arithmetic expressions. However, the nature of a function in the von Neumann model demands that a single-word result value always be computed and returned. This restriction keeps such techniques from having the power to expand von Neumann languages very significantly.

A CALL/RETURN scheme is often used to implement concurrency in von Neumann languages. Concurrency in these languages is not "fine grain" (i.e., concurrency is not consciously built into the von Neumann model at the lowest levels). Thus, some explicit technique is needed to implement a grosser kind of concurrency at the language level. It seems to follow that CALL/RETURN, the basic statements for "passing control," would often be extended to serve as concurrency controlling statements. Much problem continuity and clarity is lost by the usage of such constructs for concurrency, particularly since the original purpose of CALL/RETURN was for sequential passing of control, a technique which opposes a concurrent view.

In terms of problem clarity and understanding, CALL/RETURN mechanisms tend to detract from languages. Such compensating techniques as extensive English-language commentaries in the source code are necessary to maintain logical continuity of understanding. Very complex features must be added to these languages to strengthen them significantly and allow the language statements themselves to maintain logical clarity at the problem level. The resulting structure is very rigid and large.

Two of the basic problems with von Neumann languages seem to be:

- word-at-a-time programming;

- changeable parts have too little expressive power.

Backus' goal is to provide a language framework which can be expanded naturally, while simultaneously increasing the expressive power of the language. He approaches the problem at the point where new procedures must be created to solve a problem. A goal of his functional style is to allow this process of procedure creation to happen within this basic framework of the language while leaving the language problem oriented, and not construct oriented.

In order to provide powerful combining parts in a language, good combining forms must be available which can be used to fabricate new procedures from

old ones. The control flow model provides primitive combining forms and makes using them difficult.

Backus notes the split between what he refers to as the "expression world" and the "statement world" in the von Neumann model. "Functional forms naturally belong to the world of expressions; but no matter how powerful they are, they can only build expressions that produce a one-word result. It is in the statement world that these one-word results must be combined into the overall result."

As an example, consider the sequence of FORTRAN statements

A = SQRT(B\*B+C\*C+EPS(W-U))

D = X+Y\*Y+A\*\*3

Certainly, the expression to compute A does not lack elegance. It involves numerous arithmetic and functional applications; yet, its primary purpose is to produce a sequential result value to store in the location associated with A. This value can then be used in the following statement. No computation can be performed on the expression associated with D until the value for A is available, although the values for the subexpression X+Y\*Y are independent of A and available for use while A is being computed.

The constant combining operations of single words necessary in control flow languages is something which detracts from the power attainable if the split between

-34-

statements and expressions were not present. One goal of the functional model is to eliminate this arbitrary split.

Backus also aims to eliminate the usage of elaborate naming conventions in his functional model.

Naming conventions require complicated mechanisms in the language framework which interfere with the use of simple combining forms. For example, subroutines require dummy arguments which must be mapped to the storage locations corresponding to the arguments of the invoking procedure.

Finally, Backus wants to provide powerful mathematical properties in his functional language framework which aid program proof and construction tasks. Control flow languages generally lack these properties; hence, they are difficult to reason about and prove. In functional programs "... programs can be expressed in a language that has an associated algebra. (The) algebra can be used to transform programs and to solve equations whose 'unknowns' are programs, in much the same way one solves equations in high school algebra." In the FP style algebraic transformations and proofs can utilize the language of programs directly, rather than the (extra) language of logic (which only talks "about" programs).

Iverson demonstrated that there can be programs which are neither word-at-a-time nor dependent on lambda expressions. With APL Iverson introduced new functional forms. Since APL assignment statements can store entire

arrays at once, the functional forms are greatly extended beyond those of von Neumann languages.

However, Backus notes three problems with APL:

- the split into expressions and statements is still there, albeit on a larger scale for expressions;

- APL has only three functional forms (inner product, outer product, reduction) which are not sufficient and are difficult to use;

- APL semantics is still too closely coupled to machine states.

As the experience of APL suggests, matrix operators introduce more powerful functional forms, but they do not (in themselves) solve all the problems of von Neumann languages. For example, Backus feels the effort to write one-line programs in APL by using the powerful matrix combining forms is partially motivated by the desire to remain in the "more orderly world of expressions."

Backus' eventual goal with FP systems is to utilize them in the design of applicative state transition (AST) systems. AST systems have the following properties:

- history sensitivity;

- loosely-coupled state-transition semantics in which a state transition occurs only once in each major computation;

- simple states and state transitions;

dependence upon an underlying applicative system to provide the basic programming language and to describe state transitions.

An AST system is composed of three elements:

- 1) an applicative subsystem (i.e., an FFP system);

- 2) a state D that is the set of definitions of the applicative subsystem;

- 3) a set of transition rules that describe how inputs are transformed into outputs and how the state D is changed.

The programming language of an AST system is defined: it is that of the applicative subsystem (i.e., can be FFP system). The FP programming style described later can be used. The state D cannot change except at output time. The old state is replaced by the new state at output time. State transitions can have useful mathematical properties. Programming is not divided into expressions and statements.

Some other key advantages of AST systems are as follows:

- since the state cannot change during a major computation, side effects are eliminated, and independent applications can be evaluated concurrently;

- major new features are introduced by utilizing the common language framework;

- the framework is minimal and is the only fixed part of the system;

- the functional nature of names is exploited.

Backus feels that the new classes of history-sensitive models utilizing applicative styles and languages are key developments. If their superiority over conventional languages can be proven, the economic basis for developing new kinds of computers to best implement them will be established. The full power of large scale integration can then be better utilized in computer designs to produce more concurrent and efficient machines.

With this final goal for AST systems in mind, Backus outlines an approach for designing non-von Neumann languages:

- an (informal) functional style of programming

(FP) without variables based upon the usage of combining forms for constructing programs;

- an algebra of functional programs;

- a formal functional programming system (FFP) to serve as the basis for AST systems;

- AST systems.

Mago's [MAGO80] cellular architecture in Section 3.2 is based upon this approach, and the resultant FFP.

FP systems are members of a class of simple applicative programming systems in which the only operation is that of "application." Programs in this type of system are functions without variables. In the language framework, a fixed set of combining forms

called functional forms are defined. To these fixed functional forms are added some simple definitions: the combinations of fixed functional forms and definitions are the only building blocks available to construct new functions from existing ones. Variables and substitution rules are specifically excluded from the system. New functions become new operations in an associated algebra of programs.

The functions of an FP system map objects into objects and always require one single argument, or a tuple of arguments. These simple, highly-structured forms define the behavior of FP programs unambiguously and allow program proofs by algebraic methods.

An FP system is constructed of the following sets:

- a set 0 of objects;

- a set F of functions that map objects into objects;

- a (single) operation called "application";

- a set FF of functional forms used to form new functions in f;

- a set D of definitions that define some functions in F and assign a name to each.

Backus provides examples of these entities. Some examples from [BACK78] follow:

## - objects

1

$$\phi$$

7.8 CDX  $\langle X, 1, 4.7 \rangle$   $\langle xy, w, \langle x \rangle, h \rangle, wz \rangle$   $\perp$

# - applications

$$+:<1,2>=3$$

$$2: < A, B, C > = B$$

These are read "+ applied to the sequence <1,2> yields 3, and "the selector 2 applied to the sequence <A,B,C> yields B."

# - primitive functions

These functions are supplied with the basic FP system.

## - selector functions

1:x = x =

$$\langle x_1, ..., x_n \rangle \rightarrow x_1; \perp$$

This is read "the selector function 1 applied to x is defined as the first element in the sequence  $(x_1)$  when  $x = \langle x_1, \ldots, x_n \rangle$  and is undefined otherwise."

## - identity

$id:x \equiv x$

### - reverse

reverse:

$$x = x = \phi \rightarrow \phi$$

;

$$x = \langle x_1, ..., x_n \rangle \rightarrow \langle x_n, ..., x_1 \rangle; \perp$$

## - functional forms

These are basic forms which are used to produce other functions by combination.

# - composition

$$(f \cdot g) : x = f : (g : x)$$

f and g are preexisting forms.

# - apply to all

$$\alpha f: x = x = \phi \rightarrow \phi;$$

$$x=\langle x_1,x_2,\ldots,x_n \rangle$$

$$\rightarrow \langle f:x_1, f:x_2, \dots, f:x_n \rangle$$

;  $\perp$

### - definitions

A definition in an FP system is an expression of the form

## $\underline{\text{def}} \ell \equiv r$

where  $\ell$  is an unused function symbol and r is a functional form.

-  $\underline{\text{def}}$  IP=(/+)·( $\alpha$ x)·transp

This is Backus' definition of inner product, IP, using the following functions: insert (/), apply to all  $(\alpha)$ , and transpose (transp).

An object x (in 0) is either an atom, a sequence  ${}^{<x_1,x_2,\dots,x_n>}$ , where  $x_i$  is an object, or  $\bot$  ("bottom" or "undefined"). The set A of atoms determines the set 0 of objects. The empty sequence is denoted by  $\phi$  and is the only object which is both an atom and a sequence. The atoms T and F denote the familiar boolean values "true" and "false". An important constraint in the construction of objects is associated with  $\bot$ : if x is a sequence with  $\bot$  as an element, then  $x=\bot$ . That is, the "sequence constructor" is " $\bot$ -preserving." A proper sequence never has  $\bot$  as an element.

An FP system is not burdened with a large number of operations; it has exactly one: application. If f (in F) is a function and x (in O) is an object, then

f:x

is an application which denotes the object resulting from applying f to x. f is called the operator of the application and x is the operand. Functions f (in F) are bottom-preserving:

$f: \perp = \perp$  (all f in F).

Every function in F is either primitive (i.e., supplied), defined, or a functional form.

f: x = 1 has some properties which are important in talking about the mapping:

- if the computation for f:x terminates and yields the object \(\perceq\), f is said to be undefined at x.

f terminates but has no meaningful value at x.

- when f does not terminate, it is said to be nonterminating at x.

A functional form (FF) is an expression denoting a basic function which is supplied with the model. The function depends on the functions or objects which are the parameters of the expression. As an example, for f and g in F, f·g is a functional form called the composition of f and g. The composition denotes the function such that, for arbitrary x in O,

$$(f \cdot g) : x = f : (g : x)$$

.

Table 1 lists some FP functional forms [BACK78].

A definition in an FP system is an expression of the form

$$\underline{\text{def}} \ \ell \equiv r$$

Where the left side  $\ell$  is an unused function symbol and the right side r is a functional form which may depend on  $\ell$ . It means that symbol  $\ell$  is to denote the function represented by r. A defined symbol is applied by replacing it by the right side of its definition. A definition may

Functional Form

## Notation

| (FF)         | uch a lingerch, company constitution                                             |

|--------------|----------------------------------------------------------------------------------|

| Composition  | $(f \cdot g) : x \equiv f : (g : x)$                                             |

| Construction | $[f_1,,f_n]:x = \langle f_1:x,,f_n:x \rangle$                                    |

| Condition    | $(p\rightarrow f;g):x \equiv (p:x)=T\rightarrow f:x$                             |

|              | $(p:x)=F\rightarrow g:x; \perp$                                                  |

| Constant     | $\overline{x}:y \equiv y = \bot + \bot; x(x \text{ an object parameter})$        |

| Insert       | $/f: x = x = \langle x_1 \rangle \rightarrow x_1; x = \langle x_1,, x_n \rangle$ |

|              | (n≥2)                                                                            |

|              | $f:>;$                                                                           |

| Apply to All | $\alpha f: X \equiv X = \phi \rightarrow \phi;$                                  |

|              | $x = \langle x_1, x_2, \dots, x_n \rangle \rightarrow$                           |

|              | $\{f: x_1, \ldots, f: x_n\}; \perp$                                              |

Table 1

Some FP Functional Forms

[BACK78]

be a non-terminating function. The set D of definitions is well formed if all left sides are unique symbols. For examples of definitions, see Table 1 on page 43.

Backus presents an example of a functional program for inner product [BACK78]. This example will now be discussed.

The definition of the functional program for inner product is:

In more symbolic form:

DEF IP =

$$(/+) \cdot (\alpha^*) \cdot \text{Trans}$$

.

The set FF of functional forms is determined by:

- combinations of existing (primitive) functions to form new ones;

- Composition ".";

- Insert "/";

- Apply to All " $\alpha$ ".

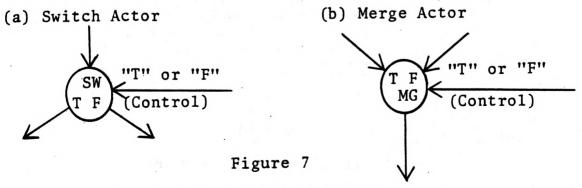

Figure 11 shows IP and the steps involved as it is applied to the vector pair (<1,2,3>,<6,5,4>).

The semantics of an FP system are determined by the choice of four sets and the manner of computing functions from them. The FP system itself is determined by the four sets:

- the set of atoms A, which determine the set of objects;

- the set of primitive functions P;

- the set of functional forms FF;

- a well formed set of definitions D.

There are only four possibilities for computing f:x:

- f is a primitive function, and is computed from its description;

- f is a complex function produced using functional forms, and the description of the forms define how f is to be computed in terms of parameters and rules;

- f is defined in the set D;

- none of the above, or  $f:x \equiv \bot$

If f does not terminate for a given rule, then  $f:x \equiv \bot$ . The definition of expansion and the Expansion Theorem stated in Appendix B will prove whether f terminates. If it does not, f will be undefined and will not produce a predictable value when applied to x.

FP systems can be viewed as programming languages, but they are very minimal in terms of conventional languages. When so viewed, f is a program, object x is the initial contents of the store, and f:x is the final contents of the store. The set D of definitions is the program library. The primitive functions and functional forms provided in the language framework are the basic statements of a specific programming language. Depending upon the choice of primitive functions and functional forms, the FP-language framework provides for a large class of languages with varying styles and capabilities. The algebra of programs associated with each is dependent upon

its particular set of functional forms.

Backus states the limitations of FP systems as follows:

- a given FP system is a fixed language;

- FP systems are not history sensitive;

- input and output can be treated only in the sense that x is an input and f:x is an output;

- if the sets of primitive functions and functional forms are weak, all computable functions may not be expressible.

As an example of a major weakness of FP systems, an FP system cannot be used to compute a new program, since functions are kept distinctly separate from objects. The process of computing new functions would require the "apply" operator such that

apply:

$$\langle x, y \rangle \equiv x:y$$

where x is an object on the left and a function on the right. A second major weakness with FP systems is that new functional forms cannot be defined within the system.

Lack of history sensitivity is the primary limitation. FP systems must be extended before they become practically useful; FFP and AST systems do this.

The advantages of FP systems are as follows:

- they use names only to name functions in definitions, and names can only be treated as functions that can be combined with other functions;

- they are based on reduction semantics which eliminate the need for word-at-a-time constructs which are too closely tied to machine states;

-46-

- they offer a core of primitive constructs from which higher level constructs and techniques can be naturally developed.

FFP systems are developed from the consideration of FP systems. Backus defines the primary goal of FFP systems as follows: "FFP systems develop a foundation for the algebra of programs that disposes of the theoretical issues, so that a program can use simple algebraic laws and one or two theorems from the foundations to solve problems and create proofs in the same mechanical style used to solve high school algebra problems." See Appendix B for a discussion of the algebra of programs and proofs and an example of a correctness proof.

In FP systems the set FF of functional forms is fixed.

In FFP systems this restriction is lifted and new functional forms can be created. In FFP systems objects are used to represent functions; otherwise, FFP systems are very much like FP systems. In FFP systems

Apply:

$$\langle x, y \rangle = (x:y)$$

is a legal construct, but not in FP systems.

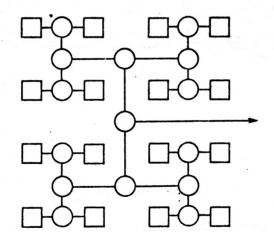

To end this section, we will review the definition of applicative state transition systems (AST) and use Table 1 and Figure 11 to step through the definition of a new function called "inner product", or "IP". The discussion will reveal the natural extensibility of such systems.

Definition: An AST system is composed of three

elements:

- 1) an applicative subsystem, such as Backus'

FFP system;

- 2) a state D that is the set of definitions of the applicative subsystem;

- 3) a set of transition rules that describe how inputs are transformed into outputs and how the state D is changed.

"Applicative" implies the application of definitions and functions (supplied and derived) to arguments to produce results. For example, some definitions in FFP are related to the basic functions, "+" and "\*". The results of applying these functions are defined by the language framework as follows:

$$+: \to x + y$$

\*:  $\to x*y$ .

Table 1 defines some functional forms that are supplied in the basic language framework: Composition, Construction, Apply to All, etc. These basic definitions and supplied functional forms can be combined within the basic language framework to define more complex functions, which can be used with the basic definitions and functional forms to define still more complex functions, ad infinitum. The line-by-line detail

of the transition rules and states obtained by successive applications of the definitions and supplied functional forms in FFP to define a more complex function, IP, is now given. Figure 11 summarizes the discussion.

#### - DEF IP

The new function (defined function) IP is defined in terms of supplied forms and definitions:

$$\underline{\text{DEF}}$$

IP  $\equiv$  (/+)  $\cdot$  ( $\alpha$ \*)  $\cdot$  TRANS.

This being an applicative subsystem, it is meant that the new function IP can be applied to a sequence of vectors in the system:

$$IP: \langle x_1, x_2 \rangle$$

where

$$x_1 = \langle x_{11}, x_{12}, \dots, x_{1n} \rangle$$

$x_2 = \langle x_{21}, x_{22}, \dots, x_{2n} \rangle$

$x_{mn} \in R \quad (m=[1,2]).$

For the sake of example, suppose IP is to be applied to the vector pair <<1,2,3>,<6,5,4>>. The application implied by the definition is then

$$(/+) \cdot (\alpha^*) \cdot TRANS : <<1,2,3>,<6,5,4>>.$$

This is the initial state of the application.

### - Composition (·)

By the rule of Composition from Table 1, the last result is equivalent to

$$(/+) \cdot (\alpha^*) : (TRANS: <<1,2,3>,<6,5,4>>)$$

or

$$(/+):((\alpha^*):(TRANS:<<1,2,3>,<6,5,4>>))$$

### - Transpose (TRANS)

TRANS is not defined in Table 1. In FFP, it is defined for two sequences as follows:

TRANS:

$$<< a_1, a_2, ..., a_n > , < b_1, b_2, ..., b_n > > \equiv$$

$<< a_1, b_1 > , < a_2, b_2 > , ..., < a_n, b_n > > .$

Hence

TRANS:

$$<<1,2,3>,<6,5,4>> \rightarrow$$

$<<1,6>,<2,5>,<3,4>>$ .

Substituting the expression resulting from the application of TRANS to the vector pair back into the original string derived by applying Composition, above, we get

$$(/+):((\alpha*):(TRANS:<<1,2,3>,<6,5,4>>))$$

$$\rightarrow$$

(/+):(( $\alpha$ \*):<<1,6>,<2,5>,<3,4>>).

This latter expression defines the next state of the system, following the application of TRANS.

# - Apply to All $(\alpha)$

Referring to Table 1,

is equivalent to

where "\*" is applied to all members of the outer sequence. Using this result, we obtain the next state of the system as follows:

### - Apply (\*)

In an AST system, innermost applications are always performed first. In the last expression, three innermost applications are present:

"\*" is applied to these as follows:

\*:

$$<1,6> \rightarrow 1*6 = 6,$$

\*: $<2,5> \rightarrow 2*5 = 10,$

\*: $<3,4> \rightarrow 3*4 = 12.$

Substituting, we obtain the next state of the system:

# - Insert (/)

Here, apply the functional form from Table 1 to obtain the next system state:

$$(/+):<6,10,12> + :<6,+:<10,12>>.$$

# - <u>Apply (+)</u>

Applying the innermost application first:

$$+:<10,12> \rightarrow 10+12 = 22.$$

The state transition is given by  $+:<6,+:<10,12>> \rightarrow +:<6,22>.$

### - Apply (+)

The final application yields the final system state and the final result:

$$+:<6,22> \rightarrow 6+22 = 28.$$

Some small liberties were taken with this example, as a comparison of the state transition for the "Insert" step will show. But basically, all state transitions to the final result are shown. Notice how the set of basic definitions and supplied functional forms are combined to define more complex functions. Each defined function in the system can then be applied to arguments without using any naming conventions, except for names attached to functions. Once IP is defined as outlined, we can write

$$IP: \langle \langle 1, 2, 3 \rangle, \langle 6, 5, 4 \rangle \rangle \rightarrow 28$$

and utilize IP to define progressively higher functions, all within the language context. The language is thus naturally extended, accordingly.

Many details of FP, FFP, and AST systems are omitted, or discussed only briefly in this section.

Refer to [BACK78] for full details.

```

\rightarrow (/+) · (\alpha*) · Trans: <<1,2,3>,<6,5,4>>

DEF IP

\rightarrow (/+):((\alpha*):(Trans:<<1,2,3>,<6,5,4>>)

Composition (\cdot)

\rightarrow (/+):((\alpha*):<<1,6>,<2,5>,<3,4>>)

Transpose

+ (/+):<*:<1,6>,*:<2,5>,*:<3,4>>

Apply to All (\alpha)

+ (/+):<6,10,12>

Apply (*)

+ : <6,+: <10,12>>

Insert (/)

+ : <6,22>

Apply (+)

Apply (+)

→ 28

```

Figure 11

Inner Product Functional Program Application

[BACK78]

### 2.2 The von Neumann (Control Flow) Model

This section examines the model reflected by conventional computers and programming languages, the von Neumann, or as Treleaven calls it, the control flow model [TREL79]. A model can be studied by comparing its properties with those of other models, by examining its properties in detail, and by examining its structures. This section studies the control flow model from all three of these perspectives.

Backus studies the control flow model by comparing it to others [BACK78]. He presents a theoretician's classification of computing models. The data flow model discussed in Section 2.1.1 does not fit well into this scheme, which was presented in Backus' 1977 ACM turing award lecture. However, the classification highlights some relevant properties of control flow machines. It also provides a good comparison of control flow and applicative models.

Backus presents a list of criteria to classify computing models:

- 1) foundations is there a useful mathematical description of the model?

- 2) history sensitivity can information be passed from one program to a successor at runtime?

- 3) semantics does a program in the model use state transition semantics or reduction

semantics? If state transitions are used, are these simple or complex?

4) program clarity - are source representations clear and conceptually useful in that they embody concepts that can be used to reason about processes?

Using these criteria, he defines three classes of computing system models:

- 1) simple operational models;

- 2) applicative models;

- 3) control flow models.

Table 2 summarizes these classifications in chart form with an example of each.

It is difficult to fit data flow languages into Backus' scheme (the data flow line listed in Table 2 was not in Backus' original table). They seem to partially fit the class of operational models, but with much clearer programs than other members of the class. Backus believes that some data flow languages could even be considered to possess the beginnings of reduction semantics [BACK78]. Certainly, data flow languages are not ordinarily history sensitive.

The general properties of the control flow model as charted in Table 2 summarize Backus' view of this model. As these properties are studied, one should not forget that Backus has been one of the innovators of the young science of electronic computation and,

# BACKUS MODEL CLASSIFICATIONS

|      | Class                         | Example                                                   | Foundations                    | History<br>Sensitivity | Semantics                              | <u>Clarity</u>                        |

|------|-------------------------------|-----------------------------------------------------------|--------------------------------|------------------------|----------------------------------------|---------------------------------------|

|      | Operational                   | Turing Machines                                           | Concise<br>Useful              | Sensitive              | State Transitions<br>Simple States     | Unclear<br>Not Conceptually<br>Useful |

|      | Applicative                   | Functional<br>Programming                                 | Concise<br>Useful              | Not Sensitive          | Reduction Semantics<br>(No States)     | Clear<br>Conceptually<br>Useful       |

| -56- | Control Flow<br>(von Neumann) | Conventional<br>Computers and<br>Programming<br>Languages | Complex<br>Bulky<br>Not Useful | Sensitive              | State Transitions<br>Complex States    | Clear<br>Not Conceptually<br>Useful   |

|      | Data Flow                     | Figure 10                                                 | Concise<br>Useful              | Not Sensitive          | (Beginnings of)<br>Reduction Semantics | Clear                                 |

Table 2

A Chart Illustrating Backus' Classification Scheme

[BACK78]

due to his role as an original developer of the FORTRAN programming language, one of those most responsible for the current primary position of the control flow model in practice.

The foundations of the control flow model are judged to be complex, bulky, and not useful. Backus notes the lack of a satisfactory mathematical description of the model. He feels it to be so complex and bulky that its description has scant mathematical value.

Programs in the control flow model are history sensitive. That is, one program can pass information to another that can affect the behavior of the latter. This may well be at once a primary strong point and yet a concurrency-limiting property of the model.

Z = X\*Y-4\*A\*(X+Y)

Move B to A

Figure 12

Typical Control Flow Assignment Statements

The semantics of control flow programs involve complex machine state transitions. Observe the typical control flow assignment statement involving a moderately complex arithmetic expression as shown in Figure 12. Some idea of state-transition complexity can be gained by "mentally-executing" this statement. If this is done, a rapid series of memory fetches of literal values and values associated with named variables are "seen" passing from memory to the arithmetic logic unit for arithmetic combination as the arithmetic expression is evaluated. When this sequence of operations is complete, the final computed value passes from the ALU to memory (i.e., it is "stored" in a location associated with the named variable "Z").

Each passage of a value between memory and the ALU defines a state transition, and each combination of sets of values in ALU and memory cells defines a state of the control flow machine. Even the simplest assignment, such as the simple COBOL "MOVE" of Figure 12, involves multiple state transitions.

Consider state transitions in the functional model discussed in section 2.1.2 in contrast to this situation. State transition rules in the functional model are entirely defined within the model and depend only upon the manner in which inputs are transformed into outputs and the subsequent change in the state D representing the set of definitions of the underlying

FFP system. Thus, a state transition in this system is not related to any complex rules involving machine operations on any physical entity such as global memory.

Finally, the control flow program clarity property is deemed "clear but not conceptually useful" by Table 2. Generally, programs of the model do provide clear expressions of a process or computation, but they do not provide concepts that help people to reason easily about processes. One need only reflect on the excessive requirements of the simplest program proof to understand that some inherent properties of control flow programs seem to make formal reasoning about them very difficult. Reasons for this will become clear as we consider the structures and properties in greater detail.

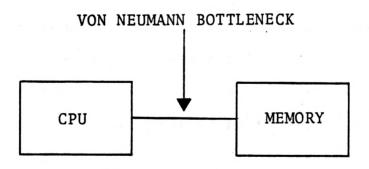

Figure 13

Basic Structure of a Control Flow Computer

[BACK78]

In the ensuing discussion, it can be argued that we are discussing implementation and not model, since we must speak of the control flow model in terms of registers, global memory accesses, etc. Indeed, this seems to be a failing of our current views of von Neumann computing, where many aspects of model and implementation have become almost interchangeable. Nevertheless, program counters, hidden registers and register transfers involving state transitions, CPU-to-memory paths, variable naming conventions equated with memory mappings, etc., are all at this point in history intimately associated with the von Neumann "model."

Backus does not consider one obvious alternative to replacing the von Neumann model with another that has a better theoretical structure: the alternative of separating the von Neumann model itself from its many historical implementations and strengthening its theoretical structure. His purpose does not seem to fit that particular approach. Without pretending to assume anything about what he thinks about this matter, it is possible he believes the alternative to be not particularly viable.

Perhaps the alternative approach could be the subject of other reports. In this report we must consider the concept of the "von Neumann model" as it now exists in theory and practice. Certainly, a definite strength of

this view is the history sensitivity property, which makes commercial and business computing pragmatic. One contrast between the von Neumann model and later models does seem to arise simply because the conceptual environment in which they have arisen and evolved is much different than that which spawned von Neumann computing.

Conceptually, a von Neumann, or control flow computer is composed of the three parts illustrated in Figure 13:

- central processing unit (CPU);

- 2) memory store;

- 3) connecting tube.

The connecting tube can transmit a single computer word between the CPU and the memory, or vice versa. One memory cell, for example, can only be moved to another by traversing the tube from the memory to the CPU and back again. The CPU contains central storage cells, called "registers":

- central registers available to the programmer;

- central registers "hidden" from the programmer;

- special register(s) called the "memory address

- register(s)" (MAR);

- special register called the "program counter" (PC).

Only one value at a time can flow on the connecting tube. A machine state transition is initiated by placing a word on the tube for transmission to or from the store. A machine state is represented by each successive set of values of cells in memory and in the CPU registers during operation.

[BACK78] outlines the task of a program in the control flow environment: It must change the contents of memory in some major way. This task can only be done by shipping one word at a time through the connecting tube, or von Neumann bottleneck. Variable names are always associated with memory locations, and much of the activity on this avenue is in addition to the main task the program is designed to accomplish and is related to manipulating and computing names, etc. PC and MAR registers, for example, simply provide data names for instructions themselves and their operands, respectively, during operation. Each instruction must be fetched (by name) from memory to the CPU (across the bottleneck) to begin its execution cycle. Each of its operand names must then be fetched into the CPU using the same mechanism. "Programming" a control flow machine consists primarily of managing the enormous flow of words across the connecting tube, and much of that flow concerns not only data relevant to the problem, but also data names in the form of memory addresses.

Backus believes the connecting tube to be both a literal and an intellectual bottleneck:

- literal bottleneck for problem traffic;

- intellectual bottleneck that has kept computer engineers and scientists tied to word-at-a-time thinking.

The intellectual bottleneck has blocked designers from thinking in terms of the larger, conceptual units of the problem to be solved.

All control flow computers of this sort possess the CPU register called the "PC", above. Machines based on this model tend to be very serialized, step-at-a-time mechanisms admitting no real concepts of concurrent operation. This property of control flow machines will become more obvious when the control flow language structures are discussed in the next section.

# 2.2.1 The Structure of Conventional Programming Languages

The control flow model existed first in hardware and was programmed in machine language. Conventional symbolic assembly languages evolved as aids to the machine programmer, and high-level languages were developed solely for the same reason at a point in time following the development of assembly language concepts. In the case of the control flow model, the hardware development drove the language interface, as symbolic languages were viewed strictly as man-machine communication aids.