Nieuwe FPGA-ontwerptools en -architecturen

New FPGA Design Tools and Architectures

Elias Vansteenkiste

Promotor: prof. dr. ir. D. Stroobandt Proefschrift ingediend tot het behalen van de graad van Doctor in de ingenieurswetenschappen: elektrotechniek

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. R. Van de Walle Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2016 - 2017

ISBN 978-90-8578-960-4 NUR 959 Wettelijk depot: D/2016/10.500/92

## **Examination Commission**

prof. dr. ir. Gert De Cooman

Department of Electronics and Information Systems - ELIS

Faculty of Engineering and Architecture

**Ghent University**

prof. dr. ir. Joni Dambre, secretary

Department of Electronics and Information Systems - ELIS

Faculty of Engineering and Architecture

Ghent University

prof. dr. ir. Steve Wilton

SoC Research Group

Department of Electrical and Computer Engineering

The University of British Columbia

prof. dr. ir. Nele Mentens

Department of Electrical Engineering - ESAT

Faculty of Engineering Technology

KU Leuven

prof. dr. ir. Pieter Simoens

Department of Information Technology - INTEC

Faculty of Engineering and Architecture

**Ghent University**

prof. dr. ir. Guy Torfs

Department of Information Technology - INTEC

Faculty of Engineering and Architecture

Ghent University

em. prof. dr. ir. Erik D'Hollander

Department of Electronics and Information Systems - ELIS

Faculty of Engineering and Architecture

**Ghent University**

prof. dr. ir. Dirk Stroobandt, advisor

Department of Electronics and Information Systems - ELIS

Faculty of Engineering and Architecture

**Ghent University**

### Dankwoord

Eerst en vooral wil ik Karel Bruneel bedanken voor het overdragen van zijn enthousiasme waarmee hij over zijn - op het eerste gezicht - exotische technieken vertelde. Hij heeft me warm gemaakt voor een thesis rond dynamische herconfiguratie van FPGAs en later ook voor een doctoraat. Tijdens mijn doctoraat spendeerde hij soms meer tijd in mijn kantoor dan in het zijne. Karel Bruneel, samen met Tom en Brahim, leerden Karel Heyse en mij de kneepjes van het vak kennen. Ik apprecieer ook de beschikbaarheid van Karel Heyse als collega-student. Hij was altijd bereid om klankbord te spelen. Ik wil ook Dries bedanken voor de goeie samenwerking en de steun op het einde van mijn doctoraat. Hij was er al bij als masterstudent toen hij een project deed aan onze onderzoeksgroep, daarna als thesisstudent en nu ook als doctoraatsstudent. Karel Heyse en Dries hebben ook geholpen bij het nalezen van deze thesis. Graag wil ook de rest van het Hardware and Embedded System team bedanken voor de discussies en samenwerking. Ik apprecieer ook enorm de vrijheid die mijn promoter Dirk mij gegeven heeft tijdens mijn doctoraat. Ook ben ik erg dankbaar voor de tijd en moeite die de leden van de examencomissie besteed hebben in het nalezen van een eerdere versie van mijn boek. Het heeft de kwaliteit van deze thesis verhoogd.

I am especially grateful towards professor Steve Wilton for making the trip from Vancouver to Ghent to be in my examination board.

De mensen uit het reslab wil ik ook bedanken, waaronder Aaron, Sander, Francis, Pieter, Tim, Jonas, Lio, Jeroen, Ira, Tom, ... Ik keek altijd uit naar de avonden die we gevuld hebben met spelletjes, van Age of Empires II tot Game of Thrones. Daarnaast waren er ook de geanimeerde discussies tijdens de lunch. Het begon altijd met de jacht op goed eten in centrum Gent, waar de nodige onderhandelingen op zijn plaats waren. In het bijzonder bedank ik Aaron. Hij is een goede vriend en was een compagnon de route sinds de beginjaren van onze studies aan de Universiteit. We vertrokken samen op uitwisseling naar Taiwan, begonnen na onze studies een doctoraatsstudie en liepen bijna gelijktijdig een stage in Silicon Valley.

My gratitude also goes to Alireza Kaviani for the chance he gave me to do

an internship at Xilinx' CTO Lab in San José. I learned a lot about FPGAs during my stay. I also want to thank my two other colleagues at Xilinx. Henri Fraissé and Pongstorn Maidee accepted me in their team and helped me guide through Vivado's source code, which is a complex maze.

Zo wil ik ook Karel Bruneel bedanken omdat hij mij onderdak heeft verschaft in San Francisco.

Voor de rest wil ik ook mijn trouwe vrienden bedanken, waaronder Stijn, Elke, Benjamin, Sofie, Dries, ... De vrienden van de zwemclub en de waterpolo, Brecht, Jorley, Willem, Dirk, Jens, Fien, Tim zorgden altijd voor geanimeerde gesprekken na training.

Een speciaal plaatsje wil ik hier reserveren voor mijn vriendin Kaat. Zij is mijn nummer 1. Alhoewel ze de afgelopen maanden af en toe heeft moeten plaats maken voor mijn nummer 2, mijn macbook, hoop ik dat ze me dat niet al te kwalijk zal nemen. Ze was altijd bereid in de bres te springen als ik een deadline had. Ik neem er ook graag de luidruchtige schoonzussen, Sara, Liesbet en Hanne bij en de rest van de gezellige schoonfamilie.

Last but not least, dank aan mijn ouders voor alle kansen die ik gekregen heb, en hun onvoorwaardelijke steun. Ze staan samen met mijn zus en broer altijd voor mij klaar, hoe hectisch het soms ook is.

> Elias Vansteenkiste December 19, 2016

## Samenvatting

Field-Programmable Gate Arrays (FPGA's) zijn programmeerbare, digitale chips die ingezet kunnen worden voor verschillende doeleinden. Ze worden gebruikt voor toepassingen waarbij hogere prestaties vereist zijn dan de prestaties die door de goedkopere microprocessors geleverd kunnen worden. Typische vereisten zijn een hoge doorvoer, korte wachttijden en een laag stroomverbruik. Een voorbeeld van een toepassing die vaak wordt uitgevoerd met een FPGA is het routeren en filteren van pakketjes in de internet-infrastructuur. In de internet-infrastructuur moeten de pakketjes verwerkt worden aan hoge doorvoersnelheden en met een minimale vertraging. Om dit te kunnen realiseren bestaan FPGA's uit een groot aantal blokken die georganiseerd zijn in een rooster. Sommige blokken zijn flexibel, anderen zijn gespecialiseerd in het uitvoeren van een specifieke functie. Al deze blokken kunnen verbonden worden om een grotere functionaliteit uit te voeren.

De ontwerper beschrijft de versneller op een hoog niveau. Een FPGA-configuratie wordt dan gecompileerd door gespecialiseerde software. Zodra de configuratie gecompileerd is, kan de ontwerper controleren of de configuratie aan de applicatie-eisen voldoet. Als de configuratie aan de vereisten voldoet, dan is het ontwerp klaar. In het geval dat de vereisten niet voldaan zijn, moet de ontwerper zijn beschrijving veranderen zodat de eigenschappen van het ontwerp verbeteren. Daarna moet de FPGA-configuratie andermaal gecompileerd worden en moet de ontwerper opnieuw controleren als aan de eisen van de applicatie voldaan is. Dit langzame proces heet de FPGAontwerpcyclus en wordt typisch vele keren doorlopen. Een belangrijk knelpunt in de ontwerpcyclus is de uitvoeringstijd van de FPGAcompilatie. FPGA-ontwerpen zijn steeds groter (of complexer) geworden volgens de wet van Moore. Grotere ontwerpen hebben meerdere uren nodig om gecompileerd te worden. Een belangrijk doel van het werk in dit proefschrift is het verkorten van de ontwerpcyclus door de FPGA-compilatie te versnellen.

FPGA-compilatie is opgedeeld in verschillende deelproblemen: synthese, packing, plaatsing en routering. Elk deelprobleem wordt behandeld door een ander ontwerptool. De ontwerpbeschrijving wordt

eerst gesynthetiseerd en afgebeeld op de primitieve blokken die beschikbaar zijn op de FPGA. Het resultaat is een netwerk van primitieve blokken. Tijdens packing worden de primitieve blokken geclusterd, waardoor we een netwerk van complexe blokken verkrijgen. De complexe blokken in het netwerk worden toegewezen aan een fysieke locatie op de FPGA tijdens plaatsing terwijl de schakeling op de FPGA geoptimaliseerd wordt voor de toepassingsvereisten. Na plaatsing worden de connecties tussen de blokken gerouteerd.

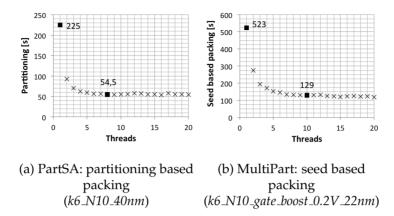

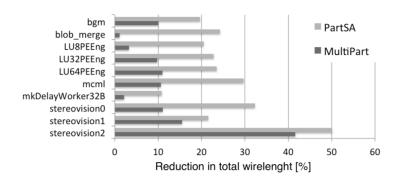

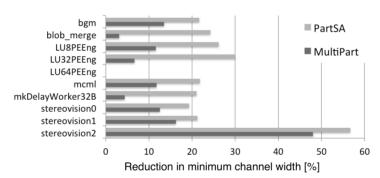

Plaatsing en routering zijn de meest tijdrovende stappen van de FPGA-compilatiecyclus. De uitvoeringstijd van de packing stap is minder kritisch, maar het beïnvloedt de uitvoeringstijd en de kwaliteit van de plaatsing en routering, daarom hebben we ons gefocust op het versnellen en verbeteren van de packing, plaatsing en routering. De traditionele algoritmes ontwikkeld voor deze problemen zijn niet geschikt voor processors met meerdere kernen, die in het afgelopen decennium de norm geworden zijn in computersystemen. We introduceren nieuwe packing- en plaatsingtechnieken die ontwikkeld zijn voor het uitvoeren op processors met meerdere kernen.

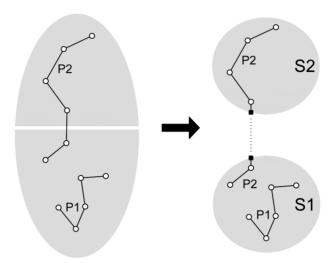

De Packing stap is geïntroduceerd voor het compileren van ontwerpen die geïmplementeerd moeten worden op moderne FPGAs met een hiërarchische architectuur. Er zijn twee populaire technieken voor packing: kiem-gebaseerd en partitionering-gebaseerd. Een kiem-gebaseerd algoritme clustert het ontwerp in één keer en kan daardoor gemakkelijker verzeild geraken in een lokaal minimum. Het is ook moeilijk om te implementeren zodat het gebruik kan maken van meerdere processorkernen. Een kiem-gebaseerd algoritme is wel goed in het opleggen van architectuurbeperkingen. Partitioneringgebaseerde algoritmes produceren een hogere kwaliteit omdat ze de natuurlijke hiërarchie van het ontwerp behouden. Het is ook gemakkelijker een meerdradige implementatie te maken van een partitioneringgebaseerde algoritme. In tegenstelling tot de kiem-gebaseerde algoritmes is het echter wel moeilijk om de architectuurbeperkingen op te leggen. We combineerden deze twee benaderingen om het beste van beide werelden te krijgen.

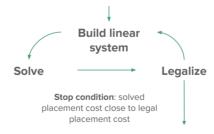

Bij plaatsing van de blokken in het ontwerp wordt voor ieder blok een fysieke bloklocatie op de FPGA toegewezen. Conventionele analytische methodes plaatsen een ontwerp door het minimaliseren van een kostfunctie die een schatting van de post-routeringprestatie voorstelt. Helaas is het niet mogelijk om alle architectuurbeperkingen door een analytisch oplosbare kostfunctie te beschrijven, daarom wordt het probleem opgelost in meerdere iteraties. In elke iteratie wordt een kostfunctie aangepast aan het resultaat van de vorige iteraties en de archi-

tectuurbeperkingen. Daarna wordt de functie opnieuw geminimaliseerd. De minimalisering omvat een tijdrovend proces: het oplossen van een lineair systeem. Experimenten tonen aan dat het niet nodig is om een hoge nauwkeurigheid te hebben voor de tussentijdse resultaten. In onze nieuwe plaatsingstechniek volgen we de snelst afdalende gradient. Dit is sneller dan het oplossen van een lineair systeem. Het maakt het ook mogelijk om blokniveauparallellisme toe te passen.

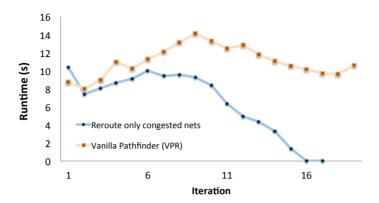

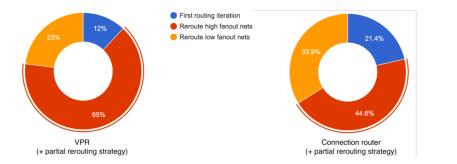

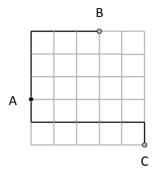

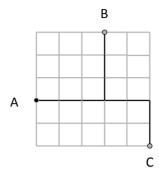

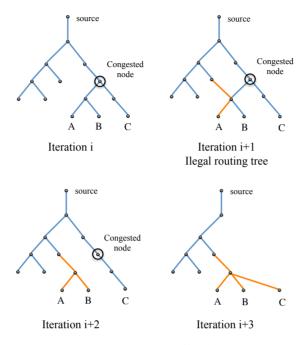

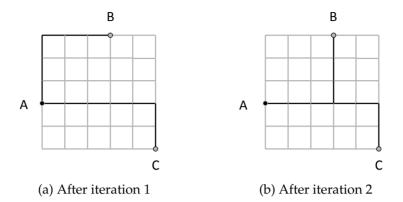

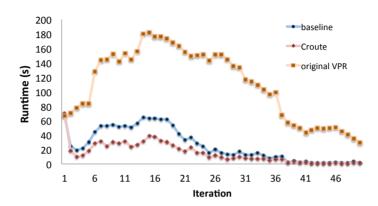

In de routeringsstap vindt de router een pad voor elk net in het ontwerp. Een net bestaat uit meerdere verbindingen vanuit dezelfde signaalbron, dit is typisch een uitgangspin van een blok. Paden voor verschillende netten kunnen geen draden delen of dit zou leiden tot een kortsluiting. Conventionele routeringsalgoritmen lossen dit probleem op door een mechanisme toe te passen waarbij netten meermaals worden opgebroken en opnieuw gerouteerd, terwijl de kost van draden verhoogd wordt als die door meerdere netten gebruikt worden. Hierdoor lost de congestie geleidelijk op en krijgen we een routering zonder kortsluitingen. In onze aanpak herrouteren we connecties in plaats van netten. Dit stelt ons in staat om enkel connecties die gecongesteerde draden gebruiken opnieuw te routeren (in plaats van volledige netten) wat veel tijd bespaart, zeker voor de netten met veel connecties.

Tijdens het ontwikkelen van de nieuwe ontwerptools ontdekten we een ander belangrijk probleem in de academische FPGA-gemeenschap. Onderzoek naar FPGA-ontwerptools of -architecturen wordt meestal uitgevoerd met behulp van een academisch raamwerk waarvan de broncode vrij te verkrijgen is, omdat academici geen toegang hebben tot de broncode van commerciële FPGA-ontwerptools en -ontwerpen. We hebben een populair academisch raamwerk met een commercieel raamwerk van één van de belangrijke FPGA-fabrikanten vergeleken. We hebben het verschil in resultaten gemeten en we vonden een grote kloof op het vlak van compilatietijd en kwaliteit van het eindresultaat. De snelheidsprestaties van de ontwerpen gecompileerd door het academisch raamwerk waren 2x slechter dan wanneer ze werden gecompileerd door het commercieel raamwerk. Een tweede doel van dit proefschrift is het bewust maken van de kloof tussen commerciële en academische resultaten en die kloof proberen te verkleinen.

Om de kloof te verkleinen introduceren we nieuwe technieken om de runtime en de kwaliteit van de FPGA-ontwerptools te verbeteren, in lijn met onze eerste doelstelling. Een groot deel van het verschil is te verklaren door de geavanceerdere commerciële FPGA-architectuur. Daarom onderzochten we nieuwe FPGA-architecturen met kleine logische poorten in het interconnectienetwerk. We dimensioneerden de transistoren in deze architecturen en we hebben nieuwe ontwerptools

ontwikkeld voor deze architecturen om de prestaties te evalueren.

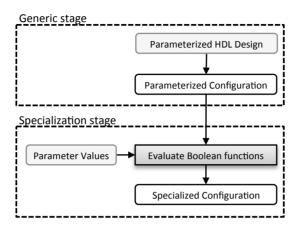

Een derde doelstelling is het verhogen van de efficiëntie van FPGA-ontwerpen. De efficiëntie van FPGA-ontwerpen kan verhoogd worden door gebruik te maken van de runtime-herconfigureerbaarheid van FPGA's. Een FPGA-configuratie kan gespecialiseerd worden voor de eisen van de applicatie terwijl de applicatie op de FPGA uitgevoerd wordt. Gespecialiseerde configuraties zijn sneller en kleiner. We hebben bijgedragen aan een automatische toolflow die geparametriseerde configuraties produceert. Tijdens de uitvoering worden deze geparametriseerde configuraties geëvalueerd om gespecialiseerde configuraties te verkrijgen zonder de tijdrovende compilatie van het ontwerp opnieuw uit te voeren. We hebben nieuwe plaatsings- en routeringstechnieken ontworpen die de herconfigureerbaarheid van de interconnectieschakelaars in de FPGA uitbuiten.

In het kort: deze thesis draagt bij tot nieuwe ontwerptools, architecturen en het verkleinen van de kloof tussen commerciële and academische ontwerptools.

## Summary

**Field-Programmable Gate Arrays (FPGAs)** are programmable, multipurpose digital chips. They are used to accelerate applications in case a higher performance is required than the performance delivered by the cheaper microprocessors. Typical requirements are high throughput, low latency and low power consumption. An example of an application that is often implemented with an FPGA is packet routing and filtering in the internet infrastructure where packets have to be processed at high throughputs and with a low latency. To realize this functionality, the FPGA consists of an array of blocks. Some blocks are flexible, others are specialized in executing a specific function. All these blocks can be connected which each other to form a more complex functionality.

The designer describes the accelerator in a high level description language and is compiled by specialized software to an FPGA configuration. Once compiled the designer checks if the application requirements are satisfied. If the requirements are met, the design is finished. If the requirements are not satisfied, the designer has to change his description and recompile the design to recheck the constraints. This slow process is called the FPGA design cycle. It is typically performed multiple times. An important bottleneck in the design cycle is the FPGA compilation runtime. FPGA design sizes have grown following Moore's law. Large designs take multiple hours to be compiled. An important goal of the work in this thesis is to **shorten the design cycle by speeding up FPGA compilation**.

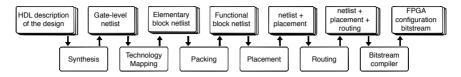

FPGA compilation software is divided in several subproblems: synthesis, packing, placement and routing. Each subproblem is handled by a different design tool. The design description is first synthesized and mapped to the primitive blocks available on the FPGA. The result is a network of primitive blocks. During packing the primitive blocks are packed into more complex blocks. The complex blocks in the network are assigned to a physical location on the FPGA during placement while optimizing the circuit on the FPGA for the application requirements. After placement the connections between the blocks are routed by setting switches in the interconnection network of the FPGA.

Placement and routing are the most time consuming steps of the FPGA compilation flow. Packing requires less runtime but it influences the runtime and quality of the placement and routing process. So to reduce the compilation runtime we focused on new techniques to improve packing, placement and routing. The traditional algorithms designed for these problems are not suited to exploit processors with multiple cores, which have become a commodity in the last decade. We introduce new packing and placement techniques that have been developed with a multi-core environment in mind.

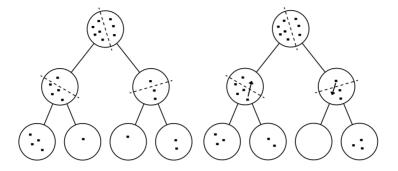

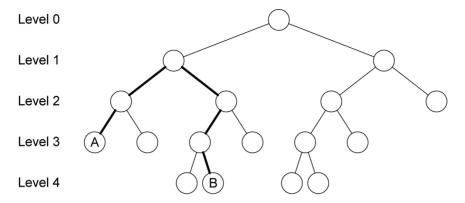

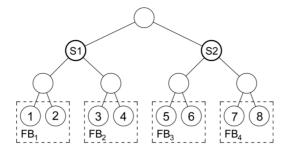

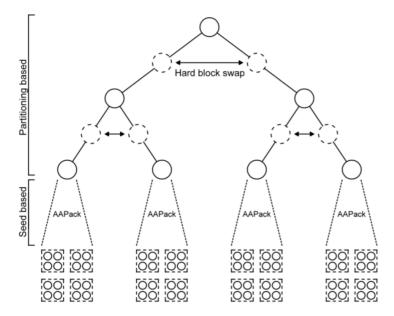

Our new packing technique observes that modern FPGAs have a hierarchical structure to improve area (cost) and delay. On each hierarchical level there are a number of equivalent blocks which can be connected by a routing network. This hierarchical structure is the main reason why a packing phase has been introduced in the compilation flow. In our approach we want to better take the natural hierarchy of the design into account during packing. There are two common approaches to the packing problem: seed-based packing and partitioningbased packing. Seed-based packing packs the design in a single pass. It is prone to local minima and difficult to adapt to be able to exploit multiple processor cores, but it handles architectural constraints well. Partitioning-based packing produces better quality designs because it preserves the natural hierarchy of the design. It is also easy to execute in multiple threads. However it is difficult to handle architectural constraints. We combined these two packing approaches to get the best of both worlds.

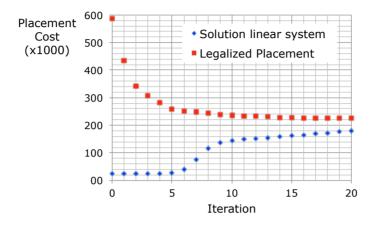

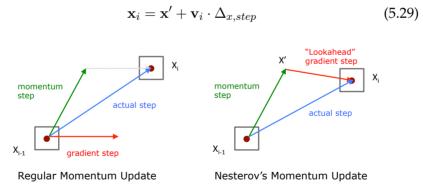

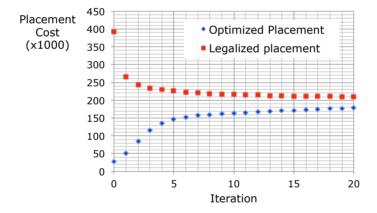

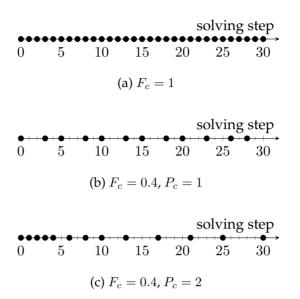

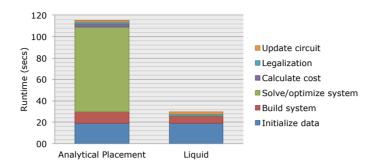

In placement the packed blocks in the design are assigned to a physical block onto the FPGA. Conventional analytical placement places a design by analytically solving the minimization of a cost function, which represents an estimate of the post-route performance. Unfortunately it is not possible to put all the architectural constraints in one analytically solvable cost function. So the problem is divided in multiple iterations. In each iteration the cost function is adapted to the result of the previous iterations and is minimized again. The minimization encompasses the runtime intensive solving of a linear system. Experiments show that it is not necessary to have the high accuracy of the intermediate solutions. In our approach we use a steepest gradient descent based optimization which is faster than solving a linear system and still produces the same quality placements. It also allows to exploit block level parallelism.

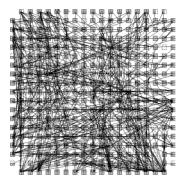

In the routing step the router finds a path for each net in the design. A net consists of several connections coming from the same signal source. Paths for different nets cannot share wires or this would lead

to a short circuit. Regions where paths want to share wires but can't are called congested regions. Conventional routing algorithms solve this problem by a negotiated congestion mechanism in which nets are ripped up and rerouted multiple times while increasing the cost of congested wires. In this way the congestion is gradually solved. In our approach we rip up and reroute connections instead of nets. This allows us to only reroute the congested connections which saves a lot of runtime, certainly for the nets with a lot of connections.

In the process of improving the design tools, we discovered another important problem in the academic FPGA community. Research on FPGA design tools or architectures is typically performed with an open source framework, because the commercial FPGA design tools are proprietary and closed source. We compared the popular academic framework with the commercial framework of one of the important FPGA vendors. We measured the gap and found it to be significant in terms of compilation runtime and quality of the end result. The speed-performance of the designs compiled by the academic framework were 2x slower than if they were compiled by the commercial framework. So another goal of this thesis is to raise awareness and reduce the gap between commercial and academic results.

To reduce the gap we introduced new techniques to improve the runtime and quality of the FPGA design tools, which aligns with our first objective (to shorten the design cycle by speeding up FPGA compilation). A large part of the gap is also because of a more advanced commercial FPGA architecture. We investigated new FPGA architectures that have small logic gates in the routing network. We sized the transistors in these architectures, developed new compilation tools for these architectures and evaluated their performance.

A third objective of this thesis was **improving the efficiency of FPGA designs**. The efficiency of FPGA designs can be improved by exploiting the runtime reconfigurability of FPGAs. An FPGA configuration can be specialized for the runtime needs of the application while the FPGA is executing. Specialized configurations are faster and smaller. We contributed to an automatic flow that produces parameterized configurations. These parameterized configurations are evaluated at runtime to get a specialized configuration without the runtime intensive recompilation of the design. We developed placement and routing tools that exploit the reconfigurability of the routing switches in the FPGA.

We conclude with emphasizing that this thesis contributes to new design tools, new architectures, and the reduction of the gap between commercial and academic tools.

# Contents

| E  | kamir | nation ( | Commission                                  | i            |

|----|-------|----------|---------------------------------------------|--------------|

| D  | ankw  | oord     |                                             | ii           |

| Sa | amen  | vatting  | (Dutch)                                     | $\mathbf{v}$ |

| Sı | umma  | ary (En  | glish)                                      | ix           |

| C  | onten | ıts      |                                             | xiii         |

| Li | st of | Acrony   | vms                                         | xix          |

| 1  | Intr  | oductio  | on                                          | 1            |

|    | 1.1   | Introd   | duction to FPGAs                            | . 1          |

|    | 1.2   | Introd   | duction to the Research                     | . 7          |

|    |       | 1.2.1    | The Slow FPGA Design Cycle                  | . 8          |

|    |       | 1.2.2    | The Gap between Academic and Commercial Re- |              |

|    |       |          | sults                                       | . 10         |

|    |       | 1.2.3    | Improving the Efficiency of FPGAs           | . 10         |

|    | 1.3   | Contr    | ibutions                                    |              |

|    | 1.4   | Struct   | ture of the Thesis                          | . 14         |

|    | 1.5   | Publi    | cations                                     | . 14         |

| 2  | Bac   | kgroun   | ad                                          | 17           |

|    | 2.1   | FPGA     | Architecture                                | . 17         |

|    |       | 2.1.1    | Low Level Building Blocks                   |              |

|    |       | 2.1.2    | Basic Logic Element (BLE)                   | . 23         |

|    |       | 2.1.3    | Soft Blocks                                 |              |

|    |       | 2.1.4    | Hard Blocks                                 | . 25         |

|    |       | 2.1.5    | Input/Output Blocks                         | . 26         |

|    |       | 2.1.6    | High-level Overview                         |              |

|    |       | 2.1.7    | Programmable Interconnection Network        | . 28         |

|    | 2.2   | FPGA     | CAD Tool Flow                               | . 30         |

|    |       | 2.2.1    | Optimization Goals                          | . 31         |

|   |      | 2.2.2  | Overview of the Tools                           | 32 |

|---|------|--------|-------------------------------------------------|----|

|   |      | 2.2.3  | Compilation Runtime                             | 34 |

|   |      | 2.2.4  | Related Work                                    | 36 |

|   | 2.3  | The H  | listory of the FPGA                             | 37 |

|   |      | 2.3.1  | FPGA versus ASIC                                | 37 |

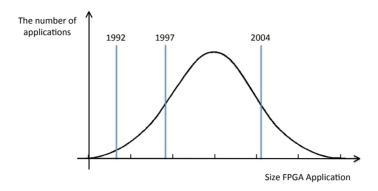

|   |      | 2.3.2  | Age of Invention (1984-1991)                    | 38 |

|   |      | 2.3.3  | Age of Expansion (1992-1999)                    | 39 |

|   |      | 2.3.4  | Age of Accumulation (2000-2007)                 | 40 |

|   |      | 2.3.5  | Current Age                                     | 41 |

|   |      | 2.3.6  | Current State of FPGA Vendors                   | 42 |

| 3 | The  | Divide | e between FPGA Academic and Commercial Results  | 43 |

|   | 3.1  | Introd | luction                                         | 43 |

|   | 3.2  | Backg  | round and Related Work                          | 44 |

|   | 3.3  | Comn   | nercial and Academic Tool Comparison            | 46 |

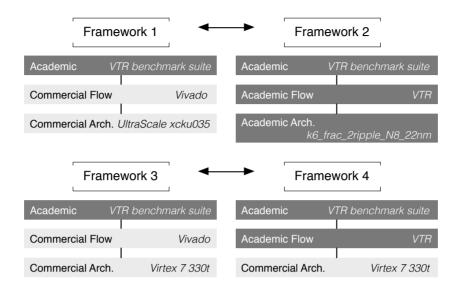

|   |      | 3.3.1  | Evaluation frameworks                           | 46 |

|   |      | 3.3.2  | Speed-performance                               | 47 |

|   |      | 3.3.3  | Area-efficiency                                 | 49 |

|   |      | 3.3.4  | Runtime                                         | 50 |

|   |      | 3.3.5  | Using VTR for a Commercial Target Device        | 52 |

|   |      | 3.3.6  | The Reasons for the Divide                      | 53 |

|   | 3.4  | Hybri  | d Commercial and Academic Evaluation Flow       | 54 |

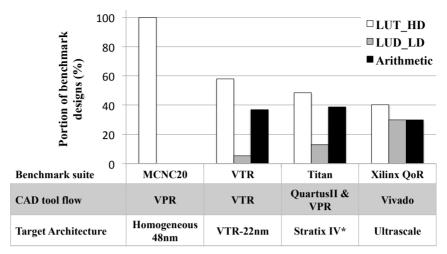

|   |      | 3.4.1  | Benchmark Design Suites                         | 57 |

|   | 3.5  | Concl  | uding Remarks                                   | 60 |

| 4 | Pres |        | Design Hierarchy to Improve Packing Performance | 63 |

|   | 4.1  |        | luction                                         | 63 |

|   | 4.2  |        | ed Work                                         | 65 |

|   | 4.3  |        | ogeneous Circuit Partitioning                   | 67 |

|   |      | 4.3.1  | Balanced Area Partitioning                      | 67 |

|   |      | 4.3.2  | 1 0                                             | 68 |

|   |      | 4.3.3  | 8                                               | 69 |

|   | 4.4  |        | g-driven Recursive Partitioning                 | 71 |

|   |      | 4.4.1  | Introduction to Static Timing Analysis          | 71 |

|   |      | 4.4.2  | Timing Edges in Partitioning                    | 72 |

|   | 4.5  | PARTS  |                                                 | 73 |

|   |      | 4.5.1  | Introduction to Simulated annealing             | 73 |

|   |      | 4.5.2  | Cost Function                                   | 75 |

|   |      | 4.5.3  | Fast Partitioning                               | 76 |

|   |      | 4.5.4  | Parallel Annealing                              | 78 |

|   |      | 4.5.5  | Problems with PARTSA                            | 80 |

|   | 4.6  |        | TIPART                                          | 80 |

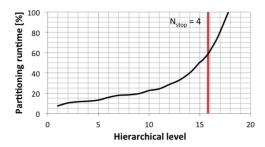

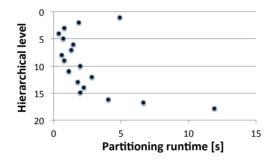

|   |      | 4.6.1  | Optimal Number of Subcircuits                   | 81 |

|   |      | 4.6.2 Passing Timing Information via Constraint Files . | 82  |

|---|------|---------------------------------------------------------|-----|

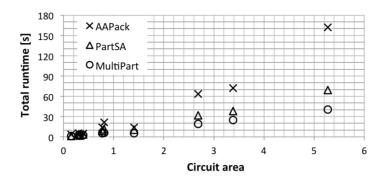

|   | 4.7  | Experiments                                             | 83  |

|   |      | 4.7.1 Optimal Number of Threads                         | 83  |

|   |      | 4.7.2 An Architecture with Complete Crossbars           | 84  |

|   |      | 4.7.3 An Architecture with Sparse Crossbars             | 86  |

|   |      | 4.7.4 A Commercial Architecture                         | 87  |

|   | 4.8  | Conclusion and Future Work                              | 88  |

| 5 | Stee | epest Gradient Descent Based Placement                  | 91  |

|   | 5.1  | Introduction                                            | 91  |

|   | 5.2  | FPGA Placement                                          | 93  |

|   |      | 5.2.1 Wire-length Estimation                            | 95  |

|   |      | 5.2.2 Timing Cost                                       | 96  |

|   | 5.3  | Simulated Annealing                                     | 97  |

|   |      | 5.3.1 The Basic Algorithm                               | 98  |

|   |      | 5.3.2 Fast and Low Effort Simulated Annealing           | 99  |

|   | 5.4  | Analytical Placement                                    | 100 |

|   |      |                                                         | 101 |

|   |      | 5.4.2 Building the linear system                        | 102 |

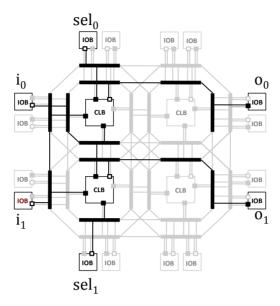

|   |      | 5.4.3 Bound-to-bound Net Model                          | 104 |

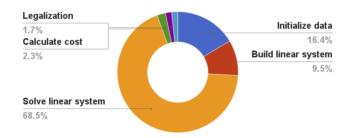

|   |      | 5.4.4 Runtime Breakdown                                 | 105 |

|   |      | 5.4.5 Timing-Driven Analytical Placement                | 106 |

|   | 5.5  | Liquid                                                  | 106 |

|   |      | 5.5.1 The Basic Algorithm                               | 106 |

|   |      |                                                         | 107 |

|   |      |                                                         | 111 |

|   |      |                                                         | 113 |

|   |      | 5.5.5 Runtime Breakdown Comparison                      | 115 |

|   | 5.6  |                                                         | 116 |

|   | 5.7  | Experiments                                             | 117 |

|   |      | 5.7.1 Methodology                                       | 117 |

|   |      | 5.7.2 Runtime versus Quality                            | 118 |

|   |      |                                                         | 120 |

|   |      |                                                         | 122 |

|   |      | 5.7.5 Comparison with Simulated Annealing               | 122 |

|   |      | 5.7.6 Post-route Quality                                | 123 |

|   | 5.8  | Future Work                                             | 123 |

|   | 5.9  | Conclusion                                              | 124 |

| 6 | A C  | onnection-based Routing Mechanism                       | 125 |

|   | 6.1  | <u> </u>                                                | 125 |

|   | 6.2  |                                                         | 127 |

|   | 6.3  | -                                                       | 128 |

|   |              | 6.3.1  | PATHFINDER: A Negotiated Congestion Mecha-         |     |

|---|--------------|--------|----------------------------------------------------|-----|

|   |              |        | nism                                               | 129 |

|   | 6.4          | Crou   | TE: The Connection Router                          | 132 |

|   |              | 6.4.1  | Ripping up and Rerouting Connections               | 132 |

|   |              | 6.4.2  | The Change in Node Cost                            | 133 |

|   | 6.5          | Negot  | tiated Sharing Mechanism                           | 136 |

|   |              | 6.5.1  | The Negotiated Sharing Mechanism Inherent to       |     |

|   |              |        | CROUTE                                             | 136 |

|   |              | 6.5.2  | Trunk Bias                                         | 137 |

|   | 6.6          | Partia | l Rerouting Strategies                             | 137 |

|   | 6.7          |        | iments and Results                                 | 138 |

|   |              | 6.7.1  | Methodology                                        | 138 |

|   |              | 6.7.2  | Results                                            | 139 |

|   | 6.8          | Concl  | usion and Future Work                              | 141 |

|   |              |        |                                                    |     |

| 7 |              |        | Route tools for the Dynamic Reconfiguration of the |     |

|   |              | -      | etwork                                             | 143 |

|   | 7.1          |        | view of Dynamic Partial Reconfiguration            | 143 |

|   |              | 7.1.1  | Introduction to Dynamic Circuit Specialization     | 144 |

|   |              | 7.1.2  | Contributions                                      | 145 |

|   | 7.2          | U      | round                                              |     |

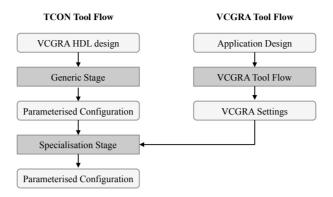

|   |              | 7.2.1  | Configuration Swapping                             |     |

|   |              | 7.2.2  | Dynamic Circuit Specialization                     | 147 |

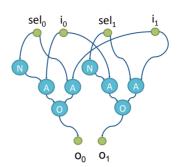

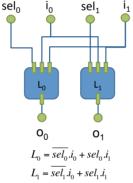

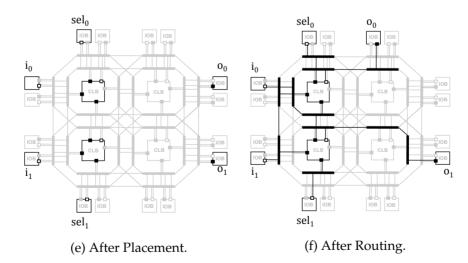

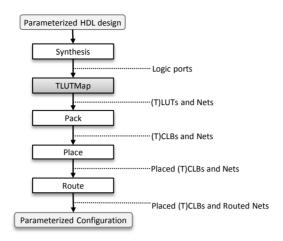

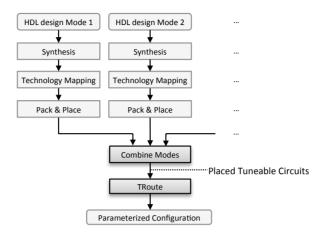

|   |              | 7.2.3  | TLUT Tool Flow                                     | 149 |

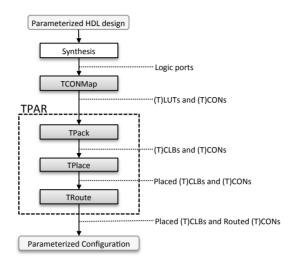

|   | 7.3          | The T  | CON tool flow                                      | 149 |

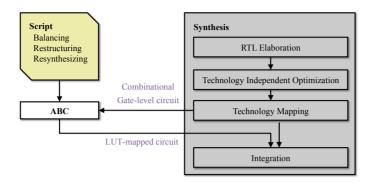

|   |              | 7.3.1  | Synthesis                                          | 150 |

|   |              | 7.3.2  | Technology Mapping                                 | 150 |

|   |              | 7.3.3  | TPACK and TPLACE                                   | 152 |

|   |              | 7.3.4  | TROUTE                                             | 153 |

|   |              | 7.3.5  | Limitations                                        | 155 |

|   | 7.4          | TPACI  | К                                                  | 155 |

|   | 7.5          | TPLAG  | CE                                                 | 157 |

|   |              | 7.5.1  | Wire Length Estimation for Nets in Static Circuits | 158 |

|   |              | 7.5.2  | Wire Length Estimation for Tuneable Circuits       | 159 |

|   |              | 7.5.3  | Evaluation of the Wire Length Estimation           | 163 |

|   | 7.6          |        | TE                                                 | 164 |

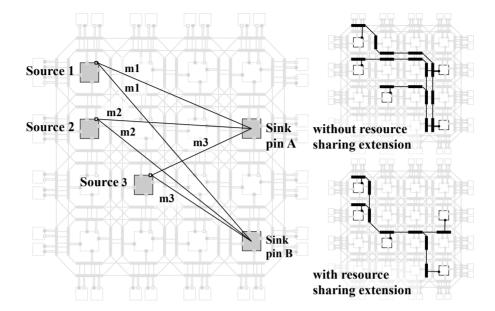

|   |              | 7.6.1  | The TCON Routing Problem                           | 165 |

|   |              | 7.6.2  | Modifications to the Negotiated Congestion Loop    | 165 |

|   |              | 7.6.3  | Resource sharing extension                         | 166 |

|   | 7.7          |        | cations and Experiments                            | 168 |

|   | <del>-</del> | 7.7.1  | FPGA Architecture                                  | 168 |

|   |              | 7772   | Methodology                                        | 169 |

|   |      | 7.7.3   | Virtual Coarse Grained Reconfigurable Arrays   | 170 |

|---|------|---------|------------------------------------------------|-----|

|   |      | 7.7.4   | Clos Networks                                  | 172 |

|   |      | 7.7.5   | Runtime comparison                             | 174 |

|   |      | 7.7.6   | Specialization Overhead                        | 175 |

|   | 7.8  | Conclu  | asion                                          | 176 |

| 8 | Logi | c Gates | s in the Routing Nodes of the FPGA             | 177 |

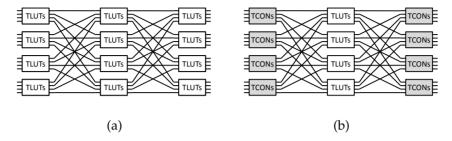

|   | 8.1  |         | iew                                            | 177 |

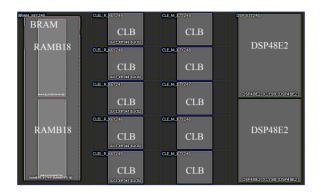

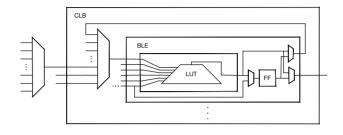

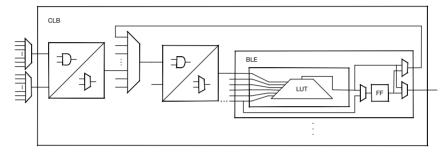

|   | 8.2  | FPGA    | Architecture                                   | 178 |

|   |      | 8.2.1   | High-level Overview                            | 178 |

|   |      | 8.2.2   | Baseline Architecture                          | 179 |

|   |      | 8.2.3   | Routing Node                                   | 181 |

|   | 8.3  | Transis | stor-level Design                              | 182 |

|   |      | 8.3.1   | Selecting the Type of Logic Gate               | 183 |

|   |      | 8.3.2   | The N:2 Multiplexer                            | 184 |

|   |      | 8.3.3   | Level Restoring Tactics                        | 187 |

|   |      | 8.3.4   | Routing Nodes in Different Locations           | 189 |

|   |      | 8.3.5   | Concluding Remarks on the Sizing Results       | 189 |

|   | 8.4  | Conve   | ntional Technology Mapping                     | 190 |

|   |      | 8.4.1   | Optimisation Criteria                          | 190 |

|   |      | 8.4.2   | Definitions                                    | 192 |

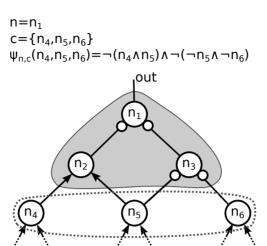

|   |      | 8.4.3   | Conventional Technology Mapping Algorithm      | 193 |

|   | 8.5  | Mappi   | ing to LUTs and AND Gates                      | 198 |

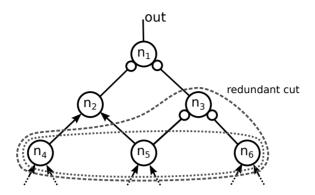

|   |      | 8.5.1   | Cut Enumeration and Cut Ranking                | 199 |

|   |      | 8.5.2   | Cut Selection and Area Recovery                | 201 |

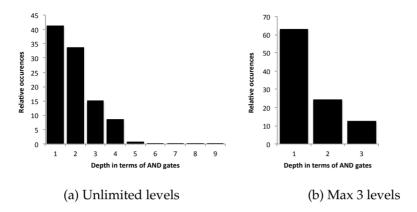

|   |      | 8.5.3   | Area and Depth                                 | 202 |

|   |      | 8.5.4   | AND Gate Chains                                | 204 |

|   | 8.6  | Packin  | ıg                                             | 205 |

|   |      | 8.6.1   | Modeling the Architecture                      | 205 |

|   |      | 8.6.2   | Conventional Packing                           | 208 |

|   |      | 8.6.3   | Resynthesis during Cluster Feasibility Check   | 209 |

|   |      | 8.6.4   | Performance Improvement                        | 211 |

|   | 8.7  | Post-ro | oute Performance                               | 212 |

|   | 8.8  | Conclu  | ading Remarks                                  | 214 |

| 9 | Con  |         | s and Future Work                              | 217 |

|   | 9.1  | Conclu  | asions                                         | 217 |

|   |      | 9.1.1   | The Gap between the Academic and Commercial    |     |

|   |      |         | Results                                        | 217 |

|   |      | 9.1.2   | New FPGA Compilation Techniques                | 218 |

|   |      | 9.1.3   | Dynamic Reconfiguration of the Routing Network | 218 |

|   |      | 9.1.4   | FPGA Architectures with Logic Gates in the     |     |

|   |      |         | Routing Network                                | 219 |

| Bibliogr | aphy  | tectures                                             | 223 |

|----------|-------|------------------------------------------------------|-----|

|          | 9.2.2 | Generic Method to Investigate New FPGA Architectures | 221 |

|          | 9.2.1 | Work                                                 |     |

## List of Acronyms

ADC Analog-to-Digital Converter

AES Advanced Encryption Standard

AIG And-Inverter Graph

AP Analytical Placement

ARM Advanced RISC Machines

ASIC Application-Specific Integrated Circuit

ASIP Application-Specific Instruction-set Processor

BDD Binary Decision Diagram

BLE Basic Logic Element

BLIF Berkeley Logic Interchange Format

BRAM Block RAM

CAD Computer-Aided Design

CAM Content-addressable Memory

CGRA Coarse-Grained Reconfigurable Array

CLB Configurable Logic Block

CM Configuration Manager

CMOS Complementary Metal-Oxide-Semiconductor

CPD Critical Path Delay

CPU Central Processing Unit

CTO Chief Technology Officer

CV Computer Vision

CW Channel Width

DAO Depth-optimal Area Optimization

DCS Dynamic Circuit Specialisation

DDR SDRAM Double data rate synchronous dynamic random-access memory

DPR Dynamic Partial Reconfiguration

DRAM Distributed RAM

DSP Digital Signal Processing

EDA Electronic Design Automation

FB Functional Block

FET Field-Effect Transistor

FF Flip-Flop

FIFO First In, First Out

FinFET Fin Field Effect Transistor

FIR filter Finite Impulse Response filter

FM Frequency Modulation

FPGA Field-Programmable Gate Array

GB GigaByte

GP General Purpose

GPGPU General-Purpose computing on Graphics Processing Units

GPU Graphics Processing Unit

HDL Hardware Description Language

HP High-Performance

HPC High-Performance Computing

HPWL Half-Perimeter Wire Length

HWICAP Hardware ICAP

HLS High-Level Synthesis

IBM International Business Machines Corporation

ICAP Internal Configuration Access Port

IO Input/Output

IOB Input/Output BlockIP Intellectual Property

ISE Xilinx Integrated Synthesis Environment

JIT Just-In-Time

K-LUT K-input LUT

KU Kintex UltraScale LAB Logic Array Block

LC Logic Cluster

LD Logic Depth

LI Local Interconnect

LIFO Last In, First Out

LVDS Low-Voltage Differential Signaling

LUT LookUp Table

MAC Multiply-Accumulate Unit

MB MegaByte

MM Multi-mode

MCW Minimum Channel Width

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MUX Multiplexer

NFA Non deterministic Finite Automaton

NIDS Network Intrusion Detection System

NMOS N-channel MOSFET

NRE cost Non-Recurring Engineering cost

OS Operating System

PAL Programmable Array Logic

PaR Place and Route

PCIe Peripheral Component Interconnect Express

PE Processing Element

PI Primary Input

PLL Phase Lock Loop

PMOS P-channel MOSFET

PO Primary Output

PPC Partial Parameterized Configuration

PR Partial Reconfiguration

RAM Random-Access Memory

ROM Read-Only Memory

RCP Representative Critical Path

RRG Routing Resource Graph

RTL Register-Transfer Level

RTR Run-Time Reconfiguration

RTL Register-Transfer Level

SA Simulated Annealing

SB Switch Block

SDC Synopsys Design Constraints format

SRAM Static Random Access Memory

SRL Shift Register LUT

STA Static Timing Analysis

TCAM Ternary Content-Addressable Memory

TCON Tuneable Connection

TH Treshold

TLUT Tuneable LUT

TPaR Tuneable Place and Route

TWL Total Wire Lenght

TRCE The Timing Reporter And Circuit Evaluator tool from Xilinx

VCGRA Virtual CGRA

VHDL Hardware Description Language

VPR Versatile Place and Route

VTB Verilog-To-Bitstream VTR Verilog-To-Routing

WL Wire Length

WNS Worst Negative Slack

XDL Xilinx Design Language

# Introduction

This thesis starts with an introduction to the FPGA by answering some frequently asked questions. Next the fundamental problems related to FPGA compilation and architectures that are addressed in this thesis are described. This is followed by our contributions that help towards solving the problems. In the last sections we describe the structure of this thesis and list the publications about the work in this dissertation.

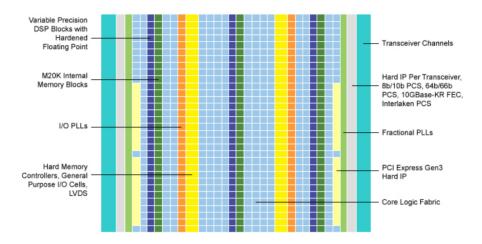

### 1.1 Introduction to FPGAs

What is an FPGA? A Field Programmable Gate Array is a type of programmable, multi-purpose digital chip. They are programmable in the 'field' after they are manufactured. An FPGA essentially consists of a huge array of gates which can be programmed and reconfigured any time, anywhere. However, "A huge array of gates" is an oversimplified description of an FPGA. A modern FPGA consists of an array of programmable blocks. Some of those blocks are very flexible. They contain look-up tables which can perform simple Boolean logic operations, registers to temporarily store results and resources that connect the lookup tables and registers. Other blocks are specialized in a specific task such as Digital Signal Processing (DSP) blocks, memory blocks, high speed communication resources, ... The blocks are embedded in an interconnection network, which can be programmed to connect the blocks together to make a circuit of your choice.

Why would we use an FPGA? An FPGA is used to accelerate an application that requires intensive computations, high throughput, low latency calculations or has a stringent power budget. An FPGA is flexible and is built to exploit the parallel nature of the problem. How much parallelism is used to implement the application is completely up to the designer. The application design architect can tailor a custom processor to meet the individual needs of the application.

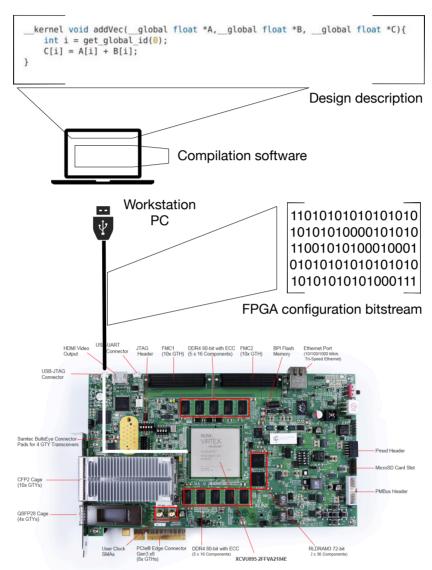

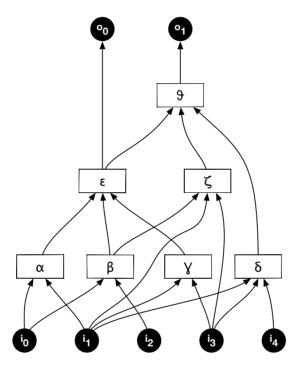

How does it work? How is an FPGA used? The typical work environment for an FPGA is depicted in Figure 1.1. The hardware/application designer writes his application accelerator or process kernel in a high level description language such as VHDL, Verilog, OpenCL, ... Subsequently the design description is compiled by specialized software to an FPGA configuration bitstream on the workstation of the application designer. The compilation software is typically divided in different steps which are being handled by different tools. The compilation tool flow is also called Computer Aided Design (CAD) or Electronic Design Automation (EDA) tool flow. We use the former term in what follows. The software tools in the CAD tool flow are an important subject in this thesis. The majority of the chapters describe improvements and speed-up techniques made to the most time consuming steps of the compilation tool flow. After the compilation, the design is then typically tested on a printed circuit board which contains the target FPGA. The FPGA configuration bitstream is sent to the program interface of the test board and the FPGA is programmed with the configuration bitstream.

How does it compare to other popular digital chips? Other important popular digital chips are microprocessors, Graphical Processing Units (GPUs) and Application-Specific Integrated Circuits (ASICs):

- Microprocessors perform tasks by splitting them up in small and simple operations and perform these operations sequentially in one or more threads, depending on the number of cores in the microprocessor. Each of these simple operations (instructions) is executed by specific hardware on the microprocessor chip.

- GPUs contain a large array of processors specialized for multiply and accumulate (MAC) operations and distributed memory to support this. They are specially designed to support video processing and graphics rendering, but they are also used for other applications that need a lot of MACs, such as training convolu-

Printed Circuit Board (PCB) with FPGA chip

Figure 1.1: An overview of a work environment for an FPGA

Table 1.1: Comparison of typical microprocessor, FPGA, ASIC and GPU designs. Partly reproduced from [56].

|                                            | Microprocessor | FPGA                  | ASIC         | GPU            |

|--------------------------------------------|----------------|-----------------------|--------------|----------------|

| Example                                    | ARM Cortex-A9  | Virtex Ultrascale 440 | Bitfury 16nm | Nvidia Titan X |

| Flexibility during development             | Medium         | High                  | Very high    | Low            |

| Flexibility after development <sup>1</sup> | High           | High                  | Low          | High           |

| Parallelism                                | Low            | High                  | High         | Medium         |

| Performance <sup>2</sup>                   | Low            | Medium                | High         | Medium         |

| Power consumption                          | High           | Medium                | Low          | High           |

| Development cost                           | Low            | Medium                | High         | Low            |

| Production setup cost <sup>3</sup>         | None           | None                  | High         | None           |

| Unit cost <sup>4</sup>                     | Medium         | High                  | Low          | High           |

| Time-to-market                             | Low            | Medium                | High         | Medium         |

<sup>&</sup>lt;sup>1</sup>E.g. to fix bugs, add new functionality when already in production

tional networks, digital signal processing, ...

• **ASICs** are single purpose chips. They are manufactured to only perform one big function. Any digital circuit can be baked into the silicon during production, but they cannot be reprogrammed. They are typically fast and low power, like FPGAs, but each chip can only perform the one function that is baked into the silicon during production and cannot be reprogrammed.

An overview and comparison of the properties of these chips with the properties of the FPGA is summarized in Table 1.1

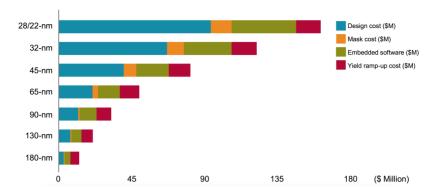

FPGAs are typically used when the application requirements are not met by the cheaper microprocessors. They have a vastly wider potential to accelerate applications than the microprocessor and they excel in power consumption. Only ASICs can achieve higher speeds, lower power consumption and lower unit costs, because they are specially made for the application and don't have the overhead sustained by the programmability of the FPGA. However, for low and medium volumes ASICs are too expensive, because producing a custom silicon chip has a large upfront cost due to the high cost of design and production setup (e.g. photomasks). FPGAs are mainly used for small to medium volume products and ASICs for very high volume products. ASICs also lack flexibility, once they are produced they can't change their functionality

During development an ASIC is specialized for the application. Each wire and transistor is placed specially for the application and it is

<sup>&</sup>lt;sup>2</sup>For a sufficiently parallel application

<sup>&</sup>lt;sup>3</sup>Cost of producing the first chip

<sup>&</sup>lt;sup>4</sup>Cost of producing each chip after the first

therefor the most flexible of accelerators. The FPGA is the second most flexible during development. The application has to be implemented by connecting low level generic programmable blocks and specialized blocks on the FPGA. They can be interconnected in various patterns. Microprocesors are less flexible during development, because the application has to be executed by splitting the task up in simple operations that are executed sequentially in one or a few threads. The development of the accelerator is restricted mostly when developing for GPUs. GPUs typically contain from several hundred up until several thousand cores. However, each processing core is only capable of executing a small subset of basic operations, most notably the multiply and accumulate operations. GPUs are very specialized accelerators, they are focused on MAC-heavy applications that require a high throughput and low latency. In an ASIC and an FPGA the dataflow can be specialized for the application, in a GPU you are restricted by different aspects, such as the available memory caches and the 16/32/64 floating point operations. Additionally FPGAs serve a broader spectrum of applications than the GPU.

FPGAs, GPUs and microprocessors have a lower commercial risk and a faster time-to-market than ASICs [142]. Mistakes made during development can easily be fixed after development by reprogramming the device. There is also the possibility to add new functionality in future upgrades. The reprogrammability extends the time a product stays relevant, because features can be changed according to the changing demand. For this reason, some products ship with an FPGA/GPU/microprocessor that is over-dimensioned, to allow for future upgrades. For ASICs there is almost no flexibility after development. Development mistakes that make it into an ASIC require a very expensive silicon respin or even a product recall. Microprocessor solutions have the lowest time-to-market, because of its ubiquity and the well developed compilation and debug tools. Developing for FPGAs and GPUs is more complex, which results in a higher time-to-market The ASIC takes the cake for time-to-market with its complex and slow development process.

Microprocessors have only limited capabilities to exploit the parallellism of an application. They typically only have a 1 to 6 cores. GPUs have typically much more with up to 3840 cores for the recent Nvidia Quadro P6000 GPU. For FPGAs and ASICs, the number of processing units is completely up to the designer. It can be adapted to the needs of the application.

For a same technology node an ASIC will have a higher performance compared to the FPGA in terms of area, speed and power con-

sumption, because the functionality is hard-wired and there is no programmability overhead. However, many new ASIC designs do not use the latest process technology, because they are way more expensive than older ones, whereas FPGA vendors do [1, 4]. Because of this, the speed, area and power gap is smaller between FPGAs compared to a functionally equivalent ASIC in an older process technology. For a MAC heavy application that requires high throughput, the GPU probably will have the upper hand in comparison to the FPGA, but where the FPGA excels is the power performance. FPGAs even outperform the GPU in terms of energy efficiency for the MAC intensive evaluation of convolutional networks [81]. The microprocessor typically has the lowest performance in terms of area, speed and power consumption.

An ASIC is has the highest development cost. A lot of man hours and high license costs for the EDA tools. It also has a large production setup costs, which is the cost to produce the first chip. The FPGA does not have production setup costs and it has a lower development cost than an ASIC, but it has a higher development cost than developing an accelerator for GPU or CPU, because of the license costs and the more time consuming design cycle. A downside of both the FPGA and the GPU is the relatively high unit cost, which is typically higer than the omnipresent microprocessor. An ASIC has relatively the lowest unit cost.

#### Who uses FPGAs? What are the important applications of the FPGA?

The most important applications implemented on the FPGA are packet routing, switching and filtering in the internet infrastructure. Wired and wireless communication has grown to over half of the FPGA business with important customers as Cisco, TE connectivity, Juniper networks and many more. With such an important share of the revenue, it has driven innovation in FPGAs to support this application domain.

Another important application domain is high performance computing, with important customers as IBM for example. Datacenters prefer FPGAs to perform some tasks over other processing units, because of their superior performance per power unit and the flexibility to reprogram the FPGA at any time. Microsoft is a pionier in this aspect. Other important application domains are video processing and sensor processing, for example low latency virtual reality rendering and seismic imaging software. FPGAs are also favoured in embedded systems, because of their low power signature.

FPGAs are also used by engineers in the design of ASICs. The application is first prototyped, debugged and tested with the help of an

FPGA. Radiation upsets are emulated with an FPGA. Test vectors are calculated by injecting faults in the design. Possibly the first generation of a product is sold with an embedded FPGA. Once the major problems have been ironed out, the hard-wired version of the design is produced and embedded in the second generation of products. An example is the Lattice Semiconductor LFXP2-5E low-cost non-volatile FPGA that was embedded in the motherboard of Apple's 2011 Macbook pro to switch the LVDS display signal between the two GPUs. In the 2012 versions it was replaced by the Texas Instrument's dedicated ASIC, HD3SS212. Another company using the same strategy is Nokia.

New application fields are being unlocked as we write. One example is accelerating inference by evaluating convolutional nets on the FPGA.

Who produces FPGAs? The main FPGA vendors are Xilinx and Altera, now part of Intel. They are both based in Silicon Valley. They design and sell FPGAs, but they outsource the manufacturing to specialized silicon foundries, such as Taiwan Semiconductor Manufacturing Company, Limited (TSMC) or Intel. Other smaller FPGA companies focus on niche markets, such as Lattice with its low power and low cost FPGAs and Microsemi with its non-volatile low power FPGAs.

**How much does an FPGA cost?** The cost of an FPGA is largely dependent on the size of the chip, i.e. how many programmable blocks and input/output interfaces are available on it. The price range of one FPGA unit varies a lot between 1 EUR for low end, smaller and older FPGAs to a few 10,000 EUR for the high end, large flagship devices of the newest technology node.

The second aspect of an implementation that affects its cost is the clock frequency. The clock frequency is the drum beat that defines the rate at which computations are performed. It is determined by the electric delay of the hardware and depends on the configuration of the FPGA. If a design does not meet minimal performance requirements, this can be solved by redesigning it using more resources (e.g. more parallelism or pipelining) or choosing a more expensive FPGA with lower electric delay (higher speedgrade or newer technology node).

### 1.2 Introduction to the Research

There are a few fundamental problems and opportunities we try to address in this thesis. We will mainly discuss the problems in this section,

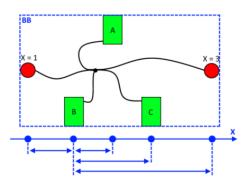

Figure 1.2: The FPGA design cycle and the runtime breakdown of the FPGA compilation.

the solutions we investigated are described in the next section.

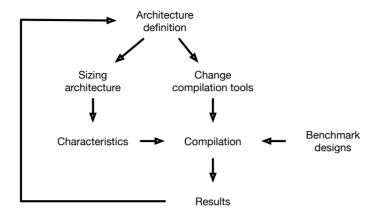

### 1.2.1 The Slow FPGA Design Cycle

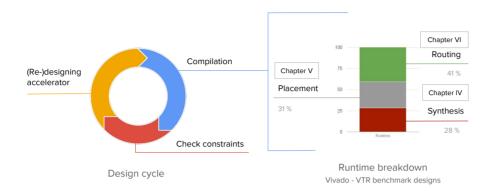

The design cycle for FPGA design is illustrated in Figure 1.2. The hardware engineer designs the accelerator by describing the different modules of the accelerator. Once the design has been described, the design is compiled to an FPGA configuration. The compiler tries to meet the design constraints. However, it is possible that the design constraints are too stringent for the given design description and FPGA architecture. So after the compilation is finished, the designer has to check if the FPGA configuration meets all the application constraints. Typical constraints are maintaining a certain throughput, an upper limit for latency, lowest cost (area) and a small power budget. In case the compiled design meets the constraints, the cycle is finished. In case it doesn't meet the constraints, the engineer has to change his design to obtain different characteristics after compilation. Depending on the gap between the obtained performance and the goal, there a number of options: make fundamental changes to the algorithm, target a different FPGA or make smaller changes, such as properly pipelining for example. The design has to be recompiled and the constraints have to be rechecked. This cycle typically has to be performed numerous times. We want to shorten the design cycle as much as possible, because a slow design cycle means high engineering costs and a slow time-to-market.

There are two important approaches for shortening the design cy-

cle. On the one hand we can try to increase the productivity of the engineer by increasing the ease of use. For example, an active research field with this aim is the high-level synthesis efforts. They make it easier for the designer to describe the application by using a high level language: C, SystemC or OpenCL. On the other hand the compilation runtime should be as short as possible. For large designs the compilation is the bottleneck of the design cycle. It can easily take a few hours to compile a design. For example the <code>mes\_noc</code> design from the Titan benchmark suite with 549K blocks requires 4h to be compiled by the Altera's Quartus compilation tool flow and 10h with an academic compilation tool flow for a single threaded execution. The size of commercial designs easily surpasses 500K blocks.

Reducing the compilation time also improves the ease of use, because the engineer can use the compilation flow for trial and error approaches as is common in the software programming domain. In this thesis we focus on reducing the compilation time by improving the compilation steps.

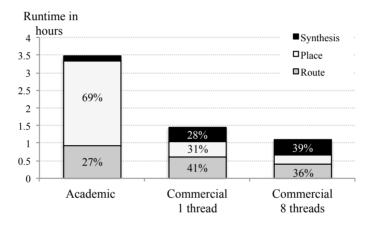

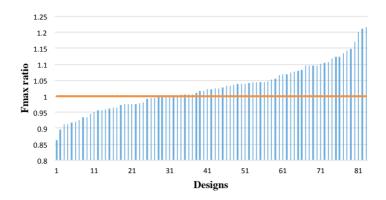

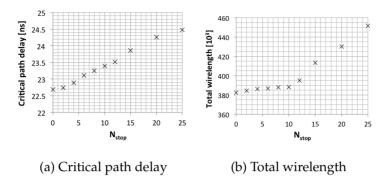

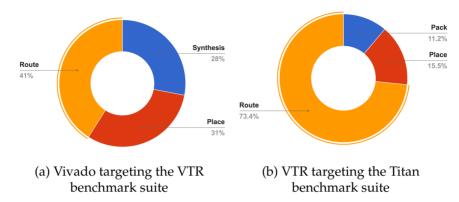

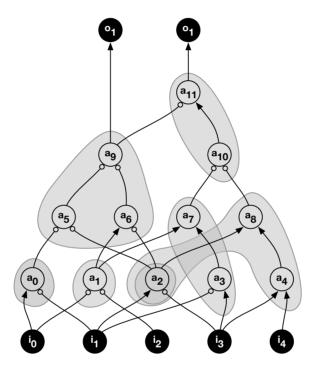

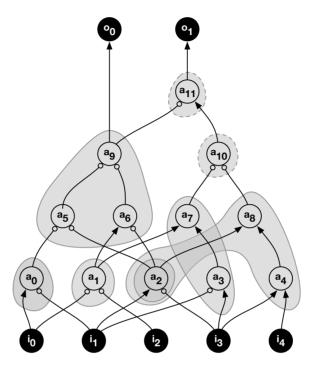

#### **FPGA Configuration Compilation**

Generating the optimal FPGA configuration is nearly impossible, because the solution space is very large. To simplify the problem, the compilation is split up in several steps. In the first step the design description is synthesized and mapped to the available functional block types on an FPGA, resulting in a network with functional block instances. We call this step synthesis. Next, each block in the network is assigned to a physical block location on the FPGA, which is called the placement step. Finally, the connections between the blocks are routed by deciding which switches need to be set in the interconnection network. Even the subproblems in each of the compilation steps are hard to solve. Generating the optimal solution for one step would take a very long time. This only worsens for larger designs, so the FPGA vendors and academic community try to find heuristics that generate a near optimal solution in a reasonable timeframe. Each compilation step has its influence on the end result and influences the runtime of the other steps downstream. The bar chart in Figure 1.2 shows the runtime breakdown for the different compilation steps. The current synthesis, placement and routing approaches account for an equal part of the total compilation runtime. In this thesis we look at each of these steps in a dedicated chapter and propose new techniques to reduce the runtime and improve the quality of the result.

#### 1.2.2 The Gap between Academic and Commercial Results

It is hard to make conclusions about research work around new FPGA compilation techniques or new FPGA architectures, because everyone is working with a different framework. A framework includes the target FPGA, the compilation tools and the benchmark designs. The FPGA vendors keep the details of their architecture secret. They specialize their FPGA compilation tools to their architectures and the compilation tools are closed source. This makes it hard for academic researchers to benchmark their new approaches in a commercial framework. There are academic frameworks available but they lag behind the commercial frameworks in almost every aspect, which makes it hard to estimate the value of new techniques.

#### 1.2.3 Improving the Efficiency of FPGAs

As Moore's law is ending and technology process scaling is slowing down [4, 119, 139], it is imperative to find new ways to improve the FPGAs performance. This includes investigating new architectures and different techniques to use the FPGA more efficiently. The main objective is to reduce the cost of FPGA design, while improving the performance.

#### Architecture

In the past years the continuous race towards the next smaller technology node pushed FPGA architects towards designing architectures that are performing well when scaling down and are easy to adapt to the new process technology node. Incremental changes to the architecture and tools were preferred above drastic changes. One example is changing the ratio between specialized blocks and generic blocks in the FPGA. Another example is changing the size of specialized memory blocks.

As the advantage of newer process technology diminishes, newer more exotic architectures can become more interesting to further push the performance forward.

#### **Partial Reconfiguration**

New techniques are emerging that try to exploit the "hidden" features of the current FPGAs to improve the efficiency. One example is partial and runtime reconfiguration. The configuration memory of an FPGA has to be loaded with a configuration bitstream at start-up before the

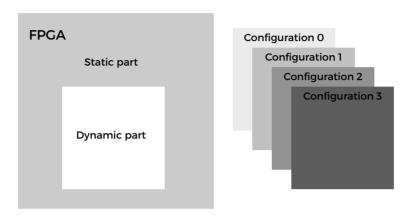

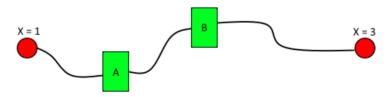

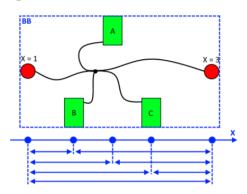

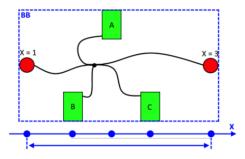

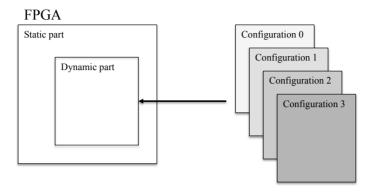

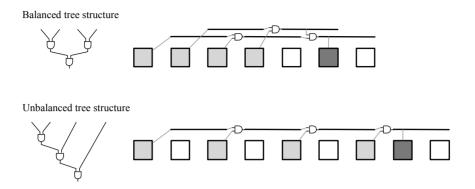

FPGA can start to execute. Modern FPGAs allow parts of the configuration memory to be rewritten at runtime, thus changing the function of these resources. This can be done without affecting the operation of other parts of the FPGA. Two types of reconfiguration can be distinguished. They are illustrated in Figure 1.3.

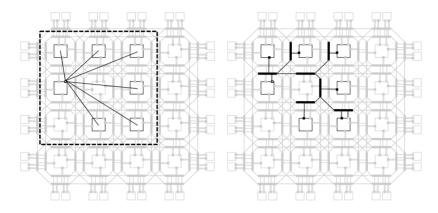

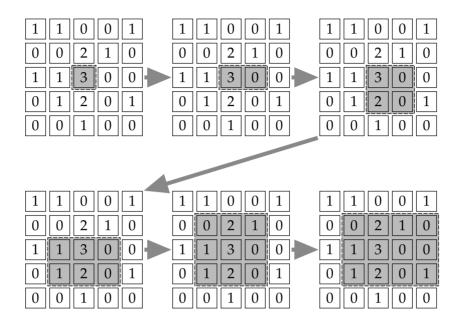

Modular Reconfiguration is a technique in which a region of the FPGA is reserved to implement several predefined circuits, one at a time, and it is possible to switch between the predefined circuits on the fly using partial reconfiguration (Figure 1.3a) [12, 141, 146]. Without partial reconfiguration, all of the circuits would have to be implemented in separate regions of the FPGA, each using its own set of resources. This would result in a resource cost that is many times larger. This type of partial runtime reconfiguration is becoming popular in datacenters. It reduces the cost when larger FPGAs in the cloud can run two or more independent accelerators concurrently.

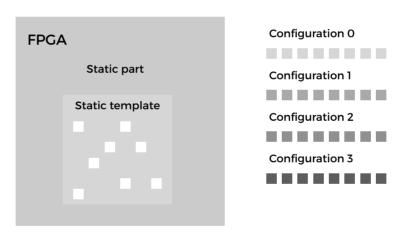

**Micro Reconfiguration** Partial reconfiguration can also be used to reconfigure very small parts of the FPGA, such as a single logic or routing resource (Figure 1.3b). This is called micro reconfiguration. Micro reconfiguration is used to slightly tweak a circuit, for example the coefficients of a digital filter or ease the transition between different modes.

**Problems** The partial and runtime reconfiguration techniques have not found their way in a lot of commercial applications because the techniques perform badly in terms of ease of use. There is a lack of good compilation tools and the process currently requires a lot of manual work. In this work we mainly focused on micro reconfiguration.

#### 1.3 Contributions

In this dissertation we contributed towards solving the problems mentioned in the previous section. These are our main contributions:

Quantifying the Gap between Academic and Commercial Results It is difficult to assess how the new ideas on compilation tools and architectures presented in academic conferences and publications would perform in a commercial framework. Academic work is benchmarked against the well known compilation tools, architectures and benchmark designs in open source frameworks. There is a danger in only using open source frameworks to evaluate new tool and architectural ideas,

(a) Modular reconfiguration.

(b) Micro reconfiguration

Figure 1.3: The two partial and runtime reconfiguration techniques

it creates an academic bias. We measured the gap between academic and commercial results and found it to be substantial. To reduce the gap we focused mainly on new FPGA compilation techniques and architectures. There are already other academic researcher working on trying to reduce the gap between commercial and academic benchmark designs [106].

**New FPGA Compilation Techniques** Many of the old compilation techniques are designed for single core processors. It is hard to adapt these old techniques in order to exploit the acceleration potential of the multiple cores in the modern workstations. We investigated the main runtime consuming parts of the old techniques and propose new compilation techniques that can accelerate these parts by exploiting the multi-core processor environment. We propose new pack, placement and routing techniques that improve the runtime and quality. These efforts contribute to a shorter FPGA design cycle and a smaller divide between the academic and commercial results We also made our new compilation tools available to the academic community in an open source project [136]. In contrast to the other open source projects in the academic community, which are mainly implemented in C [1, 88], the new compilation tools are implemented in Java. Java is a platform independent high level programming language. This makes it easier for other researchers to adapt the compilation tools to suit their research objective.

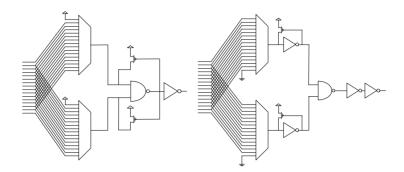

# Developing New Compilation Techniques for Micro Reconfiguration To exploit micro reconfiguration, we propose to dynamically specialize the accelerator for the needs of the application. To make it easier for the designer we automatically produce a static template and parameterized configurations for the micro parts in the configuration. This is only possible because of the newly proposed dynamic circuit specialization compilation flow. We contributed to this compilation flow with new place and route techniques.

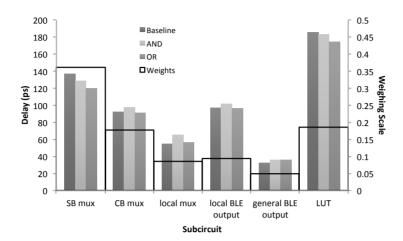

**Investigating new FPGA Architectures** To improve the efficiency of FPGAs we investigated a range of new architectures. We focused on FPGA architectures with small logic gates introduced in their interconnection network. To test these architectures we developed new compilation techniques and sized the architecture with the help of an electronic circuit simulator.

#### 1.4 Structure of the Thesis

This thesis is organized as follows: in the background section (Chapter 2) we give an overview of the current state of the FPGA architecture and describe the different steps in the CAD tool flow that generate FPGA configurations, synthesis, technology mapping and packing, placement and routing. A historic context of the FPGA is also described in this chapter to put the work in this thesis in perspective. In Chapter 3 we investigate the performance gap between the results obtained by academic and commercial research frameworks. A research framework includes the FPGA CAD tool flow, a target FPGA architecture and benchmark designs. A research framework allows researchers to make conclusions about new techniques, algorithms or architectures. The gap indicates that research conclusions in the academic and commercial world can differ, which negatively impacts the whole FPGA ecosystem.

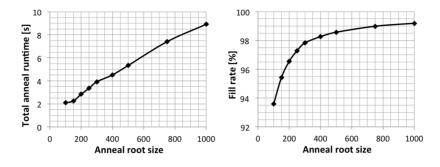

In Chapters 4, 5 and 6 we give more detailed background on the packing, placement and routing problem respectively and describe new algorithms applied to these problems. A hierarchical multi-threaded partitioning algorithm for packing is described in Chapter 4. A steepest gradient descent based algorithm for placement is explained in Chapter 5 and in Chapter 6 we introduce a connection-based routing algorithm with a more fine grained negotiated congestion mechanism which allows to save routing runtime.

In Chapter 7 we describe the placement and routing algorithms we developed for compiling parameterized FPGA configurations for the dynamic reconfiguration of the FPGA's routing network. We also investigated a new FPGA architecture with logic gates in the routing nodes and in Chapter 8 we describe the sizing results, the technology mapping and packing algorithms we developed to test the architecture.

#### 1.5 Publications

#### **Journal Papers**

- Dries Vercruyce, Elias Vansteenkiste and Dirk Stroobandt. "How preserving Design Hierarchy during Multi-threaded packing can improve Post Route Performance". IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, In review.

- Tom Davidson, Elias Vansteenkiste, Karel Heyse, Karel Bruneel and Dirk Stroobandt. "Identification of Dynamic Circuit Specialization Opportunities in RTL Code". ACM Transactions on Recon-

figurable Technology and Systems, Vol. 8, Issue 1, No. 4, 2015, 24 pages

- D. Pnevmatikatos, K. Papadimitriou, T. Becker, P. Böhm, A. Brokalakis, Karel Bruneel, C. Ciobanu, Tom Davidson, G. Gaydadjiev, Karel Heyse, W. Luk, X. Niu, I. Papaefstathiou, D. Pau, O. Pell, C. Pilato, M.D. Santambrogio, D. Sciuto, Dirk Stroobandt, T. Todman and Elias Vansteenkiste. "FASTER: Facilitating Analysis and Synthesis Technologies for Effective Reconfiguration". *Microprocessors and Microsystems*, Volume 39, Issues 4–5, June–July 2015, Pages 321–338.

- Elias Vansteenkiste, Brahim Al Farisi, Karel Bruneel and Dirk Stroobandt. "TPaR: Place and Route Tools for the Dynamic Reconfiguration of the FPGA's Interconnect Network". *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 33, Issue 3, 2014, Pages 370–383.

#### Conference Papers with International Peer Review

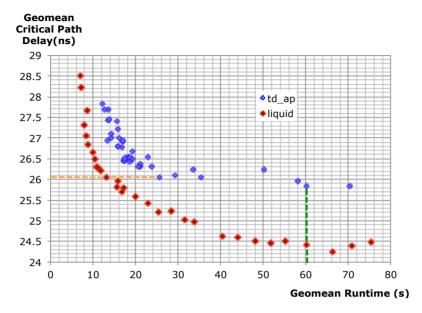

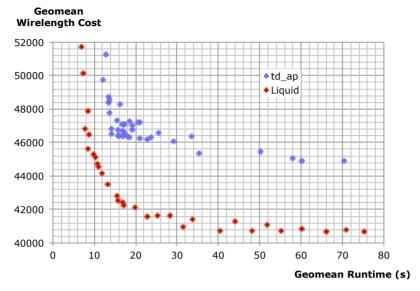

- Elias Vansteenkiste, Seppe Lenders and Dirk Stroobandt. "Liquid: Fast Placement Prototyping Through Steepest Gradient Descent Movement". In 26th International Conference on Field Programmable Logic and Applications, Proceedings (FPL2016), 2016. Pages 49-52

- Dries Vercruyce, **Elias Vansteenkiste** and Dirk Stroobandt. "Runtime-Quality Tradeoff in Partitioning Based Multithreaded Packing". In *26th International Conference on Field Programmable Logic and Applications, Proceedings (FPL2016)*, 2016. Pages 23-31

- Elias Vansteenkiste, Alireza Kaviani and Henri Fraisse. "Analyzing the divide between FPGA academic and commercial results". In *International Conference on Field-Programmable Technology, Proceedings (ICFPT2015)*. Pages 96-103 (nominated for Best Paper Award)

- Berg Severens, Elias Vansteenkiste and Dirk Stroobandt. "Estimating Circuit Delays in FPGAs after Technology Mapping". In 25th International Conference on Field Programmable Logic and Applications, Proceedings (FPL2015), 2015, Pages 380 383

- Alexia Kourfali, Elias Vansteenkiste and Dirk Stroobandt. "Parameterised FPGA Reconfigurations for Efficient Test Set Genera-

- tion". In International Conference on ReConFigurable Computing and FPGAs, Proceedings (ReConFig2014), 2014, 6 Pages

- Brahim Al Farisi, Elias Vansteenkiste, Karel Bruneel and Dirk Stroobandt. "A Novel Tool Flow for Increased Routing Ronfiguration Similarity in Multi-mode Circuits. In IEEE Computer Society Annual Symposium on Very-Large-Scale Integration, Proceedings (VLSI2013), 2013. Pages 96-101

- Elias Vansteenkiste, Karel Bruneel and Dirk Stroobandt. "A Connection-based Router for FPGAs". In *International Conference on Field-Programmable Technology, Proceedings (ICFPT2013)*, Pages 326 329.

- Karel Heyse, Tom Davidson, Elias Vansteenkiste, Karel Bruneel and Dirk Stroobandt. "Efficient Implementation of Virtual Coarse Grained Reconfigurable Arrays on FPGAs". In 23rd International Conference on Field Programmable Logic and Applications, Proceedings (FPL2013), 2013, 8 pages

- Karel Heyse, Tom Davidson, Elias Vansteenkiste, Karel Bruneel and Dirk Stroobandt. "Efficient Implementation of Virtual Coarse Grained Reconfigurable Arrays on FPGAs". In 50th Design Automation Conference (DAC2013), 2013, Pages 1-8

- Elias Vansteenkiste, Karel Bruneel and Dirk Stroobandt. "Maximizing the Reuse of Routing Resources in a Reconfiguration-aware Connection Router". In 22nd International Conference on Field Programmable Logic and Applications, Proceedings (FPL2012), 2012, Pages 322 329

- Elias Vansteenkiste, Karel Bruneel and Dirk Stroobandt. "A Connection Router for the Dynamic Reconfiguration of FPGAs". In Lecture Notes in Computer Science: 8th International Symposium on Applied Reconfigurable Computing (ARC2012), 2012, Pages 357 364

## 2 Background

This chapter contains background information about FPGAs. The architecture of an FPGA and the CAD tools that are used to compile a design to an FPGA configuration are described first. Subsequently the history of the FPGA is described to put the work in this thesis in perspective and explain the current state of the FPGA architecture and tools. The goal of this chapter is to provide a solid foundation for the following chapters. Throughout the background you will find references to all the other chapters in this thesis.

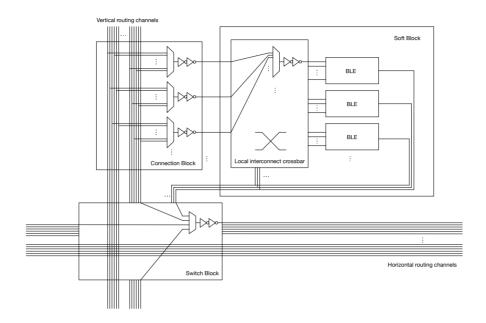

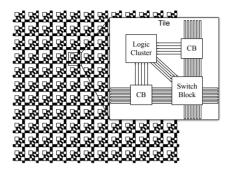

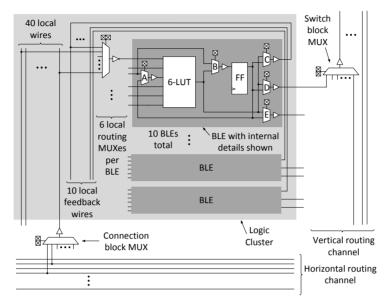

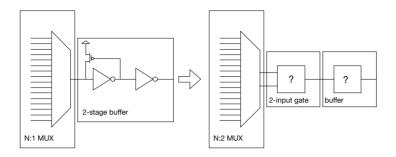

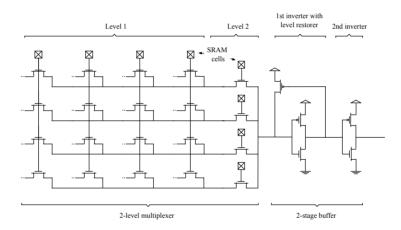

#### 2.1 FPGA Architecture

In this section, a basic overview of a typical FPGA architecture and the state of commercial FPGA architectures is described. An FPGA consists of a large number of functional blocks embedded in a programmable interconnection network. The functional blocks can roughly be divided into a number of categories: Input/Output blocks, hard blocks and soft blocks. We start with the low level building blocks of the FPGA and follow a bottom-up approach to explain the architecture. The description starts with the basic building blocks and ends with the high-level overview of the FPGA architecture.

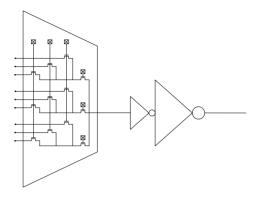

#### 2.1.1 Low Level Building Blocks

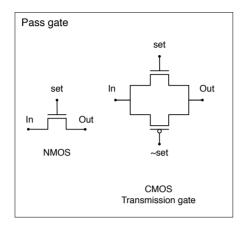

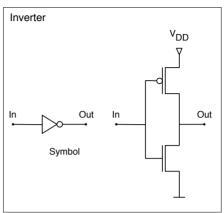

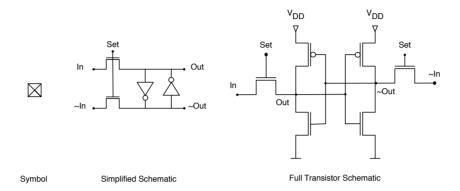

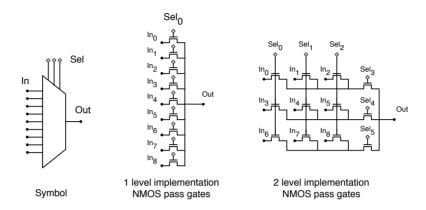

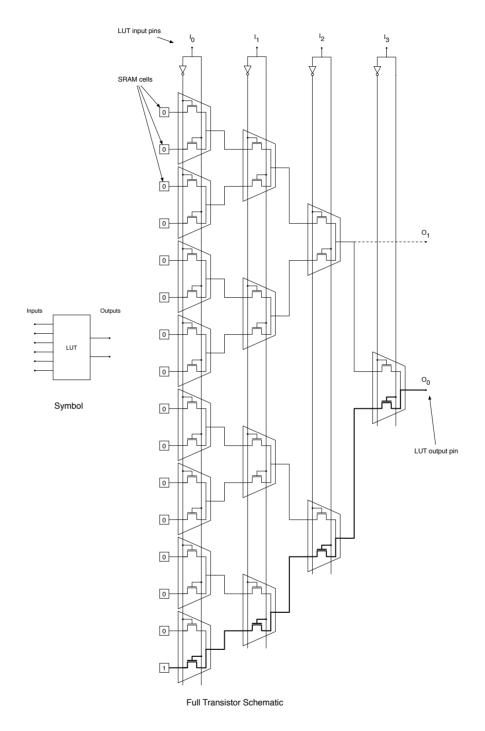

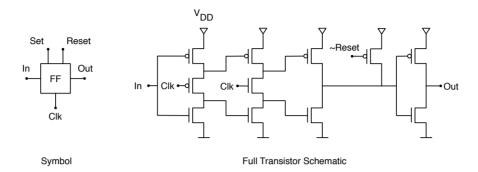

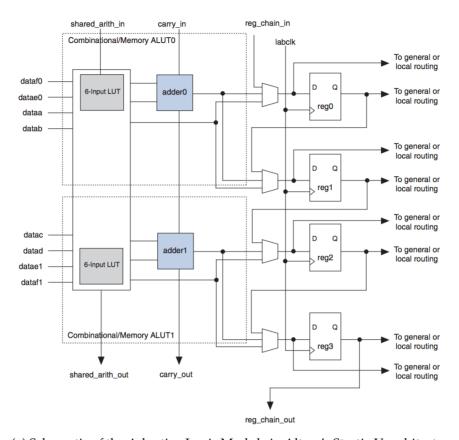

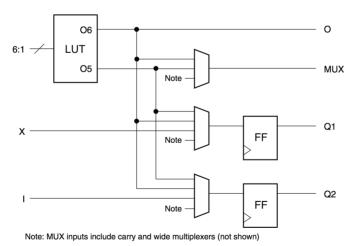

Figure 2.1: The schematics for the pass gate and inverter. Both are basic building blocks of an FPGA.

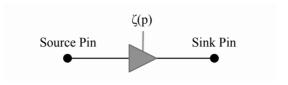

**Pass Gates** are basic switches, with three pins, the input, output and on/off pin. If it is turned on, it passes the logic level from the input pin to the output pin. If the switch is turned off, then the input and output pin are disconnected by a high impedance. It is a basic element used to build multiplexers and SRAM cells. Pass gates can be implemented using an n-type MOSFET (NMOS) or p-type MOSFET (PMOS). NMOS pass gates are good at passing a logic low signal but they are bad at passing a logic high. Similarly PMOS pass gates are good at passing a logic high but bad at passing a logic low. This causes problems for chained pass gates. The logic signal degrades at each stage and needs to be restored. Instead of restoring the signal, another common solution is to combine the advantages of the NMOS and PMOS pass gate by connecting them in parallel. This is called a transmission gate. The downside here is that two transistors are used to produce a transission gate. Figure 2.1 shows the symbol used for a NMOS pass gate and the schematic for the transmission gate.

**Inverters** have only two pins. The inverter outputs the complement of the input signal. The schematic of an inverter is depicted in Figure 2.1. The input signal drives the gates of an NMOS and a PMOS. The NMOS is switched to pass on the logic low level if the input signal is high and the PMOS passes the logic high level if the input signal is low. The inverter is the preferred circuit to strengthen signals because the NMOS and PMOS are switched in the way their advantages are ex-

Figure 2.2: Schematics for the SRAM cell.

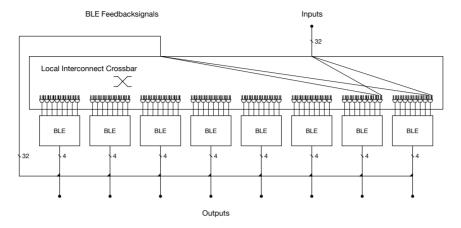

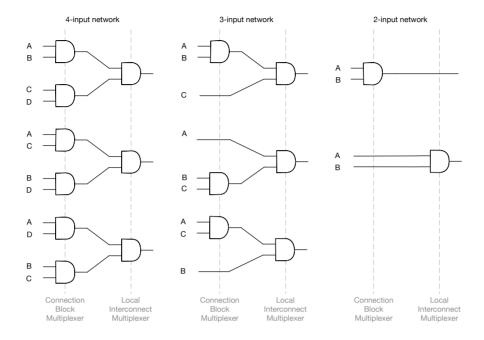

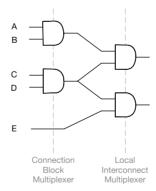

ploited. The PMOS is good at passing a logic high and the NMOS is good at passing a logic low. Inverters are used to strengthen a weakened signal and reduce the rise/fall times for signals that have to drive a large downstream capacitance. Typically two or more inverters are cascaded to form a chain buffer.