Electronic Theses and Dissertations

Retrospective theses

1998

# Compiling Prolog to Logic-inference Virtual Machine

Wang, Yifei (Fred)

http://knowledgecommons.lakeheadu.ca/handle/2453/3087 Downloaded from Lakehead University, KnowledgeCommons

#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# UMI

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permissiom.

· •

.

È

# Compiling Prolog to Logic-Inference Virtual Machine

by

Yifei (Fred), Wang (C)

A thesis submitted to the Faculty of Research and Graduate Studies in partial fulfillment of the requirements for the degree of

> Master of Science in Mathematical Sciences

Department of Computer Science School of Mathematical Sciences Lakehead University Thunder Bay, Ontario

September 10, 1998

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-52084-6

### ABSTRACT

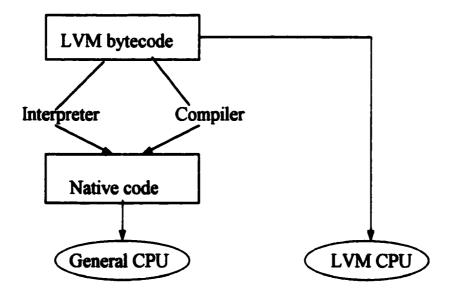

The Logic-inference Virtual Machine (LVM) is a new Prolog execution model consisting of a set of high-level instructions and memory architecture for handling control and unification. Different from the well-known Warren's Abstract Machine [1], which uses Structure Copying method, the LVM adopts a hybrid of Program Sharing [2] and Structure Copying to represent first-order terms. In addition, the LVM employs a single stack paradigm for dynamic memory allocation and embeds a very efficient garbage collection algorithm to reclaim the useless memory cells. In order to construct a complete Prolog system based on the LVM, a corresponding compiler must be written.

In this thesis, a design of such LVM compiler is presented and all important components of the compiler are described. The LVM compiler is developed to translate Prolog programs into LVM bytecode instructions, so that a Prolog program is compiled once and can run anywhere.

The first version of LVM compiler (about 8000 lines of C code) has been developed. The compilation time is approximately proportional to the size of source codes. About 80 percent of the time are spent on the global analysis. Some compiled programs have been tested under a LVM emulator. Benchmarks show that the LVM system is very promising in memory utilization and performance.

# **ACKNOWLEDGMENTS**

I would like to express my thanks and appreciation to my supervisor, Professor Xining Li, for his guidance, advice and help.

I would like to thank to my wife (Huai-Rong, Hu) and my mother (Xue-Mei, Sun) for their understanding, encouragement and support.

Also I am grateful to the Natural Science and Engineering Council of Canada for the financial support.

Finally, I would like to thank my external examiner Dr. A. Nayak (Carleton University) and internal examiner Professor L.D. Black (Lakehead University) for their comprehensive comments.

ŀ

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

# List of Figures and Tables

.

| Figure 1.1 Structure of LVM compiler                        | 2  |

|-------------------------------------------------------------|----|

| Figure 2.1 A tagged cell                                    | 5  |

| Figure 2.2 Term representation in Structure Copying         | 5  |

| Figure 2.3 Term representation in Structure Sharing         | 6  |

| Figure 2.4 WAM data areas                                   | 7  |

| Figure 2.5 Environment frame in WAM                         | 7  |

| Figure 2.6 Choice point frame in WAM                        | 8  |

| Figure 2.7 Term representation in Program Sharing           | 9  |

| Figure 2.8 LVM memory architecture                          | 10 |

| Figure 2.9a V-frame format in LVM                           | 11 |

| Figure 2.9b C-frame format in LVM                           | 12 |

| Figure 2.9c B-frame format in LVM                           | 12 |

| Figure 3.1 Interface to the lexical analyzer                | 19 |

| Figure 3.2 Role of parser in the compiler                   | 20 |

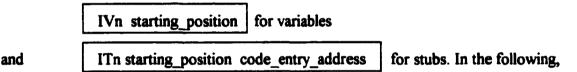

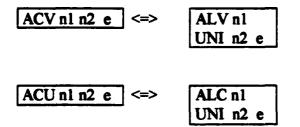

| Figure 4.1 Order of stub and variable allocation on stack   | 22 |

| Figure 5.1 Simulation of expression evaluation              | 48 |

| Figure 8.1 Memory layout in case of BB below AF             | 76 |

| Figure 8.2 Memory layout for BB above AF                    | 76 |

| Figure 9.1 Execution model of LVM bytecode                  | 81 |

| Table 3.1 Specifiers of operators                           | 17 |

| Table 3.2 Predefined operator table                         | 17 |

| Table 4.1 Code segment labeling rules                       | 21 |

| Table 4.2 Stack cell assignment and offsets of objects      | 29 |

| Table 4.3 LVM unification instructions                      | 32 |

| Table 4.4 Memory layout of objects for p(+,-,+)/3 clause    | 33 |

| Table 5.1 Integer arithmetic instructions                   | 46 |

| Table 5.2 Data load/store instructions                      | 47 |

| Table 5.3 Branching instructions                            | 49 |

| Table 5.4 Special comparison instructions                   | 50 |

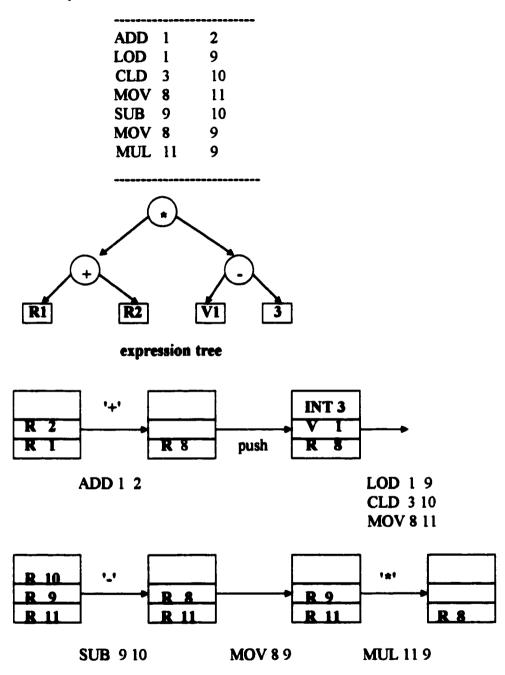

| Table 5.5 Variable and stub initialization instructions     | 51 |

| Table 5.6 Object allocation for p(+,-)/2 clause             | 51 |

| Table 5.7 Opcode matrix of list initialization instructions | 52 |

| Table 5.8 Memory allocation for p(-,-)/2                    | 54 |

| Table 9.1 Execution time (sec)                              | 82 |

iv

# Contents

| Acceptance Sheet                                           | i  |

|------------------------------------------------------------|----|

| ABSTRACT                                                   | ii |

| ACKNOWLEDGMENTS                                            |    |

| List of Figures and Tables                                 | iv |

|                                                            |    |

| Chapter 1. Introduction                                    | 1  |

| 1.1 Logic Programming and Prolog                           | 1  |

| 1.2 Motivation                                             | 1  |

| 1.3 Prolog Compiler Design                                 | 2  |

| 1.4 Outline                                                | 4  |

| Chapter 2. Overview of Prolog Implementation               | 5  |

| 2.1 Structure Term Representation                          | 5  |

| 2.2 Warren Abstract Machine (WAM)                          | 6  |

| 2.3 Logic-Inference Virtual Machine (LVM)                  | 8  |

| Chapter 3. Lexical and Syntax Analysis                     | 13 |

| 3.1 Syntax of Prolog Text                                  | 13 |

| 3.2 Token Generator                                        | 19 |

| 3.3 Syntax Analysis                                        | 19 |

| Chapter 4. Clause Analysis and Translation                 | 21 |

| 4.1 Structure Argument Representation and Flattening       | 21 |

| 4.2 Variable Classification and Index Calculation          | 24 |

| 4.3 Register Allocations and Conflict in Parameter Passing | 29 |

| 4.4 Unification Code of a Clause                           | 31 |

| 4.5 Control Code of a Clause                               | 34 |

| 4.5.1 Fact                                                 | 35 |

| 4.5.2 Chain Call                                           | 37 |

| 4.5.3 Rule                                                 | 38 |

| 4.5.4 Query                                                | 40 |

\*

ţ

| Chapter 5. Built-in Predicates, Arithmetic Expressions and Initializations | 42 |

|----------------------------------------------------------------------------|----|

| 5.1 Built-in Predicates                                                    | 42 |

| 5.2 Cut                                                                    | 43 |

| 5.3 Arithmetic Expressions                                                 | 45 |

| 5.3.1 Arithmetic Operations                                                | 46 |

| 5.3.2 Register Allocation                                                  | 47 |

| 5.3.3 Arithmetic Comparison                                                | 49 |

| 5.4 Initializations                                                        | 50 |

| Chapter 6. Predicate Determinacy Analysis and Indexing                     | 55 |

| 6.1 Last Argument Dispatching                                              | 55 |

| 6.2 Guarded Dispatching                                                    | 58 |

| 6.3 Nondeterministic Predicates                                            | 62 |

| Chapter 6. Compilation Optimization                                        | 65 |

| 7.1 Variable, Stub and SCI Object Initialization Delay                     | 65 |

| 7.2 Unnecessary Unification Instruction Elimination                        | 66 |

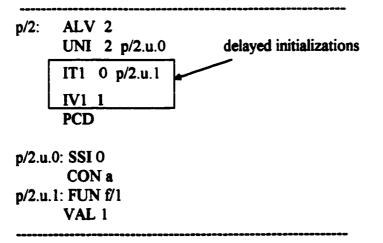

| 7.3 Stub and Variable Initialization Instruction Compression               | 67 |

| 7.4 Combination of Frame Allocation and Unification Instructions           |    |

| 7.5 Special Optimization                                                   | 69 |

| Chapter 8. Assistance to Garbage Collection                                | 73 |

| 8.1 Survey of Garbage Collection                                           | 73 |

| 8.2 Chronological Garbage Collector in the LVM                             | 75 |

| 8.3 Garbage Level Estimation                                               | 77 |

| 8.4 GC Root Set Collection and GC Point Setting                            | 78 |

| Chapter 9. Conclusions                                                     | 81 |

| 9.1 LVM Performance                                                        | 81 |

| 9.2 Compiler Features                                                      | 83 |

| 9.3 Future Work                                                            | 84 |

| Appendix A. LVM Instruction Set                                            | 85 |

| Appendix B. LVM Built-in Instructions                                      | 88 |

| Bibliography                                                               | 91 |

•

## **Chapter 1. Introduction**

#### 1.1 Logic Programming and Prolog

The motivation of logic programming is to separate the problem solving process into two parts: (1) a logical specification and (2) execution description [5]. The programmers only focus on the logic specification of the problem. The logic systems automatically provide the execution control. Therefore, logic programming is a higher level of abstraction than the imperative programming in languages like Ada, C or Pascal.

A logic program is a set of logic sentences (clauses) written in Horn clause logic. A group of clauses with the same name and arity (number of arguments), called a predicate is used to define a relation, like a procedure in the imperative languages. Hence, a logic program can be defined as a set of predicates.

Logic programming has four main features as follows:

(a) Logic variable can be instantiated only once.

(b) Logic variable can hold value of any type, which is so called dynamic typing.

(c) Unification is a pattern matching operation for binding variables, building and accessing compound term.

(d) Backtracking is a searching operation for finding out all satisfying clauses in a predicate.

Prolog is an approximate logic programming language with two constraints on its implementation model for the balance between implementation efficiency and logical completeness. They are:

(a) The clause listed lexically ahead in a predicate is tried first.

(b) The goals in each clause are invoked from left to right.

Prolog has been applied in a variety of fields like expert systems, natural language understanding, theorem proving, deductive databases, CAD tool design, compiler writing, and applications of artificial intelligence with coded knowledge.

#### **1.2 Motivation**

Many Prolog systems are often an order of magnitude slower than imperative language systems like C. To optimize system performance, a heavy global static analysis based on abstract interpretation has been performed in some high performance Prolog compilers, such as Aquarius [3] and Parma [4]. But all these Prolog systems are built on the principle of Warren Abstract Machine (WAM) execution model [1].

To achieve the same goal, we approach the problem in a different way. A new Prolog system based on a new abstract machine, called Logic-Inference Virtual Machine

1

ŀ

(LVM), has been developed. In the next chapter, the important features of WAM and LVM will be briefly described and compared. The LVM adopts a hybrid of Program Sharing and Structure Copying to represent first-order terms. Also, the LVM employs a single stack paradigm for dynamic memory allocation and embeds a very efficient garbage collection algorithm to reclaim the useless memory cells. In order to construct a complete Prolog system based on the LVM, a corresponding compiler has to be written.

#### **1.3 Prolog Compiler Design**

The main objective of this thesis is to write a compiler for the LVM system. The LVM compiler (LVMC) is to translate Prolog source code into LVM bytecode. The driving force in the LVMC design is to encode as many LVM features as possible. To generate the high quality of LVM bytecode, the compiler implements several optimizations and carefully considers the code execution performance. The structure of the LVM compiler is shown in Figure 1.1.

Figure 1.1 Structure of LVM compiler

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

The LVMC consists of four phases: (1) lexical and syntax analysis, (2) global analysis, (3) clause analysis and code generation, and (4) post-optimization and code output.

In the phase (1), source code is converted to parse trees. Meanwhile the syntactic errors in source code are detected.

In global analysis, the LVMC will collect or generate the argument input mode, then reorder the last arguments of clauses if necessary, and further extract determinacy information of each predicate as well as determine garbage estimation. If a predicate has the mode declaration, the mode analysis of this predicate will be ignored. Although LVM uses the last argument as the first-order discriminator for the purpose of partial unification and control dispatching, there is no constraint on the programmer's programming style. The compiler will dynamically reorder the clause arguments in the reference to LVM based on the mode information. During the determinacy analysis, redundant or unreachable clauses are eliminated.

The clause analysis is the key component of the LVMC. The clause analysis involves the variable analysis, frame allocation and register allocation. The variable analysis has three major tasks:

(a) Each variable must be classified into one of two types: stack variable and register variable. A stack variable is one, which resides on stack and possibly outlives the procedure call. A register variable is a temporary variable, which does not survive across procedure calls. Register variables are mainly used in fact clauses, arithmetic computation or deterministic clause chain-calls. However, they must not occur in any constructor.

(b) The status of variables inside all arguments must be analyzed. A variable may be used in two ways: uninitialized (V-type) or instantiated (L-type). In order to eliminate the unnecessary dereferencing or trailing operations, the V-type variables are bound by destructive assignment.

(c) Since a stack variable may be referenced by several structural terms, the different address offsets of this variable must be calculated according to the stub location in stack.

To speed up the arithmetic computation and term unification of deterministic clauses, soft registers must be scheduled carefully. Register allocation is done using a simple algorithm and register conflict is avoided.

The code generation for each clause is straightforward based on four basic formats. But the initialization of some constructor objects can be delayed until the unification. For a special set of predicates, a special translation algorithm is applied to produce optimized code.

In the final phase of LVMC, post-optimization on the intermediate code is done before the final LVM bytecode output. For example, several consecutive instructions are compacted into one instruction. The arithmetic computation strength is reduced as much as possible. Redundant instructions are removed.

#### 1.4 Outline

The rest of the thesis is organized as follows: Chapter 2 gives a brief overview of Prolog term representation methods: Structure Sharing, Structure Copying and Program Sharing. Then, two virtual machines: WAM and LVM are compared. Chapter 3 describes the lexical and syntax analysis of the LVM compiler. Chapter 4 presents the clause analysis and translation methods. Chapter 5 discusses how to handle arithmetic operations and built-in predicates, and how to specify the initialization instructions. Chapter 6 shows how to use the indexing technique to generate bytecode for a predicate. Chapter 7 discusses some optimizations on the generated bytecode. It includes a special optimization on a set of predicates. Chapter 8 describes how to assist the LVM memory management system at compilation time. Chapter 9 gives conclusions.

# **Chapter 2. Overview of Prolog Implementation**

#### 2.1 Structure Term Representation

The term representation is one of the core parts of any Prolog system. The term representation determines the unification implementation technique in Prolog. Since Prolog is a dynamically typed language, the type and value of a variable is determined only at run time. Therefore, a variable cell is represented in general by a tagged value cell as shown in Figure 2.1.

|     | A LA L LTT |

|-----|------------|

|     | VALUE      |

| ing |            |

|     |            |

Figure 2.1 A tagged cell

All Prolog terms are classified into three basic types: variable, constant and structure term. A variable is further categorized into two types: unbound or bound. An unbound variable is self-reference pointer with REF as its tag. In our current LVM system, there are three kinds of constant terms, which are represented as follows

| INT | valuel |

|-----|--------|

| CON | value2 |

| NIL |        |

where INT denotes an integer, CON a string and NIL a null list.

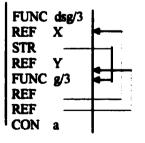

At the abstract level, two methods are used to represent a structure term, that is, structure copying (SC) and structure sharing (SS). The structure copying technique was introduced by Maurice Bruynooghe [6] and Christopher Mellish [7]. In SC Prolog systems, all terms of different types are fitted into the size of a machine word/register (a tagged value cell). When a variable comes to stand for a structure term during unification, the entire structure including all arguments is copied to a new allocated heap. After the copying, the information about the structure name (functor) and arity becomes indirectly accessible, the knowledge of this structure instance is concealed. For example, the term of dsg(X, g(X, Y, a), Y) could be represented in Figure 2.2 by the SC method

Figure 2.2 Term representation in Structure Copying

The SS method was first introduced by Boyer and Moore [8] and used in earlier

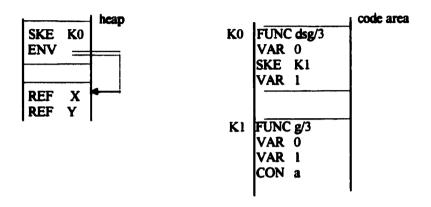

Prolog systems. The SS method takes advantage of the fact that all different instances of a same structure term share a single prototype and differ only in their variable bindings. Therefore, a structure term is divided into two components: skeleton and environment. The skeleton contains the constants and the offsets of environment. The skeleton is stored in the code area. The environment contains the variables and is stored in the heap. Two pointers are needed to represent a structure term, one to the skeleton and other to the environment. Two successive machine words have to be allocated to instance a structure term. For example, the term of dsg(X, g(X, Y, a), Y) could be represented in Figure 2.3 by the SS method

Figure 2.3 Term representation in Structure Sharing

Both structure term representation methods have been thoroughly investigated [6,7]. In general, the SS method is faster than the SC method in creating terms, but the SC method is faster in accessing and unifying terms because the SS method needs more time in decoding skeletons. Also the SC method consumes less memory than the SS method. Only the earlier Prolog system [9] used the SS method. Now the structure copying is the standard implementation method in various Prolog systems. In 1983, David Warren [1] presented a new abstract Prolog instruction set, now called Warren Abstract Machine (WAM), which adopts the SC method as the basic component for the efficient structure term unification. After 1983, most of high performance Prolog systems have been developed on WAM or WAM-like abstract machine for further efficiency improvement.

#### 2.2 Warren Abstract Machine (WAM)

Normally, a Prolog abstract machine is divided into two components as follows:

#### An abstract machine = instruction set + memory model

#### 2.2.1 Memory Model of WAM

The stack-based memory model of WAM is shown in Figure 2.4. The local stack is used to store the environment and choice point frames. The structure terms are allocated on the global stack, called heap. The trail is used to save the address of bounded variables that have to be unbound during backtracking. The PDL (push-down list) is used to perform the unification of nested compound terms.

Figure 2.4 WAM data areas

#### **2.2.2 Unification and Parameter Passing**

The WAM embeds the unification instructions within the control sequences. Therefore, a single engine is employed for both control and unification. Two steps carry out the unification: (a) the copying of the arguments of the calling goal into arguments registers, and (b) the unification of the arguments registers with the arguments of the head of the called clause. Three types of instructions {PUT, GET, UNIFY} are available to handle unification. The instruction {UNIF} is executed in two modes. In the write mode, a new structure is created, while in the read mode the true unification is performed. As mentioned before, the SC method conceals the skeleton information of a structure term, a general unification algorithm is carried out when both objects are instances of the same structure term. For increasing the efficiency, a unification call is encoded into a sequence of special unification instructions if one of operands is known at compilation time.

#### 2.2.3 Backtracking and Stack Management

The WAM uses two kinds of frames to store the information associated with predicate calls, that is, environment frame and choice-point frame. The environment frame has the following fields:

| Parent | parent environment frame   |

|--------|----------------------------|

| СР     | continuation program point |

| Y1,,Ym | permanent variables        |

Figure 2.5 Environment frame in WAM

An environment frame is pushed on the (local) stack before any deterministic clause is executed.

The choice point frame is used to handle the backtracking of a nondeterministic predicate, which has multiple candidates of clauses to try. The choice point frame has the following fields:

| BP     | alternative program point  | _ |

|--------|----------------------------|---|

| СР     | continuation program point |   |

| Е      | current environment frame  |   |

| B      | most recent choice point   |   |

| TR     | top of trail               |   |

| Н      | top of heap                |   |

| X1,,Xn | argument registers         |   |

Figure 2.6 Choice point frame in WAM

After a new choice point frame is pushed on the stack, the choice point pointer is set to point to the new choice point so that a linked chain of choice points is formed. To increase the WAM efficiency, the clause indexing including conditional branching is necessary to avoid the creation of choice points if possible.

The WAM simulates the conventional procedure call to control Prolog program execution. The two steps of parameter passing result in a bottleneck of its performance. The argument registers have to be saved and restored for the backtracking. The information associated with a predicate call is stored in possibly two frames. A full tail recursion elimination is difficult to implement. Two alternatives to the WAM have been developed. The Vienna Abstract Machine (VAM) [11,12] eliminates the parameter passing bottleneck of WAM by performing the unification of each pair of a goal and a head argument in a single step without the register interface. Another abstract machine, called ATOM (yet Another Tree-Oriented Abstract Machine) [13,14] uses one frame for each predicate call and arguments are passed directly into stack frames. These new abstract machines successfully minimize the inefficiencies of WAM.

#### 2.3 Logic-Inference Virtual Machine (LVM)

Apart from exploring the efficiency of parameter passing and frame allocation, the new abstract machine, called Logic-Inference Virtual Machine (LVM), blends a new structure term representation method - Program Sharing (PS) with SC to represent and handle structure terms. The unification instructions are defined and implemented in a totally different way. A brief introduction to LVM is given in the following.

#### 2.3.1 Program Sharing

Program Sharing is a new method of Prolog structure term representation. This method was introduced by X. Li[2,15,16]. The PS method originating from SS method shares the same idea that the static information of a structure term is separated from its dynamic environments. But the PS method has three main features different from SS:

(1) A structure skeleton is stored in the code area as executable code or a segment of a program. There is no data in a Prolog program. All terms in a Prolog program are compiled into instruction code.

(2) Only one pointer (called a structure code stub) is used to solve the two-cell problem in SS method. The stub content is the entry of a structure code and the stub address is the environment base for executing the structure code. There are three types of structure code stubs: DCI (direct copied instance), SSI (static shared instance) and SCI (static copied instance).

(3) The environment variable indices in the structure code are calculated relative to each stub. In a nested structure term, a variable with multiple occurrences has multiple index values. In SS method, a variable has a unique index value, and variable indices are calculated against a common frame base.

For example, the term of dsg(X, g(X, Y, a), Y) with (-) type of input mode is represented in Figure 2.7 by the PS method.

Figure 2.7 Term representation in Program Sharing

Where {VAR, FUNC, SSI and CON} are unification instructions. The variable (X) has the indices of 2 relative to the stub <, K0> and 1 relative to another stub <, K1>. Similarly, the variable (Y) has two indices (3,2) relative to each stub, respectively. These relative indices are specified in the unification instruction code shown in Figure 2.7. For the structure unification, by accessing a stub we have the entry to the code segment, which defines the structure unification instruction code, and by the stub address we get the environment, which will be consulted to access stack variables and nested stubs.

The PS method has the advantage of both SC and SS methods. It represents terms of different types in the size of a machine word, and also translates the static information into executable instruction code and spends much less overhead for handling dynamic environment.

#### 2.3.2 LVM Architecture and Instruction Set

LVM is a virtual machine based on the mixture of PS and SC methods. The choice between PS and SC to represent a structure term depends on the input mode of the term. For the efficiency, the LVM strongly supports and encourages mode declaration. The mode information of head arguments of clauses can be obtained from the user declaration or through a global analysis [18]. In our current version of LVM, four types of input modes of arguments are defined. They are (-) for out, (?) for in\_or\_out, (+) for in, (++) for in\_and\_ground. If a head argument is a compound term, all nested subterms inherit the same mode. For simplicity, all structure arguments in goals are assumed to have (?) mode.

The LVM classifies structure terms into selectors and constructors based on their modes. A structure term is a selector if it can't be bound to any variable outside the clause; otherwise, it is a constructor. Therefore, structure terms with (+) mode are always translated as selectors, and with (-) or (?) mode as constructors. Furthermore, all ground structure terms are treated as selectors, regardless of their input modes. A selector is represented by an instruction <DCI, code\_entry>. Since we experience the high efficiency of list manipulation in WAM, LVM uses PS for all non-list constructors and SC for all list constructors. Correspondingly, two more unification instructions are provided. <SSI, stub\_offset> represents a static shared constructor of a non-list term. <SCI, stub\_offset> represents a static copied instance of a list term.

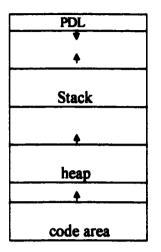

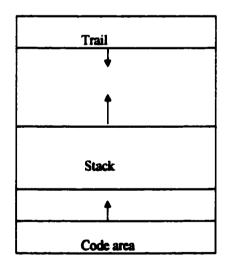

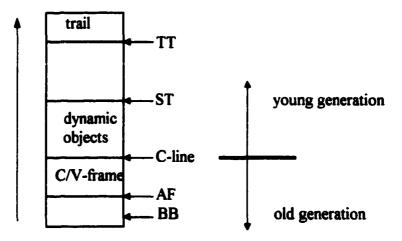

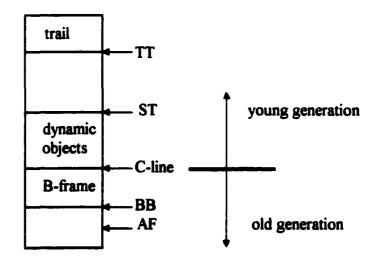

The LVM memory architecture is shown in Figure 2.8. The major difference from the WAM memory layout in Figure 2.4 is that LVM uses one stack to hold both dynamic objects and control frame information. Also the PDL stack is eliminated.

Figure 2.8 LVM Memory Architecture

Appendix A shows the complete instruction set of LVM. They cover unification, arithmetic computation, branching, frame allocation and object initialization. The details were given in X. Li's technical report [17].

#### 2.3.3 Other Features of LVM

Except that LVM uses PS and SC methods to represent structure terms, LVM has other features in the following aspects:

#### (1) Unification and Parameter Passing

LVM consists of two coordinating processors: a 1P processor for control and a 2P processor for unification. The 2P engine sequentially executes pairwise unification instruction codes. It fetches two instructions simultaneously. Since the type of each operand is known at compilation time and LVM sees terms as executable instructions, the unification algorithm is much cheaper without loss of type information. The LVM compiler generates code segments for the control and unification, which can be loaded in separate locations. For example, with a caller of f(Y,a) and a callee of f(X,X), the unification codes for the caller are:

#### VAR Y

CON value,

and unification codes for the callee are:

#### VAR X VAR X.

The 2P engine first unifies two unification instructions:  $\{VAR \ Y\}$  and  $\{VAR \ X\}$ , the variable Y becomes bound to the variable X. Then, it fetches next two unification instructions  $\{CON \ value\}$  and  $\{VAR \ X\}$ . The constant  $\{value\}$  is directly assigned to the variable X. Therefore after the unification, the variable Y becomes a constant cell.

LVM eliminates the parameter passing bottleneck by unifying caller and callee arguments in one step. Unlike the Vienna abstract machine  $(VAM_{2P})$  [11,12], the LVM unification instructions are neutral. Also LVM delays the structure full unification until it is necessary in order to enhance the system efficiency.

#### (2) Backtracking and Stack Management

LVM implements procedure invocation and backtracking by allocating different chains of control frames on the stack. There are three kinds of control frames in the LVM: V-frame, C-frame and B-frame. Separation of V-frame from C-frame is for the minimization of memory usage and the speed up of frame reallocation.

(a) V-frame: It only consists of dynamic objects without control information. It is used for fact or chain-call clauses involving constructors.

| Variables |  |

|-----------|--|

| Stubs     |  |

Figure 2.9a V-frame format in LVM

(b) C-frame: It has three cells for control information and other cells for dynamic objects. It is used for any clause with more than one user defined goals in its body.

| Varia | bles                       |

|-------|----------------------------|

| Stubs | J                          |

| ST:   | current stack top          |

| CP:   | continuation program entry |

| AF:   | continuation frame         |

Figure 2.9b C-frame format in LVM

(c) B-frame: It contains all information needed for backtracking shown in Figure 2.9c. A B-frame is allocated at a new choice point.

| NT:         | alternative program entry  |

|-------------|----------------------------|

| TT:         | trail top                  |

| GP:         | caller's unification code  |

| GF:         | caller's unification frame |

| <b>R</b> 0: | R0 register                |

| CP:         | continuation program entry |

| AF:         | continuation frame         |

| BB:         | most recent choice point   |

Figure 2.9c B-frame format in LVM

(3) Garbage Collection and Memory Reclaim

Since LVM uses one stack to hold both frames and dynamic objects, an efficient garbage collection (GC) algorithm is very important to the LVM implementation. In Chapter 9, a chronological garbage collection algorithm will be discussed. The LVM needs the compiler to generate GC instructions to tell the execution system when, where and what should be collected, so that garbage estimation must be carried out in the earlier phase of compilation. The experimental LVM system showed that the GC algorithm has very low runtime overhead.

In summary, several advantages of the current LVM are:

(a) Memory usage is minimized for the structure term representation.

(b) It is easy to allocate/reallocate stack frames.

(c) The environment management is simple due to one stack policy.

(d) There is no cost in parameter passing from a stack frame to another frame.

(e) During backtracking, it is unnecessary to check binding directions, such as from local objects to global objects and from young generation to old generation, and the trailing/detrailing operation is cheap.

(f) A natural generation line of procedure calls exists for the implementation of garbage collection.

# **Chapter 3. Lexical and Syntax Analysis**

In this chapter, the first phase of the LVMC, which is the lexical analysis and syntax analysis of Prolog source code, is described. A simple error handler is used in the LVMC. When this phase is successful, a parse tree is generated for each clause. This chapter is organized as follows. First, the syntax of Prolog texts in standard Prolog is described. Then, the detailed method of lexical analysis and syntax analysis is shown.

#### 3.1 Syntax of Prolog Text

A Prolog text is a sequence of directives and clauses in an order which is specified by directives. Directives and clauses are represented by terms. In standard Prolog [19], terms are written in function notation. Therefore, the structure of a term is specified without any ambiguity. The syntax of terms defines the syntactic rules for writing terms correctly. Here the syntax is presented using the context free grammar. The context free grammar has the form:

nonterminal --> sequences of nonterminals and terminals

terminal --> sequences of characters

#### 3.1.1 Prolog Character Set

Terminal symbols, called tokens, consist of sequence of Prolog characters. There are five types of Prolog characters defined as:

| prolog_char | > alpha_num_char |

|-------------|------------------|

|             | graphic_char     |

|             | solo_char        |

|             | layout_char      |

|             | meta_char        |

(1) Alpha\_numeric characters

alpha\_num\_char --> | digit\_char | letter\_char

letter\_char --> capital\_letter | small\_letter capital\_letter --> [A-Z] small\_letter --> [a-z] digit\_char --> decimal\_digit\_char | binary\_digit\_char | octal\_digit\_char | hexa\_digit\_char

| decimal_digit_char | > [0-9]              |

|--------------------|----------------------|

| binary_digit_char  | >0 1                 |

| octal_digit_char   | > [0-7]              |

| hexa_digit_char    | > [0-9]  [A-F] [a-f] |

#### (2) Graphic characters

(3) Solo characters

solo\_char -->! | ( | ) | [ | ] | { | } | | , | ; | &

#### (4) Layout characters

| layout_char | > SP | // space character in ASCII    |

|-------------|------|--------------------------------|

|             | NL   | // new-line character in ASCII |

|             | HT   | // tab character in ASCII      |

#### (5) Meta characters

meta char  $\rightarrow \ | \ ' | \ ' |$

#### 3.1.2 Syntax of Term

term -->var |atom |integer|floating point |compound\_term

The floating point number is not implemented in current version of the LVM system, but the compiler still parses the floating point numbers.

#### (1) Variables

Variables are strings of letters, digits and underscore starting with capital letter or underscore.

var --> named\_var | anonymous\_var named\_var --> capital\_letter (alpha\_num\_char)\* | \_(alpha\_num\_char)\* anonymous\_var--> \_ (2) Atoms

Atoms can be constructed in three ways:

- (a) Strings of letter, digits and underscore starting with a lower-case letter;

- (b) Strings of characters enclosed in single quotes;

- (c) Strings of special characters

(3) Numbers

There are two types of numbers: integer and floating point.

integer --> integer\_constant | binary\_constant | octal\_constant | hexa\_constant

> integer\_constant--> decimal\_digit\_char | decimal\_digit\_char integer\_constant binary\_constant--> Ob binary\_digit\_char (binary\_digit\_char)\* octal\_constant --> Oo octal\_digit\_char (octal\_digit\_char)\* hexa\_constant --> Ox hexa\_digit\_char (hexa\_digit\_char)\*

floating point  $\rightarrow$  integer\_constant . integer\_constant [exponent |  $\varepsilon$ ]

| exponent | > [e  E] sign integer_constant |

|----------|--------------------------------|

| sign     | >+ - E                         |

Here  $\varepsilon$  is an empty string.

(4) Compound\_term

Compound terms can be written in one of four notations. They are:

(4.1) Function notation (bracketed expression)

compound\_term --> atom ( arg\_list )

arg\_list --> term (, term)\*

where the name of function is called functor, and the number of arguments called arity. The outer-most functor is called its principal functor, e.g., .(a1,.(a2, .(a3,[]))).

(4.2) List notation

The principal functor is '.'/2, and the first argument is a term and the second a list.

compound term --> [ term items]

items --->(, term)<sup>+</sup> | | term | NIL\_list NIL list -->[]

where a special case of NIL\_list is treated as a special atom in LVMC. For example, [a1,a2,a3], [a1,a2|a3] and [a1,a2|[b1,b2]] are list terms.

(4.3) Curly notation

compound\_term --> { term } | ( term )

(4.4) Operator notation

Some terms are written as unbracketed expressions using functors in operator notation. Each operator is characterized by three parameters: name (an atom), specifier (one of xf,yf,xfx,xfy,yfx,fx,fy) and priority (an integer between 1 and 1200).

The specifier of an operator defines its arity (1 or 2), class( prefix, infix, postfix) and associativity (left-, right-, non-associative). Table 3.1 lists all types of specifier.

The priority of a term is 0 if it is written in functional, list notation, or it is a bracketed expression or atomic term. If a term is written in operator notation, its priority is the priority of the principal functor. The predefined operators are listed in Table 3.2.

| Specifier | arity | class   | associativity |

|-----------|-------|---------|---------------|

| fx        | 1     | prefix  | non-          |

| fy        | 1     | prefix  | right-        |

| xfx       | 2     | infix   | non-          |

| xfy       | 2     | infix   | right-        |

| yfx       | 2     | infix   | left-         |

| xf        | 1     | postfix | non-          |

| yf        | 1     | postfix | left-         |

Table 3.1 Specifiers of operators

| Operator          | specifier | priority |

|-------------------|-----------|----------|

| :>                | xfx       | 1200     |

| :- ?-             | fx        | 1200     |

| ,                 | xfy       | 1100     |

| ;                 | xfy       | 1050     |

| ,                 | xfy       | 1000     |

| \+                | fy        | 900      |

| = \=              | xfx       | 700      |

| == \== =:         | xfx       | 700      |

| @<@=<@>@          | >= xfx    | 700      |

| is =:= =\= < <= : |           | 700      |

| +- ^ V            | yfx       | 500      |

| * / // rem mod <  | <>> yfx   | 400      |

| **                | xfx       | 200      |

| ^                 | xfy       | 200      |

| -\                | fy        | 200      |

Table 3.2 Predefined operator table

| compound_term | > atom_preop term   |

|---------------|---------------------|

|               | term atom_postop    |

|               | term atom_inop term |

#### 3.1.3 Clauses

clause --> head :- body | predication

where the first grammar defines a rule with :-2/2 as the principle functor, the second grammar defines a fact.

head --> predication

Ì.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

body --> (body, body) // conjunction: principal functor ','/2 | (body; body) // disjunction: principal functor ';'/2 | (body -> body) // implication: principal functor '->/2' | variable | predication

where the functor name of predication must be different from ','/2, ';'/2 and '->'/2.

predication -->atom | compound\_term where the compound\_term must be callable term with arity  $\geq 0$ .

#### 3.1.4 Directives, Query and Declarations

The principal functor of directives is (:-)/1.

| directive     | >        | :- dire  | ctive_term                                   |

|---------------|----------|----------|----------------------------------------------|

| direct        | ive_tern | n> dir   | rective_atom (predication)                   |

|               | directi  | ive ator | n> discontinuous                             |

|               |          | -        | dynamic ensure loaded                        |

|               |          |          | include initialization                       |

|               |          |          | multifile                                    |

|               |          | 0        | diantian                                     |

| query         | >        | ?- pre   | dication                                     |

| declaration   | >        | mode     | declaration                                  |

|               |          | detern   | hinacy_declaration                           |

|               | i        | gc_de    | claration                                    |

| mode_declara  | tion     | >        | :- mode atom ( mode_type (,mode_type)*).     |

| moue_deciara  |          |          | > ++  + - ?                                  |

|               |          |          | :- determinacy atom/arity (integer_constant) |

|               |          |          | >[0-9]                                       |

| co deslocatio | •        |          |                                              |

| gc_declaratio | 11       |          | :- garbage atom/arity ( integer_constant )   |

#### 3.1.5 Comments

There are two types of comments: single line and multiple line comments.

comment --> single\_line\_comment | bracketed\_comment

single\_line\_comment --> % comment\_text new\_line\_character bracketed comment --> /\* comment\_text \*/

comment\_text --> prolog\_char\_comment\_text | ɛ

In summary, the Prolog text is defined by the following grammar:

#### prolog\_text --> (comment|query|declaration |clause |directive)\*

#### 3.2 Token Generator

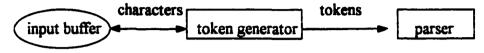

The role of the lexical analyzer is to scan characters of program text and convert the input into a stream of tokens. The token with its attribute is passed to the parser. Therefore, the lexical analyzer and parser form a token producer-consumer pair shown in Figure 3.1.

Figure 3.1 Interface to the lexical analyzer

The lexical analyzer is implemented by a token generator. An input buffer is set up for reading and pushing back characters. A block of 256 characters is read into the buffer from the file at a time. A pointer keeps track of the input position. A lookahead character is checked. It should be noted that all atoms including the operators belong to the name\_token. The number\_tokens are further classified into integer\_token and float\_token.

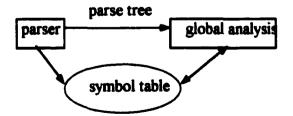

#### **3.3 Syntax Analysis**

In the compiler design, the syntax analysis of Prolog programs is implemented by a parser. The parser accepts a stream of tokens from the token generator and verifies that the stream of tokens can be generated from the Prolog grammar specified in Section 3.1. The output of the parser is a representation of the parse tree, which will be used in the next phase of the compiler. Meanwhile, a collection of information about a predicate is put into a symbol table. The interface of the parser is shown in Figure 3.2. In the current version of LVMC, the syntax error is handled in three steps:

- (a) reporting the presence of errors,

- (b) printing out the reason of errors, and then

- (c) terminating the compiler.

A better syntax error handler would be implemented in the future version of the compiler.

Figure 3.2 Role of parser in the compiler

Since the grammar of Prolog is relatively simple, an unambiguous grammar for Prolog is reconstructed so that no production right side has two adjacent nonterminals. Therefore, an easy-to-implement form of bottom-up syntax analysis method, called operator-precedence parsing [20], is employed in the parser. In the implementation, a stack with elements, of which data structure is defined as

typedef struct stacktype {

int tokentype;

int priority;

int specifier;

argument\_information \*term;

structure stacktype \*next;

} stacktype;

1

is used to hold the input tokens. The priority and specifier of some predefined operators is listed in Table 3.2. The basic parsing strategy of LVMC is

(a) Initially, the parser sets up an empty stack, and accepts tokens one by one until an end\_token is reached. When the end\_token arrives, the parser outputs the parse tree of the clause if there is only one term remaining on the stack. Otherwise, it invokes syntax error handler.

(b) For each token, if the token is one of the set of operators, then the parser invokes a corresponding reducing function to reduce the top elements on the stack. Otherwise, it simply shifts or pushes the token onto the stack.

# **Chapter 4. Clause Analysis and Translation**

The clause analysis is the crucial part of the LVMC. It involves the structure argument classification, variable analysis, register scheduling and V/C-frame allocation. They will be discussed in detail in Section 4.1-4.3.

The translation of a clause generates two streams of instruction code: control instruction code and unification instruction code, in separate segments. In general, the control instructions for a clause include instructions of stack allocation, object initialization, unification code invocation, procedure invocation and garbage collection. The unification instructions represent all arguments of the head and the bodies in a clause. During the compilation, various code segments are labeled uniquely and systematically. The name conventions are listed in Table 4.1. The clause translation will be discussed in Sections 4.4 and 4.5.

| labeling          | Meaning                      | Code type        |

|-------------------|------------------------------|------------------|

| name/arity        | predicate code entry         | control code     |

| name/arity.i      | clause code entry            | control code     |

| name/arity.i.i    | branching code entry         | control code     |

| name/arity.i.u.0  | head unification code entry  | unification code |

| name/arity.i.u.i  | goal unification code entry  | unification code |

| name/arity.i.s.i. | selector or constructor code | unification code |

Table 4.1 Code segment-labeling rules

#### 4.1 Structure Argument Representation and Flattening

The LVMC classifies the structure arguments of a clause into three types: selector, constructor and dual. A structure argument is a selector if it is ground or its input mode is (+, ++). A structure argument is a constructor if its input mode is (- or out) and it contains at least one variable. If a structure argument has input mode of (? or in./out), it may be used as either a selector or a constructor, and also contains at least one variable, then it is a dual. Here, we can see that the types of structure arguments of a clause really depend on the input modes of the arguments. The input mode of a structure argument is obtained either from mode declaration or from mode global analysis.

If a compound structure has a certain mode, then all nested substructures inherit the same mode. The mode declaration applies to head arguments only. For the goals of a clause, we assume that all structure arguments are duals. It is enforced that a ground structure argument is always a selector regardless of its input mode.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

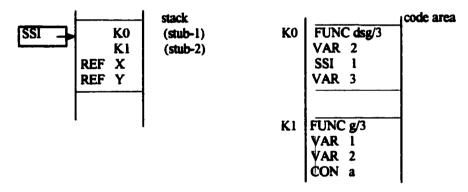

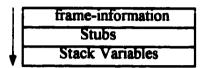

The LVM uses instruction: DCI c\_entry to represent a selector. Here c\_entry specifies the code entry of the whole structure unification in code area. A constructor is represented either by instruction: SSI offset if it is a non-list structure or by instruction: SCI offset if it is a list. Here offset denotes a relative position of this stub with respect to a LVM stack frame of the clause. Since a pure constructor will be bound to an arbitrary variable during execution, the stub must be allocated inside its associated stack frame to represent a dynamic instance creation. For a clause, a V-frame or C-frame may need to be allocated (See Section 4.5). The order of stub and variable allocation is shown in Figure 4.1.

Figure 4.1 Order of stub and variable allocation on stack

During compiling a clause, all nested structure arguments must be flattened in order to determine the number of stubs and their offsets. A stack with element defined as

typedef struct fstack { char ftype, boolean delayable, char \*functor, unsigned index, unsigned arity, arginf \*arg\_list, struct fstack \*next } fstack;

is used to implement the flattening algorithm. The flattening algorithm is:

(a) scan arguments of a clause from left to right. For each structure argument, push an element with data structure of "fstack" on the stack. The field of "ftype" of the element depends on its input mode, it may be one of types {SSI,SCI,DCI}. The field of "delayable" is reserved for {SCI,SSI} elements to implement initialization delay optimization. Only if a structure argument appearing in head of a clause has (?)-type of input mode, the "delayable" is set to "No". In all other cases, the field "delayable" of {SSI,SCI} elements is set to "YES".

(b) scan all elements of the stack from top to bottom. If its "arg\_list" has substructure, an element of "fstack" type for the substructure is inserted upon its parent in the stack.

(c) repeat (b) until there is no nested structure in the field of "arg\_list".

(d) index all SSI elements from top to bottom and then index SCI elements from top to bottom by second pass. A SSI element requires one cell in LVM stack frame, but a SCI element needs two cells for copying its structure term.

**Example 4.1** Let's assume we have the following clause with mode declaration.

------

:-pss mode(+,-,+).

pss(X, h(Y,g(a,b)), f(X,g(Z,b))):-qs(j(Z,k(a,b),W)),rs(X,Y,Z).

After the flattening procedure (a), we have the following working stack:

| type | index | delayable | arg_list      |

|------|-------|-----------|---------------|

| SSI  | 0     | Y         | h(Y,g(a,b))   |

| DCI  | 1     | -         | f(X,g(Z,b))   |

| SSI  | 1     | Y         | j(Z,k(a,b),W) |

After all nested structures are completely flattened, the contents of the working stack are:

| type | index | Delayable | arg_list       |

|------|-------|-----------|----------------|

| SSI  | 0     | Y         | h(Y, DCI:1)    |

| DCI  | 1     |           | g(a,b)         |

| DCI  | 2     | -         | f(X, DCI:3)    |

| DCI  | 3     | -         | g(Z,b)         |

| SSI  | 1     | Y         | j(Z, DCI:4, W) |

| DCI  | 4     | -         | k(a,b)         |

For clause pss/3, the number of stubs is 2. The indexing of {SSI}elements starts from 0.

**Example 4.2** This example has list arguments. The LVM uses Structure Copying method to represent them. The cells of {SCI} type need to be allocated on LVM stack frame.

:-psc mode (+,-,-). psc([X|Y], [X,a,b],[[Y],d]).

\_\_\_\_\_

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

| type | index | delayable | arg_list  |

|------|-------|-----------|-----------|

| DCI  | 1     | -         | [X Y]     |

| SCI  | 0     | Y         | [X [a,b]] |

| SCI  | 2     | Y         | [[Y],d]   |

After the first procedure (a) of the algorithm, we have the following working stack:

After completely flattening all nested lists and indexing all SCI elements again, the working stack becomes:

| type | index | delayable | arg_list      |

|------|-------|-----------|---------------|

| DCI  | 1     | •         | [X Y]         |

| SCI  | 0     | Y         | [X DCI:2]     |

| DCI  | 2     | -         | [a DCI:3]     |

| DCI  | 3     | -         | [b []]        |

| SCI  | 2     | Y         | [SCI:4 DCI:4] |

| SCI  | 4     | Y         |               |

| DCI  | 4     | -         | [d][]]        |

For this clause psc/3, three SCI elements need to be copied to LVM stack frame through special initialization instructions (See Section 4.4).

#### 4.2 Variable Classification and Index Calculation

#### 4.2.1 Classifications of Variables

The LVMC classifies the variables of a clause into two types:

(1) stack variable (S-type): A stack variable is one which possibly outlives a procedure call and must reside in the LVM stack frame. A stack variable is represented by an offset to its dynamically allocated stack frame and is accessed by "base plus index" method.

(2) register variable (R-type): A register variable is a temporary variable which does not survive across procedure calls. A register variable is used in a fact clause, arithmetic computations or a deterministic chain call. A register variable never occurs in any constructor. Except above two types of variables, a special variable, called "void" variable, may exist in a clause. A void variable is a variable which occurs once and only in the argument with (+) input mode of head of a clause. A void variable must be declared by "\_" in a clause. The LVMC treats a void variable as constant term by an instruction:

#### VOID

A stack or register variable may be used in two ways: uninitialized (V-type) or instantiated (L-type). The LVMC uses {RGV and RGL} to represent the two states of a register variable respectively, and {VAR and VAL} to represent the two states of a stack variable respectively. A V-type variable is a variable without initial value. A L-type variable is a variable with initial value, but may be unbound. Here, unbound means that the variable is initialized as a self-referential pointer. Binding a L-type variable is expensive because the variable must be dereferenced. One of the major sources of inefficiency of early WAM implementations arises from that V-type variables are created as selfreferential pointers and then unified soon afterward. Beer [21] first noticed this problem, and proposed a solution that the V-type variables are bounded via destructive assignments without dereferencing. In other word, the initialization of V-type variables can be canceled. The LVM bounds the V-type variable by destructive assignment. The analysis of variable status in a clause is important to improve the efficiency of any implementation.

Naturally, the next question is how to identify status of variables in a clause. Van Roy [22] used a global analysis algorithm to extract the uninitialized variable from a clause. Lindgren [23] detected the uninitialized variables by a syntactic transformation method. In the LVMC, we supposed that the input modes of arguments of predicates are known before the clause analysis, the algorithm of variable analysis becomes simple. Our algorithm also takes the LVM unification method into account.

The unification method of LVM system is quite different from all others. Most. Prolog systems implement unification in the depth-first order, but the LVM invokes the unification code segments in the reverse depth-first order. When two unification instructions represent both structure terms (either selector or constructor), the unification of deeper-level structure terms is delayed unless those two instructions are the last pair in the current code segments. In other word, partial unification is performed.

In the variable analysis, a linked list "xlist" with node data structure defined as

typedef struct varinfo { char \*var-name, char RS-type, char used, char first-occurred, char delayable, struct varinfo \*next } varinfo;

Ì

is used to hold the variable information in a clause in order to decide variable R/S-type and necessity of variable initialization as well as possible initialization delay. The LVMC uses four rules to set first-occurred and delayable flags:

(1) If a stack variable occurs in plain argument list of head, its first-occurred flag is set to true;

(2) If a stack variable occurs in any head structure argument of selector before any constructor argument during scanning and flattening the head argument lists, its first-occurred flag is set to true;

(3) If a stack variable occurs in arguments of goals before any constructor argument during scanning and flattening the goal argument lists, its first-occurred flag is set to true.

(4) If a stack variable doesn't appear in structure arguments of head with (?) mode , then its delayable flag is true.

After the analysis, the R/S-type of all variables is set correctly. For a stack variable in the "xlist", if its first-occurred flag is false, this variable must be initialized. Furthermore, if its delayable flag is true, this variable initialization can be delayed until after head unification control instruction.

The V/L-type information is associated with each variable. A variable may appear in the argument lists of head and goals or inside structure argument terms. Assuming that the clause is

H(...):-G1(...),G2(...),...,Gn(...),

the LVMC uses the following algorithm to determine the V/L-type of a variable:

(1) Scan the argument lists of head and flatten its structure terms. Then do the same for each goal argument in order of G1->G2->...->Gn.

(2) following (1) process, if a variable appears first time and the current argument is plain argument or selector, then it is V-type; otherwise it is L-type.

Actually, the variable analysis is naturally embedded into the structure term flattening process. The void variables always are of V-type.

**Example 4.3** To see how the variable V/L type identification works, let's consider the following clause. All variables in this clause are stack variables. The V/L type of variables is listed in the right side.

Ľ

| p(X,                     | X: V-type                                       |

|--------------------------|-------------------------------------------------|

| h(Y, g(Z)),<br>f(X,g(Y)) | Y: L-type, Z: L-type(*)<br>X: L-type, Y: V-type |

| ):-<br>q(j(Z,W)),        | Z: L-type, W:L-type(*)                          |

| r(X,Y,Z).                | X: L-type, Y: L-type, Z: L-type                 |

The LVMC scanning order of arguments is:

$X \rightarrow f(X,g(Y)) \rightarrow h(Y,g(Z)) \rightarrow j(Z,W) \rightarrow X \rightarrow Y \rightarrow Z.$

Here, variables {Z,W} need to be initialized.

#### 4.2.2 Indexing of Variables

At each clause invocation point, a stack frame (V/C-frame) and registers are used to hold dynamic objects generated from the called clause. The stack frame is allocated in the LVM stack area. Although the size of a V/C-frame varies from one clause to another, the stack frame is an integral memory in the LVM working stack. Later on, any object on the stack can be accessed using the base plus offset addressing method. Normally, the LVM uses the bottom of going allocated frame as the consulting base. The offset is the distance of location of the object inside the stack frame from the frame bottom in units of machine words.

A stack frame may contain environment parameters, stubs, SCI objects and stack variables. In order to prevent negative offsets in nested unification instructions, the LVMC assigns the stack cells by the following rule:

(1) Cell assignment starts from the relative location 0;

(2) Cells are assigned by the order of environment parameter->stubs-->SCI objects-->stack variables;

(3) Stub arrangements are consistent with their flattening order to guarantee the correct accessing scope of the nested stubs and stack variables;

(4) Stack variables, which need initialization, are assigned with lower indices than those uninitialized.

In the LVMC, there are two types of offsets: S-offset and C-offset. The S-offset is an offset against the base of the allocated frame. The S-offset is used to generate the unification instructions for the head and goal arguments, and also to access the variables in the structure term of a selector. Therefore, the following objects have S-offsets: (1) stack variables, which directly are plain arguments of the head and goals;

(2) stack variables, which occur in structure terms of selector or DCI objects;

(3) stubs/SCI objects, which are arguments of the head and goals.

For a constructor stub or SSI object, since it will be bound to a variable and then be carried to any place during execution, so its environment is created to associate with the stub. Therefore, the absolute address of the stub serves as the base of the unification code environment and its content as the unification code entry pointer. A C-offset is an offset against the location of a constructor stub. The following objects have C-offset:

(1) stack variables, which occur inside structure terms of constructor;

(2) stubs/SCI objects, which are substructures of a structure term of constructor.

Since all stubs, SCI objects and stack variables have been assigned locations in the stack frame during compilation, the offset calculation becomes easy. Let X be any object in C and C a constructor stub, then

C-offset (X in C) = location(X) - location(C).

The S-offset of an object is its relative location with respect to the stack frame.

**Example 4.4** Let's consider the following clause:

:-mode p(-,?,-). p(f(Y,g(Z)),X,h(Y,g(W))):-q(X,Y), r(X,Z).

After nested structure flattening and variable analysis, we find that there are four stubs and 4 stack variables  $\{X,Y,Z,W\}$ . Stack variables  $\{X,Y,Z\}$  have first occurrence, so they don't need initialization. The variable W must be initialized. A C-frame is used to hold all objects. Thus a total of eleven cells will be allocated as the execution environment of the clause on the LVM stack area. The cell assignments are listed in the Table 4.2.

In the head unification codes of clause p/3, we use S-offset: offset 3 to refer to C1, offset 8 to X and offset 5 to C3. The variable Y has three offsets: one S-offset and two C-offsets. Since variable Y occurs in constructors C1 and C3, the two C-offsets are:

C-offset (Y in C1) = location (Y) - location (C1) = 9-3 = 6

C-offset (Y in C3) = location (Y) - location (C3) = 9-5 = 4

Therefore, in the unification code segment of C1, we use C-offset 6 to refer to Y and C-offset 1 to refer to C2.

| Location | Object      | S-offset | C-offset   |

|----------|-------------|----------|------------|

| 0        | c-frame env |          |            |

| 1        | c-frame env |          |            |

| 42       | c-frame env |          |            |

| 3        | C1=f(Y,C2)  | C1:3     | Y: 6 C2: 1 |

| 4        | C2=g(Z)     | C2:4     | Z: 6       |

| 5        | C3=h(Y,C4)  | C3:5     | Y: 4 C4: 1 |

| 6        | C4=g(W)     | C4:6     | W: 1       |

| 7        | w           | 7        |            |

| 8        | x           | 8        |            |

| 9        | Y           | 9        |            |

| 10       | z           | 10       |            |

Table 4.2 Stack cell assignment and offsets of objects

Since the LVM uses the Structure Copying method to represent the list constructors, it is possible that several copied list instances share a single variable. Therefore, a special set of list initialization instructions are designed to handle the shared occurrence problem. The detail will be discussed in Section 4.4.

## 4.3 Register Allocations and Conflict in Parameter Passing

In the LVM, there are 64 general purpose registers emulated by memory, which can be directly accessed without indirection. Eight of them labeling from R0 to R7 are dedicated to pass parameters between the caller and the callee. Others from R8 to R63 are used to store the intermediate results in arithmetic computation. Here, we only discuss the parameter passing registers.

#### 4.3.1 Magic Register: R0

The role of R0 register is quite different from that of other registers (R1..R7). R0 register is used to speed up last argument dispatching. Although Prolog programmers have a natural tendency to write the codes using discriminating patterns as first arguments, the LVM does not depend on this tendency. Since the LVM implements unification delay algorithm, the LVMC chooses an appropriate argument from the head arguments of a clause and swaps it with the last argument, if one or more head arguments have (+) input mode. In such cases, the clauses of a predicate may be dispatched by their last arguments. To speed up the dispatching, the LVM uses R0 register to store the last argument before issuing a procedure call. Two control instructions {SWT and SHS} are designed to implement the dispatching based on the R0 value.

If a predicate is last argument dispatchable, the LVMC uses the following conditions to select a variable from the last argument of a head for each clause to be the R0 register variable:

(1) In the head, the variable occurs in the last argument once.

(2) Since the R0 represents a dereferenced value of the corresponding variable in the goal side of the clause, the variable may be used in any arithmetic expression before the first user defined goal. The variable can only appear in the first user defined goal but not other goals, and can also be used as its last argument.

**Example 4.5** To illustrate the selection, let us consider the following two clauses, which are last argument dispatchable.

:-mode p1(-,+,+). p1([X|Xs],Y,Z):-Y>Z, W is Z+1,p1(Xs,W,Z). :-mode p2(-,+). p2([X|Xs], f(Y,X)):-p2(Xs,Y).

In the first clause, variable Z is selected as R0 register variable. The variable Z is the lastargument of the head, also the last argument of user defined goal p1/3. Before the invocation of the goal call p1/3, the variable Z is used in two arithmetic expressions. In the second clause, variable Y is selected as R0 register variable.

Except speeding up the dispatching, R0 register can help to pass parameters faster between the caller and callee. When the callee is last argument dispatchable, the caller can directly store its last argument in R0 regardless of the properties of the caller predicate, then the later-on unification process directly involves R0 register. If the caller predicate is nondeterministic, R0 is protected in choice point or B-frame. To implement this optimization, the LVM designs two sets of procedure invocation instructions {CAL, CCL, LAC} as follows:

| CAL              | u_code_entry                 | predicate_code_entry                         |

|------------------|------------------------------|----------------------------------------------|

| CAL Ri/Vi<br>CCL | u_code_entry<br>u code entry | predicate_code_entry<br>predicate_code_entry |

| CCL Ri/Vi        | u_code_entry                 | predicate_code_entry                         |

| LAC              | u_code_entry                 | predicate_code_entry                         |

| LAC Ri/Vi        | u_code_entry                 | predicate_code_entry                         |

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

If the first operand of the procedure invocation instructions is of Ri/Vi, it means that the specified register (Ri) or stack variable (Vi) is dereferenced and its final value is saved in R0. Then the last instruction in the goal unification code segment is replaced by instruction: "RGL 0". The LVMC arranges the R0 register to pass the last argument of a goal call when the goal predicate is last argument dispatchable.

## 4.3.2 R1...R7 Registers

R1...R7 register variables can only be used in fact, deterministic chain clause to pass parameters. Unlike R0, those register variables can't be used in nondeterministic chain clause and normal rule clause. If these register variables are not enough to represent the parameter passing variables in a clause, then the remainder of parameter variables will be treated as stack variables. In this case, extra stack cells need to be allocated on the LVM stack frame.

During register allocation, a conflict may happen. To demonstrate this problem, let us check the following deterministic clause p/2:

p(X, Y, Z) := q(Y, W, X).

After variable analysis, the clause is first transformed into:

p(R1, R2, R3): -q(R3, R4, R1).

Here, p/3 passes its parameters to q/3 goal via registers in the order of R3->R4->R1. If the predicate q/3 uses "q(R1,R2,R3):-.." to accept these parameters, after the caller's R3 unifies with the callee's R1, the caller's R1 information has been lost, therefore the register conflict occurs. To avoid this conflict, the LVMC uses the following strategies to schedule R1..R7 registers in register allocation:

(1) Registers (R1..R7) are allocated incrementally by the order of index to the head and goal arguments from left to right.

(2) If the current register variable index is less than the left-hand register variable index, a new register variable with a greater index will replace this register variable, and a register to register assignment will be inserted before this goal call.

Thus, in the above example, the LVMC will change the clause to be in the form of

p(R1, R2, R3) := R5 = R1, q(R3, R4, R5).

# 4.4 Unification Code of a Clause

For a clause, there may be several independent unification code segments for the head and its goal arguments respectively. Each unification code segment consists of several unification instructions. These unification instructions have a single format of Opcode Operand

| Opcode | Operand    | Meaning                            |

|--------|------------|------------------------------------|

| INT    | value      | an integer                         |

| CON    | value      | a constant                         |

| NIL    |            | a null list                        |

| VOID   |            | a void variable                    |

| VAR    | offset     | an uninitialized stack variable    |

| VAL    | offset     | an instantiated stack variable     |

| RGV    | index      | an uninitialized register variable |

| RGL    | index      | an instantiated register variable  |

| DCI    | entry      | a direct/dynamic-copied instance   |

| SSI    | offset     | a static shared instance           |

| SCI    | offset     | a static copied instance           |

| FUN    | name/arity | a functor with name/arity          |

Totally twelve unification instructions are defined in LVM and listed in Table 4.3.

Table 4.3 LVM unification instructions

Unification code segments of a clause can be generated in any order, provided that they are properly labeled. The LVMC uses the name conventions listed in Table 4.1. Inside each code segment the order of unification instructions must obey the lexical order of the objects in the argument list.

After the clause analysis, the unification code generation method is simple. It simply describes the argument lists of head and goals from left to right. For a flattened structure stored in "fstack" (See Section 4.1), it starts with a FUN instruction and follows with a sequence of instructions to match its arguments. But a selector list is treated as a structure without functor so that the FUN instruction is omitted.

**Example 4.6** Suppose that we have the following clause p/3:

:- mode p(+,-,+).

p(Y,f(X,Y,Z),[X|Xs]):-p(Y,Z,Xs).

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

| Object   | Object type  | S-offset | C-offset |

|----------|--------------|----------|----------|

| f(X,Y,Z) | SSI          | 0        |          |

| [X Xs]   | DCI          | -        |          |

| X        | Stack var    | 1        |          |

| Y        | stack var    | 2        | 2        |

| Ζ        | Stack var    | 3        | 3        |

| Xs       | Register var | 0        |          |

After the clause analysis, we find that there are three stack variables  $\{X,Y,Z\}$ , a R0 register variable  $\{Xs\}$ , and one structure stub as shown in Table 4.4.

Table 4.4 Memory layout of objects for p(+,-,+)/3 clause

For this clause, four unification code segments should be generated. One is for the clause head arguments, one is for the goal arguments and other two segments are for the nested structure terms in head arguments. The unification code segments are labeled as follows:

| U-code Labeling | Meaning              |

|-----------------|----------------------|

| p/3.u.0         | head unification     |

| p/3.s.1         | constructor f(X,Y,Z) |