**VOLUME: 14 | NUMBER: 2 | 2016 | JUNE**

# REALIZATION OF OFCC BASED TRANSIMPEDANCE MODE INSTRUMENTATION AMPLIFIER

Neeta PANDEY, Deva NAND, V. Venkatesh KUMAR, Varun KUMAR AHALAWAT, Chetna MALHOTRA

Department of Electronics and Communication Engineering, Delhi Technological University, Shahbad Daulatpur, Main Bawana Road, Delhi-110042, India

n<br/>66pandey@rediffmail.com, devkamboj<br/>07@gmail.com, vvenkateshkumar.kumar@gmail.com, varun.ahlawat@gmail.com, chtmal<br/>hotra@gmail.com

DOI: 10.15598/aeee.v14i2.1551

**Abstract.** The paper presents an instrumentation amplifier suitable for amplifying the current source transducer signals. It provides a voltage output. It has a high gain, common mode rejection ratio and gain independent bandwidth. It uses three Operational Floating Current Conveyors (OFCCs) and four resistors. The effect of nonidealities of OFCC on performance of proposed Transimpedance Instrumentation Amplifier (TIA) is also analyzed. The proposal has been verified through SPICE simulations using CMOS based schematicThe paper presents an instrumentation amplifier suitable for amplifying the current source transducer signals. It provides a voltage output. It has a high gain, common mode rejection ratio and gain independent bandwidth. It uses three operational floating current conveyors (OFCCs) and four resistors. The effect of nonidealities of OFCC on performance of proposed Transimpedance Instrumentation Amplifier (TIA) is also analyzed. The proposal has been verified through SPICE simulations using CMOS based schematic.

# **Keywords**

Difference amplifier, operational floating current conveyor, transimpedance instrumentation amplifier.

#### 1. Introduction

The Operational Floating Current Conveyor (OFCC) [1], [2] is a versatile active building block which provides flexibility to the circuit designer. It inherits the features of current conveyor and the current feedback

op-amp with additional current output terminal. The availability of both high and low impedance ports at input and output provides flexibility to circuit designer. The OFCC has been used for implementing instrumentation amplifier [3], read out circuit [4], logarithmic amplifier [5], rectifier [6], filters [7], [8], [9], [10], [11], variable gain amplifier [12], and wheatstone bridge [13].

An Instrumentation Amplifier (IA) is invariably used as an input block in applications such as automotive transducers [14], industrial process control [15], [16], [17], linear position sensing [18] and bio-potential acquisition systems [19], [20], [21], [22], [23], [24] to amplify differential signals and to suppress unwanted common mode signals. Generally the operational amplifier based IA are classified as Voltage Mode IA (VMIA) whereas current mode building block based IA are referred as Current Mode IA (CMIA). Another way to classification is based on the type of input and output signal on which IA is working. The Transimpedance IA (TIA) is one among such classification where the sensed current is amplified and converted into a voltage. There is limited literature available on TIAs [25]. [26], [27], and no OFCC based TIA is available in open literature to the best of author's knowledge. The details of available TIAs are comprehended in Tab. 1 according to the number and type of active and passive elements used along with the impedance presented at input and output. The following points are observed from Tab. 1:

- The opamp based topology [26] uses excessive number of resistors.

- The input impedance is low for [27] which is ideal for current sensing whereas a high input impedance is presented for [25], [26].

- The output impedance of [26], [27] is proper i.e. matrix given in Eq. (1): low in contrast to the one provided by [25].

- Extra active elements are required for impedance matching at input [25], [26] and output [25].

**Tab. 1:** Characteristics of available instrumentation amplifiers.

| Ref. | Active   | No. of    | Input     | Output    |

|------|----------|-----------|-----------|-----------|

| no.  | elements | resistors | impedance | impedance |

| [25] | 2 CCII+  | 3         | High      | High      |

| [26] | 3 opamps | 10        | High      | Low       |

| [27] | 3 OTRA   | 5         | Low       | Low       |

It is clear from the above discussion that only topology [27] provides proper input and output impedance levels and does not require additional circuitry for The aim of this paper is impedance matching. to present an OFCC based TIA offering proper input/output interface. It uses three active blocks and four resistors i.e. same number of active blocks as [27] and the lesser passive components than [27]. Both input and output impedances of proposed topology are low.

The paper is organized in five sections as follows: Section 2. briefly discusses the basic characteristics of OFCC and detailed description of proposed TIA structure. Section 3. describes behavior of proposed TIA in presence of nonidealities. The simulation results are presented in Section 4. followed by conclusions in Section 5.

#### 2. Proposed Circuit

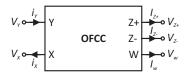

The key component of the proposed circuit is the OFCC block as shown in Fig. 1. It has two inputs (X, Y) and three outputs (W, Z+, Z-).

Fig. 1: OFCC block.

The port X is a low impedance current input while the port labeled Y is a high impedance voltage input. The ports Z+ and Z- are high impedance current outputs, where Z+ has positive polarity and Zhas negative polarity. The terminal marked W is the low impedance output voltage terminal. The terminal characteristics of the OFCC are characterized by the

$$\begin{bmatrix} I_Y \\ V_X \\ V_W \\ I_{Z+} \\ I_{Z-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 \\ 0 & Z_t & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & -1 & 0 & 0 \end{bmatrix} \begin{bmatrix} V_Y \\ I_X \\ I_W \\ V_{Z+} \\ V_{Z-} \end{bmatrix}, \quad (1)$$

where open loop transimpedance gain  $Z_t$  is impedance between the ports X and W and other symbols have their usual meanings.

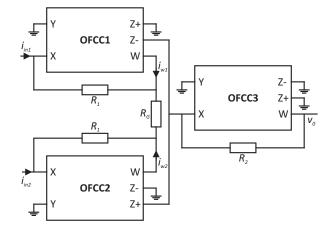

Fig. 2: Proposed OFCC based TIA.

Figure 2 shows the proposed TIA circuit. It consists of three OFCCs and four resistances. The third OFCC block in Fig. 2 is simply used as a current to voltage convertor which converts the amplified difference of currents that has been received as an input to OFCC1 and OFCC2, into voltage. The differential transimpedance gain of the instrumentation amplifier for an ideal case is computed as follows.

The currents  $(i_{w1}, i_{w2})$  flowing out of W terminals of OFCC1 and OFCC2 respectively, are:

$$i_{w1} = -\left[i_{in1} + \frac{R_1}{R_G}(i_{in1} - i_{in2})\right],$$

(2)

$$i_{w2} = -\left[i_{in2} + \frac{R_1}{R_G}(i_{in2} - i_{in1})\right].$$

(3)

The output voltage is computed as:

$$v_{out} = -R_2(-i_{w1} + i_{w2}) = R_2(i_{w1} - i_{w2}) =$$

$$= \left[ (i_{in2} - i_{in1}) \left( 1 + \frac{2R_1}{R_G} \right) \right]. \tag{4}$$

Using Eq. (4), the differential gain  $(A_d)$  is obtained as:

$$A_d = \frac{v_{out}}{i_{in2} - i_{in1}} = \left(1 + \frac{2R_1}{R_G}\right) R_2.$$

(5)

# 3. Non Ideal Analysis

Practically, there are two kinds of OFCC non-idealities. The first type of nonidealities comes from tracking errors between port voltages and currents and their effect depend strongly on topology. As the Y terminal in proposed topology is grounded the performance is unaffected due to voltage tracking errors. Considering the current tracking error, the currents at Z+ and Z-terminals are represented as:

$$i_{Z+} = \alpha i_{w2},\tag{6}$$

$$i_{Z-} = -\gamma i_{w1},\tag{7}$$

where  $\alpha$  and  $\gamma$  are non ideality constants.

Therefore, Eq. (4) modifies to:

$$v_{out} = \left[ (\alpha i_{in2} - \gamma i_{in1}) + \dots + \left( (\alpha + \gamma) \frac{R_1}{R_G} (i_{in2} - i_{in1}) \right) \right] R_2.$$

(8)

Assuming  $\alpha = \gamma = 1$  in Eq. (8) the differential gain  $(A_d)$  is written as:

$$A_d = \frac{v_{out}}{i_{in2} - i_{in1}} = \left(1 + \frac{2R_1}{R_G}\right) R_2. \tag{9}$$

Considering  $i_{in1} = i_{in2} = i_{cm}$  in Eq. (8) for common mode operation, the common mode gain  $(A_{cm})$  is obtained as:

$$A_{cm} = \frac{v_{out}}{i_{cm}} = (\alpha - \gamma)R_2. \tag{10}$$

Therefore the CMRR of the final circuit is:

$$CMRR = \frac{A_d}{A_{cm}} = \frac{1}{\alpha - \gamma} \left( 1 + \frac{2R_1}{R_G} \right). \tag{11}$$

The second nonideality comes due to finite transimpedance gain  $Z_t$  and its frequency dependence which is approximated as  $Z_t = 1/(sC_p)$  at high frequencies. The value of  $C_p$  is  $(Z_{to} \ \omega_{tc})$ , where  $Z_{to}$  and  $\omega_{tc}$  represent open loop transimpedance gain and its cut off frequency respectively.

Considering finite  $Z_t$ , Eq. (4) is recalculated as

$$v_{out} = [\epsilon_1(s)i_{w1} - \epsilon_2(s)i_{w2}]\epsilon_3(s)R_2, \qquad (12)$$

$$v_{out} = \left[ \left( (i_{in2} - i_{in1})(\epsilon_2(s) - \epsilon_1(s)) \frac{R_1}{R_G} \right) + \dots \right.$$

$$\left. \dots (\epsilon_2(s)i_{in2} - \epsilon_1(s)i_{in1}) \right] \epsilon_3(s)R_2,$$

$$(13)$$

where

$$\epsilon_i(s) = \frac{1}{1+sC_{pi}R_1}$$

for  $i=1,2$  and  $\epsilon_3(s) = \frac{1}{1+sC_{r2}R_2}$ .

Assuming  $\epsilon_1(s) = \epsilon_2(s)$ , differential gain is calculated as:

$$A_d = \left(1 + \frac{2R_1}{R_G}\right) R_2 \epsilon_{uc},\tag{14}$$

where  $\epsilon_{uc} = \frac{1}{1 + sC_{p3}R_2} \cdot \frac{1}{1 + sC_{p1}R_1}$  and is uncompensated error function.

Taking  $i_{in1} = i_{in2} = i_{cm}$  the common mode gain is given by:

(6)

$$A_{cm} = \frac{sR_1R_2(C_{p1} - C_{p2})}{(1 + sC_{p1}R_1)(1 + sC_{p2}R_1)(1 + sC_{p3}R_2)}.$$

(15)

Therefore the CMRR becomes:

$$CMRR = \frac{A_d}{A_{cm}} =$$

$$= \left(1 + \frac{R_G}{2R_1}\right) \left(\frac{2 + sR_1(C_{p1} + C_{p2})}{s(C_{p2} - C_{p1})R_G}\right).$$

(16)

## 4. Simulation Results

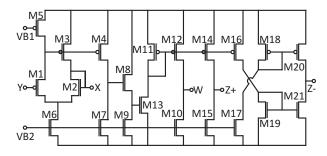

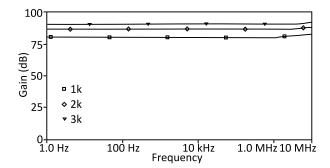

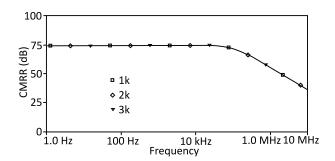

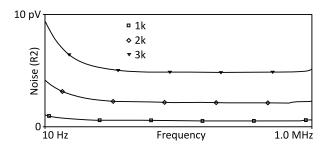

The CMOS based OFCC implementation [12] as shown in Fig. 3, is used for verifying functionality of proposed TIA. The transistor aspect ratios are given in Tab. 2. SPICE simulations are carried out using supply voltages of  $\pm 1.5$  V and bias voltages of  $\pm 0.8$  V. The simulated differential gain response of the proposed TIA is depicted in Fig. 4 for  $R_G = 1 \text{ k}\Omega$ ,  $R_1 = 5 \text{ k}\Omega$  and  $R_2$ is varied from 1 k $\Omega$  to 3 k $\Omega$  in step of 1 k $\Omega$  in order to obtain different gains. The CMRR frequency response is shown in Fig. 5. It may be noted that CMRR is independent of gain and has a bandwidth of 112 kHz. Figure 6 shows the noise spectral analysis of the proposed TIA using the same component values as those taken for obtaining differential gain response. It is observed that the output noise level has small magnitude. The power consumption of the proposed OFCC based TIA is found to be 1.5 mW.

Fig. 3: CMOS schematic of OFCC [12].

#### 5. Conclusion

In this paper, an OFCC based TIA is presented and simulated. The circuit requires only three OFCCs,

Tab. 2: Characteristics of available instrumentation amplifiers.

| Transistor         | $W (\mu \mathrm{m})/L (\mu \mathrm{m})$ |  |

|--------------------|-----------------------------------------|--|

| M1, M2             | 50/1                                    |  |

| M3, M4, M11, M12,  | 50/2.5                                  |  |

| M14, M16, M18, M20 | 50/ 2.0                                 |  |

| M5, M7, M10, M15,  | 20/2.5                                  |  |

| M17, M19, M21      | 20/ 2.0                                 |  |

| M6, M8             | 40/2.5                                  |  |

| M9, M13            | 100/2.5                                 |  |

Fig. 4: Frequency response of the proposed TIA.

Fig. 5: CMRR of the proposed TIA for different gain values.

Fig. 6: Noise spectral density for different values of gain.

three feedback resistors and one grounded resistor. It works with current mode of input in order to produce an amplified output without using complex designs. The AC analysis proves the efficiency of this new circuit and the huge bandwidth it possesses. The proposed topology offers advantages over the existing operational amplifiers based TIAs, in terms of a wider bandwidth that stays independent of the finite open loop gain of the TIA. The proposed circuit also offers low component count as compared to the existing OTRA based design.

### References

- [1] KHAN, A. A., M. A. AL-TURAIGI and M. A. EL-ELA. Operational floating current conveyor: Characteristics, Modeling and applications. In: *IEEE Instrumentation and Measurement Technology Conference*. Hamamatsu: IEEE, 1994, pp. 788–790. ISBN 0-7803-1880-3. DOI: 10.1109/IMTC.1994.351887.

- [2] GHALLAB, Y. H., M. A. EL-ELA and M. ELSAID. Operational floating current conveyor: Characteristics, Modeling and Experimental results. In: *Proceedings of International Conference on Microelectronics*. Kuwait: IEEE, 1999, pp. 59–62. ISBN 0-7803-6643-3. DOI: 10.1109/ICM.2000.884805.

- [3] GHALLAB, Y. H., W. BADAWY, K. V. I. S. KALER and B. J. MAUNDY. A Novel Current-Mode Instrumentation Amplifier Based on Operational Floating Current Conveyor. *IEEE Transactions on Instrumentation and Measurement*. 2005, vol. 54, no. 5, pp. 1941–1949. ISSN 0018-9456. DOI: 10.1109/TIM.2005.854254.

- [4] GHALLAB, Y. H. and W. BADAWY. A New Differential PH Sensor Current Mode Readout circuit using only two Operational Floating Current Conveyor. In: *IEEE International Workshop on Biomedical Circuits and Systems*. Singapore: IEEE, 2004, pp. 13–16. ISBN 0-7803-8665-5. DOI: 10.1109/BIOCAS.2004.1454145.

- [5] PANDEY, N., P. TRIPATHI, R. PANDEY and R. BATRA. OFCC based Logarithmic Amplifier. In: International Conference on Signal Processing and Integrated Networks (SPIN). Noida: IEEE, 2014, pp. 522–525. ISBN 978-1-4799-2865-1. DOI: 10.1109/SPIN.2014.6777009.

- [6] PANDEY, N., R. PANDEY, D. NAND and A. KUMAR. Current-mode rectifier configuration based on OFCC. In: International Conference on Signal Propagation and Computer Technology (ICSPCT-2014). Ajmer: IEEE, 2014, pp. 533– 536. ISBN 978-1-4799-3139-2. DOI: 10.1109/IC-SPCT.2014.6884960.

- [7] GHALLAB, Y. H., W. BADAWY, K. V. I. S. KALER, M. A. EL-ELA and M. H. ELSAID. A New Second-order Active Universal Filter with Single Input and Three Outputs Using Operational Floating Current Conveyor. In: 14th International Conference on Microelectronics. Beirut: IEEE, 2002, pp. 42–45. ISBN 0-7803-7573-4. DOI: 10.1109/ICM-02.2002.1161492.

- [8] GHALLAB, Y. H., M. A. EL-ELA and M. EL-SAID. A novel universal voltage mode filter with

- three inputs and single output using only operational floating current conveyor. In: *Proceedings of 12th International Conference on Microelectronics*. Tehran: IEEE, 2000, pp. 95–98. ISBN 964-360-057-2. DOI: 10.1109/ICM.2000.916422.

- [9] GHALLAB, Y. H. and W. BADAWY. The Operational Floating Current Conveyor and its applications. *Journal of Circuits, Systems, and Computers*. 2006, vol. 15, iss. 3, pp. 351–372. ISSN 0218-1266. DOI: 10.1142/S0218126606003118.

- [10] PANDEY, N., D. NAND and Z. KHAN. Single input four output current mode filter using operational floating current conveyor. Active and Passive Electronic Components. 2013, vol. 2013, iss. ID 318560, pp. 1–8. ISSN 1563-5031. DOI: 10.1155/2013/318560.

- [11] PANDEY, N., D. NAND and Z. KHAN. Operational floating current conveyor based single input multiple output transadmittance mode filter. Arabian Journal of Science and Engineering. 2014, vol. 39, iss. 11, pp. 7991–8000. ISSN 2191-4281. DOI: 10.1007/s13369-014-1369-z.

- [12] HASSAN, H. M. and A. M. SOLIMAN. Novel CMOS realizations of Operational Floating Current Conveyor and applications. *Jour*nal of Circuits, Systems, and Computers. 2005, vol. 14, iss. 6, pp. 1113–1143. ISSN 1793-6454. DOI: 10.1142/S0218126605002854.

- [13] GHALLAB, Y. H. and W. BADAWY. A New Design of a Current-mode Wheatstone Bridge Using Operational Floating Current Conveyor. In: International Conference on MEMS, NANO and Smart Systems. Cairo: IEEE, 2006, pp. 41–44. ISBN 1-4244-0899-7. DOI: 10.1109/IC-MENS.2006.348213.

- [14] MILLER, B. D. and R. L. SAMPLE. Instrumentation amplifier IC designed for oxygen sensor interface requirements. *IEEE Journal of Solid State Circuits*. 1981, vol. 16, iss. 6, pp. 677–681. ISSN 0018-9200. DOI: 10.1109/JSSC.1981.1051661.

- [15] SCHAFFER, V., M. F. SNOEIJ, M. V. IVANOV and D. T. TRIFONOV. A 36 V programmable instrumentation amplifier with sub-20 μV offset and CMRR in excess of 120 dB at all gain settings. *IEEE Journal of Solid State Circuits*. 2009, vol. 44, iss. 7, pp. 2036–2046. ISSN 0018-9200. DOI: 10.1109/JSSC.2009.2021921.

- [16] REDOUTE, J.-M. and M. STEYAERT. An instrumentation amplifier input circuit with a high gain immunity to EMI. In: 2008 International Symposium Electromagnetic Compatibility

- EMC Europe. Hamburg: IEEE, 2008, pp. 1–6. ISBN 978-1-4244-2737-6. DOI: 10.1109/EMCEU-ROPE.2008.4786901.

- [17] WITTE, J. F., J. H. HUIJSING and K. A. A. MAKINWA. A current feedback instrumentation amplifier with 5  $\mu$ V offset for bidirectional high side current sensing. *IEEE Journal of Solid State Circuits.* 2008, vol. 43, iss. 12, pp. 2769–2775. ISSN 0018-9200. DOI: 10.1109/JSSC.2008.2005695.

- DEMOSTHENOUS. [18] RAHAL, M. and Α. A synchronous chopping demodulator and implementation forhigh frequency inductive position sensors. IEEETransactionson Instrumentation and Measurement. 2009, vol. 58, iss. 10, pp. 3693-3701. ISSN 0018-9456. DOI: 10.1109/TIM.2009.2019314.

- [19] STEYAERT, M. S. J. and W. M. C. SANSEN. A micropower low noise monolithic instrumentation amplifier for medical purposes. *IEEE Journal of Solid State Circuits*. 1987, vol. 22, iss. 6, pp. 1163–1168. ISSN 0018-9200. DOI: 10.1109/JSSC.1987.1052869.

- [20] MARTINS, R., S. SELBERHERR and F. A. VAZ. A CMOS IC for portable EEG acquisition systems. *IEEE Transactions on Instrumentation and Measurement*. 1998, vol. 47, iss. 5, pp. 1191–1196. ISSN 0018-9456. DOI: 10.1109/19.746581.

- [21] YEN, C.-J., W. Y. CHUNG and M. C. CHI. Micro-power low offset instrumentation amplifier IC design for biomedical system applications. *IEEE Transactions on Circuits Systems I: Regular papers*. 2004, vol. 51, iss. 4, pp. 691–699. ISSN 1549-8328. DOI: 10.1109/TCSI.2004.826208.

- [22] NG, K. A. and P. K. CHAN. A CMOS analog front-end IC for portable EEG/ECG monitoring applications. IEEE Transactions on Circuits Systems I: Regular papers. 2005, vol. 52, iss. 11, pp. 2335–2347. ISSN 1549-8328. DOI: 10.1109/TCSI.2005.854141.

- [23] YAZICIOGLU, R. F., P. MERKEN, R. PUERS and C. V. HOOF. A 60  $\mu$ W 60 nV/ $\sqrt{\rm Hz}$  readout front-end for portable biopotential acquisition systems. *IEEE Journal of Solid State Circuits*. 2007, vol. 42, iss. 5, pp. 1100–1110. ISSN 0018-9200. DOI: 10.1109/JSSC.2007.894804.

- [24] WANG, C.-C., C.-C. HUANG, J.-S. LIOU, Y.-J. CIOU, I.-Y. HUANG, C.-P. LI, Y.-C. LEE, and W.-J. WU. A mini-invasive long term bladder urine pressure measurement ASIC and system. *IEEE Transactions on Biomedical Circuits*

- Systems. 2008, vol. 2, iss. 1, pp. 44–49. ISSN 1932-4545. DOI: 10.1109/TBCAS.2008.921601.

- [25] WILSON, B. Universal conveyor instrumentation amplifier. *Electronic Letters*. 1989, vol. 25, iss. 7, pp. 470–471. ISSN 0013-5194. DOI: 10.1049/el:19890323.

- [26] AGOURIDIS, R. J. FOX. D. C.  $\operatorname{and}$ Transresistance instrumentation amplifier. Proceedings of the IEEE. 1978. vol. 66, iss. 10, pp. 1286–1287. ISSN 0018-9219. DOI: 10.1109/PROC.1978.11125.

- [27] PANDEY, R., N. PANDEY and S. K. PAUL. Electronically tunable transimpedance instrumentation amplifier based on OTRA. *Journal of En*gineering. 2013, vol. 2013, iss. ID 648540, pp. 1–5. ISSN 2051-3305. DOI: 10.1155/2013/648540.

#### About Authors

Neeta PANDEY did M.Tech. (Microelectronics) from Birla Institute of Technology and Sciences, Pilani, Rajasthan, India and Ph.D. from Guru Gobind Singh Indraprastha University, Delhi, India. At present she is Associate Professor in Department of Electronics and Communication Engineering, Delhi Technological University, Delhi. A life member of ISTE, and a member of

IEEE, USA. She has published papers in International, National Journals of repute and conferences. Her research interests are in Analog and Digital VLSI Design.

Deva NAND did B.Tech (Electronics and Communication Engineering), M.Tech (Microelectronics and VLSI Design) from Kurukshetra University, Kurukshetra, India and he is pursuing Ph.D. from Delhi Technological University, Delhi, India. At present he is Assistant Professor in Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, India. His research interests include Analog Mixed Signal VLSI Design and Digital VLSI Design.

V. Venkates KUMAR pursuing B.Tech (Electronics and Communication Engineering) from Delhi Technological University, Delhi, India. His research interests include Analog VLSI Design.

Varun KUMAR AHALAWAT pursuing B.Tech (Electronics and Communication Engineering) from Delhi Technological University, Delhi, India. His research interests include VLSI Design.

Chetna MALHOTRA pursuing B.Tech (Electronics and Communication Engineering) from Delhi Technological University, Delhi, India. Her research interests include Analog Electronics and VLSI Design.