### Spacecraft Supercomputing Experiment For STP-H6 on ISS

SSIVP

#### **Investigators and Students**

<u>Sebastian Sabogal</u>, Patrick Gauvin, Brad Shea, Daniel Sabogal, Antony Gillette, <u>Christopher Wilson</u>, Ansel Barchowsky, Alan D. George – CHREC University of Pittsburgh Gary Crum, Tom Flatley – NASA Goddard Space Flight Center

#### **Research Partners**

**DoD Space Test Program & CHREC Consortium Members**

Research highlighted in this presentation was supported by CHREC members and by the I/UCRC Centers Program of the National Science Foundation under Grant No. IIP-1161022.

National Science Foundation's

Industry/University Cooperative Research (I/UCRC) Program

- Acknowledgements and Programs

- Technology and CSP Concept

- Mission Design & Architecture

- $\circ$  Goals and Objectives

- Hardware & Software

- Mission Computing & Sub-Experiment

- Parallel & Reliable Computing

- GaN Sub-Experiment

- Conclusions

# Acknowledgements & Programs

### Acknowledgements

- SSIVP is a research mission at Pittsburgh CHREC Site

- NSF Center for High-Performance Reconfigurable Computing (CHREC)

- Founded in 2007

- Comprises 4 university sites and over 30 industry and government partners

- SSIVP is collaborative effort

- Builds on success and experience of STP-H5/CSP experiment

- Key development partners:

- DoD Space Test Program

- NASA Goddard Space Flight Center

- University of Pittsburgh's Mechanical Engineering and Materials Science Department & Electric Power Systems Laboratory

Universities Basic Research

CHREC

Applied R&D Industry & Government

#### See www.chrec.org for more info

### **Space Test Program**

#### Space Test Program – Houston

- Provides sole interface to NASA for all DoD payloads on International Space Station (ISS)

- Provides timely spaceflight, payload readiness, management, and technical support for safety and integration

### History of Mission Success

- Build upon successes of HREP, MISSE 6/7/8, STP-H3, STP-H4, STP-H5 while incorporating valuable lessons learned

- STP in-house contractor (MEI Technologies) expertise allows for aggressive 2-year build/integration schedule

- Aerospace Corp provides assistance to Houston team with leadership and mission assurance roles

#### Image Courtesy DoD Space Test Program

# Technology and CSP Concept

### **CSP** The Concept

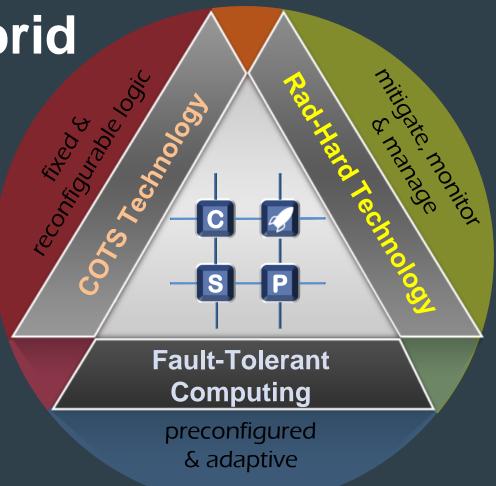

### **Multifaceted Hybrid**

Space Computing

Hybrid processor (multicore CPU + FPGA subsystem)

Hybrid system (commercial + rad-hard)

Robust Design (Novel mix of COTS, rad-hard, & FTCA)

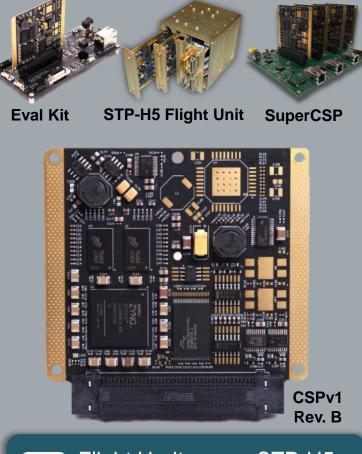

### CHREC Space Processor (CSPV1)

### Easy Development with CSP

- Selective component population scheme supports Engineering Model (EM) and Flight Design

- Rapid and cost-effective design prototyping using evaluation kit or Zedboard / Zybo / Pynq board

- Downloadable example software designs and configurations (Linux/RTEMs cFE etc...)

#### Specifications:

- Xilinx Zynq 7020 (ARM dualcore Cortex-A9 + Artix-7 FPGA)

26 Configurable ARM GPIO Pins

- (1-4) GB NAND Flash

- (256 MB-1 GB) DDR3

- Dedicated Watchdog Unit

- Internal Power Regulation

ARM GPIO Pins

- 12 Single-Ended FPGA I/O Pins

- 24 High-Speed

Differential Pairs

Flight Heritage on STP-H5, Radiation & Env. Tested

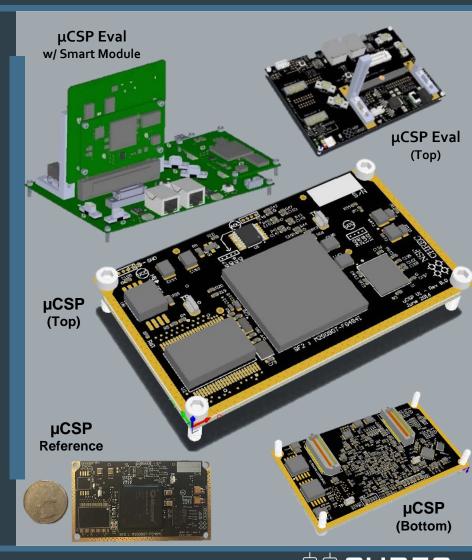

### µCSP Rev. B Flight Computer

#### **Even Smaller Solutions...**

- Multifaceted hybrid processor at center of CSP Concept

- Even lower SWaP-C profile than CSPv1 for small spacecraft missions

- Provided template for "Smart Module" designs

#### **Specifications:**

- SmartFusion 2 (ARM Cortex-M3 + FPGA)

- 64 Mb NOR Flash

- •1 Gb LPDDR3

- Dedicated Watchdog Unit

- ADC for board temp and 2 ch. For flyleaded measurements

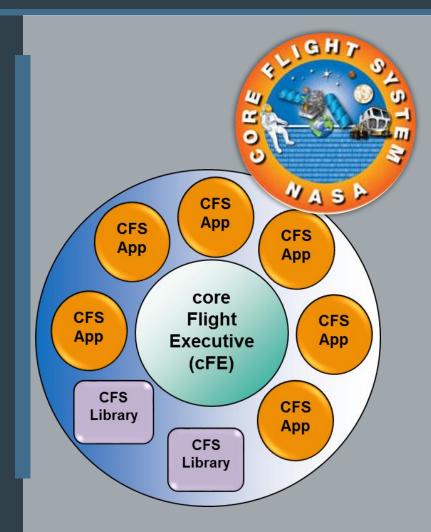

### **Core Flight Executive**

### Description

- NASA Goddard's **reusable** flight-software framework

- Open source version of cFE and cFS available at SourceForge

- Additional information at cfs.gsfc.nasa.gov and coreflightsoftware.org

- Perform local device management, software messaging, & event generation

- Flight heritage on multiple missions, but specifically STP-H5/CSP

### Core Components

- Core Flight Executive (cFE)

- Mission-independent software services

- Core Flight System (cFS)

- Applications and libraries running on cFE

# Mission Design & Architecture

RAFT

### **SSIVP Introduction**

#### Motivation

Develop, demonstrate, and evaluate nextgen technologies for space supercomputing, featuring image and video processing

Run parallel jobs and apps from ground (just like those sent to HPC center), but to cluster in space instead

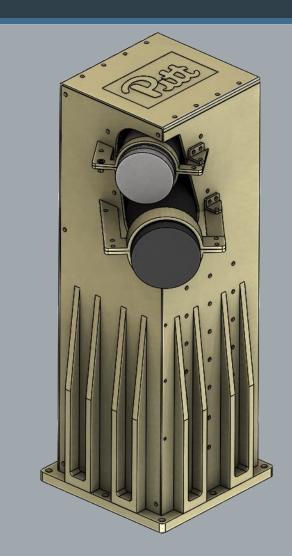

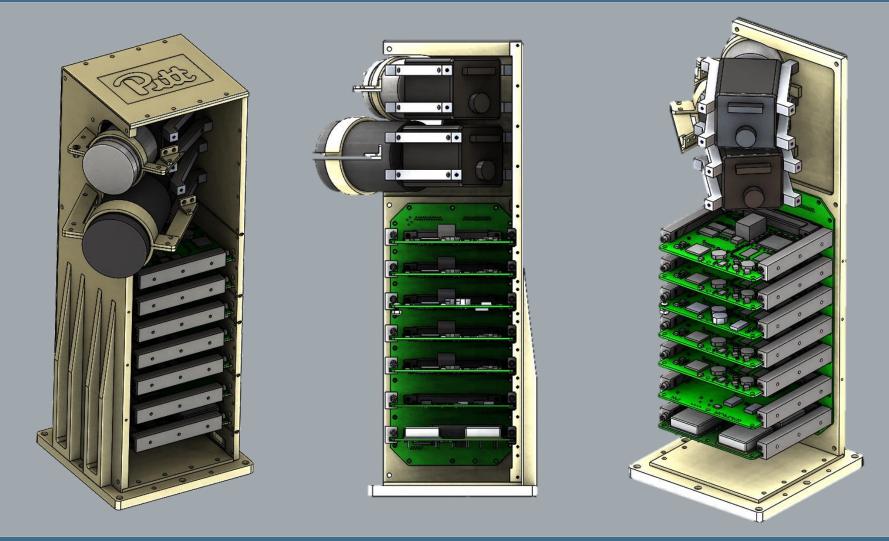

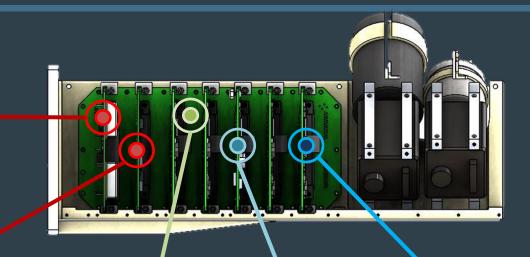

3U computing payload (5 CSPs, 1 μCSP, Power, Backplane) 2 image sensors

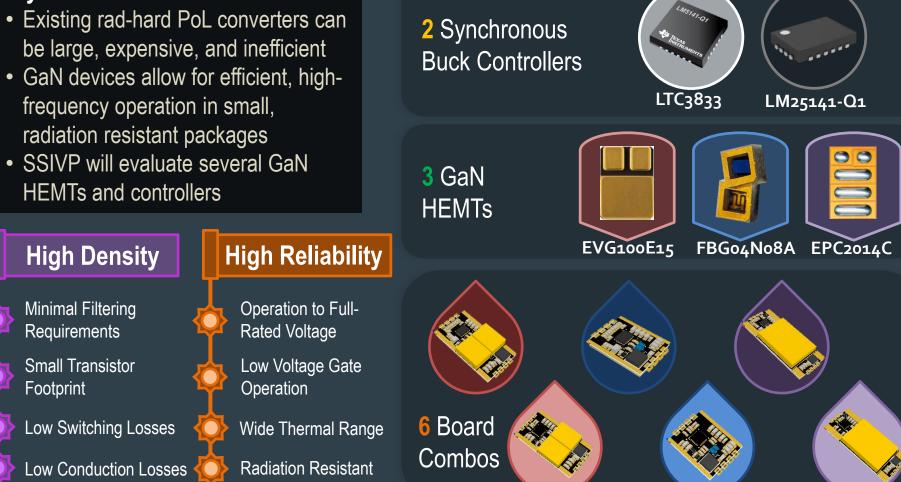

SSIVP will evaluate several GaN HEMTs and controllers

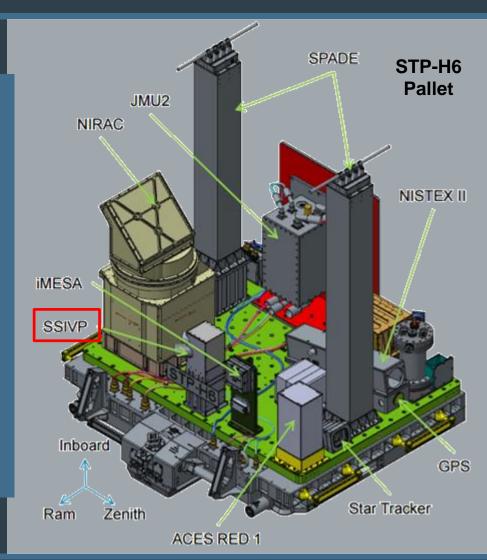

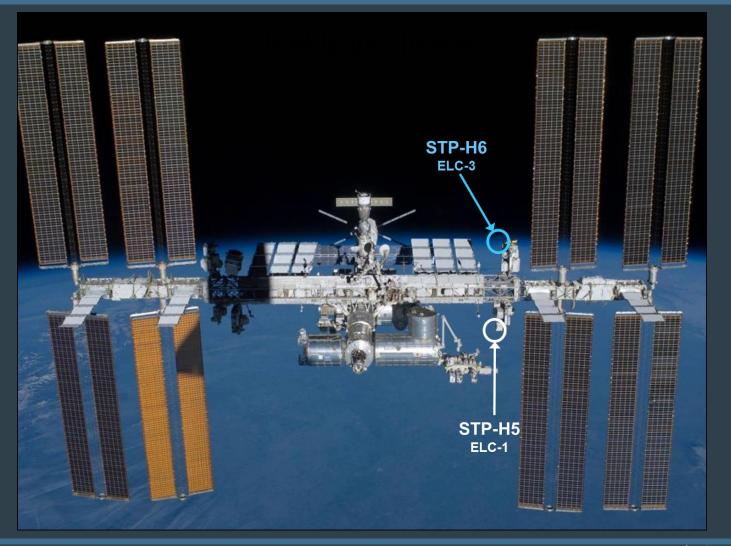

### **STP-H6** Location

Image Courtesy DoD Space Test Program

### **SSIVP** Specifications

30.22 W

26.10 W

17.02 W

### Main Assembly

• Mass: ~9.5lbs

### **Power Interface**

- Max SSIVP (All Cameras / Full Processing):

- Nominal Power:

- Min (Cameras Off):

### Data Interface

- Data rate:

- Average throughput:

931Kbaud / 737.28 kbps 737.28 kbps / 2 kbps

### Debug Interface

Capped for flight: Debug signals for 5 CSPv1s UART, 1 uCSP UART, Power Good, Heart beat and 2 JTAG Ports, 3 total connectors

### Additional Views

### **SSIVP Hardware**

Power Card

Design card to provide regulation to entire STP-H6/SSIVP flight unit

#### Smart Module

Prototype for Smart Module Designs, features GaN Sub-Experiment, accelerometer, RTDs and µCSP

SSIVP Backplane Design supports specific topology for 5 CSPv1 cards and smart module with µCSP

### CSPv1 Rev. C

Even more radhard successor

**CSPv1 Rev. B** Original CSPv1 flight card

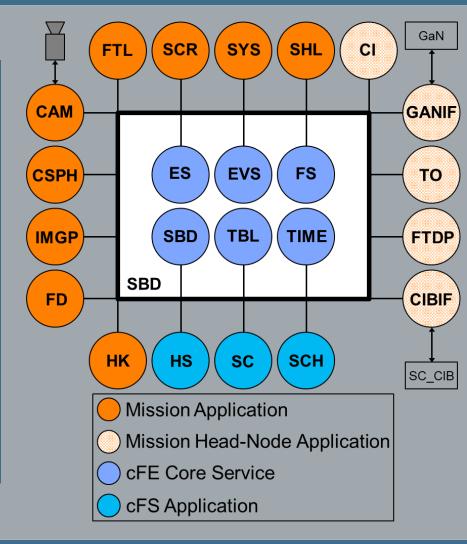

### SSIVP Software

### Flight Software

- CSPv1 flight software is Wumbo Linux, lightweight, custom operating system, based on Xilinx's Linux kernel fork and BusyBox

- Wumbo Linux is developed using Buildroot

### **CFS** Applications

Collection of adopted and custom cFS applications

### SBD (Software Bus Distributed)

- Augmented version of cFE/SB

- Adds inter-node comm. support to cFE's messaging system

- Uses peer discovery and publish/subscribe msg features in OMG's RTPS protocol

## Mission Computing & Sub-Experiment

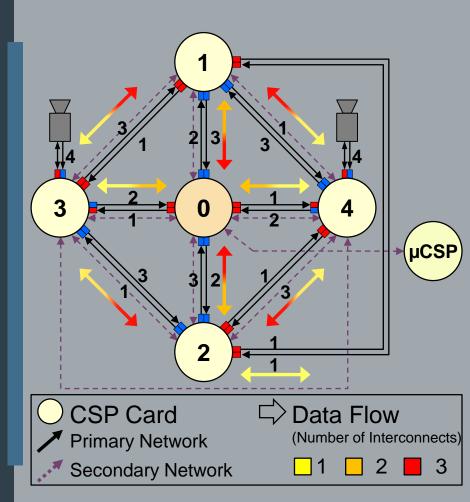

### Network Topology

#### **Two Network Architecture**

- Primary network connects CSPv1 nodes with point-to-point differential signals

- Secondary network connects CSPv1 nodes with point-to-point, single-ended signals

#### Asymmetric Bandwidth

- Primary network is designed to optimize communication for scatter-gather applications

- Camera nodes have more transmission bandwidth

- Head node has more receiving bandwidth

#### Reconfigurable Network

Networking interface reside in Zynq FPGA and can be **reconfigured post-launch**

#### Custom Design

Custom networking interface, called Sabo-Link, leverages SerDes resources in Zynq FPGA for highperformance serial communication

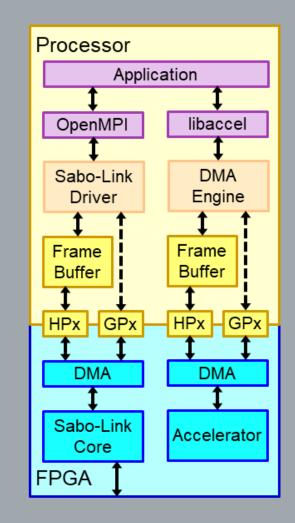

### **Parallel Computing**

Goal of SSIVP to enable Super Computing concepts with high-performance, parallel, and distributed computing

#### Enables High-Performance Computing

- Network driver support for native networking applications including OpenMPI

- Libraries and resources for **OpenMP** and **NEON**

#### Advanced Acceleration Framework

- Includes frameworks for inter-node communication and FPGAbased hardware acceleration

- Acceleration stack includes an FPGA-based image or video hardware accelerator, DMA-engine character device driver, and custom userspace library, called libaccel

#### Partial Reconfiguration

Partial Reconfiguration is used to alternate between FPGA sub-designs at runtime

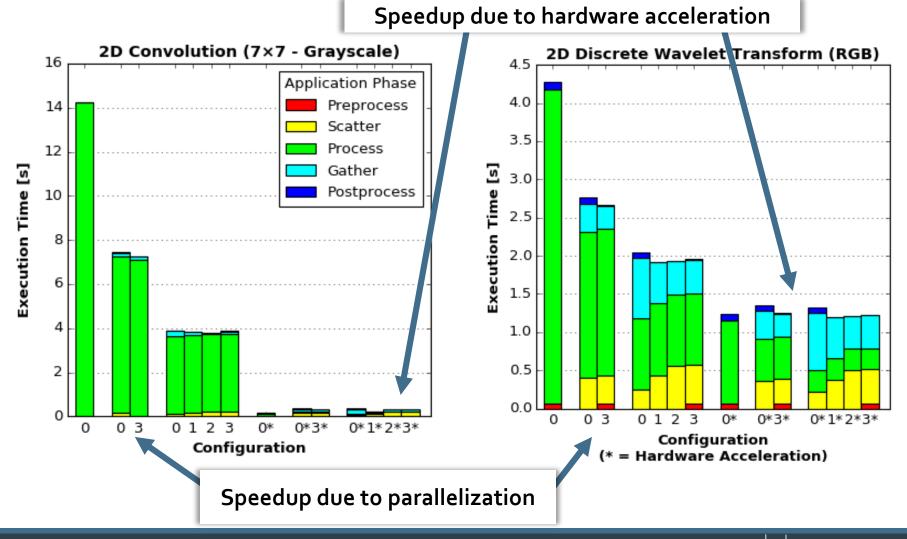

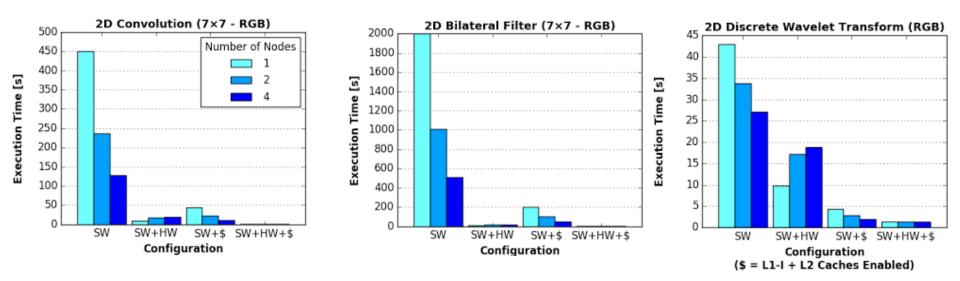

### **Results by Application Phase**

### **Results by Node Number**

Near-linear speedup with number of nodes

Significant gains with hardware acceleration

Performance benefits with caches enabled (reliability trade-off consideration)

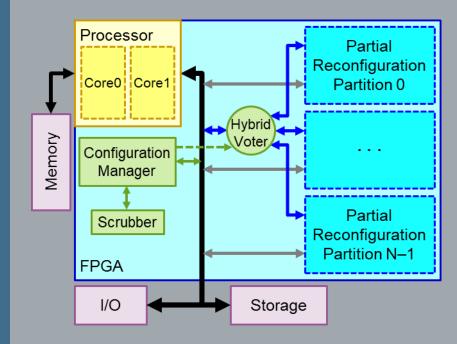

### **Dependable Computing**

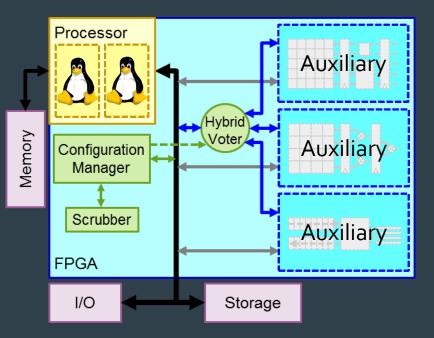

#### Hybrid Adaptive Reconfigurable Fault Tolerance

- Framework for Adaptive Fault-Tolerance on FPGA-based Hybrid SoCs

- Realize fault-tolerant strategy to apply over both fixed and reconfigurable architectures of SoC

#### Modes in CPU and FPGA Subsystems

- Adapt processor cores for symmetric multiprocessing (SMP) or asymmetric multiprocessing (AMP)

- Adapt FPGA partial reconfiguration partitions with HW accelerators or soft processors in simplex, duplex, or triplex redundancy schemes

#### Environmentally Responsive

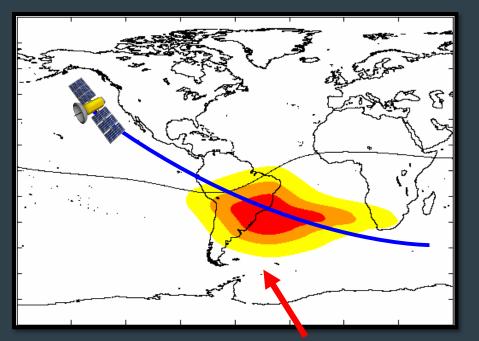

Adapt to dynamic upset rate by repurposing system resources for reliability or performance

### **Concept of Operation**

Reliability Mode 2 HPS in AMP mode SPS has 1 triplex soft-core

South Atlantic Anomaly

### **GaN PoL Sub-Experiment**

#### Why GaN?

### Conclusions

### • Major challenges lie ahead

- Escalating app demands in harsh environments

- Tightening constraints of platform, budget, process

- Necessitates adeptly doing more with less

### • High-performance experiments on STP-H6

- Focus upon validating scalability of CSPv1 flight design

- Submit compute intensive parallel jobs to onboard system

- Download exciting science and technology results

- Record vital heath & status, images, and upset rates

- Push bounds of possibility in space

- Demonstrate experimental technology and methods in space with secondary objectives

### More information?

Dr. Alan D. George (PI), Department Chair, R&H Mickle Endowed Chair, Full Professor, and NSF CHREC Center Director

NSF Center for High-performance Reconfigurable Computing (CHREC) ECE Department, University of Pittsburgh 1238D Benedum Hall, 3700 O'Hara Street Pittsburgh, PA 15261 412-624-9664 Email: alan.george@pitt.edu or alan.george@chrec.org

#### Christopher Wilson, SSIVP Experiment Manager

Email: christopher.wilson@chrec.org

#### Gary Crum, Aerospace Technologist - Data Systems

Code 587 - Science Data Processing Branch NASA Goddard Space Flight Center Building 23, Room W315 Greenbelt, MD 20771 Office: (301) 286-3713 Email: gary.a.crum@nasa.gov

200 SOCO ++10

134 121 41

**DNP** ite.

E+ 18 ......

IC IN

$\mathcal{L}$

00

(P) In

2510 ISIC

ARM I.O B FP6A Bank 3 FP6A Bank 3

Call Call

e e