# Politecnico di Torino

# Porto Institutional Repository

[Article] Efficient and reliable fault analysis methodology for nanomagnetic circuits

## Original Citation:

Turvani Giovanna; Riente Fabrizio; Cairo Fabrizio; Vacca Marco; Garlando Umberto; Zamboni Maurizio; Graziano Mariagrazia (2016). *Efficient and reliable fault analysis methodology for nanomagnetic circuits*. In: INTERNATIONAL JOURNAL OF CIRCUIT THEORY AND APPLICATIONS, vol. 45 n. 5, pp. 660-680. - ISSN 1097-007X

Availability:

This version is available at: http://porto.polito.it/2666441/ since: November 2016

Publisher:

Wiley

Published version: DOI:10.1002/cta.2252

Terms of use:

This article is made available under terms and conditions applicable to Open Access Policy Article ("Public - All rights reserved"), as described at <a href="http://porto.polito.it/terms\_and\_conditions.html">http://porto.polito.it/terms\_and\_conditions.html</a>

Porto, the institutional repository of the Politecnico di Torino, is provided by the University Library and the IT-Services. The aim is to enable open access to all the world. Please share with us how this access benefits you. Your story matters.

(Article begins on next page)

# Efficient and Reliable Fault Analysis Methodology for NanoMagnetic Circuits

G. Turvani<sup>a,\*</sup>, F. Riente<sup>a</sup>, F. Cairo<sup>a</sup>, M. Vacca<sup>a</sup>, U. Garlando<sup>a</sup>, M. Zamboni<sup>a</sup>, M. Graziano<sup>b,a</sup>

#### Abstract

The increasing issues in scaled CMOS circuits fabrication favor the flourishing of emerging technologies. Due to their limited sizes, both CMOS and emerging technologies are particularly sensitive to defects that arise during the fabrication process. Their impact is not easy to analyze in order to take the necessary countermeasures, especially in the case of circuits of realistic complexity based on emerging technologies. In this work we propose a new methodology supported by an efficient and reliable tool for the identification of the impact of faults in complex circuits implemented using the emerging technology we are focusing on in this case: NanoMagnetic Logic.

The methodology is based on three main steps. I) We performed exhaustive physical level simulations of basic blocks based on a detailed finite-element tool in order to have a full characterization, to know their properties in presence of defects and to have a solid reference point for the following steps. II) We developed a model (FANOMAG) for the basic blocks behavior suitable for simulations in presence of defects of complex circuits, i.e. lighter than a physical level one, but accurate enough to capture the most important features to be inherited at circuit level. III) Starting from a physical design of complex circuits, that we perform using a specific design tool we developed, i.e. ToPolinano, we simulated using Fanomag, now embedded in our ToPolinano tool, the behavior of circuits in presence of multiple sets of fabrication defects using a MonteCarlo approach now included in ToPolinano as new feature.

The major outcome is then a powerful methodology and tool capable to analyze with a good accuracy NML complex circuits and architectures both in ideal conditions and in presence of defects with remarkable performance in terms of simulation times.

Keywords: Emerging Technologies, Lithography, Quantum Dot Cellular Automata, NanoMagnet Logic, Molecular QCA

Email address: giovanna.turvani@polito.it (G. Turvani)

<sup>&</sup>lt;sup>a</sup>Department of Electronics and Telecommunications, Politecnico di Torino, Italy <sup>b</sup>London Centre for Nanotechnology, University College London, United Kingdom

<sup>\*</sup>Corresponding author

#### 1. Introduction

The scaling process has given to CMOS technology a long and successful life. Shrinking transistors sizes has lead to a continuous increment in speed and decrement of power consumption. However, according to the ITRS Roadmap [1], the scaling process is reaching its limits and has already started to slow down. This is due mainly to increasing difficulties in the fabrication processes and to the impact of leakage currents [2, 3]. As a consequence many new technologies are being studied as alternative or complement to CMOS transistors. One of these new technologies is based on the Field Coupled Nanocomputing (FCN) principle. It is derived by the former Quantum Dot Cellular Automata (QCA) paradigm [4] and has been mapped on several physical implementations. A full background is given in section 2. Here it is enough to say that the information is propagated not on the basis of conduction, but exploiting different physical properties, as, for example, coulomb interaction or (anti)ferromagnetic influence. We focus here on the magnetic implementation, since it is at the moment more mature from the technological point of view. Moreover it is considered promising especially in terms of power consumption, even though it has reduced properties in terms of maximum operating frequency.

Regardless of the implementation, FCN technology is by nature particularly sensitive to errors due to defects that can occur during the fabrication process or to external conditions, like temperature or noise. In this work we aim at demonstrating the method and we decided to focus on the first cause, however the methodology can be applied to the second as well. Since the technology itself is based on identical cells, fabrication defects that change a cell size and position can severely affect circuits behavior. Several works in literature analyze the impact of defects and faults on generic QCA circuits [5][6][7][8], studying which type of faults are possible and how to model them. Other works are focused on the test methodology that is required to analyze the impact of faults and defects on circuits behavior [9][10][11]. To develop defect tolerant circuits authors normally try to change the topology of the basic device, in order to obtain a more robust logic gate [12][13]. All these works are related to the generic QCA paradigm, using as base cell the ideal cell (Fig. 1.A explained in section 2) rarely with relation to its realistic physical implementation. In the NML case, technology is more mature, since NML based circuits are feasible with current fabrication processes and detailed physical level simulations reproducing both ideal and defective devices are possible. Previous works present formal methodologies to design correct layouts [14] and address fabrication defects in NML using simulations [15][16][17] or experiments [18][19][20][21][22]. However, the analysis remains limited to simple elementary cells and it is not updated to the recent developments.

In this paper we present a general methodology to analyze the effect of faults generated by fabrication defects on complex NML circuits. The importance of exploring the behavior in defective conditions of a circuit of reasonable complexity relies not only on the unavoidable comparison to CMOS circuits that have to be done in similar conditions, but also on the fact that defects or conditions are not uniformly distributed in a big circuit, neither in space nor in time. Our approach is favored by the availability of all the tools required to successfully implement the methodology, i.e. a physical level simulator (OOMMF [23]) and ToPoliNano [24][25], a CAD tool we developed to automatically

place, route and simulate high complexity NML circuits. The **innovative contributions** of this work follow.

- We analyzed elementary NML blocks currently proposed in literature using a physical level simulator (OOMMF): this updates previous works in terms of characterization, and especially gives a solid understanding and reference for the other contributions in the following.

- We adapted a model for the description of the information propagation in NML, based on physical properties, now suitable for implementation in high level simulators.

- We embedded the model into our ToPoliNano tool that is now able to simulate a NML circuit at the layout level enriched by the new physical level model. The ensemble of the simulation engine for NML in ToPoliNano and the simplified model will be hereinafter named as Fanomag (fast nanomagnet simulator). This ensemble allows to simulate with a high level of accuracy NML circuits of complexity that using a physical simulator would require enormous amount of time and memory (if feasible).

- We analyzed and characterized NML circuits considering random set of defects using the FANOMAG extension in TOPOLINANO adding a MonteCarlo approach to the simulator. This allows to remarkably speed-up the process of analyzing the impact of defects not only on the same elementary blocks analyzed in the first point, but also on circuits of higher complexity that with physical simulators would be impossible to analyze.

- We provided as a consequence a detailed evaluation of faults related to misalignment defects that can arise during the fabrication process in case of NML circuits, and give then feedback to technologists. This represent an infrastructure that can eventually handle other problems such as temperature and other defects.

In the next section we give the necessary background (Sec. 2). The methodology is presented in Sec. 3. Specific approaches adopted elementary block analysis with physical level simulations are in Sec. 3 and the description of models and methods implementations for both elementary and complex circuits is in Sec. 4. An appendix includes details set of data and equations. Results are summarized in Sec. 5, while conclusions and perspective works are in Sec. 6.

## 2. Background on FCN (QCA) and NML

The main appeal of the general QCA approach is the basic physical principle used to represent the digital information. Instead of a voltage level or current value a charge configuration is used. The basic ideal element is a square cell with four quantum dots on its corners (Fig. 1.A). Due to electrostatic repulsion at the equilibrium only the two dots on the diagonals can be filled. Since there are two diagonals only two states are

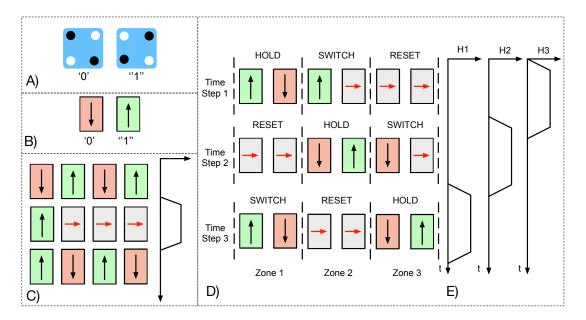

Figure 1: A) QCA ideal square cell. Four quantum dots are placed at each corner and filled with electrons. Only two charge configurations are possible and can be therefore used to represent logic values '0' and '1'. B) NML technology fundamentals. Single Domain nanomagnets are used to represent logic values. C) NML clock. An external magnetic field is used to force magnets in an Intermediate unstable state, allowing therefore signals propagation. D) Clock zones. Circuits are divided in area made by a limited number of magnets. E) Multiphase clock. At each clock zone a different clock signal is applied.

therefore possible. The consequence is that the cell can have only two distinctive charge configurations that represent the logic values '0' and '1' (Fig. 1.A) [26]. Circuits can be organized simply placing cells near each other. Information is driven through the circuit thanks to electrostatic interaction among neighbor cells [27].

NanoMagnet Logic. When a magnet is approximately smaller than 100nm it falls into the single domain condition. Only one magnetic domain is present and, choosing an appropriate shape or material, only two magnetic states are possible. In the first implementation of this technology rectangular shaped magnets [28][29] were used. The magnetic shape anisotropy favors the magnetization vector alignement with the longer axis and pointing either downward, defining a logic '0' (Fig. 1.A), or upward, defining a logic '1' (Fig. 1.A). Circuits are built aligning magnets on a plane, information propagates through the circuit thanks to magneto-dynamic interaction among neighbor magnets. To switch magnets from one stable state to the other, a clock mechanism is used [30]. As depicted in Fig. 1.B, magnets are forced in an intermediate (RESET) state through an external mean. Since this state is unstable, magnets will then realign themselves following the input element. In the first implementation of NML technology the clock was obtained with an external magnetic field [31]. A more recent solution is based on a spin-torque coupling with a current flowing through the magnets [32], which in this case is a Magneto-Tunnel Junction (MTJ) [33]. An ultra low power solution is instead based on an electric field applied to the substrate where magnets are located [34]. The substrate is made with a piezoelectric material, so its deformation drives magnets in the RESET state [35].

Regardless of the mechanism used to force magnets in the RESET state, a multiphase clock is necessary to build complex circuits. Due to thermal noise influence, only a very limited number of magnets can be chained at room temperature [36]. To build large circuits, the area must be partitioned in small clock zones, where only a limited number of magnets is present (Fig. 1.C). Each clock zone is related and subject to one of the three clock signals (Fig. 1.D). Each clock signal has the same shape but a phase difference of 120°. Thanks to this solution when magnets of a clock zone are in the SWITCH state, i.e. the magnetic field is slowly removed and magnets start to switch, magnets on the left are in the HOLD state and behave like an input. Magnets on the right clock zone are in the RESET state and have no influence, as a consequence magnets switch correctly. This situation is repeated at each successive time step. Fig. 1.C highlights the temporal evolution and the signal propagation through the NML wire.

NML circuits can be fabricated with up to date technological processes, so a rich literature of experimental results can be found. Different circuits, from simple wires [31][37] to complex logic gates [38][39] where fabricated and measured. Also the clock mechanism was demonstrated in [40]. The base cell in NML technology is a nanomagnet, a very simple structure but very small. While a magnet does not require a particularly complex fabrication process, the small size and the small gap among magnets require high resolution lithography. As a consequence two main types of defects can occur, misplacement of magnets or magnets with a different shape or size then desired. In our previous work [41] we analyzed the impact of different magnets size and shape on the behavior of NML circuits. In this work, as part of the proposed methodology, we focus on magnets misalignment, verifying what happens if magnets in critical positions inside a device are not in their ideal position. Results are reported in Section 3.

#### 3. Methodology Description

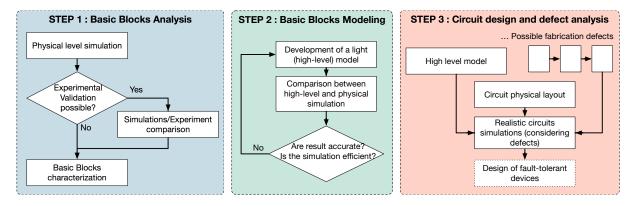

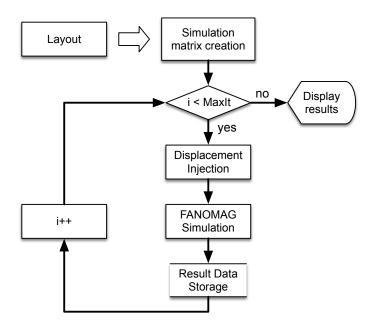

Three main steps identify the methodology we developed: 1) Basic blocks analysis, 2) Basic blocks modeling, 3) Circuits design and analysis with defects. The Basic Blocks Analysis consists in the characterization of basic blocks, like logic gates and other elementary structures, with physical level simulations and experimental results. In the Basic Blocks Modeling phase an high level model of basic blocks is developed, named FANOMAG, using the results of previous step as reference. In the final step, Circuits design and analysis with defects, extensive simulations on complex circuits are obtained exploiting the abovementioned high level model and TOPOLINANO[24][25], a tool we developed that allows automatic place and route of circuits. These simulations highlight, given a possible range of defects, in which conditions a circuit gives a correct output. The flow diagram of the methodology is depicted in Fig. 2.

Basic Blocks Analysis. This is the first step of the methodology, and it represents the fundamental link between logic circuits and their physical behavior. Low level physical simulators, independently on the technology used, require an extremely high computational power and cannot be used to simulated complex circuits. For the same reasons it is almost impossible to run extensive simulation campaigns in order to take into account process variations and defects. This is also true in CMOS for example, where,

Figure 2: Fault analysis methodology

for example, a SPICE or equivalent simulator cannot be used to simulate big circuits. High-level models are therefore developed using as a reference low level simulations, both in the development and in the validation phase.

Different sub-steps can be identified for a thorough characterization.

- Identification of basic blocks of the chosen technology. In the NML case, we have identified 5 critical structures, according to recent literature: the horizontal wire, the vertical wire, the majority voter, AND gates, OR gate.

- Low level simulations of the basic blocks in ideal conditions.

- Low level simulations considering possible defects. In the NML case the list of possible defects include magnets misplacements, magnets with different sizes and shapes, different distances among neighbor magnets. These types of defects are related to process variations. Defects as stuck-at 1 or stuck-at 0 are less frequent and for this reason we only tackle process variations, even though the methodology is flexible and can be extended to other cases as well.

- A final sub-step given by experimental validation would be welcome but is out of the scope of this contribution.

Gathering all the information provided by low level simulations and experiments, the output of this first methodological step is a detailed characterization of basic blocks of the chosen technology. The results of our characterization of NML logic gates is presented in Section 3.

Basic Blocks modeling. The aim of this step is the development of a high level model suitable for the simulation of large circuits. The requirements of this model are two: It must be near to the physical level, and as a consequence coherent with the characterization obtained at the previous step, and it must be light enough to simulate big and realistic circuits. It is by its nature an iterative process. The model is developed, tested on basic blocks and validated with the low level characterization. The physics adopted at this level (explained in Sec. 4) is less accurate w.r.t. the lower level simulations, however the adopted iterative approach assures the validity of the models for what concerns the

correctness of results to be achieved. If the results are enough compliant with the device level analysis and the model does not require high computational resources, then it is safe to proceed to the next step. Otherwise, the model must be refined. The main goal is to obtain a good compromise between simulation speed and accuracy in case of large circuits.

In order to simulate a NML circuit according to the abovementioned properties we distinguished two aspects. One is the physical phenomena describing in general the interaction between magnets. The other is the interaction among magnets considering the circuit organization and layout. In the preliminary approach implemented in our tool ToPolinano we used a simple switch-level model, where magnetization is simplified to a simple logic level. Hence (anti)ferromagnetic basic principles are used to model magnets interaction and a specific algorithm is developed to take into account the circuit organization and layout and then the information propagation through it.

The approach we added in this work instead is based on the use of a simplified physics model as in the following. The equation which drives the dynamic behavior of magnets is the Landau-Lifshitz-Gilbert (LLG) model of micromagnetism. In [42] authors developed a simplified model of LLG equation. This model is normally referred as Macro-Spin approximation and is valid for single domain nanomagnets. In [43] authors developed a tool based on single-domain description to model and design the NML devices. We embedded the Macro-Spin LLG in ToPolinano tool, without considering in this first version of our model the term which takes into account the effects of the temperature. We maintained our original approach for taking into account the circuit layout and for reckoning the information propagation through it. This ensamble is the Fanomagnetic. We can now simulate large circuits, obtaining more accurate results at the cost of increased simulation time with respect to the previous version. It must be noted however, that simulation times are much shorter than classic micromagnetic simulations, while the results obtained are similar. This second methodological step is described in details in Appendix A and 4.2.

Circuits design and analysis with defects. The last step involves the simulation of complex circuits considering the impact of defects. To reach this goal, three inputs are necessary: The high level model developed at the previous step, a set of possible defects and the physical layout of a complex circuit. In the NML case the set of possible defects is a matrix that defines random misplacements for each magnet. In our previous approach as well [25][17] faults were modeled using a probabilistic approach. A fault probability drives magnets toward the correct or wrong state depending on magnets misplacement. With FANOMAG the approach is similar (see Appendix A) except for the use of the physical level model and other refinements for optimizing the simulation speed.

The physical layout of circuits can be obtained drawing by hand the circuit. However, ToPoliNano allows automatic place and route of combinational NML circuits of any size starting from a RTL description of the architecture. The use of ToPolinano allows an easy verification of circuits behavior in presence of defects. These results can then be used as the foundation of defect tolerant devices. This last step is not described in detail in this paper, since it is still a working progress. We instead present the results of physical placement and fault analysis in Section 5, where we give also some hints of our current

work on the possible design of defect tolerant circuits.

The first methodological step suggests a thorough characterization of basic blocks. This can be achieved either by means of low level physical simulators and of experiments. Physical simulators, by their nature, provide an accurate evaluation of a device behavior. However, an experimental validation is always advised for comparison, even though experimental results are not easy to be obtained. Physical simulators notoriously require a lot of computational power, so only small elements can be simulated. This is particularly critical in case of basic blocks characterization in presence of process variations. This requires to repeat a huge number of simulations on the same basic block but in different conditions. For this work our characterization tool of choice is OOMMF [23]. For this reason this has been used to validate the result obtained with ToPoliNano, in other words all the circuits tested with our tool has been also simulated with OOMMF by looking at the final state of the magnets.

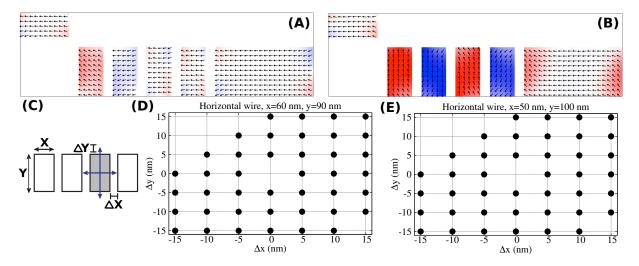

As targets for the characterization we choose the basic and more critical NML structures, namely wires (horizontal, vertical and L-shaped) and logic blocks (Majority Voter, AND/OR gate). It is a work that we already started in [16][41]. In the previous case we focused only on the Majority Voter, changing distances among neighbor magnets. The result of that previous work was that the Majority Voter works with a good reliability even increasing distances among magnets, up to 60nm. The aim of that analysis was to analyze the impact of defects generated by a lithography process with not enough spatial resolution, and, more in general, in case NML circuits could be fabricated with commercial lithographic processes. In this paper we focused on the impact of misalignments in key magnets included in basic NML blocks. This kind of defects has been selected because the model we discuss in Sec.4, which is based on a verified work in literature and used here as a reference, can be correctly applied in the case of defects we are currently considering. The further step when chosing the type of defect is to take into account varying sizes and shapes of different magnets. For this case a specific model has to be developed. Furthermore, temperature and external fields conditions could be also added as possible sources of variations, and in both cases dedicated models have to be studied. The methodology proposed here can be easily extended to these further cases, provided that models are developed and verified first at simple device level. Hereafter, then, all the micromagnetic simulations has been made considering a temperature of 0°K and a mesh equal to 5nm on x, y, z dimension. Smaller mash dimensions would provide more precise results, but this would require higher computational (and timing) costs. simulation results on the horizontal wire can be observed in Fig. 3. Fig. 3.A depicts the initial state of the OOMMF simulation, with all magnets forced in the reset state. Fig. 3.B depicts instead the final simulation step, with magnets correctly aligned in the antiferromagnetic state. The simulation shown is obtained in ideal conditions, with no magnets misplacement. The wire is composed by four chained magnets, since, according to [36], no more than four magnets can be chained in a single clock zone. An horizontal magnet is used to correctly force the first magnet in the desired state, while an helper block [44] is placed at the end of the wire to assure a correct signal propagation. The material used for magnets is Permalloy, with a width of 60nm, an height of 90nm and a thickness of 20nm. The simulations are obtained applying an external magnetic field

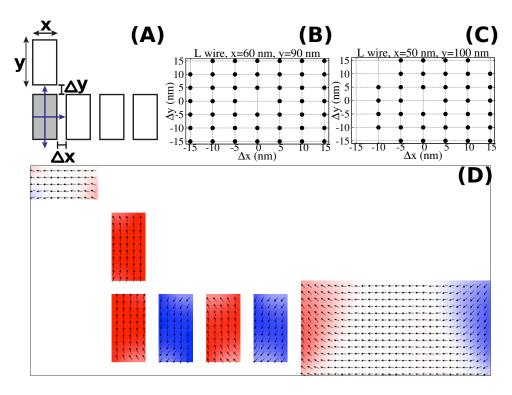

Figure 3: NML horizontal wire characterization. A) Initial step of the OOMMF simulation in the ideal case, without magnets misplacements. B) OOMMF simulation, final state. C) Horizontal wire structure with indication of magnets sizes and displacements. D) Map showing which displacements still allow to the wire to correctly propagate the signal. The maps are obtained considering magnets with a width of 60nm and an height of 90nm. Each point identifies a couple of X and Y displacement, that produces a still working wire. E) Operational maps obtained considering magnets with a width of 50nm and an height of 100nm.

which is then slowly removed. The aim of this phase is to verify whether the final state is correct also in presence of magnet misplacements. As a consequence simulations where repeated many times moving a magnet with respect to its ideal position. Fig. 3.C highlights the wire geometry and magnets displacement. Since magnets separation is 20nm, a maximum displacement of 15nm in both X and Y directions was considered. Results are presented in Figure 3.D, where a map of all working combinations is depicted. Each point of this map represents a combination of horizontal and vertical displacement that leads to a correct final state for the whole wire. Looking at Fig. 3.D it is evident that the horizontal wire in NML technology is a very robust structure, since there are only few conditions where it does not work. We repeated the characterization also considering magnets of  $50 \times 100 \times 20 \, \text{nm}^3$ , to verify if different magnet sizes and aspect ratio lead to a different behavior. However, as can be observed in the results presented in Fig. 3.E, the wire behavior does not change.

The complete characterization of the wires (vertical, L-shaped) and the logic elements (majority gate, and/or gate) can be found in Appendix B.

#### 4. Modeling And Implementation

This section gives an overview about the ToPolinano Tool in subsection 4.1 and a description of the novel contributions. Indeed in subsection Appendix A we present a new model aiming to refine the level of accuracy of our simulator. In subsection 4.2 and 4.3 we discuss respectively Fanomag, for the fast and accurate simulation engine, and the features added to take into account faults derived from process variation during the

simulation process, still maintaining high standards in terms of timing performance.

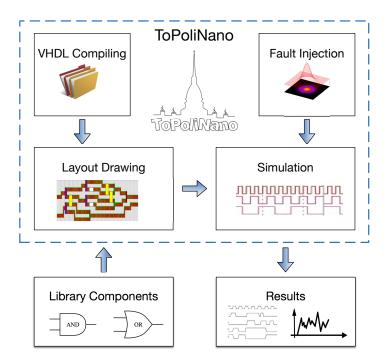

## 4.1. An overview of ToPoliNano

ToPoliNano (Torino Politecnico Nanotechnology) [45], is a CAD tool developed by the VLSI Group of Politecnico di Torino. The aim of this project is to create a new set of methologies and a tool to help researchers to study emerging technologies. Our CAD is indeed able to design and simulate circuits based on different nanotechnologies; up to now we have explored nano-array based technologies [46][47] and NML (Nano Magnetic Logic).

Figure 4: ToPoliNano working principle: circuits described by users in VHDL are parsed and used by the layout engine in order to elborate the physical layout. The simulation process allows to test the logical behaviour of the target circuit. Faults can be injected for simulations run not in ideal conditions. Results are reported as waveforms as well as statistical data.

The tool has been fully developed in C++ with the primary intention to be flexible in order to easily allow the integration of new technologies.

For what concerns the NML technology, ToPolinano is able to automatically design and simulate circuits: Starting from VHDL files it places gates, divides the circuit into clock zones and routes interconnections. The summary flow is shown in Figure 4. When the layout process is completed the simulation engine allows testing the logical behavior of circuits. As well as translational simulators for CMOS technology, ToPolinano uses external input stimuli in order to generate the output waveform, which can be represented in a graphical or textual format.

In this paper we present the implement of a new model aiming to improve both accuracy and execution time. With FANOMAG we have implemented a Macro-Spin LLG

engine and an adapted simulation algorithm capable to simulate quite complex circuits. The following paragraphs discuss our approaches.

As established in the previous paragraphs, NML, like all emerging technologies, is characterized by a high defect rate derived from the manufacturing process [46] [17]. This should be taken into account during the simulation process, thus, we implemented an algorithm able to evaluate the impact of magnet displacements at logical levels as detailed in the final subsection.

## 4.2. FANOMAG Implementation

FANOMAG has been built around the idea of exploiting the power of our ToPoliNano simulation algorithm for NML, already described in [25], together with the new level of accuracy introduced by the Macro-Spin LLG engine. This allows us to drastically speed up the simulation.

The internal representation of circuits within ToPolinano exploits the regularity of the NML structure allowing representing them as matrixes. In other words a circuits can be seen as matrix in which each node can be occupied (or not) by a single magnet. The matrix-visiting algorithm [25] advantage, which guarantees a fast circuit analysis, are then even more evident in the current version, with the introduction of a more computational expensive device model. Moreover, approximating magnets as ellipsoids allows to achieve a tolerable accuracy without any significant loss in term of computational cost.

For the same reason, with this first implementation of FANOMAG we decided to limit the magnetization contribution of the first six neighbors of the target node.

### 4.3. Fault simulation algorithm

Ideally every magnet is equidistant to all its six neighbors. However, in order to make more realistic simulations to take into account possible proces variations, small displacements must be *injected* into the ideal circuit.

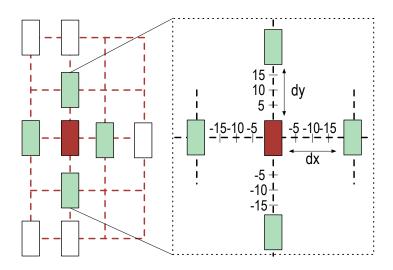

Fig. 5 shows, as an example, the possible shifts of the central magnet of the Majority Voter component. With this implementation all possible combinations of dx and dy are possible. The same approach is repeated for every magnet of the circuit: dx and dy are randomly set within a specific range set through the graphical interface when the simulation matrix is populated. This approach is repeated n times exploiting a Monte-Carlo approach, as depicted in Fig. 6. Considering now the absolute position of each magnet it is possible to calculate the status of each magnet belonging to the switch zone according to the visiting algorithm [17]. Now, every node uses FANOMAG in order to evaluate its status considering all its neighbors in terms of their distances and magnetizations.

#### 5. Results

## 5.1. Comparison between Oommf and ToPoliNano

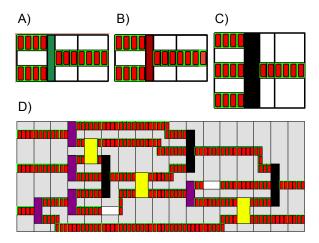

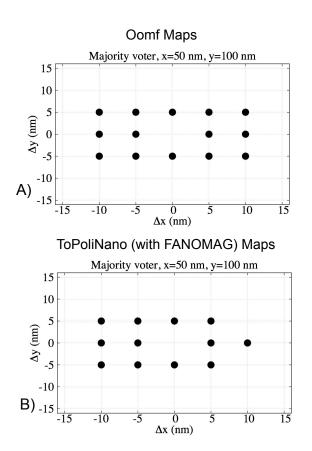

In this section we present an analysis of the Majority Voter circuit simulation obtained both with OOMMF and TOPOLINANO. As a *first step* we tested the FANOMAG simulation engine in order to verify the correctness of the algorithm. To perform the test we considered the circuit layout generated with TOPOLINANO and shown in Figure 7.C, where

Figure 5: Graphical example of a simulation matrix. The circuit represents a Majority Voter in which each magnet occupies a node of the matrix. Ideally every node is equidistant to its neighbors, but considering faults derived from process variations, small displacements (dx and dy) must be injected.

Figure 6: Fault analysis with Monte-Carlo approach: the simulation process is repeates MaxIt times changing randomly the displacement injected for every magnet of the simulation matrix.

the Majority Voter has inputs connected to wires related to a clock phase different from the pure Majority Voter zone (the dark box in the intermediate clock zone identifies the Majority Voter in the internal ToPoliNano representation). Here we consider magnet dimensions of 50nmx100nm.

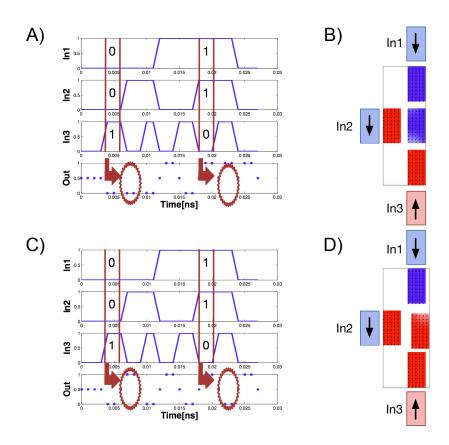

Figure 8.A shows the output waveforms obtained using ToPoliNano in all the possible combinations of inputs. Cases for inputs "001" and "110" are used here as a reference.

Figure 7: Graphical representation obtained through ToPoliNano for: A) And gate, B) Or gate, C) Majority Voter, D) Full Adder

Figure 8: A) and B) represent the simulation results obtained with ToPoliNano and OOMMF, respectively. In these cases no displacements are injected and outputs are correct. Instead figures C) and D) are obtained with dx = 10nm and dy = -10nm with respect to the original position. Here we notice that in D) the output is incorrect for the same input value "001"

The elliptical shapes in the output waveform highlight the output values that are expected to be "0" and "1" in the two combinations, respectively (outputs are shifted of one clock phase because inputs waveforms refer to the left side wires in the clock zone at the left of the Majority Voter zone in Figure 7.C). Figure 8.B shows the inner Majority Voter structure used in the OOMMF simulation. If no displacements (dx = 0nm and dy = 0nm) are injected, the circuit behavior is correct in both cases: The figure shows the case of "001" as input status. Considering instead a displacement of dx = 10nm and dy = -10nm, applied to the central magnet of the Majority Voter, we notice that results are wrong with both simulators. In particular OOMMF simulation is shown in the "001" case.

It is interesting at this point to give some ideas of the different **simulation times**. In the case of one single input combination for the inner Majority Voter the simulation time in the OOMMF case is around 15 minutes on a Linux server with an Intel Xeon E321xx Sandy Bridge with 128 GB of RAM. This does not include the visualization time which is required to analyze the results and not negligible. ToPoliNano requires for the whole Majority Voter circuit described before (having a bigger number of magnets with respect to the simple inner Majority Voter structure) using the same server and in the same conditions approximately 1.5s, including the automatic output waveforms generation. The ratio is then  $TCPU_{oommf}/TCPU_{ToPoliNano} \approx 600$ . If a speculation is done on the time required to analyze bigger circuits and to simulate the impact of process variations with a lot of possible magnets displacement it is immediate to see the remarkable advantage assured by the FANOMAG model.

As a second step to compare the two simulators we iterated the simulation – in all the input configuration – considering all the possible combination of displacement of the central magnet as  $\pm dx$  and  $\pm dy$ . An we repeated this for 5nm and for 10nm displacements. In the case of the smaller displacement (5nm) results are perfectly overlapped for the two simulators. In the case of the bigger one (10nm) results are coherent in all the cases except for two of them, as shown in Figure 9. Notwithstanding this discrepancy, the **accuracy** is high if we consider the overall amount of cases analyzed:  $NCorrect_{ToPoliNano}/Ncorrect_{oomf} = 0.894$ . Furthermore, only experimental validation could give a final word on these considerations, as OOMMF is a simulator and is based on approximated models as well as FANOMAG. We are then satisfied with the results: according to the methodology phase two we remarkably gain in simulation time as requested, at the cost of a small accuracy loss.

The reasons behind this difference can be found in the possible explanation given in the following. OOMMF is based on the solution of Landau-Lifshitz-Gilbert equations. We used in our simulations nanomagnets having rectangular structure. OOMMF discretizes the sample using a grid of cubic cells of a size given by the user (5nm in our case) and considers a uniform magnetization inside each cell. For example, we considered the structure of a Majority Voter, with nanomagnets sizes 50x100 nm, spaced horizontally and vertically by 20nm. The distances among centers of neighboring horizontal nanomagnets is 70nm, and the vertical distance is 120nm. Therefore, we can imagine a grid in which horizontal distance is lower than the vertical distance. Since OOMMF breaks down the nanomagnet structure into many cubic cells, we have an exchange of energy along the whole perimeter of the rectangle, i.e. up to the edge of the rectangular structure. Thus, the final space

Figure 9: Comparison between maps obtained with A) OOMMF and B) ToPoliNano for 10nm displacement. Nanomagnets have in this case a width of 50nm and an heigh of 100nm.

between nanomagnet is equal to 20nm. Even though this explanation should be in depth analyzed from a mathematical point of view, we imagine that this is not the case of the single domain approximation model (section Appendix A). In this case the nanomagnetic particles are considered as dots. We noticed that, if we consider a grid in which the vertical distance is higher than the horizontal one, for example 120nm and 70nm, respectively, in case of 50x100nm nanomagnet, the horizontal coupling is bigger than the vertical case. In particular, what happens is that some configurations of the inputs generate faulty output due to the higher coupling between the output magnet and its left neighbor. This is not correct in the case of the majority gate, where the value of the output should depend on the value of majority of all the inputs without a "preference". This does not happen considering uniform distances both horizontal and vertical, where the output magnet is coupled similarly with its neighbours.

### 5.2. ToPoliNano-FANOMAG faults analysis with Monte-Carlo approach

The high simulation speed and acceptable accuracy results discussed above allowed us to inspect the fault tolerance of nanomagnetic circuits due to magnet misalignment using a thorough approach. Random displacements were applied to each element of the circuit.

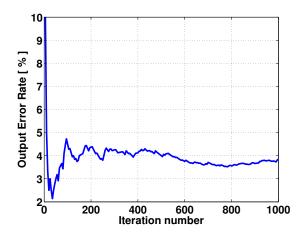

A Monte Carlo like approach were applied in order to cover as much as possible all the possible nanomagnet position within a particular range. The tested circuits are the *AND* gate, *OR* gate, *Majority Voter* and the *full adder* and are shown in figure 7. These are the results of a place& route obtained with ToPolinano. The applied displacements vary from 0nm to 5nm and from 0nm to 9nm in order to avoid magnets overlapping. The number of iterations has been fixed to 1000: A conservative value for which the output error rate (OER) is stable enough, see Figure 10. All the input combinations are exhaustively considered for each MonteCarlo iteration.

Figure 10: Averaged OER over 1000 iteration: Majority Voter circuit

Simulation results are summarized in table 1. Data are directly elaborated by the MonteCarlo engine in ToPoliNano. In particular for each case we show the percentage of faulty cases (when the output is not in accordance with the case without displacements), and the averaged OER. This value is reckoned as the ratio between the number of faulty combinations and the number of input combinations. The overall result show a better reliability in the 60nmx90nm case. This can be expected, because of the more favourable magnets aspect ratio.

Results are confirmed for the Full Adder case. It is worth underlining that the number of clock phases is 17 and the number of magnets 333. This simulation in presence of defects would be simply impossible in the case of OOMMF.

### 5.3. Considerations: some hints for fault tolerant circuits design

As we demonstrated ToPolinano enriched by fanomag is a powerful tool to analyze the impact of defects in NML technology. However, the possibilities offered by this tool do not end here. The results obtained can be used to design NML circuits with a much higher defects tolerance. Defining complete design rules for defect tolerant NML circuits is out of the scope of this article. However, to demonstrate this possibility, we report herein some hints that came up during the NML characterization with both OOMMF and ToPolinano.

• The Majority Voter is a critical component. Even a small process variation of few nanometers can lead the circuit to fail. However, the tolerance to process

| Simulation results |                        |                                                                                                             |                   |                 |

|--------------------|------------------------|-------------------------------------------------------------------------------------------------------------|-------------------|-----------------|

| Circuit            | Magnet Dimensions [nm] | $ \begin{array}{c c} \operatorname{Max} \\ \delta x \\ \operatorname{and} \\ \delta y \\ [nm] \end{array} $ | % of faulty cases | averaged<br>OER |

| Majority Voter     | 50x100                 | 5                                                                                                           | 15.3              | 0.0385          |

| Majority Voter     | 50x100                 | 9                                                                                                           | 48                | 0.1243          |

| Majority Voter     | 60x90                  | 5                                                                                                           | 9.3               | 0.0232          |

| Majority Voter     | 60x90                  | 9                                                                                                           | 32.7              | 0.0833          |

| And / Or           | 50x100                 | 5                                                                                                           | 0.5               | 0.0022          |

| And / Or           | 50x100                 | 9                                                                                                           | 11.6              | 0.044           |

| And / Or           | 60x90                  | 5                                                                                                           | 0.3               | 0.002           |

| And / Or           | 60x90                  | 9                                                                                                           | 9.7               | 0.0283          |

| Full Adder         | 60x90                  | 5                                                                                                           | 46.7              | 0.2642          |

| Full Adder         | 60x90                  | 9                                                                                                           | 69.3              | 0.3213          |

Table 1: Simulation results obtained with ToPoliNano over 1000 iterations

variations can be greatly increased, for example, allowing an increased distance among magnets. Fabricating circuits with magnets distances of 60nm leads to a much robust behavior, up to a 15nm tolerance. Not to mention that magnets with higher distances are easier to fabricate and less defects can occur during the fabrication process.

- The Majority Voter (in the 60x90x20nm<sup>3</sup> case) is less prone to errors if the central magnet move toward the central input element. Designing the Majority Voter placing the central magnet not exactly in the middle, but slightly moved on the left, toward the central input element, leads to a more robust gate.

- AND/OR gates are particularly sensitive to errors when the central magnet is moved in directions opposite to the cut position. In the OR case for example, moving the central magnet downward, leads to wrong results. As a consequence, designing the gate placing the central elements slightly upward increases the magnet robustness.

These conclusions are just an example of the results that can be obtained with ToPoli-Nano coupled to fanomag. As a future work we aim to develop a full set of design rules to help NML circuits designers and will include them in the Place&Route ToPoliNano engine.

#### 6. Conclusions

In this paper we developed a methodology for fault detection in NML technology. The methodology couples both physical level analysis with high level simulations of complex circuits. This has been achieved by using our ToPoliNano CAD tool enriched with a

new model and simulation engine, FANOMAG. It embeds the macro-spin approximation of the LLG equation together with an efficient algorithm to inspect all the magnets in the circuit. Results are validated through oomms simulations and give remarkable speed-up in terms of simulation time ( $\approx 600$  time faster) with a small cost in terms of accuracy. A detailed characterization of NML basic blocks is also presented. Results on both basic blocks and more complex circuits are given in several combination of defects using a MonteCarlo approach. Even though the methodology here presented is specifically tailored for NML technology, it can be easily adapted to other QCA implementations such as out-of-plane NML variants, strained clocked NML, etc . . . .

As future works we are refining our model by adding the possibility of handling other fabrication variation which concern this technology; in particular, we are integrating the effect of the temperature by adding to the LLG equation a highly irregular fluctuating field which depends by the temperature value. We are focusing on the development of a set of design rules for NML defects tolerant circuits. We are also working toward the identification and analysis of further faults and defects that might occur in this technology, like for example non uniform magnetic fields distribution, crosstalk among neighbor clock zones, random changes in magnets size and stuck-at situations.

## Appendix A. Macro-Spin LLG engine

Considering the single domain approximation model described in [42], the dynamic behavior of a sufficiently small nanomagnet, can be described by the solution of the time-dependent single domain Landau-Lifshitz equation. Their explicit form is reported in Eq. A.1. In this formula,  $M_x$ ,  $M_y$  and  $M_z$  represent the magnetization components of the target nanomagnet (i) and  $H_x$ ,  $H_y$  and  $H_z$  are the components of the effective field  $(H_{eff})$ . The other parameters  $M_s$ ,  $\gamma$  e  $\alpha$  represent respectively: i) the saturation magnetization, ii) the gyromagnetic ratio  $(\gamma = 2.210 \cdot 10^5 \ T^{-1}s^{-1})$  and iii) the damping constant.

$$\frac{dM_x}{dt} = M_s \gamma (H_z M_y - H_y M_z)

- M_s \alpha \gamma (H_y M_x M_y - H_x M_y^2 - H_x M_z^2 + H_z M_z M_x)

\frac{dM_y}{dt} = M_s \gamma (H_x M_z - H_z M_x)

- M_s \alpha \gamma (H_z M_y M_z - H_y M_z^2 - H_y M_x^2 + H_x M_x M_y)

\frac{dM_z}{dt} = M_s \gamma (H_y M_x - H_x M_y)

- M_s \alpha \gamma (H_x M_z M_x - H_z M_x^2 - H_z M_y^2 + H_y M_y M_z)$$

(A.1)

In this formulation, the terms  $H_x$ ,  $H_y$  and  $H_z$ , i.e the three components of the effective field, can be obtained by the Eq. A.2.

$$H_{eff}^{(i)} = H_{ext}^{(i)} - N^{(i)}M^{(i)} + \sum_{j \in neighbours, j \neq i} C^{(ij)}M^{(i)}$$

(A.2)

From the total energy term  $H_{eff}$ , it is possible to notice that there are three main contributions: i) the external applied magnetic field  $H_{ext}$ , ii) the self demagnetization of the target magnet  $(N^{(i)}M^{(i)})$  and iii) the energy derived from the interaction with neighboring nanomagnets. The demagnetization tensor N is related to the shape of the sample. The coupling term  $C^{ij}$  depends on the shapes and the distances of the neighbors nanoparticles. All these terms combined together contribute to the final magnetization M of the target nanomagnet.

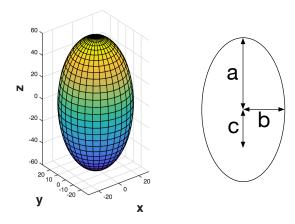

In this paper, according to [42] we approximate the nanomagnetic particle with a prolate rotational ellipsoid sufficiently small to exhibit a single domain behavior, with semi-major axis a and semi-minor axis b, see Fig. A.11.

The demagnetization tensor N associated to this geometry is reported in Eq. A.3

$$N = \begin{bmatrix} N_x & 0 & 0 \\ 0 & N_y & 0 \\ 0 & 0 & N_z \end{bmatrix} \tag{A.3}$$

$$N_z = \frac{\alpha^2}{\alpha^2 - 1} \left[ 1 - \frac{1}{\sqrt{\alpha^2 - 1}} \arcsin\left(\frac{\sqrt{\alpha^2 - 1}}{alpha}\right) \right]$$

$$N_x = N_z = \frac{1}{2} (1 - N_z)$$

$$\alpha = \frac{c}{a}$$

(A.4)

Figure A.11: Considered nanomagnet geometry with its corresponding axes

Here,  $N_x$ ,  $N_y$ ,  $N_z$  are called demagnetizing factors, they are positive and their sum must be equal to 1. The demagnetization tensor is always assumed diagonal in order to keep simpler the formulation, as reported in [42]. For this particular structure, the interactions between nanomagnet (i) and nanomagnet (j) is described by the coupling matrix  $C^{ij}$ defined in Eq. A.5.

$$C^{ij} = \frac{V^j}{4\pi r_{ij}^3} \begin{bmatrix} 3\hat{r}_x^2 - 1 \ 3\hat{r}_x\hat{r}_y & 3\hat{r}_x\hat{r}_z \\ 3\hat{r}_y\hat{r}_x \ 3\hat{r}_y^2 - 1 \ 3\hat{r}_y\hat{r}_z \\ 3\hat{r}_z\hat{r}_x & 3\hat{r}_z\hat{r}_y \ 3\hat{r}_z^2 - 1 \end{bmatrix}$$

(A.5)

where  $r_i$  represents the distance between the two nanoparticles and  $\hat{r}$  is the unit vector from nanomagnet (i) and (j). For a detailed explanation see [42].

We enriched our tool ToPolinano with the Macro-Spin LLG engine, introducing the single domain approximation model for calculation of the magnetization of the sample nanomagnets. We used the modern *odeint* C++ library [48] for numerically solving ordinary differential equation.

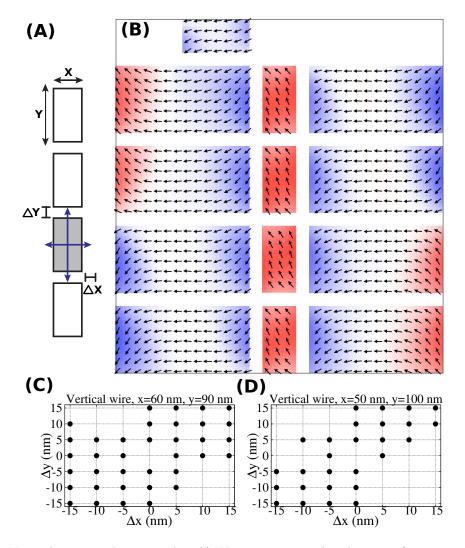

## Appendix B. Case studies

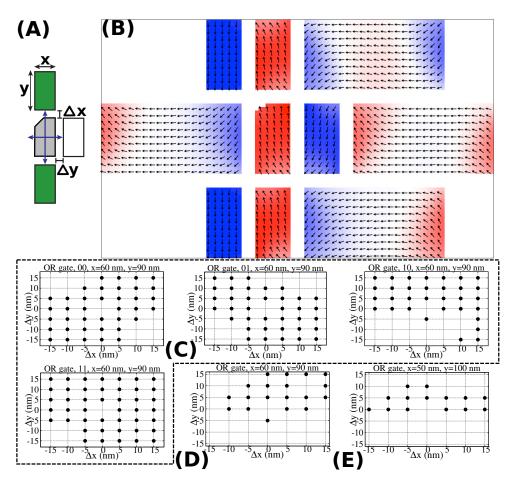

Fig. B.12 depicts the characterization results of a **vertical wire**. Fig. B.12.A depicts the basic wire structure, while Fig. B.12.B presents the final OOMMF simulation step in ideal conditions. While a vertical wire is conceptually similar to an horizontal wire, the magnetic interaction is different and the alignment is ferromagnetic. As a consequence a vertical wire necessarily requires helper blocks [44] at both magnets sides to assure a correct signal propagation. The helper blocks can be observed from the OOMMF simulation (Fig. B.12.B). The working area map considering magnets of  $60 \times 90 \times 20 \text{nm}^3$  is depicted in Fig. B.12.C, while the map for the  $50 \times 100 \times 20 \text{nm}^3$  case is instead presented in Figure B.12.D. Comparing the results to the horizontal wire ones, it can be clearly observed that the working area is smaller. The vertical wire is a less robust structure than the

Figure B.12: Vertical wire simulation results. A) Wire structure with indication of magnets sizes and displacements. B) Final OOMMF simulation step. C) Map with vertical wire working area, with  $60 \times 90 \times 20 \text{nm}^3$  magnets. D) Working area with  $50 \times 100 \times 20 \text{nm}^3$  magnets.

horizontal wire. This is mainly due to the different magnetic interaction among neighbor magnets. Moreover in this case different magnet sizes lead to different operating areas, particularly the  $60 \times 90 \times 20 \text{nm}^3$  is more robust than the  $50 \times 100 \times 20 \text{nm}^3$  case. The last wire that we analyzed is the **L-shaped wire**, which is a combination of an horizontal and vertical wire. Fig. B.13.A highlights the wire structure, the most critical element in this case is the magnets on the corner. Figures B.13.B and B.13.C highlight the working area maps considering magnets of  $60 \times 90 \times 20 \text{nm}^3$  sizes and  $50 \times 100 \times 20 \text{nm}^3$  sizes, respectively. The working area is quite good, however also in this case the  $60 \times 90 \times 20 \text{nm}^3$  case is the more robust. The final state of OOMMF simulation is depicted in Fig. B.13.D.

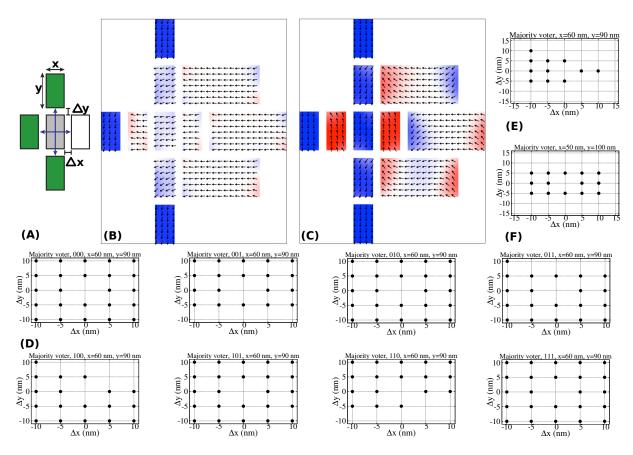

The basic **logic gate** in NML technolog is the **Majority Voter**, as a consequence it is the most critical block. In [41] we analyzed the Majority Voter changing distances among neighbor magnets. In this work we focus, as we have done with the other basic blocks, on

Figure B.13: Simulation results for an L-shaped wire. A) Wire structure. B) Working area map for the  $60x90x20nm^3$  case. C) Working area map for the  $50x100x20nm^3$  case.

magnets misplacement. Fig. B.14.A shows the basic Majority Voter structure, where three input magnets are used to influence the value of the central element. The output value is therefore equivalent to the value of the majority of the inputs. We changed the position of the central magnet, considering all possible shifting in vertical and horizontal positions in the range 5nm-10nm. Figures B.14.B and B.14.C depicts the initial and final state of the OOMMF simulations in ideal conditions, respectively. In these simulations we use three additional magnets as inputs. Helper blocks are still required to obtain a working circuit. The maps, showing the operating area for each one of the eight possible input combinations, are depicted in Fig. B.14.D. Magnets are 60x90x20nm<sup>3</sup>. Considering every single input configuration alone, the working area is pretty good. However, intersecting all the maps and obtaining therefore the working area for the entire gate, results are much worse (Fig. B.14.E). It is a situation that can be easily explained. The central magnet is influenced equally by the three magnets around it. Shifting the position of the central element enhances the contribution of some magnets with respect to the others, leading to wrong results with certain input configurations. Distances among magnets are 20nm, so even a small variation like 5nm leads to the wrong behavior in many cases. Our simulations show that, increasing distances among magnets, the gate behavior become more robust and bigger variations can be tolerated. Similarly to the previous cases, the 50x100x20nm<sup>3</sup> case has worse performance.

The last basic block that we have characterized is the OR GATE. The basic structure is depicted in Fig. B.15.A. An OR gate can be obtained simply with three vertically aligned

Figure B.14: Majority voter characterization. A) Circuit structure. B) OOMMF simulation, initial state. C) OOMMF simulation, final state. D) Majority voter working area maps with magnets of  $60 \times 90 \times 20 \text{nm}^3$  for each of all eight possible input configurations. E) Majority voter operating area considering the intersection among the maps obtained for all input configurations. Magnets are  $60 \times 90 \times 20 \text{nm}^3$ . F) Majority voter operating area with magnet of  $50 \times 100 \times 20 \text{nm}^3$ .

magnets, cutting on one corner the central element [49]. The cut gives to the magnet a preferential state, so globally the structure acts as an OR gate. If the cut is on the lower corner instead of the top corner, the resulting behavior is equal to an AND gate. We include in this work only the characterization of the OR gate, because the behavior of the AND gate is the same but mirrored. The final state of the OOMMF simulation can be observed in Fig. B.15.B. For the  $60 \times 90 \times 20 \text{nm}^3$  case the working area for each of the four input combinations is instead depicted in Fig. B.15.C, while Fig. B.15.D highlights the total operating area. The most critical input combination is 10, and it clearly constraints the gate working area. Overall the gate shows a good robustness. Fig. B.15.E depicts the working area for the  $50 \times 100 \times 20 \text{nm}^3$  case, that, similarly to the previous cases, is smaller.

Figure B.15: NML OR gate. A) Circuit structure. The OR gate can be obtained cutting one magnet, giving to it a preferential state. B) Final state of the OOMMF simulation. C) Working area for each of the four input configurations with magnets of  $60 \times 90 \times 20 \text{nm}^3$ . D) OR gate working area with magnets of  $60 \times 90 \times 20 \text{nm}^3$ . E) OR gate working area with magnets of  $50 \times 100 \times 20 \text{nm}^3$ .

### References

- [1] International Technology Roadmap of Semiconductors, http://public.itrs.net (2012).

- [2] A. Beg, Automating the sizing of transistors in cmos gates for low-power and highnoise margin operation, International Journal of Circuit Theory and Applications 43 (11) (2014) 16371654. doi:10.1002/cta.2031.

- [3] Z. Abbas, M. Oliveir, Optimal transistor sizing for maximum yield in variation-aware standard cell design, International Journal of Circuit Theory and Applications online. doi:10.1002/cta.2167.

- [4] C. Lent, P. Tougaw, W. Porod, G. Bernstein, Quantum cellular automata, Nanotechnology 4 (1993) 49–57.

- [5] M. Tahoori, M. Momenzadeh, J. Huang, F. Lombardi, Defects and faults in quantum

- cellular automata at nano scale, in: VLSI Test Symposium, 2004. Proceedings. 22nd IEEE, 2004, pp. 291–296.

- [6] S. Bhanja, S. Sarkar, Switching error modes of qca circuits, in: Nanotechnology, 2006. IEEE-NANO 2006. Sixth IEEE Conference on, Vol. 1, 2006, pp. 383–386.

- [7] M. Momenzadeh, M. Tahoori, J. Huang, F. Lombardi, Quantum cellular automata: new defects and faults for new devices, in: Parallel and Distributed Processing Symposium, 2004. Proceedings. 18th International, 2004, pp. 207–.

- [8] M. Momenzadeh, J. Huang, M. Tahoori, F. Lombardi, On the evaluation of scaling of qca devices in the presence of defects at manufacturing, Nanotechnology, IEEE Transactions on 4 (6) (2005) 740–743.

- [9] M. Tahoori, J. Huang, M. Momenzadeh, F. Lombardi, Testing of quantum cellular automata, Nanotechnology, IEEE Transactions on 3 (4) (2004) 432–442.

- [10] P. Gupta, N. Jha, L. Lingappan, Test generation for combinational quantum cellular automata (qca) circuits, in: Design, Automation and Test in Europe, 2006. DATE '06. Proceedings, Vol. 1, 2006, pp. 1–6. doi:10.1109/DATE.2006.244175.

- [11] P. Gupta, N. Jha, L. Lingappan, A test generation framework for quantum cellular automata circuits, Very Large Scale Integration (VLSI) Systems, IEEE Transactions on 15 (1) (2007) 24–36.

- [12] T. Wei, K. Wu, R. Karri, A. Orailoglu, Fault tolerant quantum cellular array (qca) design using triple modular redundancy with shifted operands, in: Design Automation Conference, 2005. Proceedings of the ASP-DAC 2005. Asia and South Pacific, Vol. 2, 2005, pp. 1192–1195 Vol. 2.

- [13] B. Sen, B. Sikdar, A study on defect tolerance of tiles implementing universal gate functions, in: Design Technology of Integrated Systems in Nanoscale Era, 2007. DTIS. International Conference on, 2007, pp. 13–18.

- [14] I. Palit, X. S. Hu, J. Nahas, M. Niemier, Systematic design of nanomagnet logic circuits, in: Proceedings of the Conference on Design, Automation and Test in Europe, DATE '13, EDA Consortium, San Jose, CA, USA, 2013, pp. 1795–1800. URL http://dl.acm.org/citation.cfm?id=2485288.2485712

- [15] M. Niemier, A. Dingler, X. Hu, Design tradeoffs for improved performance in mqca-based systems, in: Design and Test of Nano Devices, Circuits and Systems, 2008 IEEE International Workshop on, 2008, pp. 35–38.

- [16] M. Vacca, D. Vighetti, M. Mascarino, L. Amaru, M. Graziano, M. Zamboni, Magnetic QCA Majority Voter Feasibility Analysis, 2011 7th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME) (2011) 229–232doi:10.1109/PRIME.2011.5966275.

- [17] G. Turvani, F. Riente, M. Graziano, M. Zamboni, A quantitative approach to testing in quantum dot cellular automata: Nanomagnet logic case, 2014 10th Conference on Ph.D. Research in Microelectronics and Electronics.

- [18] A. Kumari, J. Pulecio, S. Bhanja, Defect characterization in magnetic field coupled arrays, in: Quality of Electronic Design, 2009. ISQED 2009. Quality Electronic Design, 2009, pp. 436–441. doi:10.1109/ISQED.2009.4810334.

- [19] M. Niemier, M. Crocker, X. Hu, Fabrication variations and defect tolerance for nanomagnet-based qca, in: Defect and Fault Tolerance of VLSI Systems, 2008. DFTVS '08. IEEE International Symposium on, 2008, pp. 534–542. doi:10.1109/DFT.2008.54.

- [20] D. Carlton, B. Lambson, A. Scholl, A. Young, P. Ashby, S. Dhuey, J. Bokor, Investigation of defects and errors in nanomagnetic logic circuits, Nanotechnology, IEEE Transactions on 11 (4) (2012) 760–762. doi:10.1109/TNANO.2012.2196445.

- [21] J. Pulecio, P. Pendru, A. Kumari, S. Bhanja, Magnetic cellular automata wire architectures, Nanotechnology, IEEE Transactions on 10 (6) (2011) 1243–1248. doi:10.1109/TNANO.2011.2109393.

- [22] J. Pulecio, S. Bhanja, Reliability of bi-stable single domain nano magnets for cellular automata, in: Nanotechnology, 2007. IEEE-NANO 2007. 7th IEEE Conference on, 2007, pp. 782–786.

- [23] M. Donahue, D. Porter, OOMMF User's Guide, Version 1.0, Tech. Rep. Interagency Report NISTIR 6376, National Institute of Standards and Technology, Gaithersburg (September 1999).

- [24] S. Frache, D. Chiabrando, M. Graziano, M. Graziano, L. Boarino, M. Zamboni, Enabling Design and Simulation of Massive Parallel Nanoarchitectures, Journal of Parallel and Distributed Computing In Press. doi:10.1016/j.jpdc.2013.07.010.

- [25] G. Turvani, A. Tohti, M. Bollo, F. Riente, M. Vacca, M. Graziano, M. Zamboni, Physical design and testing of nano magnetic architectures, in: Design Technology of Integrated Systems In Nanoscale Era (DTIS), 2014 9th IEEE International Conference On, 2014, pp. 1–6. doi:10.1109/DTIS.2014.6850676.

- [26] P. Tougaw, C. Lent, W. Porod, Bistable Saturation In Coupled Quantum-Dot Cells, Journal Of Applied Physics 74 (1993) 3558–3566.

- [27] A. Csurgay, W. Porod, C. Lent, Signal processing with near-neighborcoupled time-varying quantum-dot arrays, IEEE Transaction On Circuits and Systems 47 (8) (2000) 1212–1223.

- [28] A. Imre, L. Ji, G. Csaba, A.O. Orlov, G. Bernstein, W. Porod, Magnetic Logic Devices Based on Field-Coupled Nanomagnets, 2005 International Semiconductor Device Research Symposium (2005) 25.

- [29] G. Csaba, W. Porod, P. Lugli, A. Csurgai, Activity in field-coupled nanomagnet arrays, International Journal of Circuit Theory and Applications 35 (3) (2007) 281293,. doi:10.1002/cta.411.

- [30] M. Graziano, M. Vacca, A. Chiolerio, M. Zamboni, A NCL-HDL Snake-Clock Based Magnetic QCA Architecture, IEEE Transaction on Nanotechnology 10 (5) (2011) 1141–1149.

- [31] M. Niemier, al., Nanomagnet logic: progress toward system-level integration, J. Phys.: Condens. Matter 23 (2011) 34. doi:10.1088/0953-8984.

- [32] J. Das, S. Alam, S. Bhanja, Low Power Magnetic Quantum Cellular Automata Realization Using Magnetic Multi-Layer Structures, J. on Emerging and Selected Topics in Circuits and Systems 1 (3) (2011) 267–276.

- [33] J. Das, S. Alam, S. Bhanja, Ultra-low power hybrid cmos-magnetic logic architecture, Circuits and Systems I: Regular Papers, IEEE Transactions on 59 (9) (2012) 2008–2016.

- [34] M. Vacca, M. Graziano, A. Chiolerio, A. Lamberti, M. Laurenti, D. Balma, E. Enrico, F. Celegato, P. Tiberto, M. Zamboni, Electric clock for NanoMagnet Logic Circuits , In: Anderson, N.G., Bhanja, S. (eds.), Field-Coupled Nanocomputing: Paradigms, Progress, and Perspectives. LNCS, Springer, Heidelberg. vol. 8280.

- [35] M. Vacca, M. Graziano, L. Di Crescenzo, A. Chiolerio, A. Lamberti, D. Balma, G. Canavese, F. Celegato, E. Enrico, P. Tiberto, L. Boarino, M. Zamboni, Magnetoelastic clock system for nanomagnet logic, Nanotechnology, IEEE Transactions on 13 (5) (2014) 963–973. doi:10.1109/TNANO.2014.2333657.

- [36] G. Csaba, W. Porod, Behavior of Nanomagnet Logic in the Presence of Thermal Noise, in: International Workshop on Computational Electronics, IEEE, Pisa, Italy, 2010, pp. 1–4.

- [37] M. Becherer, J. Kiermaier, G. Csaba, J. Rezgani, C. Yilmaz, P. Osswald, P. Lugli, D. Schmitt-Landsiedel, Characterizing magnetic field-coupled computing devices by the Extraordinary Hall-effect, in: Proceedings European Solid State Device Research Conference, IEEE, Athens, Greece, 2009, pp. 105–108.

- [38] D. Karunaratne, S. Bhanja, Study of single layer and multilayer nano-magnetic logic architectures, Journal Of Applied Physics 111.

- [39] E. Varga, G. Csaba, G. Bernstein, W. Porod, Implementation of a Nanomagnetic Full Adder Circuit, 2011 11th IEEE International Conference on Nanotechnology.

- [40] M. Alam, M. Siddiq, G. Bernstein, M. Niemier, W. Porod, X. Hu, On-chip clocking for nanomagnet logic devices, Nanotechnology, IEEE Transactions on 9 (3) (2010) 348–351. doi:10.1109/TNANO.2010.2041248.

- [41] M. Vacca, M. Graziano, M. Zamboni, Majority Voter Full Characterization for Nanomagnet Logic Circuits, IEEE T. on Nanotechnology 11 (5) (2012) 940–947. doi:10.1109/TNANO.2012.2207965.

- [42] G. Csaba, W. Porod, A. Csurgay, A computing architecture composed of field-coupled single domain nanomagnets clocked by magnetic field, international Journal Of Circuits Theory And Applications 31 (2003) 67–82.

- [43] G. Csaba, M. Becherer, W. Porod, Development of cad tools for nanomagnetic logic devices, International Journal of Circuit Theory and Applications 41 (6) (2013) 634– 645. doi:10.1002/cta.1811. URL http://dx.doi.org/10.1002/cta.1811

- [44] D. Carlton, N. Emley, E. Tuchfeld, J. Bokor, Simulation Studies of Nanomagnet-Based Logic Architecture, Nanoletters 8 (12) (2008) 4173–4178. doi:10.1021/nl801607p.

- [45] M. Vacca, S. Frache, M. Graziano, F. Riente, G. Turvani, M. R. Roch, M. Zamboni, ToPoliNano: NanoMagnet Logic Circuits Design and Simulation, In: Anderson, N.G., Bhanja, S. (eds.), Field-Coupled Nanocomputing: Paradigms, Progress, and Perspectives. LNCS, Springer, Heidelberg. vol. 8280.

- [46] P. Ranone, G. Turvani, F. Riente, M. Graziano, M. Roch, M. Zamboni, Fault tolerant nanoarray circuits: Automatic design and verification, in: VLSI Test Symposium (VTS), 2014 IEEE 32nd, 2014, pp. 1–6. doi:10.1109/VTS.2014.6818761.

- [47] S. Frache, M. Graziano, M. Zamboni, A flexible simulation methodology and tool for nanoarray-based architectures, in: IEEE International Conference on Computer Design, IEEE, 2010, pp. 60–67. doi:10.1109/ICCD.2010.5647586.

- [48] K. Ahnert, M. Mulansky, Odeint Solving ordinary differential equations in C++, CoRR abs/1110.3397.

- [49] M. Niemier, E. Varga, G. Bernstein, W. Porod, M. Alam, A. Dingler, A. Orlov, X. Hu, Shape Engineering for Controlled Switching With Nanomagnet Logic, IEEE Transactions on Nanotechnology 11 (2) (2012) 220–230. doi:10.1109/TNANO.2010.2056697.