Zhang, Yun and Shi, Jilong and Zhou, Lei and Li, Jing and Sumner, Mark and Wang, Ping and Xia, Changliang (2017) Wide input-voltage range boost three-level DC-DC converter with quasi-Z source for fuel cell vehicles. IEEE Transactions on Power Electronics, 32 (9). pp. 6728-6738. ISSN 0885-8993

# Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/44028/1/Wide%20Input-Voltage%20Range%20Boost %20Three-Level%20DC-DC%20Converter%20with%20Quasi-Z%20Source%20for%20Fuel %20Cell%20Vehicles.pdf

# Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end user agreement.pdf

# A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

# Wide Input-Voltage Range Boost Three-Level DC-DC Converter with Quasi-Z Source for Fuel Cell Vehicles

Yun Zhang, Member, IEEE, Jilong Shi, Lei Zhou, Jing Li, Member, IEEE, Mark Sumner, Senior Member, IEEE, Ping Wang, and Changliang Xia, Senior Member, IEEE

Abstract: To solve the problem of the mismatched voltage levels between the dynamic lower voltage of the fuel cell stack and the required constant higher voltage (400V) of the DC link bus of the inverter for fuel cell vehicles, a Boost three-level DC-DC converter with a diode rectification quasi-Z source (BTL-DRqZ) is presented in this paper, based on the conventional flying-capacitor Boost three-level DC-DC converter. The operating principle of a wide range voltage-gain for this topology is discussed according to the effective switching states of the converter and the multi-loop energy communication characteristic of the DRqZ source. The relationship between the quasi-Z source net capacitor voltages, the modulation index and the output voltage, is deduced and then the static and dynamic self-balance principle of the flying-capacitor voltage is presented. Furthermore, a Boost three-level DC-DC converter with a synchronous rectification quasi-Z source (BTL-SRqZ) is additionally proposed to improve the conversion efficiency. Finally, a scale-down 1.2 kW BTL-SRqZ prototype has been created, and the maximum efficiency is improved up to 95.66% by using synchronous rectification. The experimental results validate the feasibility of the proposed topology and the correctness of its operating principles. It is suitable for the fuel cell vehicles.

**Keywords:** Boost three-level DC-DC converter, fuel cell vehicles, Quasi-Z source, synchronous rectification, wide range of voltage-gain.

### I. INTRODUCTION

Non-renewable energy sources continue to be consumed and fossil fuel related emissions continue to increase pollution [1~3].

Manuscript received June 28, 2016. Accepted for publication November 1, 2016. This work was supported in part by the National Natural Science Foundation of China under Grants 51577130, and 51207104, and in part by the Research Program of Application Foundation and Advanced Technology of Tianjin China under Grant 15JCQNJC03900.

Yun Zhang, Jilong Shi, Lei Zhou, and Ping Wang are with the School of Electrical Engineering and Automation, Tianjin University, Tianjin 300072, China (fax: +86-022-27402325; e-mail: zhangy@tju.edu.cn, jilong\_shi@163.com, Luxuszl@163.com, and pingw@tju.edu.cn).

Jing Li is with the Department of Electrical and Electronic Engineering, University of Nottingham, Ningbo, China (email: jing.li@nottingham.edu.cn).

Mark Sumner is with the Department of Electrical and Electronic Engineering, University of Nottingham, UK (email: mark.sumner@nottingham.ac.uk).

Changliang Xia is with the School of Electrical Engineering and Automation, Tianjin University, and also with the Tianjin Key Laboratory of Advanced Technology of Electrical Engineering and Energy, Tianjin Polytechnic University, China (e-mail: motor@tju.edu.cn).

With regard to transport, the development of clean-energy vehicles can have a major impact on improving air quality (especially in cities) as well as reducing other fossil fuel related problems [4~6]. The fuel cell vehicle is an important type of the clean-energy vehicle and its obvious advantage is that it provides clean propulsion power with zero emission, as well as higher energy utilization [7~9]. However, the fuel cell usually has a current source characteristic with low output voltage and high output current. In addition, it is difficult to use it to supply an inverter to drive a vehicle, due to its soft output characteristic [10~12]. Therefore, it must be interfaced to the DC link bus of the inverter through a step-up DC-DC converter with a wide range of voltage-gain. The wide gap in voltage levels between the fuel cell stack and the DC link bus can be matched, and stable DC link bus voltage can also be obtained.

Usually the conventional Boost two-level DC-DC converter is employed due to its simple structure [13, 14], but, it suffers from disadvantages including limited voltage-gain, and high voltage stress for its power semiconductors. To alleviate the problem of mismatched voltage levels, the rated voltage of the fuel cell stack has to be increased (increasing the difficulty of assembling the fuel cell stack). At the same time, power semiconductors with higher rated blocking voltage need to be employed and consequently the conduction losses can be improved. In order to reduce the high voltage stress of power semiconductors, Boost three-level DC-DC converters have been proposed, and then the voltage stress can be reduced by half [15~17]. However, there remain two essential problems concerning the interface between the fuel cell stack and the DC-link bus, namely the same limited voltage-gain with that of the Boost two-level converter, and the complicate control required for the flying-capacitor voltage balance of the Boost three-level converter, especially the voltage imbalance of the flying-capacitor in the transient state [18] - this latter may cause power semiconductor failure. It is therefore necessary to solve these problems for fuel cell vehicles, which use the Boost three-level DC-DC converter with a flying capacitor.

As to the non-isolated step-up DC-DC converters with high voltage-gain, the voltage multiplier circuits are adopted to extend the voltage-gain [19]. The switched-inductor structures for step-up DC-DC converters can also obtain high voltage-gain, as well as the switched-capacitor DC-DC converters [20, 21]. However, these step-up DC-DC converters with high voltage-gain are too complex to reduce their cost and size. The quadratic Boost DC-DC converter can also achieve a high

voltage-gain [22]. However, the power semiconductors of the output side (the high voltage side) suffer from high voltage stresses (due to the high output voltage), and create a high dv/dtduring switching. Although a large conversion ratio interleaved Boost DC-DC converter using two stages in parallel and one series multiplier stage can convert 24V to 200V [23], there still two diodes in the multiplier stage which suffer from the full output voltage stress. A family of diode-coupled-winding Boost DC-DC converters with a high voltage-gain can perform better than their active-clamp counterparts due to recycled leakage energy [24], achieving a maximum efficiency about 91.7%. Based on [23] and [24], a high voltage-gain interleaved Boost DC-DC converter magnetically coupled to a voltage-double circuit was proposed in [25]. In addition, another high voltage-gain Boost DC-DC converter can obtain higher efficiency, which is based on the three-state commutation cell with additional two transformers (six windings) [26].

Z source net has been applied in the traditional step-up DC-DC converters to achieve the higher voltage-gain [27], but their input and output sides don't share the common ground, which may result in maintenance safety and EMI problems. In addition, the output diode can be replaced by an inductor in the Z source DC-DC converters [28], but the voltage-gain is reduced unexpectedly. The diode rectification quasi-Z (DRqZ) source circuit is another modified energy storage circuit structure which has been proposed for the combination of a low voltage DC source and an inverter [29, 30]. It can also be used in the step-up DC-DC converters with the features of lower capacitor voltages and the common ground [31], but its voltage-gain is the same as the conventional Z source DC-DC converters, and the voltage stress of the power switch is still as high as the output voltage. The coupled inductor based Z source DC-DC converters can achieve high voltage-gain by setting the turn ratio of the coupled inductor [32]. However, the spike voltage of the power switches may be very large due to the leakage inductor of the coupled inductor. In [33], a common grounded Z source DC-DC converter with high voltage-gain is presented by changing the connection way of the grounding, the input source and the load are located on the same side of the Z source, instead of being located on both sides of the Z source. It is analyzed in [33] that the voltage stress of the power semiconductors is reduced in the range of half of the output voltage to nearly the output voltage, when increasing the duty cycle (voltage-gain). In addition, the current stress of the power switch is several times as high as the output current while increasing the duty cycle (voltage-gain).

In this paper, a wide input-voltage range Boost three-level DC-DC converter with a diode rectification quasi-Z source (BTL-DRqZ) is proposed as a solution which can reduce the voltage stress of all semiconductors to half of the output voltage; it also has a common ground for the input and output by using the flying-capacitor three-level structure, and operates well with a high voltage-gain, proper duty cycles (0.5<=d<0.75), and balancing of the voltage of the flying capacitor without additional hardware. Although one more power switch and diode are employed compared to the conventional quasi-Z source Boost DC-DC converter, the lower rated voltage semiconductors with lower on-resistance can replace the higher

rated voltage devices. In addition, the equivalent frequency of the inductor current and the capacitor voltage ripple in the proposed topology is double the switching frequency due to using one additional power switch, diode and flying capacitor, achieved by using the flying-capacitor three-level structure with two phase-shifted 180 degree gate driving signals. These features are beneficial to improve efficiency. In order to improve the efficiency of the proposed converter further, the Boost three-level DC-DC converter with a synchronous rectification quasi-Z source (BTL-SRqZ) is additionally proposed, based on the BTL-DRqZ. This paper is organized as follows: in Section II, the topology of the BTL-DRqZ for fuel cell vehicles is presented. The operation principles of the converter topology with a synchronous rectification quasi-Z source are discussed in Section III. In Section IV, the parameters of all components are designed, and the losses of the proposed topology are analyzed. Then, the experimental results measured from the prototype are analyzed in Section V. Finally, the conclusion is delivered in Section VI.

### II. TOPOLOGY OF DROZ SOURCE CONVERTER

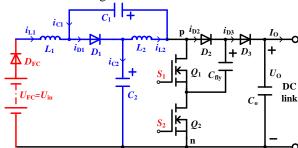

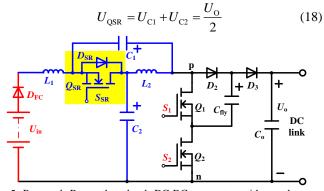

In order to widen the step-up voltage gain of the Boost DC-DC converter, the DRqZ source net " $L_1$ - $L_2$ - $D_1$ - $C_1$ - $C_2$ " has been investigated. The input of the converter is comprised of the voltage source of the fuel cell  $U_{\rm FC}$ = $U_{\rm in}$  and its associated reverse blocking diode  $D_{\rm FC}$ . A three-level DC-DC converter with flying-capacitor is adopted, to halve the voltage stress on the power devices and also allow  $U_{\rm in}$  and the DC link bus to have a common ground. The resulting BTL-DRqZ for a fuel cell vehicle is shown in Fig. 1.

Fig. 1 Proposed Boost three-level DC-DC converter with diode rectification quasi-Z source (BTL-DRqZ) for fuel cell vehicles.

### III. OPERATION PRINCIPLES

### A. Operation states

According to Fig. 1, there are four switching states " $S_1S_2$ " in a switching period, i.e.  $S_1S_2$ ={11, 10, 01, 00}, where "1" represents the power switches  $Q_1$ ,  $Q_2$  "ON", and "0" represents  $Q_1$ ,  $Q_2$  "OFF".  $L_1$  and  $L_2$  are storing energy, while  $C_1$  and  $C_2$  are discharging energy when  $S_1S_2$ =11. In the other switching states,  $L_1$  and  $L_2$  discharging energy, whereas  $C_1$  and  $C_2$  are charging. In addition, the sequence of the switching states in a switching period is related to the duty cycle ranges of the power switches  $Q_1$ ,  $Q_2$ . For example, Sequence I "01-00-10-00-01" appears within the range of  $0 < d_1 = d_2 < 0.5$ , while Sequence II "01-11-10-11-01" can be obtained by the range of  $0.5 < d_1 = d_2 < 1$ , where  $d_1$  and  $d_2$  ( $d_1 = d_2$ ) are the corresponding duty cycles for  $Q_1$  and  $Q_2$  in a Boost three-level DC-DC converter. However, the inductors  $L_1$  and  $L_2$  only discharge in Sequence I, due to the absence of switching state  $S_1S_2$ =11. Therefore, it is likely that

the proposed converter operates within the range of  $0.5 < d_1 = d_2 < 1$ .

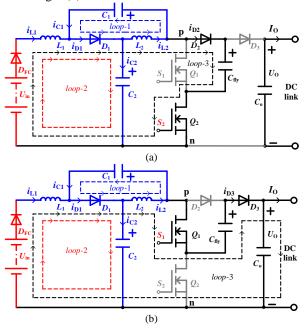

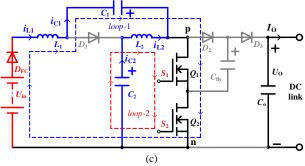

In the active switching states, the energy flow paths between the fuel cell stack source, inductors and capacitors are shown in Fig. 2, and the PWM modulation strategy and important waveforms are illustrated in Fig. 3. In Fig. 2(a), there are three energy flow loops when  $S_1S_2=01$ : in loop-1,  $L_2$  is discharging, at the same time  $C_1$  is charging through  $D_1$ . The inductor current  $i_{L2}$  and the capacitor voltage  $U_{C1}$  are shown in Fig. 3(e, f); in loop-2,  $L_1$  and  $U_{\rm in}$  in series are discharging, while  $C_2$  is charging through  $D_{\rm FC}$ and  $D_1$ . Thus the inductor current  $i_{L1}$  and the capacitor voltage  $U_{\rm C2}$  can be illustrated in Fig. 3(d, g); in loop-3,  $L_1$ ,  $L_2$  and  $U_{\rm in}$  in series are discharging, while the flying-capacitor  $C_{\rm fly}$  is charging through  $D_{FC}$ ,  $D_1$ ,  $D_2$ , and  $Q_2$ . Hence the corresponding voltage and current waves are shown in Fig. 3(d, e, h, j, k, m). In addition, the instantaneous PWM voltage of the converter  $U_{pn}$  $(S_1S_2=01)$  is simply the voltage across  $C_{fly}$ , namely  $U_{pn}=U_{Cfly}$ , as shown in Fig. 3(n).

When  $S_1S_2$ =10, there are also three energy flow paths as shown in Fig. 2(b). It can be seen that the difference between  $S_1S_2$ =10 and  $S_1S_2$ =01 is the discharging/charging state of the flying-capacitor  $C_{\rm fly}$ , e.g.  $C_{\rm fly}$ ,  $U_{\rm in}$ ,  $L_1$ , and  $L_2$ , are in a series connection and discharge to supply the DC link side through  $D_{\rm FC}$ ,  $D_1$ ,  $Q_1$  and  $D_3$ . The corresponding voltage and current waveforms are shown in Fig. 3(d, e, h, i, l, m). At the same time, the instantaneous PWM voltage of the converter  $U_{\rm pn}(S_1S_2$ =10) is described as  $U_{\rm pn}$ = $U_{\rm O}$ - $U_{\rm Cfly}$ , rather than the voltage across  $C_{\rm fly}$ , as shown in Fig. 3(n).

In another active switching state  $S_1S_2=11$ ,  $D_1$  is OFF due to the reverse voltage of  $L_1$ . As a result, two energy flow paths are left, as shown in Fig. 2(c). In loop-1,  $C_1$  (which stays in a series connection with  $U_{in}$ ) is discharging, while  $L_1$  is charging through  $D_{FC}$ ,  $Q_1$  and  $Q_2$ ; similarly,  $C_2$  is transferring energy to  $L_2$  through  $Q_1$  and  $Q_2$  in loop-2. Consequently, the instantaneous PWM voltage of the converter  $U_{pn}$ =0 ( $S_1S_2$ =11) can be obtained as shown in Fig. 3(n).

Fig. 2 Energy flow paths among the voltage source, inductors and capacitors in effective switching states. (a)  $S_1S_2$ =01 ( $D_1$  is ON). (b)  $S_1S_2$ =10 ( $D_1$  is ON). (c)  $S_1S_2$ =11 ( $D_1$  is OFF).

### B. Operation with wide range of voltage-gain

In order to simplify the explanation, it is assumed the capacitance of the capacitors in Fig. 1 is infinite, as well as the inductance of the inductors. Therefore, capacitors  $C_1$ ,  $C_2$  are seemed to be constant voltage sources, and  $L_1$ ,  $L_2$  can be considered as constant current sources. In addition, the flying-capacitor voltage is half of the output voltage  $U_0$ , e.g.  $U_{\rm Cfly} = U_0/2$ . When  $S_1S_2 = 01$  or  $S_1S_2 = 10$ ,  $L_1$  and  $L_2$  are discharging. Thus  $i_{\rm L1}$  and  $i_{\rm L2}$  are identical in Fig. 2(a, b), and the voltages across  $L_1$  and  $L_2$  are also equal (1):

$$u_{\text{L1\_dis}} = u_{\text{L2\_dis}} \tag{1}$$

By means of Fig. 2(a, b) and KVL (Kirchhoff's Voltage Laws), the voltage balance equations can be obtained as follows

$$\begin{cases} U_{\text{in}} + u_{\text{L1\_dis}} + u_{\text{L2\_dis}} = \frac{U_{\text{O}}}{2} \\ u_{\text{L2\_dis}} = U_{\text{C1}} \\ U_{\text{in}} + u_{\text{L1\_dis}} = U_{\text{C2}} \end{cases}$$

(2)

When  $S_1S_2=11$ ,  $L_1$  and  $L_2$  are charging, their voltages  $u_{\rm L1\_ch}$  and  $u_{\rm L2\_ch}$  can be described as follows from Fig. 2(c) and KVL

$$\begin{cases}

U_{\text{in}} + U_{\text{Cl}} = u_{\text{L1\_ch}} \\

U_{\text{C2}} = u_{\text{L2 ch}}

\end{cases}$$

(3)

According to (1) and (2), the discharging voltage across  $L_1$  can be written as (4),

$$u_{\rm L1\_dis} = \frac{U_{\rm O}}{2} - U_{\rm in}$$

(4)

while the charging voltage of  $L_1$  is obtained by virtue of (2)~(4)

$$u_{\rm L1\_ch} = \frac{\frac{U_{\rm O}}{2} + U_{\rm in}}{2} \tag{5}$$

Regarding the charging/discharging time of  $L_1$ , when  $S_1S_2$ =01 and  $S_1S_2$ =10, the discharging time  $t_{\rm L1\_dis}$  of  $L_1$  is described as follows by means of the PWM modulation strategy shown in Fig. 3(a~c)

$$\begin{cases} t_{\text{L1_dis}} = [(1 - d_1) + (1 - d_2)] \times T \\ d_1 = d_2 = m = d \end{cases}$$

(6)

while the charging time  $t_{L1\_ch}$  of  $L_1$  is written

$$t_{\text{Ll\_ch}} = [d_2 - (1 - d_1)] \times T$$

(7)

where  $d_1=d_2=d$  are the duty cycles of  $Q_1$  and  $Q_2$  respectively, m is the modulation index, and T is the carrier period.

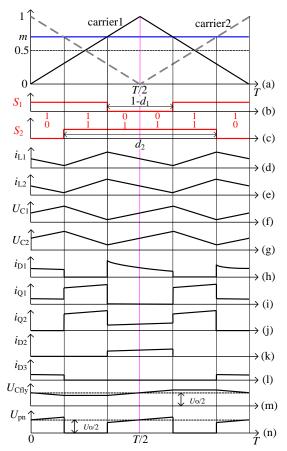

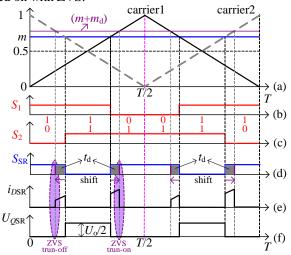

Fig. 3 PWM modulation strategy and important waveforms.

In current continuous mode, the voltage-second balance equation for  $L_1$  can be established as follows, by means of the equal charging and discharging energy in each carrier period

$$u_{\text{L1\_dis}} \times t_{\text{L1\_dis}} = u_{\text{L1\_ch}} \times t_{\text{L1\_ch}} \tag{8}$$

As a result, the step-up voltage-gain M of the BTL-qZ can be obtained by the combination of  $(4)\sim(8)$

$$M = \frac{U_{\rm o}}{U_{\rm in}} = \frac{2}{3 - 4d} \tag{9}$$

where  $0.5 \le d < 0.75$ . In addition, the capacitor voltages across  $C_1$  and  $C_2$  can also be gained by virtue of (2), (4) and (9)

$$\begin{cases} U_{\rm C1} = (d - 0.5) \times U_{\rm O} \\ U_{\rm C2} = (1 - d) \times U_{\rm O} \end{cases}$$

(10)

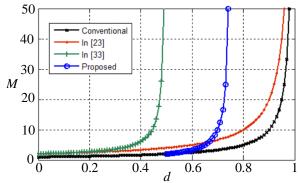

By means of (9), the proposed topology in Fig. 1 has a wider step-up voltage-gain range, especially the duty cycles of  $Q_1$  and  $Q_2$  are kept within the range of [0.5,0.75). Consequently, the conventional Boost three-level DC-DC converter's dilemma between the high voltage-gain and the non-extreme duty cycles can be solved by the proposed topology. In Fig. 4, it is shown the comparison of voltage-gain M via duty cycles d among the conventional Boost three-level converter, the interleaved converter in [23], the common ground converter in [33], and the proposed one. Therefore, the proposed converter in Fig. 1 has a wider range of voltage-gain than those previously presented. Even if it operates with lower voltage-gain (i.e. M=2), the more proper duty cycles [0.5,0.75) will appear, rather than the extreme low duty cycles in [23] and [33].

Fig. 4 Comparison of voltage-gain M via duty cycles d among conventional Boost three-level converter, interleaved converter in [23], common ground converter in [33], and proposed one.

### C. Self-balance of flying-capacitor voltage

According to Fig. 2(a, b),  $L_2$  is discharging, and its voltage  $u_{L2 \text{ dis}}$  is just the voltage across  $C_1$

$$u_{\text{L2\_dis}} \equiv U_{\text{C1}}, \quad (S_1 S_2 = 01, \quad 10)$$

(11)

When  $S_1S_2=01$ ,  $D_2$  and  $Q_2$  are ON as shown in Fig. 2(a), so the flying-capacitor voltage  $U_{\text{Cfly}\_01}$  across  $C_{\text{fly}}$  can be described as follows by (11)

$$U_{\text{Cfly}\_01} \equiv U_{\text{C2}} + U_{\text{C1}} \tag{12}$$

Similarly, when  $S_1S_2=10$ ,  $Q_1$  and  $D_3$  are ON as shown in Fig. 2(b), the flying-capacitor voltage  $U_{\text{Cfly}\_10}$  can also be obtained

$$U_{\text{Cfly}_{10}} \equiv U_{\text{O}} - (U_{\text{C2}} + U_{\text{C1}}) \tag{13}$$

While  $S_1S_2=11$ ,  $Q_1$  and  $Q_2$  are ON, but  $D_2$  and  $D_3$  are OFF as shown in Fig. 2(c). Consequently, the flying-capacitor voltage  $U_{\text{Cfly\_11}}$  is maintained. According to (12) and(13), it is concluded the flying-capacitor voltage  $U_{\text{Cfly}}$  directly depends on the sum of  $U_{\text{C1}}$  and  $U_{\text{C2}}$  from the DRqZ source net. Furthermore, the obvious relationship between  $U_{\text{Cfly}}$  and the output voltage  $U_{\text{O}}$  is deduced from (10)

$$U_{\rm Cfly} \equiv \frac{U_{\rm O}}{2} \tag{14}$$

From the analysis above, it can also be further concluded that the flying-capacitor voltage  $U_{\rm Cfly}$  is clamped by the sum of  $U_{\rm Cl}$  and  $U_{\rm C2}$  from the DRqZ source net, and  $U_{\rm Cfly}$  can follow half the output voltage  $U_{\rm O}$  by this self-balance characteristic, both in the converter's static and dynamic states. Therefore, extra balanced controls for the flying-capacitor voltage can be removed, and the voltage stress of all power semiconductors can still be constant at half the output voltage.

### D. Synchronous rectification operation for quasi-Z source

According to (14) and Fig. 2, the voltage stress of the power semiconductors  $Q_1$ ,  $Q_2$ ,  $D_2$  and  $D_3$  is half the output voltage. Regarding the voltage stress of  $D_1$  from the DRqZ source system, its blocking voltage is just the sum of  $U_{C1}$  and  $U_{C2}$  when  $S_1S_2=11$ , as shown in Fig. 2(c). Therefore, it is also half the output voltage (10). These advantages above are beneficial to reducing the conduction losses by using appropriate semiconductors, which are of lower on-resistance or lower voltage drop.

The other cause of the conduction losses is the current flowing through the diodes, i.e.  $D_1 \sim D_3$  shown in Fig. 1. The instantaneous currents  $i_{D1}$ ,  $i_{D2}$  through  $D_1$  and  $D_2$  can be described as follows when  $S_1S_2=01$ , by means of Fig. 2(a) and *KCL* (*Kirchhoff's Current Laws*).

$$\begin{cases}

i_{D1} = i_{L1} + i_{L2} - i_{D2} \\

i_{D2} = i_{L1} - i_{C2}

\end{cases}, (S_1 S_2 = 01)$$

(15)

where  $i_{C2}>0$  is the instantaneous current flowing through  $C_2$ ,  $i_{L1}$  and  $i_{L2}$  are the instantaneous currents of  $L_1$  and  $L_2$ , as shown in Fig. 2(a). Similarly, the instantaneous currents  $i_{D1}$  and  $i_{D3}$  through  $D_1$  and  $D_3$  can also be written as follows when  $S_1S_2=10$ ,

$$\begin{cases}

i_{D1} = i_{L1} + i_{L2} - i_{D3} \\

i_{D3} = i_{L1} - i_{C2}

\end{cases}, (S_1 S_2 = 10)$$

(16)

whilst  $D_1 \sim D_3$  are OFF when  $S_1S_2=11$ . Therefore, when  $S_1S_2=\{01, 10\}$ , the relationships of  $i_{D1}\sim i_{D3}$  to  $i_{L1}$  can be obtained as follows by means of (15) $\sim$ (16), the referred relations of  $i_{C2}>0$  and  $i_{L1}=i_{L2}$

$$\begin{cases} i_{D2} < i_{L1}, & (S_1 S_2 = 01) \\ i_{D3} < i_{L1}, & (S_1 S_2 = 10) \\ i_{D1} > i_{L1}, & (S_1 S_2 = 01, 10) \end{cases}$$

(17)

Consequently, it is concluded that the instantaneous currents flowing  $D_2$ ,  $D_3$  of the proposed converter are smaller than the corresponding input current of the voltage source. But, the instantaneous current flowing in  $D_1$  from the DRqZ source network is larger than the corresponding input current of the voltage source. As a result, the conduction loss of  $D_1$  must be the largest among  $D_1 \sim D_3$ . In addition,  $D_1$  can be replaced by the synchronous rectification MOSFET  $Q_{SR}$  ( $D_{SR}$  is its anti-parallel body diode), which is of lower on-resistance. This proposed BTL-SRqZ for the fuel cell vehicles is shown in Fig. 5. The voltage stress of  $Q_{SR}$  is also half the output voltage as follows when  $S_1S_2=11$

Fig. 5 Proposed Boost three-level DC-DC converter with synchronous rectification quasi-Z source (BTL-SRqZ) for fuel cell vehicles.

As to the gate driving signal  $S_{SR}$  for the synchronous rectification power switch  $Q_{SR}$ , it can be obtained from "Exclusive OR" logic combining  $S_1$  and  $S_2$  depicted in Fig.  $6(a\sim d)$ . In order to avoid conduction behavior of  $Q_{SR}$  during the state of  $S_1S_2=11$ , the dead time  $t_d$  must be added to the ideal gate driving signal of  $Q_{SR}$ , by the principle of "OFF in advance, and ON with delay" as shown in Fig.  $6(b\sim d)$ . For instance,  $Q_{SR}$  must be turned off ahead of time by  $t_d$  before the switching state changes to  $S_1S_2=11$ , and turned on with delayed time  $t_d$  after  $S_1S_2$  is changed to 01 or 10. In addition,  $t_d$  is determined by the dead time modulation index  $m_d$  and carrier period T easily as follows, shown in Fig. 6(a, d)

$$t_{\rm d} = m_{\rm d} \times \frac{T}{2} \tag{19}$$

The anti-parallel body diode  $D_{SR}$  conducts when  $Q_{SR}$  is turned off in advance, and the current flows through  $D_{SR}$  instead of  $Q_{SR}$ . As a result, the voltage stress of  $Q_{SR}$  is just the forward voltage drop of  $D_{SR}$ , i.e.  $Q_{SR}$  is turned off with near Zero-Voltage Switching (ZVS), as shown in Fig. 6(d~f). Similarly,  $Q_{SR}$  is turned on with ZVS.

Fig. 6 Gate driving signals of synchronous rectification power switches, dead time and zero-voltage switching.

### IV. COMPONENT PARAMETERS DESIGN

### A. Power switches and diodes

From (10) and (14), it is shown that the voltage  $U_{\text{Cfly}}$  of the flying capacitor  $C_{\rm fly}$  is half of the output voltage  $U_{\rm O}$ , as well as the total voltage of  $C_1$  and  $C_2$ . The voltage stress of the power switches and diodes employed in the proposed topology can be deduced in terms of the energy flow paths among the voltage source, inductors and capacitors during their effective switching states as shown in Fig. 2. When  $S_1S_2=01$ ,  $Q_1$  and  $D_3$  are in the OFF state as shown in Fig. 2(a). Therefore, the blocking voltages of  $Q_1$  and  $D_3$  are  $U_{Cfly}$  and  $(U_O - U_{Cfly})$ , respectively. When  $S_1S_2=10$ ,  $Q_2$  and  $D_2$  are turned off as shown in Fig. 2(b). So, the voltage stresses of  $Q_2$  and  $D_2$  are clamped by  $(U_O - U_{Cfly})$ and  $U_{\text{Cflv}}$ , respectively. When  $S_1S_2=11$ ,  $D_1\sim D_3$  are in the OFF state as shown in Fig. 2(c). As a result, the blocking voltages of  $D_1 \sim D_3$  are  $(U_{C1} + U_{C2})$ ,  $U_{Cfly}$  and  $(U_O - U_{Cfly})$ , respectively. Stated thus, the voltage stresses of all semiconductors are obtained as follows

$$\begin{cases} U_{\text{Q1}} = U_{\text{Cfiy}} = \frac{U_{\text{O}}}{2} \\ U_{\text{Q2}} = U_{\text{O}} - U_{\text{Cfiy}} = \frac{U_{\text{O}}}{2} \\ U_{\text{D1}} = U_{\text{C1}} + U_{\text{C2}} = \frac{U_{\text{O}}}{2} \\ U_{\text{D2}} = U_{\text{Cfiy}} = \frac{U_{\text{O}}}{2} \\ U_{\text{D3}} = U_{\text{O}} - U_{\text{Cfiy}} = \frac{U_{\text{O}}}{2} \end{cases}$$

(20)

With regard to current stresses (namely average currents in the ON state) of the semiconductors  $Q_1$ ,  $Q_2$ ,  $D_1 \sim D_3$ , they can be obtained as (21), using the ampere-second equations of the capacitors  $C_{fly}$  and  $C_O$  based on the energy flow paths among the

voltage source, inductors and capacitors in the effective switching states as shown in Fig. 2.

$$I_{Q1} = \frac{4}{3-4d} \times I_{O}$$

$$I_{Q2} = \frac{4}{3-4d} \times I_{O}$$

$$I_{D1} = (\frac{4}{3-4d} - \frac{1}{1-d}) \times I_{O}$$

$$I_{D2} = \frac{I_{O}}{1-d}$$

$$I_{D3} = \frac{I_{O}}{1-d}$$

(21)

where  $I_{Q1}$ ,  $I_{Q2}$ , and  $I_{D1} \sim I_{D3}$  are average currents of  $Q_1$ ,  $Q_2$ , and  $D_1 \sim D_3$  when they are in the ON state respectively, and  $I_O$  is the output load current. In addition, the current stress of  $D_{FC}$  is the average current of the inductor  $L_1$ , namely

$$I_{\rm DFC} = I_{\rm L1} = \frac{2}{3 - 4d} I_{\rm O} \tag{22}$$

It is noted that when  $S_1S_2=10$  and 01, the current stresses of  $Q_1$  and  $Q_2$  are lower, (they are the same as the current stresses of  $D_3$  and  $D_2$  respectively as described in (21)), while they are as high as double the average currents of the inductors i.e.  $\frac{4}{3-4d} \times I_0$  when  $S_1S_2=11$ .

# B. Inductors and capacitors

According to the charging and discharging states of the inductors  $L_1$  and  $L_2$  as shown in Fig. 3(b~e),  $L_1$  and  $L_2$  are in the charging state when  $S_1S_2=11$ . The inductances of  $L_1$  and  $L_2$  can be deduced as (23)

$$\begin{cases}

L_{1} = (2d-1) \times \frac{U_{C1} + U_{in}}{\Delta i_{L1} \times 2f_{s}} \\

L_{2} = (2d-1) \times \frac{U_{C2}}{\Delta i_{L2} \times 2f_{s}}

\end{cases}$$

(23)

where  $\Delta i_{L1}$  and  $\Delta i_{L2}$  are the current fluctuations of  $L_1$  and  $L_2$ , and  $f_s$  is the switching frequency. Combining (23) with (9) and (10), the inductances of  $L_1$  and  $L_2$  can be obtained as (24), which relates the output voltage  $U_0$ , the inductor current fluctuations  $\Delta i_{L1}$  and  $\Delta i_{L2}$ , the switching frequency  $f_s$ , and the duty cycle d

$$\begin{cases} L_{1} = (2d-1) \times (1-d) \times \frac{U_{0}}{\Delta i_{L1} \times 2f_{s}} \\ L_{2} = (2d-1) \times (1-d) \times \frac{U_{0}}{\Delta i_{L2} \times 2f_{s}} \end{cases}$$

(24)

When  $S_1S_2=11$ ,  $C_1$  and  $C_2$  are in the discharging state, the capacitances of  $C_1$  and  $C_2$  can be deduced as (25), in terms of Fig. 2(c) and Fig. 3(b~g)

$$\begin{cases} C_{1} = \frac{(2d-1) \times I_{0}}{(3-4d) \times \Delta U_{C1} \times f_{s}} \\ C_{2} = \frac{(2d-1) \times I_{0}}{(3-4d) \times \Delta U_{C2} \times f_{s}} \end{cases}$$

(25)

where  $\Delta U_{C1}$  and  $\Delta U_{C2}$  are the capacitor voltage fluctuations of  $C_1$  and  $C_2$ . Regarding the flying capacitor  $C_{fly}$ , it is discharged

when  $S_1S_2=10$  as shown in Fig. 2(b), and the capacitance of  $C_{fly}$  can be obtained as

$$C_{\text{fly}} = \frac{I_{\text{O}}}{\Delta U_{\text{Cfly}} \times f_{\text{s}}} \tag{26}$$

where  $\Delta U_{\rm Cfly}$  is the capacitor voltage fluctuation of  $C_{\rm fly}$ , that is not related with the duty cycle d of power switches. In terms of Fig. 2(b), the output capacitor  $C_{\rm O}$  is only charged when  $S_1S_2=10$ ; the capacitance of  $C_{\rm O}$  can be deduced as

$$C_{\rm o} = \frac{d \times I_{\rm o}}{\Delta U_{\rm o} \times f_{\rm s}} \tag{27}$$

where  $\Delta U_{\rm O}$  is the capacitor voltage fluctuation of  $C_{\rm O}$ .

### C. Comparisons with other step-up solutions

According to the deduced above, the comparisons can be drawn between the proposed and the other step-up solutions as shown in TABLE I. The conventional Boost and three-level Boost DC-DC converters need one inductor respectively, but their ideal voltage-gain of 1/(1-d) is limited due to the effects of parasitic resistance and extreme duty cycles. It is noted that the voltage stress of four semiconductors in the three-level Boost DC-DC converter can be reduced a half comparing with that of the conventional one, due to using two additional semiconductors and one flying capacitor. The high voltage-gain step-up DC-DC converters in [23] and [33] need two inductors respectively. Although six semiconductors are employed in the converter without the snubber circuit in [23], there still exist two diodes with the voltage stress of  $U_0$ , and its maximum conversion efficiency is about 92.6%. While a maximum conversion efficiency of the converter in [33] is improved to 94%, three semiconductors and three capacitors are needed. However, the voltage stress of all the semiconductors is between  $U_{\rm O}/2$  and  $U_{\rm O}$ , e.g.  $3U_{\rm O}/4$ , rather than  $U_{\rm O}/2$ . Regarding the proposed converter, the number of main components is between those of the converters in [23] and [33], the voltage stress of all the semiconductors is  $U_0/2$ , and its maximum conversion efficiency can be 95.66%, which is higher than those in [23] and [33].

# V. EXPERIMENTAL RESULTS AND ANALYSIS

In order to verify the feasibility and effectiveness of the proposed BTL-SRqZ for fuel cell vehicles, a scale-down 1.2 kW BTL-SRqZ converter prototype was constructed as shown in Fig. 7. In the experiment, the fuel cell stack source  $U_{FC}=U_{in}$  is replaced by an adjustable DC voltage source with a range of  $U_{\rm in}$ =60~150V, and the converter voltage loop is controlled by a TMS320F28335 DSP. The power circuit IXTK102N30P MOSFETs (its rated voltage is 300V, and its rated current is 102A, while the output voltage of the converter is  $U_0$ =400V), and DSEC60-03A Schottky Barrier Diodes are used. In addition, the switching frequency is  $f_s=10$  kHz, the dead time is  $t_d=1 \,\mu s$ , the initial values of the qZ source inductors are  $L_1$ =228  $\mu$ H and  $L_2=225 \,\mu\text{H}$  respectively, the load resistor is  $R_L=133\sim400\,\Omega$ , and the reference output voltage is 400V. The main experimental parameters of the proposed converter are shown in TABLE II.

| TABLE I Comparisons | between r | proposed and | other step-ur | o solutions. |

|---------------------|-----------|--------------|---------------|--------------|

|                     |           |              |               |              |

| Step-up Solutions                 | Voltage Gain                           | Amount of<br>Semiconductors | Amount of<br>Inductors | Amount of<br>Capacitors | Voltage<br>Stress           | <b>Current Stress</b>                                                                                                  | Maximum<br>Efficiency |

|-----------------------------------|----------------------------------------|-----------------------------|------------------------|-------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Conventional Boost                | $\frac{1}{1-d},$ $(0 < d < 1)$         | 2                           | 1                      | 1                       | $U_{\mathrm{o}}$            | $\frac{1}{1-d}I_{0}$                                                                                                   | -                     |

| Three-level Boost                 | $\frac{1}{1-d},$ $(0 < d < 1)$         | 4                           | 1                      | 2                       | $\frac{U_{\rm o}}{2}$       | $\frac{1}{1-d}I_{\mathrm{O}}$                                                                                          | -                     |

| Converter without snubber in [23] | $\frac{2}{1-d},$ $(0 < d < 1)$         | 6                           | 2                      | 3                       | $\frac{U_{o}}{2}$ , $U_{o}$ | $\frac{1.5}{1-d}I_{0}$ , $\frac{0.5}{1-d}I_{0}$                                                                        | 92.6%                 |

| Converter in [33]                 | $\frac{2(1-d)}{1-2d},$ $(0 < d < 0.5)$ | 3                           | 2                      | 3                       | $\frac{U_{\rm O}}{2(1-d)}$  | $\frac{1}{d(1-2d)}I_{0},$ $\frac{2}{1-2d}I_{0}, \frac{1}{d}I_{0}$                                                      | 94%                   |

| Proposed converter                | $\frac{2}{3-4d},$ (0.5<= $d$ < 0.75)   | 5                           | 2                      | 4                       |                             | $\begin{aligned} &\frac{4}{3-4d}I_{\rm O},\\ &\frac{1}{(3-4d)(1-d)}I_{\rm O},\\ &\frac{1}{1-d}I_{\rm O} \end{aligned}$ | 95.66%                |

| TO A TO T TO TE A C      | . 1                    | 1 .               |

|--------------------------|------------------------|-------------------|

| TABLE II Main experime   | ntal narameters of nr  | onosed converter  |

| 17 IDEE II Main experime | intai parameters or pr | oposed converter. |

| TABLE II Main experimental parameters of proposed converter. |                         |  |

|--------------------------------------------------------------|-------------------------|--|

| Parameters and components                                    | Values (units)          |  |

| Rated power P <sub>n</sub>                                   | 1.2kW                   |  |

| Input dc voltage $U_{in}$                                    | 60~150V                 |  |

| Output dc voltage $U_0$                                      | 400V                    |  |

| Switching frequency $f_s$                                    | 10kHz                   |  |

| Dead time $t_d$                                              | 1 μs                    |  |

| Inductor $L_1$                                               | 228 μΗ                  |  |

| Inductor $L_2$                                               | 225 μΗ                  |  |

| Capacitors $C_1$ , $C_2$ , $C_{fly}$                         | $450V/660~\mu F$        |  |

| Capacitor Co                                                 | $450V/440~\mu F$        |  |

| Load $R_{\rm L}$                                             | 133~400 Ω               |  |

| MOSFETs $Q_1$ , $Q_2$ , $Q_{SR}$                             | IXTK102N30P (300V/102A) |  |

| Diodes $D_2$ , $D_3$ , $D_{FC}$                              | DSEC60-03A (300V/60A)   |  |

Fig. 7 Experimental prototype.

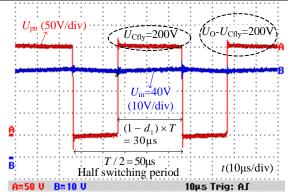

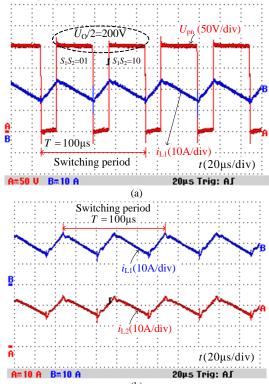

Even when the input voltage is  $U_{\rm in}$ =40V, the experimental PWM voltage  $U_{\rm pn}$  is shown in Fig. 8, and the frequency of  $U_{\rm pn}$  is double of the switching frequency. Although the step-up voltage-gain ( $U_{\rm O}/U_{\rm in}$ ) is 10, the actual duty cycles (d=d<sub>1</sub>=d<sub>2</sub>=1-0.3=0.7) are about 0.7, instead of the actual extreme value of the typical boost converter, which is more than 0.9 under the action of the voltage control loop. Furthermore, the amplitude of  $U_{\rm pn}$  is 200V (alternating with the flying-capacitor voltage  $U_{\rm Cfly}$  and  $U_{\rm O}-U_{\rm Cfly}$ ), namely half the output voltage. Thus, it verifies  $U_{\rm Cfly}$ = $U_{\rm O}/2$  in the steady state, and the flying-capacitor voltage self-balances well without any extra controls.

Fig. 8 Output PWM voltage when input voltage  $U_{in}$ =40V and M=10.

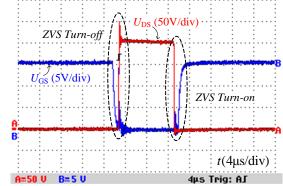

The experimental results of the synchronous rectification ZVS for the SRqZ source system are shown in Fig. 9. Because of the dead time  $t_d$ =1  $\mu s$ ,  $Q_{SR}$  is bound to be turned on with a delay, and the anti-parallel body diode  $D_{SR}$  is conducted during the dead time. It is noticed that the voltage stress of  $Q_{SR}$  changes from the forward voltage drop of  $D_{SR}$  to half the output voltage during the dead time. Therefore,  $Q_{SR}$  can be turned off with ZVS, as shown in Fig. 9. Similarly, the voltage stress of  $Q_{SR}$  changes from half the output voltage to the forward voltage drop of  $D_{SR}$  during the dead time. Thus,  $Q_{SR}$  can be turned on with ZVS.

Fig. 9 Experimental results of synchronous rectification ZVS.

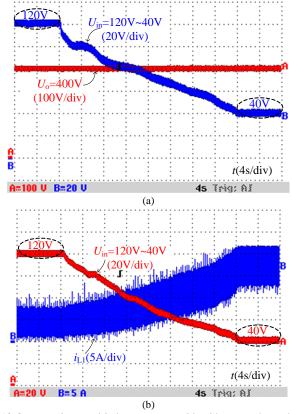

As to the applicability of the proposed converter for the fuel

cell vehicles, the experimental results, in which the input voltage  $U_{\rm in}$  is changed gradually from the wide range of 120V to 40V over dozens of seconds are shown in Fig. 10(a). It is seen that the output voltage  $U_{\rm O}$  nearly stays around the reference voltage 400V under the action of the voltage control loop, and the wide step-up voltage-gain ( $U_{\rm O}/U_{\rm in}$ ) range changes from 3.3 to 10. In fact, the actual voltage-gain in the voltage control loop is more than 3.3 to 10 due to the losses compensation of the converter's operation. Correspondingly, the input current ( $i_{\rm L1}$ ) increases gradually with the wide-range changed input voltage (from 120V to 40V), as shown in Fig. 10(b), when the load is constant.

Fig. 10 Output voltage and inductor current with wide-range changed input voltage from 120V to 40V in dynamic state. (a) Output and input voltages. (b) Input current and voltage.

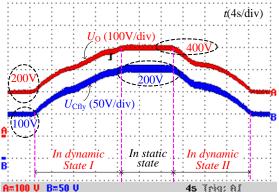

In Fig. 11, the flying-capacitor voltage  $U_{\rm Cfly}$  is changed according to the output voltage  $U_{\rm O}$  (between 200V and 400V in the open loop) in the static and dynamic states. It is noticed that the flying-capacitor voltage  $U_{\rm Cfly}$  still keeps at half of the output voltage  $U_{\rm O}$ , especially in the dynamic states I and II. Because the voltage across the flying-capacitor is clamped by the total voltages of the qZ source capacitors, whose voltages are related to the corresponding real-time duty cycles and the output voltage  $U_{\rm O}$ .

Under the voltage control loop, the proposed BTL-SRqZ converter operates well in conditions of the output voltage  $U_0$ =400V, and the output power  $P_0$ =1.2 kW. The output PWM voltage  $U_{\rm pn}$  and the inductor current  $i_{\rm L1}$  are shown in Fig. 12(a). The inductor  $L_1$  is charged when the instantaneous PWM voltage of  $U_{\rm pn}$  is zero ( $S_1S_2$ =11). Then the inductor  $L_1$  is discharged when  $U_{\rm pn}$  stays at  $U_0$ /2=200V ( $S_1S_2$ =01 or 10). In addition, the current  $i_{\rm L2}$  of the inductor  $L_2$  is nearly the same as that of  $L_1$ , as shown in Fig. 12(b). Therefore, the inductors of the

Fig. 11 Dynamic flying capacitor voltage corresponding to the variable output voltage  $U_0$ =200~400V in open loop.

qZ source are charged and discharged twice during each switching period. Compared with the converter in [33], there are one additional active power switch and two more diodes in the proposed converter. However, the equivalent switching frequency of the proposed converter is double the one of the converter in [33]. All the volumes of capacitors and inductors in the quasi-Z-source can be reduced by almost a half compared with those of the converter in [33]. In addition, the quasi-Z-source capacitor voltage stresses are lower than those of the converter in [33]. Therefore, the volume of the proposed converter can be significantly reduced compared to that of the converter in [33].

Fig. 12 Output PWM voltage and inductor currents. (a) Output PWM voltage and inductor current. (b) Inductor currents.

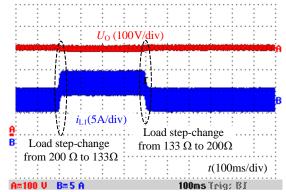

In order to validate the dynamic behavior of the proposed converter, an experiment was carried out which used a step change of load between  $133\Omega$  and  $200\Omega$ , and the output voltage and inductor current are shown in Fig. 13. The inductor currents (e.g.  $i_{\rm L1}$ ) have corresponding responses between 8A and 12A, and the output voltage  $U_{\rm O}$  nearly keeps at constant 400V with

the voltage loop. It can be seen that  $i_{L1}$  changes to 12A from 8A over 20ms with the load step-change from  $200\Omega$  to  $133\Omega$ , and it recovers from 12A to 8A over 20ms with the load step-change from  $133\Omega$  to  $200\Omega$ .

Fig. 13 Output voltage and inductor current when load step-change between  $133\Omega$  and  $200\Omega.$

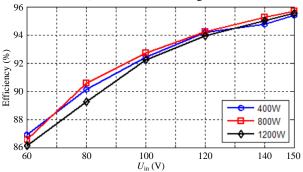

For the wide input-voltage range operation of the proposed converter, the conversion efficiencies related to the variable input voltages (e.g. 60V, 80V, ...., 140V, 150V) and the different output powers (e.g. 400W, 800W, 1200W) are measured by a Power Analyzer (Yokogawa-WT3000). Then, the relationship between the efficiency, the variable input voltages and the different output powers in SR operation are illustrated in Fig. 14. It is noticed that the maximum measured efficiency in SR operation is about 95.66% as shown in Fig. 14. In addition, when the output power is constant and the input voltage declines, the efficiency decreases correspondingly, due to the increasing losses caused by the growing input current. In the same conditions above, the efficiencies in DR operation are also measured, and the SR efficiency is higher than that of DR. The minimum efficiency difference area appears around the medium input voltage ( $U_{in}=120V$ ), and its average efficiency difference is about 0.6%. While the maximum efficiency difference area exists around the lower and higher input voltage  $(U_{\rm in}=80{\rm V})$  and 150V) areas, and its average value is near 0.85%.

Fig. 14 Relationship between efficiency, variable input voltages and different output powers in SR operation.

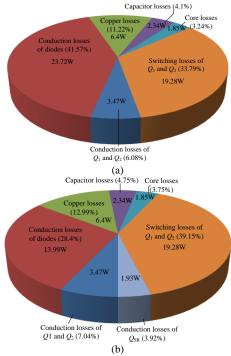

The calculated loss distributions for the experiment when  $U_{\rm in}=150{\rm V}$  and  $P_{\rm O}=1200{\rm W}$  are shown in Fig. 15. In DR operation, the total losses of the converter are 57.06W, and the loss distribution is shown in Fig. 15(a). The turn-on and turn-off (switching) and conduction losses of  $Q_1$  and  $Q_2$  account for 39.87% of the total losses. The conduction losses of all diodes  $D_1$ - $D_3$  and  $D_{\rm FC}$  account for 41.57% of the total losses, which is a little more than the switching and conduction losses of  $Q_1$  and  $Q_2$ , due to the higher conduction loss of  $D_1$  (in the

quasi-Z-source). However, the total losses of the converter are reduced to 49.26W in the SR operation, and the loss distribution is shown in Fig. 15(b). The switching and conduction losses of  $Q_1$  and  $Q_2$  account for 46.19% of the total losses, and the conduction losses of  $D_2$ ,  $D_3$ ,  $D_{FC}$  and  $Q_{SR}$  are reduced to 32.32% of the total losses due to the SR operation of  $Q_{SR}$ , instead of  $D_1$  in the quasi-Z-source.

Fig. 15 Calculated loss distributions for experiment when  $U_{in}=150V$  and  $P_{0}=1200W$ . (a) In DR operation. (b) In SR operation.

# VI. CONCLUSION

The topology of the BTL-SRqZ is proposed in this paper. It has the advantages of lower voltage stress for the power semiconductors and the common ground between the input and output sides, as well as the wider range of the voltage-gain with modest duty cycles [0.5,0.75) for the power switches. In addition, the voltage of the flying-capacitor can be clamped well at half the output voltage by the capacitor voltages of the quasi-Z source net in both the static and dynamic states. At the same time, the synchronous rectification power switch operates with ZVS turn-on and turn-off, and the losses of the quasi-Z source circuit can be reduced by the synchronous rectification operation. Therefore, it is suitable to vehicles powered by a fuel cell stack which has a soft output characteristic.

# REFERENCES

- C. Jin, X. Sheng, and P. Ghosh, "Optimized electric vehicle charging with intermittent renewable energy sources," *IEEE Journal of Selected Topics* in Signal Processing, vol. 8, no. 6, pp. 1063–1072, Dec. 2014.

- [2] B. Zeng, J. Zhang, X. Yang, J. Wang, J. Dong, and Y. Zhang, "Integrated planning for transition to low-carbon distribution system with renewable energy generation and demand response," *IEEE Trans. Power Syst.*, vol. 29, no. 3, pp. 1153–1165, May 2014.

- [3] A. Soroudi, R. Caire, N. Hadjsaid, and M. Ehsan, "Probabilistic dynamic multi-objective model for renewable and non-renewable distributed generation planning," *IET Gener. Transm. Distrib.*, vol. 5, no. 11, pp. 1173–1182, May 2011.

- [4] K. Li, T. Chen, Y. Luo, and J. Wang, "Intelligent environment-friendly vehicles: concept and case studies," IEEE Trans. Intelligent Transportation Systems, vol. 13, no. 1, pp. 318-328, Mar. 2012.

- A. T-Raissi, and D. L. Block, "Hydrogen: automotive fuel of the future," IEEE Power & Energy Magazine, vol. 2, no. 6, pp. 40-45, Nov. 2004.

- A. S. Samosir, and A. H. M. Yatim, "Implementation of dynamic evolution control of bidirectional DC-DC converter for interfacing ultracapacitor energy storage to fuel-cell system," IEEE Trans. Ind. Electron., vol. 57, no. 10, pp. 3468-3473, Oct. 2010.

- [7] G. Fontes, C. Turpin, and S. Astier, "A Large-signal and dynamic circuit model of a H<sub>2</sub>/O<sub>2</sub> PEM fuel cell: description, parameter identification, and exploitation," IEEE Trans. Ind. Electron., vol. 57, no. 6, pp. 1874-1881, Jun. 2010.

- A. Askarzadeh, and A. Rezazadeh, "An innovative global harmony search algorithm for parameter identification of a PEM fuel cell model," IEEE Trans. Ind. Electron., vol. 59, no. 9, pp. 3473-3480, Sep. 2012.

- J. Morales-Morales, I. Cervantes, and U. Cano-Castillo, "On the design of robust energy management strategies for FCHEV," IEEE Trans. Veh. Technol., vol. 64, no. 5, pp. 1716-1728, May 2015.

- [10] G. Su, and L. Tang, "A reduced-part, triple-voltage DC-DC converter for EV/HEV power management," IEEE Trans. Power Electron., vol. 24, no. 10, pp. 2406-2410, Oct. 2009.

- [11] U. R. Prasanna, and A. K. Rathore, "Dual three-pulse modulation-based high-frequency pulsating DC link two-stage three-phase inverter for electric/hybrid/fuel cell vehicles applications," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 2, no. 3, pp. 477-486, Oct. 2014.

- [12] J. Jia, G. Wang, Y. T. Cham, Y. Wang, and M. Han, "Electrical characteristic study of a hybrid PEMFC and ultracapacitor system," IEEE Trans. Ind. Electron., vol. 57, no. 6, pp. 1945-1953, Dec. 2010.

- [13] N. D. Benavides, and P. L. Chapman, "Mass-optimal design methodology for DC-DC converters in low-power portable fuel cell applications," IEEE Trans. Power Electron., vol. 23, no. 3, pp. 1545–1555, May 2008.

- G. Dotelli, R. Ferrero, P. G. Stampino, S. Latorrata, and S. Toscani, "PEM fuel cell drying and flooding diagnosis with signals injected by a power converter," IEEE Trans. Instrum. Meas., vol. 64, no. 8, pp. 2064-2071,

- [15] S. Dusmez, A. Hasanzadeh, and A. Khaligh, "Comparative analysis of bidirectional three-level DC-DC converter for automotive applications, IEEE Trans. Ind. Electron., vol. 62, no. 5, pp. 1063-1072, May 2015.

- [16] H. Chen, and J. Liao, "Design and implementation of sensorless capacitor voltage balancing control for three-level Boosting PFC," IEEE Trans. Power Electron., vol. 29, no. 7, pp. 3808-3817, Jul. 2014.

- [17] X. Ruan, B. Li, Q. Chen, S. Tan, and C. K. Tse, "Fundamental considerations of three-level DC-DC converters: topologies, analyses, and control," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 11, pp. 3733-3743, Dec. 2008.

- [18] L. Shi, B. P. Baddipadiga, M. Ferdowsi, and M. L. Crow, "Improving the dynamic response of a flying-capacitor three-level Buck converter," IEEE Trans. Power Electron., vol. 28, no. 5, pp. 2356-2365, May 2013

- [19] Y. J. A. Alcazar, D. S. Oliveira, Jr., F. L. Tofoli, and R. P. Torrico-Bascopé, "DC-DC nonisolated Boost converter based on the three-state switching cell and voltage multiplier cells," IEEE Trans. Ind. Electron., vol. 60, no. 10, pp. 4438-4449, Oct. 2013.

- [20] Y. Tang, D. Fu, T. Wang, and Z. Xu, "Hybrid switched-inductor converters for high step-up conversion," IEEE Trans. Ind. Electron., vol. 62, no. 3, pp. 1480-1490, Mar. 2015.

- [21] W. Qian, D. Cao, J. G. Cintrón-Rivera, M. Gebben, D. Wey, and F. Z. Peng, "A switched-capacitor DC-DC converter with high voltage gain and reduced component rating and count," IEEE Trans. Ind. Appl., vol. 48, no. 4, pp. 1397-1406, Jul./Aug. 2012.

- [22] A. M. Jorge, L. Rodrigo, P. Elvia, and L. G. Jorge, "Modelling and control of a DC-DC quadratic boost converter with R<sup>2</sup>P<sup>2</sup>," IET Power Electron., vol. 7, no. 1, pp. 11-22, May 2014.

- [23] R. Gules, L. L. Pfitscher, and L. C. Franco, "An interleaved Boost DC-DC converter with large conversion ratio," ISIE'03, pp. 411-416, Jun. 2003.

- [24] Q. Zhao, and F. C. Lee, "High-efficiency, high step-up DC-DC converters," IEEE Trans. Power Electron., vol. 18, no. 1, pp. 65-73, Jan.

- [25] G. A. L. Henn, R. N. A. L. Silva, P. P. Praça, L. H. S. C. Barreto, and D. S. Oliveira, "Interleaved-Boost converter with high voltage gain," IEEE Trans. Power Electron., vol. 25, no. 11, pp. 2753-2761, Nov. 2010.

- [26] P. P. Praça, G. A. L. Henn, D. S. Oliveira, L. H. S. C. Barreto, and R. N. A. L. Silva, "High voltage gain single stage DC-DC converter based on three-state commutation cell," APEC'13, pp. 2882–2887, Mar. 2013.

- [27] S. J. Amodeo, H. G. Chiacchiarini, and A. R. Oliva, "High-performance control of a DC-DC Z-source converter used for an excitation field driver," IEEE Trans. Power Electron., vol. 27, no. 6, pp. 2947–2957, Jun. 2012.

- [28] V. P. Galigekere and M. K. Kazimierczuk, "Analysis of PWM Z-source DC-DC converter in CCM for steady state," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 4, pp. 854-863, Apr. 2012.

- [29] S. Yang, F. Z. Peng, Q. Lei, R. Inoshita, and Z. Qian, "Current-fed quasi-Z-source inverter with voltage Buck-Boost and regeneration capability," IEEE Trans. Ind. Appl., vol. 47, no. 2, pp. 882-892, Mar./Apr. 2011.

- [30] O. Ellabban, H. Abu-Rub, and B. Ge, "A quasi-Z-source direct matrix converter feeding a vector controlled induction motor drive," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 3, no. 2, pp. 1063-1072, Jun. 2015.

- [31] K. Patidar, and A. C. Umarikar, "High step-up pulse-width modulation DC-DC converter based on quasi-Z-source topology," IET Power Electron., vol. 8, no. 4, pp. 477-488, 2015.

- [32] B. Poorali, A. Torkan, and E. Adib, "High step-up Z-source DC-DC converter with coupled inductors and switched capacitor cell," IET Power Electron., vol. 8, no. 8, pp. 1394-1402, 2015.

- [33] H. Shen, B. Zhang, D. Qiu, and L. Zhou, "A common grounded Z-source DC-DC converter with high voltage gain," IEEE Trans. Ind. Electron., vol. 63, no. 5, pp. 2925-2935, 2016.

Yun Zhang (M'13) was born in Jiangsu, China, in 1980. He received the B.S. and M.S. degrees in electrical engineering from the Harbin University of Science and Technology, Harbin, China, in 2003 and 2006, respectively, and the Ph.D. degree in electrical engineering from the Harbin Institute of Technology, Harbin, in 2010.

He is currently an Associate Professor at the School of Electrical Engineering and Automation, Tianjin University, Tianjin, China. His current research

interests include topologies, modulation, and control strategies of power converters for microgrid and electric vehicles.

Jilong Shi was born in Shandong, China. He received his B.S. degree in Electrical Engineering from the Changchun University Of Science and Technology, Changchun, China, in 2014. He started pursing his M.S. degree in Electrical Engineering from Tianjin University, Tianjin, China, in 2014. His current research interests include DC-DC converters, and fuel cell vehicles.

Lei Zhou was born in Ningxia, China. He received his B.S. degree in Electrical Engineering from the Tianjin University, Tianjin, China, in 2015. He started pursing his M.S. degree in Electrical Engineering from Tianjin University, Tianiin, China, in 2015. His current research interests include DC-DC converters, modeling and analysis of DC-DC converters.

Jing Li (M'15) received the B.Eng. (Hons.) and M.Sc. (Distinction) degrees from the Beijing Institute of Technology, Beijing, China, in 1999, and 2002, respectively, and the Ph.D. degree from the University of Nottingham, Nottingham, U.K., in

She was a Research Fellow with the Power Electronic, Machine and Control Group, University of Nottingham. She is currently a Lecturer at the Department of Electrical and Electronic Engineering, University of Nottingham, Ningbo, China. Her research interests include condition monitoring for

motor drive systems and power distribution systems and advanced control and design of motor drive systems.

Mark Sumner (SM'05) received the B.Eng. degree in electrical and electronic engineering from Leeds University, Leeds, U.K., in 1986, and the Ph.D. degree in induction motor drives from the University of Nottingham, Nottingham, U.K., in 1992.

He was with Rolls Royce, Ltd., Ansty, U.K. He was a Research Assistant with the University of Nottingham, where he became a Lecturer in October 1992, and is currently a Professor of electrical energy systems. His research interests include control of power electronic

systems including sensorlessmotor drives, diagnostics and prognostics for drive systems, power electronics for enhanced power quality, and novel power system fault location strategies.

Ping Wang was born in Tianjin, China, in 1959. She received the B.S., M.S., and Ph.D.degrees in Electrical Engineering from the Tianjin University, Tianjin, China, in 1981, 1991, and 2005, respectively. Since 1981, she has been a Teacher and a Researcher at Tianjin University, where she is currrently a Professor.

Her current research interests include power electronic control of renewable energy sources, PWM converters, and intelligent detection and control.

Changliang Xia (M'08-SM'12) was born in Tianjin, China, in 1968. He received the B.S. degree from Tianjin University, China, in 1990, and the M.S. and Ph.D. degrees from Zhejiang University, China, in 1993 and 1995 respectively, all in electrical engineering.

He is currently a Professor in the School of Electrical Engineering and Automation, Tianjin University, and also in Tianjin Key Laboratory of Advanced Technology of Electrical Engineering and

Energy, Tianjin Polytechnic University. In 2008, he became "Yangtze Fund Scholar" Distinguished Professor and is currently supported by National Science Fund for Distinguished Young Scholars. His research interests include electrical machines and their control systems, power electronics, and control of wind generators.