### Papadopoulos, Savvas (2017) A hybrid power converter with enhanced switching ripple cancellation. PhD thesis, University of Nottingham.

#### Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/41112/1/Savvas%20Papadopoulos\_A%20Hybrid%20Power%20Converter%20with%20Enhanced%20Switching%20Ripple%20Cancellation.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the Creative Commons Attribution Non-commercial licence and may be reused according to the conditions of the licence. For more details see: http://creativecommons.org/licenses/by-nc/2.5/

For more information, please contact eprints@nottingham.ac.uk

# A HYBRID POWER CONVERTER WITH ENHANCED SWITCHING RIPPLE CANCELLATION

Savvas Papadopoulos MEng. (Hons)

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

Sept 2016

### Abstract

As worldwide electricity demand increases, so does the requirement for effective power conversion combining increased efficiency with minimal harmonic pollution at the lowest financial cost. For medium to high voltage grid-connected applications, multilevel converter topologies enabled the use of lower rated and more efficient self-commutated switches. Due to practical limitations, efficient operation of converters with a low number of levels is restricted to low switching frequencies which in turn becomes a limiting factor for the design of smaller passive filters that are required to limit the associated switching harmonics injected in the AC grid.

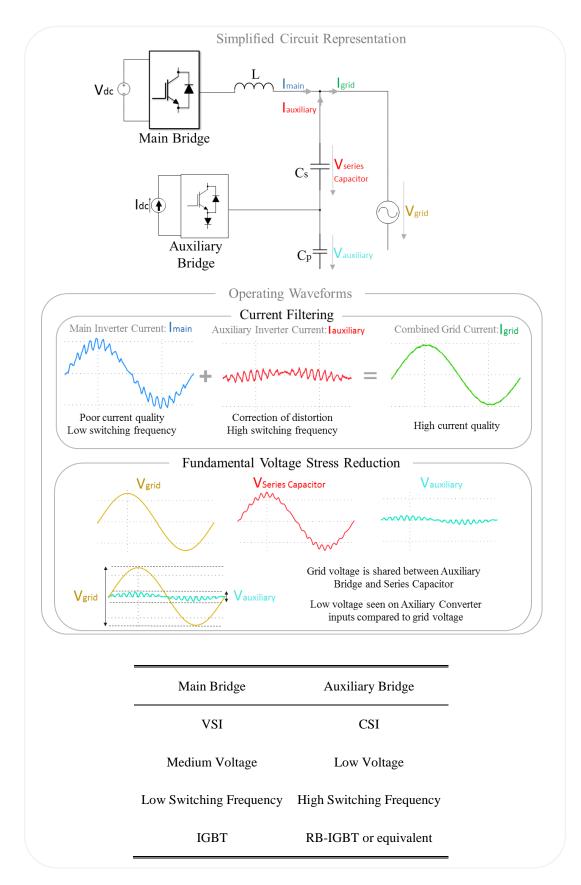

This thesis investigates the use of a novel hybrid converter concept aimed at medium-voltage (MV) grid-connected applications. Hybrid converters consist of a main inverter processing the bulk of the power with poor waveform performance and a fast and versatile auxiliary inverter to correct the distortion. In this case, the main converter is a medium-voltage three-level Neutral Point Clamped (NPC) inverter and the auxiliary inverter is a low-voltage and low-current rated Current Source Inverter (CSI), fitted with a series capacitor that is used to minimise the CSI voltage stress. As a result the added installed power by the auxiliary CSI switches can remain at very low levels (theoretically <4%), resulting in a minimal added cost, whilst offering a substantial harmonic improvement to the main VSI. Furthermore the auxiliary converter can be retro-fitted to an existing MV inverter installation to improve the current harmonic quality as required by new grid standards, at a minimal cost.

The performance of the proposed hybrid solution is evaluated through simulation at 3.3 kV MV level under various grid interconnection scenarios. The feasibility of the concept is validated experimentally, scaled to 415V grid voltage level (a more realistic level for a laboratory demonstrator) while operating under more challenging conditions such as switching ripple levels of 50% peak relative to the fundamental peak, showing that the added installed power can be as low as 7% with very high output grid current quality under all grid scenarios considered.

### Acknowledgements

I would like to express my gratitude to my supervisors Christian Klumpner, Mohamed Rashed and Pat Wheeler for their guidance and technical support which was vital towards the completion of this project. Furthermore, I would to thank Dr Klumpner for his mentorship, exemplar attitude, unprecedented dedication and availability, as well as for motivating me to pursue this path.

I would like to thank my family; my parents Πάυλος, Γιώτα and my sister Μαρία; for their unconditional psychological, emotional and substantial financial support towards my education and all my endeavours.

I would like to thank my friends, close and far away, for their kind listening, advice and motivation on the ups and downs during these four years. Among them I would like to thank my PEMC friends who I now consider as part of a second family. Thank you Marija, Manju, Attahir, Shajjad, Emre, Shuai, Luca T and Luca P, Stefano, Francesco, Alessandro, Bilal, Sharmila and Demetris. Without their advice, support and understanding, this venture into the unknown would not have been worthwhile.

I would like to thank Lee Empringham and Liliana DeLillo for their work in the foundations of the group whose legacy should be duly recognised. Special thanks to Chintan Patel for his technical support and advice at the initial stages of this project. I would also like to thank the department staff and technicians Mark Birkin, Colin Blackburn, Matthew Cooper and John Nakutis for their kind help in ensuring the experimental setup and safety is up to standards.

Last but not least I would like to thank Han for standing by my side, her support, understanding and patience during the completion of this project. The pursuit of a PhD is a journey like no other and it would not have been the same without the guidance and support of those around me.

# List of Contents

| CHAPTER 1. | Introduction                                             | . 1 |

|------------|----------------------------------------------------------|-----|

| 1.1. Moti  | vation for Project                                       | . 1 |

| 1.2. Over  | view                                                     | . 1 |

| 1.3. Aims  | s and Objectives                                         | . 5 |

| 1.4. Thes  | is Outline and Content                                   | . 6 |

| CHAPTER 2. | Literature Review and Background                         | . 8 |

| 2.1. Volta | age and Current Source Inverters: a Brief History        | . 8 |

| 2.2. Conv  | verters for Medium Voltage Applications                  | . 9 |

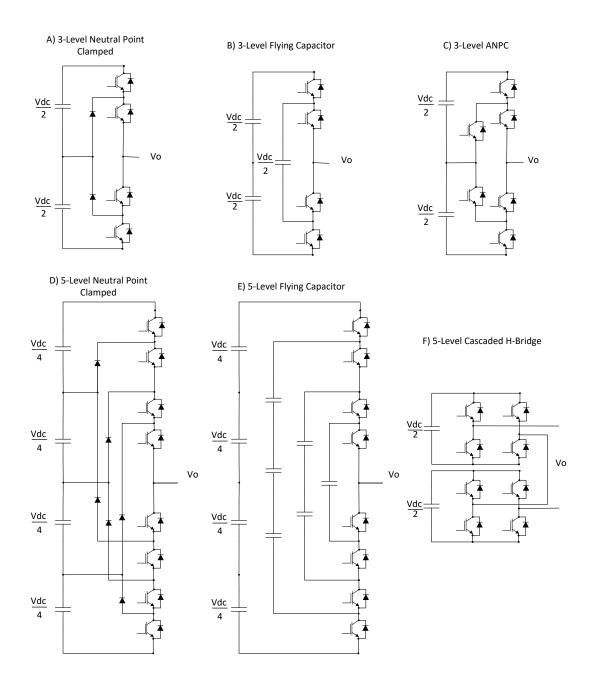

| 2.2.1.     | Multilevel Inverter Solutions                            | 10  |

| 2.3. Harn  | nonic Mitigation Techniques                              | 14  |

| 2.3.1.     | Higher Order Passive Filters                             | 14  |

| 2.3.2.     | Selective Harmonic Elimination PWM                       | 15  |

| 2.3.3.     | Active Power Filtering for Low Order Harmonics           | 16  |

| 2.4. Hybr  | id Topologies                                            | 17  |

| 2.4.1.     | Use of Series Capacitors for Reduction of Voltage Rating | 18  |

| 2.4.2.     | Series Capacitors with a Current Source Inverter         | 21  |

| 2.4.3.     | Active Current Ripple Cancellation Technique             | 22  |

| 2.5. The 1 | Hybrid Topology                                          | 23  |

| 2.5.1.     | Harmonic Output of a PWM VSI                             | 24  |

| 2.5.2.     | Choice of Auxiliary Inverter Topology                    | 27  |

| 2.5.3.     | Novelty and Potential Benefits of the Proposed Topology  | 27  |

| 2.5.4.    | Performance Evaluation Approach                          | . 28 |

|-----------|----------------------------------------------------------|------|

| 2.6. Con  | nclusion                                                 | . 30 |

| CHAPTER 3 | . Three-Phase Hybrid Inverter Using Series Capacitor     | . 32 |

| 3.1. Тој  | pology Introduction                                      | . 32 |

| 3.2. Cir  | cuit Operation                                           | . 33 |

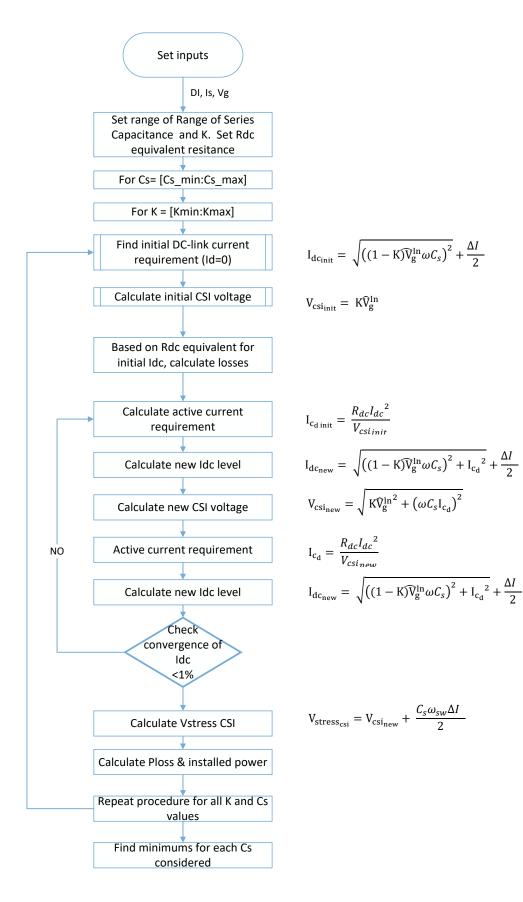

| 3.3. Des  | sign Procedure                                           | . 34 |

| 3.3.1.    | VSI Design                                               | . 34 |

| 3.3.2.    | Series Capacitor Design                                  | . 35 |

| 3.3.3.    | CSI AC Filter Design                                     | . 41 |

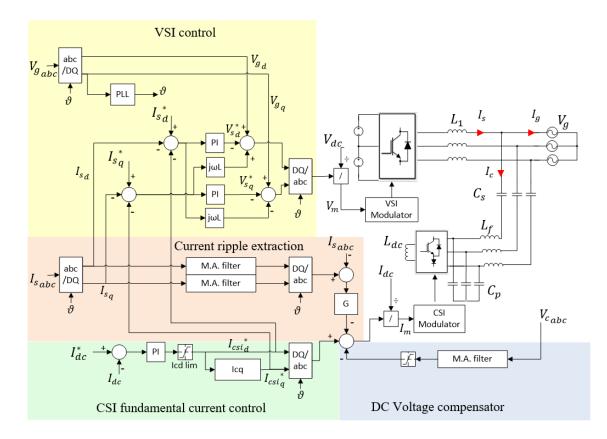

| 3.4. Con  | ntrol Circuit                                            | . 43 |

| 3.4.1.    | CSI Fundamental Current Reference Synthesis              | . 43 |

| 3.4.2.    | Current Ripple Extraction                                | . 45 |

| 3.4.3.    | DC Voltage Compensator                                   | . 45 |

| 3.4.4.    | VSI Control                                              | . 46 |

| 3.5. Me   | dium Voltage Hybrid System Design                        | . 47 |

| 3.5.1.    | Optimisation Results                                     | . 47 |

| 3.6. Sin  | nulation Results for Operation with Ideal Voltage Source | . 51 |

| 3.6.1.    | Steady State Performance                                 | . 52 |

| 3.6.2.    | DC Voltage Compensator Validation                        | . 59 |

| 3.6.3.    | Current Ripple Extraction and Transient Performance      | . 62 |

| 3.6.4.    | Series Capacitor Impact on the Output Power Factor       | . 66 |

| 3.6.5.    | Semiconductor Loss Estimation                            | . 67 |

| 3.7. Co   | nclusions                                                | . 70 |

| Filter    | 71                                                                        |     |

|-----------|---------------------------------------------------------------------------|-----|

| 4.1.      | Topology Introduction with Non-Zero Grid Impedance                        | 2'2 |

| 4.1.1.    | Small Grid Impedance                                                      | 2'2 |

| 4.1.2.    | Large Grid Impedance: LCL Interconnection                                 | '5  |

| 4.2. I    | Modified Design Procedure                                                 | 7   |

| 4.2.1.    | LCL Filter Design Procedure                                               | '8  |

| 4.2.2.    | CSI Active Filter Design                                                  | '8  |

| 4.3. I    | Resonance Damping: Passive and Active Damping                             | 31  |

| 4.3.1.    | Passive Damping                                                           | 31  |

| 4.3.2.    | Active Damping                                                            | 32  |

| 4.4.      | Simulation Results                                                        | 34  |

| 4.4.1.    | Active Damping Validation                                                 | 35  |

| 4.4.2.    | Transient and Steady State Results                                        | 37  |

| 4.5. I    | Higher Order Grid Impedance and Effect of Impedance Variation: PCC Voltag | ze  |

| Filtering | g                                                                         | )3  |

| 4.5.1.    | PCC Voltage Filter Design                                                 | 93  |

| 4.5.2.    | Effect of Grid Inductance Variation9                                      | )5  |

| 4.5.1.    | Semiconductor Loss Estimation                                             | 97  |

| 4.5.2.    | Added Installed Power                                                     | 98  |

| 4.6. 0    | Conclusion                                                                | )8  |

| CHAPTER   | R 5. Experimental Setup                                                   | )1  |

| 5.1. I    | Experimental Rig Overview                                                 | )1  |

| 5.1.1.     | CSI and VSI Implementations                                           | 102 |

|------------|-----------------------------------------------------------------------|-----|

| 5.1.2.     | The Overvoltage Protection                                            | 106 |

| 5.1.3.     | Design Procedure and Passive Component Sizing                         | 107 |

| 5.2. Con   | trol Platform                                                         | 111 |

| 5.2.1.     | VSI and CSI Modulator                                                 | 113 |

| 5.2.1.     | Data Acquisition                                                      | 117 |

| 5.2.2.     | Control System Outline                                                | 120 |

| 5.3. Meth  | hodology                                                              | 125 |

| 5.3.1.     | Measurement Equipment                                                 | 125 |

| 5.3.2.     | Experimental Procedure                                                | 127 |

| 5.3.3.     | Different Grid Scenarios                                              | 130 |

| 5.3.1.     | Minimisation of CSI Voltage Stress                                    | 131 |

| CHAPTER 6. | Experimental Validation under Ideal Grid Conditions                   | 132 |

| 6.1. Main  | n VSI Operating as Rectifier Connected Directly to a Pure Three Phase | AC  |

| Sinewave S | upply                                                                 | 132 |

| 6.1.1.     | Experimental Setup                                                    | 133 |

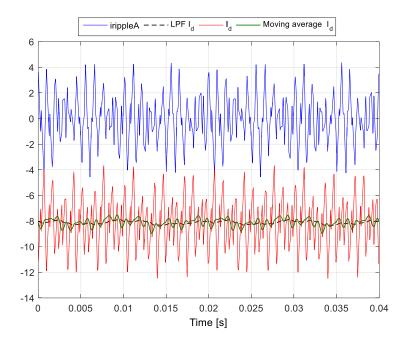

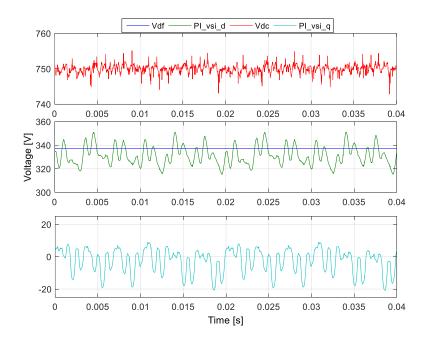

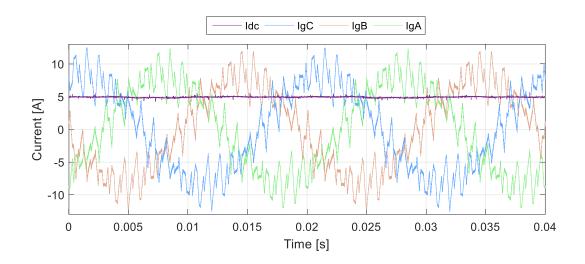

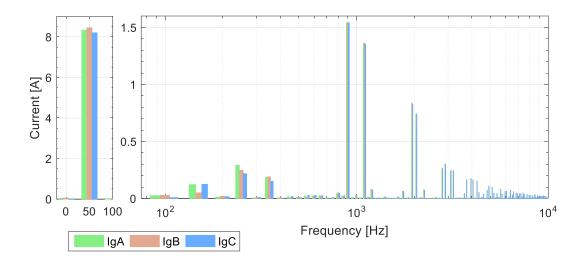

| 6.1.2.     | Transient and Steady State Operation Results for Phase A              | 134 |

| 6.1.3.     | Maximum Voltage Stress and Phase Symmetry                             | 144 |

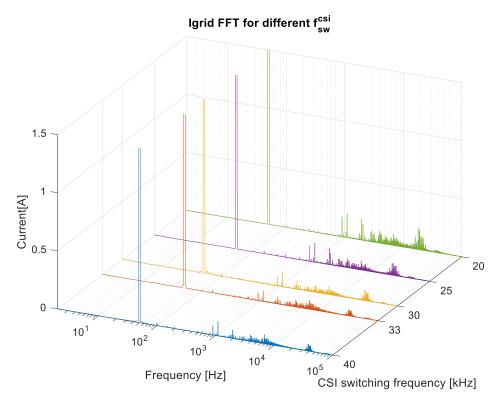

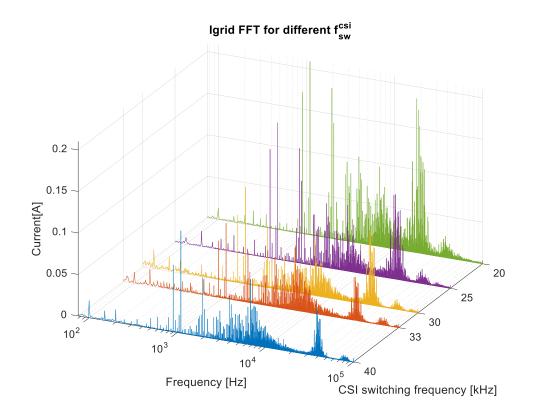

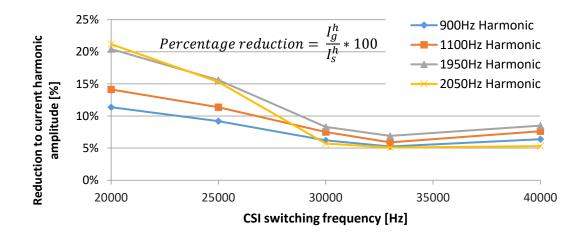

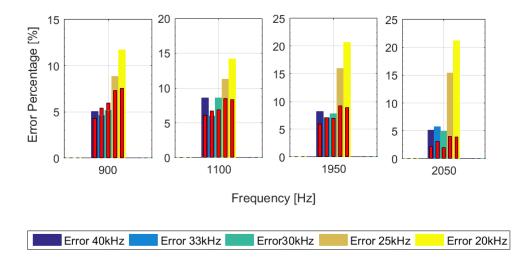

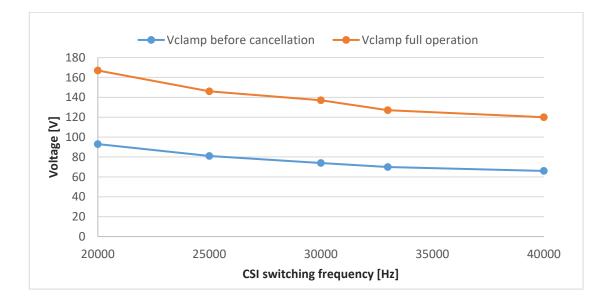

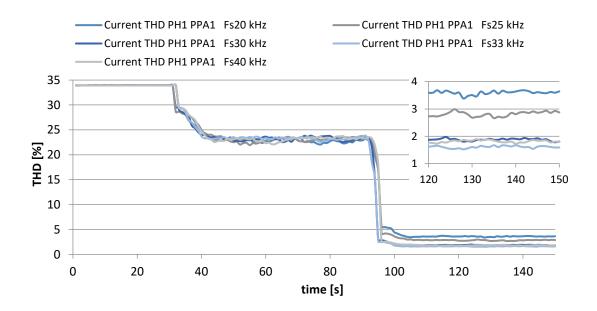

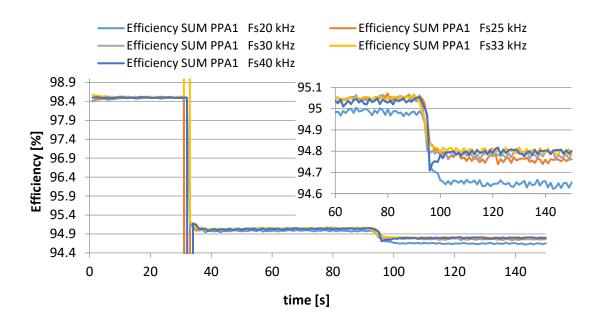

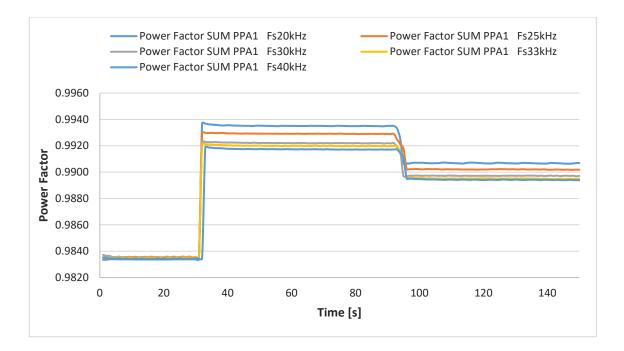

| 6.1.4.     | Performance Evaluation for Different CSI Switching Frequencies        | 148 |

| 6.2. Con-  | clusion                                                               | 159 |

| CHAPTER 7. | Experimental Validation under Real Grid Conditions                    | 160 |

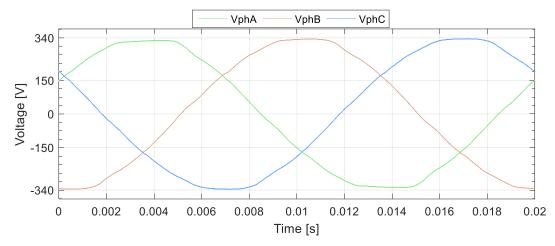

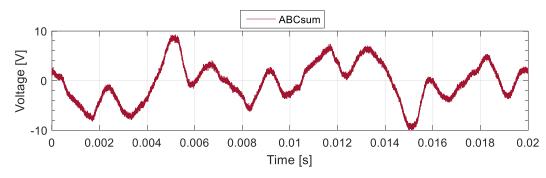

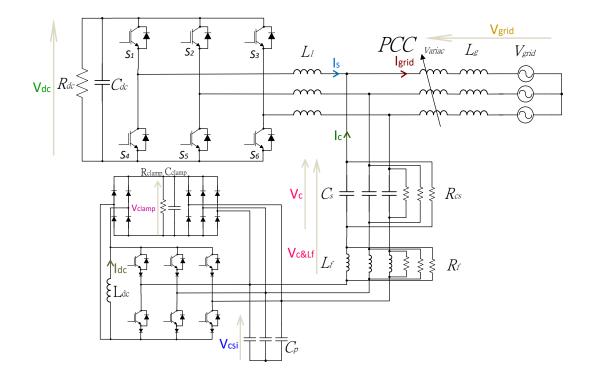

| 7.1. Grid  | Voltage Quality Assessment                                            | 161 |

| 7.1.1.     | Experimental Setup                                                    | 163 |

| 7.1.2.     | Transient and Steady State Operation Results for Phase A             | 165        |

|------------|----------------------------------------------------------------------|------------|

| 7.1.3.     | Maximum Voltage Stress and Lack of Phase Symmetry                    | 175        |

| 7.1.4.     | Simulation of Hybrid Converter Operation Emulating the Real Grid Imb | alance and |

| Harmoni    | ics                                                                  | 179        |

| 7.1.5.     | Analysis of the CSI Voltage Unbalance Mechanism                      |            |

| 7.1.6.     | Solutions for Mitigation of the CSI Voltage Unbalance                | 191        |

| 7.1.7.     | Transient and Steady State Operation Results for Phase A             | 197        |

| 7.1.8.     | Maximum Voltage Stress and Phase Symmetry                            | 206        |

| 7.1.9.     | Conclusion                                                           | 210        |

| 7.2. Grie  | d Connected Rectifier with Additional Higher Order Impedance in the  | AC Filter  |

| 212        |                                                                      |            |

| 7.2.1.     | Experimental Setup                                                   | 212        |

| 7.2.2.     | Transient and Steady State Operation Results for Phase A             | 214        |

| 7.2.3.     | Maximum Voltage Stress and Phase Symmetry                            | 224        |

| 7.2.4.     | Conclusion                                                           | 228        |

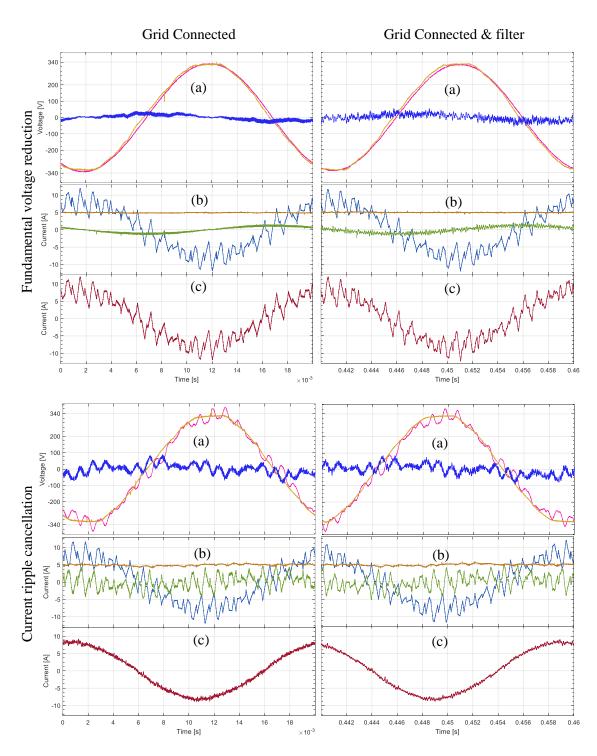

| CHAPTER 8. | . Comparative Performance Evaluation and Discussion                  |            |

| 8.1. Per   | formance Comparison                                                  | 230        |

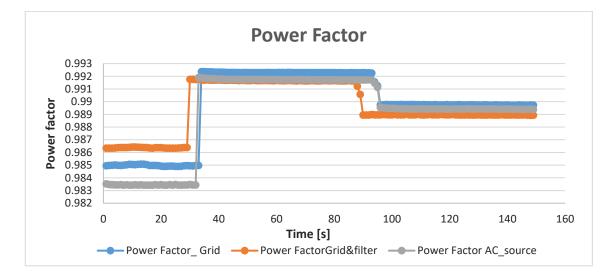

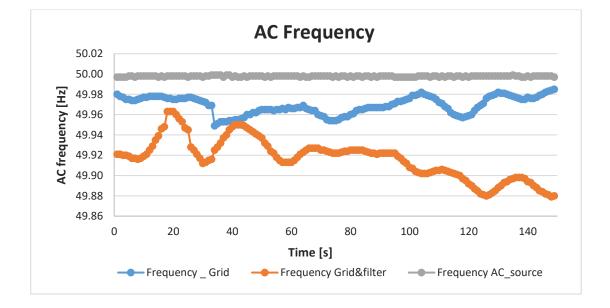

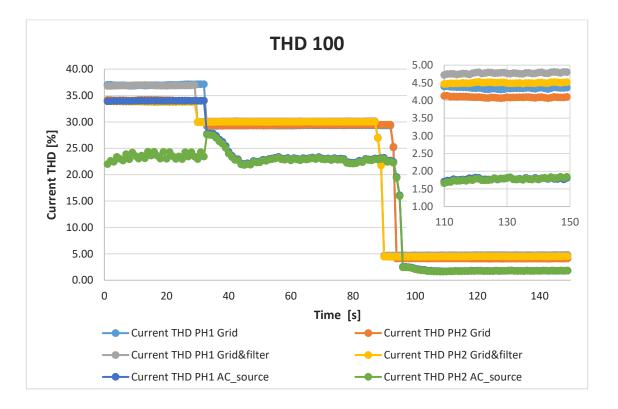

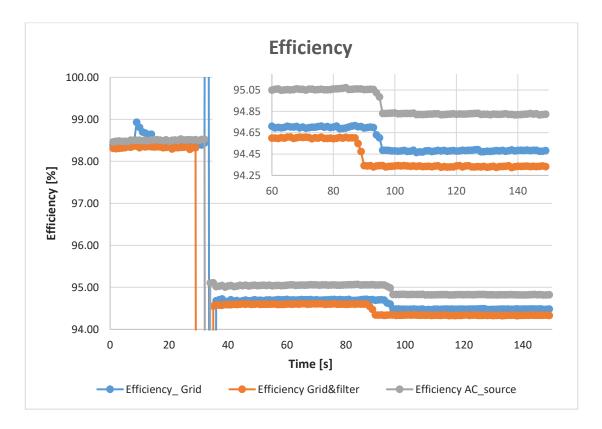

| 8.1.1.     | Power Analyser Results                                               | 230        |

| 8.1.2.     | CSI Harmonic Cancellation Performance                                | 234        |

| 8.1.3.     | Summary                                                              |            |

| 8.2. Dise  | cussion on the System Performance                                    |            |

| 8.3. Sun   | nmary of Findings                                                    |            |

| CHAPTER 9. | Conclusions                                                          | 250        |

| 9.1. Cor    | clusions on the Hybrid Concept25                                 | 0  |

|-------------|------------------------------------------------------------------|----|

| 9.1.1.      | Advantages and Disadvantages of the Hybrid Concept               | 1  |

| 9.2. Nov    | /elty                                                            | 2  |

| 9.3. Are    | as of Future Improvement and Investigation                       | 3  |

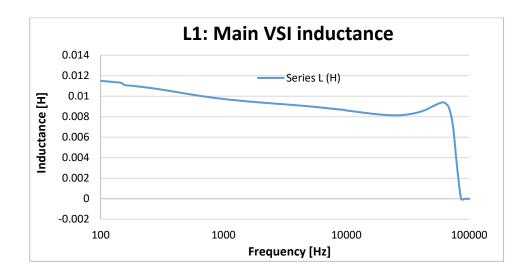

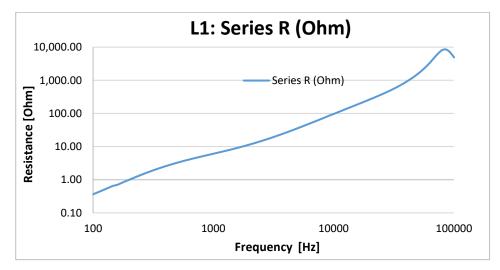

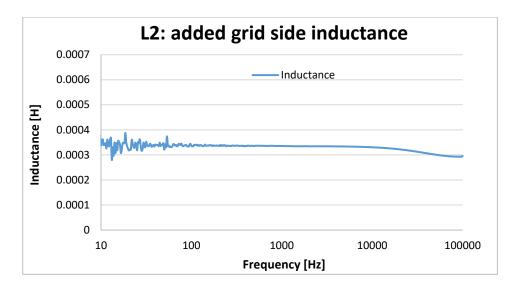

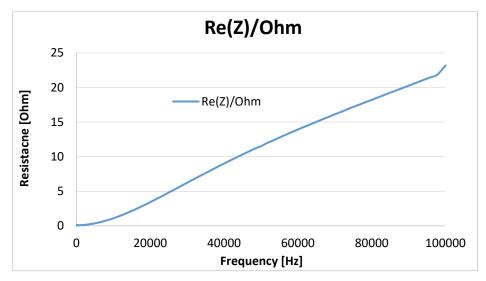

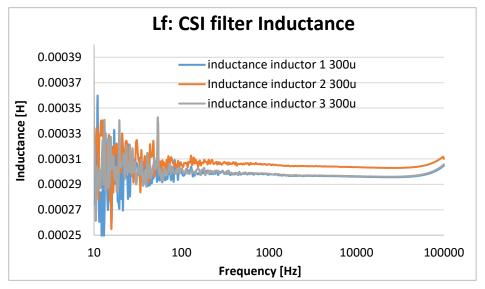

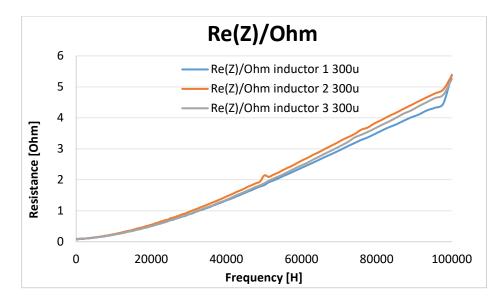

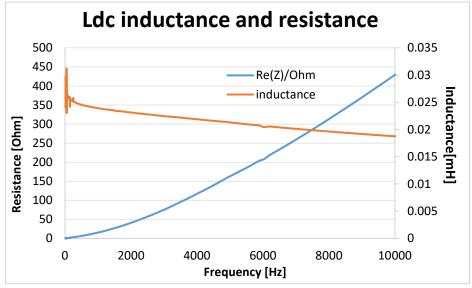

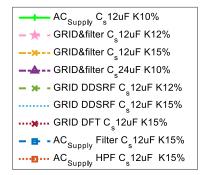

| Appendix A. | Inductor Characterisation Data                                   | i  |

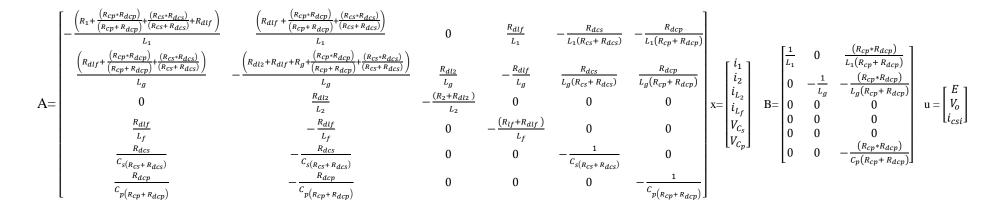

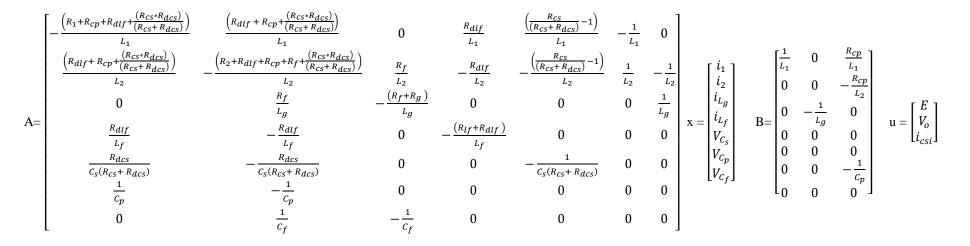

| Appendix B. | State Space Modelsi                                              | iv |

| Appendix C. | Experimental Datai                                               | ix |

| Appendix D. | THD Calculationsx                                                | ii |

| Appendix E. | Additional Experimental Plots xi                                 | iv |

| Appendix F. | Using HPF for current ripple extractionxv                        | vi |

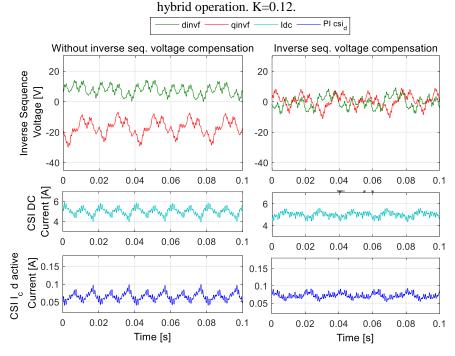

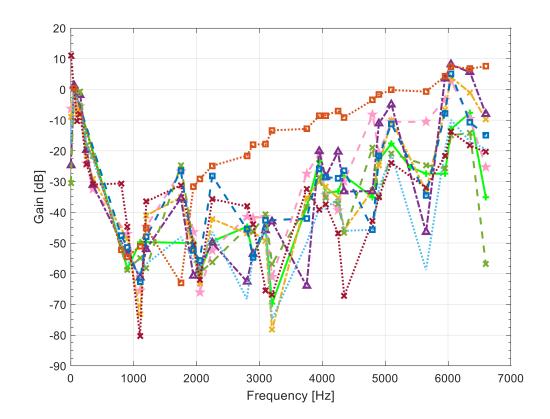

| Appendix G. | Validation of negative sequence voltage compensator operation xv | ii |

| Appendix H. | Resonance excitation Phase A results xvi                         | ii |

| Appendix I. | CSI Attenuation: Further Results xi                              | ix |

| Appendix J. | Oscilloscope Measurement Resolution x                            | X  |

| Appendix K. | Table of Experimental Tests    xx                                | xi |

| Appendix L. | List of Published Papersxx                                       | ii |

# List of Figures

| Fig. 1-1: Generic overview of proposed topology operation, configuration and features                                               | 4   |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

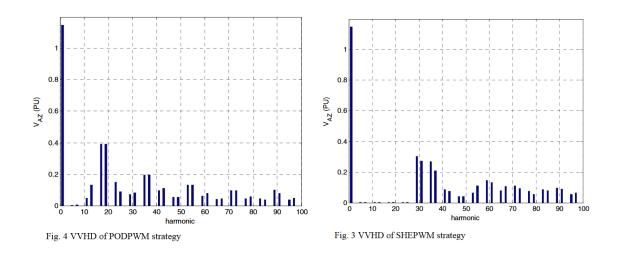

| Fig. 2-1: Theoretical Harmonic spectrum produced by Phase opposition PWM (left) and using SHE-PWM for harmonic cancellation         | m   |

| up to the 29 <sup>th</sup> order as presented in [59]1                                                                              | .6  |

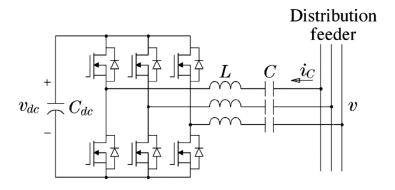

| Fig. 2-2: Hybrid active power filter connected to LC filter as proposed in [80] 1                                                   | .8  |

| Fig. 2-3: Series capacitor connected active filter topology as proposed in [81]1                                                    | .9  |

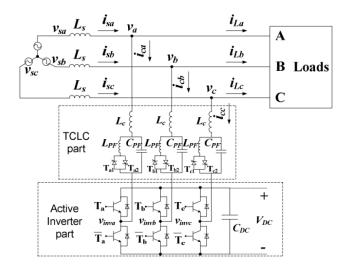

| Fig. 2-4: Thyristor Controlled LC-Coupling Hybrid Active Power Filter (TCLC-HAPF) topology as presented in [90]                     | 20  |

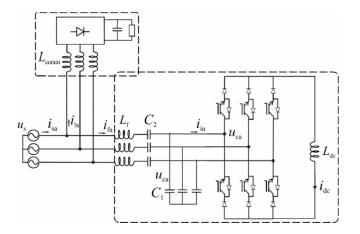

| Fig. 2-5: Series capacitor connected CSI HAPF as proposed in [94]                                                                   | !1  |

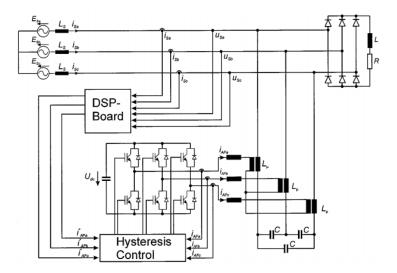

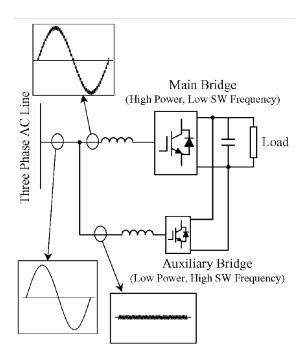

| Fig. 2-6: Hybrid topology using auxiliary converter to provide ripple cancellation for current quality improvement [99] 2           | 2   |

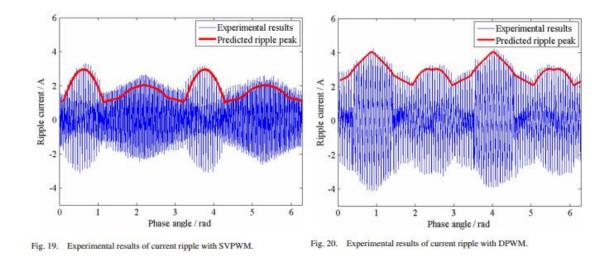

| Fig. 2-7: Experimental and predicted current ripple profile [100]                                                                   | :5  |

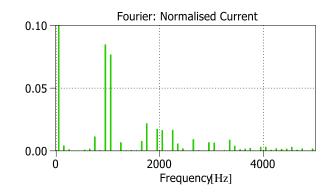

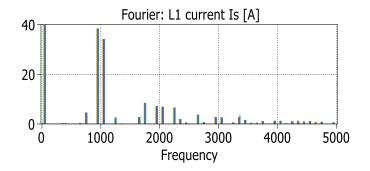

| Fig. 2-8: Example harmonic content of a VSI current for a switching frequency of 1 kHz                                              | :6  |

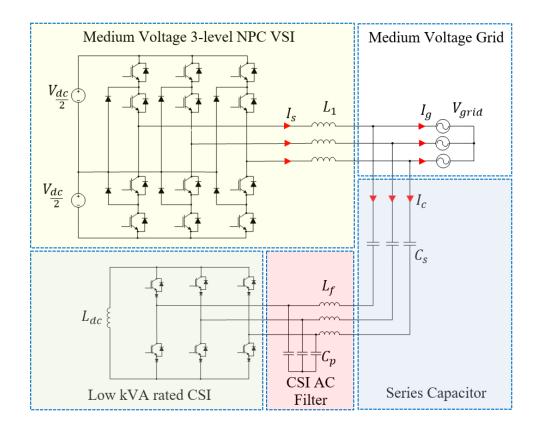

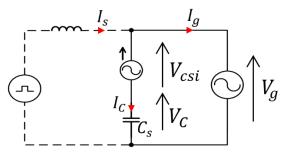

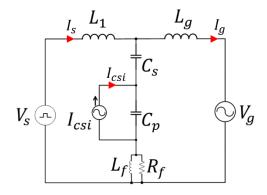

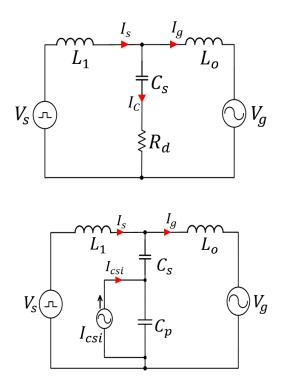

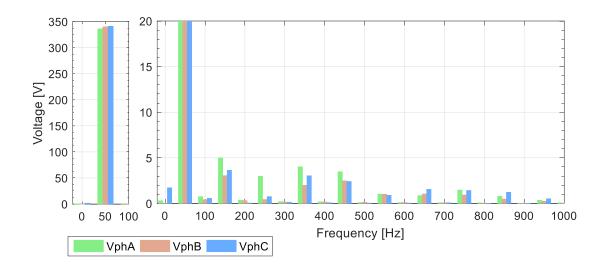

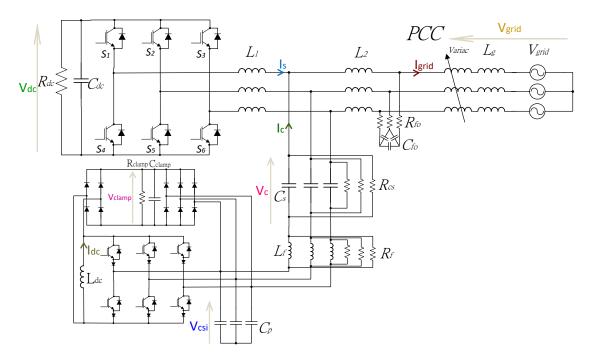

| Fig. 3-1: Hybrid system topology highlighting the main features                                                                     | 13  |

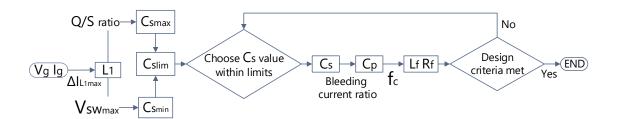

| Fig 3-2 : Flowchart of the design procedure for the passive components of the hybrid converter                                      | \$4 |

| Fig 3-3: Hybrid Circuit Single Phase Equivalent at the Fundamental frequency                                                        | 5   |

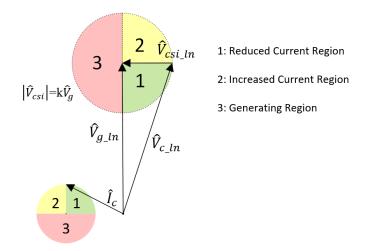

| Fig. 3-4: Fundamental frequency phasor diagram showing possible operating regions                                                   | 6   |

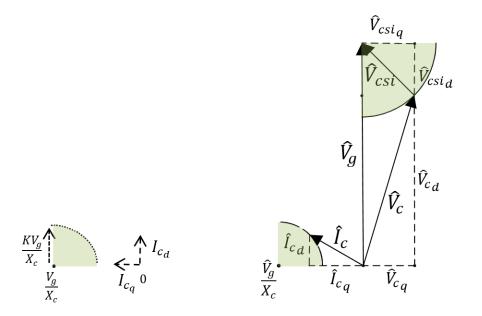

| Fig. 3-5: Fundamental frequency phasor diagram showing synchronous reference frame dq components (left) and zoom in on current      | nt  |

| circle showing the radius and placement                                                                                             | ;7  |

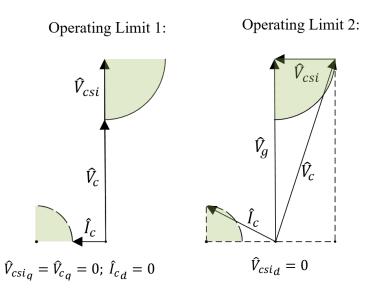

| Fig. 3-6: Phasor diagram showing operating limits for maximum and minimum current                                                   | 8   |

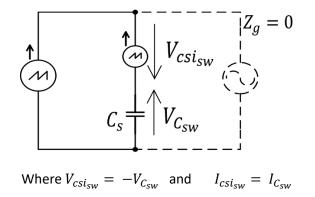

| Fig 3-7: Hybrid Circuit Single Phase Equivalent at the VSI Switching Frequency                                                      | ;9  |

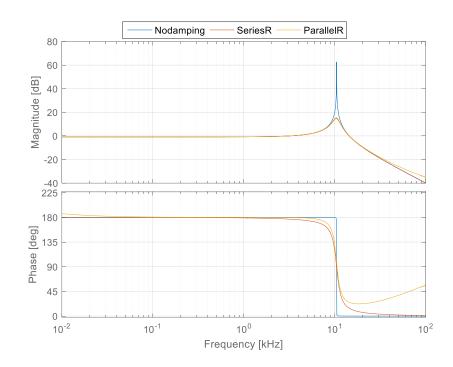

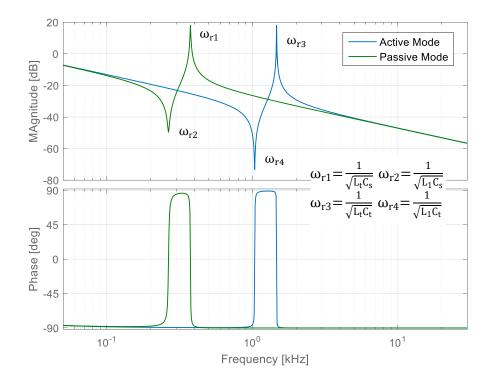

| Fig 3-8: Bode diagram showing output filter response (Icsi/Ic) with different damping options                                       | 2   |

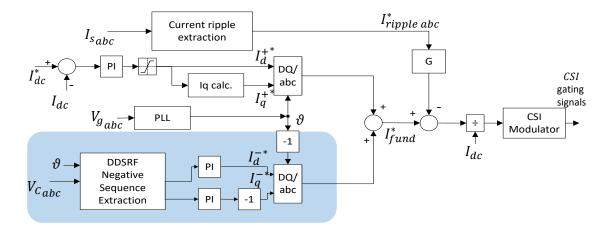

| Fig. 3-9: Control scheme of the hybrid assembly 4                                                                                   | 2   |

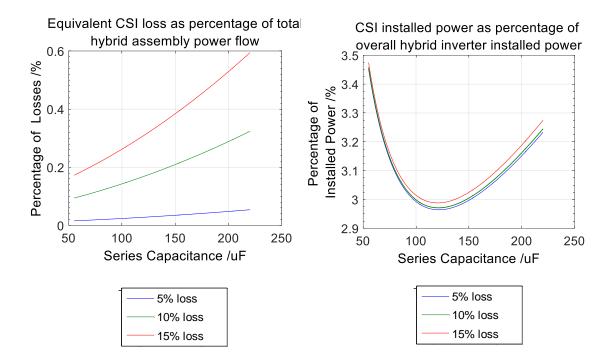

| Fig. 3-10: a) CSI Losses as percentage of hybrid system loss and b) Added Installed Power versus size of Series Capacitance         | at  |

| different DC-link resistance equivalent to 5-10-15% loss of processed apparent CSI power                                            | 60  |

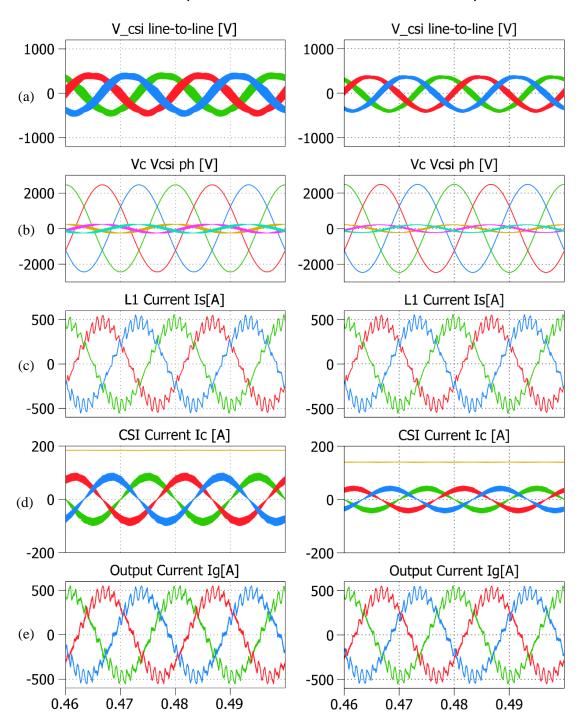

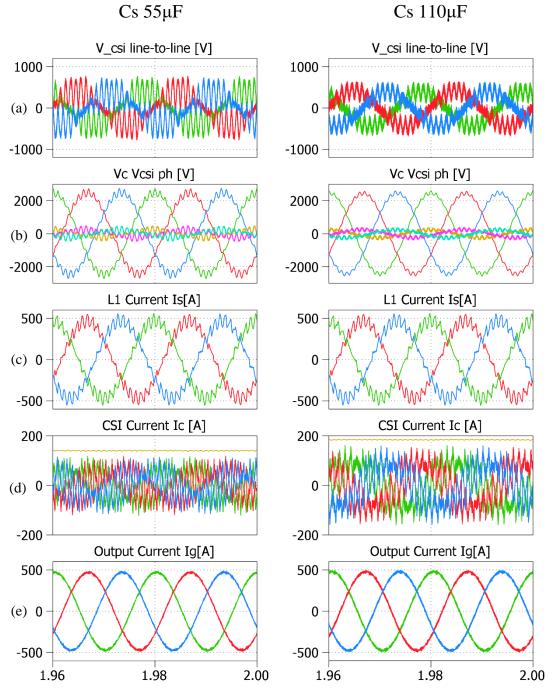

| Fig. 3-11: Simulation waveforms during steady state operation before ripple cancellation considering the two series capacitor value | es  |

| a) Line-To-Line CSI Voltages; b) Line-To-Neutral CSI And Series Capacitor Voltages; c) Input (Main Converter) Current through       | ţh  |

| the Interface Inductor (L1). d) CSI Current; e) Cumulated Output Current;                                                           | 64  |

| Fig. 3-12: Simulation waveforms during steady state operation considering the two series capacitor values a) Line-To-Line CS        | SI  |

| Voltages; b) Line-To-Neutral CSI And Series Capacitor Voltages; c) Input (Main Converter) Current through the Interface Inductor    | or  |

| (L1). d) CSI Current; e) Cumulated Output Current;                                                                                  | 5   |

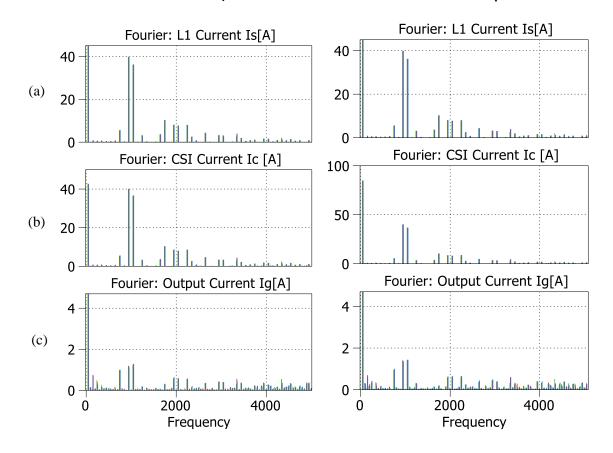

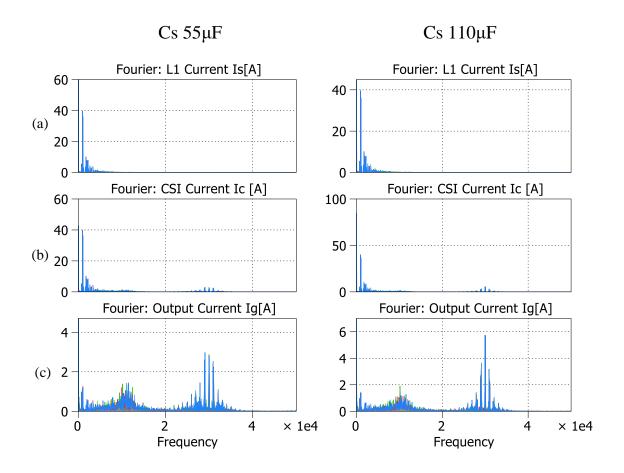

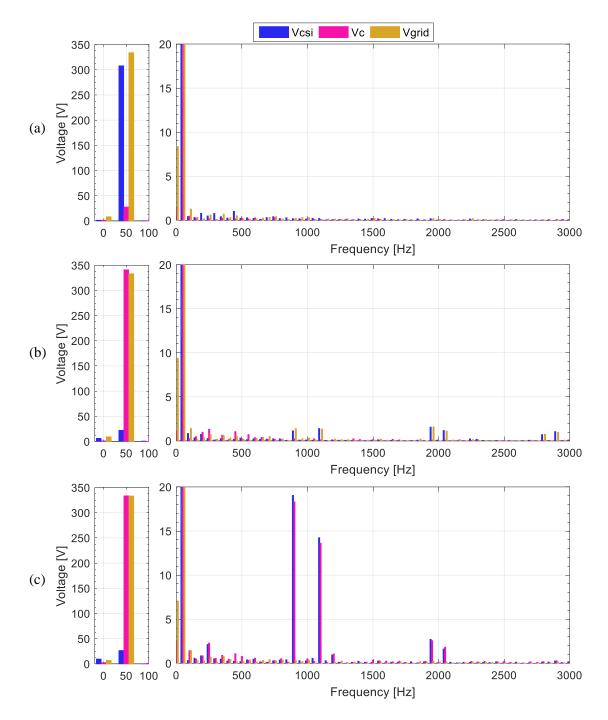

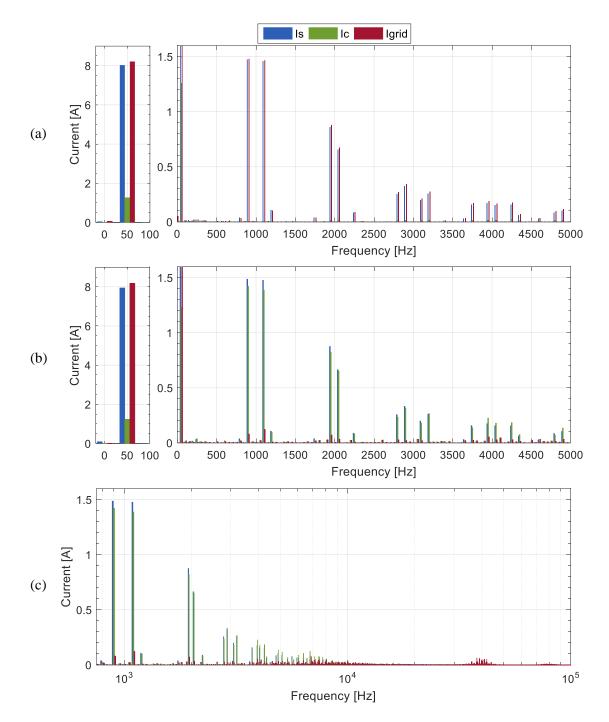

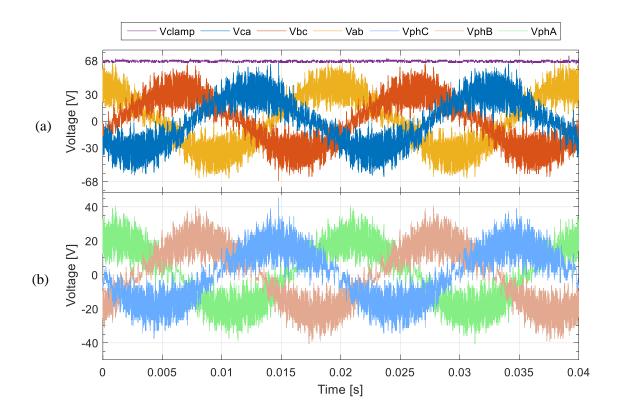

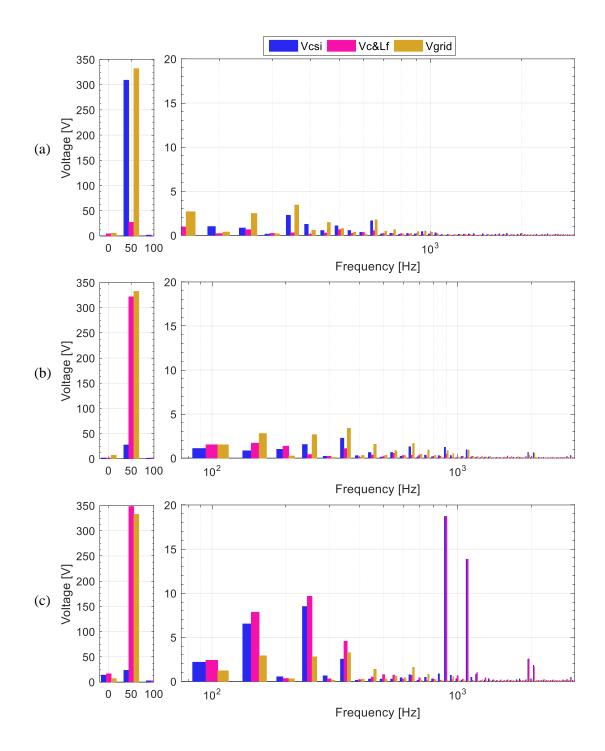

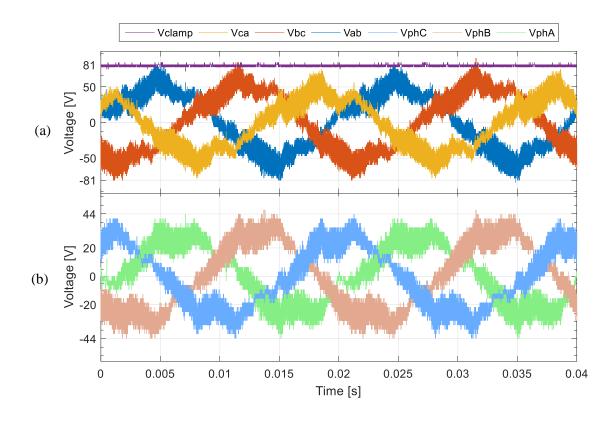

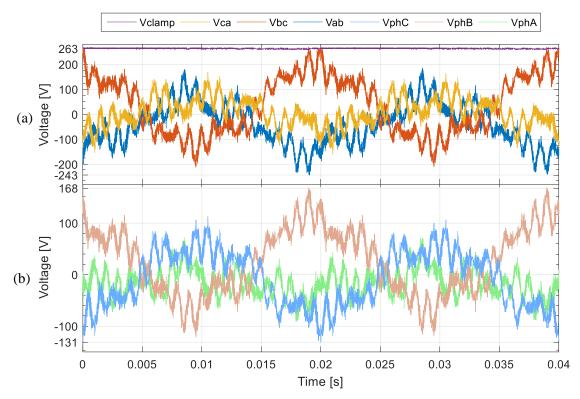

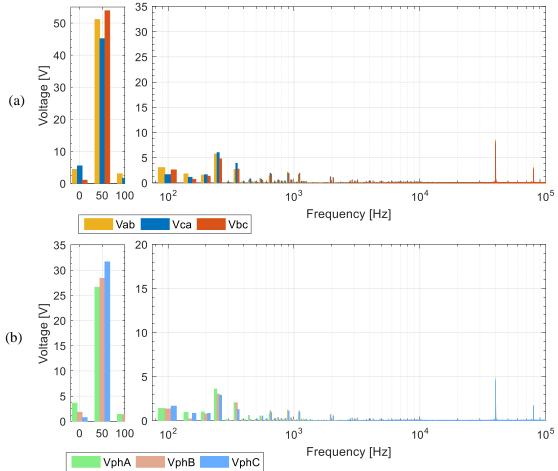

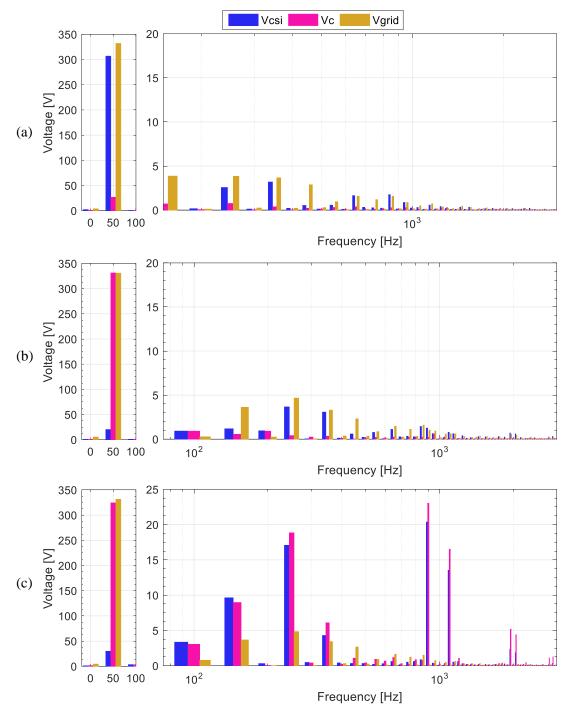

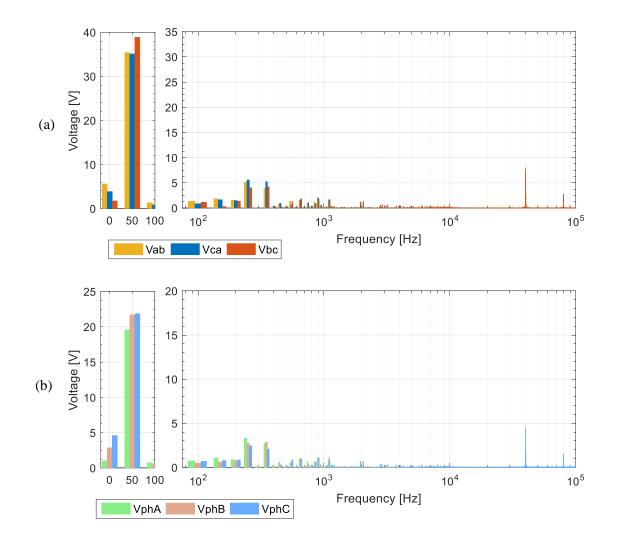

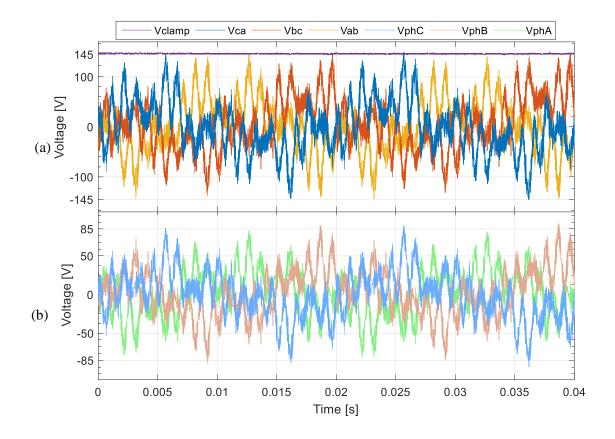

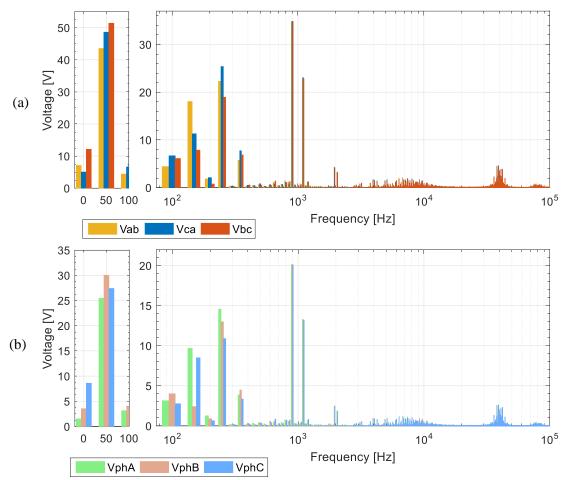

| Fig. 3-13a-c: Current harmonic content up to 5 kHz for two series capacitor values in: a) VSI Current (the fundamental current      | is  |

| clamped); b) the CSI Current and c) the zoomed in resulting cumulated grid current (fundamental component clamped)                  | 6   |

| Fig. 3-14a-c: Current harmonic content up to 50 kHz: a) VSI Current (fundamental current clamped); b) the CSI Current and c) the    | ıe  |

| zoomed in resulting cumulated grid current (fundamental component clamped)                                                          | 8   |

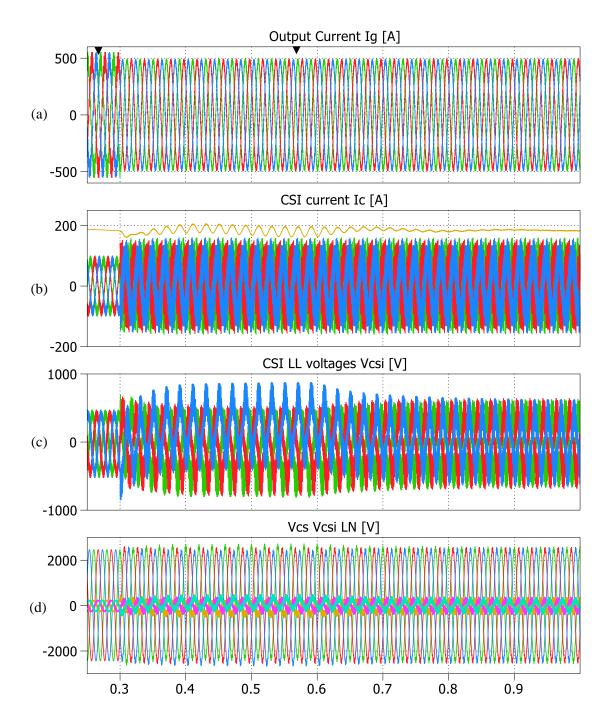

| Fig. 3-15: DC voltage compensator validation showing activation of current ripple cancellation at t=0.3s including DC current       | nt  |

| disturbances and activation of DC voltage compensator at t=0.6s. a) Grid Current; b) CSI Current; c) Line-To-Line CSI Voltages; d   | d)  |

| Line-To-Neutral CSI And Series Capacitor Voltages                                                                                   | 51  |

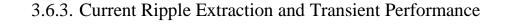

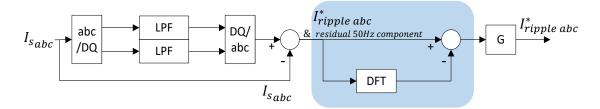

| Fig. 3-16: a) Step change in VSI current component; and b) the effect on current ripple extraction                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

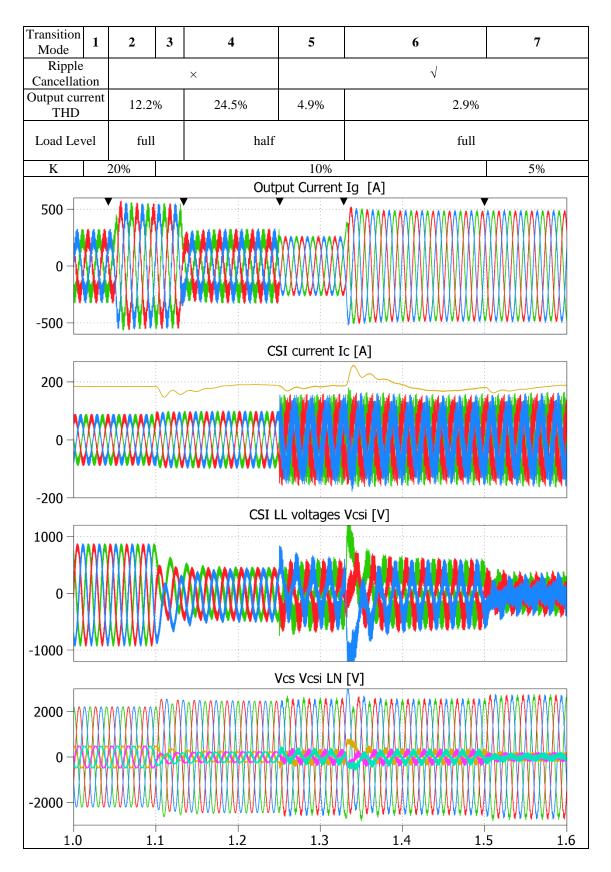

| Fig. 3-17: Voltage and Current Transient Behaviour under Different Operating Modes using Cs 110uF                                                 |

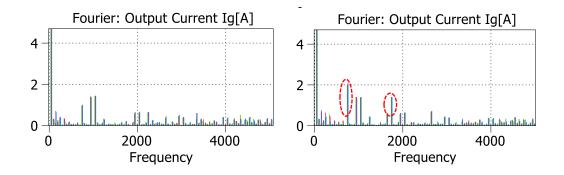

| Fig. 3-18: Harmonic content of filtered grid current for moving average filter windows of 2ms (left) and 1ms used for improving                   |

| transient response (right)                                                                                                                        |

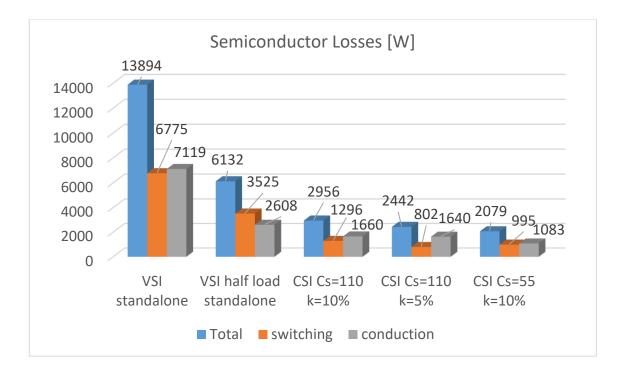

| Fig. 3-19: Estimated semiconductor losses for VSI at full and half load operation and CSI at different series capacitance and voltage             |

| reduction operating points                                                                                                                        |

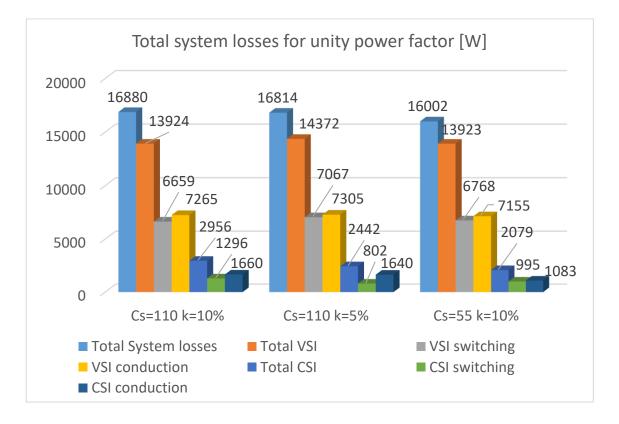

| Fig. 3-20: Estimated total semiconductor losses for combined VSI and CSI operation where the VSI is compensating for the series                   |

| capacitor reactive power to achieve unity power factor                                                                                            |

| Fig. 4-1. Single Phase equivalent circuit for Hybrid topology with non-zero grid impedance                                                        |

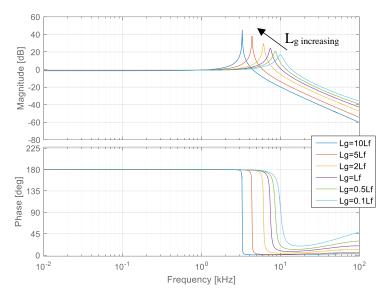

| Fig. 4-2: Bode plot showing the CSI I <sub>csi</sub> to grid current I <sub>g</sub> response for an increasing grid inductance                    |

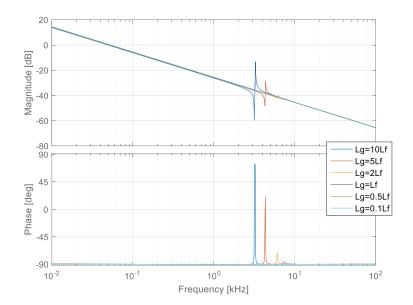

| Fig. 4-3: Bode plot showing the VSI converter voltage to VSI current Is response for an increasing grid inductance                                |

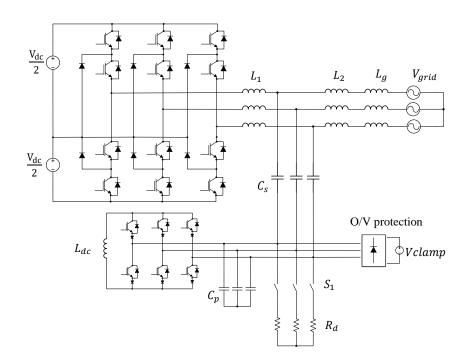

| Fig. 4-4: Hybrid converter topology with LCL filter interconnection                                                                               |

| Fig. 4-5: Single Phase equivalent circuits for a) Passive; b) Active Filtering                                                                    |

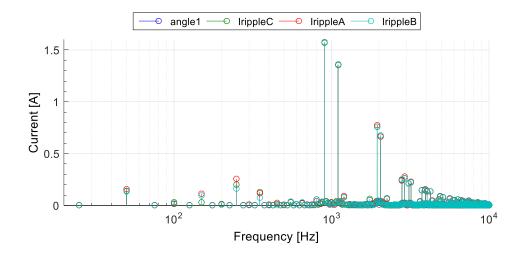

| Fig. 4-6: Main VSI inductor (L1) current harmonics                                                                                                |

| Fig. 4-7: Converter Voltage to Converter Current Bode plot for active and passive filtering mode                                                  |

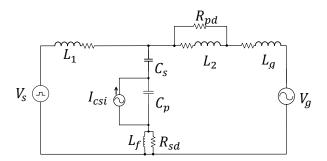

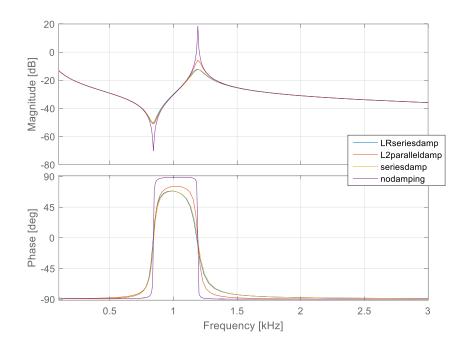

| Fig. 4-8: Single Phase Equivalent circuit showing passive damping options                                                                         |

| Fig. 4-9: Frequency response under different passive damping scenarios                                                                            |

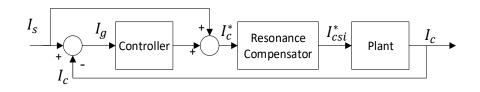

| Fig. 4-10: Active damping implementation for Ripple Cancellation                                                                                  |

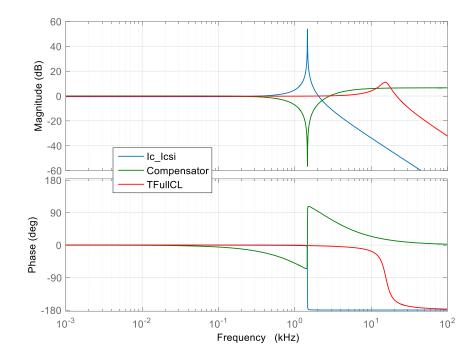

| Fig. 4-11: Bode plots of the following transfer functions: $I_{csi}$ to $I_c$ , the resonance compensator and the overall closed loop active      |

| damped system                                                                                                                                     |

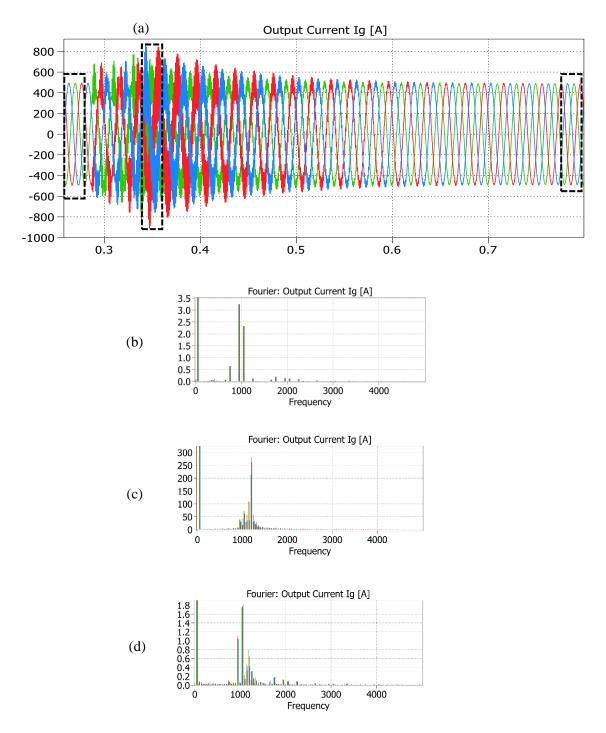

| Fig. 4-12a-d: Transient operation showing activation of CSI at t1=0.28s followed by LC circuit resonance build-up and activation of               |

| the resonance compensator at t2=0.36s followed by resonance being actively damped (t>0.7s). b)-c)-d) FFT of the MV grid currents                  |

| when b) CSI was off and switching ripple is passively damped by the LCL filter; c) just before active damping activation (t=0.34-                 |

| 0.36); d) at end of simulation when resonance levels are not visible                                                                              |

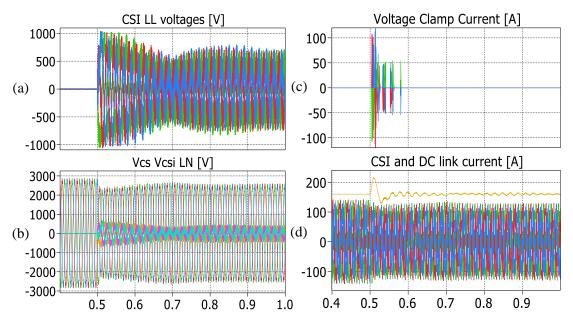

| Fig. 4-13a-d: Transient between passive and active filtering mode at t1 showing a)CSI l-l voltage b)Series capacitor and CSI phase                |

| voltages c)Voltage clamp current and d) Series capacitor current along with CSI DC link current                                                   |

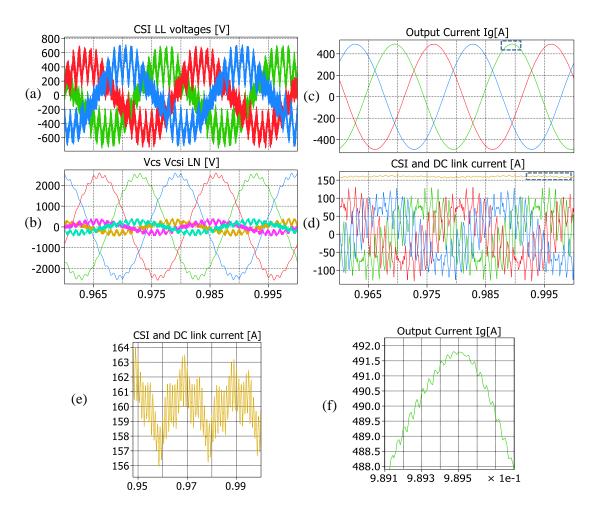

| Fig. 4-14a-f: Zoom in on waveforms shown in Fig. 4-13 showing steady state conditions during active filtering mode showing a)CSI                  |

| 1-1 voltage b)Series capacitor and CSI phase voltages c)Output current d) Series capacitor current e) further zoom-in on DC link current          |

| f)zoom-in on phase A grid current peak                                                                                                            |

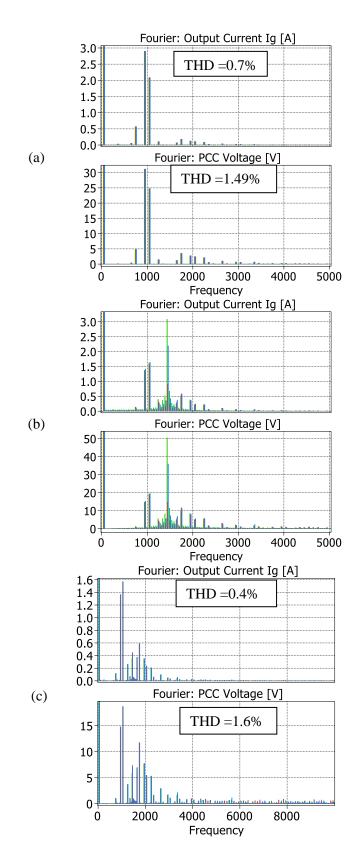

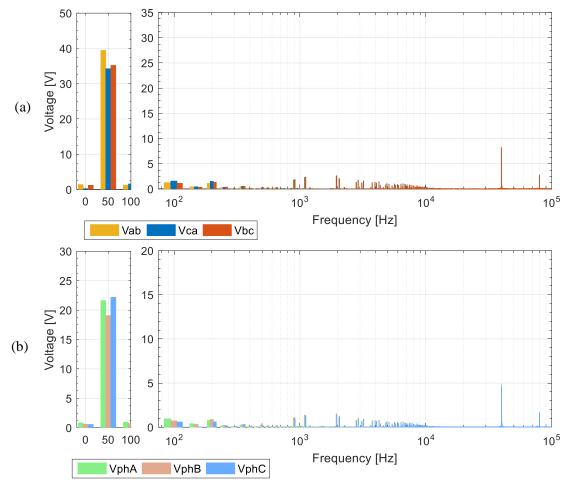

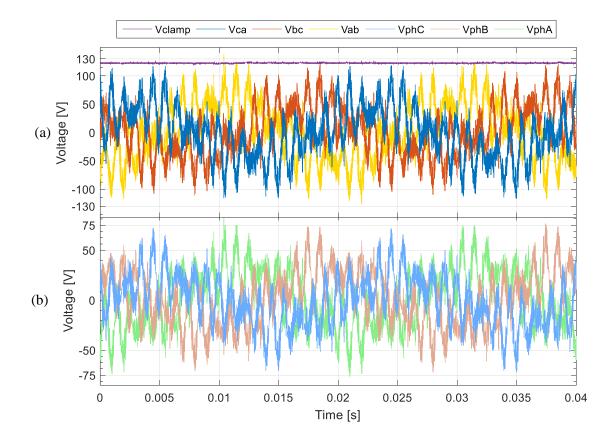

| Fig. 4-15a-c: Output current and PCC voltage harmonic content a) during passive filtering mode b)during active filtering transient                |

| showing small resonance excitation and finally c) showing steady state performance during active filtering                                        |

| Fig. 4-16a-b: Steady state output current and PCC voltage a) during passive filtering mode and b) during active filtering                         |

| Fig. 4-17a-b: Single Phase Equivalent Circuit with output RC filter during: a) passive filtering; and b) during active filtering 93               |

| Fig. 4-18a-b: Bode plot showing Gain Vs frequency for $I_g/V_s$ (VSI behaviour) as well as $I_g/I_{csi}$ (CSI behaviour) with and without RC      |

| filter                                                                                                                                            |

| Fig. 4-19a-c: Steady state output current and PCC voltage during active filtering a)without voltage filtering b)Using $C_{\rm fo}/R_{\rm fo}$ and |

| $L_2$ =2.8mH, $L_g$ =0.8mH and using $C_{fo}/R_{fo}$ and L2=2.8mH, $L_g$ =0.4mH (50% grid impedance variation). Corresponding FFT shown on        |

| the right column                                                                                                                                  |

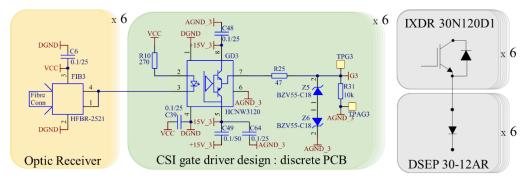

| Fig. 5-1: Overview of gate driver configuration and CSI switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 103 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

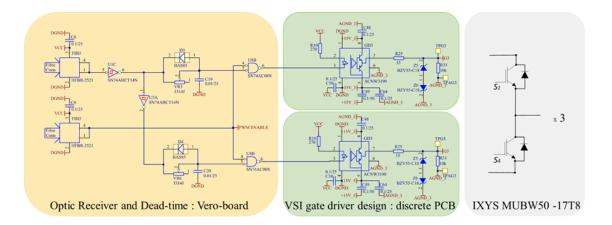

| Fig. 5-2: Implementation of the optical receiver, hardware dead-time generator and the gate driver for a full leg single phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

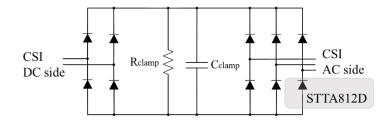

| Fig. 5-3: Schematic of the voltage clamp circuit used for CSI protection and voltage monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

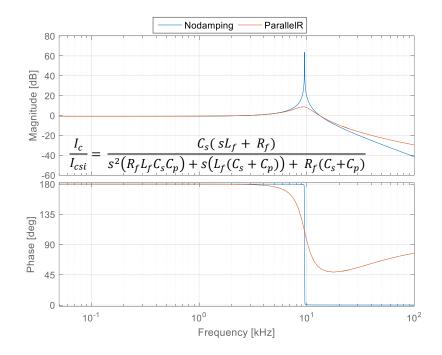

| Fig. 5-4: Calculated CSI AC filter open loop response for the component values used in the experimental prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

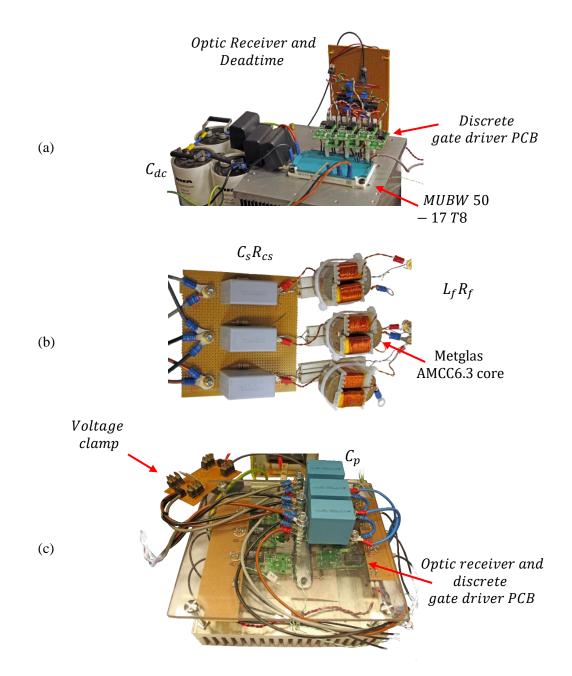

| Fig. 5-5: Pictures showing the main stages of the experimental rig: a) VSI and DC capacitance; b) Series capacitor and filter induc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ctors |

| and c) CSI with parallel capacitors and voltage clamp circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 110 |

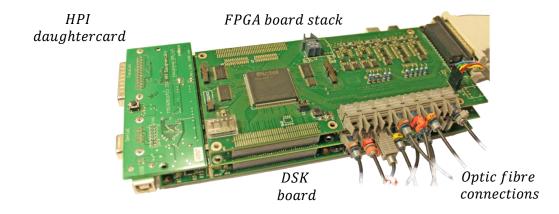

| Fig. 5-6. Picture of Control platform utilising two FPGA boards and HPI daughtercard mounted on the DSK board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 111 |

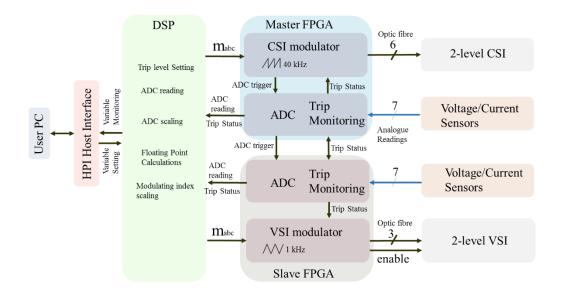

| Fig. 5-7. Control platform system overview showing basic functionality associated with each element/board of the control platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | form  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 112 |

| Fig. 5-8. Carrier Based three phase CSI modulator implemented in the FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 113 |

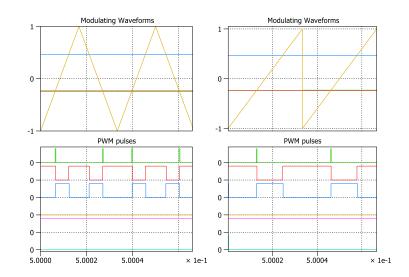

| Fig. 5-9. Pulse generation for two carrier wave periods shown for triangular carrier and sawtooth carrier waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 114 |

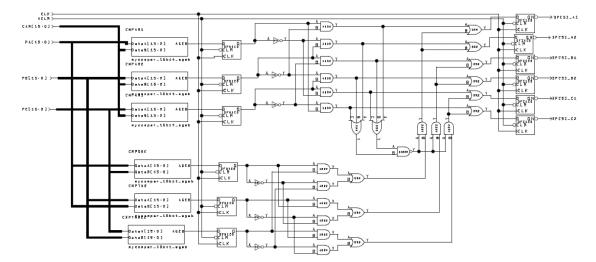

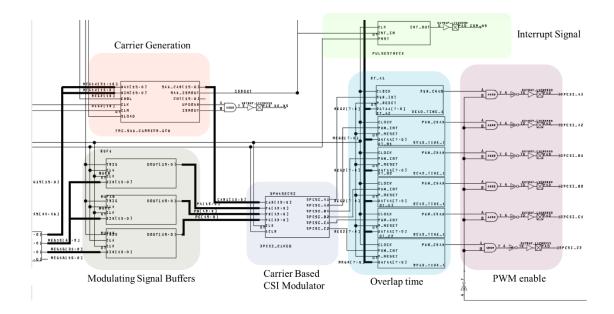

| Fig. 5-10: CSI modulator, carrier and overlap block arrangement as implemented in the Master FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 115 |

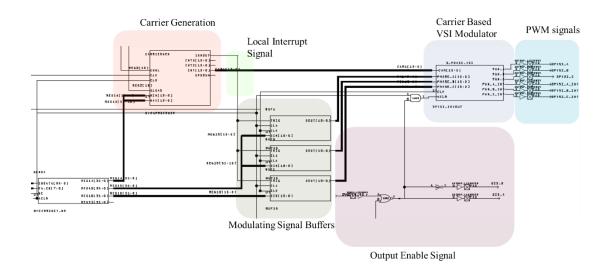

| Fig. 5-11: VSI modulator, carrier and buffer arrangement as implemented in the Slave FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 116 |

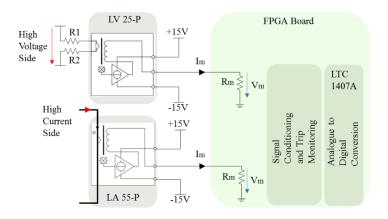

| Fig. 5-12: Overview of data acquisition showing the connection of sensors to the FPGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 117 |

| Fig. 5-13: Picture of current and voltage sensing boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 119 |

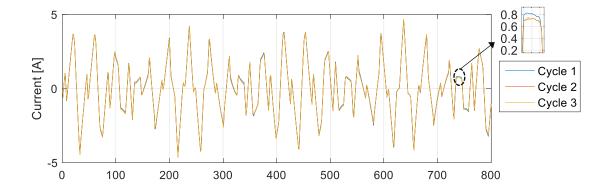

| Fig. 5-14: Extracted VSI current ripple superimposed for three consecutive fundamental cycles captured via the control platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | n 121 |

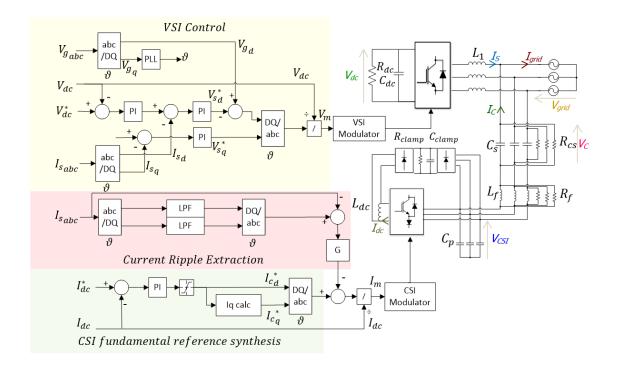

| Fig. 5-15: Equivalent control system diagram and circuit interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 122 |

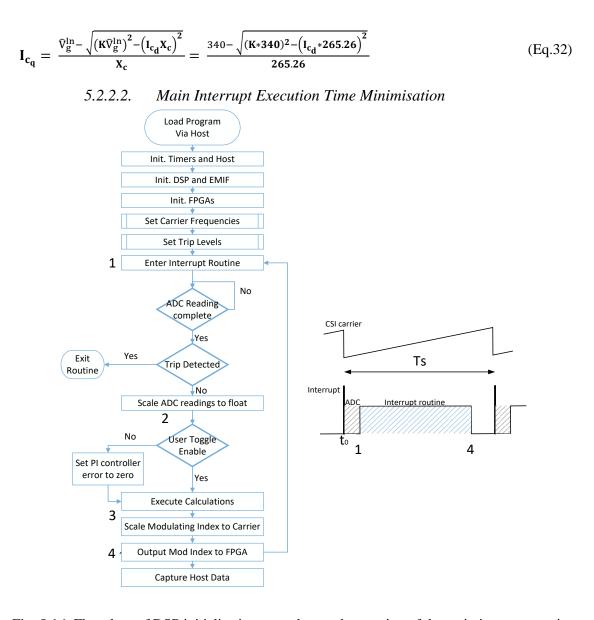

| Fig. 5-16: Flowchart of DSP initialisation procedure and execution of the main interrupt routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 123 |

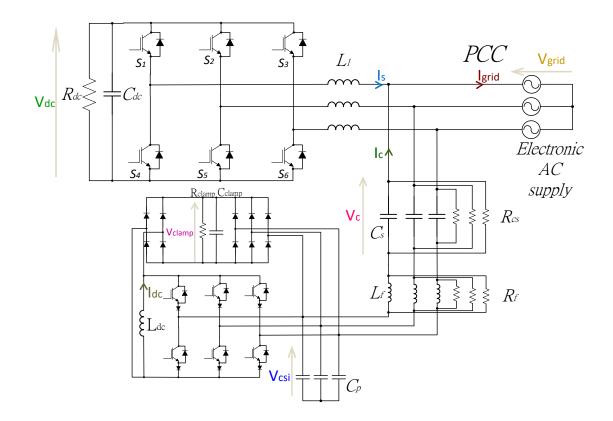

| Fig 6-1: The circuit topology of the experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 132 |

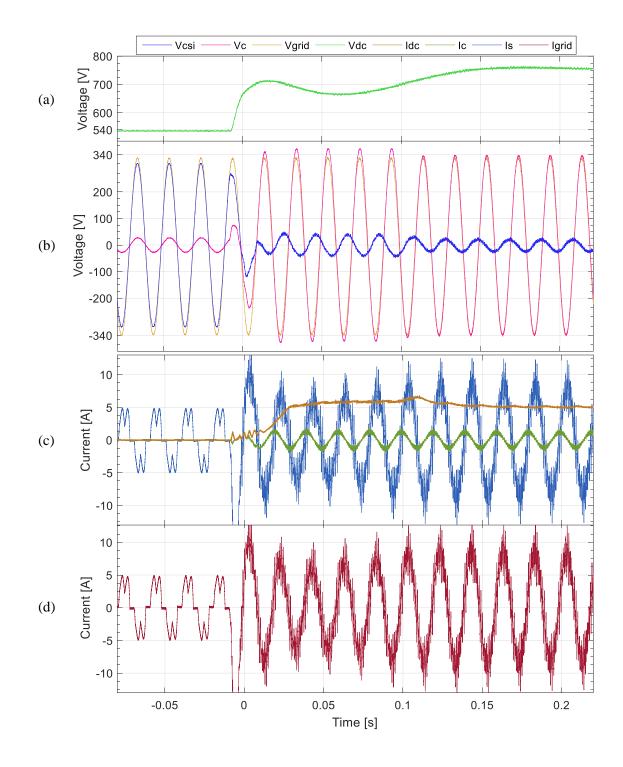

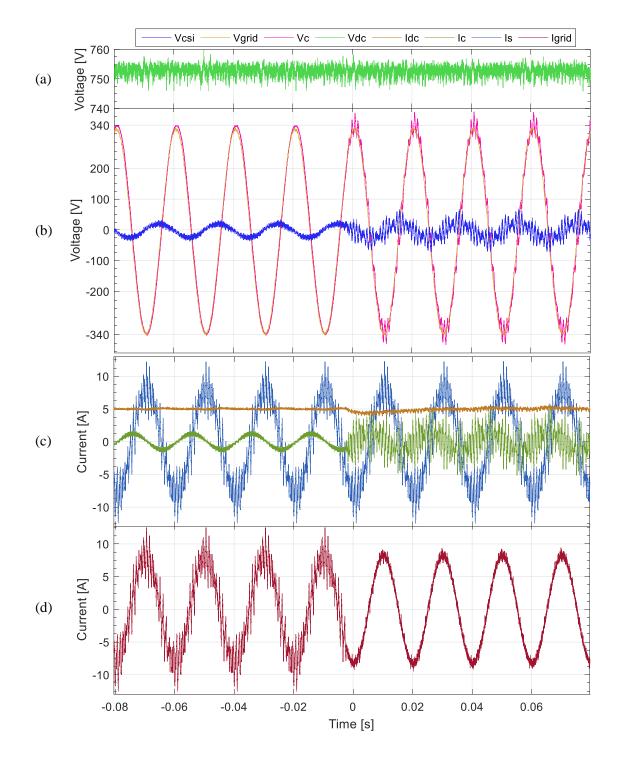

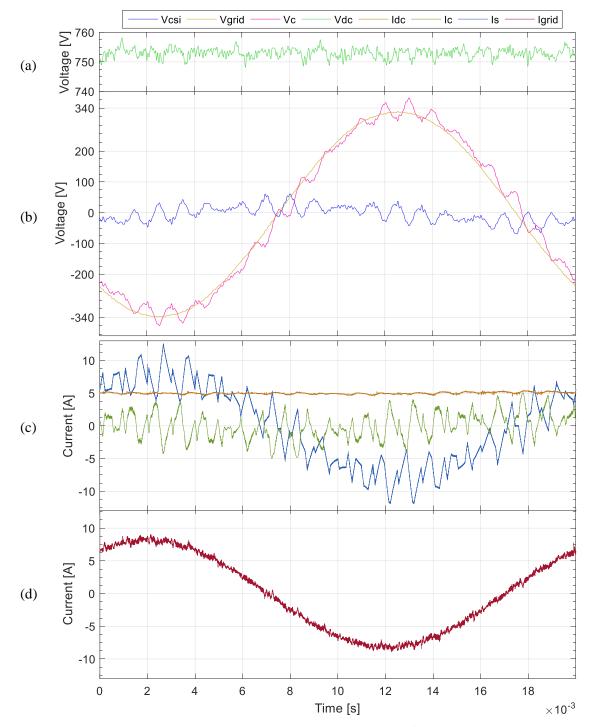

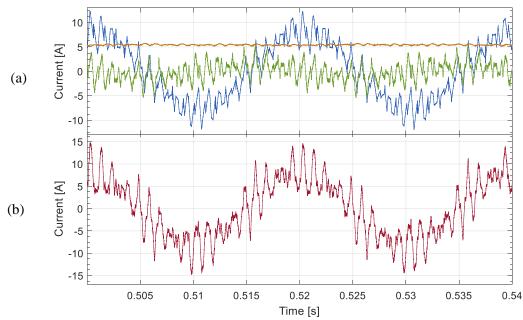

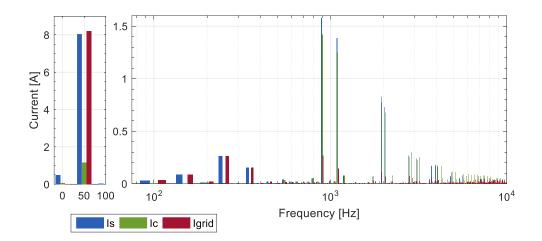

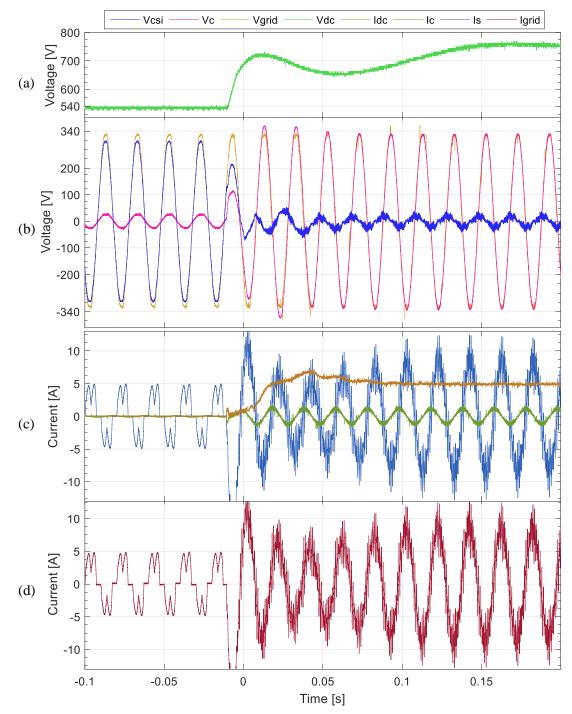

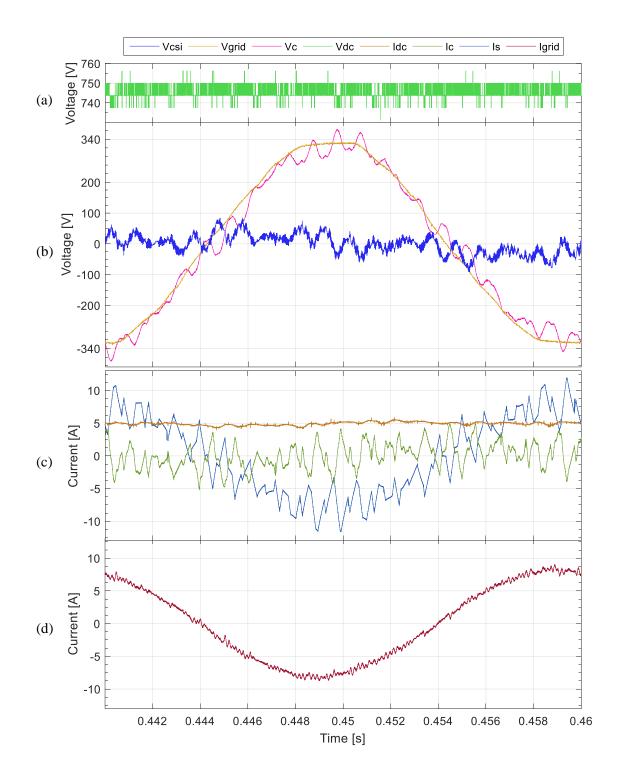

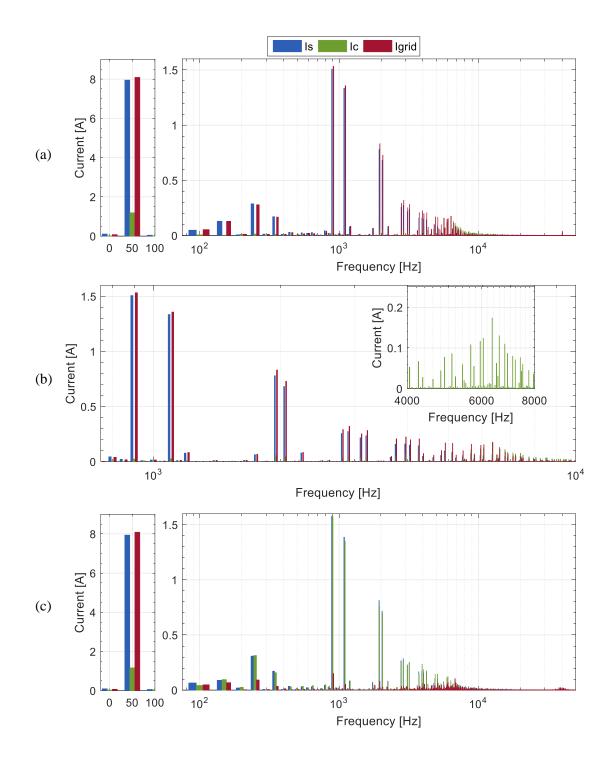

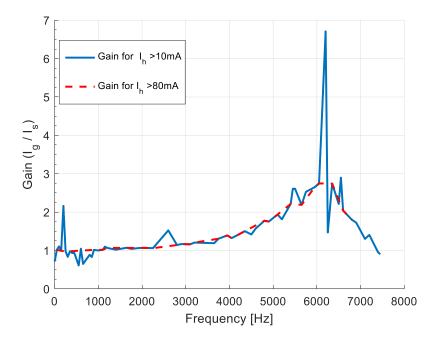

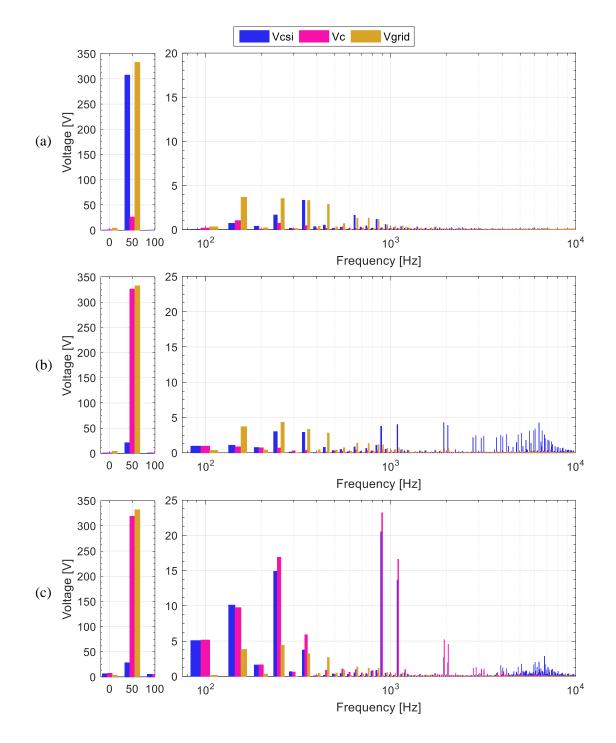

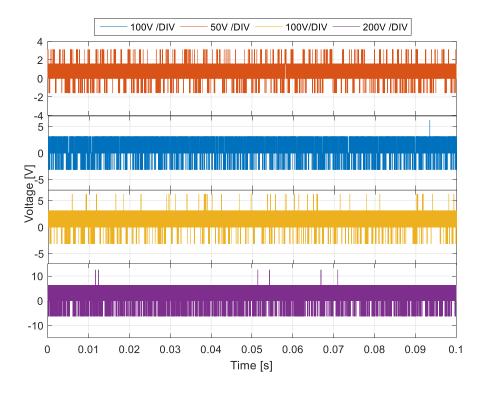

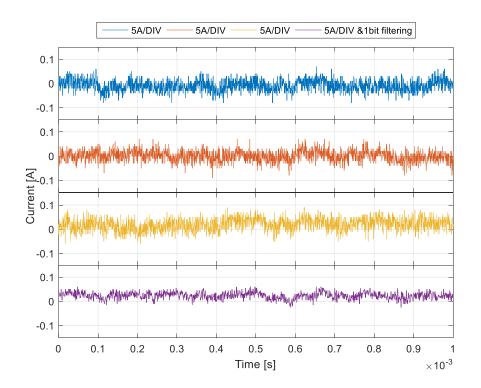

| Fig 6-2: Experimental results showing PWM activation for VSI and CSI for K=0.1 (sans ripple cancellation) for Phase A: a) VSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DC-   |

| link voltage $(V_{dc})$ ; b) Series capacitor $(V_c)$ , CSI $(V_{csi})$ and grid $(V_{grid})$ phase voltages; c) CSI DC-link current $(I_{dc})$ , Main VSI current | rrent |

| $(I_s)$ and series capacitor current $(I_c)$ ; and d) combined grid side current $(I_{grid})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 135 |

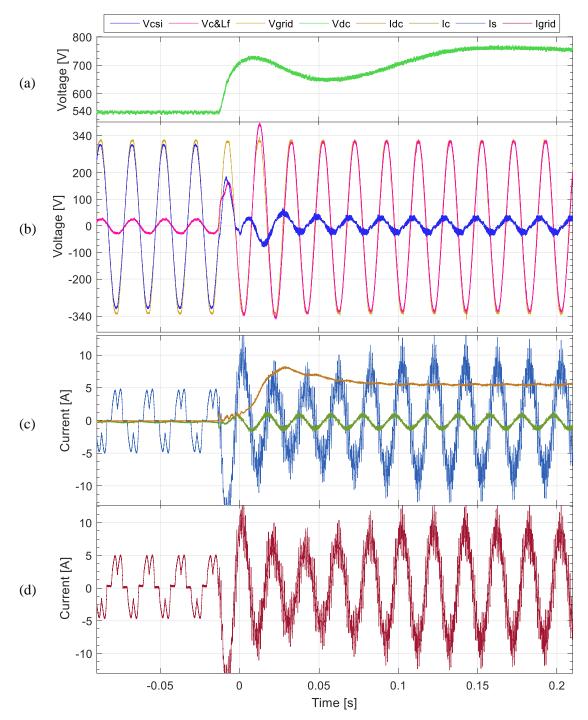

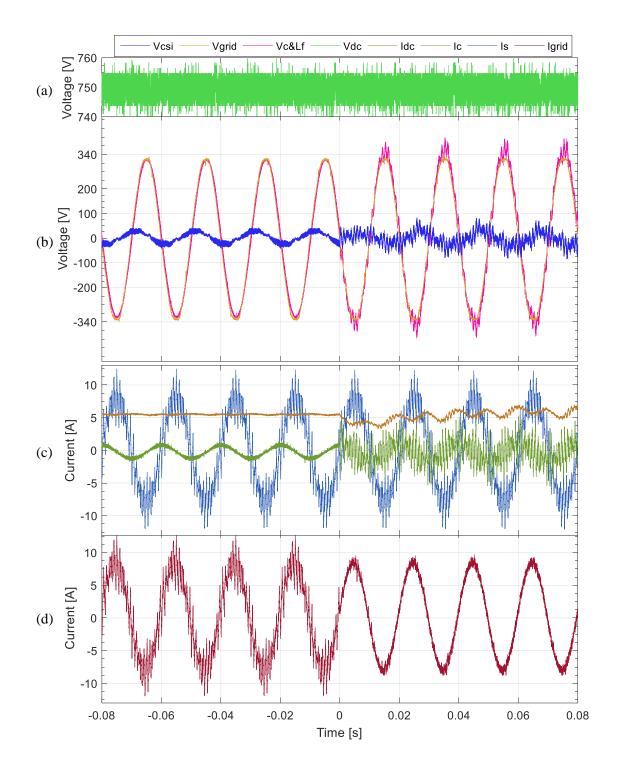

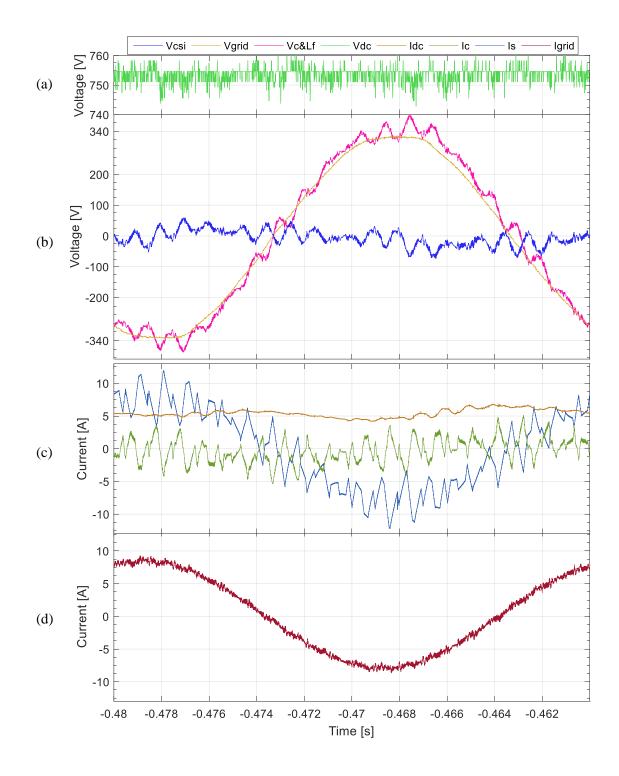

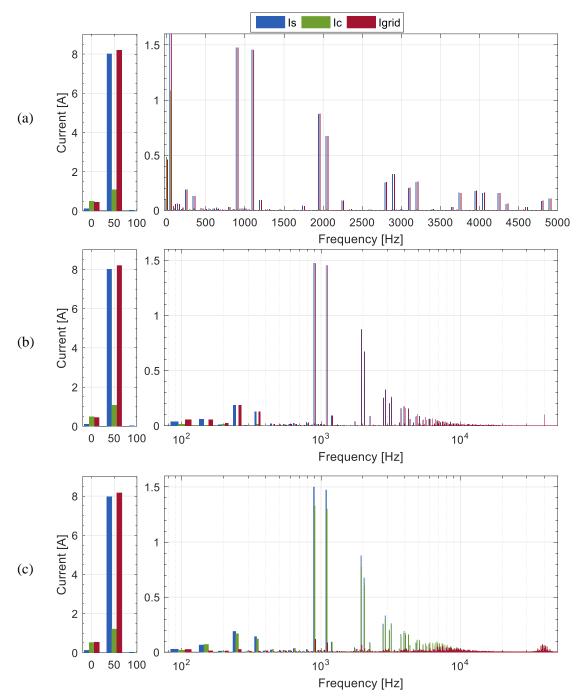

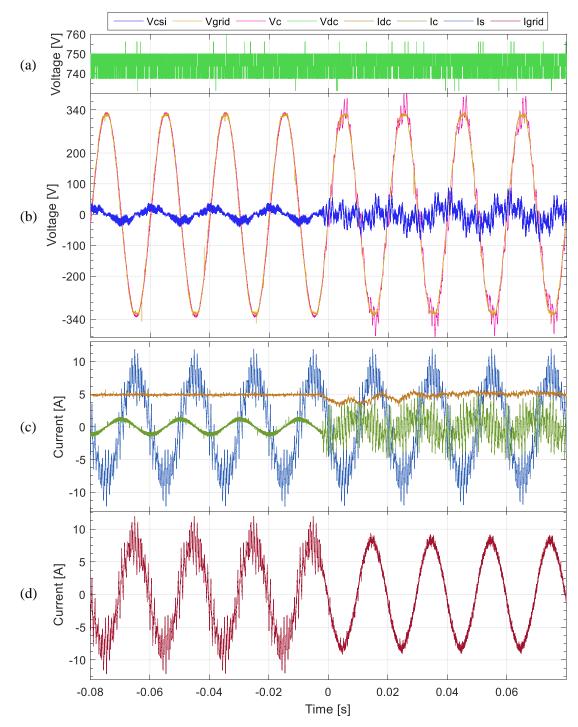

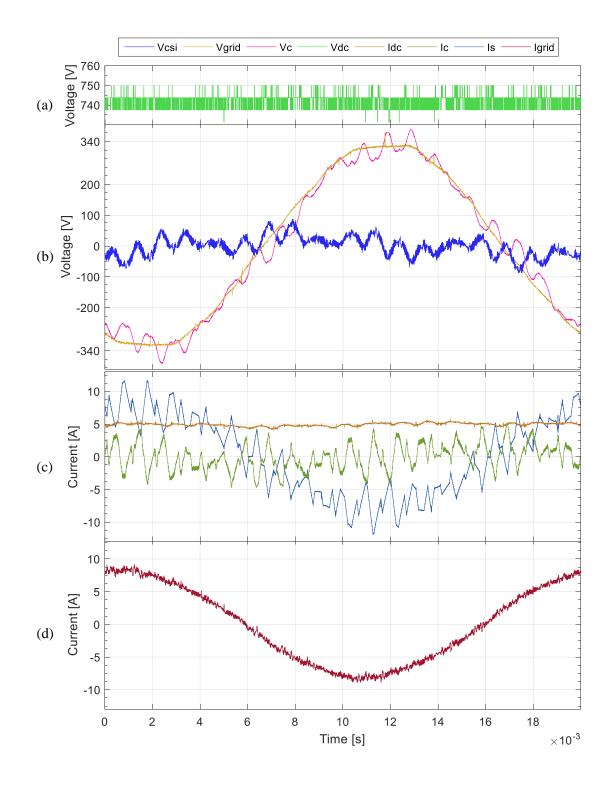

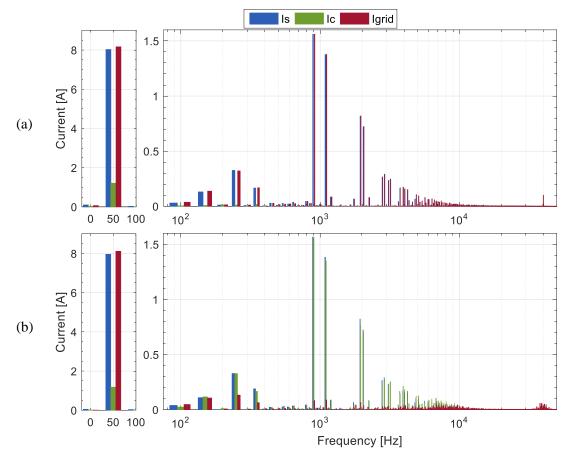

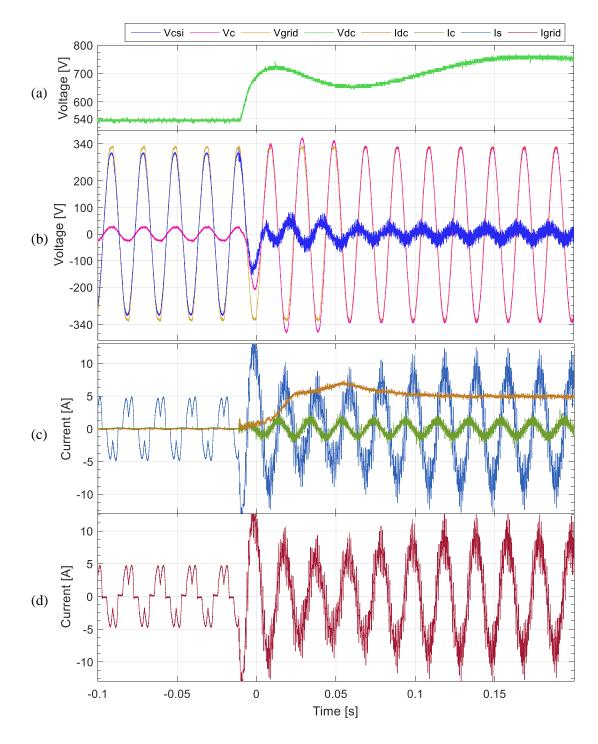

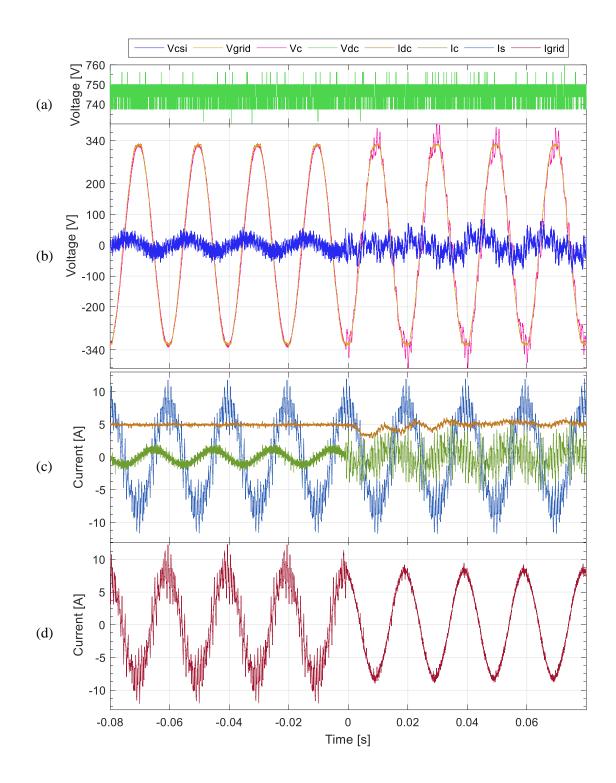

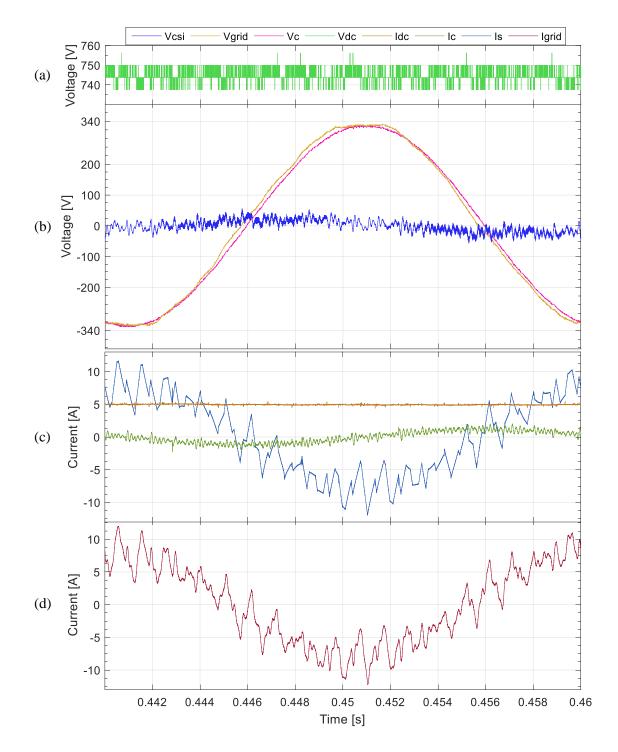

| Fig 6-3: Experimental results showing activation of ripple cancellation for VSI and CSI for K=0.1 for Phase A: a) VSI DC-link vol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ltage |

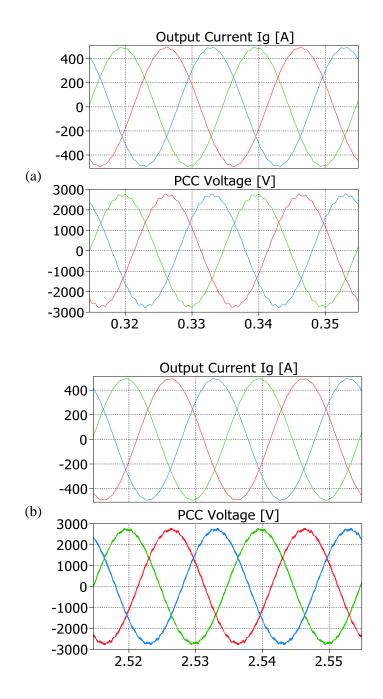

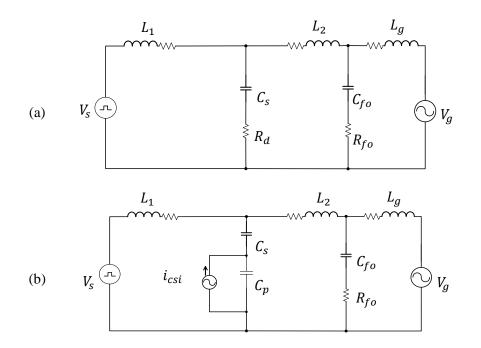

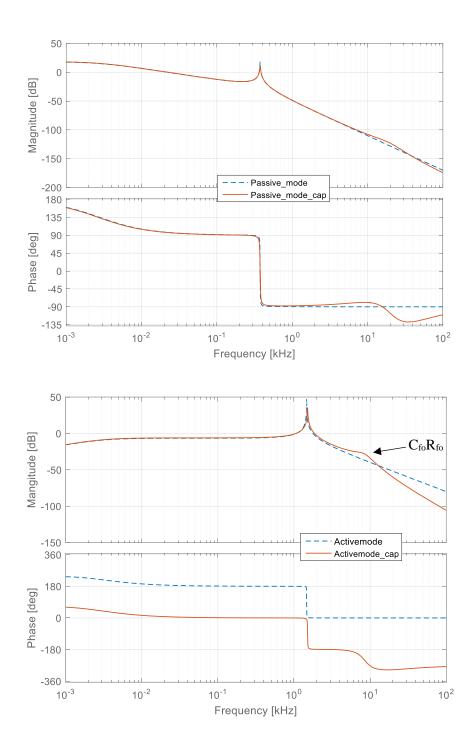

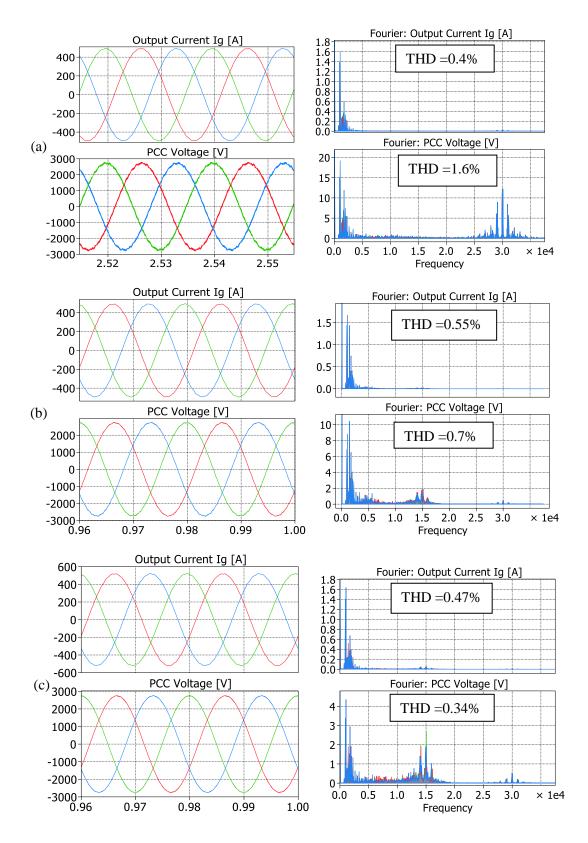

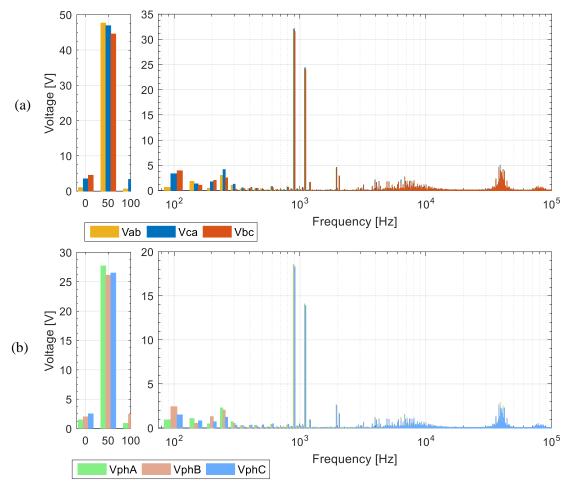

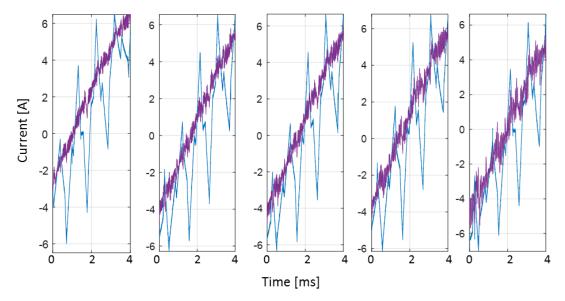

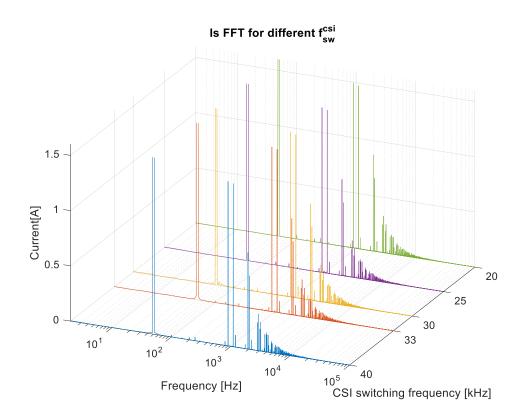

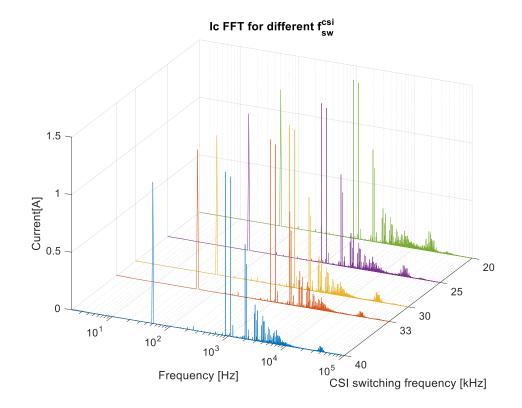

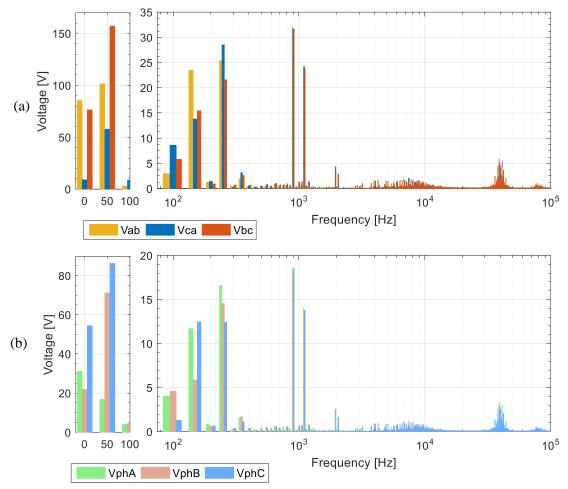

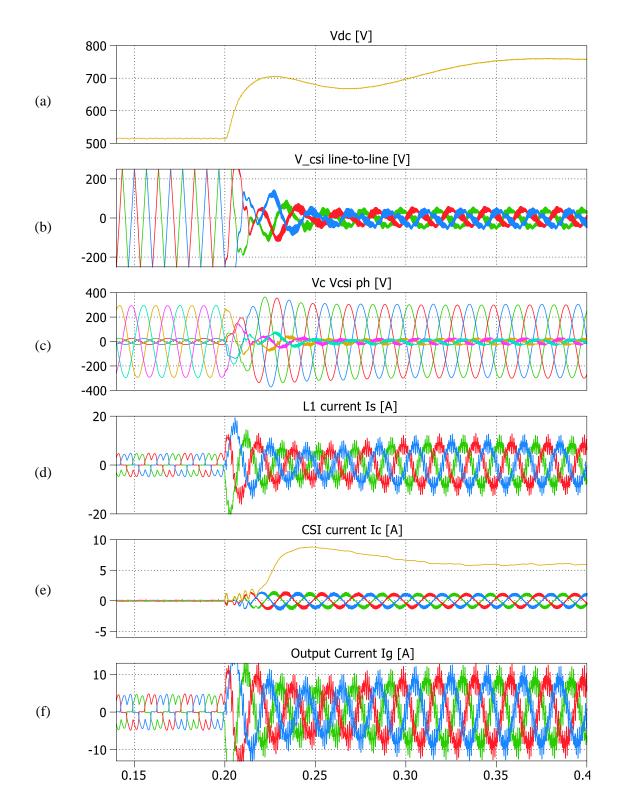

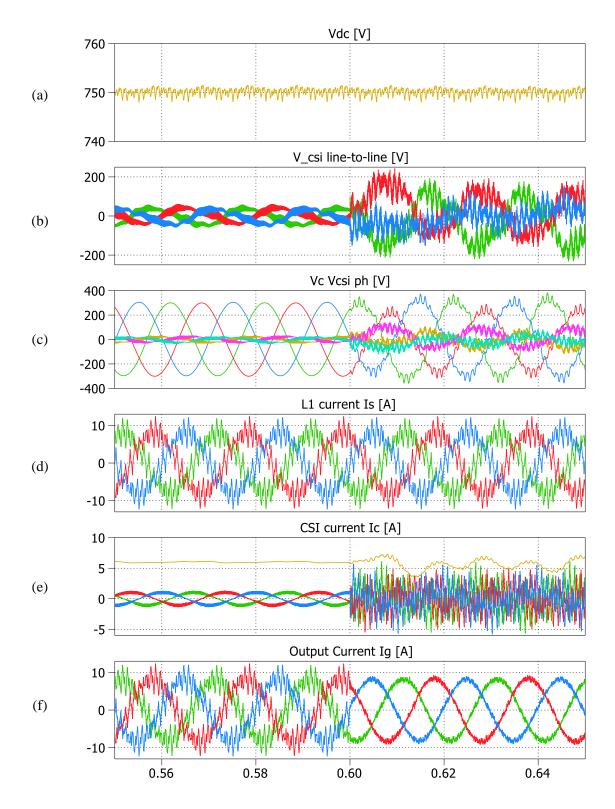

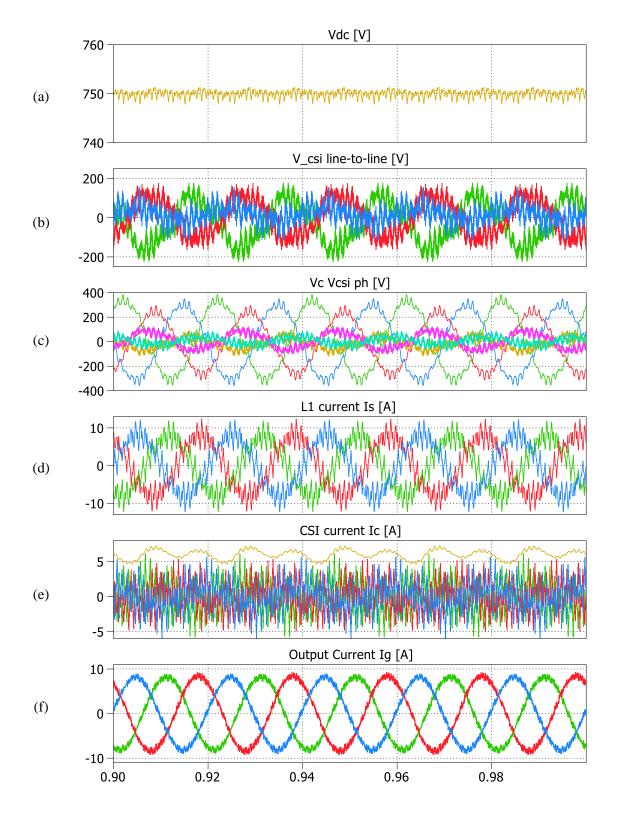

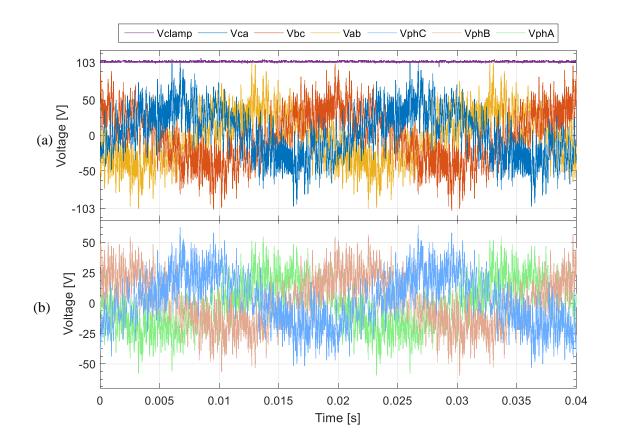

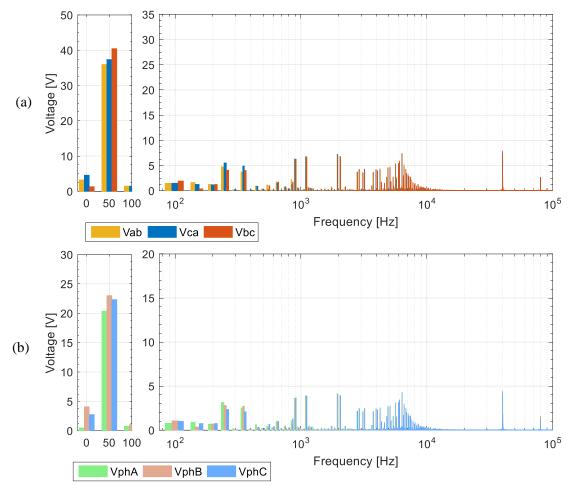

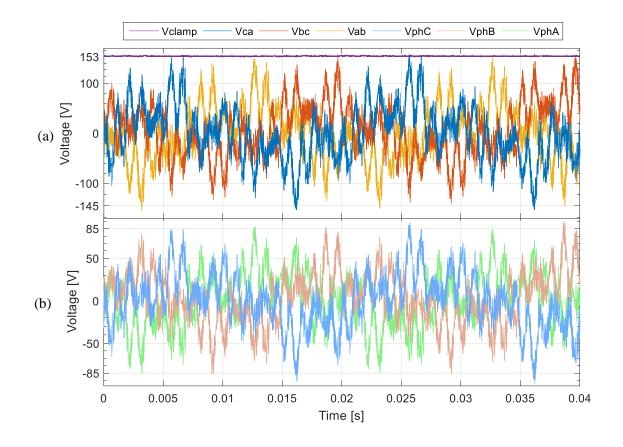

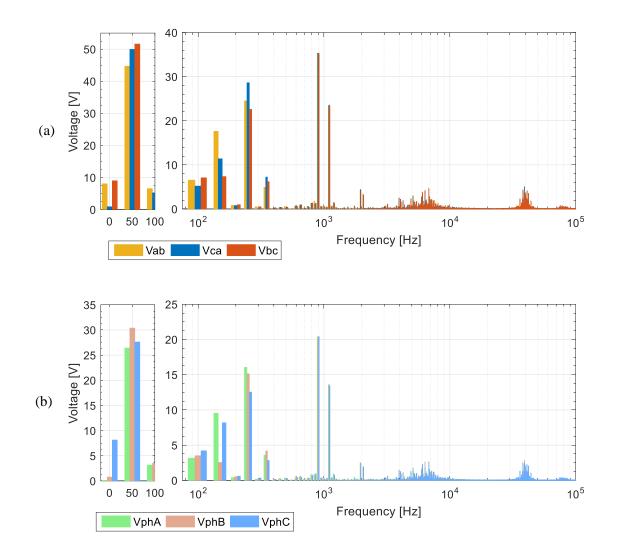

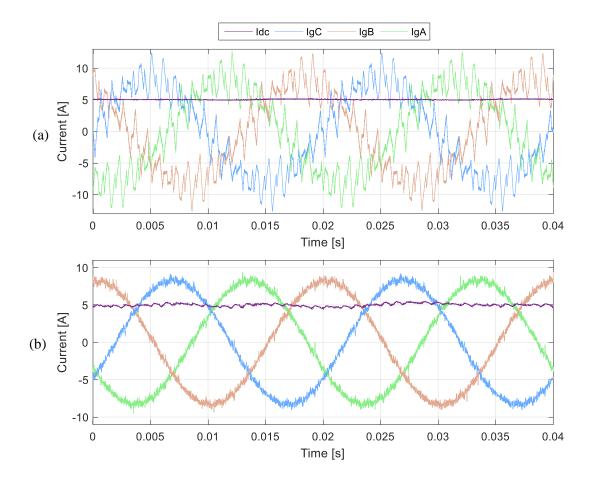

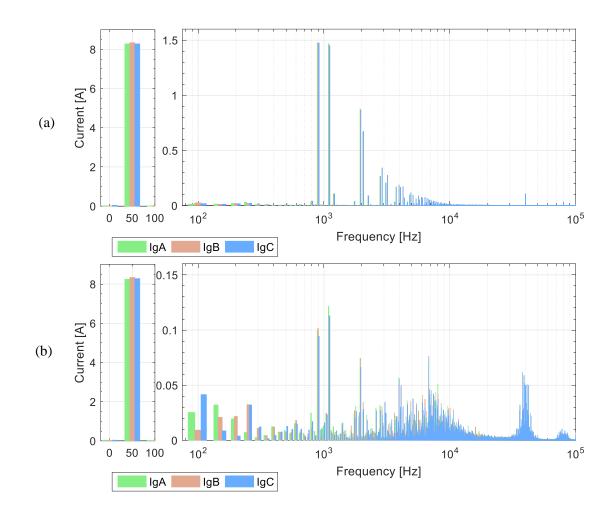

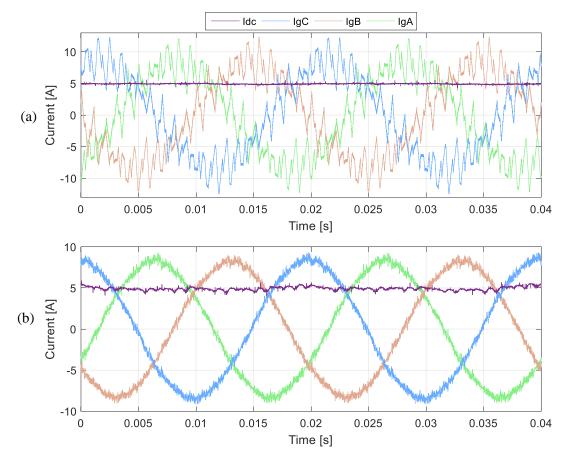

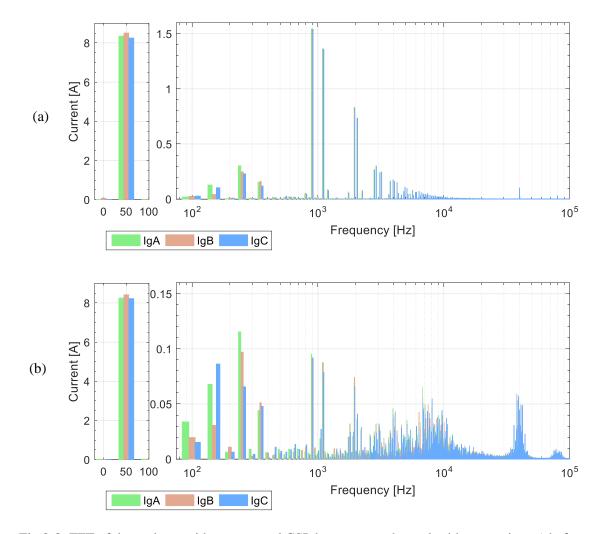

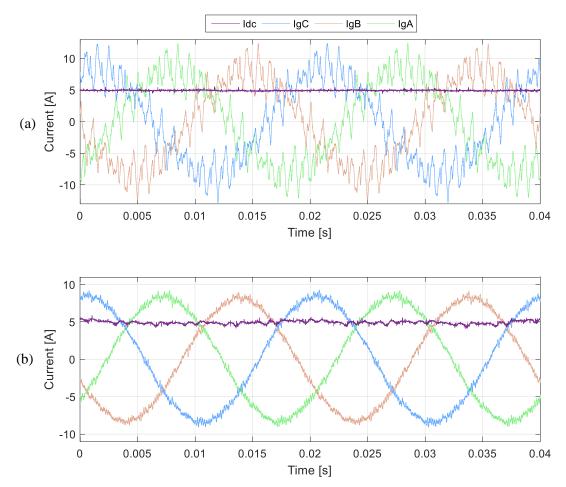

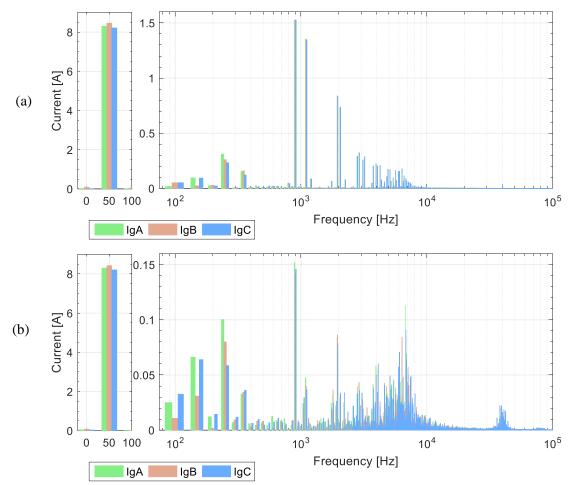

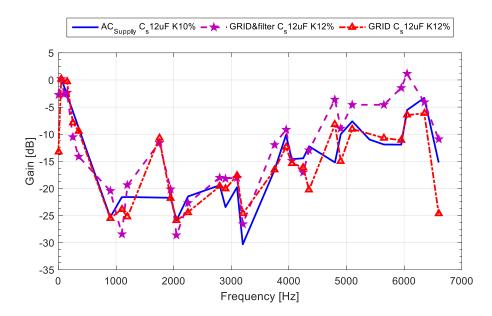

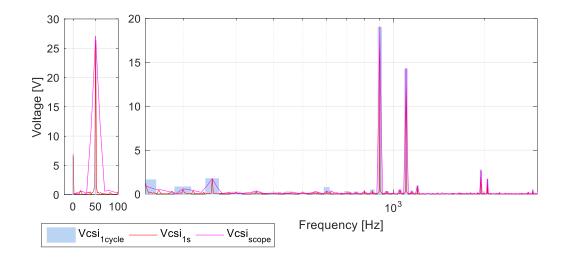

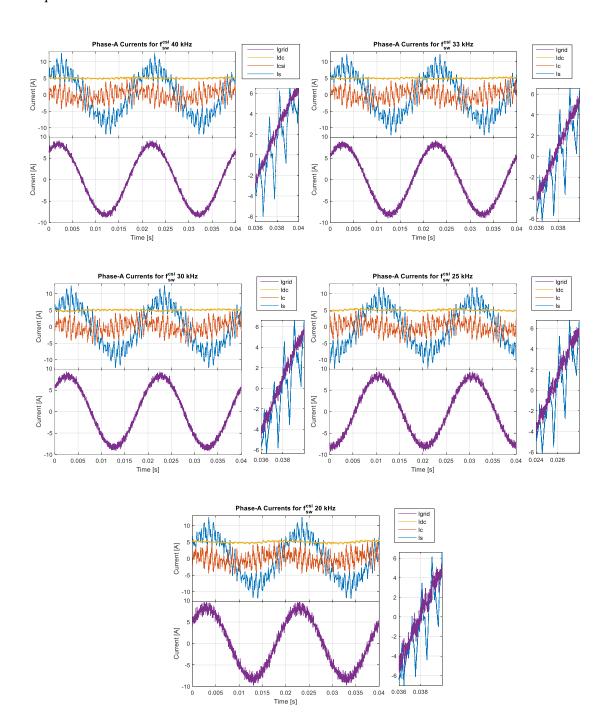

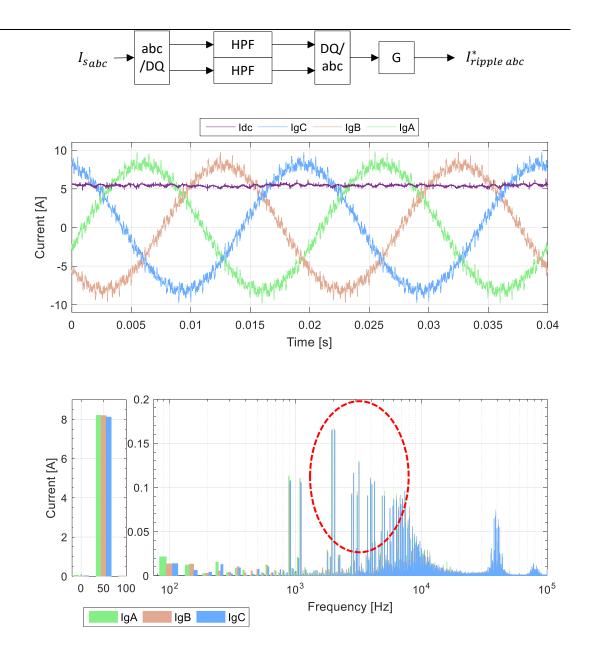

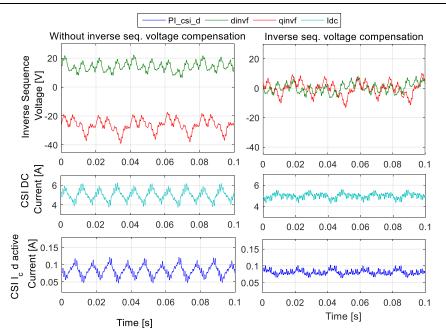

| $(V_{dc})$ ; b) Series capacitor $(V_c)$ , CSI $(V_{csi})$ and grid $(V_{grid})$ phase voltages; c) CSI DC-link current $(I_{dc})$ , Main VSI current $(I_s)$ and so $(V_{dc})$ ; b) Series capacitor $(V_c)$ , CSI $(V_{csi})$ and grid $(V_{grid})$ phase voltages; c) CSI DC-link current $(I_{dc})$ , Main VSI current $(I_s)$ and so $(V_{dc})$ ; b) Series capacitor $(V_c)$ , CSI $(V_{csi})$ and grid $(V_{grid})$ phase voltages; c) CSI DC-link current $(I_{dc})$ , Main VSI current $(I_s)$ and so $(V_{dc})$ ; b) Series capacitor $(V_c)$ , CSI $(V_{csi})$ and grid $(V_{grid})$ phase voltages; c) CSI DC-link current $(I_{dc})$ , Main VSI current $(I_s)$ and so $(V_{dc})$ ; b) Series capacitor $(V_c)$ , CSI $(V_{csi})$ and so $(V_{dc})$ ; b) Series capacitor $(V_c)$ , CSI $(V_{csi})$ and Series capacitor $(V_{dc})$ ; b) Series capacitor $(V_{dc$            | eries |