# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2017

## Design and Test of a Gate Driver with Variable Drive and Self-Test Capability Implemented in a Silicon Carbide CMOS Process

Matthew Barlow University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the <u>Electronic Devices and Semiconductor Manufacturing Commons</u>, and the <u>VLSI and</u> Circuits, Embedded and Hardware Systems Commons

#### Recommended Citation

Barlow, Matthew, "Design and Test of a Gate Driver with Variable Drive and Self-Test Capability Implemented in a Silicon Carbide CMOS Process" (2017). *Theses and Dissertations*. 1976.

http://scholarworks.uark.edu/etd/1976

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

## Design and Test of a Gate Driver with Variable Drive and Self-Test Capability Implemented in a Silicon Carbide CMOS Process

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

by

Matthew W. Barlow

University of Arkansas

Bachelor of Science in Electrical Engineering, 2007

University of Arkansas

Master of Science in Electrical Engineering, 2012

## May 2017 University of Arkansas

| This dissertation is approved for recommen | dation to the Graduate Council.         |

|--------------------------------------------|-----------------------------------------|

| Dr. H. Alan Mantooth Dissertation Director |                                         |

| Dr. Simon Ang Committee Member             | Dr. Jia Di<br>Committee Member          |

| Dr. Michael Glover Committee Member        | Dr. A. Matthew Francis Committee Member |

#### **Abstract**

Discrete silicon carbide (SiC) power devices have long demonstrated abilities that outpace those of standard silicon (Si) parts. The improved physical characteristics allow for faster switching, lower on-resistance, and temperature performance. The capabilities unleashed by these devices allow for higher efficiency switch-mode converters as well as the advance of power electronics into new high-temperature regimes previously unimaginable with silicon devices. While SiC power devices have reached a relative level of maturity, recent work has pushed the temperature boundaries of control electronics further with silicon carbide integrated circuits.

The primary requirement to ensure rapid switching of power MOSFETs was a gate drive buffer capable of taking a control signal and driving the MOSFET gate with high current required. In this work, the first integrated SiC CMOS gate driver was developed in a 1.2 µm SiC CMOS process to drive a SiC power MOSFET. The driver was designed for close integration inside a power module and exposure to high temperatures. The drive strength of the gate driver was controllable to allow for managing power MOSFET switching speed and potential drain voltage overshoot. Output transistor layouts were optimized using custom Python software in conjunction with existing design tool resources. A wafer-level test system was developed to identify yield issues in the gate driver output transistors. This method allowed for qualitative and quantitative evaluation of transistor leakage while the system was under probe. Wafer-level testing and results are presented.

The gate driver was tested under high temperature operation up to 530 °C. An integrated module was built and tested to illustrate the capability of the gate driver to control a power MOSFET under load. The adjustable drive strength feature was successfully demonstrated.

©2017 by Matthew Barlow All Rights Reserved

#### Acknowledgements

My partners in the lab have been essential to my success. From helping with test fixtures and lab setups, to helping make a large project possible, to making jokes and keeping spirits high, to giving feedback on my ideas. Specifically, (and in alphabetical order), I would like to thank Nick Chiolino, Kim Cornett, Attanu Dutta, Matt Francis, Guoyuan Fu, Obidiah Kegege, Chris Lee, Javier Valle Mayorga, Ashfaqur Rahman, Sayan Seal, and Paul Shepherd.

I would also like to thank Dr. H. Alan Mantooth for providing the opportunities throughout my time at the University of Arkansas for interesting and productive research.

I would like to thank Ewan P. Ramsay, Robin F. Thompson, Robert A. R. Young, and Jennifer D. Walls from Raytheon UK for their help and support during the design and fabrication of this work.

I would also like to thank Dr. Micheal Glover and Micheal Steger, of the High Densitity Electronics Center at the University of Arkansas. Their electronics packaging expertise was essential for going from a fresh wafer to packaged and testable circuits.

This research was funded by the National Science Foundation Grant #IIP1237816. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author and do not necessarily reflect the views of the National Science Foundation

## **Dedication**

I am forever grateful to my family, for supporting me from the beginning to the end. My wonderful wife, Kathryn, who believes in me constantly. To my dear children, Abigail, Ethan, and Iriana for cheering me up with their boundless energy. To my loving mother and father, for providing me the foundation needed to even contemplate such an endeavor. I dedicate this work to all of you. Thank you so much, I could not have done it without all of you.

## **Table of Contents**

| 1          | Introduction                           | 1   |

|------------|----------------------------------------|-----|

|            | Organization                           | 2   |

| 2          | Silicon Carbide Overview               | 3   |

|            | SiC in Power Electronics               | 6   |

|            | SiC Integrated Circuits                | 7   |

|            | Summary                                | 10  |

| 3          | Power Electronics Switching            | 11  |

|            | Examination of switching topologies    | 11  |

|            | Gate Drive Techniques                  | 26  |

|            | Silicon carbide challenges             | 30  |

|            | Summary                                | 31  |

| 4          | Gate Driver Design                     | 33  |

|            | Design Goals and Specifications        | 33  |

|            | Power Module Integration               | 37  |

|            | Adjustable Drive Strength              | 38  |

|            | Lessons Learned                        | 57  |

| 5          | Power FET Optimization                 | 59  |

|            | Parametric evaluation of problem space | 68  |

|            | Summary                                | 83  |

| 6          | Design for Test                        | 84  |

|            | Motivation                             | 84  |

|            | Characteristics of failures            | 87  |

|            | In-circuit Fault Detection             | 94  |

|            | Improved circuit testability           | 105 |

| <b>3 4</b> | Wafer test results                     | 107 |

|            | Conclusions                            | 115 |

|            | Lessons Learned                        | 116 |

| 7          | Testing                                | 117 |

|            | High temperature test design           | 117 |

|            | High temperature setup evaluation      | 120 |

|            | Test Setup Configuration.              | 124 |

|            | Power module integration.              | 136 |

|            | Conclusions                            | 153 |

|    | Lessons Learned             | 154 |

|----|-----------------------------|-----|

| 8  | Conclusions and Future Work | 155 |

|    | Future Work                 | 156 |

| A. | Appendix: Python Code Base  | 162 |

|    | Python Optimization of FETs | 162 |

|    | Gate Driver Test Interface  |     |

## **List of Figures**

| Fig. 2.1. Unipolar power device structures: vertical power MOSFET structure (a) and power Schottky diode structure (b).                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.2. Example cross-section of a CMOS inverter in the Raytheon HiTSiC process                                                                                                                                                                                                                              |

| Fig. 3.1. Fundamental switch orientation that can be expanded into various power electronics circuits by the addition of passive components                                                                                                                                                                    |

| Fig. 3.2. Clamped-inductive load circuit, with optional synchronous MOSFET Q2                                                                                                                                                                                                                                  |

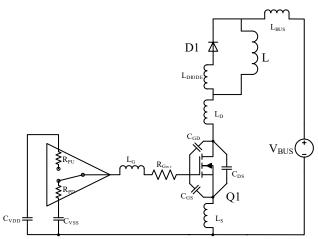

| Fig. 3.3. Clamped inductive load schematic showing location of C <sub>GD</sub> and C <sub>GS</sub>                                                                                                                                                                                                             |

| Fig. 3.4. Example MOSFET switching waveforms for a clamped-inductive load turn-on 1                                                                                                                                                                                                                            |

| Fig. 3.5. Various load configurations for a single low-side switch. (a) shows a non-inductive resistive load, (b) shows a capacitance in parallel with the load, and (c) shows an inductive load with flyback diode                                                                                            |

| Fig. 3.6. Clamped inductive load configuration with charged inductor. D1 starts in conduction, and Q2 switches on, resulting in a fast rising $V_{DS}$ on Q1. This rapid drain voltage rise ha the potential to cause the $V_{GS}$ of Q1 to rise above $V_{TH(on)}$                                            |

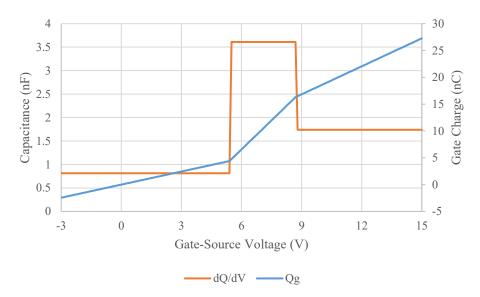

| Fig. 3.7. Gate charge and related capacitance parameters for a Cree C3M0065090J MOSFET. The gate charge parameters are linear in three separate regions as indicated by the dQ/dV line. Input capacitance is 813 pF in off region with a V <sub>DS</sub> of 400 V and an I <sub>DS</sub> of 20 A at 25 °C.[33] |

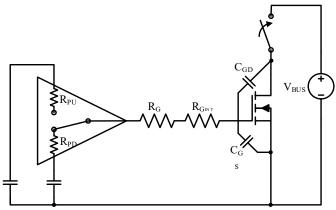

| Fig. 3.8. Parasitic turn-on sub-circuit with explicit internal capacitances and resistances illustrated for the purpose of deriving system behavior under a switching transient 2                                                                                                                              |

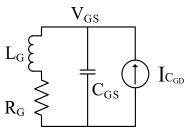

| Fig. 3.9. Simplified gate drive network for identifying safe operating conditions                                                                                                                                                                                                                              |

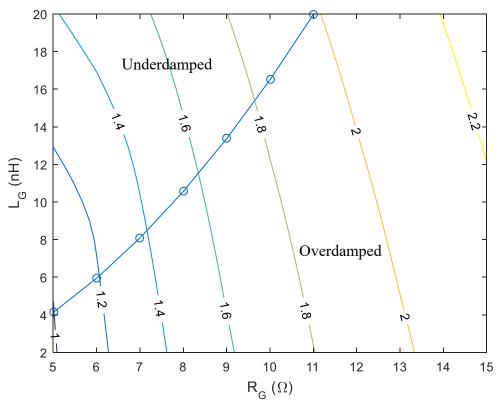

| Fig. 3.10. Example peak gate voltage after 10 ns time with an I <sub>CGD</sub> of 200 mA. The C <sub>GS</sub> used is 660 pF, which represents the gate voltage behavior switching 600 V in 12 ns. The critically damped boundary line is marked with circular markers                                         |

| Fig. 3.11. Taking the internal resistance and capacitances of devices from Fig. 3.8, parasitic interconnect inductances are added as lumped elements to complete the system model. Series inductances have been combined to simplify analysis                                                                  |

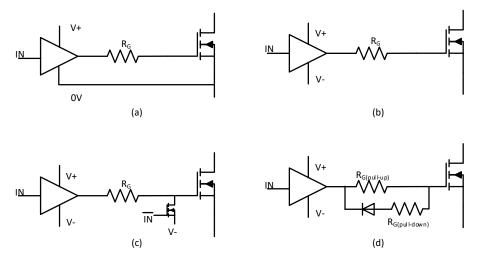

| Fig. 3.12. Various gate driver connection strategies. (a) shows a single supply connection, (b) shows a dual-rail power supply, (c) shows an active Miller clamp, and (d) shows a diode – resistor network to provide additional drive strength at turn-off                                                    |

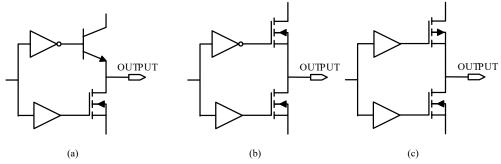

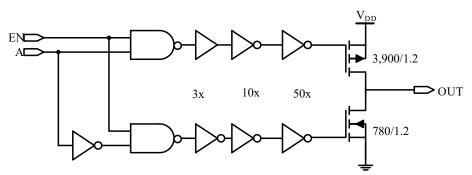

| shows a NPN pull-up de             | blogies possible with the Raytheon HiTSiC process. Part (a) evice, (b) shows a NFET pull-up device, and (c) shows a PFET                            |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

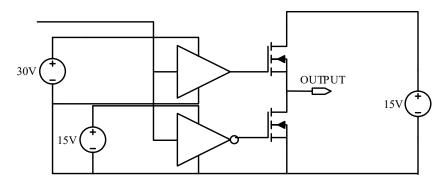

| Fig. 4.2. Voltage domains requi    | ired for a NFET totem pole output                                                                                                                   |

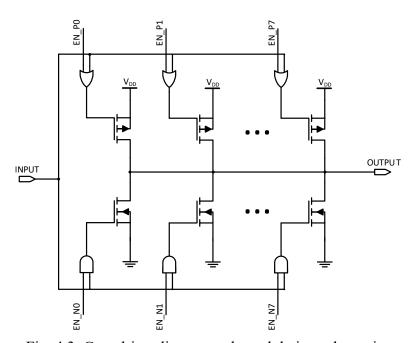

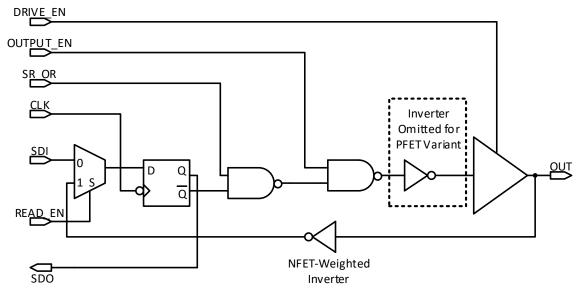

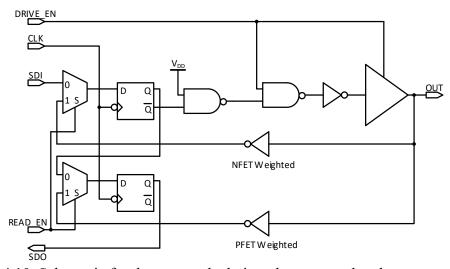

| Fig. 4.3. Gate drive slice streng  | th modulation schematic                                                                                                                             |

| Fig. 4.4. Input signal timing for  | multiple drive strength switching                                                                                                                   |

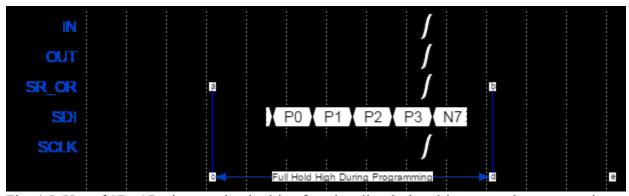

|                                    | maintain drive functionality during drive strength programming                                                                                      |

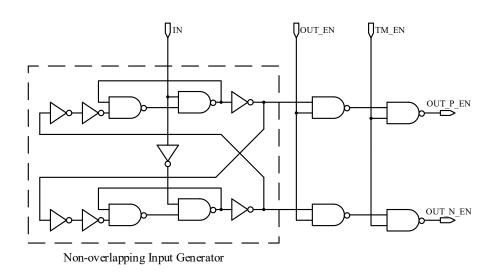

| Fig. 4.6. Dead-time generation     | and input control logic                                                                                                                             |

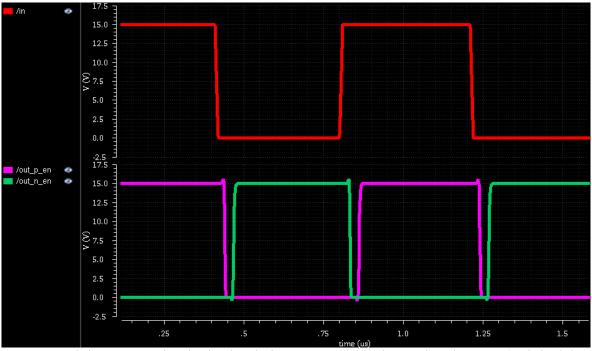

| and turned into separate           | logic simulation at 25 °C. The input signal on top (red) is delayed active high signals for the PFET pull-up (magenta) and the a)                   |

|                                    | drive logic for a NFET. The output connects directly to the gate                                                                                    |

| Fig. 4.9. Single transistor slice  | driver with tristate logic                                                                                                                          |

| Fig. 4.10. Schematic for the tes   | t-mode drain voltage control and measurement                                                                                                        |

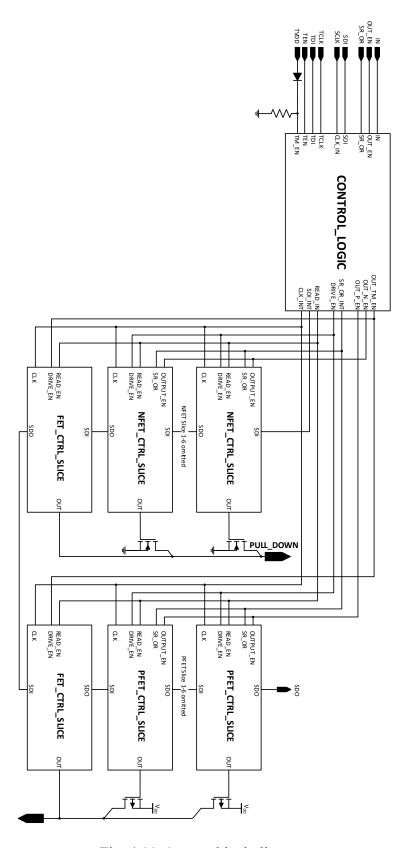

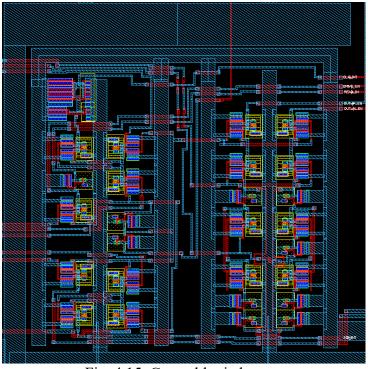

| Fig. 4.11. System block diagram    | m49                                                                                                                                                 |

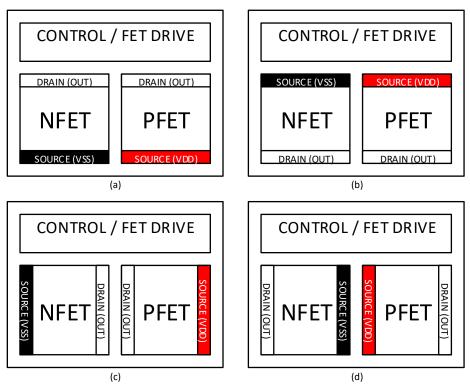

| Fig. 4.12. Power transistor orien  | ntation options considered                                                                                                                          |

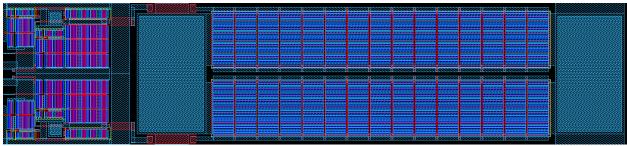

| =                                  | owing two NFET output transistor slices and the associated pads54                                                                                   |

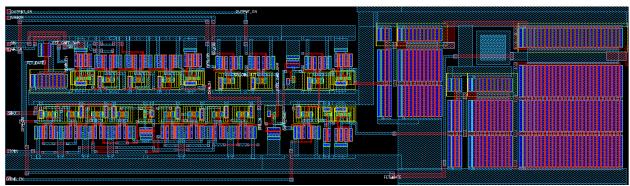

| Fig. 4.14. Layout of the control   | logic for a single NFET slice. 54                                                                                                                   |

| Fig. 4.15. Control logic layout.   |                                                                                                                                                     |

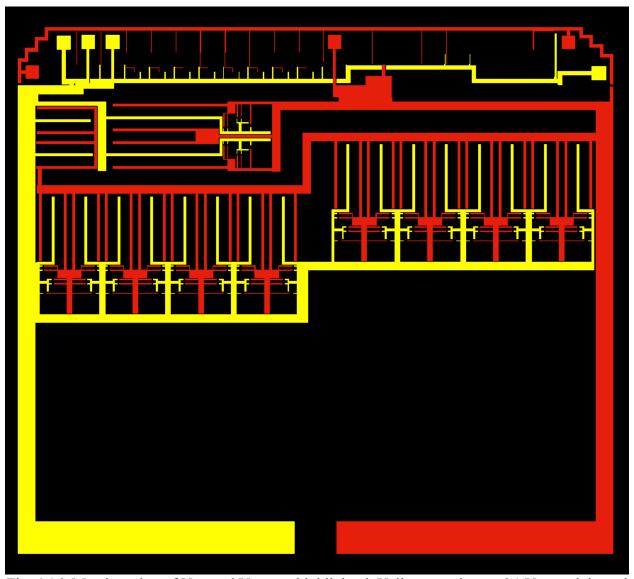

| = =                                | and V <sub>SS</sub> nets highlighted. Yellow area is metal 1 V <sub>SS</sub> , and the red                                                          |

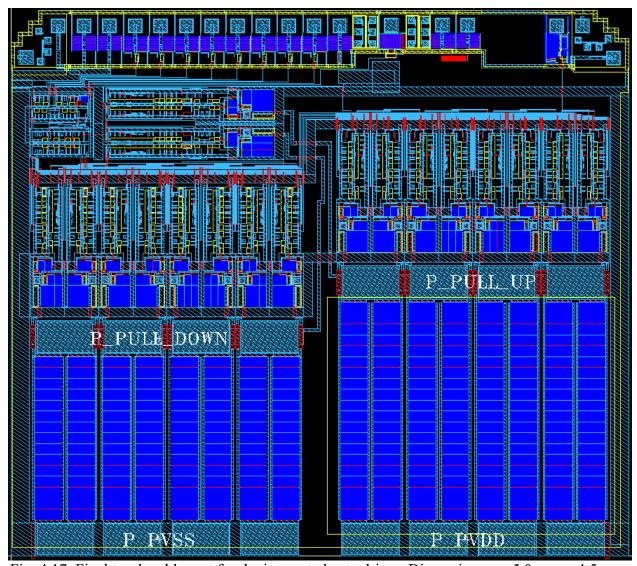

|                                    | t for the integrated gate driver. Dimensions are 5.0 mm x 4.5 mm.                                                                                   |

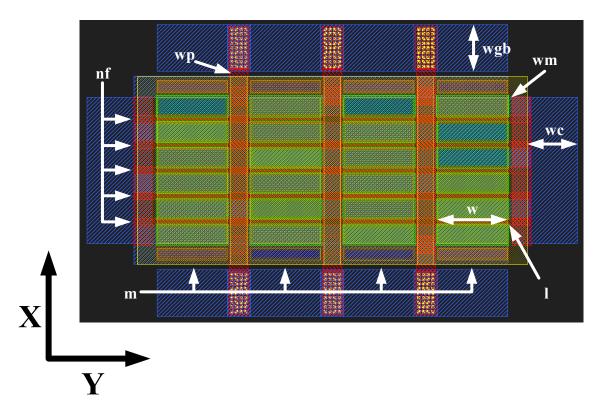

| fingers stacked verticall          | t from the layout generation routine. In this design, there are five $y$ ( $nf = 5$ ), and there are four stacks of fingered transistors ( $m = 63$ |

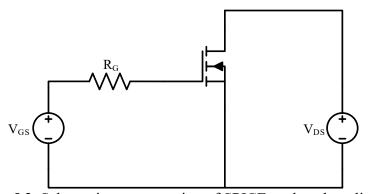

| Fig. 5.2. Schematic representation | ion of SPICE testbench netlist                                                                                                                      |

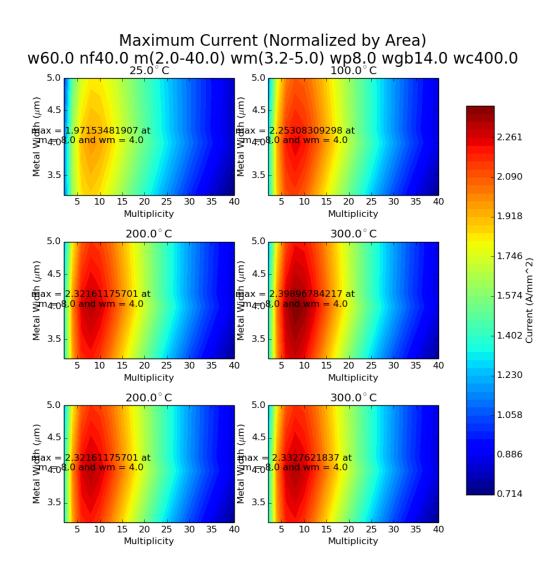

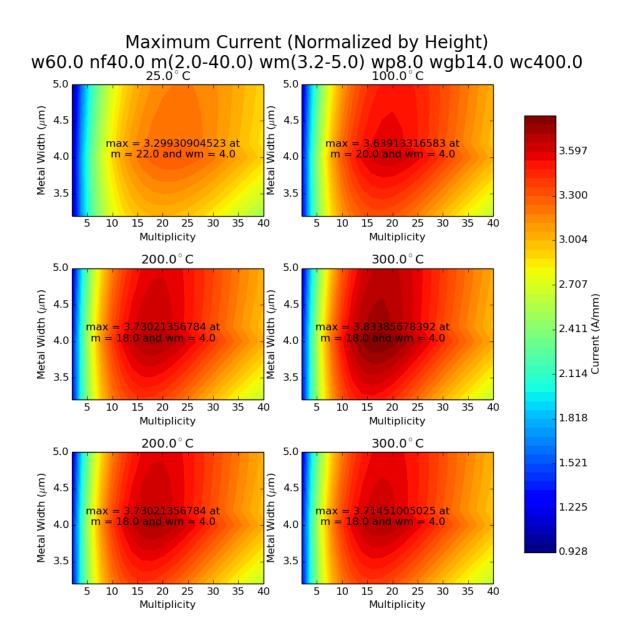

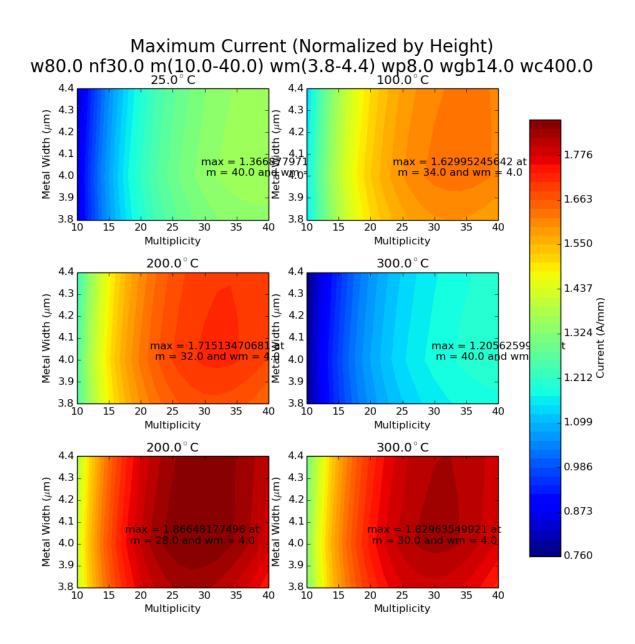

| Fig. 5.3. Comparison of effective transistor width versus the width of the main metal conductors. Transistor width is adjusted by changing the number of 60 µm wide transistor blocks (multiplicity). Designs are simulated over temperature, normalized to total layout area, and plotted                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

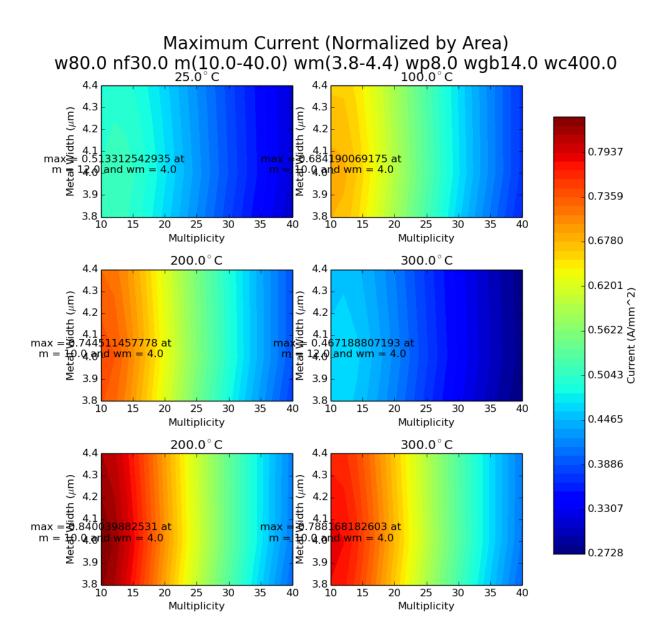

| Fig. 5.4 Parametric evaluation of the static current characteristics of a NFET over size and metal width. Current is presented as A/mm. Maximum current occurs when total width is 1.32 mm at 25 °C to 1.08 mm at 200 °C. Spending additional area on metal width does not improve current density.                                                                                                                                                                                   |

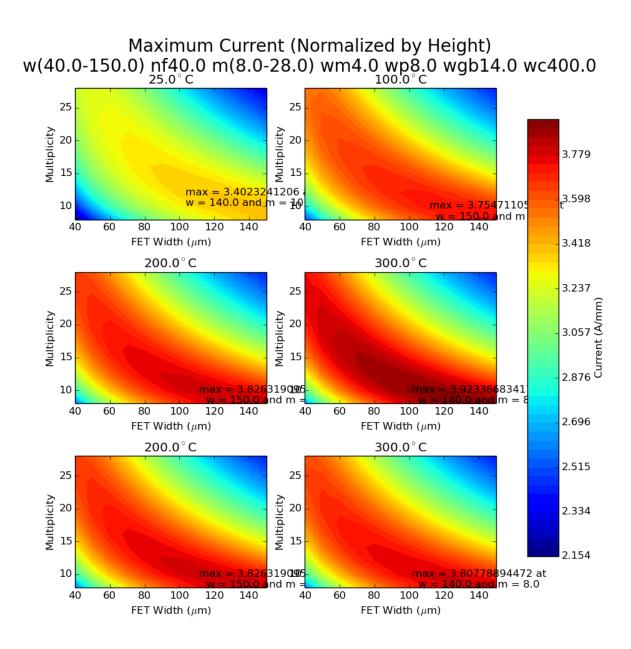

| Fig. 5.5. Maximum current response while comparing the number of divisions in a design 73                                                                                                                                                                                                                                                                                                                                                                                             |

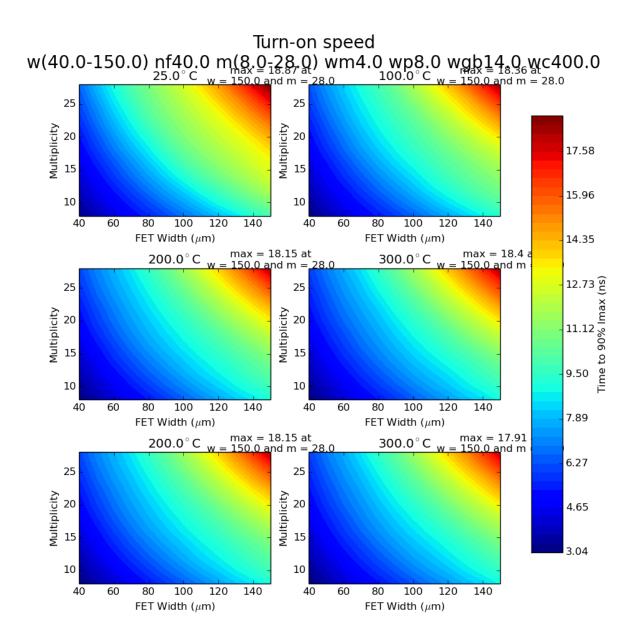

| Fig. 5.6. Turn-on time comparing the number of divisions in a design                                                                                                                                                                                                                                                                                                                                                                                                                  |

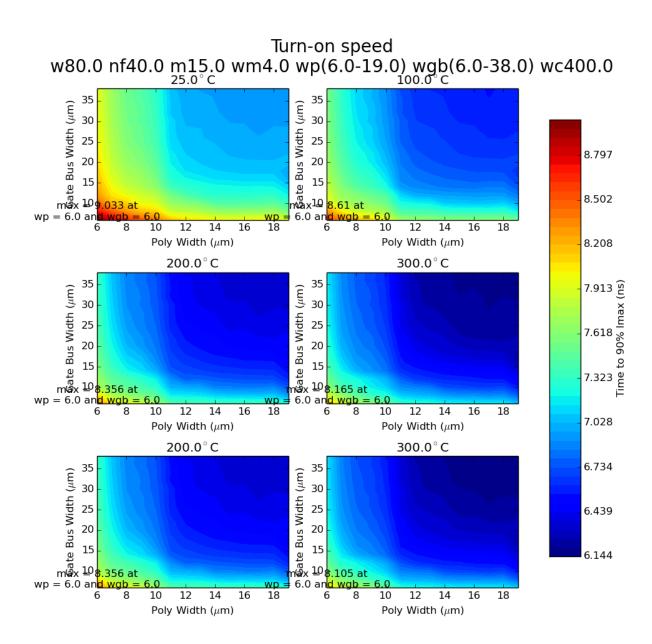

| Fig. 5.7 Turn-on speed comparing gate signal distribution sizes (wgb and wp)                                                                                                                                                                                                                                                                                                                                                                                                          |

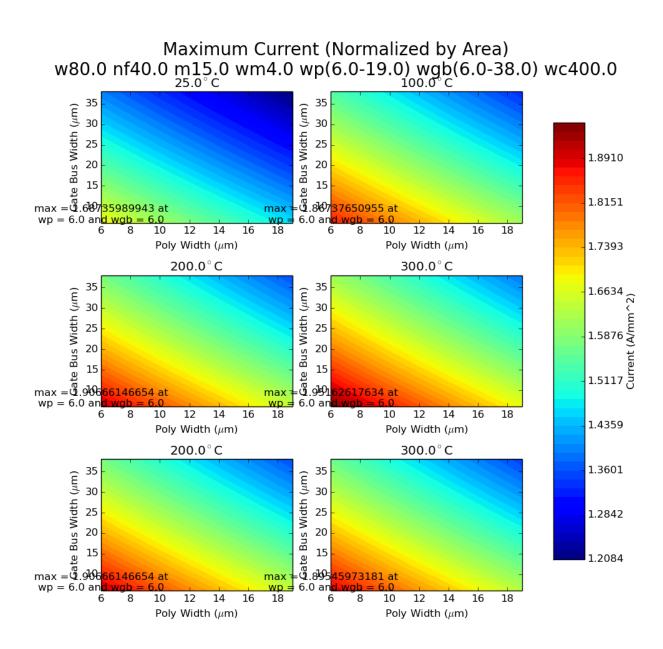

| Fig. 5.8. Current density of different gate signal distribution (gp v wgb)                                                                                                                                                                                                                                                                                                                                                                                                            |

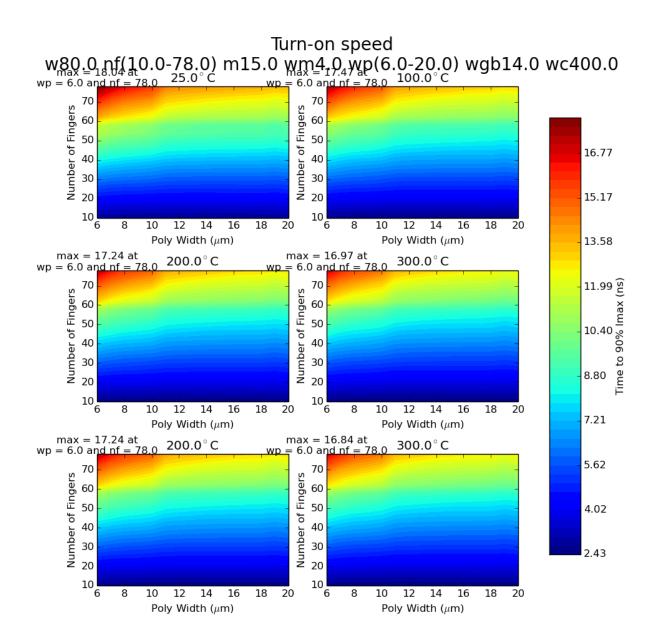

| Fig. 5.9 Turn-on time comparing poly distribution width and the number of fingers                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fig. 5.10. PFET current density in A/mm <sup>2</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fig. 5.11. Maximum current in A/mm for a PFET.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Fig. 6.1. Bonding pad from the first pass after attempting 1 mil gold ball bonding three times.  The gold coating on the pad (yellow) has been torn off where the ball bonds were made, leaving the underlying metal below.                                                                                                                                                                                                                                                           |

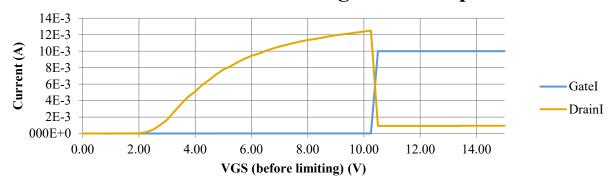

| Fig. 6.2. Gate oxide breakdown on a 1.2 $\mu m$ channel length transistor during a $V_{GS}$ sweep, with a $V_{DS}$ of 0.1 V. Breakdown occurs at a $V_{GS}$ of 10.5 V, and $I_{G}$ reaches the programmed current limit of 10 mA. Subsequent runs indicate a gate-source short of 375 $\Omega$                                                                                                                                                                                        |

| Fig. 6.3. Topology of a drain-source short                                                                                                                                                                                                                                                                                                                                                                                                                                            |

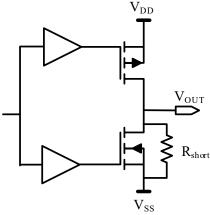

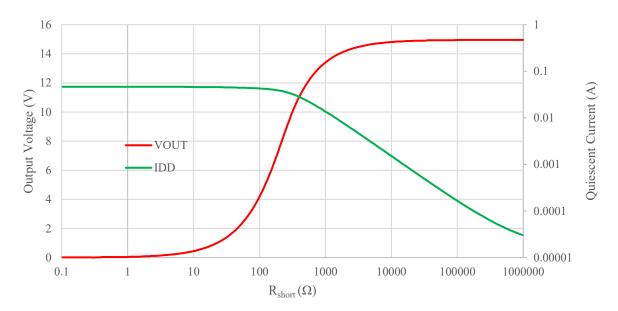

| Fig. 6.4. Circuit response of an example power inverter over a range of drain-source leakage. A resistor connected to the drain and source of a NFET is varied in resistance from 0.1 Ω to 1 MΩ. The added resistance contributes to the quiescent current (green) draw up to the point where it overpowers the PFET pull-up. After that point, the output voltage (red) is affected, and current is limited by the saturation current of the PFET                                    |

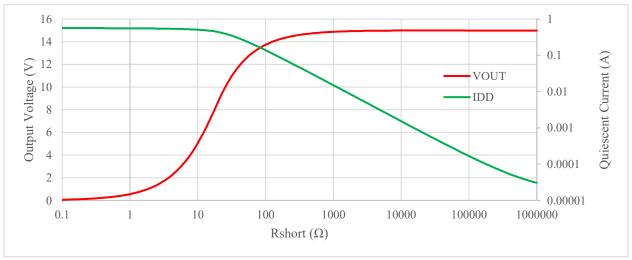

| Fig. 6.5. Circuit response of an example power inverter over a range of gate-source leakage. A resistor is placed across the gate and source of the power NFET, and the value is varied from $0.1~\Omega$ to $1~M\Omega$ . The resistance contributes to increased quiescent current (green) of the system to the point where the resistance decreases the gate-source voltage (red). Smaller resistances result in a current limited by the saturation current of the output driver. |

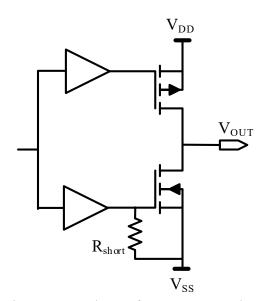

| Fig. 6.6. Topology of a gate-source short.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

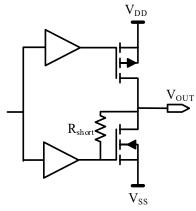

| Fig. | 6.7. Topology of a gate-drain short                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

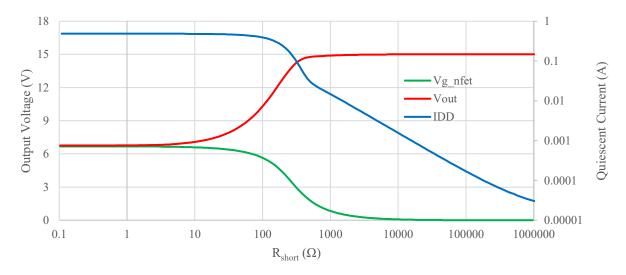

| Fig. | 6.8. Circuit response of an example power inverter over a range of gate-drain leakage. A resistor is placed between the gate and drain of an output NFET and the value is swept from 0.1 $\Omega$ to 1 M $\Omega$ . The NFET gate is driven to 0 V with an expected drain voltage of 15 V. Quiescent current (blue) increases with decreasing resistance to the point where the NFET gate voltage rises above $V_T$ . On the left side, the current becomes dominated by the NFET driven into the saturation region, drawing additional current as $V_{GS}$ (green) rises and $V_{DS}$ (red) falls. |

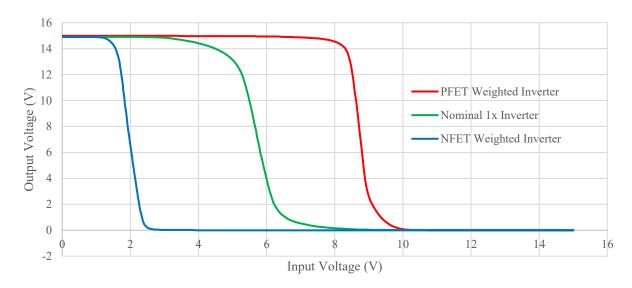

| Fig. | 6.9. Weighted inverter thresholds, compared to a standard 1X inverter. The PFET-weighted inverter is shown in red, and the NFET-weighted inverter is shown in blue                                                                                                                                                                                                                                                                                                                                                                                                                                  |

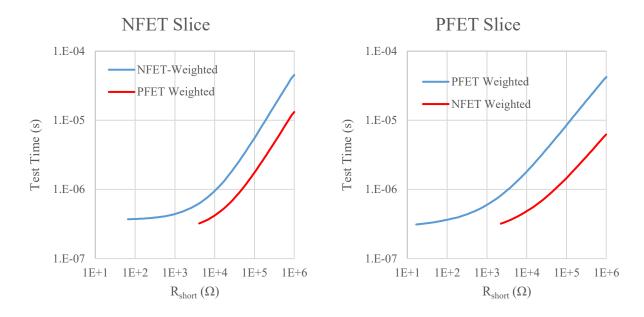

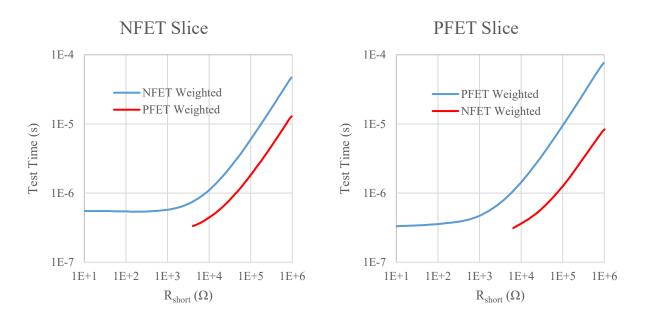

| Fig. | 6.10. Drain-source short characteristics for NFET (left) and PFET (right) devices. The red line indicates the larger $ V_{DS} $ threshold from the weighted inverter pair, and the blue line indicates the lower threshold.                                                                                                                                                                                                                                                                                                                                                                         |

| Fig. | 6.11. Gate-source short characteristics for NFET (left) and PFET (right). The red curve represents the amount of time required to indicate a fault for an equivalent gate-source resistance.                                                                                                                                                                                                                                                                                                                                                                                                        |

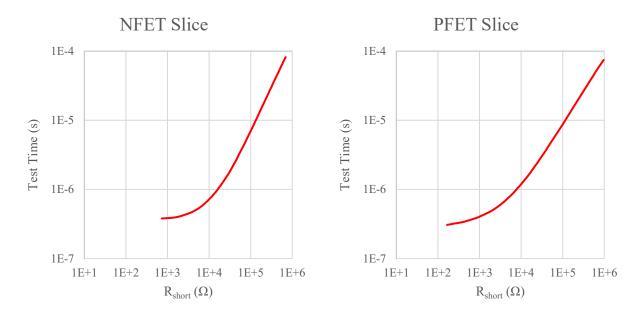

| Fig. | 6.12. Gate-Drain short characteristics, with an initial condition of $V_{GS} = 15V$ , and $V_{DS} = 0V$ . The curve indicates the time required for the gate voltage to discharge to the drain voltage through the added equivalent gate-drain resistance, as measured from the gate.                                                                                                                                                                                                                                                                                                               |

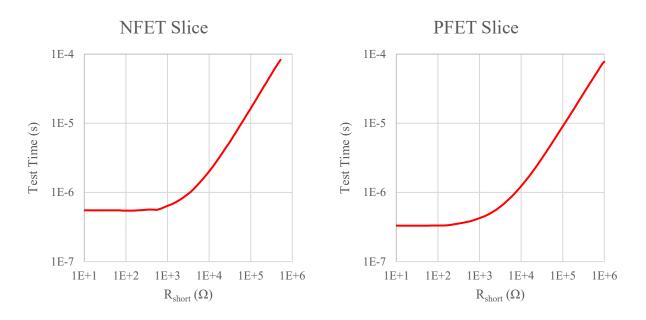

| Fig. | 6.13. Gate-drain short characteristics, with an initial condition of $V_{GS} = 0V$ , and $V_{DS} = 15V$ . The weighted inverters measure the drain voltage as it leaks through to the gate, turning on the transistor. The red line indicates the higher $ V_{DS} $ threshold, and the blue line indicates the lower $ V_{DS} $ threshold.                                                                                                                                                                                                                                                          |

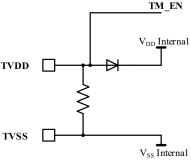

| Fig. | 6.14. TVDD and TM_EN pad cell schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Fig. | 6.15. Example test configuration GUI for wafer level gate driver verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

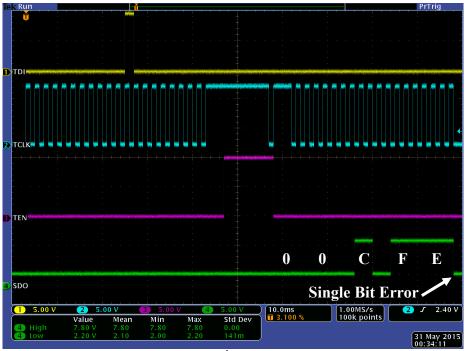

| Fig. | 6.16 R5C4 gate-drain Test Pass. The yellow trace is the test data input (TDI), the cyan trace is the test clock (TCLK), and the magenta trace is the test enable input (TEN). The green trace observes the serial data output (SDO) from the gate driver IC. The serial data output reads 0x00CFF, which indicates a passing result.                                                                                                                                                                                                                                                                |

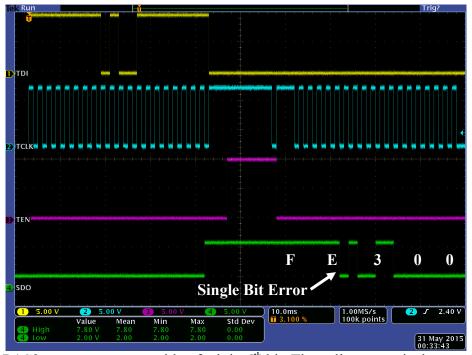

| Fig. | 6.17. R5C4 gate-source Test Pass. The yellow trace is the test data input (TDI), the cyan trace is the test clock (TCLK), and the magenta trace is the test enable input (TEN). The green trace observes the serial data output (SDO) from the gate driver IC. The serial data output reads 0xFF300, which indicates a passing result                                                                                                                                                                                                                                                               |

| Fig. | 6.18 R1C2 gate-drain Test with fault in 19 <sup>th</sup> bit. The yellow trace is the test data input (TDI), the cyan trace is the test clock (TCLK), and the magenta trace is the test enable input                                                                                                                                                                                                                                                                                                                                                                                                |

|        | (TEN). The green trace observes the serial data output (SDO) from the gate driver IC. The serial data output reads 0x00CFE, which indicates a fault (expected 0x00CFF) 112                                                                                                                                                                                                                                                                       |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 6 | 6.19 R1C2 gate-source test, with a fault in 6 <sup>th</sup> bit. The yellow trace is the test data input (TDI), the cyan trace is the test clock (TCLK), and the magenta trace is the test enable input (TEN). The green trace observes the serial data output (SDO) from the gate driver IC. The serial data output reads 0xFD300, which indicates a fault (expected 0xFF300).                                                                  |

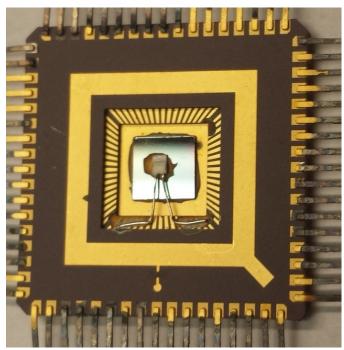

| Fig. 7 | 7.1. RTD sensor configuration for hot finger thermocouple temperature correlation testing. The LDCC 68 package is identical to other packages used for testing. A blank SiC die was used to simulate the circuit under test, and the platinum RTD was epoxied to the top of the die. The RTD leads span multiple pins to allow for 4-wire Kelvin connections. Discolorations are due to the solder and high temperatures used during testing 121 |

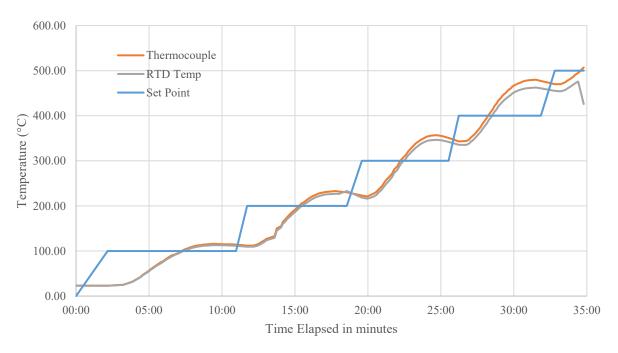

| Fig. 7 | 7.2 Aluminum hot finger temperature calibration results. Hot plate used the thermocouple as feedback, resulting in temperature overshoot                                                                                                                                                                                                                                                                                                         |

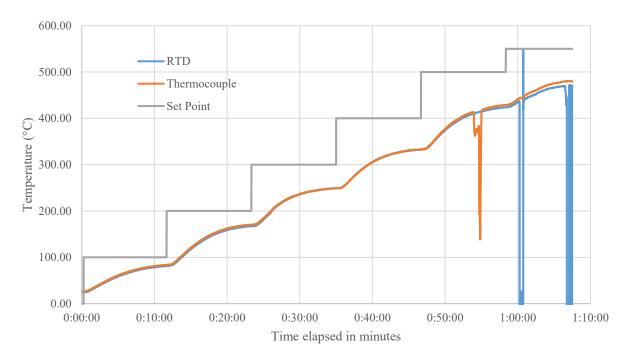

| Fig. 7 | 7.3. Copper hot finger calibration results. Hot plate was controlled without feedback, resulting in the underdamped temperature response. Negative discontinuities were a result of intermittent thermocouple contact at 55 minute, and RTD lead shorting at 1:00:00 and 1:07:00.                                                                                                                                                                |

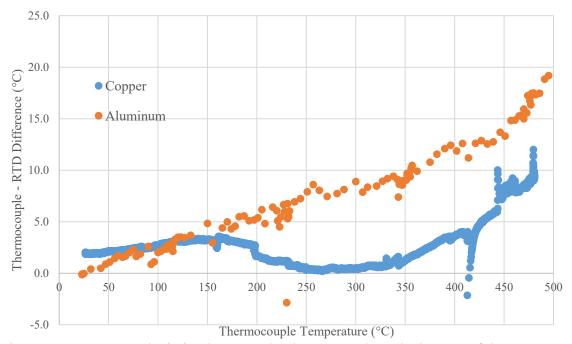

| Fig. 7 | 7.4. Temperature deviation between the thermocouple at the bottom of the LDCC 68 package and the top surface of the SiC die measured with the RTD. Measurement issues caused large discontinuities at points, major outliers have been removed                                                                                                                                                                                                   |

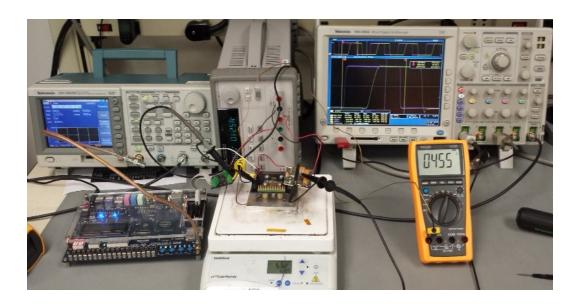

| Fig. 7 | 7.5. Hot plate testing using the QFP64 test configuration with the gate driver loaded with a C2M0280120D power MOSFET. Measured temperature at the bottom of the package is 455 °C, with an input frequency of 1.0 MHz                                                                                                                                                                                                                           |

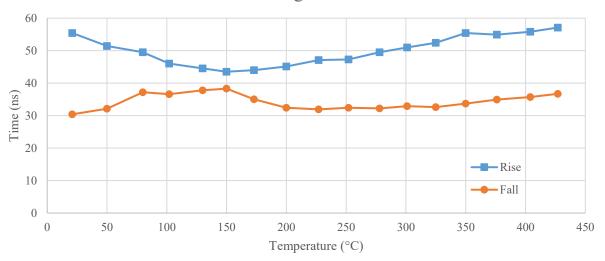

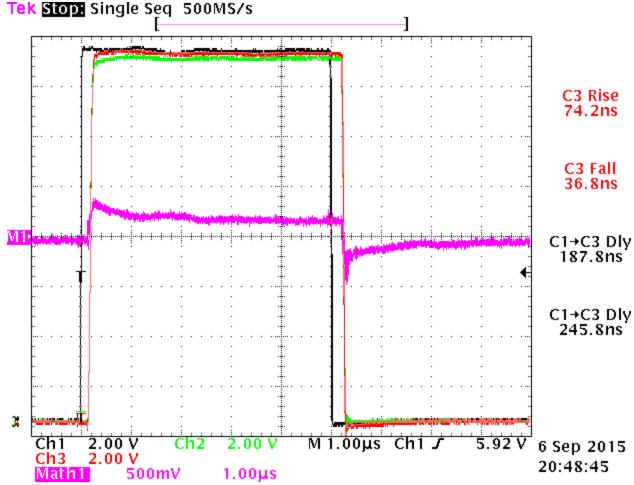

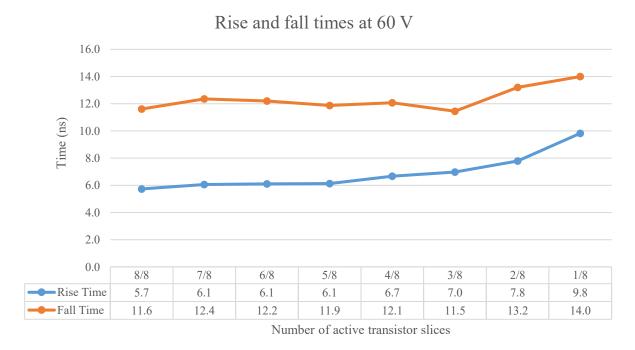

| Fig. 7 | 7.6 Rise and fall times driving a C2M0280120D MOSFET at 15 V by W31 R3C2 128                                                                                                                                                                                                                                                                                                                                                                     |

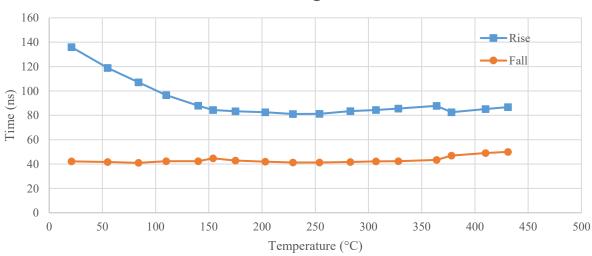

| Fig. 7 | 7.7 Rise and fall times driving C2M0280120D at minimum drive strength by W31 R3C2.                                                                                                                                                                                                                                                                                                                                                               |

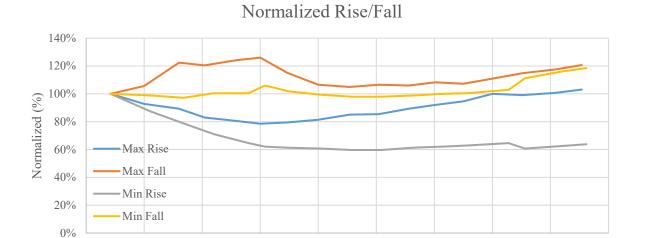

| Fig. 7 | 7.8 Comparison of rise and fall time variation over temperature while driving a C2M0280120D MOSFET by W31 R3C2. Times are from the minimum and maximum drive strengths, and are normalized to the value at 25 °C                                                                                                                                                                                                                                 |

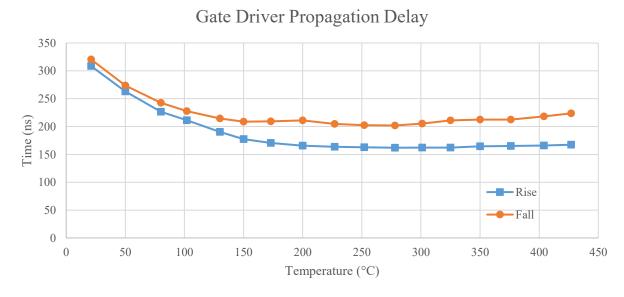

| Fig. 7 | 7.9 Propagation delay over temperature driving a C2M0280120D at 15 V by W31 R3C2.129                                                                                                                                                                                                                                                                                                                                                             |

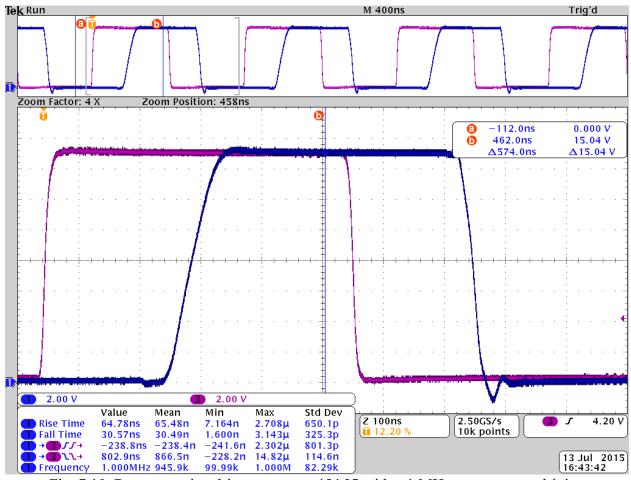

| Fig. 7 | 7.10. Representative driver output at 454 °C with a 1 MHz square wave driving C2M0280120D MOSFET by W31 R3C2                                                                                                                                                                                                                                                                                                                                     |

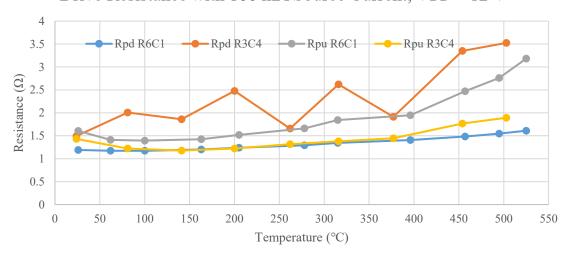

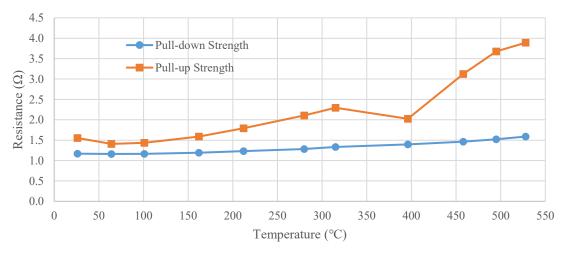

| Fig. 7 | 7.11. Gate driver output resistance over temperature, with a V <sub>DD</sub> of 12 V                                                                                                                                                                                                                                                                                                                                                             |

| Fig. 7 | 7.12. Gate driver output resistance of W31 R6C1 over temperature with a $V_{DD}$ of 15 V 132                                                                                                                                                                                                                                                                                                                                                     |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

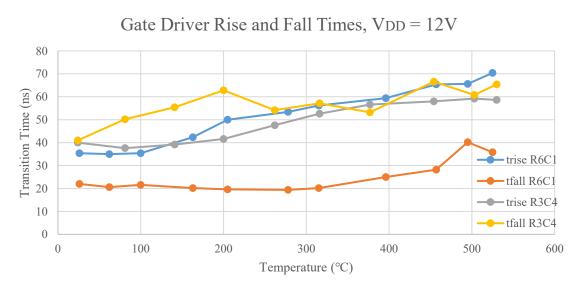

| Fig. | 7.13. Gate driver rise and fall times over temperature at a V <sub>DD</sub> of 12 V driving the gate of a C3M0065090D power MOSFET                                                                                                                                                                                                |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

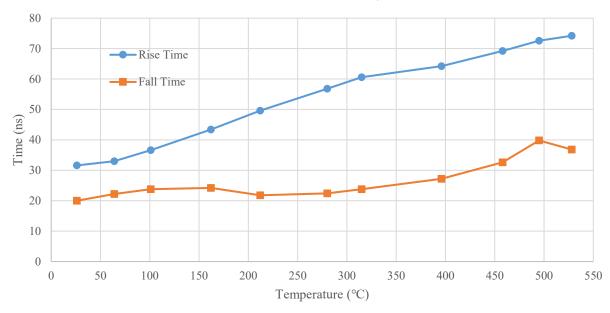

| Fig. | 7.14 Gate driver rise and fall times over temperature for die W31 R6C1 with $V_{DD}$ = 15 V driving the gate of a C3M0065090D power MOSFET                                                                                                                                                                                        |

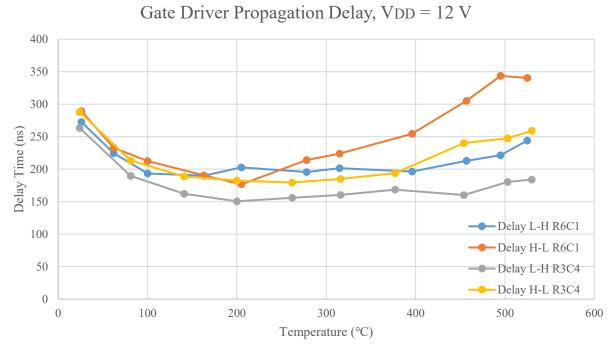

| Fig. | 7.15. Gate driver propagation delay with $V_{DD}$ = 12 V driving the gate of a C3M0065090D power MOSFET                                                                                                                                                                                                                           |

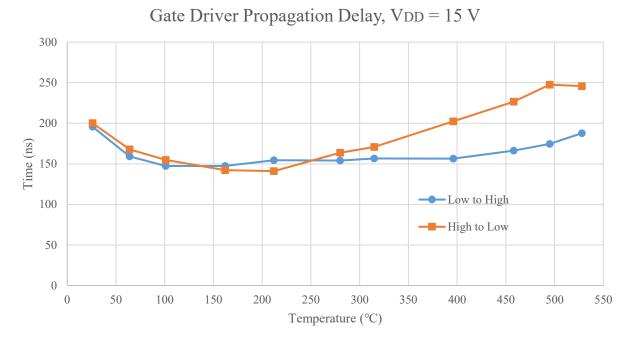

| Fig. | 7.16. Gate driver propagation delay of W31 R6C1, with $V_{DD}$ = 15 V driving the gate of a C3M0065090D power MOSFET                                                                                                                                                                                                              |

| Fig. | 7.17. Representative waveform R6C1, 528 °C, driving a C3M0065090D                                                                                                                                                                                                                                                                 |

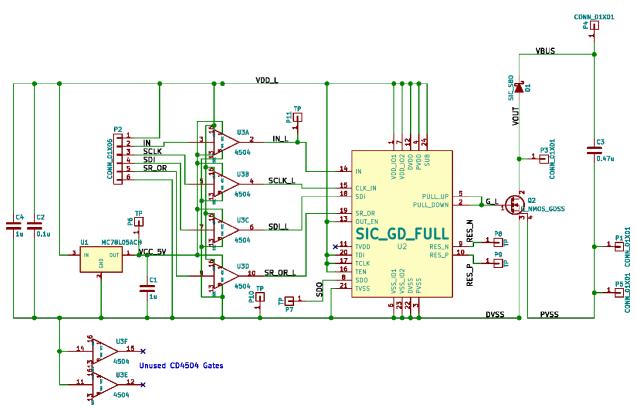

| Fig. | 7.18. Power module demonstration schematic                                                                                                                                                                                                                                                                                        |

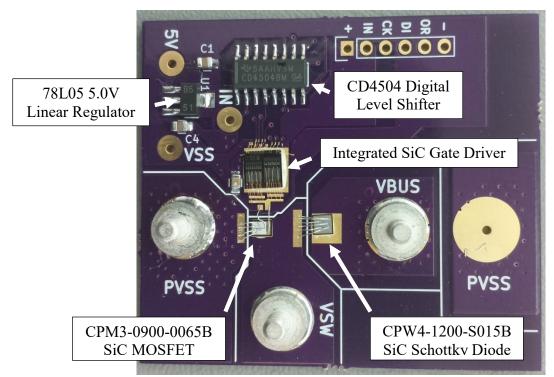

| Fig. | 7.19. Assembled board with all components soldered and wirebonded                                                                                                                                                                                                                                                                 |

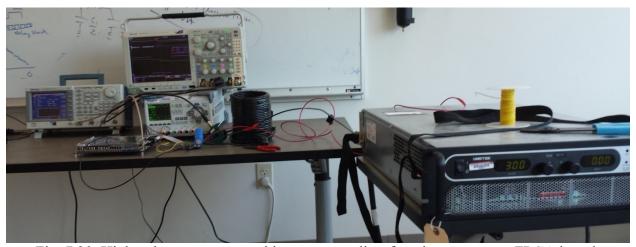

| Fig. | 7.20. High voltage test setup with power supplies, function generator, FPGA board, oscilloscope, and module                                                                                                                                                                                                                       |

| Fig. | 7.21. Oscilloscope probe connection for the drain-source voltage measurement. A wire loop holds the ground portion of the oscilloscope probe and makes the connection to PVSS, and a wire target is soldered to VSW for the tip contact. The probe is taped using electrical tape (not shown) for additional mechanical stability |

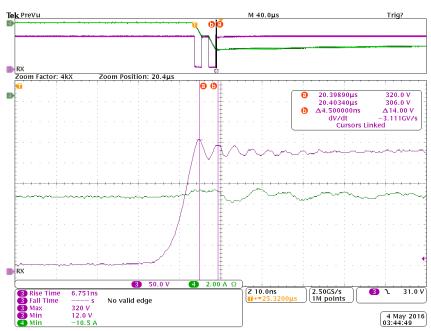

| Fig. | 7.22. Representative oscilloscope waveform demonstrating the 2 pulse test configuration and turn-off waveform at a $V_{BUS}$ of 300 V and an inductor current of 10 A                                                                                                                                                             |

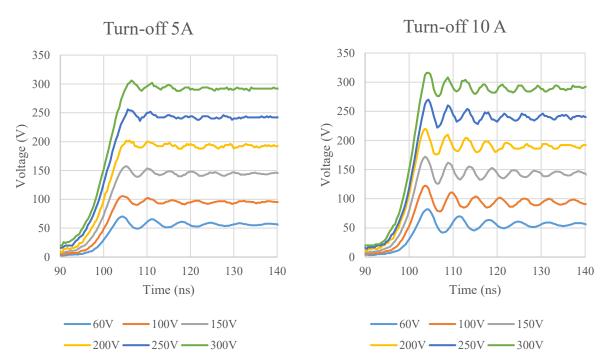

| Fig. | 7.23. Turn-off waveforms at a constant inductor current across multiple bus voltages.  Waveforms have been synchronized to the peak voltage after turn-off. The different load conditions are based on the inductor load current at the time of turn-off                                                                          |

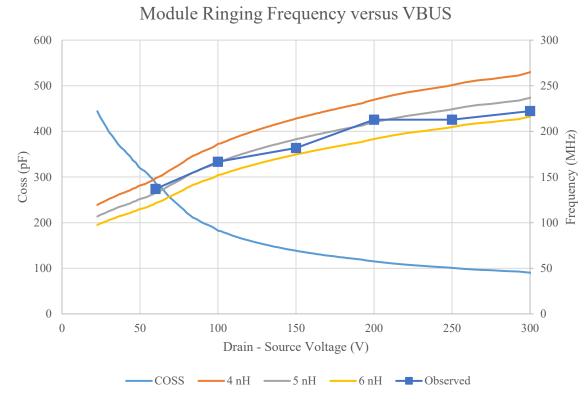

| Fig. | 7.24. A comparison of $C_{OSS}$ of the C3M0090065 device across applied drain voltage. By assuming a fixed inductance in a resonant circuit, a projected series resonant frequency can be projected as a function of $V_{DS}$ . The observed resonant frequency tracks between 4-6 nH loop inductance.                            |

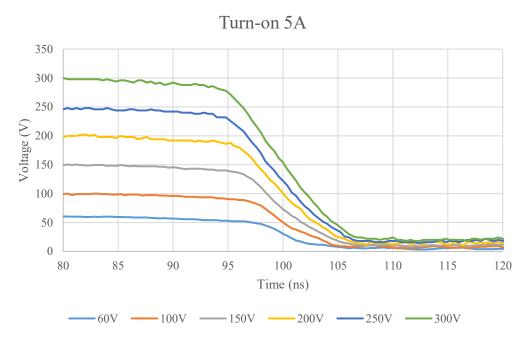

| Fig. | 7.25. Turn-on waveforms at a constant inductor current across multiple bus voltages. Waveforms have been synchronized to the 50 % transition point                                                                                                                                                                                |

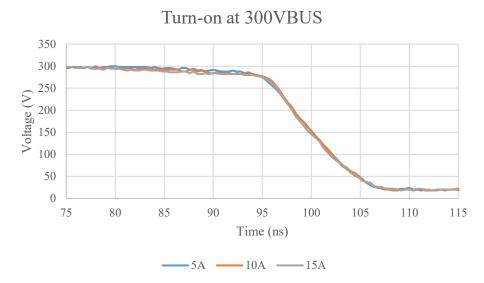

| Fig. | 7.26. Turn-on waveforms with varying inductor current and a 300 V DC bus voltage 147                                                                                                                                                                                                                                              |

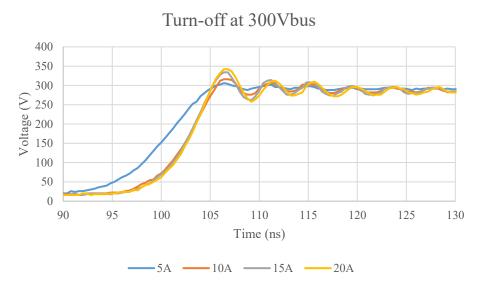

| Fig. | 7.27. Turn-off waveforms with varying inductor current and a 300 V DC bus voltage. Waveforms are roughly synchronized to the peak voltage after turn-off                                                                                                                                                                          |

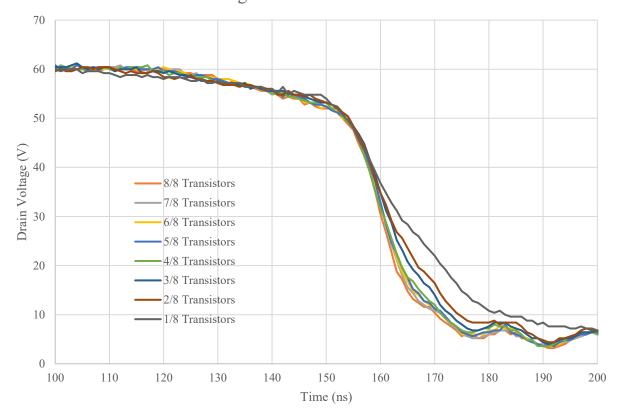

| Fig. | 7.28. Turn-on waveforms over various drive strengths. The load inductor current is 5 A with a nominal drain voltage of 60 V                                                                                                                                                                                                       |

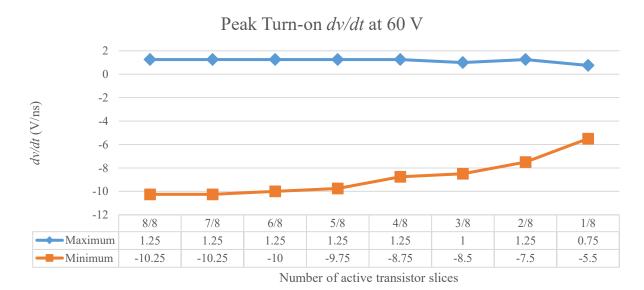

| Fig. 7.29. Peak turn-on dv/dt while varying the drive strength. Switching conditions were a VBUS of 60 V and an inductor current of 5 A. The maximum dv/dt corresponds to any ringing after turn-on, and is near the observed noise level in the system. The minimum dv/dt is the main slew rate during switching. |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Fig. 7.30. Rise and fall times as a function of drive strength. All situations are performed with bus voltage of 60 V. Turn-on corresponds to a 5 A load current and to a turn-off 10 A load current.                                                                                                              |          |

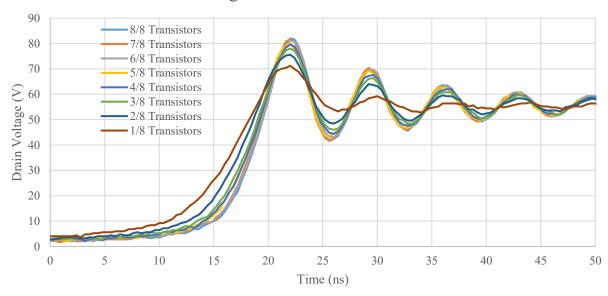

| Fig. 7.31. Turn-off waveforms over various drive strengths. The load inductor current is 10 A with a nominal drain voltage of 60 V.                                                                                                                                                                                |          |

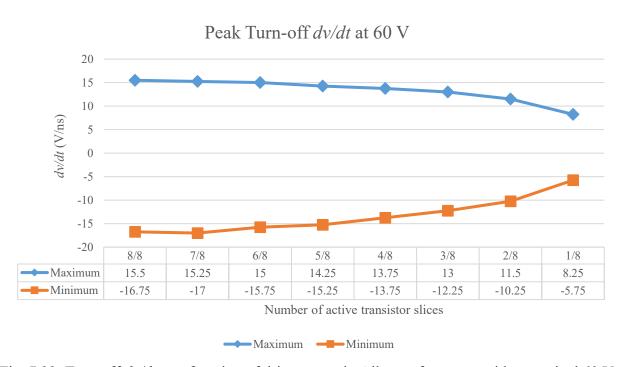

| Fig. 7.32. Turn-off dv/dt as a function of drive strength. All waveforms are with a nominal 60 bus voltage and 10 A load inductor current. The positive dv/dt corresponds to the main rising voltage from turn-off, and the negative dv/dt matches with the falling voltage aft the first drain voltage overshoot. | i<br>ter |

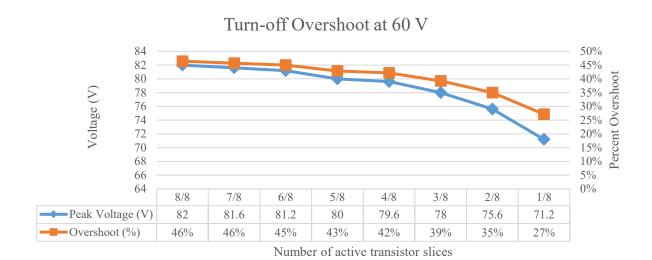

| Fig. 7.33. Comparison of overshoot voltages and percent overshoot as a function of drive strength.                                                                                                                                                                                                                 | 153      |

#### List of Acronyms and Abbreviations

AC Alternating Current AlN Aluminum Nitride

BJT Bipolar Junction Transistor

DBC Direct Bond Copper

DC Direct Current

DFT Design For Testability

DRC Design Rule Checks

DUT Device Under Test

ENIG Electroless Nickel Immersion Gold

ESD Electro Static Discharge

GaN Gallium Nitride

GUI Graphical User Interface

I/O Input / Output IC Integrated Circuit

IGBT Isolated Gate Bipolar Transistor

LVS Layout Versus Schematic

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NFET N-channel Field Effect Transistor

PEX Parasitic Extraction

PFET P-channel Field Effect Transistor

SiC Silicon Carbide

SJT Super Junction Transistor

SMU Source Measure Unit

SOI Silicon On Insulator

TSV Through-Silicon Via

ZCS Zero Current Switching

ZVS Zero Voltage Switching

#### 1 Introduction

For decades, silicon devices have dominated the semiconductor industry. Easy manufacturing techniques and constant improvements led to a well-developed ecosystem of devices ranging in capabilities from the latest digital processors to image sensors to power switching devices. Recently, an interest in wide bandgap combinations such as silicon carbide (SiC) and gallium nitride (GaN) have led to new devices with capabilities that exceed the performance of their silicon counterparts [1]. Researchers at the University of Arkansas have been working with SiC power devices as they were introduced and reached maturity [2]–[4]. Recent developments in SiC have allowed for more intensive integrated circuit (IC) design prospects. Combining the SiC power devices along with the SiC IC parts is a logical extension of the technology.

Theoretical performance benefits from changing a power device from a silicon technology to a silicon carbide device have turned into tangible benefits. The properties of silicon carbide allow for useful Schottky diodes at higher breakdown voltages than silicon, and power MOSFETs exist at 600 V ratings and above with lower on-resistance and lower capacitance than their silicon counterparts. The large bandgap provides new opportunities, as silicon carbide demonstrates capabilities at a temperature range beyond the reach of traditional silicon devices. With this performance extension made possible by silicon carbide power devices, control electronics are required that can operate in the same demanding environment. The most fundamental control circuit for a power device such as a MOSFET is a gate driver, a device that takes a logic-level signal and amplifies it to a strength capable of rapidly turning on and off a power MOSFET. Without a suitable gate driver circuit to safely control the power MOSFET, several of the performance benefits of silicon carbide devices cannot be realized. A

high-temperature capable gate drive circuit is an essential circuit for enabling high-temperature capable power electronics.

#### **Organization**

This dissertation is organized with overview material first. Chapter 2 describes general wide bandgap phenomena with a focus on silicon carbide. Direct applications of silicon carbide to power devices and integrated circuits are covered, with an emphasis on the silicon carbide integrated circuit process used in this work. Following that, in chapter 3, will be an overview of power electronics used in this work. General power electronics concepts are presented with particular attention paid to implications for gate drive electronics.

Chapters 4-6 deal with the design of the integrated silicon carbide gate driver. As the chronological development of the driver spans two manufacturing runs and interconnected development of separate features, a purely time-oriented organization does not make sense. Instead, the core driver development is described in chapter 4. The output transistors for the gate driver were optimized, and the description of that process is given in chapter 5. An evaluation of design-for-test (DFT) issues related to the design, and active decisions to improve testability in the design are provided in chapter 6, as well as the evaluation of the DFT system as implemented and the yield tests that resulted.

The in-circuit testing of the gate driver is given in chapter 7. This chapter covers the test configurations used, and the evaluation of the test setup. Multiple samples are tested under various configurations to successfully demonstrate the functionality of the gate driver. Finally, conclusions and future work are given in chapter 8. An appendix contains the code that was written in the course of completing this work.

#### 2 Silicon Carbide Overview

Silicon has dominated the semiconductor industry so thoroughly that all other semiconductors are judged relative to silicon to determine their merits and disadvantages. The most defining differentiation in new semiconductor materials has been the bandgap energy, E<sub>G</sub>. Silicon carbide and gallium nitride exhibit much higher bandgap energies of 3.26 eV and 3.39 eV, respectively, compared to the nominal 1.12 eV of silicon. These so-called wide bandgap semiconductors have several different intrinsic properties that are enumerated in Table 2.1 [5]. Silicon carbide has multiple crystal polytypes, such as 3C, 4H, and 6H, but the primary focus of recent research and production devices has been on 4H SiC.

Table 2.1 Material Properties of Silicon Carbide and Gallium Nitride compared to Silicon

| Parameter                                                               | Silicon    | 4H-SiC     | GaN               |

|-------------------------------------------------------------------------|------------|------------|-------------------|

| Bandgap Energy                                                          | 1.12 eV    | 3.26 eV    | 3.39 eV           |

| Critical Electric Field                                                 | 0.23       | 2.2        | 3.3               |

| Relative Permittivity                                                   | 11.8       | 9.7        | 9.0               |

| <b>Electron Mobility</b>                                                | 1400       | 950        | 800/1700(1)       |

| Intrinsic Carrier Concentration ni at                                   | 1e10       | 8e-9       | 2e-10             |

| 300K                                                                    |            |            |                   |

| Thermal Conductance                                                     | 1.5        | 3.8        | 1.3 (epi)         |

| Baliga FOM ε <sub>r</sub> * μ <sub>n</sub> *E <sub>C</sub> <sup>3</sup> | 2.01x10e20 | 9.81x10e22 | 5.50x10e23 (2DEG) |

<sup>(1)</sup> Significant difference between bulk and 2-dimension electron gas

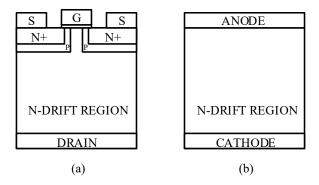

Considering the impacts of Table 2.1 on typical power devices, the first choice is to compare a theoretically optimal transistor from one material to another. For the purposes of power devices, it is useful to compare the ideal on-state resistance. Unipolar power devices, such as power MOSFETs and Schottky diodes, contain a drift region, shown in Fig. 2.1, that is responsible for blocking voltage when the device is not conducting. The length of this drift region dictates the voltage that the device is capable of blocking, and lower resistance is desirable for reducing device conduction loss. The specific resistance of the ideal drift region can

be characterized by Eq. (2.1)[6]. The ideal resistance of the drift region  $R_{on\text{-}ideal}$  is given as a function of the breakdown voltage BV, which increases with the square of the required voltage. In the denominator, the relative permittivity  $\epsilon_r$ , electron mobility  $\mu_n$ , and critical electric field  $E_C$  combine as material-specific constants that influence the device performance. The denominator products (2.2), also known as Baliga's figure of merit for power devices [6] is a useful number for comparing semiconductor materials. The lower mobility of silicon carbide in Table 2.1 is easily compensated by the large difference in critical electric field, especially as  $E_C$  is cubed in the equation. Comparing the Baliga figure of merit to silicon, silicon carbide has a score 491 times better, and gallium nitride scores 2,735 times better than the silicon baseline. This demonstrates the first potential improvement of wide bandgap devices: lower on-resistance at a given breakdown voltage.

Fig. 2.1. Unipolar power device structures: vertical power MOSFET structure (a) and power Schottky diode structure (b).

$$R_{on-ideal} = \frac{4BV^2}{\varepsilon_R \mu_n E_c^3} \tag{2.1}$$

$$Baliga\ FOM = \varepsilon_R \mu_n E_C^3 \tag{2.2}$$

The higher Baliga figure of merit score indicates that an ideal SiC device at a given breakdown voltage can be physically smaller in both area and drift region thickness than an equivalent silicon device. A smaller die area requires a smaller effective gate area, which reduces the amount of gate-source capacitance necessary with all other effects being equal. However, the increased critical electric field  $E_C$  decreases the required drift region thickness, bringing the gate physically closer to the drain contact and increasing the gate-drain capacitance of a vertical power MOSFET. This changes the inherent ratio of gate-source to gate-drain capacitance, which has implications that will be described further in chapter 3.

The other promise of wide bandgap materials is the potential for high-temperature operation. The intrinsic carrier concentration of a semiconductor should be lower than the doped carrier concentration for proper operation. As the absolute temperature, T, rises in a semiconductor material, the intrinsic carrier concentration  $n_i$  will also increase. If the intrinsic carrier concentration approaches or exceeds the doped carrier concentration, the semiconductor will not function as intended. The properties determining the intrinsic carrier concentration in a semiconductor are the bandgap energy of the material  $E_G$  and the state densities  $N_C$  and  $N_V$ . Equation (2.3) [6] shows the relationship between these material properties, absolute temperature T, and Boltzmann's constant (1.38 x  $10^{-23}$ J K<sup>-1</sup>). The state density in SiC is 44% of silicon, but the major difference in intrinsic carrier concentration over temperature comes from the higher bandgap voltage of silicon carbide.

$$n_i = \sqrt{N_C N_V} e^{-\frac{E_G}{2kT}} \tag{2.3}$$

In practice, standard silicon parts operate up to 125 °C, with enhanced power devices operating up to 175 °C. High temperature silicon-on-insulator (SOI) extends the useful range of silicon integrated circuits up to 250 °C, with research pushing the boundaries up to 450 °C [12]. Silicon carbide has a much greater operational temperature range in commercial and experimental devices, with commercially available power transistors rated for 210 °C [13], and experimental power converters operating at 250 °C [14]. On the integrated circuit front, silicon carbide has been shown to function above 400 °C [15], [16] and even higher than 500 °C. The higher temperature capability fuels forays into new circuit locations and situations, such as reduced cooling requirements, engine combustion chambers, and down-hole exploration [4]. The unique capabilities of silicon carbide are opening new realms for power electronics and electronics in general.

Another benefit demonstrated in Table 2.1 is the difference in thermal conductivity.

Silicon carbide has a higher coefficient of thermal conductivity that is useful for power devices.

This higher coefficient value allows for more efficient heat transfer from internal structures to external heat dissipation structures such as heat sinks, cooling base plates, or radiators. More efficient heat transfer also results in more uniform die temperatures, resulting in hot spots that are less pronounced compared to silicon.

#### **SiC in Power Electronics**

In particular, silicon carbide power devices lend themselves to high voltage operation.

Commercially available transistors range in maximum drain-source voltages of 600 V [13] to 1700 V [17]. Schottky barrier diodes are available in similar voltage ranges, and provide benefits over standard silicon PN junction diodes. Higher voltage devices exist, but have not reached widespread commercial distribution. Packaged single devices have current ratings up to 160 A

[18]. This range of voltages and currents lends itself to several high power applications traditionally performed by silicon insulated gate bipolar transistors (IGBT). Such applications include AC motor drives, power inverters [3], and electric car chargers [19]. The benefits of SiC transistors over typical IGBT applications are reduced device capacitance, instant turn-off instead of IGBT tail current, and better thermal conductivity. These benefits result in lower switching energy and lower energy loss.

## **High Temperature Gate Driver Research**

Prior work towards high temperature gate drive began with an SOI drive circuit with external SiC JFET for the output drive [9]. Later SOI efforts led to a driver and module rated for 225 °C [20]. Integrated SiC gate drive electronics began with an attempt at a CMOS driver in 6-H SiC [21]. Further work in a Cree NFET process realized the first SiC integrated gate driver [15], [22]. Another effort with an integrated NPN process resulted in a circuit capable of driving low-voltage drive SJT devices [23]. With the advent of a high temperature silicon carbide CMOS process [24], a SiC CMOS gate driver for SiC power MOSFETs is a logical extension.

#### **SiC Integrated Circuits**

Integrated circuits are another domain where interest in high-temperature electronics has fueled investigations into silicon carbide. Initial efforts began with the 6H polytype of silicon carbide due to availability, and small device count CMOS circuits were developed and tested [21], [25]–[27]. Further work has been done with NFET enhancement and depletion mode processes [15], [16], [28], JFETs [29], [30], and BJTs [23]. Of particular interest to power electronics design are gate driver circuits. With power devices capable of operating at elevated temperatures, companion circuitry such as transistor drivers are necessary for a complete high-temperature implementation. A seemingly ideal scenario of placing a SiC gate driver on the same

die as a power MOSFET was explored in [15], but the limitations imposed by the vertical power MOSFET processing made that an elusive goal.

Overall, SiC integrated circuits face limitations not experienced by contemporary silicon devices. While the electron mobility of SiC is lower than Si, the effective transistor transconductance is lower than expected [31]. One issue with doping SiC circuits is that high-energy ion implantation is the primary doping method [31]. The doping was performed before any growth of gate oxide to allow for the high temperature annealing. This eliminates the self-aligned gate benefits used in silicon, increasing the difficulty of manufacturing. The gate must also overlap the source and drain terminals more than a self-aligned process, resulting in higher gate-source and gate-drain capacitance. These disadvantages make lateral MOSFETs lower in performance compared to silicon counterparts.

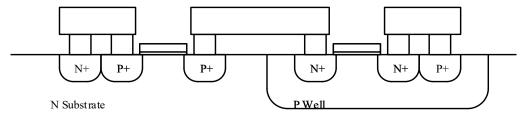

Recently, Raytheon Systems Limited in the UK has developed a CMOS integrated circuit process using 4H SiC [24], [32]. This process consists of an N-substrate for PFET devices with a P-type well for the NFETs. This is opposite of traditional silicon designs where the PFET parts are contained inside an N-type well. The minimum MOSFET channel length of the process is 1.2 µm, with two polysilicon layers for MOSFET gates and floating polysilicon-insulator-polysilicon capacitors. A single metal layer is available for interconnect, made of a refractory metal. A cross-section of a CMOS inverter is shown in Fig. 2.2.

Fig. 2.2. Example cross-section of a CMOS inverter in the Raytheon HiTSiC process

The University of Arkansas began work with the HiTSiC® process in late 2012 through the National Science Foundation Building Innovation Capacity program. Upon receiving samples from experimental runs, initial efforts began with measurements of transistor test structures with the intent of developing simulation models for the NFET and PFET devices. A process development kit (PDK) was created for Cadence Virtuoso, and simulation models were created in BSIM3v3 to represent the expected behavior of the first run. Devices were measured over temperature to create separate fixed-temperature models at 25 °C, 100 °C, 200 °C, and 275 °C. Layout verification tests in Calibre were included, and consisted of design rule checking (DRC), layout versus schematic (LVS), and parasitic extraction (PEX). The first tapeout was completed in August 2013, with wafers returning in February 2014. Models were updated to measured data from run 1, and upgraded to BSIM4 to allow greater flexibility adapting a silicon model to silicon carbide. Additional model corners were generated based on burn-in behavior observed, which resulted in two model values at 200 °C and 300 °C: a "fresh" version representing a new device, and the normal version exposed to several hours of bias at temperatures above 200 °C. Layout rules were updated following some yield issues, and minor updates in the PDK were made in time for the second tapeout in September 2014. Second run wafers returned in April 2015 for testing. Gate driver circuits were fabricated on both runs, with the final version on run 2 comprising the majority of the design information presented.

#### **Summary**

On paper, silicon carbide has many compelling properties that lead to a favorable comparison to silicon. A theoretical SiC power device has many benefits over a similar silicon device, though SiC manufacturing techniques have yet to approach the level of refinement in silicon systems. With demonstrated potential from early devices, work continues towards advancing power silicon carbide further. Recent developments in SiC integrated circuit process design have produced several methods for high-temperature electronics capable of operation from 400 °C to 600 °C with good performance. These recent developments have opened the door for new technologies and circuit implementations at high temperatures that are not possible with silicon. Power and integrated electronics now can push into new regimes where electronics dared not venture before.

#### 3 Power Electronics Switching

The application of silicon carbide power transistors and diodes requires a thorough understanding of the uses and limitations of transistors in power electronics applications. This chapter examines several switching concepts that are relevant to application circuits that use SiC power MOSFETs and gate drivers. Many concepts are universal at the broadest level of design, while a few are specific to MOSFETs or silicon carbide.

#### **Examination of switching topologies**

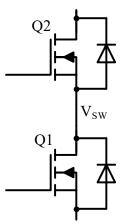

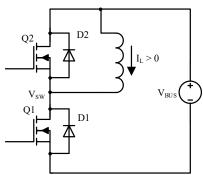

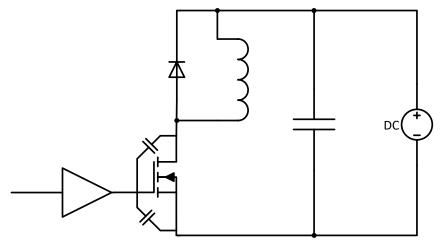

While not an exhaustive survey of switch-mode power converters, many power topologies can be derived from a circuit with two switches connected together, as in Fig. 3.1. Depending on the circuit functionality required, Q1 or Q2 may be omitted, though D1 and D2 functionally exist as discrete devices or as internal body diodes from the MOSFET. Frequently this structure is implemented in non-isolated converters such as buck, boost, and half-bridges. Multiple copies can be instantiated to form an H-bridge or a 3-phase inverter. Blocking is required in one voltage orientation, and diode conduction in the other direction is acceptable or necessary for proper operation. This diode operation can be augmented by activating the switch, and this is called synchronous switching. Switch mode converters add an inductive component to the V<sub>SW</sub> node functioning as an energy storage device or a filter, with the on-cycle of the switching charging the inductor through the active switch, and discharging with a path through a diode in the off-cycle. This switching configuration is commonly called a clamped inductive load, and has a specific set of system dynamics. Specifically, the inductor charges when one of the switches turns on, and turning off the switch will result in the output voltage rising to forward-bias the opposing diode.

Fig. 3.1. Fundamental switch orientation that can be expanded into various power electronics circuits by the addition of passive components.

Consider an idealized switch that does not turn off instantly, but instead rapidly and steadily increases the effective resistance across the two terminals. A MOSFET representation of such a circuit is shown in Fig. 3.2. At turn-off of the power device, the inductor forces the voltage of the output node to forward-bias the high-side diode. The current during the voltage swing is the full inductor current, and only decreases once the diode is forward-biased. The voltage across the switch rises to  $V_{BUS}$  while the current is at  $I_L$ , and the current decreases from  $I_L$  to 0 A while the voltage is at  $V_{BUS}$ . At turn-on, the exact process is reversed, with the switch increasing in current from 0 to  $I_L$  while at  $V_{BUS}$ , and then the voltage decreasing once the current in the transistor reaches  $I_L$ . This type of switching involves high peak power, is frequently called "hard switching", and is the sole type of switching examined here. Other techniques include zero voltage switching (ZVS) and zero current switching (ZCS) where resonant circuits are used to reduce the voltage or current across the switch to reduce switching losses.

Fig. 3.2. Clamped-inductive load circuit, with optional synchronous MOSFET Q2

MOSFET Clamped-inductive load switching

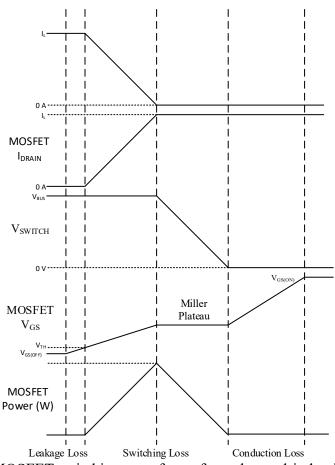

Further exploration of the clamped inductive load requires replacing the theoretical switches with real components. For this discussion, a MOSFET is used to explore the deeper complexities of a hard-switched clamped inductive load. Sample idealized waveforms are shown in Fig. 3.4. There are four distinct phases of turn-on in a clamped inductive load switching event, beginning with the initial change in MOSFET gate voltage. The gate voltage increases steadily from the resting "off" voltage to the point where the MOSFET begins to turn on at V<sub>TH</sub>. No other changes in the system are observed during this phase. Once the gate voltage rises above  $V_{TH}$ , the MOSFET begins to conduct current. While current starts flowing through the MOSFET, the drain voltage will remain constant. As long as the MOSFET drain current is less than the total inductor current, the remaining inductor current must have an additional path. In this circuit, the alternate path is through the diode in parallel with the inductor. As long as current is flowing through the diode, the drain voltage will stay at a diode drop above V<sub>BUS</sub>. The gate voltage will continue to increase consistently in this phase until the drain current is equal to the inductor current. Once the MOSFET has turned on enough to turn off the diode, the drain voltage can start changing, which leads to the next state.

Fig. 3.3. Clamped inductive load schematic showing location of C<sub>GD</sub> and C<sub>GS</sub>

Once the drain current is greater than the inductor current, the drain voltage falls. The falling drain voltage provides negative feedback from the output to the gate of the MOSFET through  $C_{GD}$ . In typical MOSFETs,  $C_{GD} \ll C_{GS}$ , which results in a gate charge depletion that is proportional to the dv/dt of  $V_{DS}$  and  $C_{GD}$ . This current flow steals the gate driver charging current from charging  $C_{GS}$ , and slows the rise in gate voltage. This flatter section in the  $V_{GS}$  waveform is commonly referred to as the Miller plateau. The Miller plateau lasts until  $V_{DS}$  reaches its steady-state value of approximately 0 V.

The final switching phase consists of the MOSFET gate voltage rising to the intended drive voltage after crossing the Miller plateau. This change in gate voltage is necessary to decrease the  $R_{DS(ON)}$  of the MOSFET to acceptable levels. The drain voltage may decrease slightly, but not at a rate that produces significant gate current. The end of this phase is marked by the gate voltage reaching  $V_{GS(ON)}$ .

MOSFET turn-off in a clamped-inductive system is functionally the same as turn-on, except the phases occur in reverse order. The gate driver will begin to decrease the gate voltage to the point where the MOSFET  $R_{DS(ON)}$  begins to increase significantly. This results in the drain voltage rising as the inductor forces  $V_{DS}$  higher to accept the total current. As the drain voltage

rises, current flows into the gate through  $C_{GD}$ , resulting in the negative feedback that causes the Miller plateau. The drain voltage rises until it reaches a voltage high enough to turn on the diode. The drain current then decreases to 0 A as the gate voltage decreases below  $V_{TH}$ , and then the gate voltage decreases to  $V_{GS(OFF)}$ .

Fig. 3.4. Example MOSFET switching waveforms for a clamped-inductive load turn-on.

It is important to note that the clamped-inductive switching configuration develops several peak conditions during switching that do not exist to the same extent in other common configurations. The clamped-inductive load guarantees that the MOSFET will experience maximum di/dt, maximum dV/dt, and maximum instantaneous power in a single controlled switching event. While several performance maximums will occur, the system will constrain

peak MOSFET drain currents, and the total energy dissipated is a function of the switching speed.

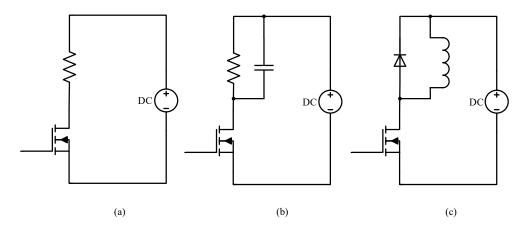

Consider three other switching loads illustrated in Fig. 3.5: a resistive load, a capacitive load, and an uncharged inductive load. For the simple resistive load (a), the drain voltage and drain current both begin to change simultaneously. Peak currents, as well as drain dV/dt are determined by how fast the MOSFET turns on and the value of  $R_{LOAD}$ . Adding a capacitor in parallel with the MOSFET, as in (b), will slow the drain fall-time and limit the peak dV/dt of the drain voltage. The drain current contains no inherent limiting mechanism, resulting in an unconstrained peak drain current that is dependent on the MOSFET switching speed and the size of the capacitance. The same magnitude of drain current as a clamped-inductive circuit may be observed during switching if the load capacitance is large enough. The total energy dissipated by the power MOSFET in this scenario is directly proportional to the capacitance of the load, and may exceed the safe operating area of the device. An uncharged inductor will result in a small decrease in peak drain dV/dt since the drain voltage will begin to change immediately after  $V_{GS}$  crosses  $V_{TH(ON)}$  instead of after the drain is charged to the load current. With no load current, the total switching energy dissipated will be less than the clamped inductive load case.

Fig. 3.5. Various load configurations for a single low-side switch. (a) shows a non-inductive resistive load, (b) shows a capacitance in parallel with the load, and (c) shows an inductive load with flyback diode

The drive strength of the gate driver is a constant influence in the switching speed. In all but the Miller plateau, the MOSFET gate behaves similar to a capacitor. As a result, the total switching time is primarily determined by the gate driver drive strength. Circuit conditions can also influence the switching rates. The magnitude of the inductor current determines how long it takes to transfer the current from the clamping diode to the power MOSFET. The magnitude of the drain voltage determines how long it takes for the MOSFET to cross the Miller plateau.

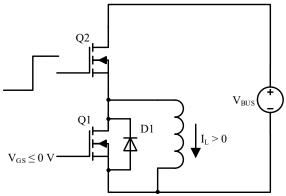

Fig. 3.6. Clamped inductive load configuration with charged inductor. D1 starts in conduction, and Q2 switches on, resulting in a fast rising  $V_{DS}$  on Q1. This rapid drain voltage rise has the potential to cause the  $V_{GS}$  of Q1 to rise above  $V_{TH(on)}$

Fig. 3.7. Gate charge and related capacitance parameters for a Cree C3M0065090J MOSFET. The gate charge parameters are linear in three separate regions as indicated by the dQ/dV line. Input capacitance is 813 pF in off region with a  $V_{DS}$  of 400 V and an  $I_{DS}$  of 20 A at 25 °C.[33]

While the normal switching criteria manage the switching characteristics of the MOSFET, another scenario must be considered with some topologies containing multiple transistors. Considering the system in Fig. 3.6, when the high-side MOSFET Q2 switches on, the drain voltage will experience a rapid voltage swing. Internal capacitances and resistances are shown in Fig. 3.8. This rapidly rising voltage will induce a current in the parasitic MOSFET capacitances  $C_{GS}$  and  $C_{GD}$ . Given a gate charge plot of  $Q_G$  vs.  $V_{GS}$  from a transistor datasheet, the estimated switching condition required to turn on Q1, assuming no gate drive, can be calculated. Fig. 3.7 shows the gate charge ( $Q_G$ ) versus  $V_{GS}$ , and the resulting gate capacitance from the datasheet of a Cree C3M0065090J.

The simplest gate drive stability criteria is determined by assuming that the transistor gate drive provides only the initial DC operating point, and has no impact on the gate voltage during switching. For the purposes of evaluation,  $C_{GD}$  is set to a constant value, and the drain voltage is assumed to transition at a fixed dV/dt. This allows an estimation of the current flowing into the

gate node (3.1). A common datasheet graph for a power MOSFET includes a gate voltage plot versus gate charge, which allows for an identification of how much gate charge is required to transition from  $V_{GS} = 0$  V to  $V_{GS(th)}$ . Using this value and our gate current from (3.1), the maximum time a gate current can be sustained before the gate voltage limit is reached is given in (3.2). This "safe" time can then be fed back to identify a safe  $V_{BUS}$  (3.3), and then substituting in (3.2) and (3.1) results in equation (3.4). This shows a relationship between the gate charge required to turn on the device with  $C_{GD}$ , and the assumed dV/dt term disappears.

$$I_{CGD} = C_{GD} \times \frac{dV_{DS}}{dt} \tag{3.1}$$

$$\frac{Q_{G(ON)}}{I_C} = t_{safe} \tag{3.2}$$

$$t_{safe} \times \frac{dV_{DS}}{dt} = V_{BUS_{safe}} \tag{3.3}$$

$$V_{BUS_{safe}} = \frac{dV_{DS}}{dt} \left( \frac{Q_{G(ON)}}{C_{GD}} \frac{dV_{DS}}{dt} \right) = \frac{Q_{G(ON)}}{C_{GD}}$$

(3.4)

Further refining of (3.4) can be accomplished by simplifying the  $Q_{G(ON)}$  term into a capacitance multiplied by the turn-on voltage. While this approximation requires a linear relationship between charge and voltage, examining the gate charge plot in Fig. 3.7 shows a linear Q/V behavior below the Miller plateau. This refinement allows replacement of  $Q_{G(ON)}$  in (3.5), and substitution into the previous safe voltage yields a safe bus voltage expressed as a ratio of gate capacitances and proportional to  $V_{GS(ON)}$  in (3.6). Perhaps more intuitively, this shows the circuit operating as a capacitive voltage divider. For systems where  $V_{GS}$  is driven to a voltage below 0 V when off, the safe bus voltage can be found with equation (3.7).

$$Q_{G(ON)} = C_{GS}V_{GS(on)} (3.5)$$

$$V_{BUS_{safe}} = \frac{C_{GS}}{C_{GD}} V_{GS(on)} \tag{3.6}$$

$$V_{BUS_{safe}} = \frac{C_{GS}}{C_{GD}} \left( V_{GS(on)} - V_{GS(off)} \right)$$

(3.7)

Table 3.1 Device properties from selected high voltage transistors

| Part Number                            | STF12N120K5[34] | APT37M100L[35] | IPW90R120C3[36] | CMF10120D[37] | C2M0160120D[38] | C3M0065090J[33] | SCT2160KE[39] | GA10JT12-247[40] | Units |