### University of Arkansas, Fayetteville ScholarWorks@UARK

Mechanical Engineering Undergraduate Honors Theses

Mechanical Engineering

5-2017

# System-Layout-Dependent Thermally Induced Solder Stress & Reliability Implications

Ange C. Iradukunda

Follow this and additional works at: http://scholarworks.uark.edu/meeguht

Part of the <u>Computer-Aided Engineering and Design Commons</u>, <u>Electro-Mechanical Systems</u> <u>Commons</u>, <u>Electronic Devices and Semiconductor Manufacturing Commons</u>, <u>Energy Systems</u> <u>Commons</u>, <u>Power and Energy Commons</u>, and the <u>Signal Processing Commons</u>

#### **Recommended** Citation

Iradukunda, Ange C., "System-Layout-Dependent Thermally Induced Solder Stress & Reliability Implications" (2017). *Mechanical Engineering Undergraduate Honors Theses*. 64. http://scholarworks.uark.edu/meeguht/64

This Thesis is brought to you for free and open access by the Mechanical Engineering at ScholarWorks@UARK. It has been accepted for inclusion in Mechanical Engineering Undergraduate Honors Theses by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

System-Layout-Dependent Thermally Induced Solder Stress & Reliability Implications

A thesis submitted in partial fulfilment of the honors requirements for the degree of Bachelor of Science in Mechanical Engineering

By

Ange Christian Iradukunda

### April 2017

University of Arkansas

### Abstract

Electronic flip chip assemblies consist of dissimilar component materials, which exhibit different CTE. Under thermal cyclic operating conditions, this CTE mismatch produces interfacial and interconnect stresses, which are highly dependent on system layout. In this paper, sensitivity analyses are performed using ANSYS FEA to establish how the proximity and arrangement of neighboring devices affect interconnect stress. Flip chip alignment modes ranging from edge-to-edge to corner-to-corner are studied. Results of these FEA studies, demonstrated that closely packing devices together has the effect of making them act as one. This results in a significant increase in the thermomechanical stresses induced on peripheral solder joints, heightening reliability risk. The sensitivity subsides gradually as device spacing increases, and eventually stops being a factor. 6mm is the threshold separation at which this occurs, in both edge-edge and corner-corner placement, for the system under analysis in this paper. Understanding the effect of system layout is instrumental for optimizing system design and improving reliability of power modules to meet the increasing power density needs.

# Table of Contents

| Abstract                                |

|-----------------------------------------|

| ntroduction                             |

| 1.1. Background of Flip Chip Technology |

| 1.2. Flip Chip Reliability              |

| Approach                                |

| 2.1 Modelling Solder Joints             |

| 2.1.1 Singularities                     |

| 2.1.2 Creep Behavior                    |

| 2.2 Anand's Viscoplasticity Model       |

| Results                                 |

| Conclusions                             |

| 21 References                           |

| Appendix A                              |

| Simulation Procedure                    |

| Appendix B                              |

| Raw data                                |

| Appendix C                              |

| Peak stress on Solder                   |

| Acknowledgements                        |

# Figures

| Figure 1. Front view of a flip chip attachment                                              | 6  |

|---------------------------------------------------------------------------------------------|----|

| Figure 2. CTE Mismatch stress induced by expansion in thermal conditions                    | 7  |

| Figure 3. Quarter-symmetric Flip chip model                                                 | 10 |

| Figure 4. From top left, edge-edge model, corner-corner model, and corner-edge model        | 10 |

| Figure 5. Singularity                                                                       | 12 |

| Figure 6. (a) Edge-edge model (b) Peripheral Solder Stress profile for 1 mm separation      | 16 |

| Figure 7. (a) Corner-corner model (b) Peripheral Solder Stress profile for 1 mm separation  | 17 |

| Figure 8. (a) Edge-corner model (b) Peripheral solder stress for edge-corner at 1mm spacing | 18 |

| Figure 9. Max solder stress vs. spacing for edge-edge and corner-corner placement           | 19 |

| Figure 10. ANSYS Plasticity models                                                          | 25 |

| Figure 11. ANSYS Large Deflection feature                                                   | 26 |

| Figure 12. Peak stress location (By Arie Smith)                                             | 29 |

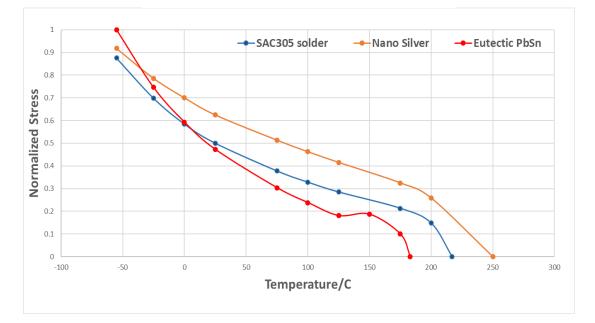

| Figure 13. Normalized stress vs Temp for different Solder Material (By Arie Smith)          | 29 |

# Tables

| Table 1. Material Properties at -55 °C                   | 11 |

|----------------------------------------------------------|----|

| Table 2. Anand's model constants for the solder material | 15 |

| Table 3. Corner-corner data                              | 27 |

| Table 4. Edge – edge data                                | 27 |

| Table 5. Corner-edge data                                |    |

# Introduction

#### 1.1. Background of Flip Chip Technology

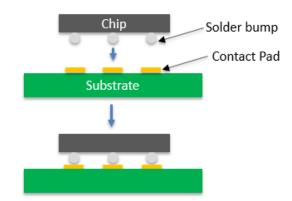

The ongoing trend of miniaturization and increased power density in power electronics has driven the growth of flip chip technology. Flip chip, also known as Controlled Collapsible Chip Connection (C4), describes a method of electrically and mechanically connecting the semiconductor die to the package substrate. Solder bumps are deposited on the die and the die is flipped over to align the solder with contact pads on the substrate. The bonding is then completed by reflowing the solder joints in a thermal oven [1-2]. Figure 1 below is an illustration of a simple flip chip package.

Figure 1. Front view of a flip chip attachment

Flip chip technology provides several advantages. Flip chip packages do not have the periphery limitations associated with wire bonding. The entire area under the chip can be utilized for input/output (I/O) connections, and devices can be moved closer together resulting in higher packaging density. The signal path between the die and the package is also minimized enabling better electrical performance [3].

Another major advantage of flip chip technology is 3D architecture. It provides the ability to stack chips or even heat removal devices, where wire bonds are limiting. However, these advantages add complexity to understanding and predicting the reliability of the packaging.

#### **1.2.** Flip Chip Reliability

Flip chip technology has enabled the development of power modules with increasing power capability, high current and high voltage resulting in significant power dissipations. This self-heating coupled with environmental conditions give rise to wide operating temperatures for flip chip packaging modules. In electric vehicle applications, for example, power modules are subjected to operating temperatures that can exceed 150°C when the car is running, or fall below 0°C when the car is stationary in cold weather conditions [4 - 5].

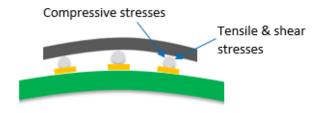

These thermal fluctuations represent a significant reliability risk for flip chip devices. Flip chip assemblies consist of dissimilar materials that have Coefficient of Thermal Expansion (CTE) mismatch. The organic substrates, on which flip chips are mounted to capitalize on their lower processing cost and lower dielectric constant, have much higher CTE (CTE  $\geq$  40 ppm/<sup>0</sup>C) compared to that of the die (CTE  $\approx$  3ppm/<sup>0</sup>C). Because of the CTE mismatch, layers of the flip chip expand and contract at different rates when temperature changes. This causes warpage and induces stress on interconnects and interfaces within the flip chip package [6].

Figure 2. CTE Mismatch stress induced by expansion in thermal conditions

Previous studies have shown that solder interconnects represent significant reliability risk from the induced stress because of thermomechanical fatigue. With continued thermal cycling, inelastic strains and cumulative fatigue damage develop in the solder joints, leading to crack formation, propagation and, ultimately, causing device failure. The failure of solder interconnects in electronic modules under conditions of thermomechanical fatigue is well-documented [10-15]. In order to mitigate solder fatigue and improve package reliability, it is essential to understand how variables such as flip chip device geometry, material composition, and layout of neighboring devices affect thermomechanical stresses on the interconnects. Several works have looked at the impact of device geometry as well as material [16, 17], but there is still a lack of understanding on the impact of system layout. The focus of this research is to study the influence of proximity and arrangement of adjacent flip chip devices on solder stress in order to optimize system layout for reliability.

## Approach

The objective of this approach is to investigate the impact of flip chip device layout on thermomechanical stresses that drive reliability failures in solder joints. Finite Element Analyses (FEA) using ANSYS® 17.1 is conducted to determine solder interconnect stress as a function of proximity for various placement modes of neighboring devices.

In this effort, the analyses are evaluated at a steady-state temperature profile, and the entire module is assumed to be isothermal. Concurrent FEM studies, conducted by Arie Smith, on the fatigue mechanisms of solder interconnects have shown that worst-case cold side exposure (-55 °C) drives the highest stress and reliability risk in solder interconnects (Appendix C, figure 15). Therefore, the layout studies were carried out at -55°C, where the effects of system layout are accentuated, because of the high stresses. The stress-free reference temperature in the analysis is defined as the reflow (or melting) temperature of the solder, for which the value is 188°C for 60/40 SnPb.

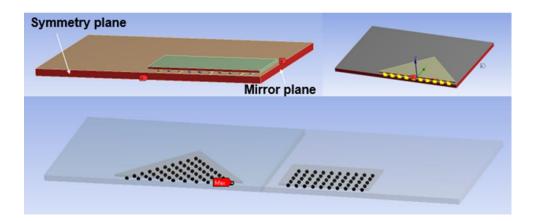

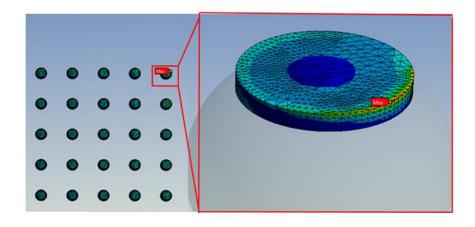

For the propose of the FEA simulations, a simplified flip chip device is used, taking advantage of symmetry to reduce computational time. The single device consists of a Silicon Carbide (SiC) die, 60/40 Tin-Lead (SnPb) solder, and FR-4 30% Glass filled Epoxy substrate. The dimensions of the full-sized device as well as an image of a quarter-symmetric model of the device are shown below:

- SiC chip: 10 x 10mm, thickness 0.235mm

- 60/40 SnPb Solder bumps: 0.23mm diameter, (10 x 10)

- FR4 Substrate SiC Chip Symmetry region 2 Symmetry region 1 Solder

- FR-4 Substrate: 30 x 30mm, thickness 0.635mm

Figure 3. Quarter-symmetric Flip chip model

The layout sensitivity analyses are performed for three different device placement modes, the first one being at zero-degree parallel placement (edge-edge), and the second one at 45-degree rotated alignment (corner-corner). The final placement mode combined the previous two for an edge-corner layout. Figure 4 below provides an illustration of these placement modes. For edgeedge and corner-corner arrangement, the flip chip devices were mirrored through the use of planes. This then enabled the variation of device separation by changing the distance from the chip to the mirror plane. Proximity was varied from 0.1mm to the full length of the die at 10mm.

Figure 4. From top left, edge-edge model, corner-corner model, and corner-edge model

The thermal structural analyses in ANSYS Mechanical require that properties be defined for each material within the flip chip Assembly. The thermal aspect of the analysis requires, at minimum, that the Thermal Coefficient of expansion (CTE) of each material be defined. The structural analysis, on the other hand, requires a young's modulus as well as Poisson's ratio. The materials of the simple flip chip used in our modeling fall into two categories: isotropic and orthotropic. The latter refers to materials whose properties vary in magnitude depending on the direction of measurement, whereas the former refers to materials with uniform properties in all directions. The SiC die and 60/40 SnPb solder fall into the isotropic category whereas FR-4 belongs to the orthotropic class. The nature of FR-4 as a composite material composed of woven fiberglass and epoxy resin gives rise to this variation in properties in different directions. A compilation of the material properties at -55°C is provided in table 1.

| Material   | CTE (C <sup>-1</sup> ) | Young's Modulus, E (MPa) | Poisson's Ratio |

|------------|------------------------|--------------------------|-----------------|

| SiC        | 4.00E-06               | 113500                   | 0.14            |

| 60/40 SnPb | 2.50E-05               | 34470                    | 0.316           |

| FR-4       | X 1.30E-05             | X 22604                  | XY 0.02         |

|            | Y 1.30E-05             | Y 22604                  | YZ 0.143        |

|            | Z 7.00E-05             | Z 6458                   | XZ 0.143        |

Table 1. Material Properties at -55 °C [18]

Other key elements that had to be incorporated in our models were displacement constraints. These were applied to get a statically determinate half-symmetry model, that is, there are no more constraints than would be required to prevent rigid-body motion (than would be required to keep the stiffness matrix non-singular).

#### 2.1 Modelling Solder Joints

#### 2.1.1 Singularities

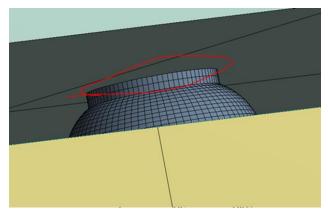

In modelling solder interconnects, two major challenges were encountered, the first being singularities. A singularity prevents convergence of stress results as mesh size is refined for accuracy. The stress keeps increasing to infinity, because it is acting in a region with zero-surface area. With regard to the solder bump, the singularity occurs at the infinitely sharp re-entrant edge shown below.

Figure 5. Singularity

There are several plasticity models that can be used to account for singularities. When an external load is applied to a part in FEA, the internal strain is the dependent variable. Displacement is the primary variable that ANSYS solves for, and the strain is the first spatial derivative of that. Without plasticity models, the stress is linearly proportional to the strain resulting in the boundless increase observed at a singularity. If, instead of a linear constitutive law, an actual stress-strain curve (from a tensile test, for example) is defined, an upper limit can be placed on the stress response at a singularity. In principle, a singularity still exists, but the stress reaction increases far more slowly with mesh refinement. So slowly, in fact, that the stress values converge. A 1%

convergence may not be achieved, but 4% is feasible. In ANSYS, the stress-strain curve is defined for the solder bump using plasticity models, for which several are available to choose from.

The stress converges, but not the strain. This is acceptable as long as the strain remains under the ultimate strain limit. Furthermore, the strain response can be prevented from increasing without bound by turning on 'Large Deflection' effects in ANSYS under analysis settings (Figure 11 in Appendix A). This allows the highly stressed region to relieve itself by updating the deformed geometry. This practice is common in the electronics packaging industry.

#### 2.1.2 Creep Behavior

The stress-strain behavior of solder is very complex. It is both temperature dependent and rate dependent. This time-dependent inelastic deformation is known as visco-plasticity or creep. Solder material typically have low melting temperatures, and as result operate at high homologous temperatures. Homologous temperature being the ratio of the operating temperature to the melting temperature of the solder in absolute degrees ( $T_H = T_o/T_m$ ). Assuming a range of -55°C to 150°C for operating conditions, 60/40 SnPb solder, which melts at 188°C, would have  $T_H$  between 0.47 and 0.92. Metallic materials generally experience creep as the dominant form of deformation at  $T_H > 0.4$  [7]. That means that even at the worst-case cold side temperature (-55°C), 60/40 SnPb solder would still exhibit considerable creep. Therefore, it is imperative to model solder as a rate and temperature-dependent visco-plastic material.

#### 2.2 Anand's Viscoplasticity Model

Anand's Model [19] is an example of a visco-plasticity model that accounts for singularities as well as creep deformation of solder interconnects. As mentioned above, solder material exhibit two types of inelastic deformation: time-independent or plastic, and time-dependent or creep. Anand differentiates between elastic and inelastic strain, but unifies the two forms of inelastic behavior into a single inelastic term. The term is expressed in terms of internal state variables [8]. Anand's model relies on two equations; a flow equation and an evolution equation, to model this deformation behavior of solder [8].

Flow Equation

$$\dot{\varepsilon}_{in} = A e^{\frac{-Q}{RT}} \left[ \sinh\left(\xi \frac{\sigma}{s}\right) \right]^{\frac{1}{m}} \tag{1}$$

**Evolution Equation**

$$\dot{s} = \left\{ h_o(|B|)^a \frac{B}{|B|} \right\} \dot{\varepsilon}_{in} \tag{2}$$

Where

$$s^* = \hat{s} \left[ \frac{\dot{\varepsilon}_{in}}{A} e^{\frac{Q}{RT}} \right]^n$$

And

$$B = 1 - \frac{s}{s^*}$$

The  $\dot{\varepsilon}_{in}$  is the inelastic strain rate and is the sum of time-dependent plastic strain rates and creep. The first part of the flow equation is an Arrhenius' Law-type term, which accounts for the dependence of the creep process on temperature. The hyperbolic sine term in the second part of the equation describes the stress dependence of the inelastic strain rate; the state variable is

included in this term. When it comes to solder behavior, the evolution equation mainly looks at the strain hardening effect through the hardening coefficient  $h_o$ [9].

Using the Anand model in ANSYS requires that all nine constants of the flow and evolution equations be inputted for the solder material. The constants are determined experimentally through creep testing. For 60/40 Sn-Pb, the material constants have been measured experimentally and documented in previous papers [18]. The table below contains the definitions of the constants as well as their corresponding values for 60/40 Sn-Pb.

| Parameter | Description                                                          | Units                      | 60/40 SnPb |

|-----------|----------------------------------------------------------------------|----------------------------|------------|

| So        | Initial value of deformation resistance                              | Stress (Pa, psi)           | 56.33      |

| Q/R       | Activation energy divided by universal gas constant                  | energy/volume<br>(kJ/mole) | 10830      |

| A         | Pre-exponential factor                                               | 1/time (1/S)               | 1.49E+07   |

| ξ         | Multiplier of stress                                                 | dimensionless              | 11         |

| m         | Strain rate sensitivity of stress                                    | dimensionless              | 0.303      |

| ho        | Hardening/softening constant                                         | Stress (Pa, psi)           | 2640.8     |

| Ŝ         | Coefficient for saturation value of deformation resistance           | Stress (Pa, psi)           | 80.42      |

| п         | Strain rate sensitivity of saturation value (deformation resistance) | dimensionless              | 0.0231     |

| а         | Strain rate sensitivity of hardening or softening                    | dimensionless<br>a>1       | 1.34       |

Table 2. Anand's model constants for the solder material

\*The procedure used to run the ANSYS analyses is outlined in Appendix A.

# Results

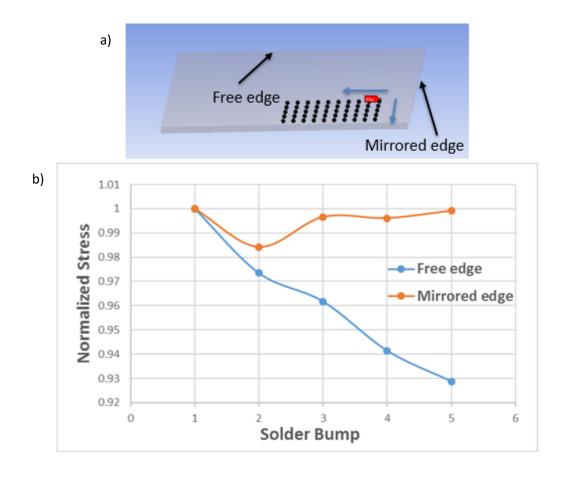

The impact of neighboring devices on solder interconnect stress for edge-edge placement at 1mm spacing is demonstrated in Figure 6. The stress profile is for peripheral solder joints along half the device for 1 mm edge-edge separation. The solder bumps lining the mirrored edge and free edge are ordered in the direction of the arrows shown in figure 6a.

Figure 6. (a) Edge-edge model (b) Peripheral Solder Stress profile for 1 mm separation

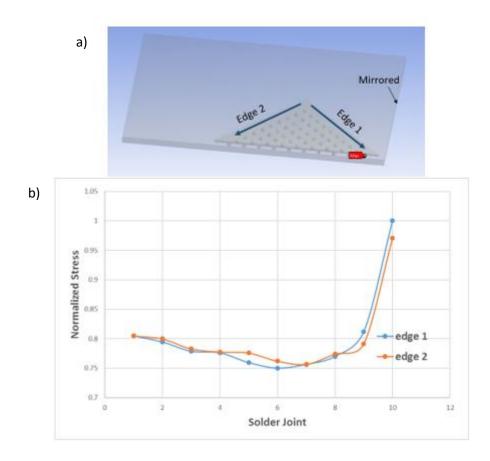

Figures 7 illustrates results for peripheral solders in corner-corner placement at the same separation distance of 1mm.

Figure 7. (a) Corner-corner model (b) Peripheral Solder Stress profile for 1 mm separation

Results in figures 6 and 7 show that thermomechanical stresses on solder interconnects are sensitive to neighboring devices. Both charts indicate that solder interconnects lining the mirrored edge experience higher stress than those lining the free edge. In particular, the corner solder joints, which are highlighted in figure 6a and 7a, experience the highest stress and, as a consequence, represent the highest reliability risk.

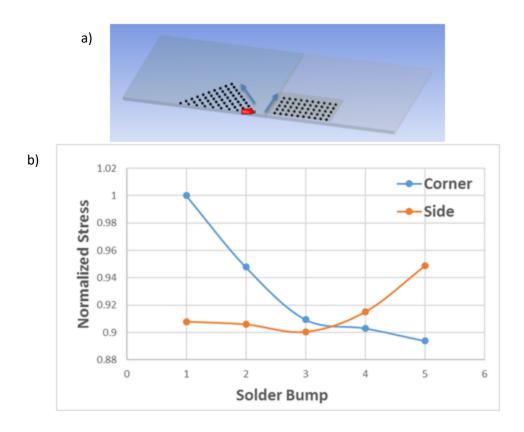

Figure 8 illustrates peripheral solder stress profile for edge-corner placement at 1mm spacing.

*Figure 8.* (a) *Edge-corner model* (b) *Peripheral solder stress for edge-corner at 1mm spacing*

From figure 8, it can be observed that corner alignment sees the most stress, particularly the corner solder joint (highlighted in red in figure 8a), furthest from the center of the package. However, for corner alignment, the stress decreases considerably as you move further away from the corner in the direction of the arrow in figure 8a. As for edge alignment, stress behavior is consistent with the trend observed in figure 6; peak stress occurs on solder joint furthest from the center of the package.

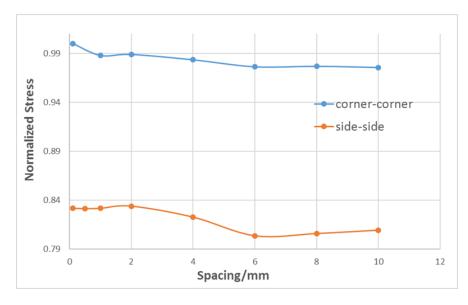

Figure 9 is a plot of peak solder stress as a function of proximity for corner-corner and edge-edge placement.

Figure 9. Max solder stress vs. spacing for edge-edge and corner-corner placement

Results in figure 9 demonstrate that corner-corner placement drives the highest stress and reliability risk. Furthermore, both curves in figure 9 have an asymptote indicating that mechanical stress sensitivity between solder joints of neighboring devices stops being a factor at roughly 6mm spacing.

The fluctuations in the results are a result of convergence issues. Convergence was around 5-10%, which is not adequate for the stress analyses in this experiment. A lower allowable change was not possible because of limited computing power at the time of running the simulations. However, collected data still show useful trends that can inform system layout for reliability. Additional placement modes will need to be studied to fully understand and optimize for layout sensitivity. Parallel alignment from 0-45 degree location and rotated alignment from 0-45 degree location are examples of other possible placement modes. The effects of the substrates' stiffness

(that is thickness and young's modulus) should also be investigated, since the stresses are transferred through the substrate. Additionally, understanding behavior under transient temperature conditions will also be an area of interest.

## Conclusions

Arrangement combined with proximity of neighboring devices result in variations of interconnect stress as well as the risk to failure, particularly on the peripheral solder joints lining adjacent edges of neighboring devices. Closely packing devices together has the effect of making the devices act as one. This has a considerable upward effect on the thermomechanical stresses induced on peripheral solder joints, heightening reliability risk. The sensitivity subsides gradually with increasing device spacing, and eventually stops being a factor. For the system under analysis in this paper, 6 mm is the minimum separation at which this occurs in both edge-edge and corner-corner placement. Results showed that the corner solder joint, furthest from the center of the package, in 45-degree rotated alignment (corner) experiences the highest stress and reliability risk.

This work is part of a project whose goal is to enable the prediction of reliability using FEA based on operating temperatures, material, and device/system layout in order to co-optimize power electronic system design for reliability and power density. In this effort, the FEA stress data will be correlated to experimental stress testing on test coupons and prototype modules. These experimental tests will provide empirical stress-based failure rates, which combined with the FEA stress states for different system designs, will provide a stress-based model for predicting reliability of power modules.

# References

- 1. R. R. Tummala, E. J. Rymaszewski, and A. G. Klopfenstein, Microelectronics Packaging Handbook. New York: Chapman & Hall, 1999.

- 2. J. H. Lau, Flip Chip Technologies. New York: McGraw Hill, 1995

- G. Pascariu, P. Cronin, and D. Crowley, "Next generation electronics packaging utilizing flip chip technology," in Electronics Manufacturing Technology Symposium, 2003. IEMT 2003. IEEE/CPMT/SEMI 28th International, July 2003, pp. 423–426.

- 4. JEDEC Spec. JESD47H.01: Stress-Test-Driven Qualification of Integrated Circuits; April 2011.

- 5. IPC-9701 Jan. 2002.

- Wu, T. Y., Y. Tsukada, and W. T. Chen. "Materials and mechanics issues in flip-chip organic packaging." *Electronic Components and Technology Conference*, 1996. Proceedings., 46th. IEEE, 1996.

- Zhang, Yuming, et al. "Low-temperature creep of SnPb and SnAgCu solder alloys and reliability prediction in electronic packaging modules." *Scripta Materialia* 68.8 (2013): 607-610.

- 8. Zhang, Q., and A. Dasgupta. "Constitutive properties and durability of lead-free solders." *Lead-Free Electronics, S. Ganesan and M. Pecht, Eds., Wiley-Interscience* (2003): 65-137.

- 9. Rodgers, B. R. Y. A. N., et al. "Experimental determination and finite element model validation of the Anand viscoplasticity model constants for SnAgCu." *Thermal, Mechanical and Multi-Physics Simulation and Experiments in Micro-Electronics and Micro-Systems, 2005. EuroSimE 2005. Proceedings of the 6th International Conference on.* IEEE, 2005.

- 10. E. R. Bangs and R. E. Beal, "Effect of Low Frequency Thermal Cycling on the Crack Susceptibility of Soldered Joints," Welding Res. Supp., Oct. 1975, pp. 377s-383s.

- 11. J. F. Burgess et al., "Solder Fatigue Problems in Power Packages," IEEE CHMT-7. 7 (1984) pp. 405- 410.

- E. Levine and J. Ordenez, "Analysis of Thermal Cycle Fatigue Damage in Microsocket Solder Joints," IEEE Trans. Components. Hybrids, and Manufacturing Tech. CHMT-4 (1981) pp 515-519.

- 13. Lau JH (1993) Thermal stress strain in microelectronics packaging. New York: Van NostrandReinhold

- 14. 2. Lau JH (1991) Solder joint reliability, theory and application. New York, Van Nostrand Reinhold

- 15. Lechovič, Emil, et al. "Solder joint reliability." *Materials Science and Technology* 9 (2009): 1-8.

- 16. Michaelides, Stelios, and Suresh K. Sitaraman. "Effect of material and geometry parameters on the thermo-mechanical reliability of flip-chip assemblies." *Thermal and Thermomechanical Phenomena in Electronic Systems, 1998. ITHERM'98. The Sixth Intersociety Conference on.* IEEE, 1998.

- 17. Frear, D. R. "The mechanical behavior of interconnect materials for electronic packaging." *JOM Journal of the Minerals, Metals and Materials Society* 48.5 (1996): 49-53.

- 18. Cheng, Z. N., et al. "Viscoplastic Anand model for solder alloys and its application." *Soldering & Surface Mount Technology* 12.2 (2000): 31-36.

- Anand, L., 1982, "Constitutive Equations for the Rate-Dependent Deformation of Metals at Elevated Temperatures", Journal of Engineering Materials and Technology, Transactions of the ASME, vol. 104, no. 1, pp. 12-17

# Appendix A Simulation Procedure

The analyses were performed using ANSYS 17.1 Mechanical. The simulation procedure was as follows:

- 1. Launch ANSYS Workbench

- 2. In the toolbox, locate and double click on Static Structural to insert a new analysis

- 3. In the new Static Structural Analysis, right click on the geometry cell and import geometry. SolidWorks model can be imported if saved as a STEP file

- 4. Double click on the Engineering data cell to input material properties from table 1

- a. Select Anand from the list of plasticity models

- b. Enter the Anand constants illustrated in table 2

- 5. Return to project homepage, and click on the model cell to open the Mechanical editor

- In Mechanical editor, assign materials to each part and specify a stress-free reference temperature for each body. This corresponds to the melting temperature of the solder material (188°C for 60/40 SnPb)

- If taking advantage of symmetry, right-click the geometry branch to add symmetry regions

- 8. On the mesh feature, ensure that mechanical mesh is selected

- 9. Right click the static structural branch to add:

- a. Temperature load (-55°C) and specify time steps

- b. Add displacement constraints. The model should be constrained from rotating

- Right click the solution branch to insert result objects such as Max von Mises Stress, Strain energy and deformation

23

- 11. Right-click on a result object to inset a convergence criteria

- a. In the convergence detail, enter an allowable change depending on the level of accuracy required

- 12. Select the solution branch and increase the number of allowable refinement loops form default value, which is set at one. This enables adaptive meshing iterations

- 13. Click on Analysis settings branch

- a. Activate large deflection to prevent boundless increase of strain on the solder joints (figure 11)

- b. Change solver type to Iterative to speed up the solution as refinement loops increase mesh size

- 14. Solve the model

\*To vary distance to the mirror plane, the parts were modified in design modeler with the help of the extrude feature

|                |                                                    | Juna | Jources   |                                       |           |

|----------------|----------------------------------------------------|------|-----------|---------------------------------------|-----------|

| e V            | Toolbox 🔻 🕂                                        | ×    | Outline o | of Schematic A2, B2: Engineering Data |           |

| 2              | Physical Properties                                | -    |           | A B                                   | C D       |

| Import         |                                                    |      | 1         | Contents of Engineering Data 🗦 🥥      | 🐼 Source  |

| box            | <ul> <li>Hyperelastic Experimental Data</li> </ul> |      | 2         | Material                              |           |

| Analys         | Hyperelastic     ■                                 |      | 3         | 🏷 Eutectic SnPb 💽                     | 🔲 📆 d     |

| Desi           |                                                    |      | 4         | 🇞 Fr4 💌                               | 🔲 📆 C     |

| Eige           | Plasticity                                         |      | 5         | 🗞 sic 🔽                               | 🔲 📆 c     |

| Eige           | Bilinear Isotropic Hardening                       |      |           | · · · · · · · · · · · · · · · · · · · | Fat       |

| Elect          | 🚰 Multilinear Isotropic Hardening                  |      |           |                                       |           |

| Expli          | 🚰 Bilinear Kinematic Hardening                     |      | 6         | 📎 Structural Steel 💌                  | AS        |

| Harn           | 🚰 Multilinear Kinematic Hardening                  |      |           |                                       | 8,        |

| Hydi           | 🚰 Chaboche Kinematic Hardening (ANSY               |      | *         | Click here to add a new               |           |

| Hydi           | 🚰 Anand Viscoplasticity                            |      |           | material                              |           |

| Mag            | 🚰 Gurson Model                                     |      |           |                                       |           |

| Mod            | 🎦 Johnson Cook Strength                            |      |           |                                       |           |

| Mod            | 😭 Cowper Symonds Strength                          |      | Propertie | es of Outline Row 6: Structural Steel |           |

| Mod            | 🚰 Steinberg Guinan Strength                        |      | riopera   |                                       | _         |

| Mod            | 🚰 Zerilli Armstrong Strength                       |      |           | A                                     | В         |

| Ranc           | Formulation                                        |      | 1         | Property                              | Value     |

| Resp           | 🚰 Chaboche Kinematic Hardening                     |      | 2         | 🔁 Density                             | 7850      |

| Rigio          |                                                    |      | 3         | Isotropic Secant Coefficient of       |           |

| Shap           |                                                    |      |           |                                       |           |

| Stati          |                                                    |      | 4         | Coefficient of Thermal<br>Expansion   | 1.2E-05   |

| Stati<br>Stati | ⊞ Gasket                                           |      |           | Zero-Thermal-Strain                   |           |

| Stea           |                                                    |      | 5         | Reference Temperature                 | 22        |

| Stea           |                                                    |      | 6         | 🗉 🄁 Isotropic Elasticity              |           |

| Stea           |                                                    |      | 12        | 🗉 📔 Alternating Stress Mean Stress    | 💷 Tabular |

| Ther           | Geomechanical     ■                                |      | 16        | 🗉 🎦 Strain-Life Parameters            |           |

Figure 10. ANSYS Plasticity models

| 9  | Т  | Dis                                   | placement                                  |       |

|----|----|---------------------------------------|--------------------------------------------|-------|

| 10 | 1  | ⊡…, 🙆 So                              |                                            |       |

| 11 |    |                                       | Solution Information                       |       |

| 12 |    |                                       | Equivalent Stress                          |       |

| 13 |    | · · · · · · · · · · · · · · · · · · · | Maximum Principal Stress                   |       |

|    |    | · · · · · · · · · · · · · · · · · · · | Maximum Shear Stress                       |       |

| 14 | 1  | · · · · · · · · · · · · · · · · · · · | Equivalent Stress u1                       |       |

| 15 |    | · · · · · · · · · · · · · · · · · · · | Equivalent Stress 2<br>Equivalent Stress 3 |       |

| 16 |    |                                       | Fourivalent Stress 4                       |       |

| 17 |    | Details of "Analysis Settin           |                                            |       |

| 18 | 15 | Step Controls                         |                                            |       |

| 19 |    | Number Of Steps                       | 1.                                         |       |

| 20 |    | Current Step Number                   | 1.                                         |       |

| 21 |    | Step End Time                         | 1. s                                       |       |

| 22 | 1  | Auto Time Stepping                    | Program Controlled                         |       |

| 23 |    | Solver Controls                       |                                            |       |

| 24 |    | Solver Type                           | Direct                                     | Ge    |

| 25 |    | Weak Springs                          | Off                                        | Grap  |

|    |    | Solver Pivot Checking                 | Program Controlled                         | oi al |

| 26 | 1  | Large Deflection                      | Off OA                                     |       |

| 27 |    | Inertia Relief                        |                                            |       |

| 28 |    | E Restart Controls                    |                                            |       |

| 29 | E  | • Nonlinear Controls                  |                                            |       |

| 30 | E  | • Output Controls                     |                                            |       |

| 21 | F  | Analysis Data Mana                    | anement                                    |       |

Figure 11. ANSYS Large Deflection feature

# Appendix B Raw data

### Table 3. Corner-corner data

| #04/04/  | 2017 23:38:0 | 7           |             |             |            |            |             |                         |          |

|----------|--------------|-------------|-------------|-------------|------------|------------|-------------|-------------------------|----------|

| #The pa  | irameters de | fined in th | e project a | are:        |            |            |             |                         |          |

| #        | P1 - Extru   | P2 - Equiv  | P3 - Equiv  | P4 - Strain | P5 - Equiv | P6 - Equiv | alent Stres | s <mark>4</mark> Maximu | im [MPa] |

| #        |              |             |             |             |            |            |             |                         |          |

| # The fo | llowing head | der line de | fines the n | ame of the  | e columns  | by referen | ce to the p | arameters.              |          |

| Name     | P1           | P2          | P3          | P4          | P5         | P6         |             |                         |          |

| DP 0     | 0.05         | 128.5776    | 94.12112    | 6.28E-05    | 94.12112   | 90.42891   |             |                         |          |

| DP 1     | 0.5          | 129.3392    | 92.97201    | 6.16E-05    | 92.97201   | 90.24223   |             |                         |          |

| DP 2     | 1            | 130.4823    | 93.06643    | 6.17E-05    | 93.06643   | 89.92102   |             |                         |          |

| DP 3     | 2            | 129.854     | 92.55281    | 6.14E-05    | 92.55281   | 90.01887   |             |                         |          |

| DP 4     | 3            | 129.3624    | 91.88613    | 6.22E-05    | 91.88613   | 90.0917    |             |                         |          |

| DP 5     | 4            | 129.4803    | 91.93232    | 6.29E-05    | 91.93232   | 90.06051   |             |                         |          |

| DP 6     | 5            | 130.5494    | 91.81896    | 6.28E-05    | 91.81896   | 89.56138   |             |                         |          |

| DP 7     | 6            | 130.0764    | 91.85539    | 6.13E-05    | 91.85539   | 90.30582   |             |                         |          |

Table 4. Edge – edge data

| # 04/05/ | 2017 01:04:0 | 1           |              |            |            |             |           |            |         |            |              |

|----------|--------------|-------------|--------------|------------|------------|-------------|-----------|------------|---------|------------|--------------|

| # The pa | arameters de | fined in th | ne project a | are:       |            |             |           |            | 1       |            |              |

| #        | P10 - Extru  | P5 - Equiv  | P6 - Equiv   | P7 - Equiv | P8 - Equiv | P9 - Strain | Energy    | Maximum    | Maximun | n Value Ov | er Time [mJ] |

| #        |              |             |              |            |            |             |           |            | 1       |            |              |

| # The fo | llowing head | der line de | fines the n  | ame of the | e columns  | by referen  | ce to the | e paramete | ers.    |            |              |

| Name     | P10          | P5          | P6           | P7         | P8         | P9          |           |            |         |            |              |

| DP 0     | 0.05         | 78.51965    | 119.8865     | 78.27162   | 77.10787   | 8.01E-05    |           |            |         |            |              |

| DP 1     | 0.25         | 78.58443    | 120.3474     | 78.25181   | 77.34028   | 8.00E-05    |           |            |         |            |              |

| DP 2     | 0.5          | 78.43825    | 120.2726     | 78.27879   | 77.24013   | 8.04E-05    |           |            |         |            |              |

| DP 3     | 1            | 79.00829    | 120.1728     | 78.48701   | 77.5388    | 8.11E-05    |           |            |         |            |              |

| DP 4     | 2            | 77.42922    | 117.6689     | 77.42922   | 76.43641   | 8.01E-05    |           |            |         |            |              |

| DP 5     | 3            | 75.62765    | 115.0934     | 75.62765   | 74.00674   | 7.32E-05    |           |            |         |            |              |

| DP 6     | 4            | 75.84599    | 115.201      | 75.84599   | 74.00357   | 7.37E-05    |           |            |         |            |              |

| DP 7     | 5            | 76.17182    | 115.5902     | 76.17182   | 74.03174   | 7.56E-05    |           |            |         |            |              |

| DP 8     | 6            | 78.13243    | 119.0887     | 78.13243   | 77.21689   | 7.91E-05    |           |            |         |            |              |

# Table 5. Corner-edge data

| #04/05/20  | 017 10:34:21 |               |               |               |                |                 |                |               |             |         |       |

|------------|--------------|---------------|---------------|---------------|----------------|-----------------|----------------|---------------|-------------|---------|-------|

| # The para | ameters defi | ned in the pr | oject are:    |               |                |                 |                |               |             |         |       |

| #          | P1 - Equival | P2 - Equival  | P3 - Equivale | P4 - Equivale | P5 - Strain Er | P6 - Equivalen  | P7 - Equivalen | P8 - Equivale | nt Stress 7 | Maximum | [MPa] |

| #          |              |               |               |               |                |                 |                |               |             |         |       |

| #The follo | owing heade  | r line define | s the name o  | f the columns | s by reference | e to the parame | eters.         |               |             |         |       |

| Name       | P1           | P2            | P3            | P4            | P5             | P6              | P7             | P8            |             |         |       |

| 0.1        | 113.638191   | 82.1375969    | 82.1375969    | 72.4696044    | 7.00E-05       | 76.54036856     | 75.79756506    | 73.06696135   |             |         |       |

| 0.25       | 113.933433   | 80.8044845    | 80.8044845    | 72.3484609    | 7.05E-05       | 76.89330326     | 76.09039533    | 73.09153712   |             |         |       |

| 0.5        | 116.442393   | 81.9945571    | 81.9945571    | 74.7977321    | 8.33E-05       | 78.75962352     | 77.58223439    | 74.39563393   |             |         |       |

| 1          | 113.394729   | 82.4530973    | 82.4530973    | 74.7746132    | 8.43973E-05    | 79.20769203     | 78.06529531    | 75.50410845   |             |         |       |

| 2          | 116.263113   | 82.310607     | 82.310607     | 74.64185      | 8.28E-05       | 79.63228591     | 77.36293634    | 74.77407171   |             |         |       |

| 3          | 114.216866   | 82.7722279    | 82.7722279    | 74.8440083    | 8.0148E-05     | 79.37304265     | 78.11215011    | 75.234786     |             |         |       |

| 4          | 112.093046   | 82.0848787    | 82.0166001    | 71.714662     | 7.93E-05       | 79.01857496     | 77.39982463    | 75.03843332   |             |         |       |

| 5          | 110.348586   | 82.9217534    | 82.9217534    | 72.7029149    | 8.18197E-05    | 79.56998248     | 77.83729388    | 75.58626381   |             |         |       |

|            |              |               |               |               |                |                 |                |               |             |         |       |

Appendix C Peak stress on Solder

Figure 12. Peak stress location (By Arie Smith)

Figure 13. Normalized stress vs Temp for different Solder Material (By Arie Smith)

# Acknowledgements

First and foremost, I would like to thank my advisor, Dr. Huitink, for his support and guidance throughout this process. Thank you for always being willing to help with my constant stream of questions. I want to express my appreciation to Dr. Wejinya for taking time from his busy schedule to serve on my defense committee; your support over the years has been invaluable.

In addition, I would like to thank my peers Arie Smith, Jonathan Treco and other members of the team for their support and friendship on this journey. It has not always been easy, but we carried each other forward. To the University of Arkansas and College of Engineering, thank you for the once-in-a-lifetime opportunity. I cannot finish without mentioning my family who support me in every way possible.