# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

8-2016

# Compact Modeling of SiC Insulated Gate Bipolar Transistors

Sonia Perez University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the <u>Electronic Devices and Semiconductor Manufacturing Commons</u>, and the <u>VLSI and</u> Circuits, Embedded and Hardware Systems Commons

#### Recommended Citation

Perez, Sonia, "Compact Modeling of SiC Insulated Gate Bipolar Transistors" (2016). *Theses and Dissertations*. 1708. http://scholarworks.uark.edu/etd/1708

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

## Compact Modeling of SiC Insulated Gate Bipolar Transistors

### A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Microelectronics-Photonics

by

Sonia Perez Henderson State University Bachelor of Science in Physics, 2008

> August 2016 University of Arkansas

| This thesis is approved for recommendation        | on to the Graduate Council.                  |  |

|---------------------------------------------------|----------------------------------------------|--|

|                                                   |                                              |  |

| Dr. H. Alan Mantooth<br>Thesis Director           |                                              |  |

| Adjunct Professor Tom Vrotsos<br>Committee Member | Dr. Anthony Matt Francis<br>Committee Member |  |

| Dr. Greg Salamo<br>Committee Member               | Dr. Rick Wise<br>Ex-Officio Member           |  |

| The following signatories attest that all soft | tware used in this thesis was legally licensed for use  |

|------------------------------------------------|---------------------------------------------------------|

| by Sonia Perez for research purposes and pr    | ublication.                                             |

| Ms. Sonia Perez, Student                       | Dr. H. Alan Mantooth, Thesis Director                   |

| This thesis was submitted to http://www.tur    | rnitin.com for plagiarism review by the TurnItIn        |

| company's software. The signatories have e     | examined the report on this thesis that was returned by |

| •                                              | e items highlighted by the software are incidental to   |

| common usage and are not plagiarized mate      | erial.                                                  |

Dr. H. Alan Mantooth, Thesis Director

Dr. Rick Wise, Program Director

#### **Abstract**

This thesis presents a unified (n-channel and p-channel) silicon/silicon carbide Insulated Gate Bipolar Transistor (IGBT) compact model in both MAST and Verilog-A formats. Initially, the existing MAST model mobility equations were updated using recently referenced silicon carbide (SiC) data. The updated MAST model was then verified for each device tested. Specifically, the updated MAST model was verified for the following IGBT devices and operation temperatures: n-channel silicon at 25 °C and at 125 °C; n-channel SiC at 25 °C and at 175 °C; and p-channel SiC at 150 °C and at 250 °C. Verification was performed through capacitance, DC output characteristics, and turn-off transient simulations. The validated MAST model was then translated into the Verilog-A language, and the Verilog-A model results were validated against the updated MAST model.

#### Acknowledgements

I would like to thank Dr. Matt Francis, Tom Vrotsos, Ramchandra Kotecha, Staci Brooks, Dr. Rick Wise, and Dr. Alan Mantooth for their time, patience, and knowledge throughout my education. I would not have gained this incredible amount of knowledge, perspective, and confidence without you all. I would also like to thank my family for supporting me throughout the extended time it took me to complete this work. I would also like to acknowledge Dr. Seuss' inspirational quotes from the beloved book "O the Places You'll Go."

This program is financially supported by the National Science Foundation under Grant No. DUE-0728636. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author and do not necessarily reflect the views of the National Science Foundation.

# **Dedication**

This thesis is dedicated to Kathy Kirk, Dr. Pam Mathews, Gordon Pearson, Tom Vrotsos, and my parents for their continued support throughout my journey to complete this degree.

# **Table of Contents**

| Chapter 1 | Introduction1                                    |

|-----------|--------------------------------------------------|

| 1.1       | SiC IGBT Impact on the Power Electronic Industry |

| 1.2       | SiC Material Properties                          |

| 1.3       | SiC IGBT State of the Art                        |

| 1.4       | Compact Device Modeling                          |

| 1.5       | Published IGBT Models                            |

| 1.6       | The Unified IGBT model 11                        |

| 1.7       | Maturing the Unified Model                       |

| Chapter 2 | IGBT Operation                                   |

| 2.1       | Operation States of the IGBT                     |

| 2.1.      | 1 Blocking State                                 |

| 2.1.      | 2 On-state                                       |

| 2.1.      | 3 Switching                                      |

| 2.2       | Variations in Structures of IGBTs                |

| Chapter 3 | The 2012 Unified IGBT Model                      |

| 3.1       | Introduction                                     |

| 3.2       | Structure                                        |

| 3.3       | MOSFET Portion                                   |

| 3.4       | BJT Portion                                      |

| 3.4.      | 1 Approximations                                 |

| 3.4.      | 2 Base Charge                                    |

| 3.4.      | 3 Collector to Emitter Capacitance               |

| 3.4.       | 4 Breakdown Voltage and Multiplication Factor           | 32 |

|------------|---------------------------------------------------------|----|

| 3.5        | MAST Formulation                                        | 33 |

| 3.6        | Temperature Scaling                                     | 36 |

| Chapter 4  | Updating the Unified IGBT Model                         | 38 |

| 4.1        | Equations and Temperature Dependence                    | 38 |

| 4.1.       | 1 Mobility Model                                        | 38 |

| 4.1.       | 2 Updated SiC Equations                                 | 39 |

| 4.1.       | 3 Temperature dependence of mobility                    | 40 |

| 4.2        | Simulation Analysis                                     | 41 |

| 4.2.       | 1 Parameter Extraction                                  | 41 |

| 4.2.       | 2 Implementing Debugging Parameters and Tools           | 46 |

| Chapter 5  | Creating a Verilog-A Compact model through Paragon 2.0  | 49 |

| 5.1        | Necessity of a Verilog-A Compact models                 | 49 |

| 5.2        | Utilizing Paragon 2.0                                   | 50 |

| 5.3        | The Verilog-A IGBT Model through Paragon 2.0 tool views | 53 |

| Chapter 6  | Results                                                 | 56 |

| 6.1        | Si IGBT Results                                         | 56 |

| 6.2        | SiC n-channel IGBT Results                              | 63 |

| 6.3        | SiC p-channel IGBT Results                              | 67 |

| 6.4        | Verilog-A Si/SiC IGBT Model Validation                  | 71 |

| Chapter 7  | Conclusion                                              | 74 |

| References |                                                         | 78 |

| Appendix A | A Si/SiC IGBT Model Equations and Parameters            | 83 |

| A.1        | Si/SiC IGBT multiplication factor equation                                           | 83 |

|------------|--------------------------------------------------------------------------------------|----|

| A.2        | Model Parameters applicable to both MAST and Verilog-A                               | 83 |

| A.3        | Model Parameters Applicable to MAST model only                                       | 84 |

| A.4        | Model Parameters Applicable to Verilog-A model only                                  | 84 |

| A.5        | Model Parameter Notes                                                                | 84 |

| Appendix B | Description of Research for Popular Publication                                      | 85 |

| Appendix C | Executive Summary of Newly Created Intellectual Property                             | 88 |

| Appendix D | Potential Patent and Commercialization Aspects of listed Intellectual Property Items | 89 |

| Appendix E | Broader Impact of Research                                                           | 90 |

| E.1        | Applicability of Research Methods to Other Problems                                  | 90 |

| E.2        | Impact of Research Results on U.S. and Global Society                                | 91 |

| E.3        | Impact of Research Results on the Environment                                        | 93 |

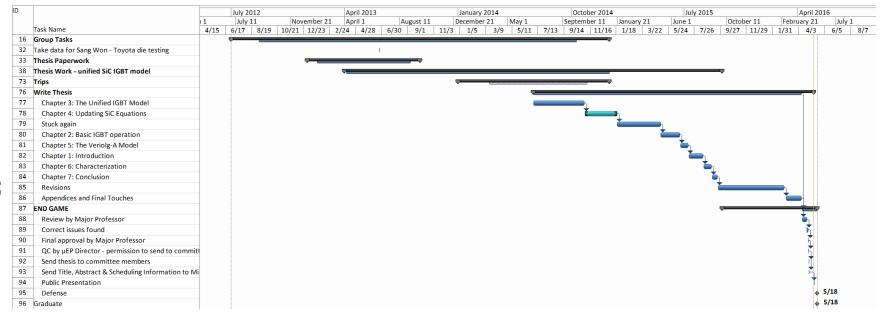

| Appendix F | Microsoft Project for MS MicroEP Degree                                              | 95 |

| Appendix G | Identification of All Software Used in Research and Thesis Generation                | 96 |

| Appendix H | All Publications Published, Submitted and Planned                                    | 97 |

|            |                                                                                      |    |

# **List of Figures**

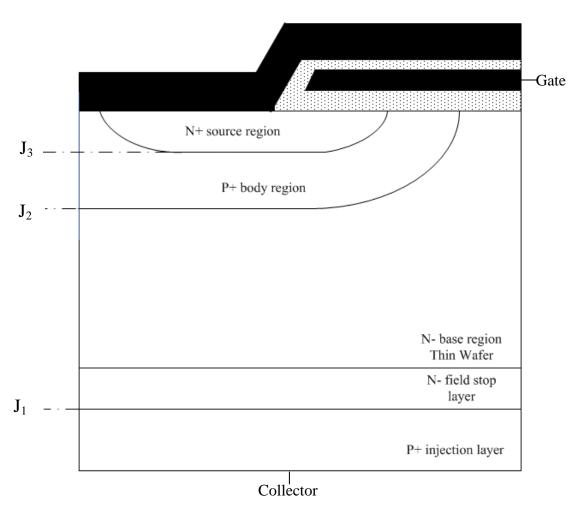

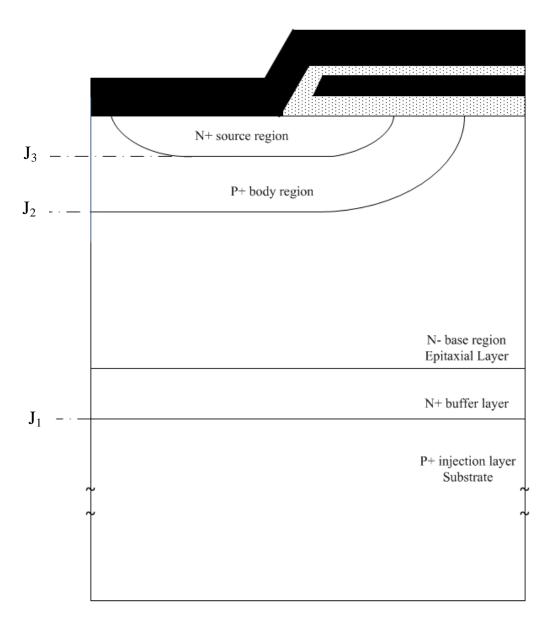

| Figure 1.1               | Cross section of an n-channel IGBT.                                                                                                                                                                                   | 4    |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

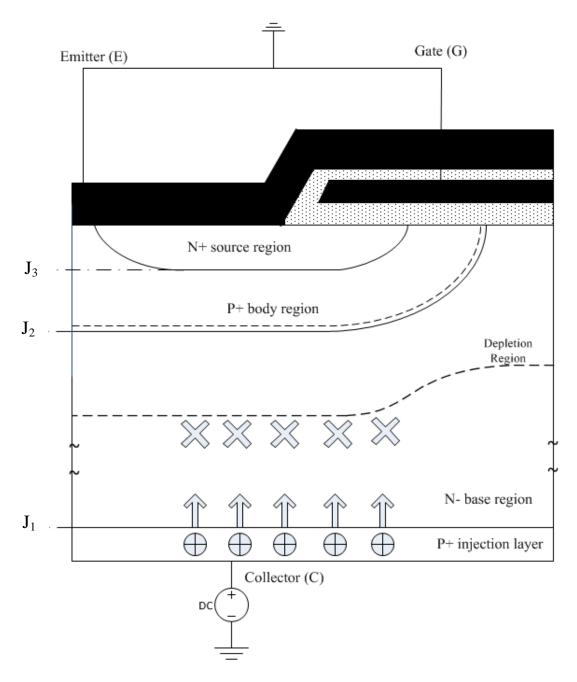

|                          | NPT n-channel IGBT cross section with a representation of the device in a blocking condition. The dashed lines are referring to the depletion regions, the bresent that the depletion layer "stops" the hole current. | . 14 |

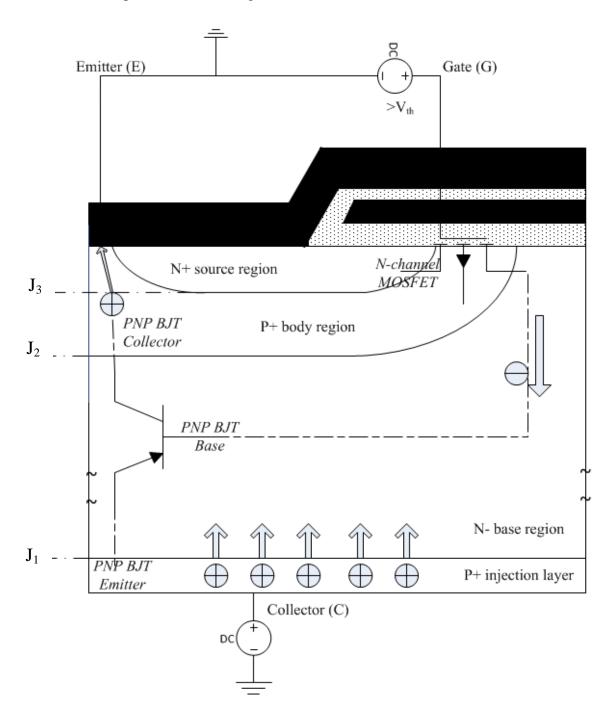

| Figure 2.2<br>carriers d | NPT n-channel IGBT cross section with an overlay representing the flow of luring the on-state                                                                                                                         | . 16 |

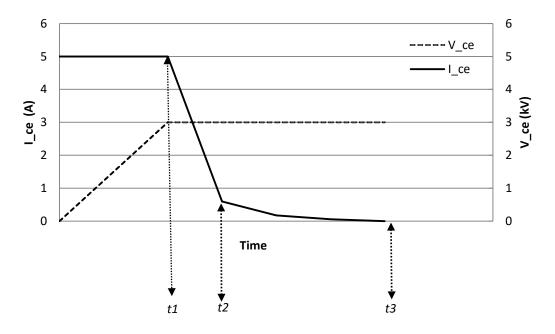

| Figure 2.3               | Example of an inductive load turn-off response.                                                                                                                                                                       | . 17 |

| Figure 2.4               | n-channel PT IGBT cross section                                                                                                                                                                                       | . 20 |

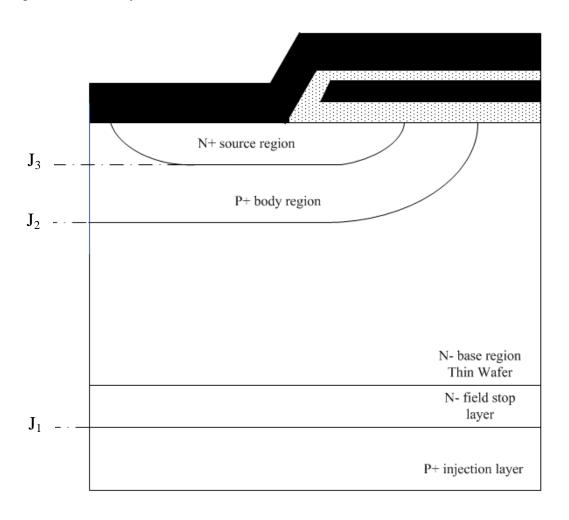

| Figure 2.5               | n-channel FS IGBT cross section                                                                                                                                                                                       | . 21 |

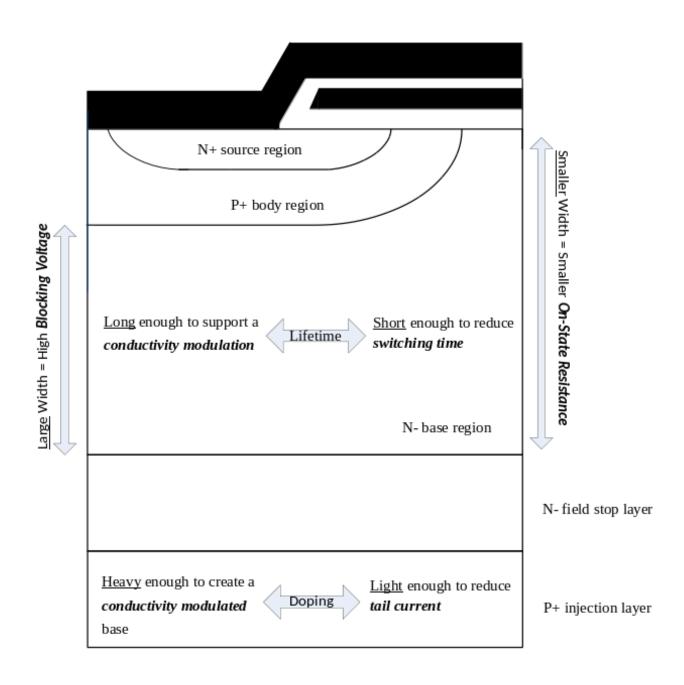

| Figure 2.6               | Trade-offs of designing an IGBT by layer                                                                                                                                                                              | . 23 |

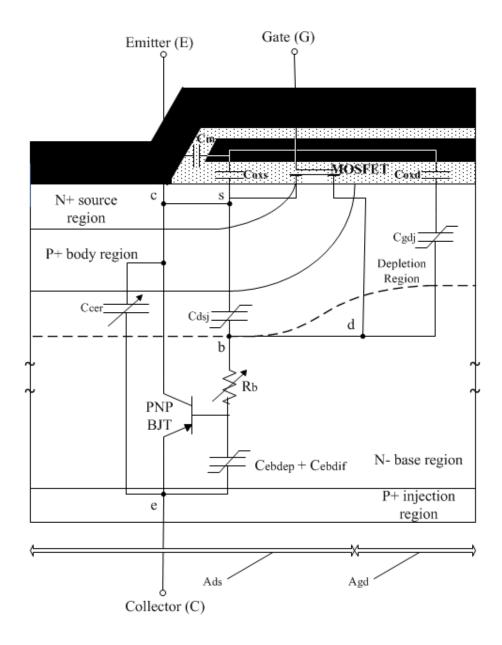

| Figure 3.1<br>model [1   | Cross-section of a NPT IGBT overlaid with an equivalent circuit of the IGBT 6]                                                                                                                                        | . 26 |

|                          | Above is a capture of the equations section within the MAST IGBT model. It ted between n and p-channel operations, with currents defined accordingly each node listed                                                 | . 35 |

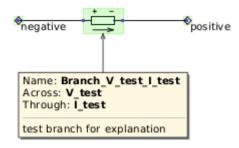

| Figure 5.1 comment       | A Branch with both positive and negative nodes labeled as "test" and with a of "test branch for explanation."                                                                                                         | . 50 |

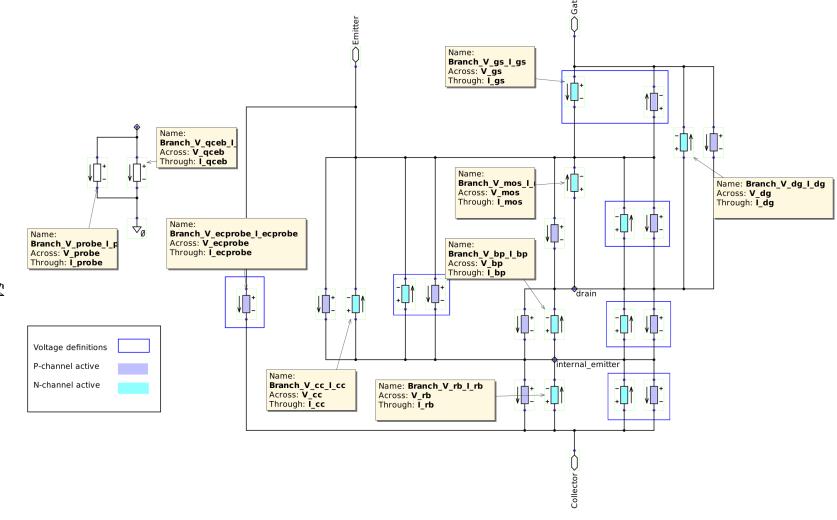

| Figure 5.2<br>and Colle  | Topology of IGBT model within Paragon 2.0, with terminals Gate, Emitter, ector                                                                                                                                        | 54   |

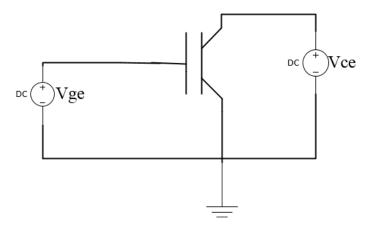

| Figure 6.1               | DC Testbench. Vce is swept and Vge is stepped at voltages described in text                                                                                                                                           | . 57 |

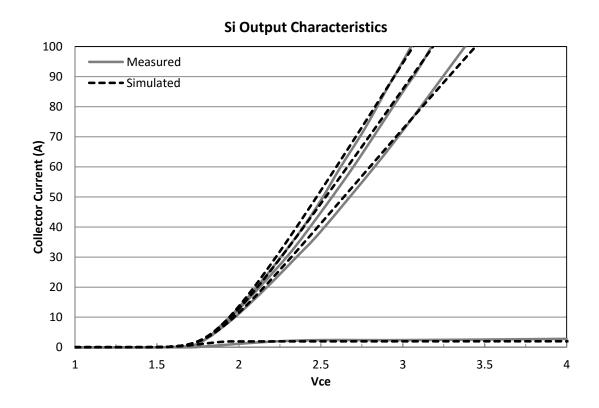

| Figure 6.2               | Si IGBT Output Characteristics at 25 °C                                                                                                                                                                               | . 57 |

| Figure 6.3               | Si IGBT Input Characteristics at 25 °C                                                                                                                                                                                | . 58 |

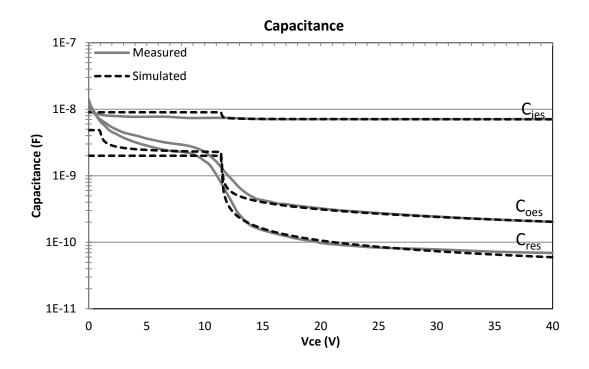

| Figure 6.4               | Si IGBT Capacitance Characteristics                                                                                                                                                                                   | . 59 |

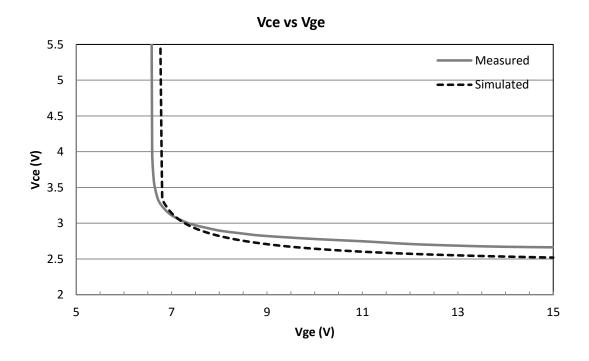

| Figure 6.5               | Si IGBT on-state voltage versus the gate voltage                                                                                                                                                                      | . 60 |

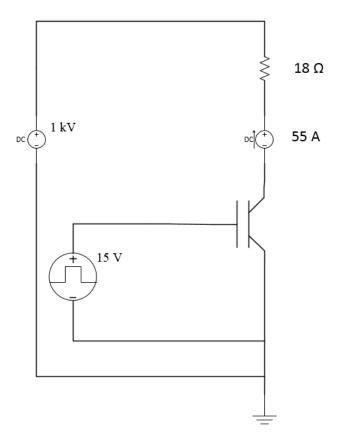

| Figure 6.6               | Resistive load testbench to simulate the Si gate charge plot                                                                                                                                                          | . 61 |

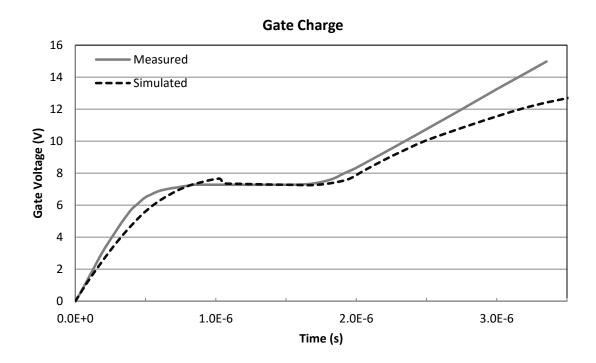

| Figure 6.7               | Si IGBT gate charge                                                                                                                                                                                                   | . 62 |

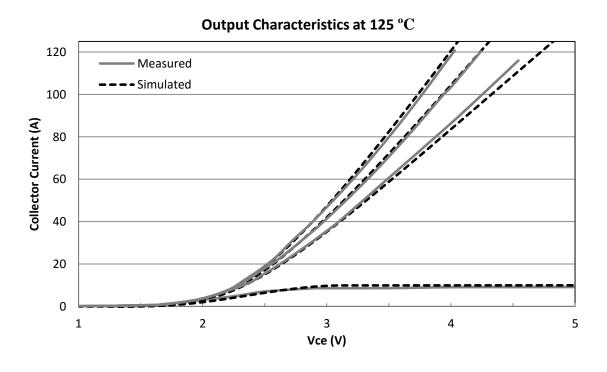

| Figure 6.8  | Si IGBT output characteristics at 125 °C                                       | 62 |

|-------------|--------------------------------------------------------------------------------|----|

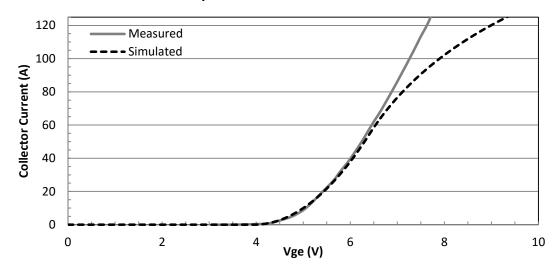

| Figure 6.9  | Si IGBT input characteristics at 125 °C                                        | 63 |

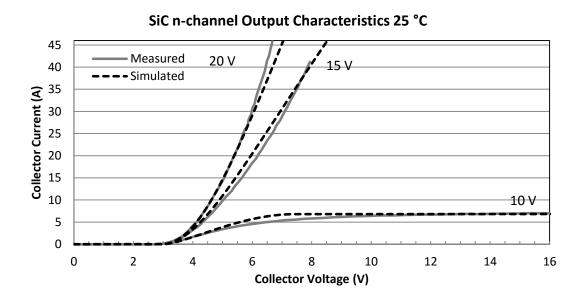

| Figure 6.10 | SiC n-channel IGBT output characteristics at room temperature                  | 63 |

| Figure 6.11 | SiC n-channel IGBT clamped-inductive load testbench                            | 64 |

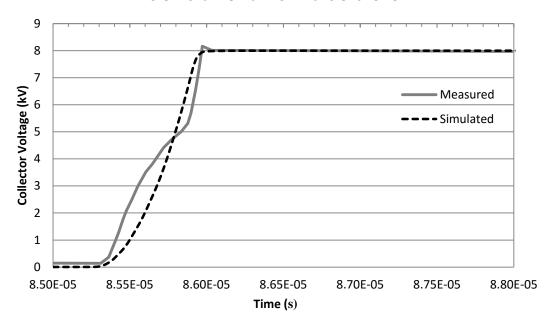

| Figure 6.12 | SiC n-channel turn-off voltage characteristics at 25 °C                        | 65 |

| Figure 6.13 | SiC n-channel turn-off current characteristics at 25 °C                        | 65 |

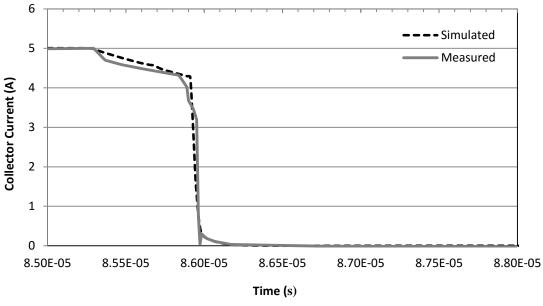

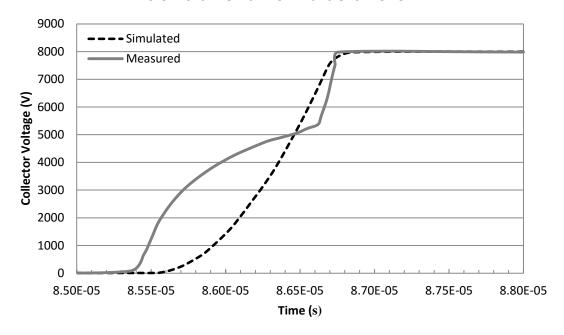

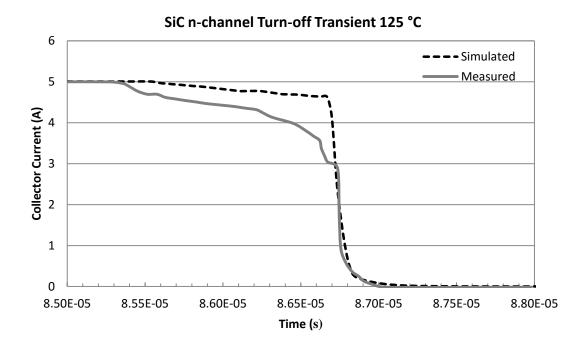

| Figure 6.14 | SiC n-channel turn-off voltage characteristics at 125 °C                       | 66 |

| Figure 6.15 | SiC n-channel turn-off current characteristics at 125 °C                       | 66 |

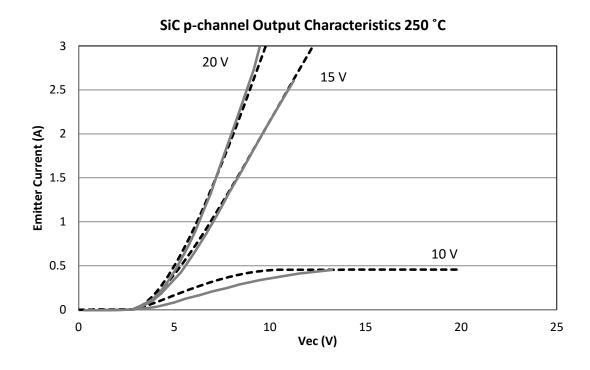

| Figure 6.16 | SiC p-channel output characteristics at 250 °C                                 | 67 |

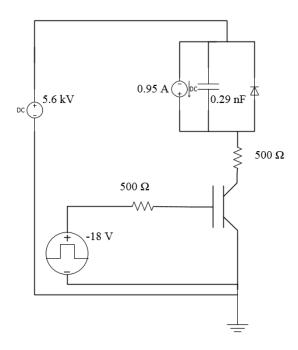

| Figure 6.17 | SiC p-channel clamped-inductive load testbench                                 | 68 |

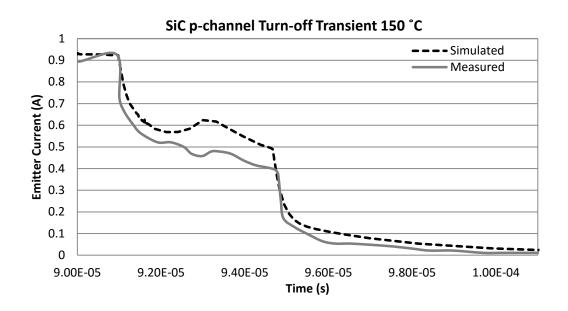

| Figure 6.18 | SiC p-channel turn-off current characteristics at 150 °C                       | 69 |

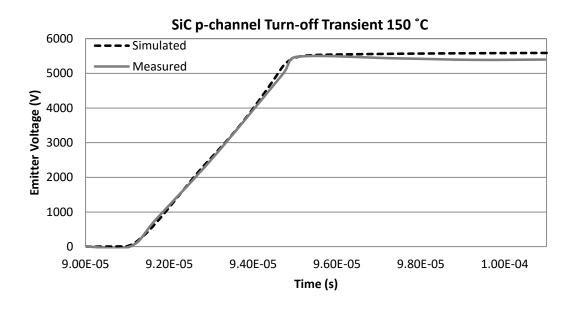

| Figure 6.19 | SiC p-channel turn-off voltage characterstics at 150 °C                        | 69 |

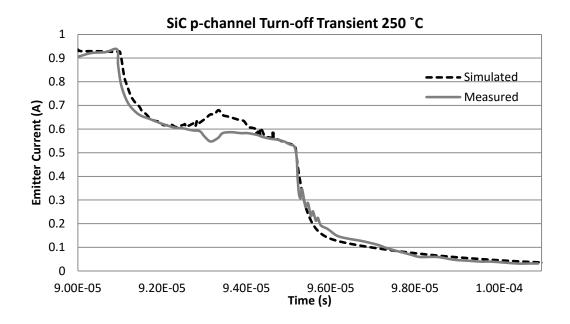

| Figure 6.20 | SiC p-channel turn-off current characteristics at 250 °C                       | 70 |

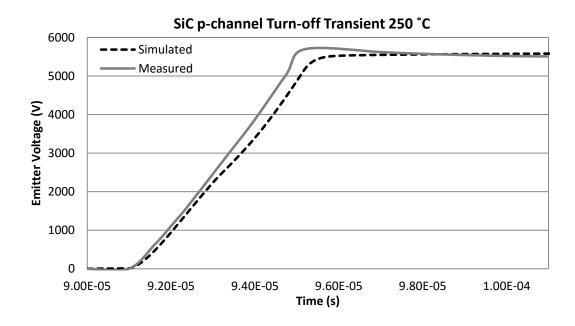

| Figure 6.21 | SiC p-channel turn-off voltage characteristics at 250 °C                       | 70 |

| Figure 6.22 | Si capacitance Verilog-A validation                                            | 72 |

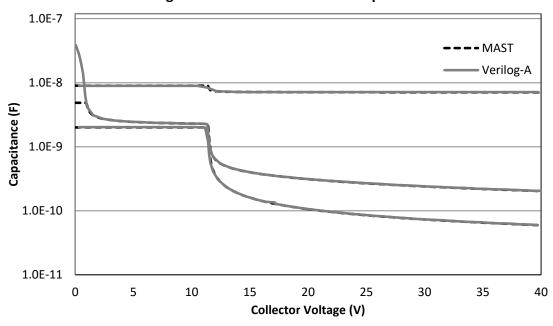

| Figure 6.23 | Si output characteristics Verilog-A validation                                 | 72 |

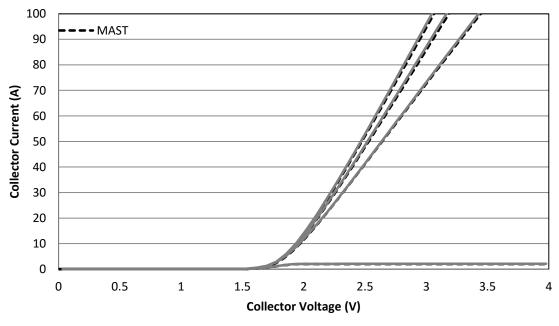

| Figure 6.24 | SiC p-channel turn-off current characteristics at 250 °C Verilog-A Validation. | 73 |

# **List of Tables**

| Table 1.1 | Material Properties Affecting High Temperature Performance of SiC Devices | . 3 |

|-----------|---------------------------------------------------------------------------|-----|

| Table 4.1 | Si n-channel Initial Mobility Equations                                   | 39  |

| Table 4.2 | Si p-channel Initial Mobility Equations                                   | 39  |

| Table 4.3 | SiC Mobility Model Parameters                                             | 39  |

| Table 4.4 | SiC n-channel Initial Mobility Equations                                  | 40  |

| Table 4.5 | SiC p-channel Initial Mobility Equations                                  | 40  |

| Table 4.6 | Silicon n- and p-channel Mobility Temperature Dependence                  | 41  |

| Table 4.7 | Silicon Carbide Mobility Temperature Dependence                           | 41  |

| Table 4.8 | Si IGBT Parameter Extraction Sequence                                     | 42  |

| Table 4.9 | SiC IGBT Parameter Extraction Sequence                                    | 46  |

| Table 6.1 | Model Parameters for each Device                                          | 71  |

#### **Chapter 1** Introduction

The focus of this thesis is on maturing and verifying a compact semiconductor device model to be utilized within circuit designs. The device discussed is a 4H silicon carbide (SiC) Insulated Gate Bipolar Transistor (IGBT). Therefore, when SiC is mentioned within this thesis it is referring to the 4H-SiC polytype. Initially, an overview of why SiC IGBTs are of interest, what a compact model is, and what other IGBT models exist in the field is discussed. Once these topics have been introduced to the reader, a detailed description of the following will be presented: the operation of an IGBT, the Unified IGBT model, the core changes to produce the current model, the results from the current model, and the possible future work to further update this silicon/SiC IGBT model.

#### 1.1 SiC IGBT Impact on the Power Electronic Industry

Silicon (Si) based electronics have propelled technology to the mobile and high power world we live in today. Insulated Gate Bipolar Transistors (IGBTs) are well utilized within power electronics applications due to their ability to provide high blocking voltage capability, with the advantage of a voltage-controlled gate. The highest known Si IGBT breakdown voltage is 6.5 kV and only operates up to 200 °C [1]. Although well above the average requirements for most printed circuit board applications, this device is not capable of withstanding extreme environment conditions of aeronautical and automotive applications that frequently exceed 200 °C. With the addition of SiC IGBTs underway, the next generation technology of high power and thermally efficient applications are being developed.

Intrinsic carrier concentration, thermal conductivity, and critical electric field are all material properties of SiC that provide spatial and performance improvements over Si

semiconductor devices. The lower intrinsic carrier concentration of SiC gives these devices the ability to operate in higher ambient temperatures than Si devices. The higher thermal conductivity of SiC, compared to Si, allows devices to operate during rapid temperature changes. Both thermal conductivity and intrinsic carrier concentration reduce the reliance on cooling systems to remove excess heat from the device to avoid destructive temperature effects. Without cooling systems, solely in place for continuous operation in Si devices, the size of these completed SiC devices is significantly reduced. The critical electric field of SiC is larger than that of Si. This material property allows vertical devices to be produced with thinner widths (or thinner base regions in terms of IGBTs) for the same blocking voltage capabilities [2]. Generally, a device designed with a thinner base region allows for more cells to be produced in the same x-y dimensions, resulting in a smaller device. These material advantages give SiC devices the ability to impact the power electronics industry through the miniaturization of electronics.

SiC devices possess the ability to switch at higher frequencies than their silicon counterpart. A device designed to switch at higher frequencies requires physically smaller passive components in the surrounding circuitry. Therefore, the footprint of the switching circuit will be reduced with a SiC device. Also, a device switching at higher frequencies requires passive components to be coupled closer to the device, further miniaturizing the switching circuit. As passive component values and interconnect path lengths are reduced, the closer the passive components are to semiconductor device; therefore, the passive components are now exposed to the same temperatures as the switching device. This presents an issue as there is a limited selection of passive components that are reliable over a wide range of temperatures [2]. In addition to the limited amount of passive components available, the size of these high temperature passives are undesirable as they combat the miniaturization effects of SiC devices.

However, SiC devices allow circuits to be designed and fabricated smaller than their silicon counterparts.

#### 1.2 SiC Material Properties

An overview of how SiC impacts the performance of IGBTs and other similar semiconductor devices will be briefly reviewed. Table 1.1 shows a few of the superior material properties that SiC has compared to Si for developing high temperature devices [3]. The rest of this section will discuss how the intrinsic carrier concentration, band gap, and the thermal conductivity affect the higher thermal operation limit of SiC.

Table 1.1 Material Properties Affecting High Temperature Performance of SiC Devices

| Properties                                                | Si          | SiC          |

|-----------------------------------------------------------|-------------|--------------|

| Intrinsic carrier concentration 300 K (cm <sup>-3</sup> ) | 1.4 X 10^10 | 6.7 X 10^-11 |

| Band gap (eV)                                             | 1.11        | 3.26         |

| Thermal conductivity (W/m·K)                              | 1.5         | 3.7          |

A low intrinsic carrier concentration,  $n_i$ , at room temperature allows SiC devices to operate at higher temperatures. (Within the Si/SiC IGBT model, the intrinsic carrier concentration is a model value and denoted as ni; therefore, from this point on the intrinsic carrier concentration will be referred to as ni.) The concentration of intrinsic carriers in a semiconductor material is directly proportional to the temperature; therefore, with an increase in temperature, ni increases. Figure 1.1 depicts a cross section of a silicon n-channel IGBT. For current to flow in this IGBT, the N+ source region requires a "connection" to the N- base region. Therefore, at room temperature, with no stimulus applied to the IGBT, current will not flow. However, as the temperature rises, electron-hole pairs are created within the semiconductor material, which increases the free electron concentration in the material. This decreases the

difference in the doping concentrations between the N+ source region and the P+ body region. This will eventually create a short, or "connection," between the N+ source region and the N-base region, with no external stimuli applied to the IGBT. Now, with any voltage applied to the collector, current will begin to flow through the device with little effort, regardless of the voltage applied at the gate. The lack of control at the gate renders this IGBT useless in any situation. This is a limit Si device designers must account for by adding large heat sinks and other cooling measures to keep the device under its theoretical temperature limit.

Figure 1.1 Cross section of an n-channel IGBT.

The upper temperature limit of most silicon semiconductor devices commercially available is 150 °C. Since the intrinsic carrier concentration in SiC starts at 20 orders of magnitude less than the intrinsic carrier concentration of Si at room temperature, this degenerative effect takes place at a much higher temperature in SiC devices. It has been shown, with the appropriate electronic packaging, SiC devices can operate higher than 400 °C [4]–[6].

Band gaps of semiconductor materials also affect the thermal operation limit in codependence with intrinsic carrier concentration, as the intrinsic carrier concentration of a material is proportional to its band gap. The larger the band gap, the more thermal energy is required for carriers to become thermally excited. Therefore, less intrinsic carriers are generated as the temperature rises. In other words, the large band gap correlates to the production of less intrinsic carriers at a given temperature, hence the co-dependence. As previously explained, with less intrinsic carriers, the device is able to operate at higher temperatures.

Thermal conductivity also relates to the operating temperatures of a semiconductor device. This property dictates how fast a material can dissipate heat. The lower the thermal conductivity, the longer it takes for heat to evenly distribute throughout the material. That is, it takes a silicon device longer to dissipate heat than its silicon carbide counterpart. Since SiC can dissipate heat at a faster rate, less bulky and inefficient hardware (i.e., heatsinks, fans, water-cooled systems, etc.) is required to cool the device. This allows devices to operate during rapid temperature changes without the hardware normally required, thereby increasing the reliability while simultaneously reducing the size and cost of SiC components needed for extreme environment conditions.

Not only does the high thermal conductivity of SiC benefit normal operation at high temperatures, this material property also enhances the ability of the device to operate under continuous high current and high voltage conditions. All devices experience self-heating to some degree at extreme operation limits. Devices created with SiC can release the heat generated through self-heating faster than Si. This reduces the deleterious effect of self-heating which would be seen in the same Si device under the same conditions.

With the higher thermal conductivity of SiC, devices created from this material are able to operate under high temperature conditions without the dependency of cooling systems. The intrinsic carrier concentration, band gap, and thermal conductivity are all superior properties silicon carbide boasts over silicon. Devices created with SiC are able to withstand higher temperatures, endure rapid temperature changes, and require less cooling systems.

#### 1.3 SiC IGBT State of the Art

IGBTs have been in production since the early 80s. Since their arrival in the industry they have added a great option for the medium frequency (5 -50 kHz) and for high voltage applications (.2 – 2 kV), opening up applications in industrial motor drives [7]. Now with the arrival of SiC Metal-Oxide Semiconductor Field-Effect Transistors (MOSFETs) on the market, SiC IGBTs are the next most powerful SiC device to be developed. In the mean time, experimental devices are being developed and their impressive achievements are published in peer-reviewed conferences such as The International Symposium on Power Semiconductor Devices and ICs (ISPSD). In 2012, the results of both SiC n-channel and p-channel IGBTs were published. The p-channel SiC IGBT supported a 15 kV blocking voltage. The n-channel SiC IGBT supported a 12 kV blocking voltage [5]. Results of an n-channel IGBT were also published during 2013 and boasted an improved 20 kV blocking voltage [10]. Within the same year, the static and dynamic characterization of a 15 kV n-channel IGBT was reported. This

performed on a single power semiconductor device at 11 kV [11]. The following year the results of a 22 kV n-channel device were published, proving to be the highest rated MOS-controlled device to that time [9]. In 2014, another p-channel IGBT was realized with a blocking voltage of 13 kV and showed static and dynamic results at 250 °C [12].

#### 1.4 Compact Device Modeling

A compact model describes the electrical behavior of a circuit component under certain conditions, and is then utilized within a circuit simulator [13]. A finite element device model is one that is based upon semiconductor device physics. Designing a device model as a compact model has a number of benefits over finite element models. Finite element models contain equations to solve in two or three dimensions and are designed to compute every physical effect carriers encounter. Although extremely accurate, finite element models do not offer circuit designers the short simulation time to simulate numerous transistors in one circuit.

Compact models are focused on the terminal behavior of the device, rather than how a single electron traverses through the material. With this focus, compact models are only concerned with 1-D device simulation, drastically reducing the computation power required to simulate a device under specific conditions. This is ideal for circuit designers, since they are only concerned with the electrical behavior at each terminal. A compact model with a 1-D device simulation focus can rely on empirical equations. This allows flexibility within the compact model, adding accuracy without computationally expensive and time-consuming features. Also, compact models should employ easily extractable parameters. Easily extractable parameters allow the user to provide a device model to a circuit designer in less time.

The purpose of creating such device models is to provide a reliable prediction of how a specific device will behave under specific conditions, defined by circuit designers who utilize the

compact model in a simulator. Using a model to optimize the design of the physical circuit, engineers use this method to reduce the time to create a finished product. The most common simulators used by designers are SPICE based. However, SPICE based simulators, such as HSPICE and Spectre, accept specific languages, a point explained further in the following section and in Chapter 5. Providing a circuit designer with a compact device model first entails selecting the compact model to send. There are three options for selecting a compact device model: select an existing model, edit and update an existing model, or create a new model. Once a compact model is chosen, the following steps provide the remaining process to deliver a model that simulates the physical device characteristics of the transistor chosen:

- measure a specific device requested in a circuit design project under various conditions (device characterization);

- 2) simulate the model under the same conditions (simulation);

- 3) overlay the measured data with the simulated data (fitting);

- 4) adjust the model parameters to produce a simulation that matches the measured device (model parameter extraction); and

- 5) provide the model and parameter set to circuit designers.

#### 1.5 Published IGBT Models

Models were created and published shortly after the invention of IGBTs in the early 1980s. A list and review of all models prior to 1998 can be found in [14], and a summary of IGBT modeling challenges can be reviewed in [15]. The foundation of this model is based upon [16], therefore a description of the models following this author's career is presented.

Dr. Hefner has published a variety of models following advancements in the structural development of the IGBT. In 1994, he published his first Si IGBT model [16]. In 1995, a buffer

layer model was published, adding effects of a highly-doped buffer layer to the IGBT model [17]. Recently, a SiC Field Stop IGBT (FS IGBT) has been published. This model added SiC material properties as well as the slight variation in physics that the FS layer adds to the IGBT in comparison with the buffer layer model [18]. Although parameter extraction software for each of these models has been created [19], all of these models implement only n-channel IGBT physics.

Although n-channel IGBT devices and models are actively researched, there is a lack of interest in p-channel IGBT models. p-channel IGBTs pose an extremely positive impact in the power electronics field through the application of complementary circuits. A complementary circuit, for example, can be implemented within an inverter. The traditional inverter topology includes an n-channel IGBT referenced to the collector of another n-channel IGBT. The reference point in this topology is floating, as the collector of the second n-channel IGBT is not constant. The floating reference causes significant problems with gate control. This creates a complication while designing a gate controller for each IGBT included in the inverter topology. However, if the referenced IGBT was a p-channel IGBT, the reference point of the p-channel IGBT is the constant positive power supply. Creating a constant reference point greatly reduces the complexity of the gate driver circuit, and therefore the entire inverter topology. Including p-channel IGBT in designs that benefit from complementary circuitry can reduce the complexity of the design as well as reduce the overall components required.

Another problem with all of the aforementioned models is that they are implemented within the MAST language and the Saber Simulator<sup>®</sup>. While this simulator has been used for some time in the power electronics industry and for power device modeling, MAST based models are not the most commonly used among circuit designers, many of whom depend on more traditional SPICE-based simulators. Verilog-A, an analog description language based on

the digital Verilog standard, has become a *de facto* standard through the efforts of industry such as the Compact Model Council [13], and many SPICE simulators accept Verilog-A models as an input format. Any disconnect between device modelers and the circuit designers hinders the advancement of technology. Therefore, there is a need for compact device models that are in languages beneficial to the broadest base of circuit designers.

Other IGBT models have been developed that are not MAST based. In 2003, a FS IGBT model and parameter extraction were developed [11], [20]. However, only turn-off time was modeled within this paper, and does not include any static characteristics. A SPICE based IGBT model was developed in 2004 accounting for IGBT latch-up and temperature effects [21]. In 2009, a physics based SPICE compact model was created with some ability to customize the device since this model can be used to characterize IGBTs with or without a FS layer [22]. The HiSIM IGBT model was published in 2011 for Si buffer layer IGBTs [23]. Although only measured against 2D device simulation data, this model showed promising predictions focusing on the turn-off behavior. In 2013, a SiC version of the same HiSIM model was published with similar results [24]. A high voltage SiC IGBT model was implemented in MATLAB and published in 2015 [25]. Again, this model will not benefit most circuit designers due to the fact that it is incompatible with any SPICE like simulator.

Although SiC n-channel IGBTs models have been researched and made available, the lack of p-channel IGBT models within the field inhibits the potential progress of power electronics. With the possibilities of complementary circuits, p-channel IGBT models are required to catapult this field into the next generation of high power and high density technology.

#### 1.6 The Unified IGBT model

The Unified IGBT model is a physics based compact MAST model of an n-channel MOSFET driving a PNP Bipolar Junction Transistor (BJT) [26]. It has been previously proven to simulate the performance of SiC n- and p-channel devices [27], and it contains the ability to simulate Si n- and p-channel device configurations as well. The foundation of the model is based upon a widely used Si IGBT model [16]. However, the Unified IGBT model reduces the amount of variables within the code to improve performance without sacrificing noticeable accuracy. This model will be fully explained in detail within Chapter 4.

#### 1.7 Maturing the Unified Model

The goal of this thesis is to update and mature the Unified IGBT model mentioned above. The maturation is accomplished by updating SiC mobility equations, creating a parameter extraction sequence, and creating a Verilog-A version of the model. The current model is in the process of being published as the first SiC p-channel IGBT model. It is also the first IGBT model to combine both Si and SiC material types with n- and p-channel device configurations.

#### **Chapter 2 IGBT Operation**

#### 2.1 Operation States of the IGBT

An IGBT can be thought of as a voltage-controlled bipolar junction transistor (BJT) with some inherent MOSFET characteristics, or as commonly referred, a MOSFET driving a BJT. It is a normally off device due to the fact that when the gate voltage applied is less than the threshold voltage of the device, the IGBT is off - the same concept as in the MOSFET. The explanation of how an IGBT works can be divided into three operating conditions: the blocking state, the on-state, and when the device is being switched. The blocking state refers to when the device's purpose is to prevent current from flowing through its collector-emitter nodes. This is the equivalent of a switch in the off position. The on-state refers to when current is flowing between the collector-emitter nodes, and the switching condition is when the device is being turned on and off.

The operation of the IGBT will be explained in reference to a non-punch-through (NPT) n-channel IGBT, which is equivalent to a n-channel MOSFET driving a PNP BJT (PNP refers to the doping types of the two PN junctions associated with the BJT). A NPT IGBT is one of three common structure types of this device, and is constructed with the following layers:

- P+ injection layer also called the P- emitter,

- N- base region also called the drain of the MOSFET and base of the BJT,

- P+ body region also called the collector of the PNP BJT, and the

- N+ source region which is the source of electrons for the MOSFET current.

These layers and their functions will be explained in more detail in the following section. The other two common structures, PT IGBT and a FS IGBT, will be described in section 2.2. Not

shown in all the following figures, but is inferred, is the metal connection beneath the P+ injection layer, completing the collector terminal of the IGBT.

#### 2.1.1 Blocking State

During the blocking state, the IGBT is off and a large amount of voltage can be applied to the collector-emitter terminals without allowing any current to flow through the device (besides a negligible amount of leakage current). For this condition to be met, the gate voltage applied to the device is less than the threshold voltage of the IGBT, so that the inversion layer beneath the gate does not form. However, every semiconductor device has an upper limit on the voltage it can support - referred to as the breakdown voltage - which can occur in two conditions.

The first condition is referred to as the reach-through condition. When a positive voltage is applied to the collector and a voltage less than the threshold voltage is applied to the gate, the junction labeled J2 in Figure 2.1 becomes forward biased. Junction J2 supports the forward blocking voltage until the depletion layer width, also depicted in Figure 2.1, reaches the P+ injection layer. When the depletion width reaches the P+ injection layer, or J1, the reach-through condition has been met. At this point, holes will be injected into the P+ body region, and a substantial amount of current will begin to flow through the IGBT. The voltage required to achieve the reach-through condition is one upper limit, or breakdown voltage ( $BV_{reach-through}$ ), of a device and is represented by Equation 2.1 [3].

$$BV_{reach-through} = \frac{q \cdot nb}{2 \cdot \varepsilon_s} \cdot wb^2$$

2.1

Where q is the electrical charge, nb is the N- base region doping concentration, wb is the width of the N- base region, and  $\varepsilon_s$  is the relative permittivity of silicon. Although this condition is not modeled in this work, it is an important consideration when designing a high voltage IGBT.

Figure 2.1 NPT n-channel IGBT cross section with a representation of the device in a forward blocking condition. The dashed lines are referring to the depletion regions, the "X's" represent that the depletion layer "stops" the hole current.

The second condition is determined by the process of avalanche breakdown, which is the condition modeled in the IGBT model and explained in Chapter 3. The same positive voltage is applied to the collector in this condition, and can take place regardless of the gate voltage of the

device. Avalanche breakdown takes place when the maximum electric field present within the depletion region (of the N- base region) equals the critical electric field of the semiconductor material. This condition is represented by Equation 2.2 [3].

$$BV_{AB} = 5.34 \times 10^{13} \cdot nb^{-0.75}$$

2.2

A NPT IGBT has reverse blocking capabilities that are not present in the PT IGBT. Just as J2 (in Figure 2.1) is defined as the junction that supports the forward blocking voltage, J1 is similarly defined as the junction that supports the reverse blocking voltage capabilities. Since J1, like J2, is also a N-P+ junction, it has the equivalent blocking capability as J2. This is why the NPT IGBT is also referred to as the symmetric IGBT.

#### **2.1.2 On-state**

During the on-state, the voltage applied to the gate will be equal to or greater than the threshold voltage of the device. This allows an inversion layer to form beneath the gate, connecting the N+ source region to the N- base region. This connection allows current to flow into the N- base region, and is the MOSFET part of the IGBT, as it performs similarly. This flow of electrons serves as the driving force, or base current, of the PNP BJT. The flow of electrons into the N- base region creates a substantial amount of holes injected from the P+ injection layer into the N- base region. The injected holes travel towards the P+ body region by both drift and diffusion mechanisms [28]. As soon as the holes reach the P+ body region they are attracted by the electrons from the source metallization that contacts the N+ source region. The holes are then quickly recombined. This junction, J2, is "collecting" the diffusing holes, and thus functions as the collector of the PNP BJT. Since the internal BJT is in a PNP configuration, the BJT collector is the negative terminal, and the emitter is the positive terminal. Thus, the emitter of the PNP

BJT is the collector of the IGBT. Through the arrows and dotted lines, the flow of carriers during the on-state in represented within Figure 2.2.

Figure 2.2 NPT n-channel IGBT cross section with an overlay representing the flow of carriers during the on-state.

#### 2.1.3 Switching

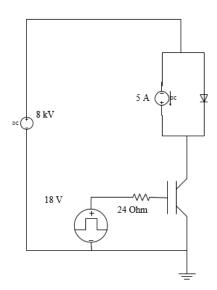

The last operation condition to be discussed is when the IGBT is switched on and off. The transient data used to verify the Si-SiC IGBT model are inductive load turn-off responses; therefore, this specific condition will be described. This response is controlled by switching the gate from a value above the threshold voltage to a value below the threshold voltage. In a clamped inductive load testbench, as shown in Figure 6.11, the IGBT will not begin to decrease in current until the full load voltage of the circuit has been reached. The initial decrease in the IGBT's collector current is represented by *t1* in Figure 2.3.

#### **Inductive Load Turn-off Transient Example**

Figure 2.3 Example of an inductive load turn-off response.

After the initial decrease in collector current, the turn-off response is highly dependent on the excess carrier lifetime within the base. When the gate voltage is switched to a value below the threshold voltage, the inversion layer underneath the gate is cut off, and the flow of electrons

from the N+ source region to the N- base region ceases. The reduction in flow of electrons causes a dramatic decrease in the IGBT's collector current and is correlated to the MOSFET current ceasing, represented by *t2* in Figure 2.3. The excess flow of electrons in turn stops the injection of holes from the P+ collector into the N- base region. However, excess electrons from the MOSFET current and excess holes from the P+ injection layer are left in the N- base region. The tail current is an electrical representation of the physical recombination of electrons and holes within the N- base region. The excess carrier lifetime determines the time it takes for the recombination to take place. Once this happens, the device is fully off, and the process will repeat when the appropriate voltages are applied. The end of the tail current is represented by *t3* in Figure 2.3.

When designing an IGBT, a tradeoff must not only be made between the on-state losses and the breakdown voltage, a tradeoff between the on-state losses and a faster turn-off time must also be made. The NPT IGBT concentration of hole injection can be controlled by the doping profile of the moderately doped P+ injection layer [11]. This allows the amount of excess carriers within the N- base region to be reasonably low, reducing the losses during turn-off, while still having enough holes injected into the N- base region to cause conductivity modulation in the base. Conductivity modulation needs to occur in the base to decrease the amount of on-state resistance within the IGBT. Hence, a tradeoff between on-state losses and turn-off time is required.

#### 2.2 Variations in Structures of IGBTs

There are two other variations to the IGBT structure that are presented here: PT IGBT, or buffer layer IGBT, and field-stop IGBT. As the benefits and structural properties of the NPT IGBT have been discussed in section 2.1, the PT and FS IGBT structures will be discussed here

in a similar manner. Not discussed in this chapter are the varieties of gate structures commonly used, such as the trench gate structure. These gate structures are similar to those utilized in MOSFET designs and have comparable benefits.

The PT-IGBT is created using a P+ substrate as the IGBT's collector terminal with a lightly doped N- base region, and a highly doped, N+, buffer layer, shown in Figure 2.4. As explained in the Blocking Region section of 2.1.1, the depletion region of J2 must be prevented from reaching through to the P+ injection layer. The N+ buffer layer does this by drastically reducing the electric field of the N- base region as it approaches the N+ buffer layer, giving the IGBT the more desirable trapezoidal electric field distribution. The trapezoidal electric field distribution of the IGBT allows the N- base region to be significantly shorter than that of a NPT IGBT at the same forward blocking voltage, decreasing the on-state losses [11]. The on-state characteristics are also improved by a large hole injection due to the high doping concentration in the P+ injection layer. However, the high amount of hole injection increases the required amount of excess carriers that must be removed during turn-off, increasing the tail current of the IGBT.

To combat this loss, the excess carrier lifetime must be controlled by designing the device with a lifetime reduction process. However, this process increases the on-state losses, as it reduces carriers within the entire N- base region, not just around the P+ substrate where the excess holes are being injected [11]. This is why a lower lifetime in the base region correlates to low conductivity in the base, which increases the on-state resistance of the device. Therefore, a tradeoff between turn-off times and on-state losses must be made when designing a PT IGBT, just as in the NPT IGBT.

As briefly described earlier, the addition of a buffer layer takes away the ability for the PT IGBT to have any practical reverse blocking capability. With a highly doped buffer layer, J1 is now bounded by two highly doped regions, reducing this junction's breakdown voltage to a few tens of volts [28]. The addition of the buffer layer also causes the structure to become asymmetrical, the origin of the asymmetrical IGBT namesake.

Figure 2.4 N-channel PT IGBT cross section.

The field-stop layer IGBT, shown in Figure 2.5, combines the thin moderately doped P-emitter of the NPT IGBT and the moderately doped N+ buffer layer of the PT IGBT creating a superior IGBT structure utilizing both enhancements of NPT and PT structures. This results in:

(1) a thin N- base region, lowering the on-state conduction losses without reducing the breakdown voltage; and (2) a low hole injection from the P- emitter, lowering the amount of stored charges in the base [11]. With fewer charges to recombine within the base, the tail current of the field-stop IGBT is shorter than a PT IGBT. The tail current can now be modified without reducing the conductivity in the base.

Figure 2.5 N-channel FS IGBT cross section.

Generally, a perfectly designed IGBT only exists for one specific application. Due to all the tradeoffs discussed throughout this chapter, an IGBT's turn-off time, blocking voltage, and on-state resistance cannot be optimized for all types of circuits. Following is a description of the tradeoffs that are made within each major layer of the IGBT, as well as a summary of all the tradeoffs that have been mentioned in this chapter. As mentioned previously, the gate structures share the same tradeoffs with MOSFETs, so the tradeoffs for different gate structures will not be discussed here.

Figure 2.6 shows a visual representation of the tradeoffs required in each section of an IGBT. Within the N- base region, two properties, lifetime and width, must be compromised with the following:

- a smaller width leads to lower on-state resistance;

- a larger width leads to higher blocking voltage ratings;

- a shorter lifetime correlates with a smaller tail current; and,

- a longer lifetime sustains a high conductivity modulated base, which reduces the onstate resistance.

The field-stop layer needs to provide the IGBT with a reduction in hole injection from the P+ injection layer, compared to a NPT IGBT. However, the field-stop layer still has to provide enough hole injection to produce conductivity modulation in the base. Similar to the field-stop layer, the P+ injection layer must be doped highly enough to produce conductivity modulation in the base, and still not flood the N- base region with excess charges, inhibiting the tail current of the device.

Figure 2.6 Trade-offs of designing an IGBT by layer.

#### **Chapter 3** The 2012 Unified IGBT Model

#### 3.1 Introduction

The Unified IGBT model is a physics based compact model that predicts the performance of Si, SiC, n-channel, and p-channel devices. The foundation of the model is based upon a Si IGBT model [16], and is modified to incorporate SiC and p-channel physics. The latest SiC mobility equations and material properties are used, as described in detail in Chapter 4. The physics to describe the IGBT's performance is designed for a non-punch through device; however, this model is proven to predict the performance of Field-stop Layer IGBTs. As a physics based compact model, it not only accurately predicts the performance of these IGBTs, but allows circuit designers to use the model without the extended simulation time of finite element based physical models. Empirical temperature scaling equations are implemented, allowing the user to fully utilize the model in any circuit design from 25 to 500 °C [26].

Discussed further is a description of how physical effects in IGBTs are accounted for, and how the model is formulated in the MAST language. A description of parameters for this model is given in Appendices A.1 and A.2.

Approximations to the foundation model have been made to improve simulation speed, with the slightest reduction in accuracy. This is discussed in Section 3.4.1, as the approximations are implemented within the BJT portion of the model. The value  $m_channel$ , present in the MOSFET current equations, effects the polarity of the device and is explained in detail in section 3.5.

### 3.2 Structure

A common n-channel NPT IGBT structure is shown in Figure 3.1, overlaid with a detailed circuit representation of the model [16]. The device has three terminals, the gate (G), the collector (C), and the emitter (E). The MOSFET and BJT symbols within the circuit show how the MOSFET drain provides base current to the BJT portion of the device. The internal drain (d) and source (s) nodes, as well as the gate terminal (G) are associated with the MOSFET portion of the IGBT. The internal collector (c), emitter (e), and base (b) nodes are associated with the PNP BJT portion of the device. In the formulation of the model, nodes, d and e are named internal nodes, as they both connect to the internal BJT and the MOSFET of the IGBT. Nodes b and d, shown in Figure 3.1, combine to form node d when the model is implemented. Likewise, nodes c and s combine and are implemented as the Emitter terminal (E).

### 3.3 MOSFET Portion

This portion of the model consists of the MOSFET current ( $I_{mos}$ ) - which supplies current to the base of the BJT - and three capacitances: the drain-source junction ( $C_{dsj}$ ),  $C_{gs}$ , and the gate-drain ( $C_{gd}$ ).  $I_{mos}$  is defined by the piecewise behavior around the device drain voltage given in Equations 3.1 and 3.2  $I_{mos}$  utilizes the common transconductance parameters,  $K_{Plin}$  and  $K_{Psat}$ , differently to produce kf and kp [17], shown in Equations 3.3 and 3.4. The model parameter theta, shown as  $\theta$  in Equation 3.5, accounts for channel mobility reduction due to the high transverse electric field. The entire reduction factor is introduced as mufact, and is shown in Equation 3.5.

Figure 3.1 Cross-section of a NPT IGBT overlaid with an equivalent circuit of the IGBT model [16].

$$I_{mos_{V_{ds} \ge 0}} = \begin{cases} 0 & , V_{gs} < vt \\ \frac{kp \cdot kf \cdot \left(V_{gs} - vt - kf \cdot \frac{V_{ds}}{2}\right) \cdot V_{ds}}{mufact} & , V_{ds} \le (V_{gs} - vt)/kf \\ \frac{0.5 \cdot kp \cdot (V_{gs} - vt)^2}{mufact} & , V_{ds} \ge (V_{gs} - vt)/kf \end{cases}$$

3.1

$I_{mos_{V_{ds}} < 0}$

$$= \begin{cases} 0, & m_{channel} \cdot \left(V_{gs} - V_{ds}\right) < vt \\ \frac{kp \cdot kf \cdot \left[m_{channel} \cdot \left(V_{gs} - vt\right) - kf \cdot \frac{V_{ds}}{2}\right] \cdot V_{ds}}{mufact}, -V_{ds} \leq m_{channel} \cdot \frac{\left[\left(V_{gs} - V_{ds}\right) - vt\right]}{kf} 3.2 \\ \frac{-0.5 \cdot kp \cdot \left[m_{channel} \cdot \left(V_{gs} - V_{ds}\right) - vt\right]^{2}}{mufact}, V_{ds} \geq \frac{V_{gs} - vt}{kf} \end{cases}$$

$$K_{plin} = \frac{kf}{kp} \tag{3.3}$$

$$K_{nsat} = kp 3.4$$

$$mufact = 1 + \theta(V_{as} - vt)$$

3.5

Capacitances related to the MOSFET portion of the device involve the gate terminal and the drain and source nodes, which can be seen in Figure 3.1. The gate-source capacitance ( $C_{gs}$ ) is the source metallization capacitance ( $C_{m}$ ) summed with the portion of the gate oxide capacitance which overlaps the source ( $C_{oxs}$ ), as shown in Figure 3.1.  $C_{gdj}$  and  $C_{oxd}$  combine to form the gate-drain capacitance, ( $C_{gd}$ ). The gate-drain capacitance is implemented as a piece-wise equation, shown in Equation 3.6, due to the fact that when  $V_{ds} > (V_{gs} - V_{td})$ , the area beneath the gate-drain overlap region becomes depleted, reducing the capacitance. The drain-source junction capacitance ( $C_{dsj}$ ), shown in Equation 3.8, is a depletion capacitance over the drain-body junction, where cjo is the zero bias junction capacitance and mj is the gradient coefficient.  $A_{gd}$  is the gate-drain overlap area and  $A_{ds}$  is the body region area, where the sum of these areas is equal to the active area of the device, a [16]. This relationship is represented in Figure 3.1.

$$C_{gd} = \begin{cases} coxd & , V_{dg} \leq -V_{td} \\ coxd / \left[ 1 + \left( \frac{coxd \cdot W_{gdj}}{A_{gd} \cdot \varepsilon} \right) \right] & , V_{dg} > -V_{td} \end{cases}$$

3.6

$$C_{bcj} = \begin{cases} \frac{a \cdot cjo}{\left(1 + \frac{V_{ds}}{pb}\right)^{mj}}, V_{ds} \ge (-fc \cdot pb) \\ \left(1 + \frac{V_{ds}}{pb}\right)^{mj}, V_{ds} \ge (-fc \cdot pb) \end{cases}$$

$$\frac{a \cdot cjo \cdot \left[1 - (1 + mj) \cdot fc - mj \cdot \frac{V_{ds}}{pb}\right]}{(1 - fc)^{mj+1}}, V_{ds} < (-fc \cdot pb)$$

3.7

$$C_{dsj} = C_{bcj} \cdot \frac{A_{ds}}{a} \tag{3.8}$$

Due to the fact that  $V_{ds}$  and  $V_{bc}$ , are equivalent, the depletion capacitance  $C_{bcj}$  is used to calculate  $C_{dsj}$ , which is shown Equation 3.8.  $C_{bcj}$  is also used to calculate the capacitance between the emitter and the collector  $(C_{cer})$ . This capacitance is part of the BJT component and will be described in the following section.

To compute the current contributions of  $C_{gs}$ ,  $C_{gd}$  and  $C_{dsj}$ , two different methods are employed. The currents generated from  $C_{gs}$  and  $C_{dsj}$  are computed by defining the charge and then taking the time derivative as explained later. These charge calculations are shown in Equations 3.9 and 3.10. The capacitance calculated in Equation 3.8 is utilized for capacitance verification. The current contribution from  $C_{gd}$  is calculated by multiplying the capacitance by the time derivative of its voltage. This is shown and explained in the MAST Formulation section.

$$qcgs = C_{gs} \cdot V_{gs}$$

3.9

$$qcdsj = A_{ds} \cdot \sqrt{2 \cdot \varepsilon_s \cdot (V_{ds} + pb) \cdot q \cdot nb}$$

3.10

#### 3.4 BJT Portion

There are three current contributions related specifically to the BJT: the base current (ibp), the total emitter current (irb), and the collector current (icp), shown in Equations 3.11 through 3.14.

$$ibp = qceb / \left(tauhl + \left[\frac{qceb^2 \cdot nb^2 \cdot isne}{qb^2 \cdot ni^2}\right]\right)$$

3.11

$$rb = \begin{cases} \frac{w}{mun \cdot a \cdot q \cdot nb} + rs &, & qceb \leq 0\\ \frac{w}{mueff \cdot a \cdot q \cdot neff} + rs &, & qceb > 0 \end{cases}$$

3.12

$$irb = \begin{cases} V_{ae}/rb & , & qceb \le 0 \\ V_{ae}/rb & , & qceb > 0 \end{cases}$$

3.13

$$icp = \frac{irb}{(1+b)} + \frac{b}{(1+b)} \cdot \left(\frac{4 \cdot dp \cdot qceb}{w^2}\right)$$

3.14

As given, qceb is the emitter to base charge, qb is the background base charge, w is the quasineutral base width, mun is the electron mobility, rs is the series resistance implemented as a

model parameter, mueff is the effective mobility, and neff is the effective base doping

concentration. b is the ambipolar mobility ratio, and dp is the hole diffusivity.

## 3.4.1 Approximations

Two approximations have been made within this model: the carrier-carrier scattering effect, which reduces the carrier mobility, as well as the second order component of the space charge concentration,  $N_{sat}$ , are both negligible, and thus can be eliminated. Both of these approximations are used within the BJT portion of the model. These two approximations reduce the number of simultaneous equations, and thus improve the speed of this compact model.

The carrier-carrier scattering effect approximation is taken into account within the total emitter current through the base resistance, rb, shown in Equation 3.12. In Equation 3.12, mun, the electron mobility, is used solely in the calculation of rb instead of accounting for the additional reduction in mobility,  $\mu_c$ , due to carrier-carrier scattering. With this second order effect,  $\mu_c$ , taken out of the equation, the base resistance becomes slightly smaller than what it would have been if the carrier-carrier scattering effect was taken into account. Although this approximation may reduce the total accuracy of the model by a minute amount, the difference

can be accounted for empirically through the parameter rs, the series resistance, which is added to the calculated value of rb shown in Equation 3.12. Adding an empirical amount of series resistance to rb increases the total base resistance; this accounts for the mobility reduction effect. However, the series resistance is a linear approximation of the mobility reduction instead of a dynamic mobility reduction dependent on the excess carriers within the base region, qceb. Since  $\mu_c$  has been replaced by rs, as qceb decreases, rb is not decreasing. Although this effect is no longer dependent on qceb, reducing the total number of simultaneous equations and adding the effect through a parameter reduces simulation time, and allows an approximate value of base resistance to be modeled.

In addition to reducing the overall simulation time, adding an empirical model parameter to model the carrier-carrier scattering effect adds another level of flexibility to the model, making it easier to verify. Without the series resistance included in Equation 3.12, no model parameter can directly control the total base resistance in a similar manner. Adjusting model parameters to indirectly affect the total base resistance of the IGBT increases the time it takes to characterize and fit the model. Therefore, with a direct correlation between rs and rb, the parameter extraction process is simplified.

Since  $\mu_c$  has been ignored, the value of mueff has also been approximated to the value shown in 3.15. The approximation from the original mueff equation is explained in [26].

$$mueff = mun + mup \cdot \frac{p0}{nb} / \left( \left[ \frac{p0}{nb} + 1 \right] \right)$$

3.15

The second-order effect on the space charge concentration,  $N_{sat}$ , approximation is taken into account when calculating the total charge concentration. The total space charge concentration within the base-collector region is equal to only the base doping concentration, nb, because the additional space charge  $N_{sat}$  is negligible. Also, because  $N_{sat}$  has been ignored, the

value of qb is approximated and is shown Equation 3.16. Likewise, all equations involving nb have been approximated this way.

$$qb = a \cdot q \cdot w \cdot nb \tag{3.16}$$

## **3.4.2** Base Charge

To define the emitter to base charge of the IGBT, qceb is solved such that the emitter-base junction voltage,  $V_{ebj}$ , and the sum of voff and the emitter-base terminal voltage ( $V_{eb}$ ) are equal. This "solve such that" (or implicit constraint equation) definition of qceb is identified via a colon in the MAST language, and is shown in Equation 3.17. Although this equation contains only voltage and parameter values, Equation 3.17 is a simultaneous equation and therefore must be implemented via the equation section of the MAST model. An explanation of the formulation of the MAST model is described in Section 3.5. Equation 3.17 is also implemented differently within the Verilog-A model, as explained in Chapter 5.

$$qceb: V_{ebj} = V_{eb} + voff 3.17$$

The emitter base junction voltage is calculated during three operation points:

- reverse conduction,

- forward conduction when qceb is less than the zero bias base charge, qceb0, and

- forward conduction when *qceb* is greater than *qceb*0.

$V_{ebj}$  is shown in Equation 3.18, and qceb0 is shown in Equation 3.19.

$$V_{ebj} = \begin{cases} V_{ebdep}, & qceb \leq 0\\ \frac{qceb \cdot V_{ebdif}}{qceb0}, & 0 < qceb < qceb0\\ V_{ebdif}, & qceb \geq qceb0 \end{cases}$$

3.18

$$qceb0 = a * \sqrt{2 * \varepsilon * q * nb * pb}$$

3.19

$V_{ebdep}$ , the emitter-base depletion voltage, and  $V_{ebdif}$ , the emitter-base diffusion voltage, are shown in Equations 3.20 and 3.21, respectively. p0, a factor used to simplify the equation, is shown in Equation 3.22.

$$V_{ebdep} = pb - \left(\frac{0.5 \cdot (qceb - qceb0)^2}{q \cdot nb \cdot a^2 \cdot \varepsilon}\right)$$

3.20

$$V_{ebdif} = V_{th} \cdot \ln \left[ \left( \frac{p0}{nb} + 1 \right) \cdot \left( \frac{p0 \cdot nb}{ni^2} + 1 \right) \right] - \frac{2 \cdot mun \cdot mup \cdot V_{th}^2}{2 \cdot V_{th} \cdot (mup + mun) \cdot mun} \cdot \ln \left[ \frac{p0}{nb} + 1 \right] 3.21$$

$$p0 = \frac{qceb}{q \cdot a \cdot l \cdot \tanh\left(\frac{w}{2 \cdot l}\right)}$$

3.22

$V_{ebdep}$  and  $V_{ebdif}$  represents the voltage across the capacitors  $C_{ebdep}$  and  $C_{ebdif}$ , respectively, as shown in Figure 3.1. These capacitances, in part, determine the emitter-base voltage, shown through the relation of  $V_{ebj}$  in Equation 3.18.

### 3.4.3 Collector to Emitter Capacitance

The collector to emitter capacitance ( $C_{cer}$ ) is a function of the internal BJT's base charge [16]. It is defined in Equation 3.23:

$$C_{cer} = qceb \cdot C_{bcj}/(3 \cdot qb)$$

3.23

where  $C_{bcj}$  is defined in Section 3.3.

## 3.4.4 Breakdown Voltage and Multiplication Factor

Although not specifically confined to the BJT portion of the device, the breakdown voltage and avalanche multiplication current will be explained here. The collector-base breakdown voltage,  $BV_{cbo}$ , is approximated using Equation 3.24 [16]. Throughout the remainder of this thesis, the collector-base breakdown voltage will be denoted as bvcbo, as it is denoted in the model. The parameter bvf is added to the approximation described in Equation 2.2 to

account for the shorter N-base regions that can support a higher blocking voltage with the same doping concentration due to the overall device structure, as described in Chapter 2.

$$bvcbo = \frac{bvf \cdot 5.34e13}{nb^{0.75}}$$

3.24

In the model, if  $V_{ds}$  is greater than the collector-base breakdown voltage multiplied by the breakdown uniformity factor – i.e. if  $V_{ds}$  reaches the breakdown voltage defined, then the avalanche multiplication factor, m, will equal such a value that causes the IGBT current to increase accordingly. Due to its size, this equation can be found in Appendix A.1. However, when the breakdown voltage is not reached, m still affects the total current of the IGBT, albeit in a small manner. The value of the avalanche multiplication factor when the breakdown voltage has not been reached is given as Equation 3.25. m is then used to determine the multiplication current, imult, which also contains the amount of current generated thermally, igen. Equations 3.26 and 3.27 describe igen and imult, respectively.

$$m = \begin{cases} 1, & V_{ds} \leq 0\\ \frac{1}{\left(1 - \left(\frac{V_{ds}}{bvcbo}\right)\right)^{bvn}}, & V_{ds} < fc\_bvbco \cdot bvcbo \end{cases}$$

3.25

$$igen = \frac{q \cdot ni \cdot a \cdot \sqrt{2 \cdot \varepsilon \cdot \left| \frac{V_{ds}}{q \cdot nb} \right|}}{tauhl}$$

3.26

$$imult = (m-1) \cdot \left| imos + icp + \left( C_{cer} \cdot \dot{V}_{ds} \right) \right| + (igen \cdot m)$$

3.27

### 3.5 MAST Formulation

Before the formulation of the model can be described, a brief overview of how MAST models are constructed is given. MAST models are separated into multiple sections with specific functions: structure, parameters, values, and the equation section. While there are other sections

that can be implemented in MAST models (namely in support of mixed-signal constructs) they are not required for a model of this type and the discussion will be limited to sections relevant to compact device models.

The structure section is used to denote the model interface. Here the outline of the model and the user parameters are defined. The outline of the model includes items such as terminals, options (parameters) the user will be able to select, and a list that includes all numbers, values, and variables – i.e. every item that is used throughout the model. Within the MAST model, a variable is defined by a simultaneous equation, and a value is an item that is dependent on one or more variables or values. The parameters section contains the number definitions. A number is any item defined as a numerical value – e.g. the zero bias base charge (qceb0), defined by Equation 3.19. Within Equation 3.19, all components are constant numerical values. More definitively, a number cannot contain an item that is dependent on a value or a variable. Therefore, only user parameters defined in the structure section and numbers can be listed in the parameter section. The values section contains the definition of all items that are dependent on variables. For example, voltages are defined here, and hence all items dependent on voltages. The equations section is where the current contributions are defined. This is also where the simultaneous equations are coded, dictating how to solve the variables. The equations section is shown in Figure 3.2.

The Unified IGBT model has the option to simulate both n-channel and p-channel IGBTs. In the interface of the model, the user selects the option for an n- or p-channel device configuration. This selection determines the sign of  $m_channel$  - a value that affects areas of the model involved with determining the polarity of the device. As an example, if the user selects the model to be a p-channel device, then  $m_channel$  will equal negative one. The voltage

definitions, one area affected by the polarity of the device, are calculated to be opposite to that of the n-channel model.  $m\_channel$  also effects the MOSFET current, and was discussed in Section 3.3. Also, as seen in Figure 3.2, when the p-channel model is selected, the currents are listed in the same order as presented in the circuit diagram; however, they are written with negative values. This also accounts for the reverse in the polarity of the p-channel device.

```

equations {

if(channel==p_channel) {

i(g->k) +=

-d_by_dt(qcgs)

i(d\rightarrow g) += -icdg

if(model->bvf == inf) {

i(d->k)

+= -imos - d_by_dt(qcdsj)

else {

i(d->k)

+= -imos - imult - vds/rds - d_by_dt(qcdsj)

i(e->k)

+= -ibp

- d_by_dt(qceb)

i(e->d)

#...Lagging filter

vdgx: d_by_dt(vdgx_w) = dvdgdt

d_by_dt(vdsx_w) = dvbcdt

qceb:

vebj = veb-model->voff

else {

i(g->k) +=

d_by_dt(qcgs)

i(d\rightarrow g) += icdg

if(model->bvf == inf) {

i(d->k)

+= imos + d_by_dt(qcdsj)

else {

i(d->k)

+= imos + imult + vds/rds + d_by_dt(qcdsj)

i(e->k)

+= icc

i(e->d)

+= ibp

+ d_by_dt(qceb)

i(a->e)

+= irb

#...Lagging filter

vdgx:

d_by_dt(vdgx_w) = dvdgdt

d_by_dt(vdsx_w) = dvbcdt

vdsx:

qceb:

vebj = veb+model->voff

```

Figure 3.2 Capture of the equations section within the MAST IGBT model. It is separated between n and p-channel operations, with currents defined accordingly between each node listed.

The current contributions from each capacitor within the model are calculated using two methods. The time derivative of the three charges used to compute the current contribution are

qcgs, qcdsj, and qceb. Two other current contributions from the capacitances,  $C_{gd}$  and  $C_{ccer}$ , are calculated following Equations 3.28 and 3.29. As stated in Section 3.3, qcdsj is only calculated for the current contributions and Equation 3.8 is used for the purpose of verifying the capacitances during the parameter extraction process, explained in Section 4.2.1. The current generated from  $C_{cer}$  is computed within the total collector current (icc) which is the sum of icp and iccer.

$$icgd = C_{gd} \cdot \frac{dV_{gd}}{dt}$$

3.28

$$iccer = C_{cer} \cdot \frac{dV_{ds}}{dt}$$

3.29

## 3.6 Temperature Scaling

The model contains temperature scaling capabilities via eight parameters: tauhltexp, kptexp, kftexp, bvntexp, bvftexp, vtdtco, vttco, and isnetexp. The first step in the temperature scaling process is to adjust model parameters so that the simulated data overlays the measured data at room temperature and set all temperature scaling parameters to zero. After room temperature validation has been completed, only the parameters with temperature scaling parameters can be changed: tauhl, kp, kf, bvn, bvf, vtd, vt, isne. The following equations are then used to extract the temperature scaling parameters externally after the parameter extraction sequences have been performed. This technique involves both nonlinear and linear scaling. The nonlinear temperature scaling equations are represented by Equations 3.30 through 3.35. The linear temperature scaling equations are designed for vt and vtd, and are represented by Equations 3.36 and 3.37 [26].

$$tauhlt = tauhl_{300} \cdot \left[\frac{templim}{tnom}\right]^{tauhltexp}$$

3.30

$$kpt = kp_{300} \cdot \left[\frac{tnom}{templim}\right]^{kptexp}$$

3.31

$$kft = kf_{300} \cdot \left[\frac{tnom}{templim}\right]^{kftexp}$$

3.32

$$isnet = isne_{300} \cdot \left[\frac{templim}{tnom}\right]^{isnetexp} \cdot e^{1.4 \cdot \left(\frac{1}{tnom} - \frac{1}{templim}\right)}$$

3.33

$$bvnt = bvn_{300} \cdot \left[\frac{templim}{tnom}\right]^{bvntexp}$$

3.34

$$bvft = bvf_{300} \cdot \left[\frac{templim}{tnom}\right]^{bvftexp}$$

3.35

$$vtt = vt_{300} \cdot vttco(templim - tnom)$$

3.36

$$vtdt = vtd_{300} \cdot vtdtco(templim - tnom)$$

3.37

## **Chapter 4** Updating the Unified IGBT Model

To update the Unified IGBT model, SiC mobility equations were researched and a parameter extraction sequence was created.

## 4.1 Equations and Temperature Dependence

## **4.1.1** Mobility Model

To estimate the carrier mobility within the IGBT, the bulk mobility within the drift region is modeled and, thus, is dependent on the drift region doping concentration and the temperature of the device. The mobility model is implemented via four main mobility equations: Si electron, Si hole, SiC electron, and SiC hole. The electron mobility is expressed as *mun*, or *mun*0; where *mun*0 represents the mobility before temperature scaling has been applied, and *mun* represents the electron mobility after temperature scaling effects have been applied. *mup* and *mup*0 represent the hole mobility in the same way. If n-channel is selected as an option by the user, *mun*0 will be equal to its calculated mobility equation, and *mup*0 will be equal to its minority carrier mobility constant value. If p-channel is selected, *mun*0 will be equal to the minority carrier constant, and *mup*0 will be equal to it calculated mobility equation, as shown in Equations 4.1 through 4.4 within Tables 4.1 and 4.2

The Si mobility equations and their estimated constants are taken from [3], as the mobility of Si has been studied extensively. The equations associated with the Si mobility model are shown below. The implementation of the temperature dependence of these mobility equations will be described in section 4.1.3.

Table 4.1 Si n-channel Initial Mobility Equations

| Si n-channel                                                     |       |            |       |  |

|------------------------------------------------------------------|-------|------------|-------|--|

| $mun0 = \frac{5.1E18 + 92 \cdot nb^{0.91}}{3.75E15 + nb^{0.91}}$ | (4.1) | mup0 = 495 | (4.2) |  |

Table 4.2 Si p-channel Initial Mobility Equations

| Si p-channel |       |                                                                    |       |

|--------------|-------|--------------------------------------------------------------------|-------|

| mun0 = 1360  | (4.3) | $mup0 = \frac{2.9E15 + 47.7 \cdot nb^{0.76}}{5.86E12 + nb^{0.76}}$ | (4.4) |

## **4.1.2 Updated SiC Equations**

The basic form of the SiC mobility equations is shown in Equation 4.5. Using the fitting parameters presented in [29] and [30] the SiC n- and p-channel mobility models are implemented, respectively. Table 4.3 organizes the SiC fitting parameters from each of the mobility models. The electron constant is taken from [3], and the hole constant is taken from [31]. The rest of the fitting parameters are cited from their respective mobility equation references. Equations 4.6 through 4.9 reveal the SiC n- and p-channel mobility equations with fitting parameters included.

$$mobility = \mu_{min} + \frac{\mu_{max} - \mu_{min}}{1 + \left(\frac{nb}{N_{ref}}\right)^{\alpha}}$$

$$4.5$$

Table 4.3 SiC Mobility Model Parameters

|            | $\mu_{min}$ | $\mu_{max}$ | $N_{ref}$ | α    | Constant |

|------------|-------------|-------------|-----------|------|----------|

| SiC n [29] | 0           | 977         | 1.17E17   | 0.49 | 1140     |

| SiC p [30] | 0           | 113.5       | 2.4E18    | 0.69 | 175      |

Table 4.4 SiC n-channel Initial Mobility Equations

| SiC n-channel                                                   |       |            |       |

|-----------------------------------------------------------------|-------|------------|-------|

| $mun0 = \frac{977}{1 + \left(\frac{nb}{1.17E17}\right)^{0.49}}$ | (4.6) | mup0 = 175 | (4.7) |

Table 4.5 SiC p-channel Initial Mobility Equations

SiC p-channel

$$mun0 = 1140 (4.8) mup0 = \frac{113.5}{1 + \left(\frac{nb}{2.4E18}\right)^{0.69}} (4.9)$$