## University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2015

## Experimental Verification and Integration of a Next Generation Smart Power Management System

Tavis Clemmer University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the Energy Systems Commons, Oil, Gas, and Energy Commons, and the Power and Energy Commons

## Recommended Citation

Clemmer, Tavis, "Experimental Verification and Integration of a Next Generation Smart Power Management System" (2015). Theses and Dissertations. 1040.

http://scholarworks.uark.edu/etd/1040

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

| Experimental Verification and Integration of a Next Generation Smart Power Management System |  |

|----------------------------------------------------------------------------------------------|--|

|                                                                                              |  |

|                                                                                              |  |

|                                                                                              |  |

|                                                                                              |  |

|                                                                                              |  |

|                                                                                              |  |

# Experimental Verification and Integration of a Next Generation Smart Power Management System

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

By

Tavis B. Clemmer University of Arkansas Bachelor of Science in Electrical Engineering, 2011

> May 2015 University of Arkansas

| This thesis is approved for recomme | ndation to the Graduate Council |

|-------------------------------------|---------------------------------|

| Dr. Alan Mantooth                   | _                               |

| Thesis Director                     |                                 |

| Dr. Juan C. Balda                   | _                               |

| Committee Member                    |                                 |

| Dr. Simon Ang                       | Dr. Roy McCann                  |

| Committee Member                    | Committee Member                |

#### **ABSTRACT**

With the increase in energy demand by the residential community in this country and the diminishing fossil fuel resources being used for electric energy production there is a need for a system to efficiently manage power within a residence. The Smart Green Power Node (SGPN) is a next generation energy management system that automates on-site energy production, storage, consumption, and grid usage to yield the most savings for both the utility and the consumer. Such a system automatically manages on-site distributed generation sources such as a PhotoVoltaic (PV) input and battery storage to curtail grid energy usage when the price is high. The SGPN high level control features an advanced modular algorithm that incorporates weather data for projected PV generation, battery health monitoring algorithms, user preferences for load prioritization within the home in case of an outage, Time of Use (ToU) grid power pricing, and status of on-site resources to intelligently schedule and manage power flow between the grid, loads, and the on-site resources.

The SGPN has a scalable, modular architecture such that it can be customized for user specific applications. This drove the topology for the SGPN which connects on-site resources at a low voltage DC microbus; a two stage bi-directional inverter/rectifier then couples the AC load and residential grid connect to on-site generation. The SGPN has been designed, built, and is undergoing testing. Hardware test results obtained are consistent with the design goals set and indicate that the SGPN is a viable system with recommended changes and future work.

#### ACKNOWLEDGMENTS

First and foremost special thanks are due to the academic advisor, Dr. Mantooth. He has been a constant guide and mentor schooling me to become a more technically sound engineer. His work ethic, vision, and constant leadership were an inspiration to accomplish my every goal. Without him, I could not have accomplished what I have. Thanks are also due to Dr. McCann and Dr. Balda for assistance and a source of technical expertise in various aspects of this project. The students, faculty, and staff at The University of South Carolina are owed a great debt of gratitude for their contributions to the other major half of this project. Special thanks are due to the project leader at USC, Dr. Roger Dougal. He has been a source of great organization and experience to rely on as us students pursued our education and developed this project.

I would like to specially thank my friend and colleague Brian Stalling for laying much of the research and design work before I became part of this project. No matter the issue or how big the problem he was always happy to assist and contribute. His help with fielding the late night "epiphanies" on how to make a breakthrough was instrumental in keeping motivation. I could not have done this without him. Finally, I would like to thank Chris Farnell, Yuzhi Zhang, Janviere Umuhoza, Fahad Hossain, and Haoyan Liu for their contributions to the SGPN V1 & V2, as well as the support with this project.

## TABLE OF CONTENTS

| CHAP | TER 1 | INTRODUCTION                                         | . 1 |

|------|-------|------------------------------------------------------|-----|

| 1.1  | Need  | d for Residential Energy Management Systems          | . 1 |

| 1.2  | Curr  | rent On-Site Electrical Generation Systems Available | . 2 |

| 1.3  | Bene  | efits of Automated Energy Management                 | . 3 |

| 1.4  | Thes  | sis Organization                                     | . 4 |

| CHAP | ΓER 2 | THEORETICAL BACKGROUND                               | . 6 |

| 2.1  | Elec  | tromagnetic Interference                             | . 6 |

| 2.1  | 1.1   | EMI Overview                                         | . 6 |

| 2.2  | Radi  | to Frequency Modulation/Demodulation                 | 11  |

| 2.2  | 2.1   | Amplitude Modulation                                 | 12  |

| 2.2  | 2.2   | Frequency Modulation                                 | 13  |

| 2.2  | 2.3   | Amplitude Demodulation                               | 15  |

| 2.2  | 2.4   | Frequency Demodulation                               | 17  |

| 2.3  | Obje  | ect Oriented Programming Background                  | 18  |

| 2.3  | 3.1   | Procedural Programming                               | 18  |

| 2.3  | 3.2   | Modular Programming                                  | 19  |

| 2.3  | 3.3   | Data Abstraction                                     | 20  |

| 2.4  | Inrus | sh Current From Bulk Capacitance in Circuit          | 21  |

| 2.5  | Mac   | romodeling2                                          | 23  |

| 2.6  | Tran  | sformer Background                                   | 25  |

| 2.6.1 Ideal Transformer Calculations                                       | . 26 |

|----------------------------------------------------------------------------|------|

| 2.7 Low Frequency Ripple Induced on DC System from a Single-Phase Inverter | . 27 |

| CHAPTER 3 HARDWARE AND CONVERTER CONTROL DESIGN                            | . 31 |

| 3.1 SGPN System Level Formulation                                          | . 31 |

| 3.1.1 SGPN Hardware and Hardware Control                                   | . 32 |

| 3.1.2 System Level Control and Operation                                   | . 34 |

| 3.2 Phase Shifted PWM Generation Design                                    | . 37 |

| 3.2.1 Design Issue                                                         | . 37 |

| 3.2.2 Phase Shifted PWM Design                                             | . 39 |

| 3.3 Internal Sine Wave Reference Voltage Generation                        | . 42 |

| 3.4 System Level Operation Control Design and Related Topics               | . 43 |

| 3.4.1 System Level Hardware Modeling                                       | . 43 |

| 3.4.2 PV Boost Converter Control Design                                    | . 45 |

| 3.4.2.1 Switching Dynamics                                                 | . 46 |

| 3.4.2.2 Ripple Effect on Stability                                         | . 46 |

| 3.4.2.3 Macromodel and MATLAB Control Design                               | . 47 |

| 3.4.3 Hardware Changes                                                     | . 55 |

| 3.4.4 Inverter Control: Island Model                                       | . 57 |

| 3.4.4.1 Island Model Inverter Modeling                                     | . 57 |

| 3.4.4.2 Island Model Inverter Control Design                               | . 58 |

| 3.4.5 Control Isolation Design                                             | . 66 |

| 3.4.5.1 Isolation Design                                                         | 66   |

|----------------------------------------------------------------------------------|------|

| 3.4.5.2 Isolation Board Design                                                   | 68   |

| CHAPTER 4 SIMULATION RESULTS                                                     | 72   |

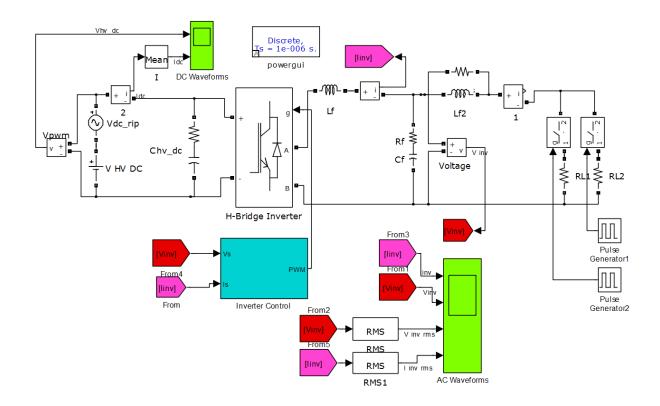

| 4.1 Closed Loop H-bridge Inverter                                                | 72   |

| 4.1.1 Island Model                                                               | 72   |

| 4.2 Full Inverter (FB DC-DC and H-Bridge Inverter)                               | 75   |

| 4.2.1 Island Model                                                               | 76   |

| 4.3 Closed Loop PV Boost Converter with Full Inverter                            | 81   |

| 4.3.1 Island Model                                                               | 81   |

| 4.3.2 Grid-Connected Model                                                       | 89   |

| 4.4 Closed Loop Battery Charge/Discharge Converter with Full Inverter            | 97   |

| 4.4.1 Island Model                                                               | 99   |

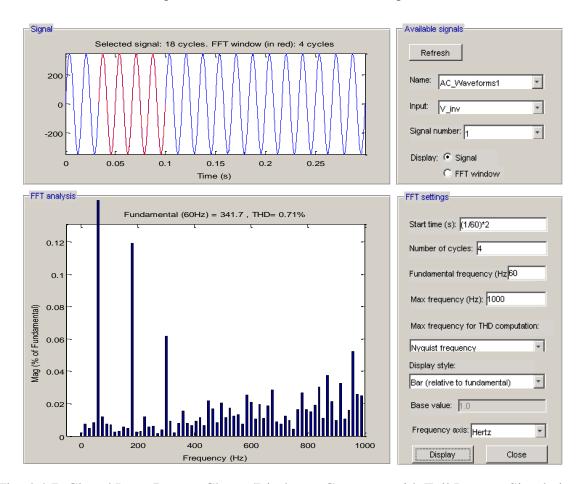

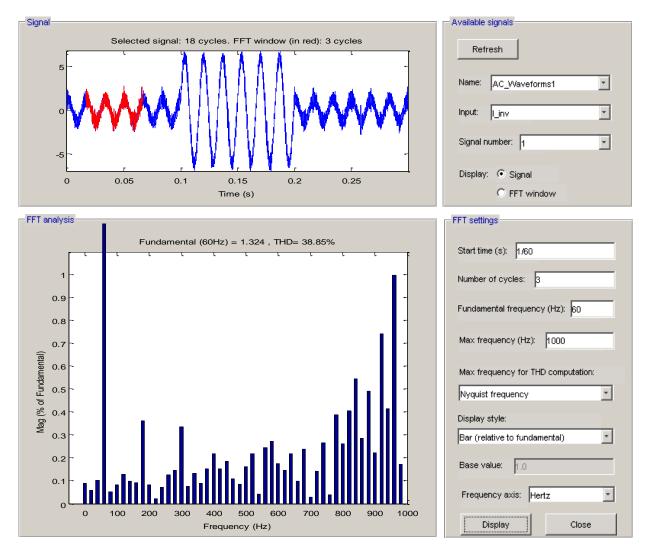

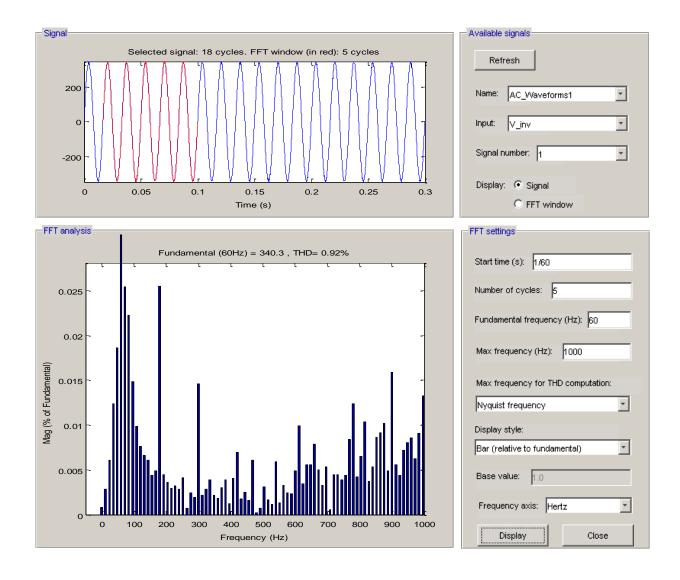

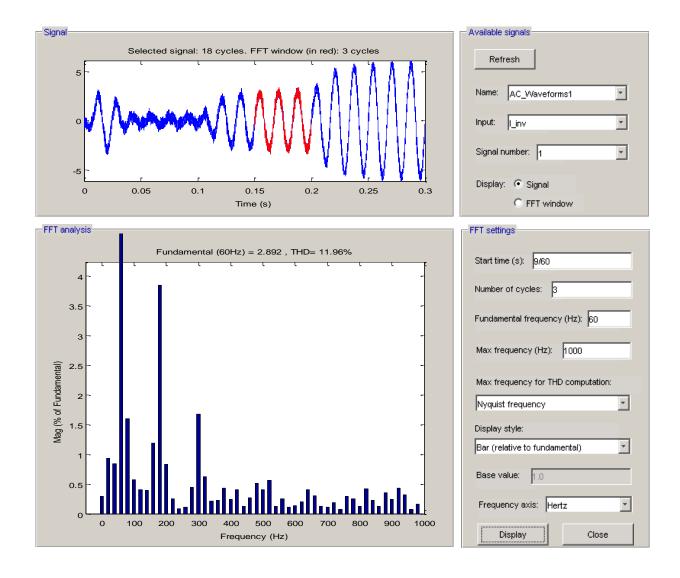

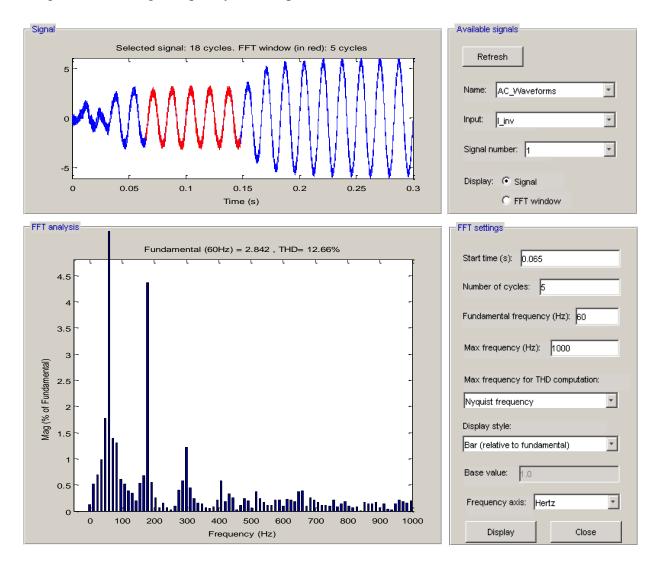

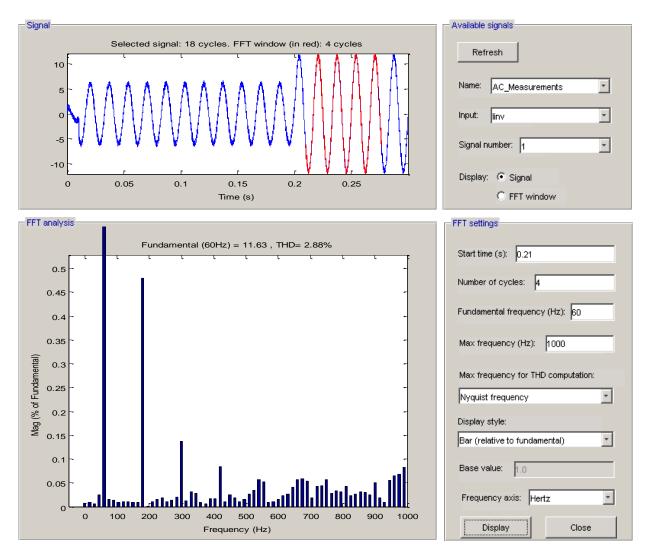

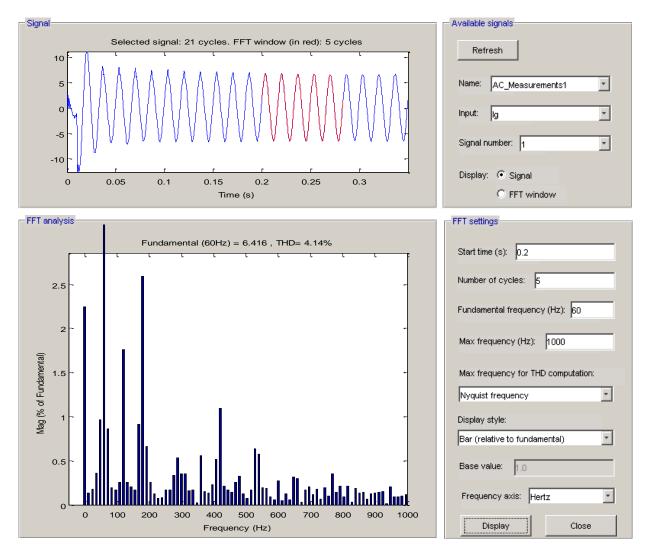

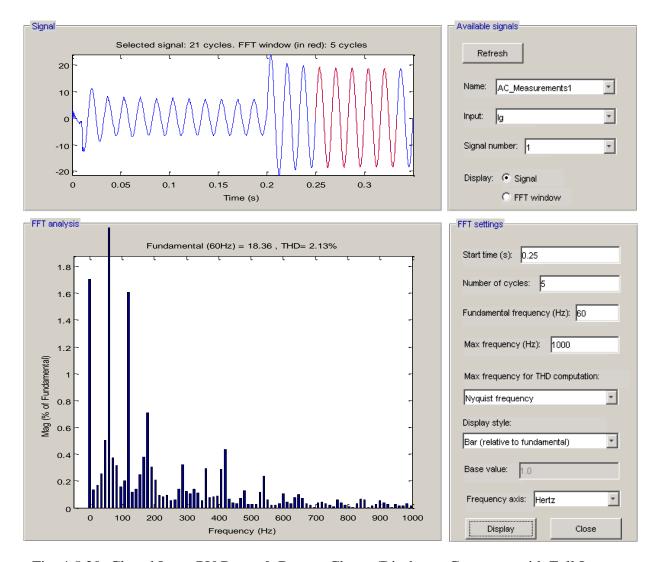

| 4.4.1.1 THD Analysis                                                             | 104  |

| 4.4.2 Grid Connected Model                                                       | 107  |

| 4.4.2.1 DC-AC Power Flow (Battery Discharge to Load)                             | 108  |

| 4.4.2.1.1 THD Analysis                                                           | 114  |

| 4.4.2.2 DC-AC Power Flow (Battery Discharge to Grid)                             | 117  |

| 4.4.2.2.1 THD Analysis                                                           | 122  |

| 4.5 Closed Loop Interleaved PV Boost and Battery Charge/Discharge Converter with | Full |

| Inverter                                                                         | 128  |

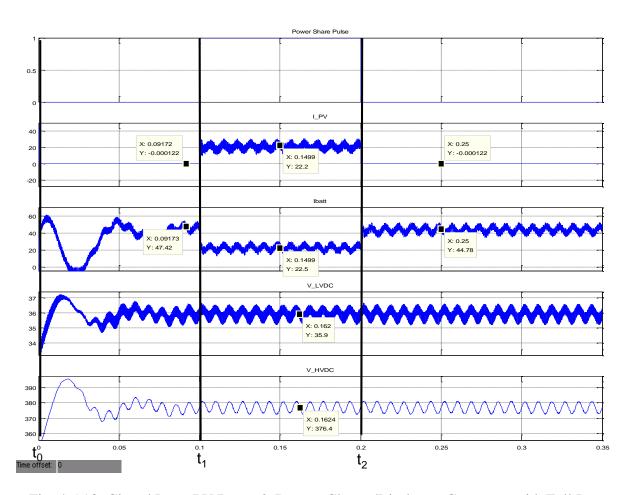

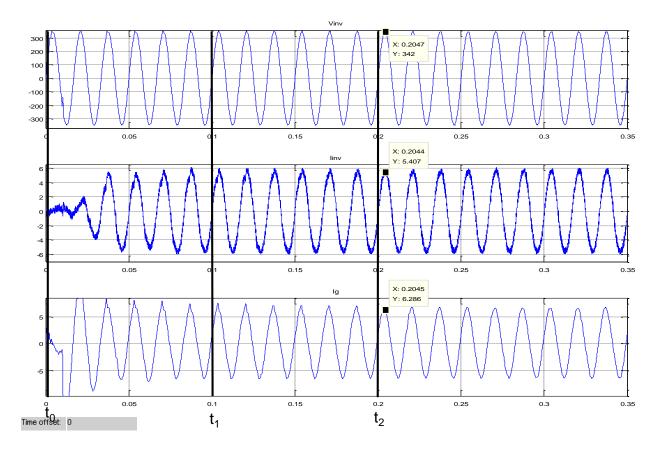

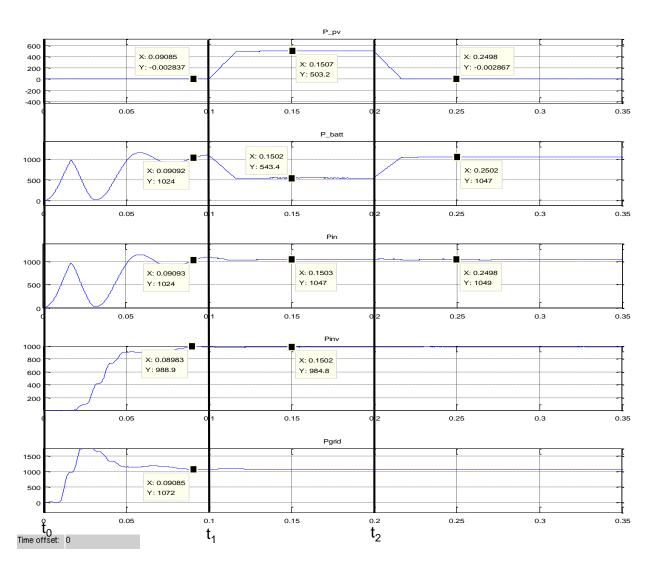

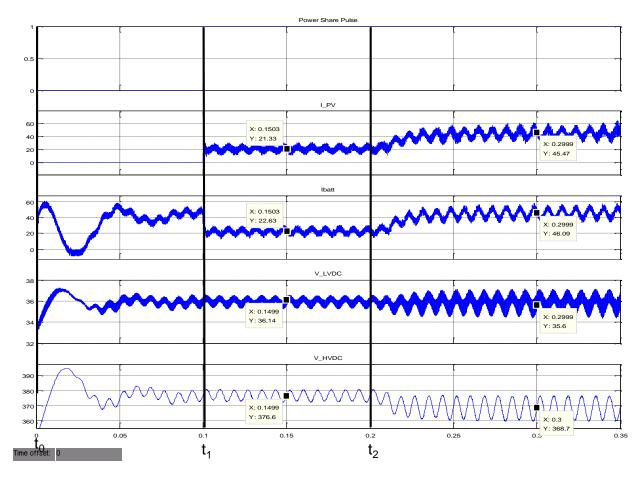

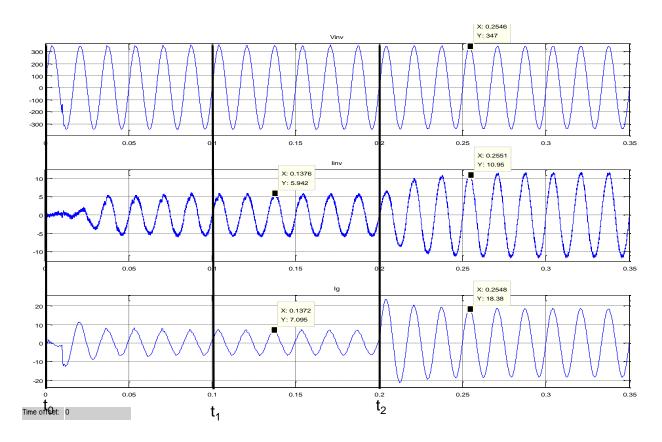

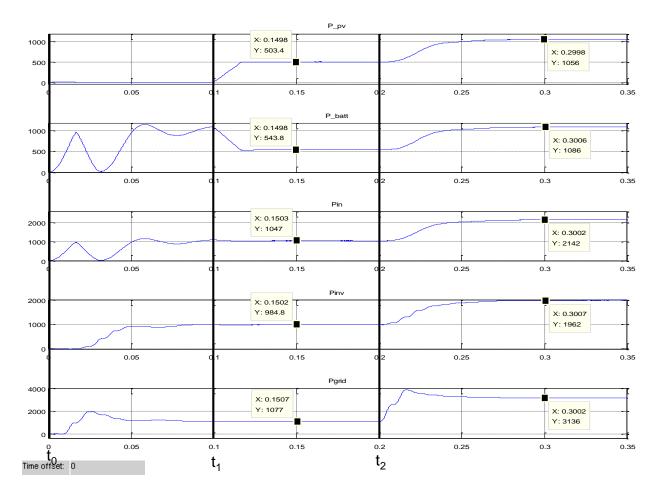

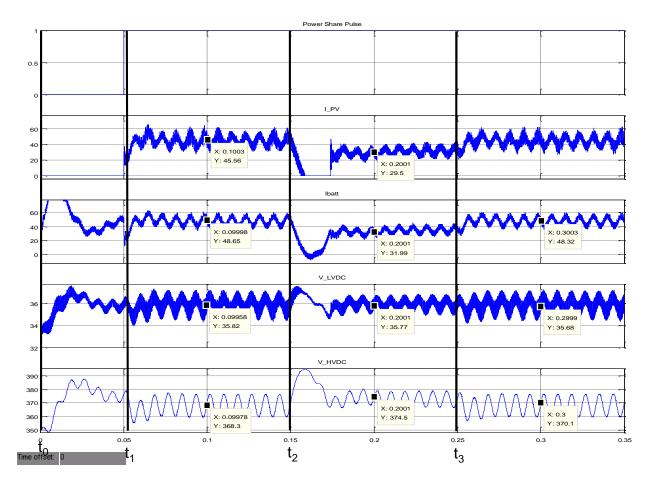

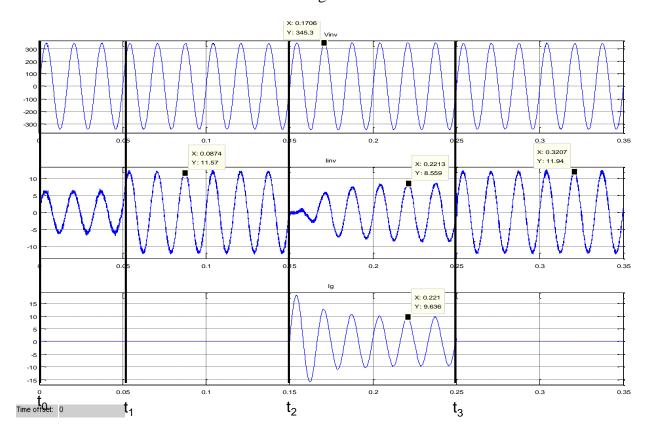

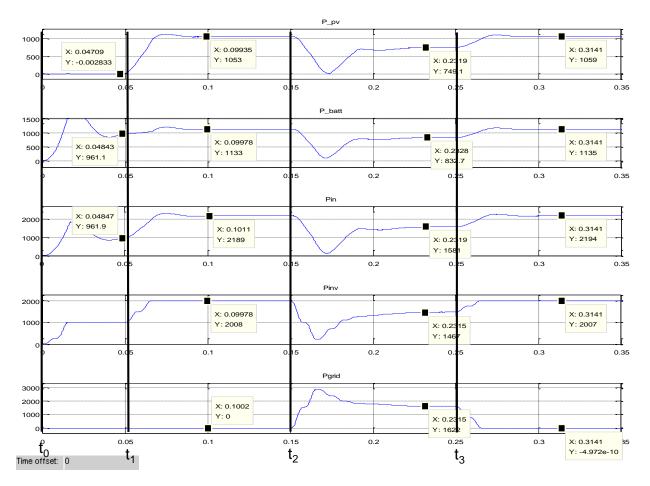

| 4.5.1 Island Model: Power Sharing Static Load                                    | 129  |

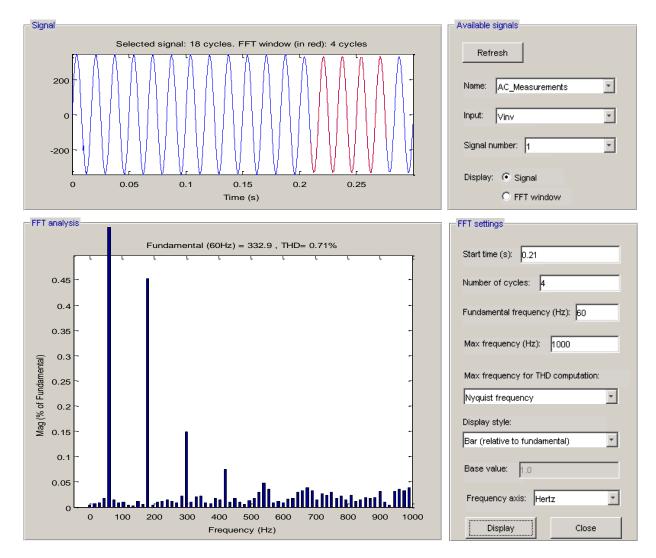

| 4.5.1.1 THD Analysis                                                                | 134  |

|-------------------------------------------------------------------------------------|------|

| 4.5.2 Island Model: Power Sharing Step Load                                         | 136  |

| 4.5.2.1 THD Analysis                                                                | 141  |

| 4.5.3 Grid Connected Model: Power Sharing Static Load                               | 143  |

| 4.5.3.1 THD Analysis                                                                | 148  |

| 4.5.4 Grid Connected Model: Power Sharing Step Load                                 | 149  |

| 4.5.4.1 THD Analysis                                                                | 154  |

| 4.6 Operating Mode Transitions                                                      | 155  |

| 4.6.1 Islanded - Grid Connected - Islanded Operation Mode Transitions with Interlea | aved |

| DC Inputs                                                                           | 156  |

| CHAPTER 5 CLOSED LOOP HARDWARE EXPERIMENTAL RESULTS AND                             |      |

| DISCUSSION                                                                          | .163 |

| 5.1 Isolation Board                                                                 | 163  |

| 5.2 Full-Bridge DC-DC Converter                                                     | 166  |

| 5.2.1 Phase-Shifted Gate PWM signals                                                | 167  |

| 5.2.2 Phase-Shifted PWM Dual Full Bridge DC-DC Converter Test Results               | 168  |

| 5.3 H-Bridge Inverter (Island Model)                                                | 170  |

| 5.3.1 Experimental Testing Consideration and Analysis                               | 173  |

| 5.4 Full Inverter (Island Model)                                                    | 177  |

| 5.5 PV Boost Converter with Full Bridge DC-DC Converter                             | 179  |

| 5.5.1 PV Boost and Full Bridge Integrated Results and Discussion                    | 179  |

| 5.6 Into  | egrated Hardware Test Results                                                | 182 |

|-----------|------------------------------------------------------------------------------|-----|

| 5.6.1     | Integration of Low Level Hardware Controls                                   | 183 |

| 5.6.2     | System Startup Sequence                                                      | 184 |

| 5.6.3     | PV Boost Converter with Full Inverter (Island Model)                         | 188 |

| 5.6.3.    | 1 Discussion on Efficiency                                                   | 193 |

| 5.6.4     | Battery Charge/Discharge Converter with Full Inverter                        | 195 |

| CHAPTER   | 6 CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORK                                | 202 |

| 6.1 SG    | PN Hardware Integration Summary                                              | 202 |

| 6.2 Rec   | commendations and Future Work                                                | 204 |

| 6.2.1     | Future Local Resources: Topology and Control Considerations                  | 204 |

| 6.2.2     | Synchronization with the Electric Grid/AC Generator                          | 205 |

| 6.2.3     | Human Machine or Graphical User Interface                                    | 206 |

| 6.2.4     | Improving Low Frequency DC Voltage and Current Ripple                        | 207 |

| 6.2.5     | Harmonic Filtering & Harmonic Mitigation Techniques                          | 208 |

| 6.2.6     | Future Work on SGPN Startup Sequence                                         | 209 |

| 6.2.7     | Recommendation for Improving Efficiency                                      | 211 |

| 6.2.8     | Improving Efficiency & Performance of the Full Bridge DC-DC converter        | 212 |

| 6.2.9     | Possibility of D-Q Control                                                   | 213 |

| 6.2.10    | Future Verification & Full System Integration with System Level Controller . | 213 |

| BIBLIOGRO | OPHY                                                                         | 216 |

## **TABLE OF FIGURES**

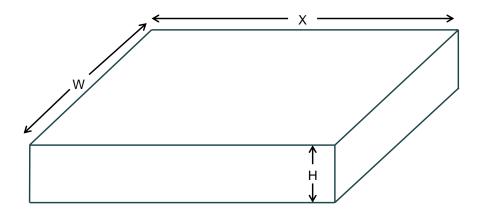

| Fig. 2.1.1: 3D - PC Board Trace                                                            | 7  |

|--------------------------------------------------------------------------------------------|----|

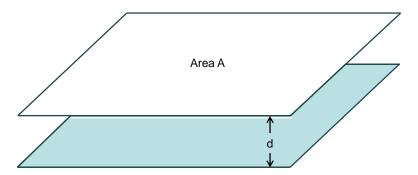

| Fig. 2.1.2: Layer – Layer Coincident PC Board Traces                                       | 8  |

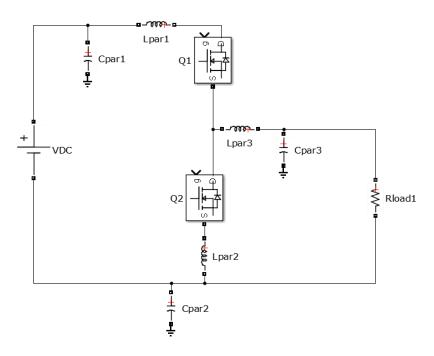

| Fig. 2.1.3: Half Bridge Schematic Example with Parasitic Elements                          | 9  |

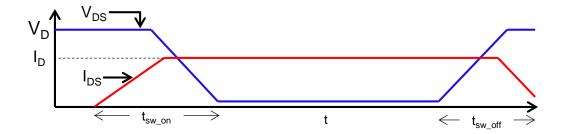

| Fig. 2.1.4: Device Turn-on/off Voltage and Current Waveforms                               | 10 |

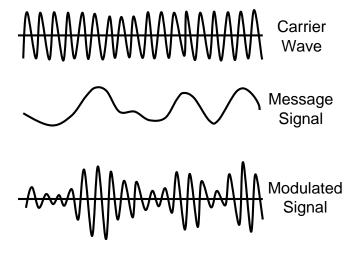

| Fig. 2.2.1: AM Modulated Signals                                                           | 13 |

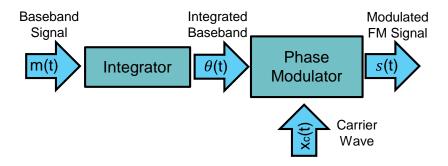

| Fig. 2.2.2: FM Modulation Basic Block Diagram                                              | 14 |

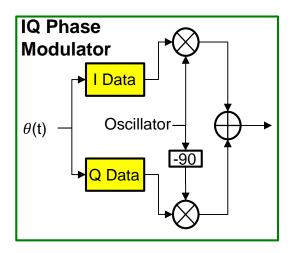

| Fig. 2.2.3: IQ Phase Modulation Block Diagram                                              | 15 |

| Fig. 2.2.4: Coherent AM Demodulation Block Diagram                                         | 16 |

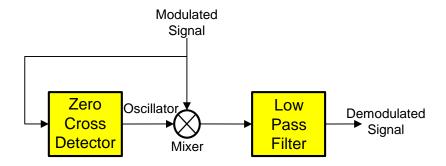

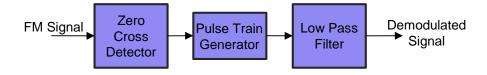

| Fig. 2.2.5: Zero-Crossing FM Demodulation Block Diagram                                    | 17 |

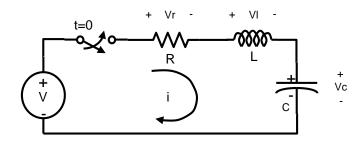

| Fig. 2.4.1: Series RLC Circuit                                                             | 22 |

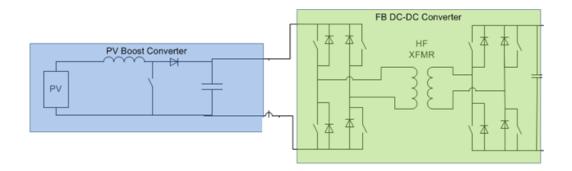

| Fig. 2.5.1: PV Boost & Dual FB DC-DC Converter Schematic                                   | 25 |

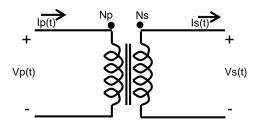

| Fig. 2.6.1: Ideal Transformer Equivalent Circuit                                           | 26 |

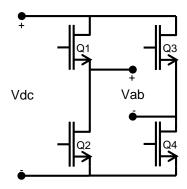

| Fig. 2.7.1: H-bridge Configuration Schematic                                               | 28 |

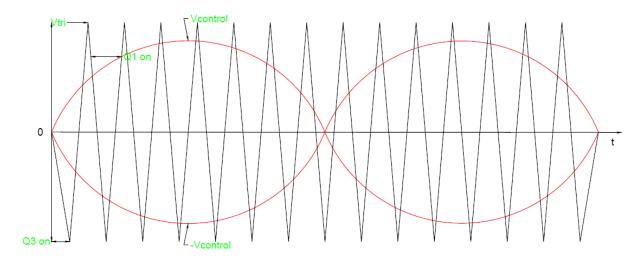

| Fig. 2.7.2: Uni-polar SPWM Generation Waveform                                             | 28 |

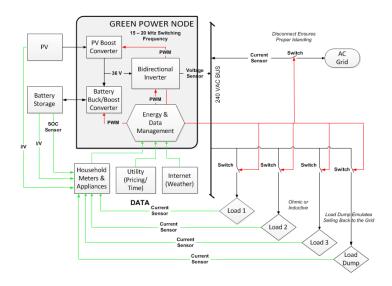

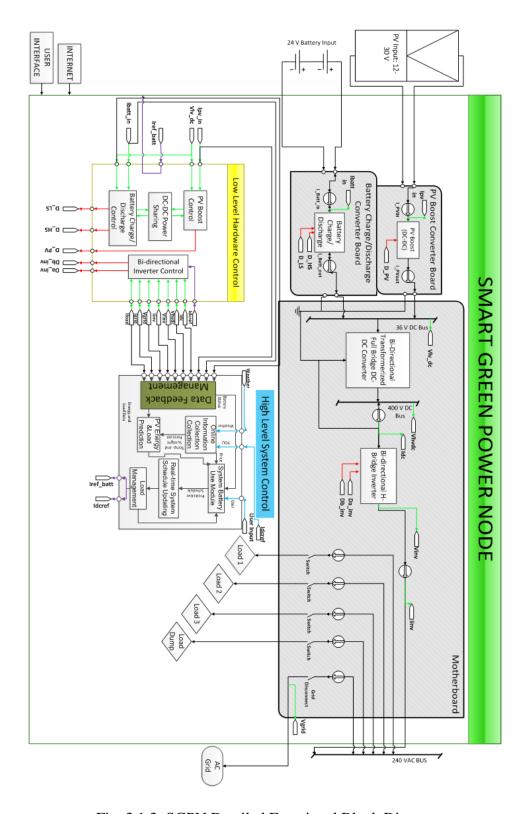

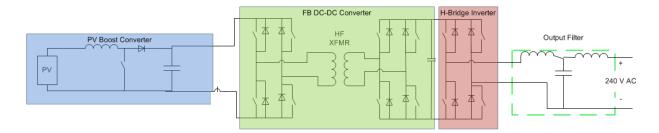

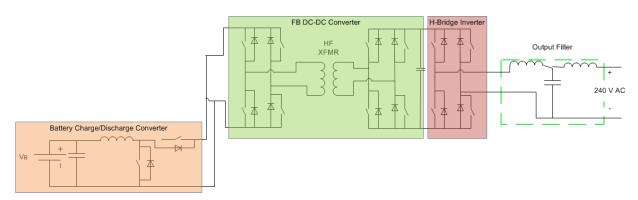

| Fig. 3.1.1: SGPN Basic Functional Block Diagram                                            | 32 |

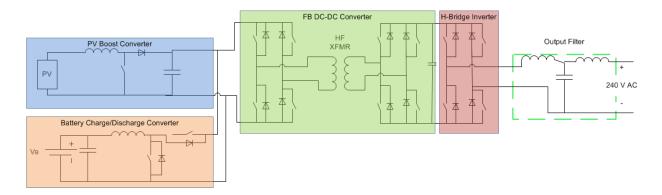

| Fig. 3.1.2: SGPN Hardware Topology Schematic                                               | 34 |

| Fig. 3.1.4: SGPN Detailed Functional Block Diagram                                         | 35 |

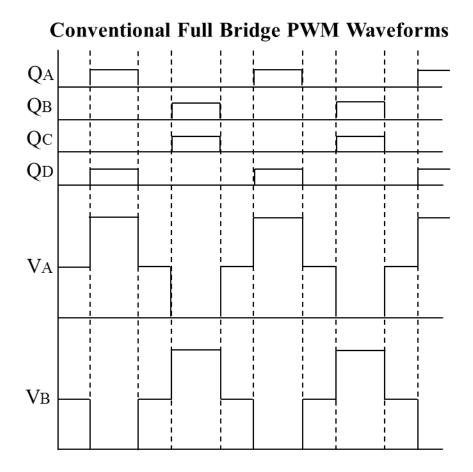

| Fig. 3.2.1: Bi-polar FB DC-DC Converter Switching Waveforms                                | 38 |

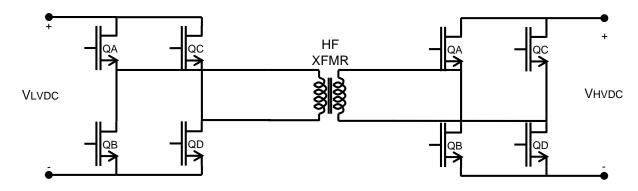

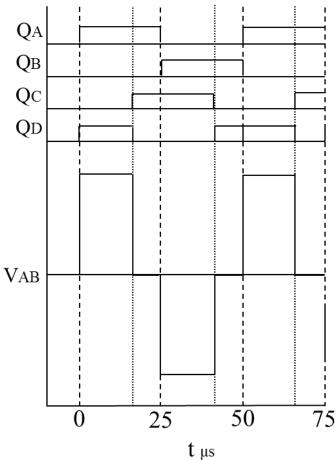

| Fig. 3.2.2: Dual FB DC-DC Converter Schematic                                              | 39 |

| Fig. 3.2.3: Phase-shifted Dual FB DC-DC Converter Switching Waveforms                      | 40 |

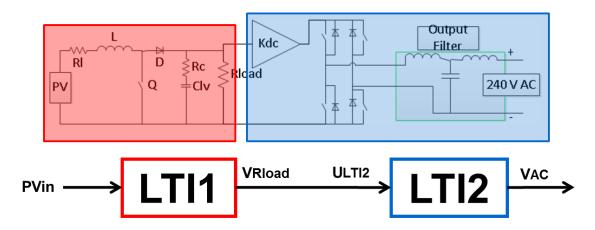

| Fig. 3.4.1: Example SGPN Operating Mode - Series Combination of LTI Systems                | 45 |

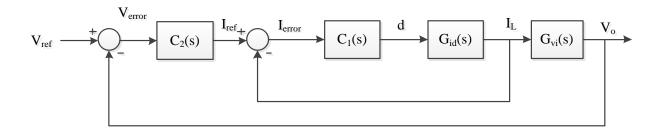

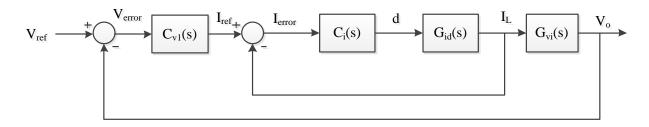

| Fig. 3.4.2: PV Boost Converter Control Loop Structure - Courtesy of Brian P. Stalling [11] | 49 |

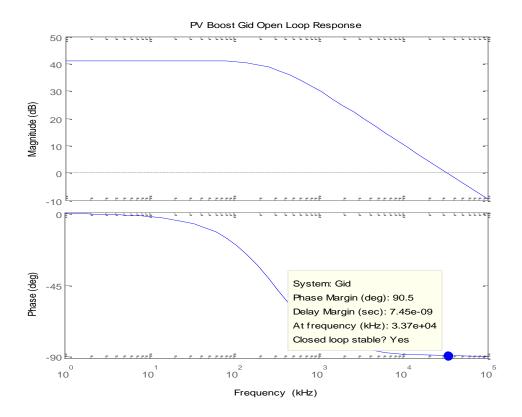

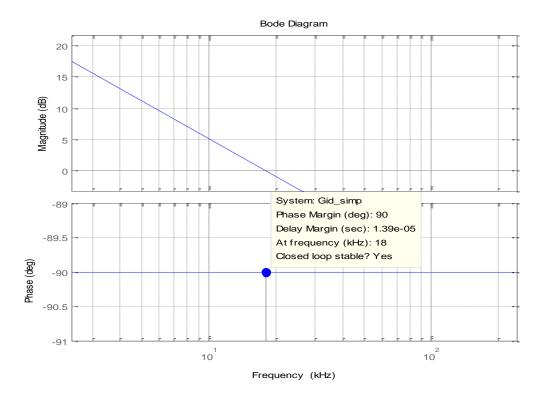

| Fig. 3.4.3: PV Boost Converter - Gid(s) Open Loop Bode Plot                               |

|-------------------------------------------------------------------------------------------|

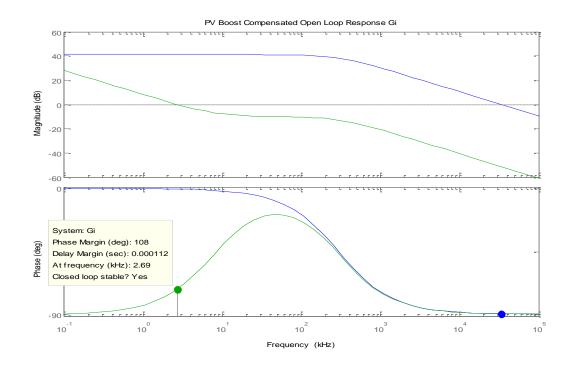

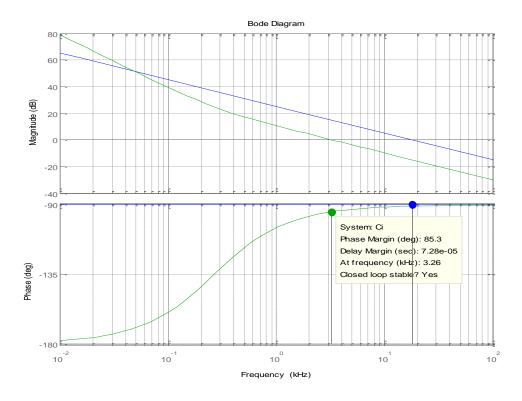

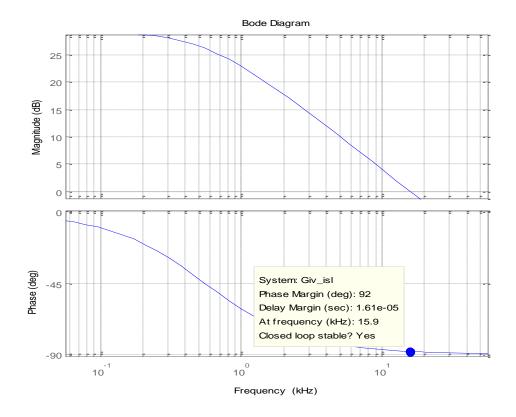

| Fig. 3.4.4: PV Boost Converter - Gi Compensated Open Loop Response Bode Plot 51           |

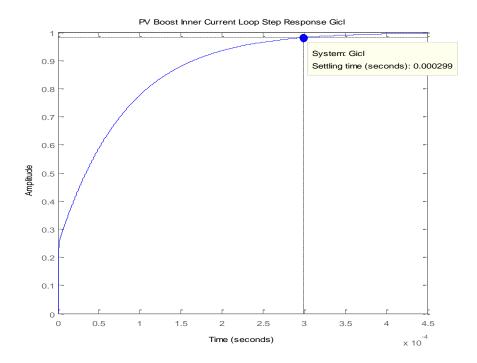

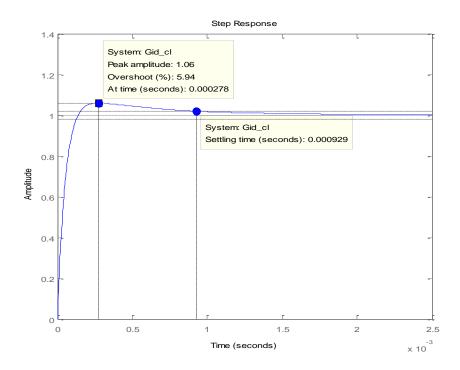

| Fig. 3.4.5: PV Boost Converter - Inner Current Loop Closed Loop Step Response             |

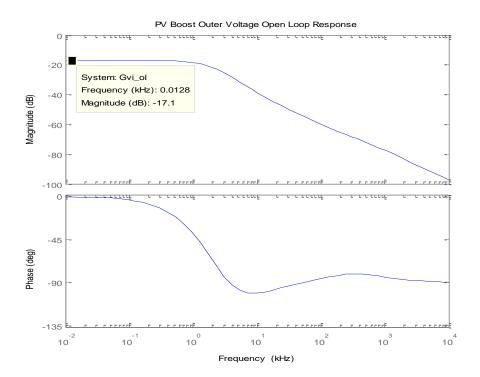

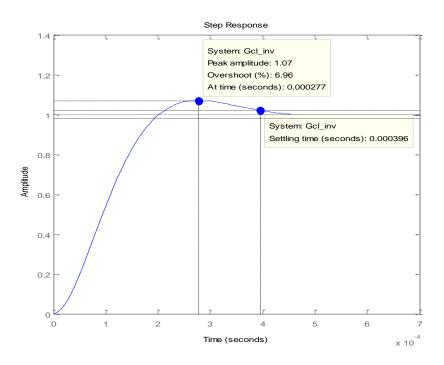

| Fig. 3.4.6: PV Boost Converter - Outer Voltage Loop Open Loop Response Bode Plot 53       |

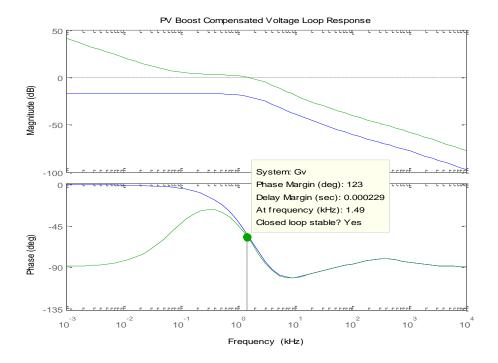

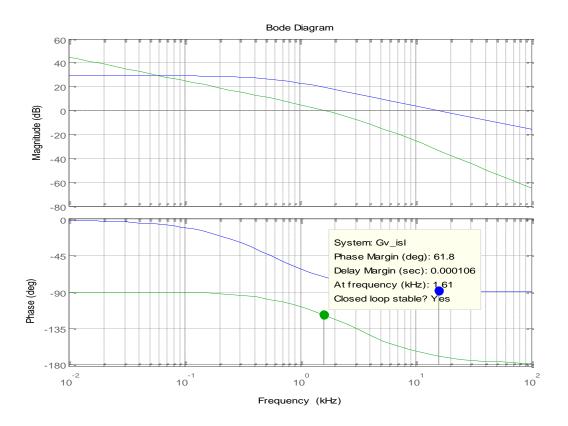

| Fig. 3.4.7: PV Boost Converter - Compensated Open Loop Voltage Loop Response Bode Plot 54 |

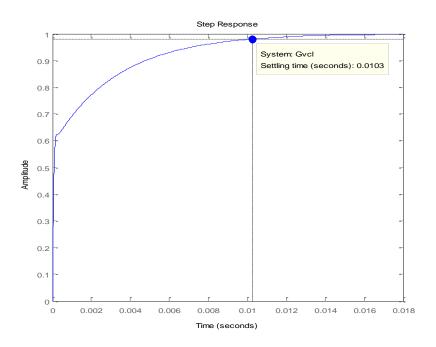

| Fig. 3.4.8: PV Boost Converter - Closed Loop Step Response                                |

| Fig. 3.4.9: H-bridge Inverter Control Loop Structure - Coutesy of Brian P. Stalling       |

| Fig. 3.4.10: H-bridge Inverter - Inner Current Loop Natural Circuit Response Bode Plot 60 |

| Fig. 3.4.11: H-bridge Inverter - Compensated Inner Current Loop Open Loop Response Bode   |

| Plot                                                                                      |

| Fig. 3.4.12: H-bridge Inverter - Inner Current Loop Closed Loop Step Response             |

| Fig. 3.4.13: H-bridge Inverter - Uncompensated Outer Voltage Loop Response Bode Plot 63   |

| Fig. 3.4.14: H-bridge Inverter - Compensated Outer Voltage Loop Response Bode Plot 64     |

| Fig. 3.4.15: H-bridge Inverter - Closed Loop Step Response                                |

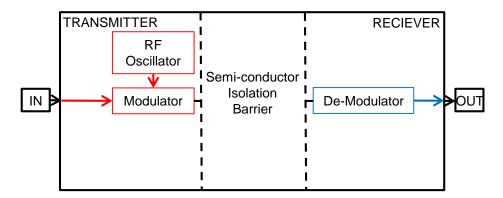

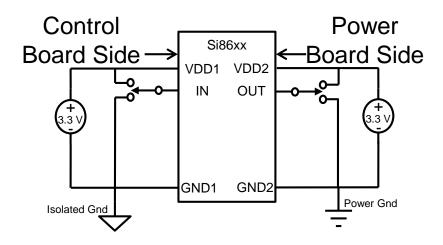

| Fig. 3.4.16: Si8660 Digital Isolation Chip - Functional Block Diagram                     |

| Fig. 3.4.17: Si8660 Digital Isolation Chip - Simplified Operational Schematic             |

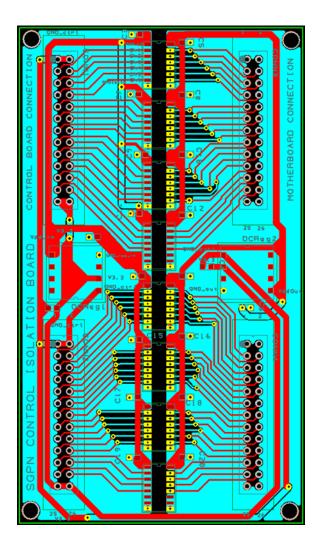

| Fig. 3.4.18: Control Isolation Board Layout                                               |

| Fig. 3.4.19: Populated Control Isolation Board Picture                                    |

| Fig. 4.1.1: H-bridge Inverter - Simulation Model                                          |

| Fig. 4.1.2: Closed Loop H-bridge Inverter Simulation – Islanded - AC Waveforms            |

| Fig. 4.1.3: Closed Loop H-bridge Inverter Simulation – Islanded - Power Waveforms         |

| Fig. 4.2.1: Closed Loop Full Inverter Simulation - Islanded - Simulation Model            |

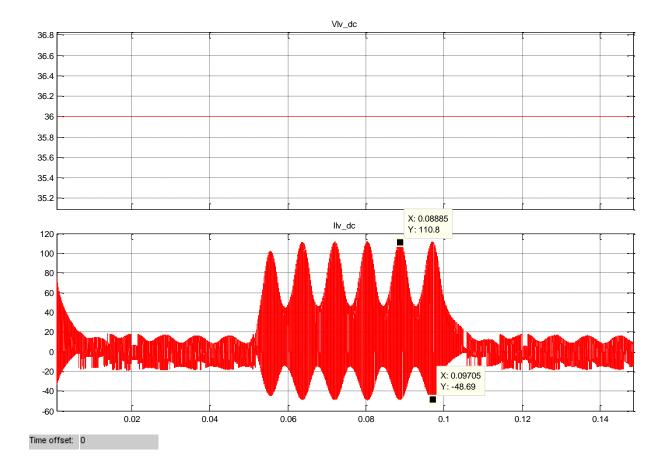

| Fig. 4.2.2: Closed Loop Full Inverter Simulation - Islanded - LV DC Waveforms             |

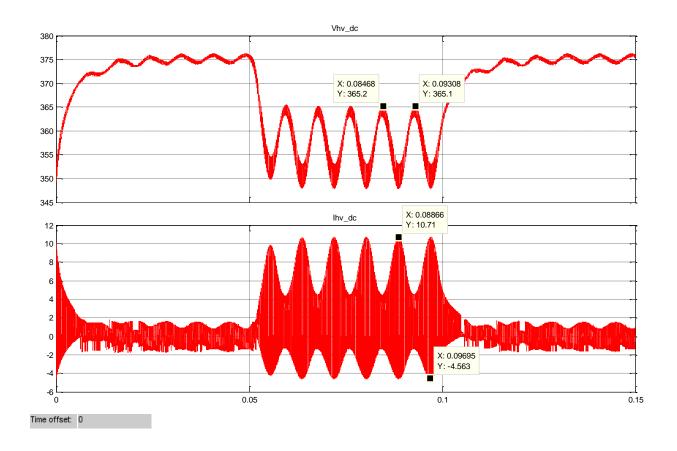

| Fig. 4.2.3: Closed Loop Full Inverter Simulation - Islanded - HV DC Waveforms                |

|----------------------------------------------------------------------------------------------|

| Fig. 4.2.4: Closed Loop Full Inverter Simulation - Islanded - AC Waveforms                   |

| Fig. 4.2.5: Closed Loop Full Inverter Simulation - Islanded - Power Waveforms                |

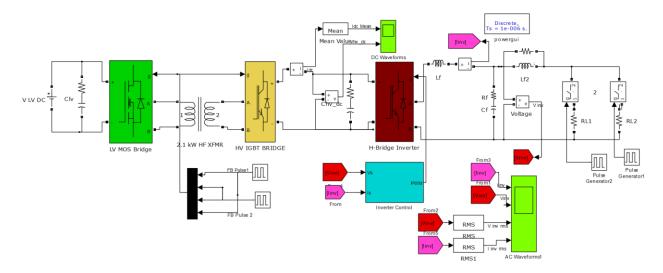

| Fig. 4.3.1: Closed Loop PV Boost Converter with Full Inverter Simulation - Islanded -        |

| Simulation Model                                                                             |

| Fig. 4.3.2: Closed Loop PV Boost Converter with Full Inverter Simulation – Islanded - DC     |

| Waveforms                                                                                    |

| Fig. 4.3.3: Closed Loop PV Boost Converter with Full Inverter Simulation – Islanded - AC     |

| Waveforms                                                                                    |

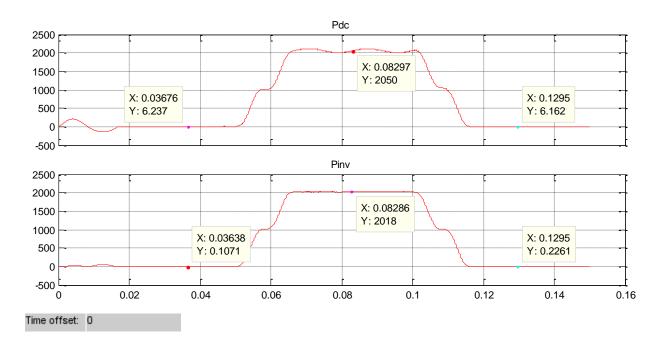

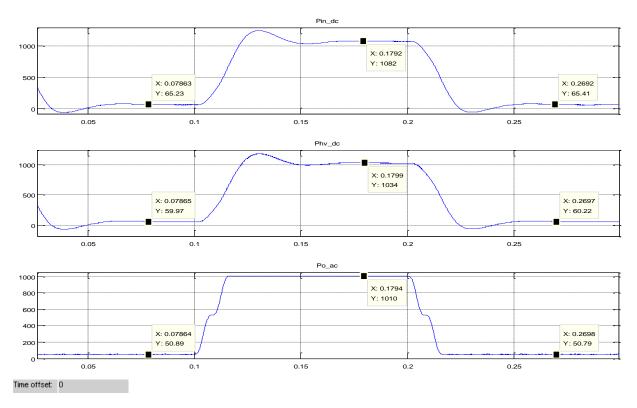

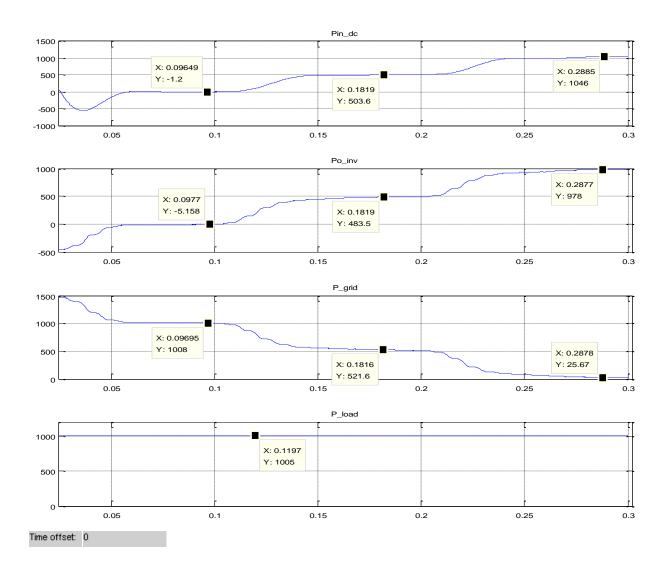

| Fig. 4.3.4: Closed Loop PV Boost Converter with Full Inverter Simulation – Islanded - Power  |

| Waveforms                                                                                    |

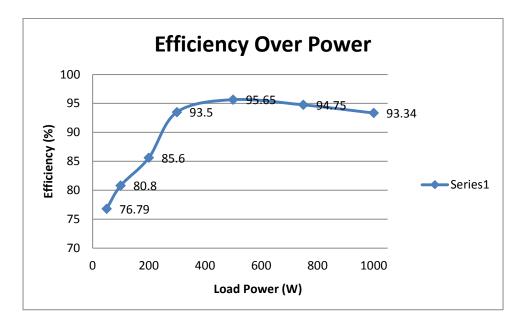

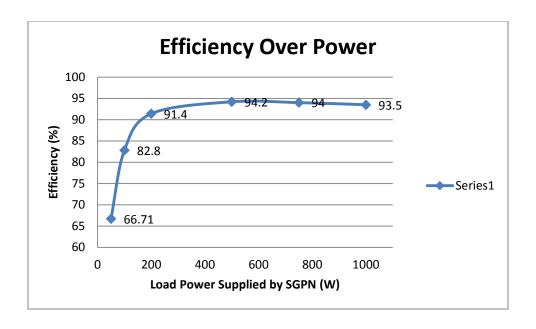

| Fig. 4.3.5: Closed Loop PV Boost Converter with Full Inverter Simulation – Islanded - System |

| Efficiency Over Power                                                                        |

| Fig. 4.3.6: Closed Loop PV Boost Converter with Full Inverter Simulation - Grid-Connected -  |

| DC Waveforms                                                                                 |

| Fig. 4.3.7: Closed Loop PV Boost Converter with Full Inverter Simulation - Grid-Connected -  |

| AC Waveforms                                                                                 |

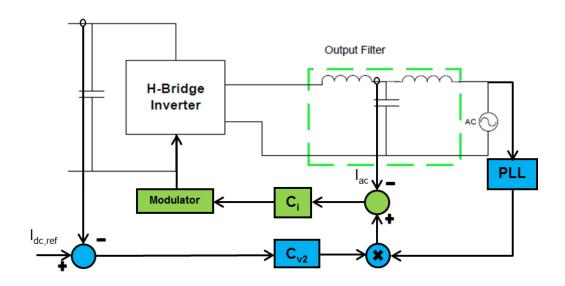

| Fig. 4.3.8: Closed Loop PV Boost Converter with Full Inverter Simulation - Grid-Connected –  |

| SGPN Power Flow Control Structure [36]                                                       |

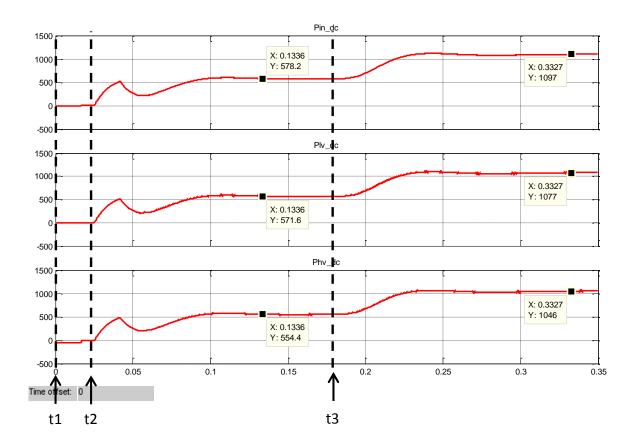

| Fig. 4.3.9: Closed Loop PV Boost Converter with Full Inverter Simulation - Grid-Connected –  |

| DC Power Waveforms                                                                           |

| Fig. 4.3.10: Closed Loop PV Boost Converter with Full Inverter Simulation - Grid-Connected - |

| AC Power Waveforms                                                                           |

| Fig. 4.3.11: Closed Loop PV Boost Converter with Full Inverter Simulation - Grid-Connected - |

|----------------------------------------------------------------------------------------------|

| System Efficiency Over Power                                                                 |

| Fig. 4.4.2: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -   |

| Simulation Model                                                                             |

| Fig. 4.4.3: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -   |

| Islanded - DC Waveforms                                                                      |

| Fig. 4.4.4: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -   |

| Islanded - AC Waveforms                                                                      |

| Fig. 4.4.5: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -   |

| Islanded - Power Waveforms 103                                                               |

| Fig. 4.4.6: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -   |

| Islanded - System Efficiency Over Power                                                      |

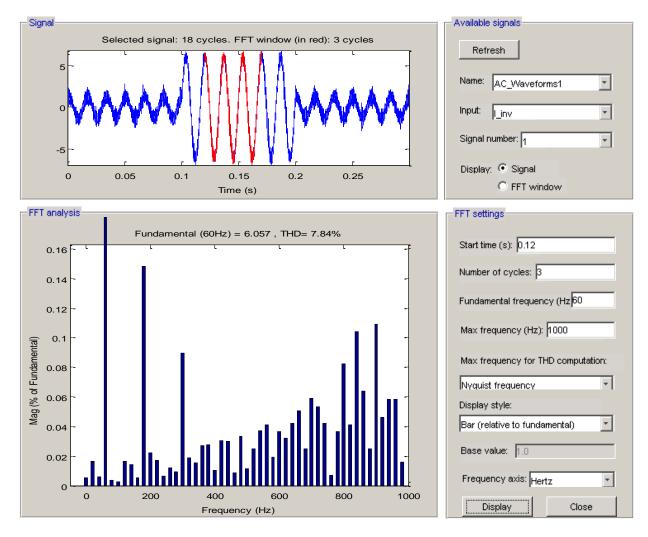

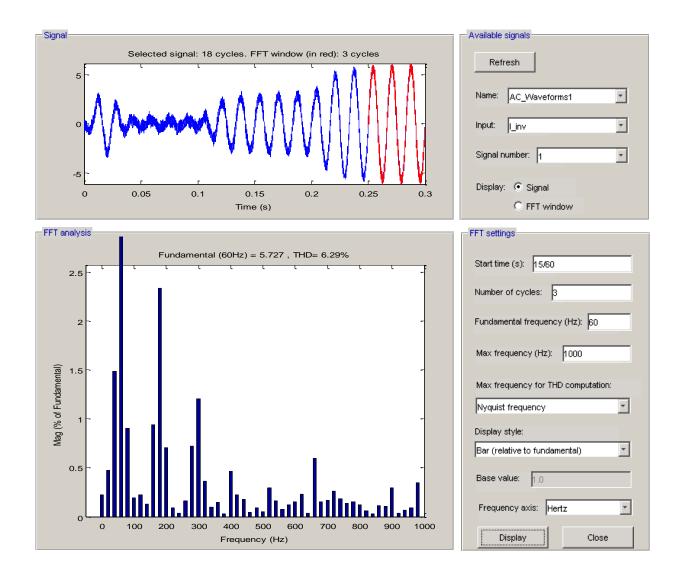

| Fig. 4.4.7: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -   |

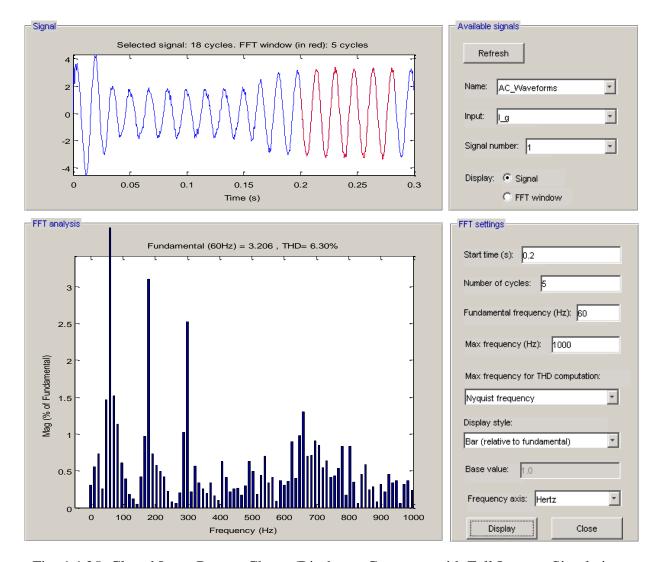

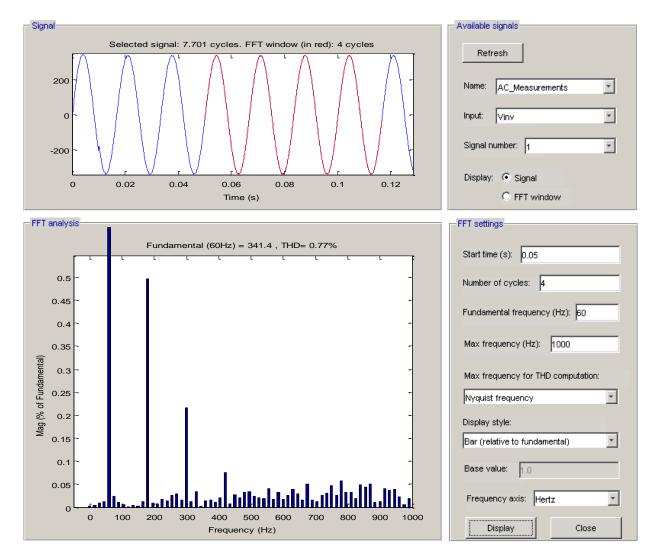

| Islanded - Voltage FFT                                                                       |

| Fig. 4.4.8: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -   |

| Islanded - Low Wattage Current FFT                                                           |

| Fig. 4.4.9: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -   |

| Islanded - High Wattage Current FFT                                                          |

| Fig. 4.4.10: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -  |

| Grid-Connected - DC Waveforms                                                                |

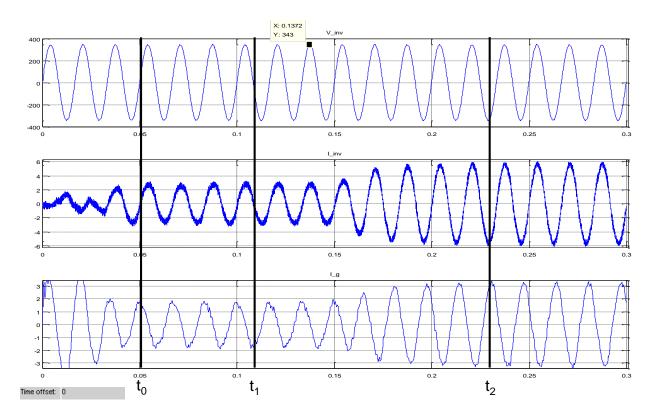

| Fig. 4.4.11: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -  |

| Grid-Connected - AC Waveforms                                                                |

| Fig. 4.4.12: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

|---------------------------------------------------------------------------------------------|

| Grid-Connected - Grid and Inverter Voltage Comparison                                       |

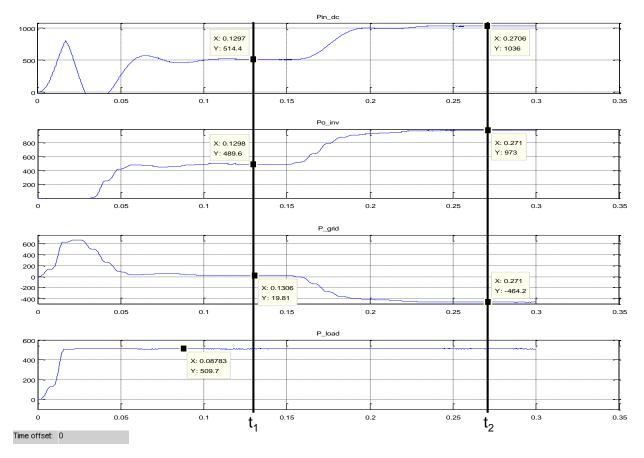

| Fig. 4.4.13: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected - Power Waveforms                                                            |

| Fig. 4.4.14: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected - System Efficiency Over Power                                               |

| Fig. 4.4.15: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected - Inverter Voltage FFT                                                       |

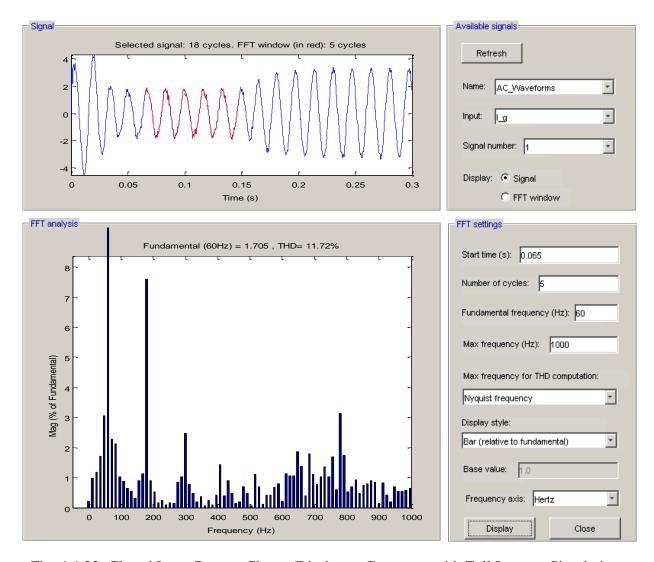

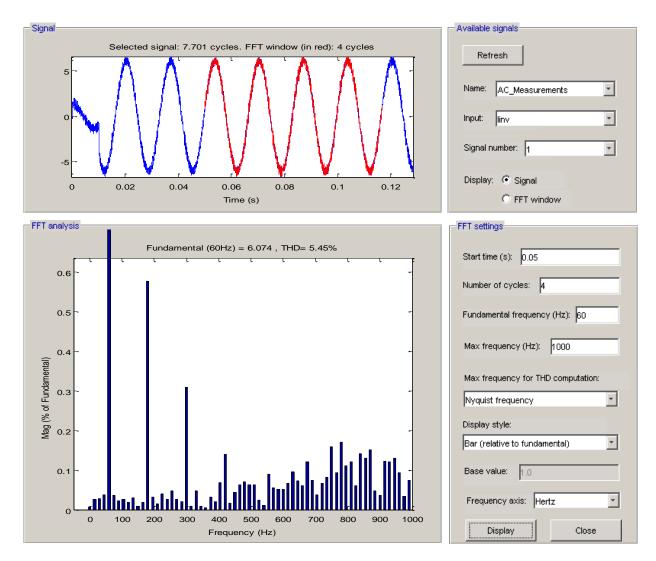

| Fig. 4.4.16: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected - Low Wattage Inverter Current FFT                                           |

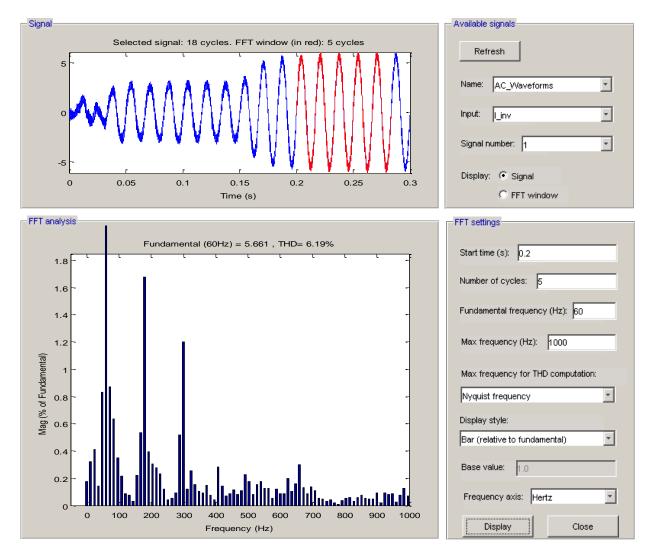

| Fig. 4.4.17: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected - High Wattage Inverter Current FFT                                          |

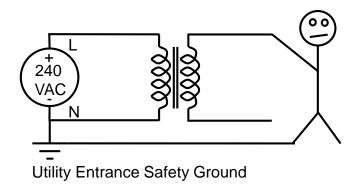

| Fig. 4.4.18: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

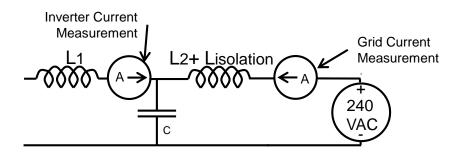

| Grid-Connected - Simplified Safety Isolation Transformer Schematic                          |

| Fig. 4.4.19: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected(Power to Grid) - AC Waveforms                                                |

| Fig. 4.4.20: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected(Power to Grid) - Power Waveforms                                             |

| Fig. 4.4.21: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected(Power to Grid) - Low Wattage Inverter Current FFT                            |

| Fig. 4.4.22: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Current Measurement Location Schematic                                                      |

| Fig. 4.4.23: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

|---------------------------------------------------------------------------------------------|

| Grid-Connected(Power to Grid) - Low Wattage Grid Current FFT                                |

| Fig. 4.4.24: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected(Power to Grid) - High Wattage Inverter Current FFT                           |

| Fig. 4.4.25: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation - |

| Grid-Connected(Power to Grid) - High Wattage Grid Current FFT                               |

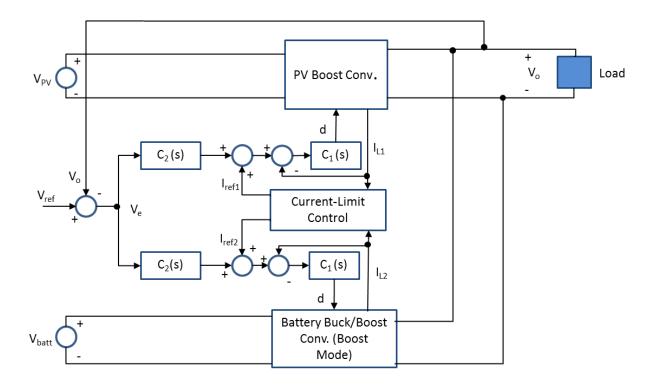

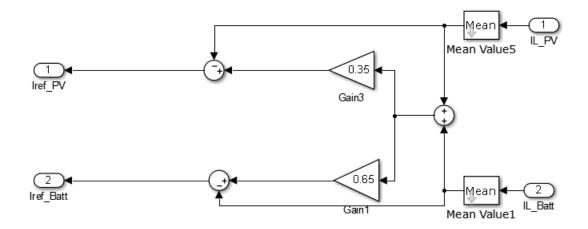

| Fig. 4.5.1: DC Power Sharing Network - Courtesy of Brian P. Stalling                        |

| Fig. 4.5.2: DC Power Sharing Network Current Limiting Control                               |

| Fig. 4.5.3: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter    |

| Simulation - Islanded - Static Load - DC Waveforms                                          |

| Fig. 4.5.4: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter    |

| Simulation - Islanded - Static Load - AC Waveforms                                          |

| Fig. 4.5.5: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter    |

| Simulation - Islanded - Static Load - Power Waveforms                                       |

| Fig. 4.5.6: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter    |

| Simulation - Islanded - Static Load - Voltage FFT                                           |

| Fig. 4.5.7: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter    |

| Simulation - Islanded - Static Load - Current FFT                                           |

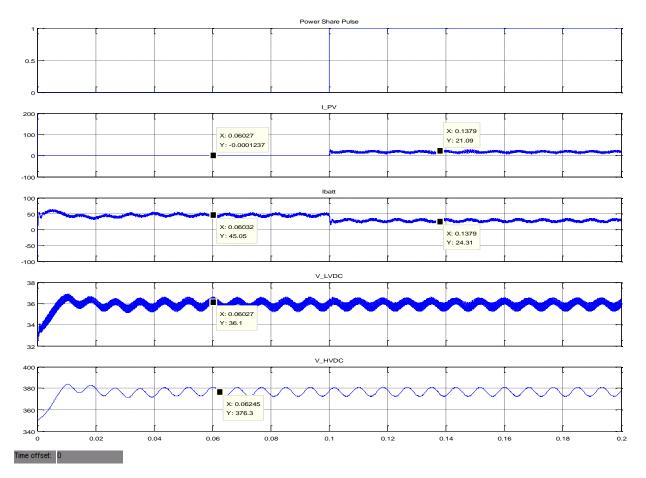

| Fig. 4.5.8: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter    |

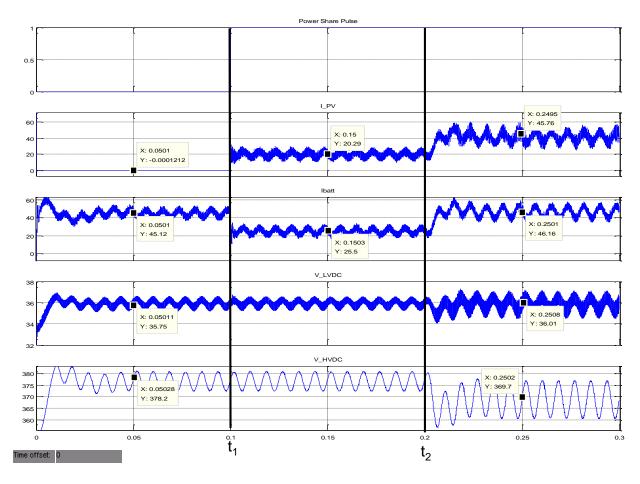

| Simulation - Islanded - Step Load - DC Waveforms                                            |

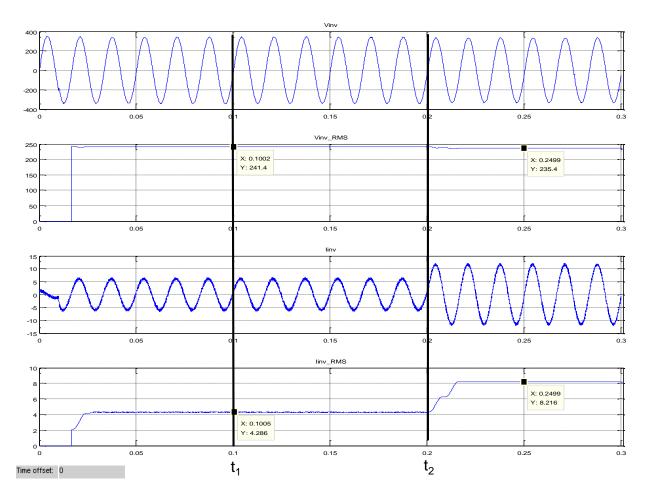

| Fig. 4.5.9: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter    |

| Simulation - Islanded - Step Load - AC Waveforms                                            |

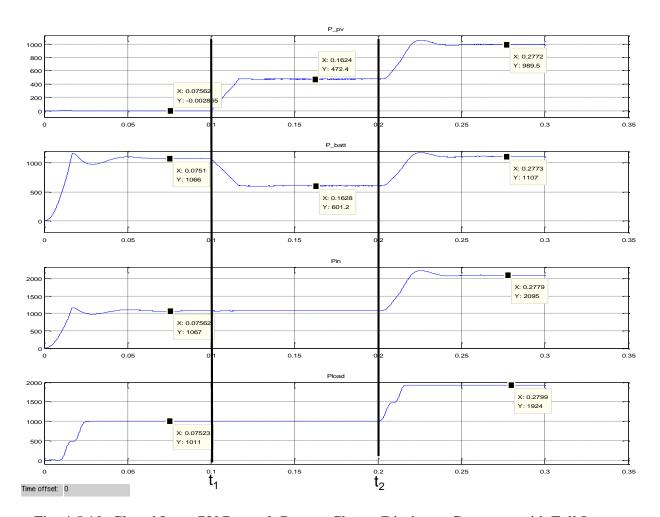

| Fig. 4.5.10: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

|-------------------------------------------------------------------------------------------|-----|

| Simulation - Islanded - Step Load - Power Waveforms                                       | 141 |

| Fig. 4.5.11: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Islanded - Step Load - Voltage FFT                                           | 142 |

| Fig. 4.5.12: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Islanded - Step Load - Current FFT                                           | 143 |

| Fig. 4.5.13: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Grid-Connected - Static Load - DC Waveforms                                  | 145 |

| Fig. 4.5.14: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Grid-Connected - Static Load - AC Waveforms                                  | 146 |

| Fig. 4.5.15: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Grid-Connected - Static Load - Power Waveforms                               | 147 |

| Fig. 4.5.16: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Grid-Connected - Static Load - Grid Current FFT                              | 149 |

| Fig. 4.5.17: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Grid-Connected - Step Load - DC Waveforms                                    | 151 |

| Fig. 4.5.18: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Grid-Connected - Step Load - AC Waveforms                                    | 152 |

| Fig. 4.5.19: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Grid-Connected - Step Load - Power Waveforms                                 | 153 |

| Fig. 4.5.20: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |     |

| Simulation - Grid-Connected - Step Load - Grid Current FFT                                | 155 |

| Fig. 5.5.3: Closed Loop PV Boost & FB DC-DC Converter Experimental Waveforms (Steady     |

|------------------------------------------------------------------------------------------|

|                                                                                          |

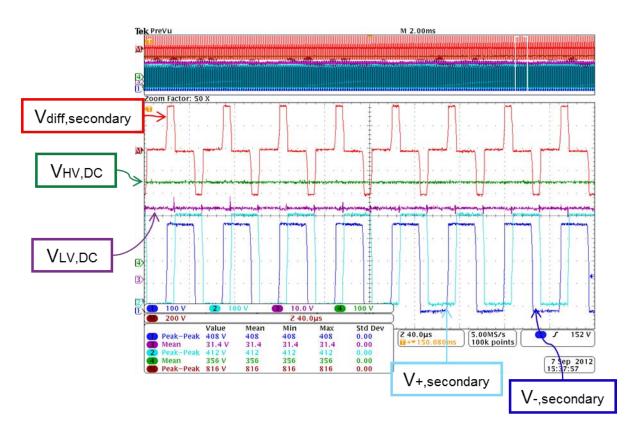

| Fig. 5.5.2: Closed Loop PV Boost & FB DC-DC Converter - FB Switching Detail Waveforms    |

| Fig. 5.5.1: Closed Loop PV Boost & FB DC-DC Converter Experimental Waveforms 180         |

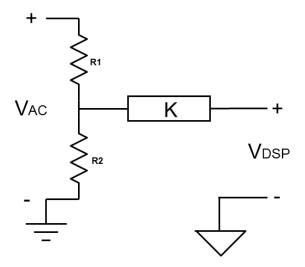

| Fig. 5.4.1. Closed Loop Full Inverter Experimental Waveforms (a)-top, (b)-bottom         |

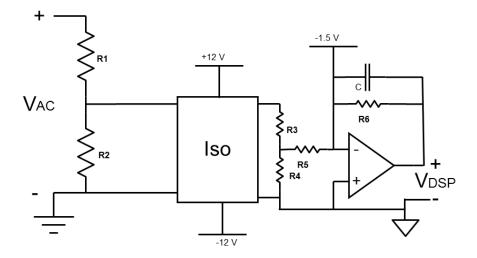

| Fig. 5.3.5: Measurement Board Simplified Schematic                                       |

| Fig. 5.3.4: Measurement Board Experimental Model Schematic                               |

| Fig. 5.3.3: Closed Loop Inverter Step Load - Zoomed In                                   |

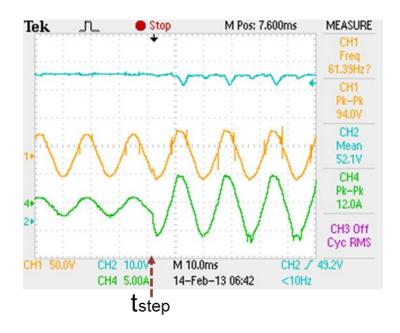

| Fig. 5.3.2: Closed Loop H-bridge Inverter Test Waveforms - Step Load                     |

| Fig. 5.3.1: Closed Loop H-bridge Inverter Test Waveforms – Static Load                   |

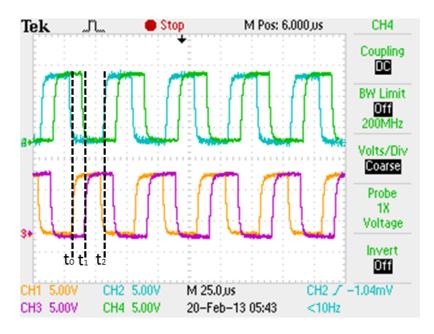

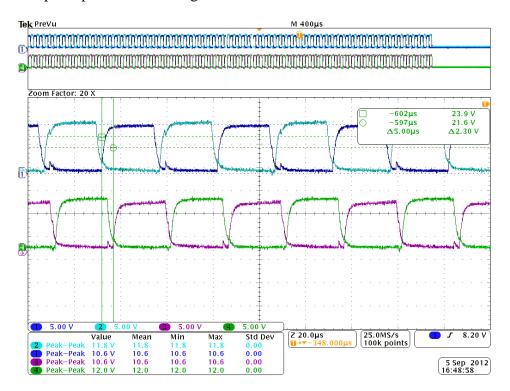

| Fig. 5.2.3: Phase-sifted FB DC-DC Converter Test Waveforms                               |

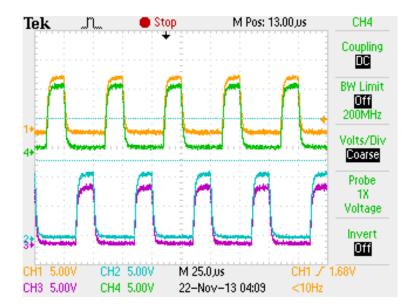

| Fig. 5.2.2: FB DC-DC Converter Device Switching - Phase-shifted                          |

| Fig. 5.2.1: Phase-shifted Gate Signals to FB DC-DC Converter                             |

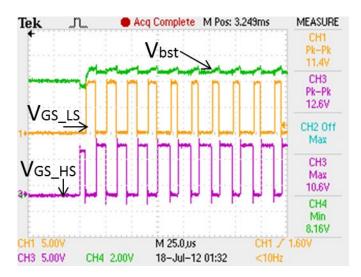

| Fig. 5.1.3: FB DC-DC Converter Device Gate Signals - with Isolation                      |

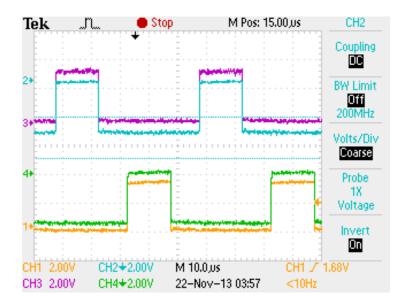

| Fig. 5.1.2: Full-bridge DC-DC Converter Device Switching Drive – with Isolation          |

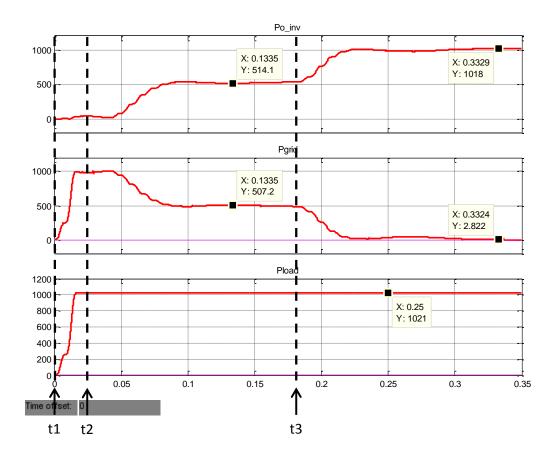

| Fig. 5.1.1: Half-bridge Configuration Device Switching - No Isolation                    |

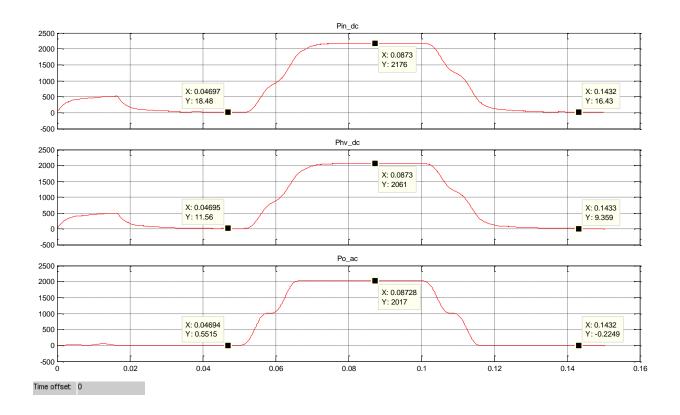

| Simulation - Operating Mode Transition - Power Waveforms                                 |

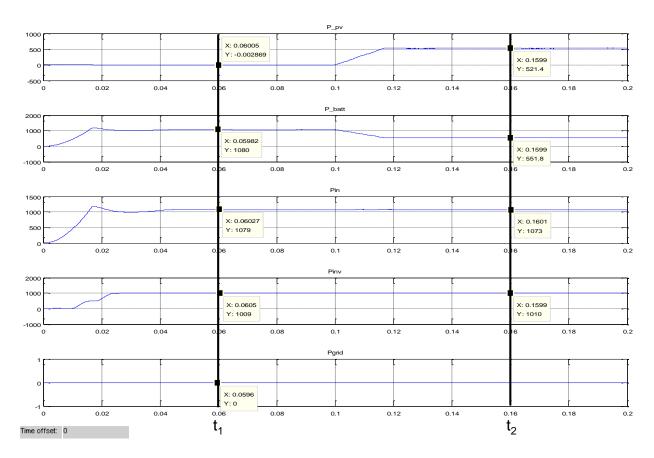

| Fig. 4.6.3: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |

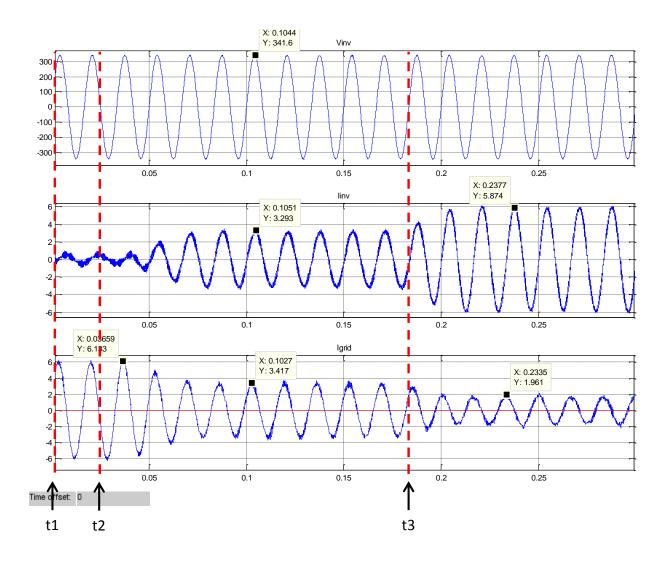

| Simulation - Operating Mode Transition - AC Waveforms                                    |

| Fig. 4.6.2: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |

| Simulation - Operating Mode Transition - DC Waveforms                                    |

| Fig. 4.6.1: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter |

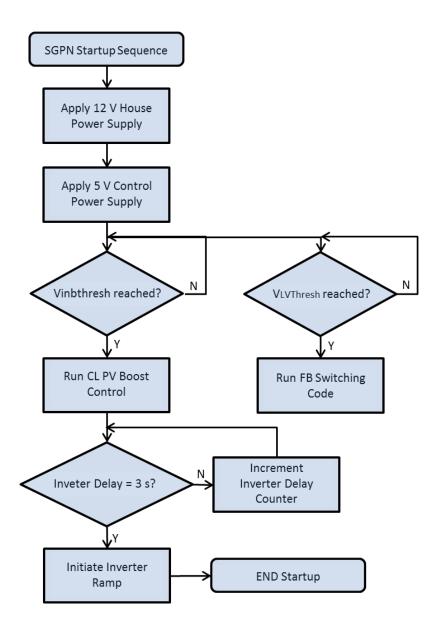

| Fig. 5.6.1: SGPN Startup Sequence Example Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

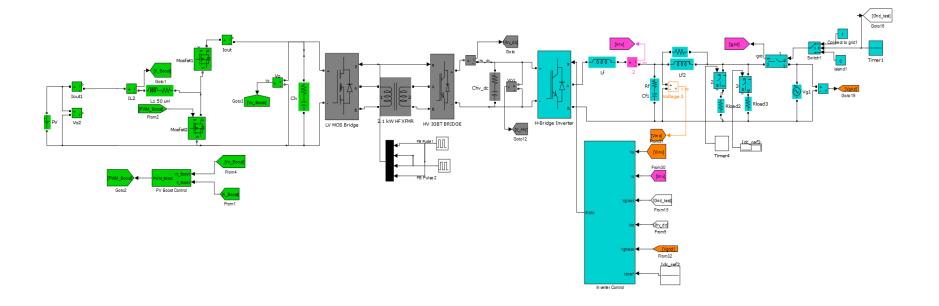

| Fig. 5.6.2: PV Boost Converter with Full Inverter Schematic - Islanded Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88 |

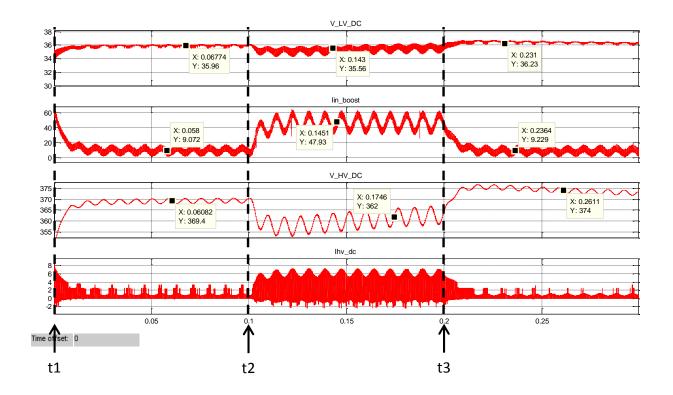

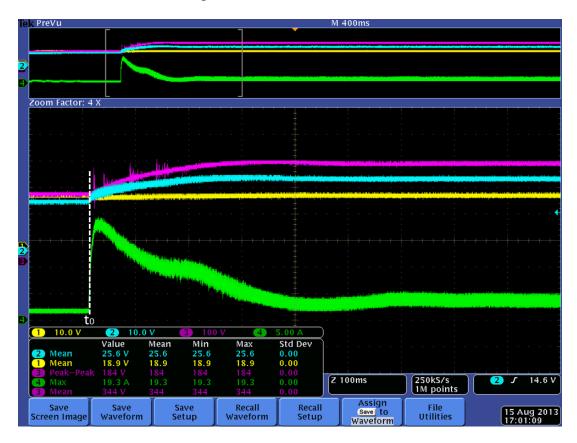

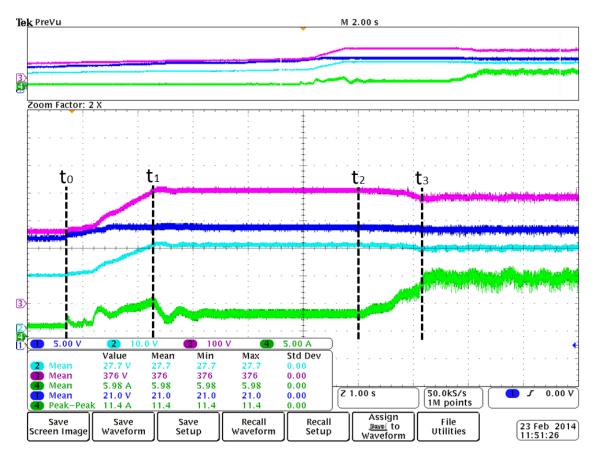

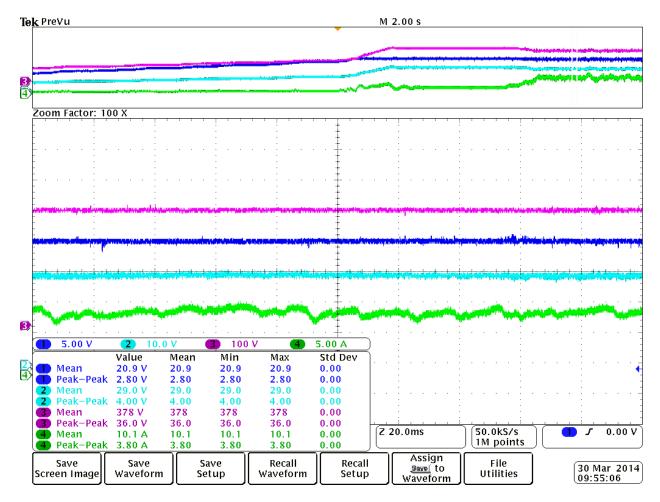

| Fig. 5.6.3: Closed Loop PV Boost with Full Inverter - Islanded - Startup DC Waveforms 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89 |

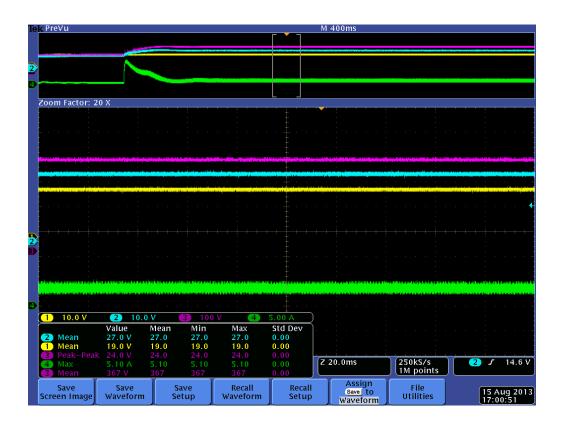

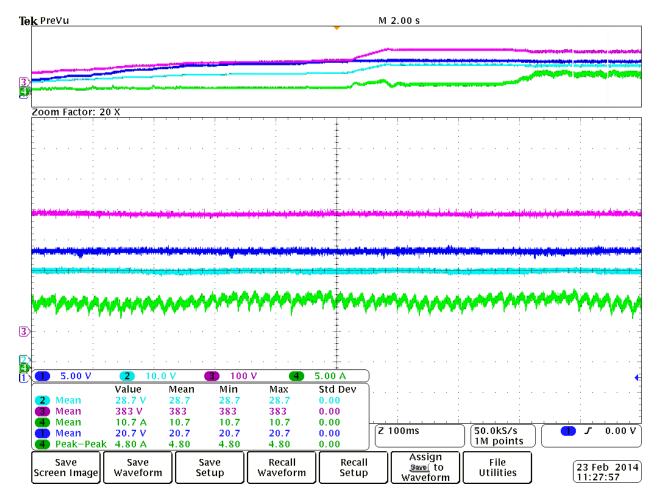

| Fig. 5.6.4: Closed Loop PV Boost with Full Inverter - Islanded - Steaady State DC Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 91 |

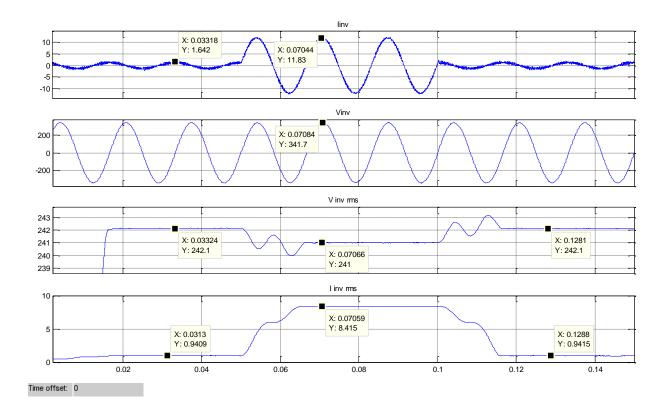

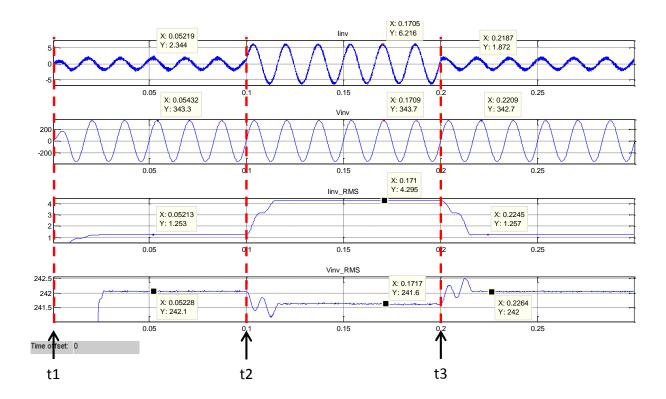

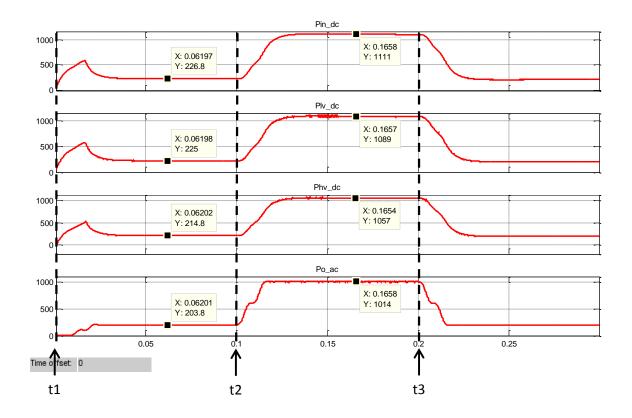

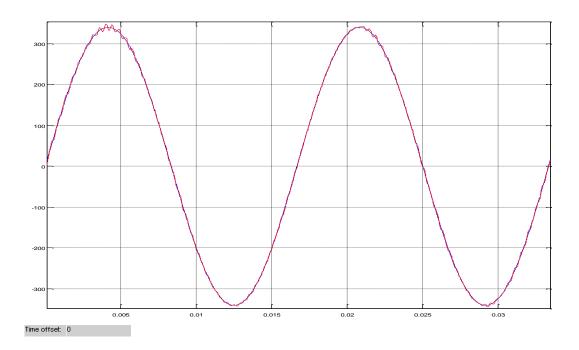

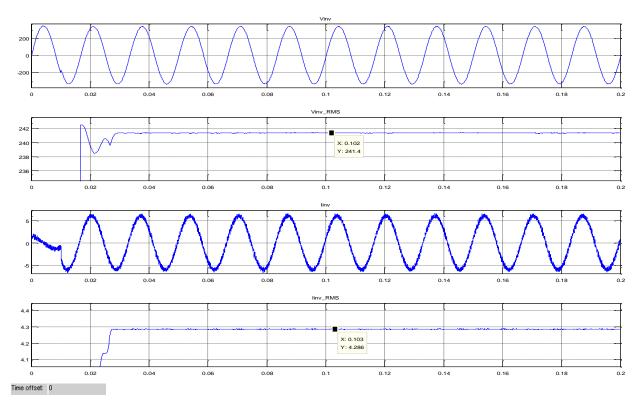

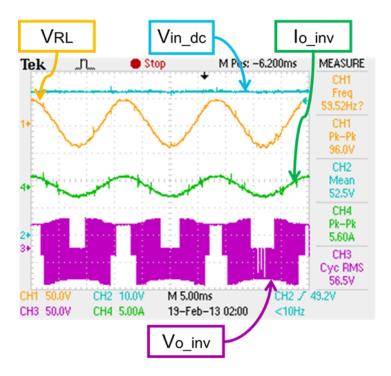

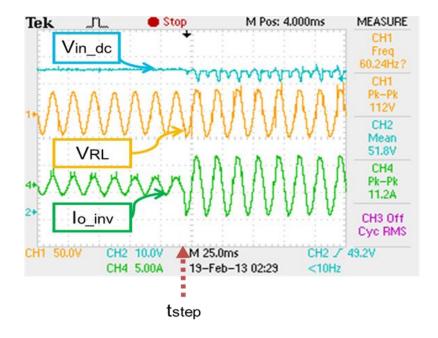

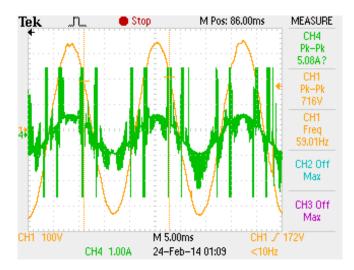

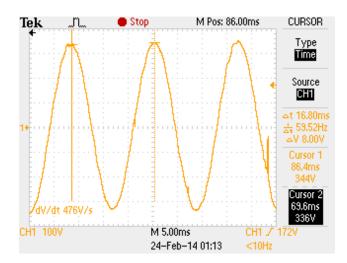

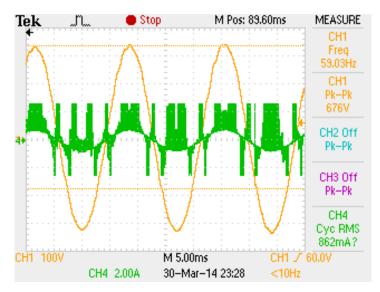

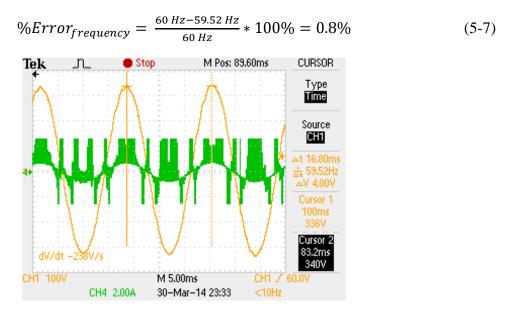

| Fig. 5.6.5: Closed Loop PV Boost with Full Inverter - Islanded - AC Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 92 |

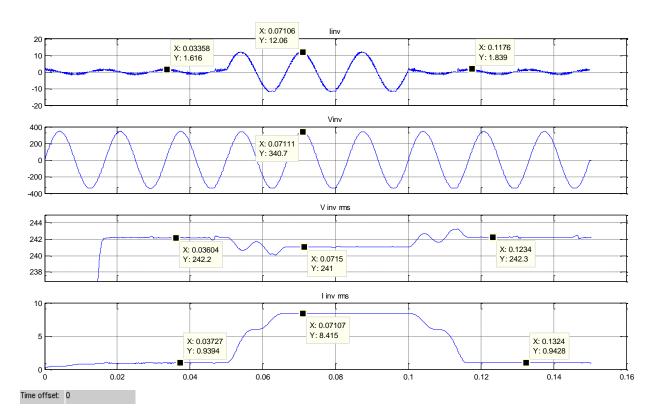

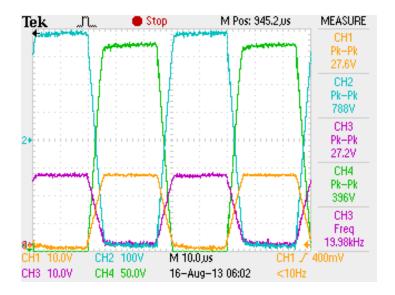

| Fig. 5.6.6: Closed Loop PV Boost with Full Inverter - Islanded - AC Waveforms with Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| Cursors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93 |

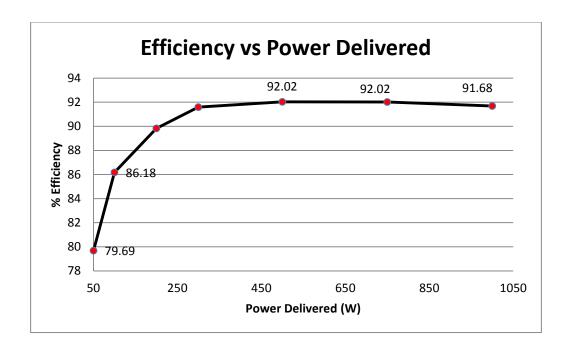

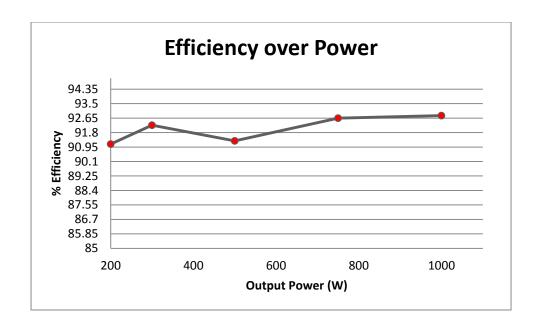

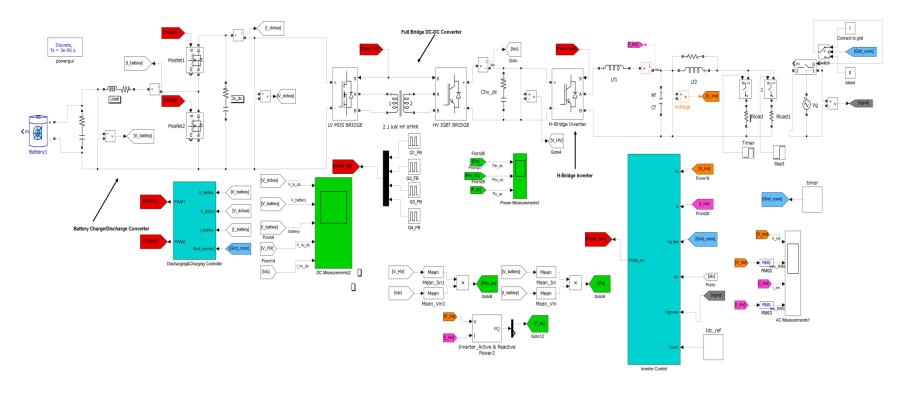

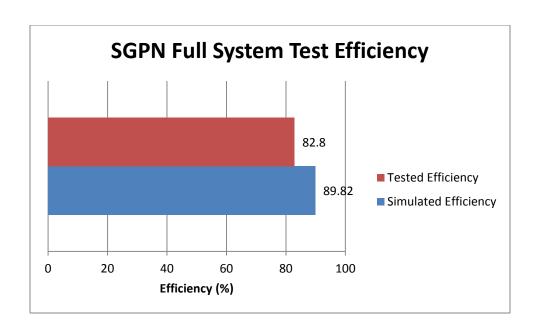

| Fig. 5.6.7. Simulated vs. Tested Efficiencies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 95 |

| Fig. 5.6.8: Battery Charge/Discharge Converter Schematic - Islanded Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95 |

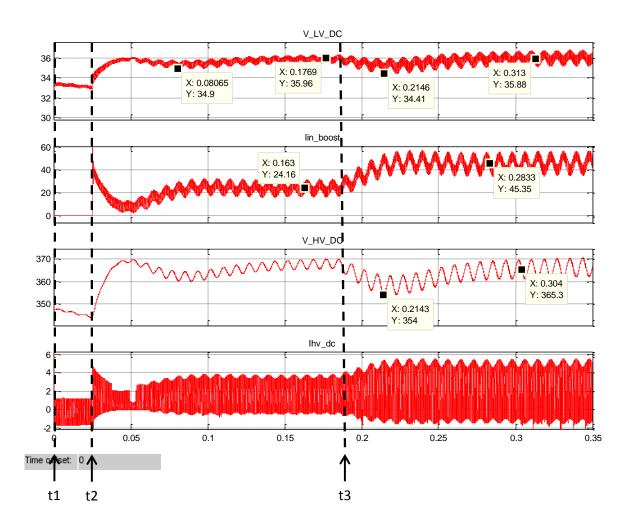

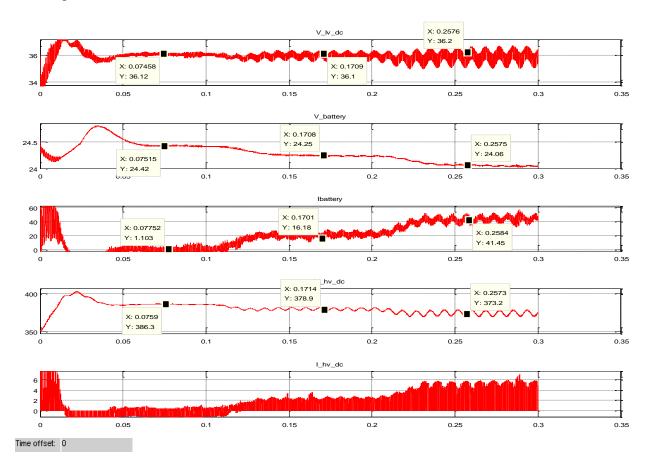

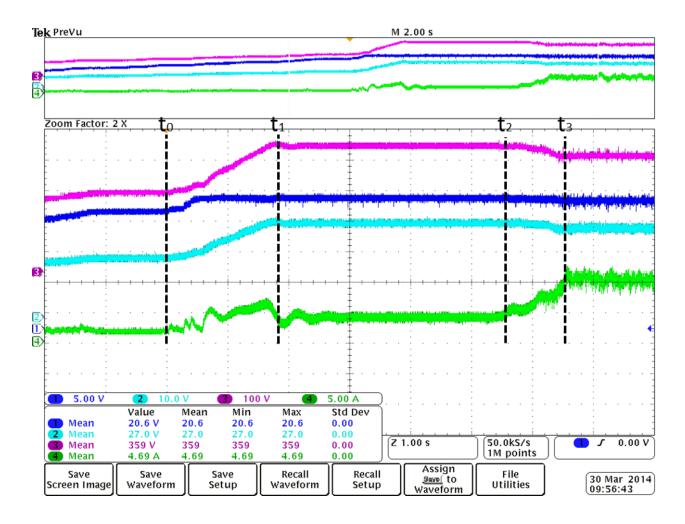

| Fig. 5.6.9: Closed Loop Battery Charge/Discharge Converter with Full Inverter - Islanded -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| Startup DC Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97 |

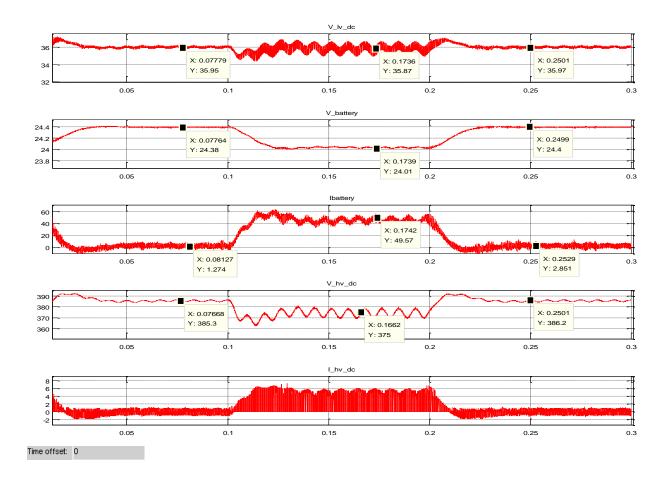

| Fig. 5.6.10: Closed Loop Battery Charge/Discharge Converter with Full Inverter - Islanded -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Steady State DC Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98 |

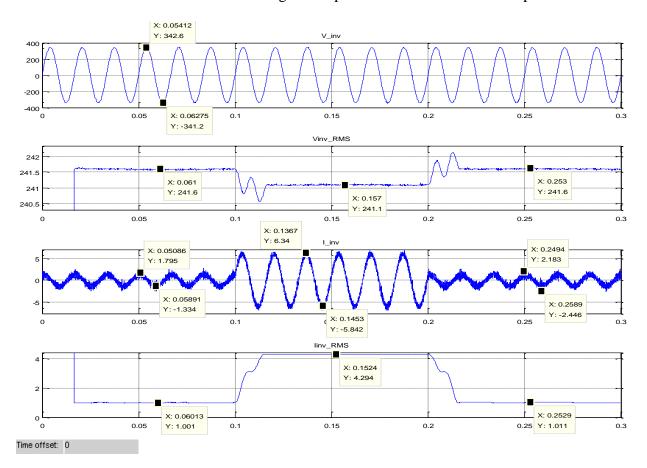

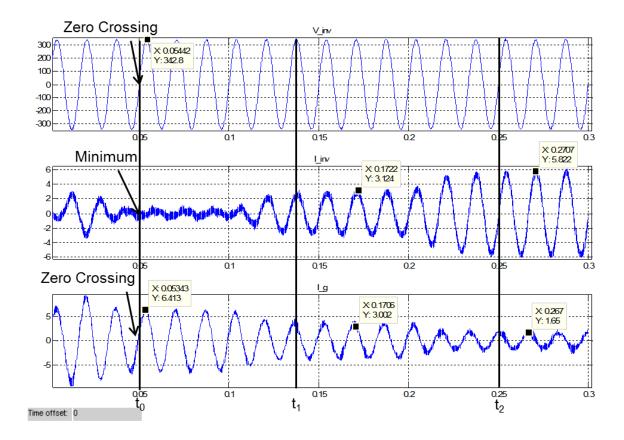

| Fig. 5.6.11: Closed Loop Battery Charge/Discharge Converter with Full Inverter - Islanded - Advanced - Advance | C  |

| Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99 |

| Fig. 5.6.12: Closed Loop Battery Charge/Discharge Converter with Full Inverter - Islanded - A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C  |

| Waveforms with Data Cursors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00 |

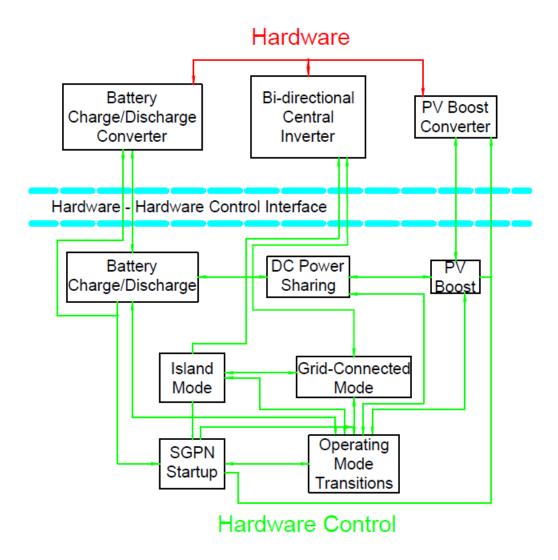

| Fig. 6.2.1: SGPN Hardware and Hardware Control Interaction Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14 |

## **TABLE OF TABLES**

| Table 2.7.1: Uni-polar SPWM Device Switching Table                                           |

|----------------------------------------------------------------------------------------------|

| Table 3.1.1: SGPN Operating Modes                                                            |

| Table 3.4.1: Comparison of Inverter Island Mode Control Design Performance Criteria 65       |

| Table 3.4.2: Isolation Board Cost Breakdown                                                  |

| Table 4.3.1: Closed Loop PV Boost Converter with Full Inverter Simulation – Islanded -DC     |

| System Performance                                                                           |

| Table 4.3.2: Closed Loop PV Boost Converter with Full Inverter Simulation - Grid-Connected - |

| Simulation Timeline                                                                          |

| Table 4.3.3: Closed Loop PV Boost Converter with Full Inverter Simulation - Grid-Connected - |

| DC System Performance 92                                                                     |

| Table 4.4.1: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -  |

| Islanded - DC System Performance                                                             |

| Table 4.4.2: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -  |

| Islanded - Simulated Efficiency By Stage                                                     |

| Table 4.4.3: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -  |

| Grid-Connected - Simulation Timeline                                                         |

| Table 4.4.4: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -  |

| Grid-Connected - DC System Performance                                                       |

| Table 4.4.5: Closed Loop Battery Charge/Discharge Converter with Full Inverter Simulation -  |

| Grid-Connected(Power to Grid) - Simulation Timeline                                          |

| Table 4.5.1: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter    |

| Simulation - Islanded - Static Load - Simulation Timeline                                    |

| Table 4.5.2: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter      |

|------------------------------------------------------------------------------------------------|

| Simulation - Islanded - Step Load - Simulation Timeline                                        |

| Table 4.5.3: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter      |

| Simulation - Islanded - Step Load - DC System Performance                                      |

| Table 4.5.4: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter      |

| Simulation - Grid-Connected - Static Load – Simulation Timeline                                |

| Table 4.5.5: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter      |

| Simulation - Grid-Connected - Step Load – Simulation Timeline                                  |

| Table 4.6.1: Closed Loop PV Boost & Battery Charge/Discharge Converter with Full Inverter      |

| Simulation - Operating Mode Transition - Simulation Timeline                                   |

| Table 5.3.1: Sensing Board Experimental Model                                                  |

| Table 5.6.1: Closed Loop Battery Charge/Discharge Converter with Full Inverter - Islanded - DC |

| System Performance                                                                             |

#### CHAPTER 1

#### INTRODUCTION

### 1.1 Need for Residential Energy Management Systems

The steady increase in the price to produce electricity and efforts made to modernize the grid have led to an increasing focus on efficiency in power production and consumption. The primary fuel source in the United States for electricity generation is coal, making up 42%, followed by natural gas at 25% and nuclear at 19% [1]. According to American Electric Power (AEP), greenhouse gas legislation that is being introduced by the United States government will further restrict the amount of carbon emissions allowed which will affect energy prices due to increasing de-regulation of the electricity market [2]. This will ultimately add to an already capital intensive generation, transmission, and distribution process.

Renewable electricity sources such as Photovoltaic (PV) systems or wind generation offer attractive alternatives to using grid power. In addition to the "free cost" nature of these sources, they emit zero carbon emissions making them ideal for use at a residential setting.