# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

8-2013

# High Voltage Direct Current Energy Transmission Using Modular Multilevel Converters

David Alejandro Guzman Pinzon University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd Part of the <u>Electrical and Electronics Commons</u>, and the <u>Electronic Devices and Semiconductor</u> <u>Manufacturing Commons</u>

**Recommended** Citation

Guzman Pinzon, David Alejandro, "High Voltage Direct Current Energy Transmission Using Modular Multilevel Converters" (2013). *Theses and Dissertations*. 859. http://scholarworks.uark.edu/etd/859

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

High Voltage Direct Current Energy Transmission Using Modular Multilevel Converters High Voltage Direct Current Energy Transmission Using Modular Multilevel Converters

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

David Alejandro Guzmán Universidad Tecnológica de Panamá Bachelor of Science in Electrical Engineering, 2010

> August 2013 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

Dr. Juan Carlos Balda

Thesis Director

Dr. Alan Mantooth

Dr. Roy McCann

Committee Member

Committee Member

#### ABSTRACT

This thesis focus on high voltage direct current (HVdc) energy transmission using modular multilevel converter (MMC) based terminals. It provides a brief comparison between different HVdc technologies, focusing on voltage source converters (HVdc-VSC) with the MMC-based terminal emerging as the topology of choice for ratings less than 1 GW. The controllers for a two-terminal HVdc-link are analyzed and Matlab/Simulink<sup>TM</sup> simulation models are presented. The simplified models and full Matlab/Simulink<sup>™</sup> based model are used to select the gains for the MMC controllers. Simulation results carried out on the full model validated the proposed methodologies. A new control technique that eliminates the voltage sensors on the grid side normally used to synchronize the MMC-based terminal with the grid is proposed. The performance of proposed technique was evaluated through Matlab/Simulink<sup>™</sup> simulations by considering inverter operation. The sensorless technique is able to synchronize a MMC-based inverter terminal to a grid under non-ideal conditions as well to accurately detect changes in the grid voltages. Finally, an analysis of the impact that a 15-kV SiC IGBT would have on HVdc MMC-based terminals is presented. The analysis evaluates parasitic inductances within the submodule (SM) of an MMC, changes on the required SM capacitance, and impact on the voltage waveform THD. The evaluations showed that the 15-kV SiC IGBT would be only suitable if the module is rated 400 A or greater.

#### ACKNOWLEDGMENTS

I express my gratitude to my family and friends in Panama for all of their love and support given during my studies away from home. My gratitude and love also goes to my girlfriend Nicki for all of her support and help.

My appreciation goes to Dr. Balda for his patience and predisposition to help with technical problems as well with ideas and advice to improve my writing. I also thank him for giving me the opportunity to work in his research group and the guidance provided for my thesis.

I also thank my committee members, Dr. Mantooth and Dr. McCann for taking their time for being part of my committee.

Finally my gratefulness to all my friends in Fayetteville for all their time shared with me and good dinners we shared together.

# DEDICATION

Esta tesis va dedicada a mis padres, Zuleika y Julio. Gracias por el amor incondicional, apoyo y consejos que me han brindado desde el día en que nací. Esta tesis no hubiera sido posible sin ustedes, los amo.

# TABLE OF CONTENTS

| CHAF | PTER ONE                                     |

|------|----------------------------------------------|

| INTR | ODUCTION1                                    |

| 1.1  | Brief History of HVdc Energy Transmission 1  |

| 1.2  | History HVdc in the United States of America |

| 1.3  | Thesis Motivation                            |

| 1.4  | Thesis Objectives                            |

| 1.5  | Thesis Organization                          |

| Ref  | Serences         5                           |

| CHAF | PTER TWO                                     |

| HIGH | VOLTAGE DIRECT CURRENT ENERGY TRANSMISSION   |

| Abs  | stract                                       |

| 2.1  | Introduction                                 |

| 2.2  | Current-Source Converters                    |

| 2.3  | Voltage-Source Converters11                  |

| 2.4  | Modular Multilevel Converter                 |

| 2    | 2.4.1. Operation principles                  |

| 2    | 2.4.2. Passive components of the MMC 17      |

| 2    | 2.4.3. MMC modulation strategies             |

| 2.5 Conclusions                                                |

|----------------------------------------------------------------|

| References                                                     |

| CHAPTER THREE                                                  |

| CONTROLLERS FOR A TWO-TERMINAL MMC-BASED HVDC TRANSMISSION     |

| SYSTEM                                                         |

| Abstract                                                       |

| 3.1 Introduction                                               |

| 3.2 Outer Controllers                                          |

| 3.2.1 Active and reactive power controllers                    |

| 3.2.2 DC voltage controller at Terminal 1                      |

| 3.3 Inner Current Control                                      |

| 3.4 SM Capacitor Voltage and Circulating Current Control       |

| 3.4.1 Capacitor average voltage control                        |

| 3.4.2 Balancing control of the instantaneous capacitor voltage |

| 3.4.3 Arm average voltage balancing control                    |

| 3.5 Voltage Reference Generation                               |

| 3.6 Conclusions                                                |

| References                                                     |

| Appendix A.1 49                                                |

| Appendix A.2                                                   |

| Appendix A.3                                                              |

|---------------------------------------------------------------------------|

| Appendix A.4                                                              |

| CHAPTER FOUR 61                                                           |

| SIMULATION RESUTLS AND SENSORLESS CONTROL OF THE SELECTED TWO-            |

| TERMINAL HVDC SYSTEM                                                      |

| Abstract                                                                  |

| 4.1 Introduction                                                          |

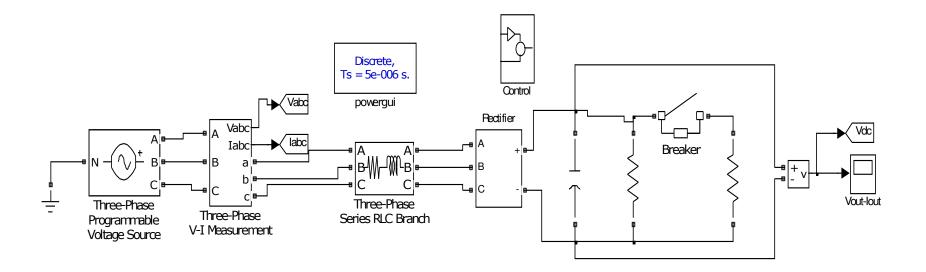

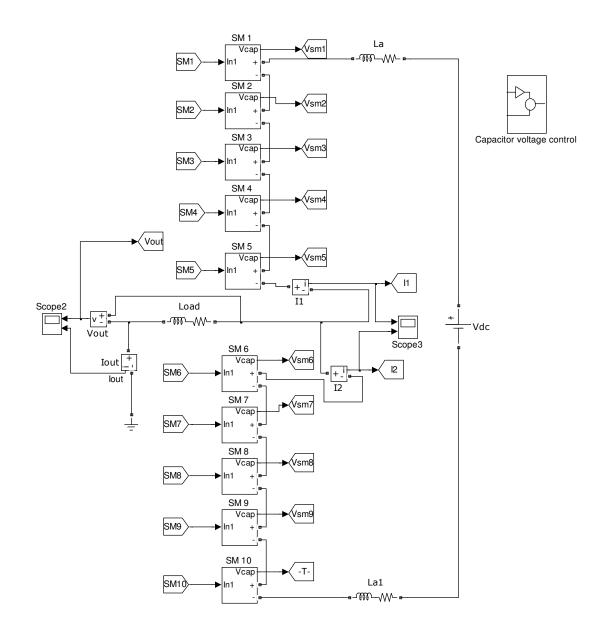

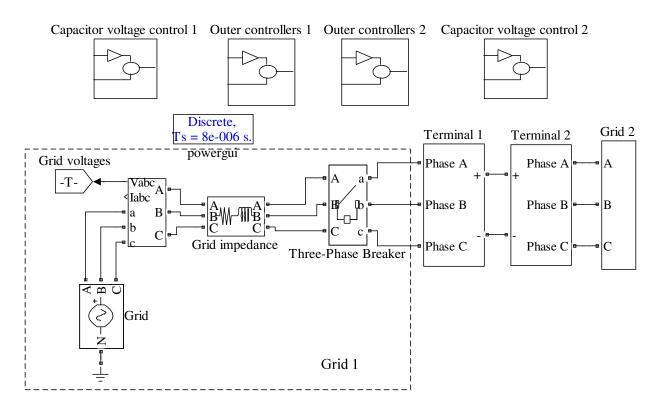

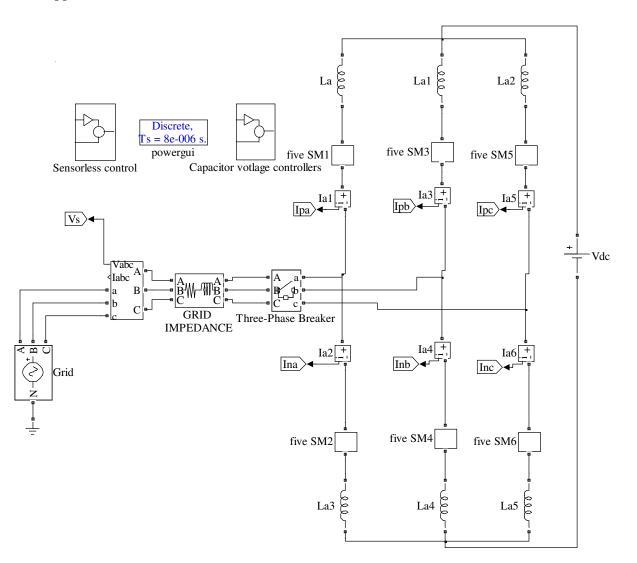

| 4.2 Matlab/Simulink <sup>™</sup> Setup of Two-Terminal HVdc System        |

| 4.3 Simulation Results of the Case Study                                  |

| 4.3.1 Outer controller results                                            |

| 4.3.2. Capacitor voltage controller results                               |

| 4.4 Sensorless Control Technique                                          |

| 4.4.1. Transfer function parameter selection                              |

| 4.4.2. PI controller design                                               |

| 4.5 Performance Evaluation of the Sensorless Technique75                  |

| 4.5.1. Comparison with the traditional control technique                  |

| 4.5.2. System performance under ideal grid conditions                     |

| 4.5.3. System perormance under harmonic pollution of the grid voltages    |

| 4.5.4. System performance under grid frequency changes                    |

| 4.5.5. System performance under variations of the grid voltage magnitudes |

| 4.6 Conclusions                                          |

|----------------------------------------------------------|

| References                                               |

| Appendix B.1                                             |

| Appendix B.2                                             |

| CHAPTER FIVE                                             |

| THE IMPACT OF HIGH-VOLTAGE AND FAST-SWITCHING DEVICES ON |

| MODULAR MULTILEVEL CONVERTERS 98                         |

| Abstract                                                 |

| 5.1 Introduction                                         |

| 5.2 MMC Sub-Modules                                      |

| 5.2.1 Power modules and capacitors                       |

| 5.2.2 Sub-module model 103                               |

| 5.3 IGBT PSpice Model 103                                |

| 5.4 Effects of Parasitic Inductances 107                 |

| 5.5 MMC Terminal Volume and THD 110                      |

| 5.5.1 IGBT module volume 110                             |

| 5.5.2 Capacitance volume 110                             |

| 5.5.3 Total harmonic distortion                          |

| 5.6 Conclusions 114                                      |

| Acknowledgment 115                                       |

| Refe   | rences                                      |     |

|--------|---------------------------------------------|-----|

| Append | lix C.1                                     | 118 |

| CHAP   | TER SIX                                     | 121 |

| CONC   | LUSIONS AND RECOMMENDATIONS FOR FUTURE WORK | 121 |

| 6.1    | Conclusions                                 |     |

| 6.2    | Recommendations for Future Work             |     |

# LIST OF FIGURES

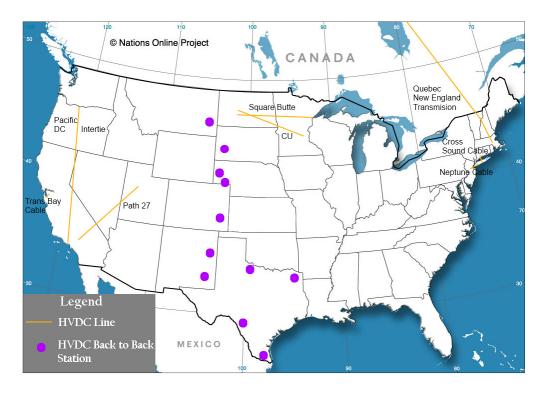

| Fig. 1.1. HVDC Projects in the USA [12]                                                       |

|-----------------------------------------------------------------------------------------------|

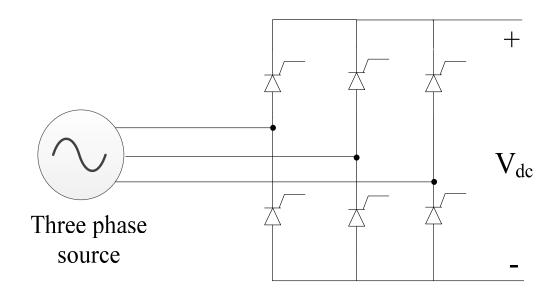

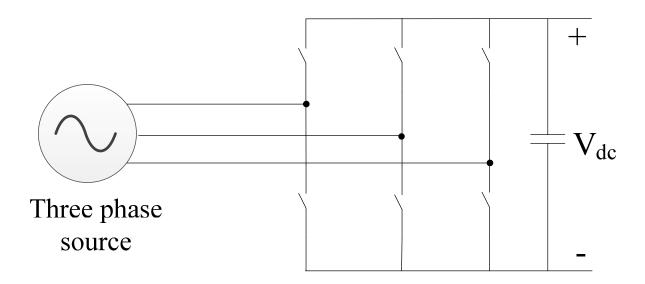

| Fig. 2.1. Six-pulse rectifier 10                                                              |

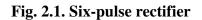

| Fig. 2.2. Twelve-pulse rectifier 10                                                           |

| Fig. 2.3. Simplified voltage source converter topology 12                                     |

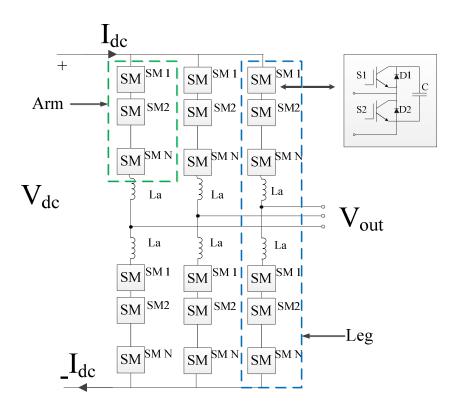

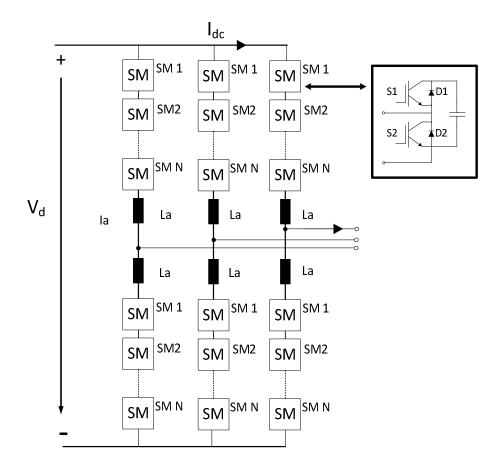

| Fig. 2.4. Modular multilevel converter [12] 14                                                |

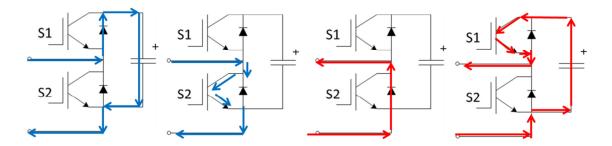

| Fig. 2.5. SM Current Paths 15                                                                 |

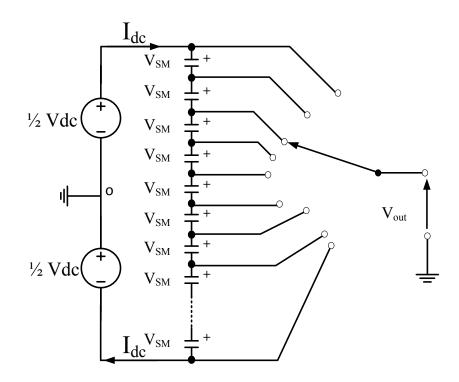

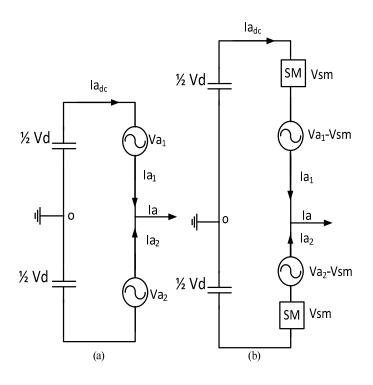

| Fig. 2.6. MMC Representation [2] 16                                                           |

| Fig. 2.7. Output Voltage of the MMC 16                                                        |

| Fig. 2.8. Ideal model of MMC17                                                                |

| Fig. 2.9. Level Shifted PWM 21                                                                |

| Fig. 2.10. Phase Shifted PWM 22                                                               |

| Fig. 3.1. Typical control scheme of a two terminal HVdc-link 28                               |

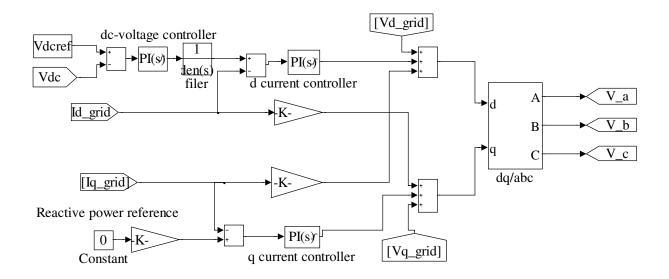

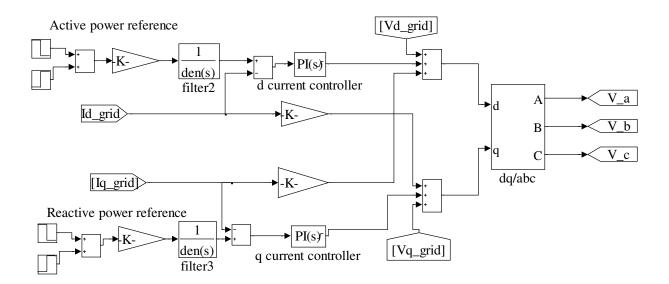

| Fig. 3.2. Control block diagrams for the power controllers                                    |

| Fig. 3.3. dc-voltage controller block diagram with: (a) no prefilter added (b) a prefilter    |

| added                                                                                         |

| Fig. 3.4. Bode plot of the dc-voltage controller without prefilter (solid) and with prefilter |

| (dashed)                                                                                      |

| Fig. 3.5. Step response of the dc-voltage controller without prefilter (solid) and with prefilter    |

|------------------------------------------------------------------------------------------------------|

| (dashed)35                                                                                           |

| Fig. 3.6. Single-phase schematic of an ideal MMC connected to a grid in inverter mode                |

| Fig. 3.7. Inner controller block diagram with: (a) no prefilter added (b) a prefilter added          |

| Fig. 3.8. Bode plot of the inner current controller without prefilter (solid) and with prefilter     |

| (dashed)                                                                                             |

| Fig. 3.9. Step response of the inner current controller without prefilter (solid) and with prefilter |

| (dashed)                                                                                             |

| Fig. 3.10. Inner current controller for the MMC 40                                                   |

| Fig. 3.11. Single-phase MMC leg42                                                                    |

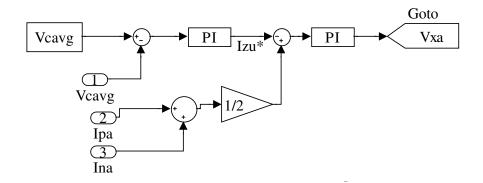

| Fig. 3.12. Block diagram of the capacitor average voltage control approach                           |

| Fig. 3.13. Individual balancing control block diagram                                                |

| Fig. 3.14. Arm-balancing control block diagram                                                       |

| Fig. 3.15. Reference voltage generation: (a) top arm, (b) bottom arm                                 |

| Fig. 4.1. Matlab/Simulink <sup>™</sup> simulation setup                                              |

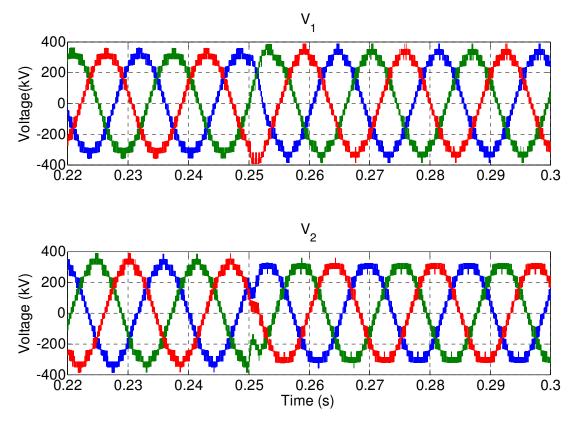

| Fig. 4.2. MMC terminals voltages: Terminal 1 (top) and Terminal 2 (bottom)                           |

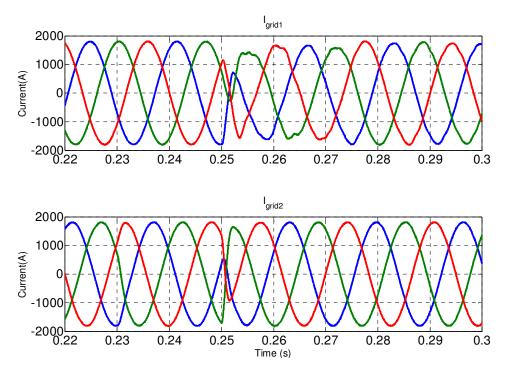

| Fig. 4.3. Grid currents: Terminal 1 (top) and Terminal 2 (bottom)                                    |

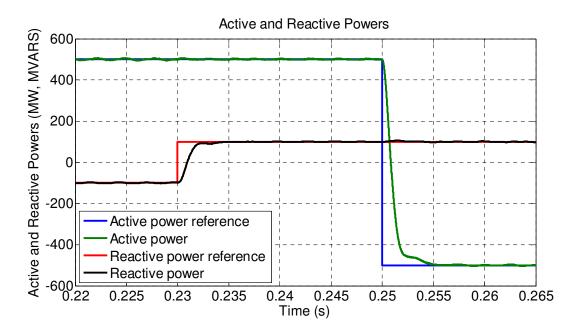

| Fig. 4.4. Active power reference (blue) and actual (green) and reactive power reference (red) and    |

| actual (black) on Terminal 2                                                                         |

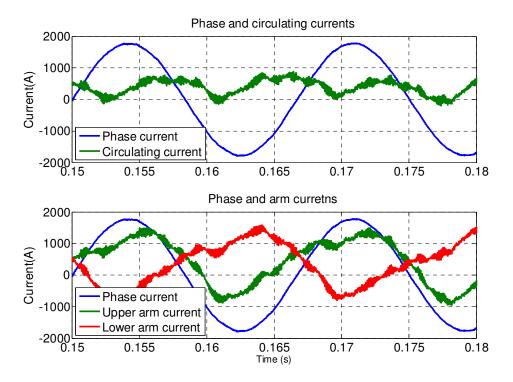

| Fig. 4.5. Phase and circulating currents (top) and phase and arms currents (bottom) when             |

| circulating current is controlled                                                                    |

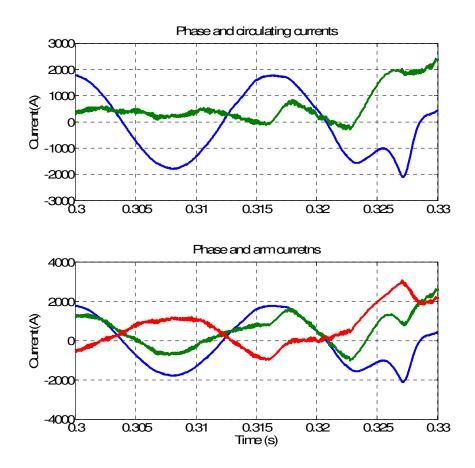

| Fig. 4.6. Phase and circulating currents (top) and Phase and arms currents (bottom) when the      |

|---------------------------------------------------------------------------------------------------|

| circulating current is not controlled                                                             |

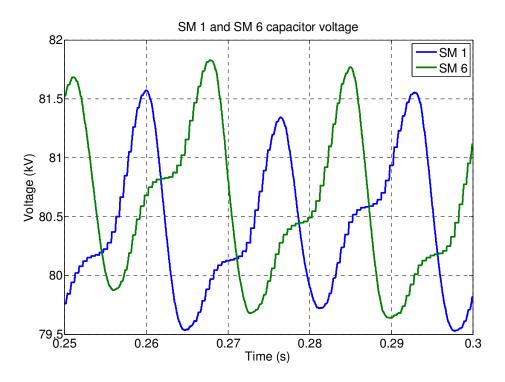

| Fig. 4.7. SM1 (blue) and SM6 (green) capacitor voltages                                           |

| Fig. 4.8 Ideal MMC connected to a grid – inverter operation                                       |

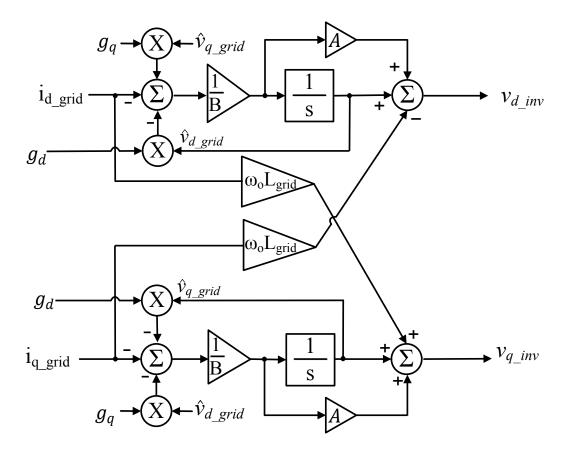

| Fig. 4.9. Proposed control technique                                                              |

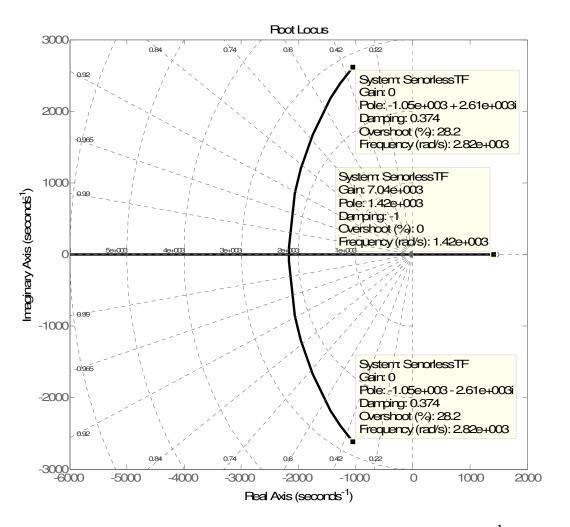

| Fig. 4.10. Root Locus of transfer function (4.5) with $g_d = -6.6 \text{ m}\Omega^{-1}$           |

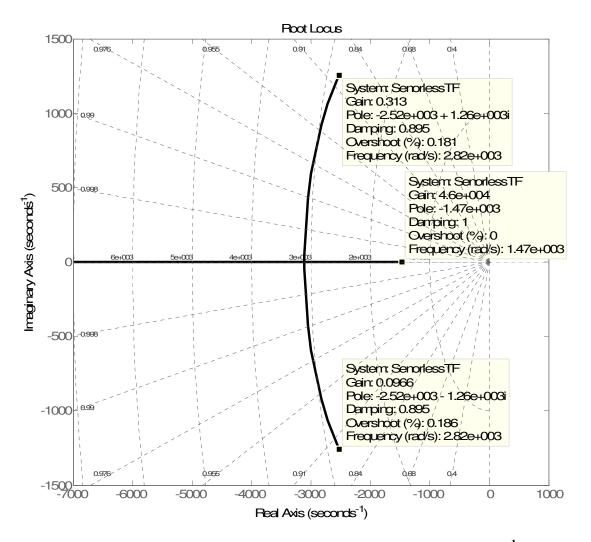

| Fig. 4.11. Root Locus of transfer function (4.5) with $g_d = 6.6 \text{ m}\Omega^{-1}$            |

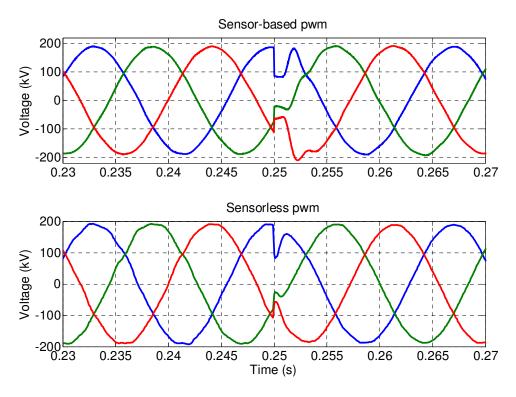

| FIG. 4.12. Sensor based voltage reference (top) and sensorless based voltage reference            |

| (bottom)                                                                                          |

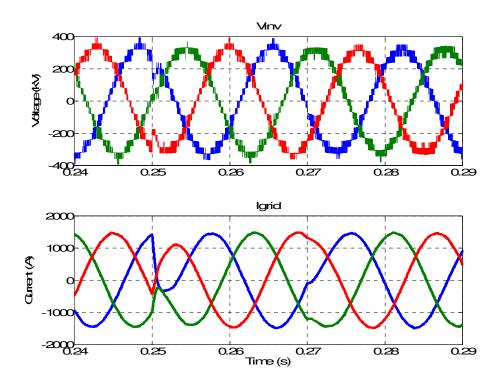

| Fig. 4.13. Inverter output voltages (top) and currents (bottom) at a grid angle of 90° 77         |

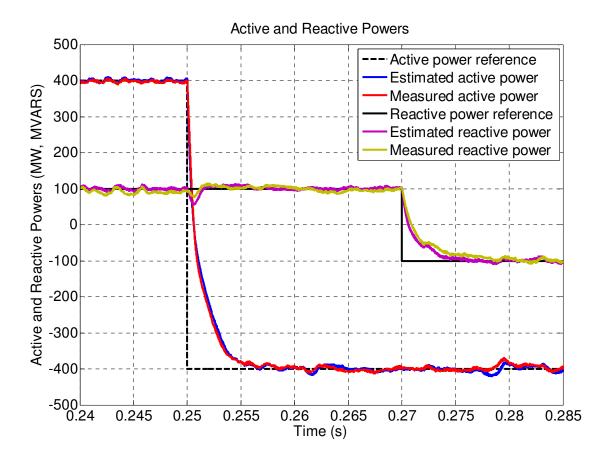

| Fig. 4.14. Active and reactive powers injected to the grid under ideal grid conditions            |

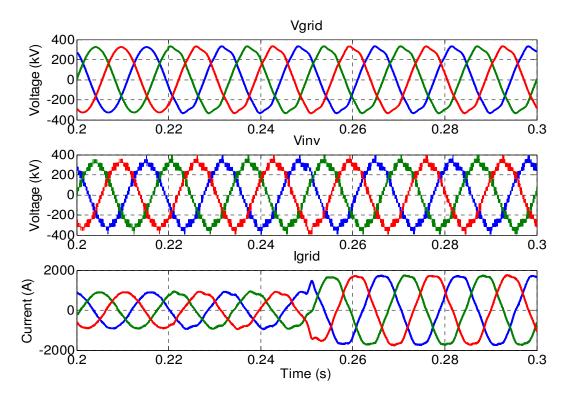

| Fig. 4.15. Grid (top) and inverter (middle) voltages and grid current (bottom) under grid-voltage |

| harmonic pollution                                                                                |

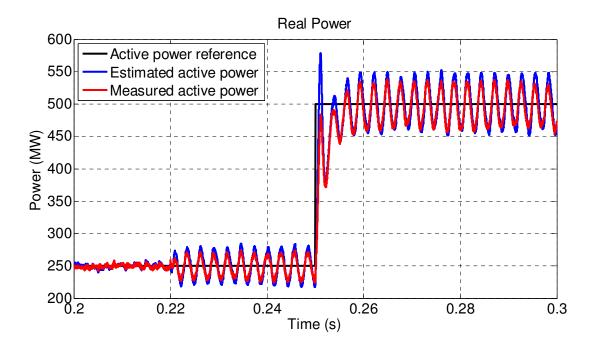

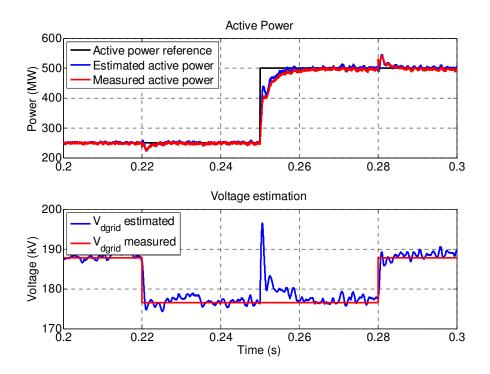

| Fig. 4.16. Reference (black), estimated (blue) and measured (red) active power under grid-        |

| voltage harmonic pollution                                                                        |

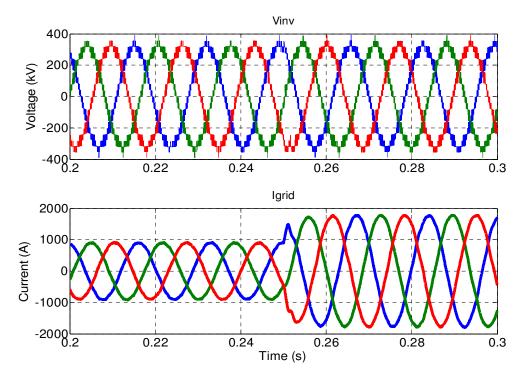

| Fig. 4.17. Inverter voltages (top) and grid currents (bottom) with a grid frequency step          |

| of -1.0 Hz                                                                                        |

| Fig. 4.18. Active power (top) and grid estimated voltages (bottom) with a grid frequency step     |

| of -1.0 Hz                                                                                        |

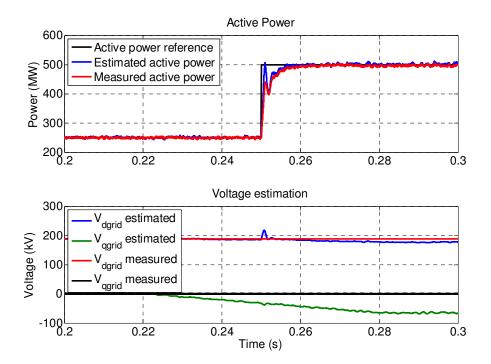

| Fig. 4.19. Inverter voltages (top) and grid currents (bottom) with a grid frequency               |

| step of 1.0 Hz                                                                                    |

| Fig. 4.20. Active power (top) and grid estimated voltages (bottom) with a grid frequency            |

|-----------------------------------------------------------------------------------------------------|

| step of 1.0 Hz                                                                                      |

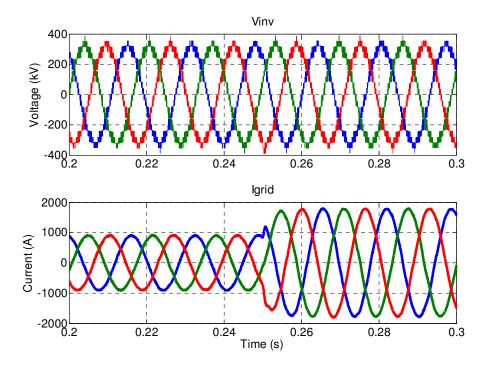

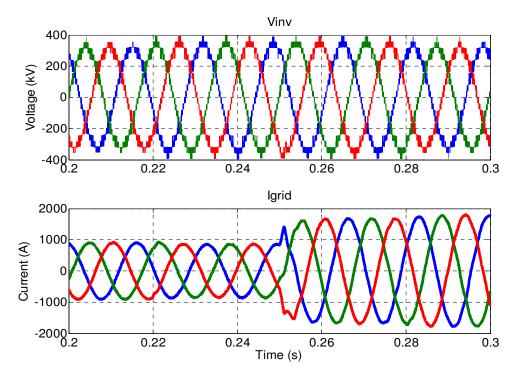

| Fig. 4.21. Inverter voltages (top) and grid currents (bottom) with a grid-voltage increase of 6% 85 |

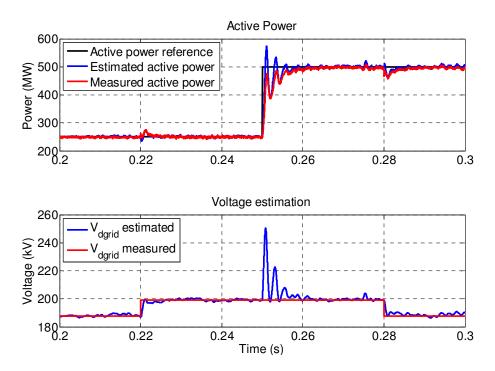

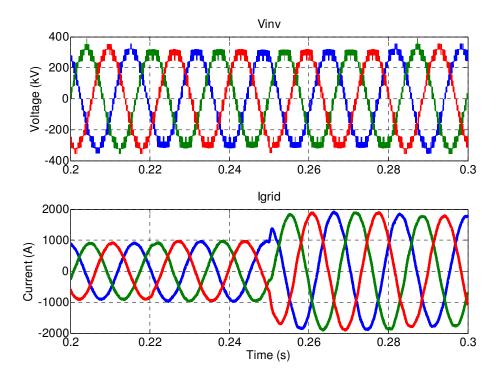

| Fig. 4.22. Active power (top) and grid estimated voltages (bottom) with a grid-voltage increase     |

| of 6%                                                                                               |

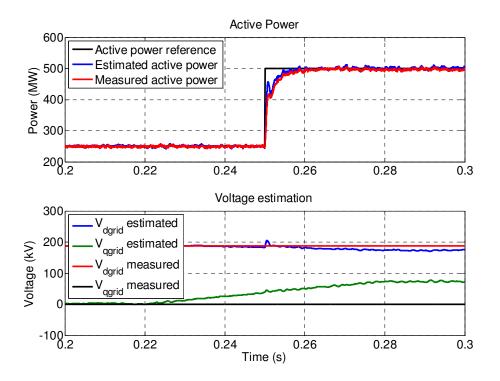

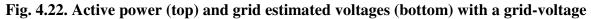

| Fig. 4.23. Inverter voltages (top) and grid currents (bottom) with a grid-voltage decrease of 6% 86 |

| Fig. 4.24. Active power (top) and grid estimated voltages (bottom) with a grid-voltage decrease     |

| of 6%                                                                                               |

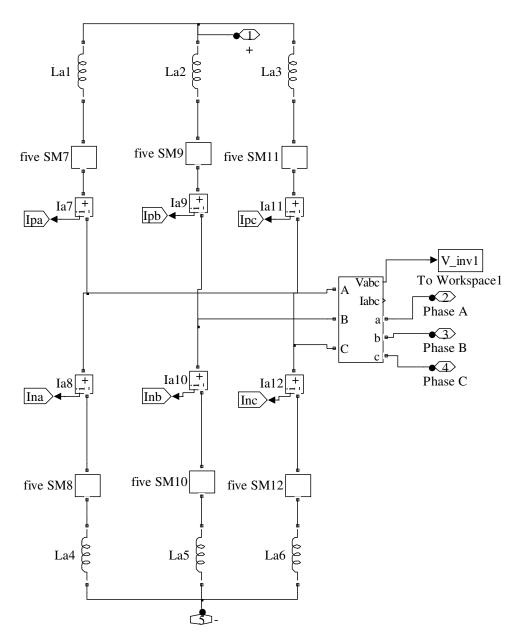

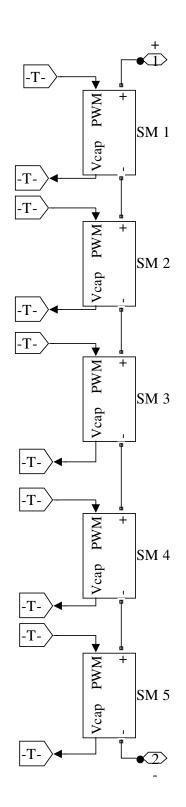

| Fig. 5.1. Modular multilevel converter topology                                                     |

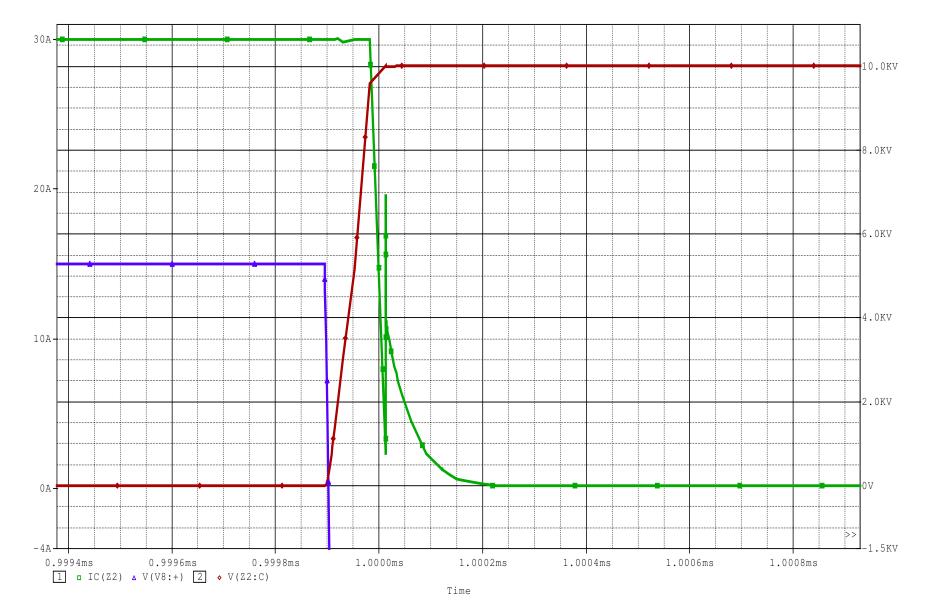

| Fig. 5.2. (a) Phase A of a MMC model [8], (b) Used model of Phase A of an MMC 104                   |

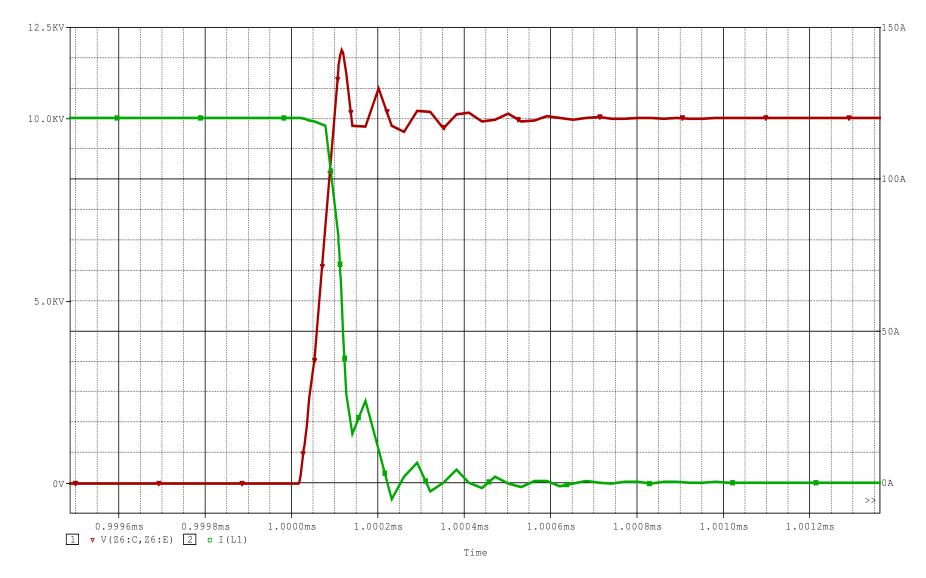

| Fig. 5.3. Turn-off of the 15-kV SiC IGBT PSpice model 105                                           |

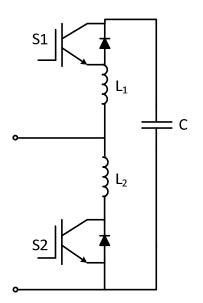

| Fig. 5.4. SM parasitic Inductances                                                                  |

| Fig. 5.5. Turn off transient of the IGBT PSpice model 109                                           |

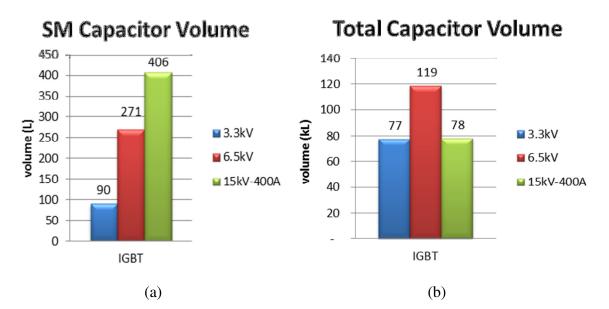

| Fig. 5.6. (a) SM Capacitor volume. (b) Total volume of capacitors in the MMC112                     |

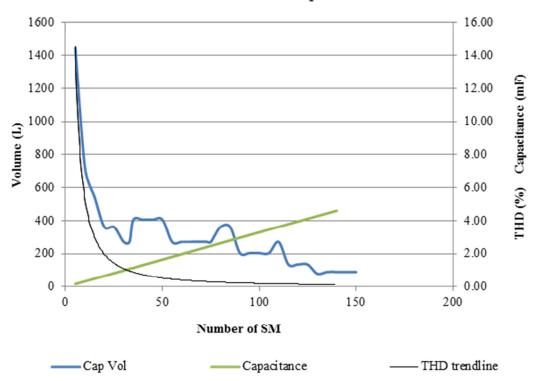

| Fig. 5.7. THD, SM capacitance volume, capacitance and N relation                                    |

# LIST OF TABLES

| Table 2.1. HVdc-CSC and HVdc-VSC Comparison [2], [10]                         | 13    |

|-------------------------------------------------------------------------------|-------|

| Table 3.1. HVdc system parameters [4]                                         | .29   |

| Table 4.1. System parameters for the Case Study                               | 63    |

| Table 4.2. Controllers gains for the system whose parameters are in Table 4.1 | 63    |

| Table 4.3. Controller gains for the sensorless technique                      | 75    |

| Table 5.1. System Parameters [10]                                             | 101   |

| Table 5.2. Number of modules required per MMC terminal                        | . 103 |

| Table 5.3. IGBT PSpice parameters                                             | 105   |

| Table 5.4 Sensitivity analysis results                                        | . 108 |

| Table 5.5 IGBT module volume                                                  | . 110 |

| Table 5.6. Total volume occupied by the MMC sub-modules                       | 112   |

# LIST OF PAPERS

## CHAPTER FIVE

[1] D.A. Guzman P., J. C. Balda, "The impact of high-voltage and fast-switching devices on modular multilevel converters," *Proceedings of Applied Power Electronics Conference and Exposition (APEC), 2013 Twenty-Eighth Annual IEEE*, pp. 2171-2177, 17-21 March 2013

#### **CHAPTER ONE**

#### **INTRODUCTION**

#### 1.1 Brief History of HVdc Energy Transmission

The idea of using high voltage direct current (HVdc) systems for energy transmission is not new. The first energy distribution systems in the USA were direct current (dc) systems since lines were short. The dc systems in the USA were challenged by the alternate current (ac) systems at the end of the 1880's in what is known as the "War of the Currents" [1]. At that time, the dc power had to be generated close to where it was consumed, since the generated voltages were relatively low, so long distance transmission was not possible. Furthermore, increasing or decreasing the dc voltage was also not possible, so loads that required a different voltage needed separate generating sources. These were some of the technical reasons that led ac systems to become the most practical choice for energy transmission at that time.

In the early 1920's, the limitations of the ac systems over long distances and for submarine cables were recognized. It was not until 1954 that the first commercial HVdc project was built because of the maturity and commercial availability of mercury arc valves [2]. This first HVdc project was built to transport electric power between the Sweden mainland and the island of Gotland, and had a power rating of 20 MW. In 1970, the HVdc link of the island of Gotland was upgraded to handle 30 MW of power. To make this upgrade possible, the system was reengineered using the first thyristors valves for a commercial HVdc project. In 1997, the first project using voltage source converters (VSC) based on IGBT's was commissioned to ABB [3].

Since 1997 several HVdc terminals using VSC have been built around the world. In 2003 a new topology was proposed for terminals using VSC technology. This topology was called the modular multilevel converter (MMC) [4]. With the coming of the MMC and the technological advances in semiconductor devices, HVdc has become a feasible technology for integrating renewable energies with power grids all over the world [5]. Recently, Europe has been planning a dc grid, to interconnect different sources of energy and increase the stability of the regional grid [6].

#### **1.2** History HVdc in the United States of America

The first HVdc project in the USA, built in 1932 by General Electric Company, was an experimental station located between Mechanicville and Schenectady, NY [7]. It was not until 1970, however, that the first commercial HVdc project was commissioned: the Pacific DC Intertie. The goal of this project was to connect the hydro-electric power in the state of Oregon with the load centers in Los Angeles, CA. The Pacific DC Intertie was the first of many other HVdc projects in the USA. Among these other projects is the Quebec – New England Transmission, which has two stages. The first stage has two stations located between Sherbrook, Quebec (Canada) and Monroe, New Hampshire (USA). Stage two included three additional terminals to the connection. This made the Quebec – New England Transmission the only multi-terminal HVdc project in the USA [8].

Soon after the Quebec – New England additional terminals were finished, the Trans-Bay Cable project was built, and started its operations in 2010 between San Francisco, CA, USA and Pittsburg, CA, USA, becoming the first project in the USA to use a modular multilevel converter (MMC), utilizing HVdc-VSC based terminals [9]. The location of the HVdc projects in the USA

as of February 2013 is shown in Fig. 1.1 [10]. More recently the "Tres Amigas" project has been awarded to Alstom to implement a 750 MW VSC-HVdc project [11].

#### **1.3** Thesis Motivation

The increasing penetration of renewable energy sources in power grids is expected to play a significant role in the future. In some cases, renewable energy sources such as wind are located off shore, and bringing this power to the mainland can be a challenge.

One of the alternatives for solving these problems is using HVdc transmission whose use is not limited to integrating renewable energy sources into power grids; it can also interconnect two different grids between two countries.

Fig. 1.1. HVDC Projects in the USA [12]

An example of a case where two countries' power grids can be connected by an HVdc system is the plan to interconnect the grids of Panama and Colombia [13]. The author of this thesis was born and raised in Panama. The interconnection of Panama and Colombia will be the first HVdc project made in Panama and it is of great interest of the author to contribute towards the realization of this project. To contribute with the realization of this project, the author needs a deeper understanding of how HVdc technology works. This knowledge can be acquired by doing research and learning the state of the art in HVdc. Therefore, simulations models are selected as a learning and research tool for gaining a deeper understanding in HVdc technologies.

#### **1.4** Thesis Objectives

The main objective for this thesis is to analyze the different technologies used for transmitting power between two points, focusing on MMC-based HVdc systems. To accomplish the main objective, the enabling objectives are:

- To familiarize the reader with modular multilevel converters for HVdc applications.

- To build a simulation model of the interconnection of two ac-grids using an HVdc link. Both terminals will be MMC-based. The terminals will be placed in Panama and Colombia to represent the planned interconnection between these two countries [13].

- To implement a sensorless control technique for connecting the MMC-based inverter terminal with the grid. This technique eliminates the grid-side voltage and current sensors used to synchronize an MMC-based terminal with a grid.

- To analyze the impact of a high voltage device on MMC-based terminals for HVdc applications, with a focus on SiC IGBT's.

## **1.5** Thesis Organization

To achieve the main objective of this thesis the following chapters are proposed:

- Chapter Two presents the reasons for using HVdc transmission. Different HVdc technologies are compared and analyzed. The principles of operation of the MMC and the selection of the passive components are also detailed in this chapter.

- Using Chapter's Two background theory, Chapter Three shows a methodology to calculate the various for the controllers of an HVdc systems as wells as the controllers to control the capacitor voltages and circulating currents within the MMC-based terminal using simplified Matlab/Simulink<sup>™</sup> models.

- Using the controllers presented in Chapter Three, Chapter Four presents a full Matlab/Simulink<sup>™</sup> based simulation model of a two-terminal HVdc link and implements a sensorless control technique to connect the inverter terminal of an HVdc system with a grid. The performance of this sensorless control technique is evaluated under ideal and non-ideal grid conditions [14].

- Chapter Five explains the impact of a high voltage, fast switching device in the MMC realization. The study includes the impact on the number of sub-modules required, the capacitance of the sub-module, and the possible impacts in the THD of the system [15].

- Chapter Six summarizes the work done, presents the conclusions of the research and recommendations for future work are presented as well.

## References

B. Finn, "Origin of Electrical Power", National Museum of American History, [Online]. Available: http://americanhistory.si.edu/powering/past/prehist.htm [Accessed: Feb. 1, 2013]

- [2] O. Peake, "The History of High Voltage Direct Current Transmission," *presented at the Australasian Engineering Heritage Conference*, 2009.

- [3] ABB "Tesla vs. Edison: the war of currents" [Online] Available: http://www.abb.com/cawp/seitp202/c646c16ae1512f8ec1257934004fa545.aspx [Accessed: Feb. 1, 2013]

- [4] A. Lesnicar, R. Marquardt, "An innovative modular multilevel converter topology suitable for a wide power range," *Proceedings of Power Tech Conference*, 2003 IEEE Bologna, vol.3,pp. 23-26, June 2003.

- [5] N. Ahmed, A. Haider, D. Van Hertem, Lidong Zhang, and H.-P. Nee, "Prospects and challenges of future HVDC SuperGrids with modular multilevel converters," *Proceedings of the 2011-14th European Conference on Power Electronics and Applications*, 2011, pp. 1–10.

- [6] P. Fairley, "Germany jump-starts the supergrid," Spectrum, IEEE, vol.50, no.5, May 2013

- [7] J.A. Besha, "The Historic Mechanicville Hydroelectric Station. 1. The Early Days [History]," *Industry Applications Magazine*, IEEE, vol.13, no.1, pp.8-11, Jan.-Feb. 2007.

- [8] ABB "History of ABB's HVDC expertise" [Online] Available: http://www.abb.us/cawp/seitp202/7cfd9a3a7416a383c1256e8600406f4f.aspx [Accessed: Jan. 31, 2013].

- [9] H.-J. Knaak, "Modular multilevel converters and HVDC/FACTS: A success story," *Proceedings of the 2011-14th European Conference on Power Electronics and Applications*, vol., no., pp.1-6, Aug. 30 2011-Sept. 1 2011.

- [10] University of Idaho "HVDC Projects Listing" [Online] Available: http://www.ece.uidaho.edu/hvdcfacts/Projects/HVDCProjectsListingMarch2012existing.pdf [Accessed: Dec.3, 2012]

- [11] Alstom "Alstom Grid will provide Tres Amigas LLC in the USA with first-of-its-kind Smart Grid "SuperStation"" [Online] Available: http://www.alstom.com/press-

centre/2011/4/Alstom-Grid-will-provide-Tres-Amigas-LLC-in-the-USA-with-first-of-its-kind-Smart-Grid-SuperStation/ [Accessed: Jun. 2, 2013]

- [12] Nations Online [Online] Available: http://www.nationsonline.org/oneworld/usa\_\_blank\_map.htm [Accessed: Jun.26, 2012]

- [13] Inter-American Development Bank "Colombia-Panama Interconnection" [Online] Available: http://www.iadb.org/en/projects/project-description-title,1303.html?id=rs%2Dt1241 [Accessed: Jan.31, 2013].

- [14] Escobar-Mejia, D. Guzman, J.C. Balda and C. Busada, "New Control Technique for Sensor-less Grid Synchronization of Modular Multilevel Converters for HVDC Systems," *Proceedings of the IEEE Energy Conversion Congress & Exposition*, 2013.

- [15] D. Guzman, J.C. Balda, "The Impact of High-Voltage and Fast-Switching Devices on Modular Multilevel Converters", *Proceedings of the Applied Power Electronics Conference and Exposition*, 2013.

#### **CHAPTER TWO**

## HIGH VOLTAGE DIRECT CURRENT ENERGY TRANSMISSION

#### Abstract

This chapter explains the advantages of HVdc transmission over HVac transmission and provides a comparison between different HVdc technologies focusing on HVdc-VSC, more specifically in modular multilevel converters (MMC). Some of the advantages of the MMC over others HVdc-VSC topologies are presented and the fundamental principles of operation of the MMC are explained. With the information presented in this chapter the reader should be able to have a basic understanding of the different classifications within HVdc technologies and the fundamental operating principles of MMC.

## 2.1 Introduction

When compared with high voltage alternate current (HVac) energy transmission, HVdc has several advantages that can be summarized as follows [1]-[3] :

- No technical limit for underwater cable distances.

- More power capability per cable.

- Lower losses per line; 20% less losses when compared to a HVac line.

- Power transmission over long distances.

- Does not require synchronous operation; can connect to ac systems with any frequency.

- Does not increase the short-circuit current of the switchgear of the connecting ac systems.

- It is possible to use the ground as a return path; therefore, each conductor could be controlled as an independent circuit.

These advantages over HVac have made HVdc the technology of choice for transmitting power over long distances and for offshore transmission. After choosing HVdc, the next stage is to choose the converter technology for implementing the HVdc system. The specific technologies are line-commutated current-source converters (CSCs or HVdc-CSC), and voltage source converters (VSCs or HVdc-VSC) [1]. This Chapter provides a detailed explanation and comparison of the above two technologies and analyzes, in particular, the topology of the MMC.

#### 2.2 Current-Source Converters

This is the oldest and most used technology in HVdc systems [4] and is currently the most cost-effective alternative for power ratings over 1.2 GW 0. This technology employs thyristors as switches to change from ac to dc, or vice versa. The thyristors are configured as a three-phase, full-wave bridge rectifier as shown, in its simplest form, in Fig. 2.1. This configuration is also known as a six-pulse bridge, named after the harmonic ripple it produces, which is six times the fundamental frequency on the ac voltage side. The inverter topology is similar. To mitigate the harmonics effects and reduce the size of the ac filters, a twelve-pulse configuration can be used. The twelve-pulse configuration consists of two six-pulse arrangements connected to Y–Y and Y–  $\Delta$  transformers, as shown in Fig. 2.2. Filters are placed at both sides of the rectifier to mitigate the switching noise. The ac-side filters are also used to provide reactive power to the converter. Rectifier and inverter operation demand reactive power from the ac system due to the commutation process; this can be described as the current transfer between phases due to the thyristors switching [6]. Therefore, the ac current lags the voltage during the converters normal operation. The ac system connected to the CSC has to provide the reactive power to the CSC if the ac filters are unable. Thus, the CSC is required to be connected to a strong ac system to keep its stability.

Fig. 2.2. Twelve-pulse rectifier

In order to connect to weaker ac systems, series capacitors are connected between the transformers and the valves to compensate for the reactive power; these are known as capacitor-commutated converters (CCCs).

The controllers of the CSCs or CCCs can only control the active power, and in order to change the power flow, the polarity of the terminals must be reversed. The filters required for an HVdc-CSC link to operate are very bulky and take up most of the space in the HVdc substation, up to 75%. These are some of the drawbacks of the HVdc-CSC links which, despite these drawbacks, are widely used in the USA and around the world to transmit high amounts of energy over long distances. The popularity of HVdc-CSC links is due to the maturity of the technology. This was the first engineering solution proposed by the manufactures, such as ABB 0. When HVdc-CSC was first proposed, mercury valves where used as switches [7]. Each switching position requires several series-connected switches to satisfy the voltage isolation requirements. Voltage isolation and current capability make thyristors the best switch for a high power HVdc-link.

#### 2.3 Voltage-Source Converters

To overcome the limits in the controllability of the HVdc-CSC, it is necessary to be able to control the turn-on and turn-off of the switches. The VSC uses IGBTs to control the turn-on and turn-off of the switch, and the IGBTs are voltage controlled using pulse width modulation (PWM). The VSCs are able to control active and reactive powers independently, and can be controlled as a synchronous generator [6]. Fig. 2.3 presents a simplified three-phase, two-level VSC. It is called two-level because it produces two different ac voltage levels when it is working as an inverter:  $+\frac{V_{dc}}{2}$  and  $-\frac{V_{dc}}{2}$ , using the midpoint of the dc bus as the reference.

However, the two-level VSC still requires bulky filters at the output. To overcome this limitation, multilevel converters were proposed [8]. The main multilevel converter topologies are: diode-clamped multilevel converter, flying capacitor multilevel converter and modular multilevel converter [9]. The latter is preferred by manufacturers due to the advantages given in Section 2.4. HVdc-VSC terminals using MMC are compared to the HVdc-CSC terminals in Table 2.1 [2].

Currently it is not economically to make an HVdc-link over 1.5 GW using HVdc-VSC so, all of the projects that are over this power rating use HVdc-CSC technology. Likewise, a new project below 1.5 GW is expected to use the HVdc-VSC technology. Currently, the two technologies coexist together, and some HVdc links have been changed from HVdc-CSC to HVdc-VSC for increased controllability [11].

Fig. 2.3. Simplified voltage source converter topology

| HVdc-CSC                                          |                                                           | HVdc-VSC                                            |                                                                 |

|---------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------|

| Advantages                                        | Disadvantages                                             | Advantages                                          | Disadvantages                                                   |

| Low cost                                          | High harmonics content                                    | Low harmonic content                                | Higher cost                                                     |

| High power rating                                 | Filters require a large area                              | Control of active and reactive power                | Limited power rating <b>due to power devices</b>                |

| Reliable and robust                               | Requires polarity<br>reversal to change<br>power flow     | No polarity reversal required to change power flow. | Low overload capability <b>due to power devices</b>             |

| Low losses                                        | Multi-terminal is challenging to achieve                  | Multi-terminal<br>HVDC is accessible                | High losses due to high<br>electronic component<br>count        |

| Can suppress dc<br>faults without a dc<br>breaker | Needs a high short<br>circuit ratio (strong<br>ac system) | Smaller HVdc<br>substations                         | Requires a dc circuit<br>breaker (depending on<br>the topology) |

| Well studied technology                           | Not able to do a<br>"black start"                         | Able to do a "black start"                          |                                                                 |

|                                                   | Requires a<br>synchronous voltage<br>source               | Can work with weak<br>AC systems                    |                                                                 |

# Table 2.1 . HVdc-CSC and HVdc-VSC Comparison [2], [10]

### 2.4 Modular Multilevel Converter

Due to the advantages mentioned over the other topologies. The MMC is selected as the topology for this work in HVdc applications. The MMC topology is shown in Fig. 2.4, with the green dashed line showing one of the arms of the MMC and the blue dashed line showing one of the legs of the MMC. When compared to the HVdc-VSC topologies, mentioned in Section 2.3, the MMC has the following advantages [10]:

- Less expensive and faster fabrication process due to modular design.

- It is easy to scale up to high voltages without adding extra complexity.

- The rise time of dc-side fault currents is limited by the arm inductors.

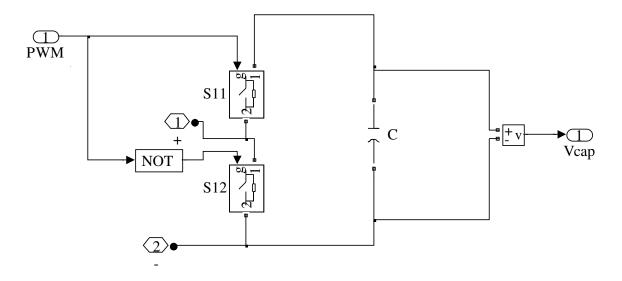

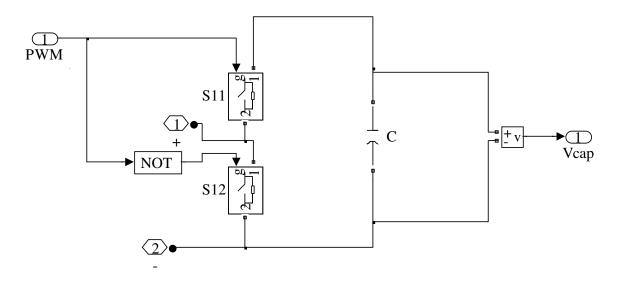

There have been three proposed topologies for the SM of a MMC. These topologies are: halfbridge sub-module (HBSM), full-bridge sub-module (FBSM) and clamp-double sub-module (CDSM) [12]. The major limitation of the HBSM is that it is unable to block dc-side faults, but this can be overcome by the use of a dc-breaker like the one proposed in 0. The mayor advantages of the HBSM are the lower component count, when compared to the other SM topologies, and higher efficiency. For the reasons mentioned before, the HBSM is selected as the SM topology for the MMC. The HBSM has four possible current paths, as shown in Fig. 2.5.

Fig. 2.4. Modular multilevel converter [12]

Fig. 2.5. SM Current Paths

The blue lines indicate current flowing into the SM and the red lines indicate current flowing out of the SM. Currents flowing into the SM charge the capacitor and currents flowing out discharge the capacitor.

## 2.4.1. Operation principles

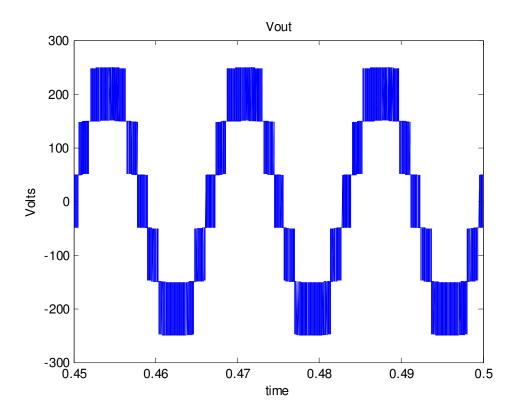

The MMC operates by inserting or bypassing the SM capacitor to form, in staircase shape, the output voltage waveform [14]. The capacitor is inserted when S1 is on, and bypassed when S2 is turned on. When both switches in the SM (i.e., S1 and S2) are off, the current flows through the freewheeling diodes. The operation of the MMC is illustrated in Fig. 2.6, using dc sources instead of capacitors and a selector. The selector inserts or bypasses dc sources according to the control algorithm of the MMC. The inserted dc sources produce a voltage output with a staircase form, as shown in Fig. 2.7. The six levels voltage waveform in Fig. 2.7 is produced with five SMs per arm of the MMC.

Fig. 2.6. MMC Representation [2]

Fig. 2.7. Output Voltage of the MMC

#### 2.4.2. Passive components of the MMC

This section explains the process of selecting the values for the passive components, namely, the SM capacitor and the arm inductor, whose main functions are energy storage and limiting the circulating current, respectively. The selection of the SM capacitance and inductance values for the MMC has been discussed in [15]-[17], and this section is an explanation of what is presented in the literature.

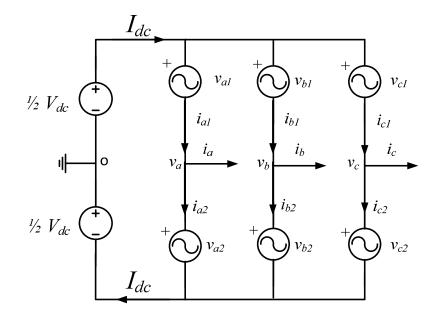

Assuming that the MMC has an infinite amount of SM and neglecting inductor  $L_a$ , the arms of the MMC can be replaced by ideal ac voltage sources as shown in Fig. 2.8, and the dc link can be considered as an ideal dc source. By applying Kirchhoff's current law to Fig. 2.8, the arm current for one phase can be defined as [17]:

$$i_{a1}(t) = \frac{1}{3}I_{dc} + \frac{1}{2}i_a(t) = \frac{1}{3}I_{dc} + \frac{1}{2}\hat{I}_a\sin(\omega_0 t + \varphi)$$

(2.1)

where  $\omega_0$  is the fundamental frequency of the system in radians per second,  $\varphi$  is the phase shift between the voltage and the current, and  $\hat{I}_a$  is the peak phase current.

Fig. 2.8. Ideal model of MMC

By applying Kirchhoff's voltage law to Fig. 2.8, the arm voltage source can be defined as:

$$v_{a1}(t) = \frac{1}{2}V_{dc} - v_a(t) = \frac{1}{2}V_{dc} - \hat{V}_a \sin(\omega_0 t)$$

(2.2)

For simplicity, (2.3) and (2.4) the relation between ac and dc variables as are defined as [16]:

$$m = \frac{3}{2} \frac{\hat{I}_a}{I_{dc}} \tag{2.3}$$

$$k = 2\frac{\hat{V}_a}{V_{dc}} \tag{2.4}$$

Introducing (2.3) and (2.4) into (2.1) and (2.2), respectively, gives:

$$i_{a1}(t) = \frac{1}{3} I_{dc} [1 + m \sin(\omega_0 t + \varphi)]$$

(2.5)

$$v_{a1}(t) = \frac{1}{2} V_{dc} [1 - k \sin(\omega_0 t)]$$

(2.6)

In order to calculate the power in the arm of the MMC, (2.5) and (2.6) are multiplied, yielding:

$$P_{a1}(t) = \frac{P_{dc}}{6} [1 + m\sin(\omega_0 t + \varphi)] [1 - k\sin(\omega_0 t)]$$

(2.7)

where  $P_{dc}$  is defined by (2.8)

$$P_{dc} = V_{dc} I_{dc} \tag{2.8}$$

Integrating (2.7) over half a period yields the total energy change  $\Delta W$  in the arm of the MMC as follows:

$$\Delta W = \frac{2 P_{dc}}{3 k\omega_0 \cos \varphi} \left[ 1 - \left(\frac{k \cdot \cos \varphi}{2}\right)^2 \right]^{3/2}$$

(2.9)

In order to obtain the energy change of the MMC SM, (2.9) is divided by the number of SMs per arm (N), yielding:

$$\Delta W_{SM} = \frac{2 P_{dc}}{3 k\omega_0 N \cos \varphi} \left[ 1 - \left(\frac{k \cdot \cos \varphi}{2}\right)^2 \right]^{3/2}$$

(2.10)

The energy stored in a capacitor is defined as:

$$W = \frac{1}{2}CV^2 \tag{2.11}$$

By combining (2.10) and (2.11), the SM capacitance can be calculated as:

$$C_{SM} = \frac{\Delta W_{SM}}{2\varepsilon V_{SM}^2} \tag{2.12}$$

where  $\varepsilon$  is the capacitor voltage ripple factor in percentage and  $V_{SM}$  is the SM voltage. The capacitors of the SM are charging and discharging during the normal operation of the MMC. This will create a voltage difference across the arm inductances that can be defined by [18]:

$$v_{dif} = V_{dc} - (v_{a1} + v_{a2}) = 2R_a i_{z_a} + 2L_a \frac{d}{dt} i_{z_a}$$

(2.13)

$$i_{za} = \frac{i_{a1} + i_{a2}}{2} \tag{2.14}$$

where  $i_{z_a}$  represents the circulating current between phases and  $R_a$  the arm resistance of the MMC. Neglecting the arm resistance, the voltage difference (2.13) can be approximated by:

$$v_{dif} = 2L_a \frac{d}{dt} i_{z\_a} \tag{2.15}$$

Then (2.15) can be used to determine the value of the arm inductance. If the inductance arm inductance is too low, the circulating current can become difficult to control; if selected too great  $v_{dif}$  becomes too large and makes the voltages of the leg difficult to balance [15]. Using (2.14) and simulations, to fine tune the results, it was found that a value of 2% was a good compromise between the two tradeoffs.

#### 2.4.3. MMC modulation strategies

Different PWM strategies can be implemented to modulate the MMC. Space vector modulation has been applied to three-level converters [19]. As the number of levels increases, the complexity of a space vector algorithm increases as well. For a high number of levels, the implementation of space vector modulation is very complex and requires high computational power. Another option is sinusoidal PWM (SPWM). For a multilevel SPWM, multiple triangular carriers are required. The number of triangular carriers is related to the number of levels of the converter. In the MMC, the number of carriers is equal to the number of SM per arm. The carriers can be arranged in a level shifted disposition (LS-SPWM) or in a phase shifted disposition (PS-SPWM). The LS-SPWM can be divided into three categories which are [20]:

- In phase disposition (IPD)

- Phase opposite disposition (POD)

- Alternative phase opposite disposition (APOD)

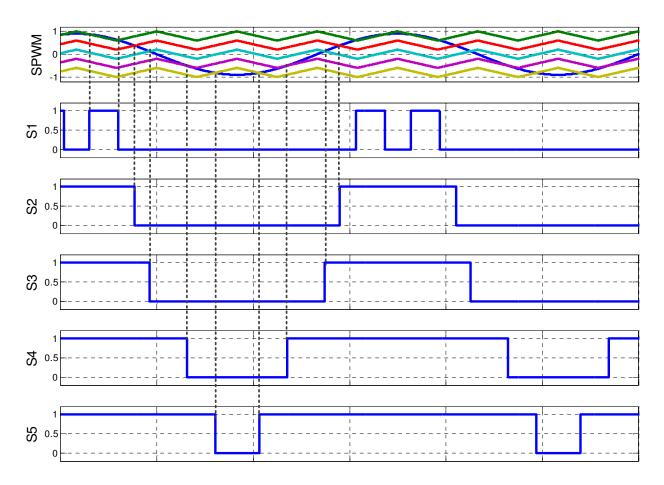

In a IPD LS-SPWM arrangement for a five-level control the carriers are spread in different levels between -1 and 1, as illustrated in Fig. 2.9. For the IPD, all the carriers are in phase, for the POD, the carriers are shifted 180° in their respective level, and for the APOD, the carriers above zero are in phase and 180° phase shift when compared to the carriers below zero. According to [15], PS-SPWM has a better performance in terms of harmonic distortion for MMC applications.

Fig. 2.9. Level Shifted PWM

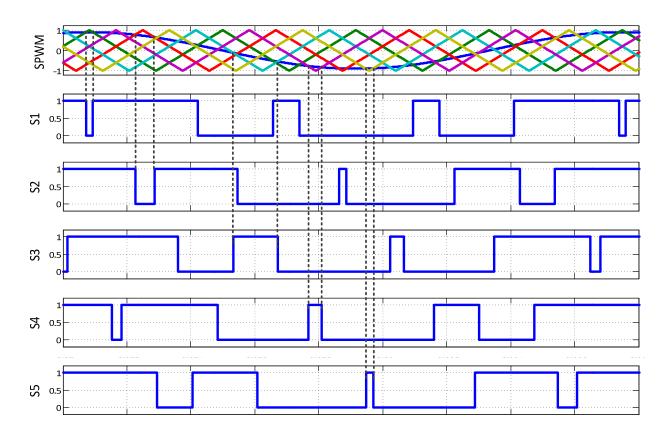

Therefore, the PS-PWM is selected to be used for the simulations of this thesis. The operation of PS-SPWM for a five-level control, with each triangular carrier controlling one of the switches, is presented in Fig. 2.10. The phase shift between the carriers is determined by:

$$\Phi = \frac{360}{N_c} \tag{2.15}$$

where  $N_c$  is the number of carriers. Equation (2.15) in the time domain becomes:

$$T_d = \frac{1}{(N_c f_c)} \tag{2.16}$$

Fig. 2.10. Phase Shifted PWM

where  $f_c$  is the triangular carrier frequency. Since the switches of the SM are complementary to each other, only one carrier is needed to control both switches. The SM on the top and bottom arm of a leg of the MMC operates in complementary manner as well [21].

The complementary operation of the SM on a leg means that the maximum amount of SM that can be on at any given time is N. The complementary operation can be represented by:

$$N = N_{on} = n_{up} + n_{low} \tag{2.17}$$

where  $N_{on}$  represents the number of SM that are inserted at any time in the MMC leg,  $n_{up}$  represents the number of SM that are inserted in the upper arm of the MMC, and  $n_{low}$  is the number of the SM that are inserted in the lower arm of the MMC.

Using the modulation scheme and concepts presented in this chapter, it is possible to simulate the operation of the MMC using an adequate simulation software package such as Matlab/Simulink<sup>TM</sup> or PSCAD<sup>®</sup>, the former is used for this thesis.

#### 2.5 Conclusions

HVdc transmission has more advantages over HVac transmission that make it more suitable when it comes to transmitting power over long distances or underwater cables. Once HVdc has been selected, a study of the right HVdc technology for the HVdc terminal must be performed. Each HVdc technology (HVdc-CSC or HVdc-VSC) has its advantages and disadvantages depending on the application, with both technologies coexisting.

Among the different HVdc-VSC topologies, the MMC has several advantages over the others making it an attractive solution for HVdc-VSC projects. Within the SM topologies for the MMC, the half-bridge it is the most efficient due to lower component count. The operation of the MMC produces a staircase shape output voltage that with a high number of levels reduces the THD of the output voltage is to the point of eliminating the necessity for ac-side filters.

Chapter Three will analyze the SM capacitor voltage controllers and the controllers used for HVdc transmission using the MMC fundamental operating principles provided in this chapter.

#### References

- [1] J. Arrillaga, Y.H. Liu, and N.R. Watson *Flexible Power Transmission, The HVDC Options*, West Sussex: John Wiley & Sons 2007.

- [2] R. Adapa, "High-Wire Act: HVdc Technology: The State of the Art," *Power and Energy Magazine, IEEE*, vol. 10, no. 6, pp. 18-29, Nov. 2012.

- [3] K. Meah, S. Ula, "Comparative Evaluation of HVDC and HVAC Transmission Systems," *Power Engineering Society General Meeting*, 2007. *IEEE*, pp. 1-5, 2007.

- [4] R. Rudervall, J. Charpentier, and R. Sharma, "High voltage direct current (HVDC) transmission systems technology review paper," *Energy week*, pp. 7-8, 2000.

- [5] ABB. *Applications for HVDC Light*®, [Online]. Available: http://www.abb.us/industries/us/9AAF400197.aspx [Accessed: Jan. 15, 2013]

- [6] M.P. Bahrman, B.K. Johnson, "The ABCs of HVDC transmission technologies," *Power* and Energy Magazine, IEEE, vol. 5, no. 2, pp. 32-44, 2007.

- [7] O. Peake, "The History of High Voltage Direct Current Transmission," *presented at the Australasian Engineering Heritage Conference*, 2009.

- [8] A. M. Abbas, P.W. Lehn, "PWM based VSC-HVDC systems A review," *Power & Energy Society General Meeting, PES '09. IEEE*, pp. 1-9, 2009.

- [9] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, Bin Wu, J. Rodriguez, M. A. Pérez, and J. I. Leon, "Recent Advances and Industrial Applications of Multilevel Converters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [10] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, M.A.M. Prats, , "The age of multilevel converters arrives," *Industrial Electronics Magazine*, *IEEE*, vol. 2, no. 2, pp. 28-39, June 2008.

- [11] Alstom "Alstom Grid will provide Tres Amigas LLC in the USA with first-of-its-kind Smart Grid "SuperStation" [Online] Available: http://www.alstom.com/presscentre/2011/4/Alstom-Grid-will-provide-Tres-Amigas-LLC-in-the-USA-with-first-of-itskind-Smart-Grid-SuperStation/ [Accessed: Jun. 2, 2013]

- [12] R. Marquardt, "Modular Multilevel Converter: An universal concept for HVDC-Networks and extended DC-Bus-applications," *Proceedings of Power Electronics Conference* (*IPEC*), 2010 International, pp. 502-507, 2010.

- [13] ABB. ABB solves 100-year-old electrical puzzle new technology to enable future DC grid [Online]. Available: http://www.abb.com/cawp/seitp202/65df338284e41b3dc1257aae0045b7de.aspx

[Accessed: Nov. 30, 2012]

- [14] E. Abildgaard, "Exploring the Properties of a Modular Multilevel Converter Based HVDC Link. With Focus on Voltage Capability, Power System Relations, and Control System," M.S. Thesis, Dept. Electric Power Eng., Norwegian Univ. of Sci. and Tech., Norway. 2012.

- [15] M. Vasiladiotis, "Analysis, Implementation and Experimental Evaluation of Control Systems for a Modular Multilevel Converter," M.S. Thesis, Dept. Elect. Eng., Roy. Tech. Inst., Stockholm, Sweden 2009.

- [16] Y. Zhang, G. P. Adam, T. C. Lim, S. J. Finney, and B. W. Williams, "Analysis and experiment validation of a three-level modular multilevel converters," *Proceedings of IEEE* 8th International Conference on Power Electronics and ECCE Asia (ICPE & ECCE), pp. 983, 990. 2011.

- [17] Y. Zhang, G. P. Adam, T. C Lim, S. J. Finney, and B. W. Williams, "Mathematical Analysis and Experimet Validation of Modular Multilevel Converters," *Journal of Power Electronics*, vol. 12, no. 1, pp. 33, 39, 2012.

- [18] A. Antonopoulos, L. Angquist, H.P. Nee, "On dynamics and voltage control of the Modular Multilevel Converter," *Proceedings of 13th European Conference on Power Electronics and Applications*, EPE '09. pp. 1-10 Sept. 2009

- [19] R.K. Behera, S.P. Das, "Space vector modulation for a three-level NPC ac-dc converter system: An experimental investigation," *Proceedings of International Conference on Power, Control and Embedded Systems (ICPCES)*, pp. 1-5, Nov. Dec. 1 2010.

- [20] C. Sandu, N. Carnu, and V. C. Costea, "Medium Voltage Modular Multi-Level Inverter," M.S. Thesis, Dept. of Energy Tech., Aalborg Univ., Aalborg, Denmark, 2008.

- [21] E. Solas, G. Abad, J. A. Barrena, A. Cárcar, and S. Aurtenetxea, "Modulation of Modular Multilevel Converter for HVDC application," *Proceedings of Power Electronics and Motion Control Conference (EPE/PEMC), 14th International*, pp. T2-84 - T2-89, 2010.

[22] T. Modeer, H.P. Nee, S. Norrga, "Loss comparison of different sub-module implementations for modular multilevel converters in HVDC applications," *Proceedings of the 2011-14th European Conference on Power Electronics and Applications (EPE 2011),* pp.1-7, 2011.

## **CHAPTER THREE**

# CONTROLLERS FOR A TWO-TERMINAL MMC-BASED HVDC TRANSMISSION SYSTEM

## Abstract

The control of two terminal MMC-based HVdc system encompasses several controllers regulating the SM capacitor voltage, minimizing the circulating currents and transferring the desired active and reactive powers. This chapter analyzes the active and reactive power outer controllers, the dc-voltage outer controller, the current controller, and the SM capacitor voltage controllers and circulating current controller. The gains for the controllers are selected using simplified models, and Bode plots and step responses are used to evaluate the current and dc voltage controllers.

### 3.1 Introduction

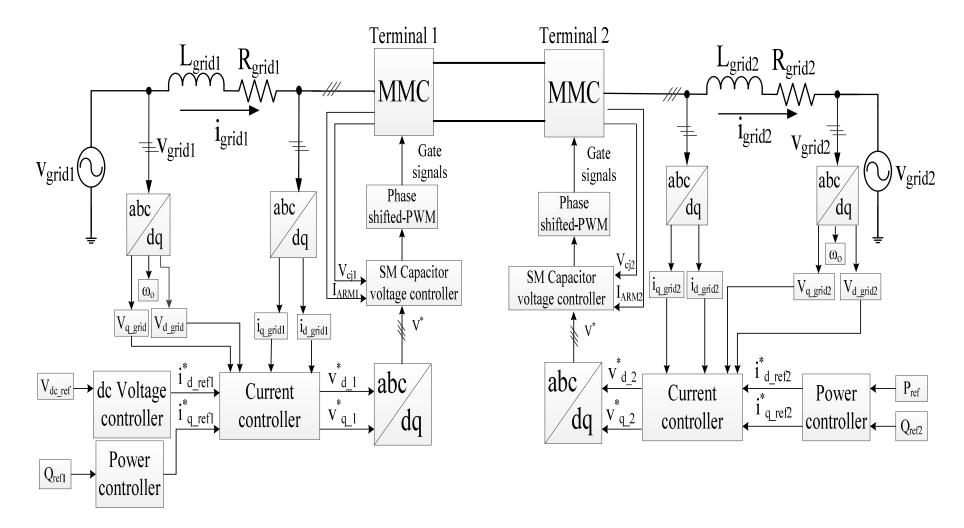

Chapter Two provided the background to understand the MMC topology and the PS-SPWM algorithm controlling the switching devices. This chapter focuses on the controllers depicted in Fig. 3.1 for a two-terminal MMC-based HVdc transmission system. It is customary to control a two-terminal HVdc link by having the sending-end Terminal 1 controlling the dc-link voltage and reactive power, and the receiving-end Terminal 2 controlling the active and reactive powers injected into the receiving grid [1]. The associated controllers are indicated in Fig. 3.1 as "dc Voltage controller", "Power controller" and "Current controller" for Terminal 1. In addition, two other control functions are

Fig. 3.1. Typical control scheme of a two terminal HVdc-link

important; namely, maintaining the SM capacitor voltages at their reference values, and controlling the circulating current to avoid system instabilities [2]. These two functions are accomplished by the "SM Capacitor voltage controller" block on each terminal. The "dc Voltage controller" and "Power controller" form the so-called outer controllers. The "Current controller" is the inner controller.

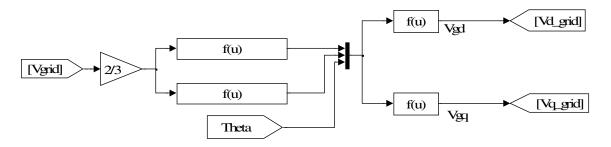

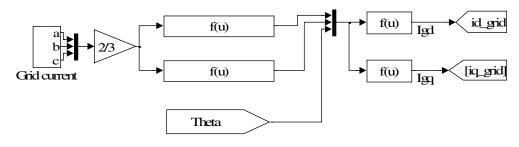

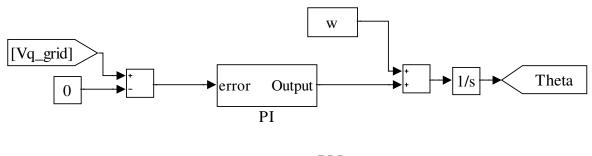

The "abc/dq" block makes use of the Park's Transformation [3] to transform from the abc stationary reference frame to a synchronously-rotating frame and its detailed Matlab/Simulink<sup>TM</sup> representation is given in Appendix A.1. The controllers are analyzed and their respective gains selected using the system whose parameters are given in Table 3.1 [4].

## **3.2 Outer Controllers**

The outer controllers could be selected as: active power control, reactive power control, dc voltage control or ac voltage control. For this application, the following is selected [5]:

- Terminal 1 (rectifier): dc voltage control and reactive power control

- Terminal 2 (inverter): active power control and reactive power control

Selecting these controllers allows for independent control of reactive power at each terminal. Terminal 1 regulates the dc-link voltage and Terminal 2 controls the power flow.

| Parameter | V <sub>dc</sub> | $V_{grid1}, V_{grid2}$ | f <sub>o</sub> | L <sub>grid1</sub> , L <sub>grid2</sub> | $R_{grid1}, R_{grid2}$ | $\mathbf{f}_{\mathrm{sw}}$ |

|-----------|-----------------|------------------------|----------------|-----------------------------------------|------------------------|----------------------------|

| Value     | ±200 kV         | 230 kV                 | 60 Hz          | 28 mH                                   | 0.75 Ω                 | 2 kHz                      |

Table 3.1. HVdc system parameters [4]

#### 3.2.1 Active and reactive power controllers

The active and reactive power controllers used in this thesis are based on the ones proposed in [6]. For a three-phase grid, the real instantaneous power is given by:

$$P(t) = Re\{\overrightarrow{v_a}(t)\}Re\{\overrightarrow{\iota_a}(t)\} + Re\{\overrightarrow{v_b}(t)\}Re\{\overrightarrow{\iota_b}(t)\} + Re\{\overrightarrow{v_c}(t)\}Re\{\overrightarrow{\iota_c}(t)\}$$

(3.1)

by means of the identity  $Re\{a\}Re\{b\} = \frac{Re\{ab\}+Re\{ab^*\}}{2}$  and space phasor notation for  $v_{abc}$ , and  $i_{abc}$ , (3.1) is rewritten as:

$$P(t) = \frac{Re\{\overrightarrow{v_{a}}(t) \, \overrightarrow{i_{a}}(t)\} + Re\{\overrightarrow{v_{a}}(t) \, \overrightarrow{i_{a}}(t)^{*}\}}{2} + \frac{Re\{\overline{v_{b}}(t) \, \overrightarrow{i_{b}}(t)e^{-j\frac{4\pi}{3}}\} + Re\{\overrightarrow{v_{b}}(t) \, \overrightarrow{i_{b}}(t)^{*}\}}{2} + \frac{Re\{\overline{v_{c}}(t) \, \overrightarrow{i_{c}}(t)e^{-j\frac{4\pi}{3}}\} + Re\{\overrightarrow{v_{c}}(t) \, \overrightarrow{i_{c}}(t)^{*}\}}{2}}{2}$$

(3.2)

For a three-phase balanced system  $e^{j0} + e^{-j\frac{4\pi}{3}} + e^{-j\frac{8\pi}{3}} \equiv 0$ , then (3.2) becomes:

$$P(t) = Re\left\{\frac{3}{2}\,\overrightarrow{v_a}(t)\,\overrightarrow{\iota_a}(t)^*\right\}$$

(3.3)

The same procedure can be applied to obtain the reactive power equation. The difference is that the imaginary part of  $\{\vec{v}(t) \ \vec{i}(t)\}$  is used when deriving the reactive power equation:

$$Q(t) = Im\left\{\frac{3}{2}\vec{v_a}(t)\vec{\iota_a}(t)^*\right\}$$

(3.4)

Equations (3.3) and (3.4) are written in the d-q synchronously-rotating frame as follows:

$$P(t) = \frac{3}{2} \left( V_{d_{grid}}(t) i_{d_{grid}}(t) + V_{q_{grid}}(t) i_{q_{grid}}(t) \right)$$

(3.5)

$$Q(t) = \frac{3}{2} \left( -V_{d\_grid}(t) i_{q\_grid}(t) + V_{q\_grid}(t) i_{d\_grid}(t) \right)$$

(3.6)

where  $V_{d_grid}$ ,  $V_{q_grid}$ ,  $i_{d_grid}$  and  $i_{d_grid}$  are the voltages and the currents in the d-q axes, respectively. For steady-state conditions, with the d axis on Phase A,  $V_{q_grid} = 0$ . Therefore, (3.5) and (3.6) under steady-state conditions, are rewritten as:

$$P(t) = \frac{3}{2} V_{d_{grid}}(t) i_{d_{grid}}(t)$$

(3.7)

$$Q(t) = -\frac{3}{2} V_{d\_grid}(t) i_{q\_grid}(t)$$

(3.8)

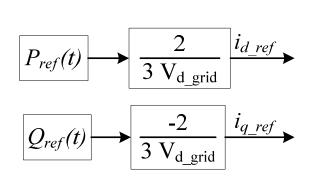

By inspection of (3.7) and (3.8), P(t) and Q(t) can be independently controlled by  $i_{d_grid}$  and  $i_{q_grid}$ , respectively, since the grid voltage is constant. Considering the fast reference tracking provided by the inner current controller explained in Section 3.3,  $i_{d_grid} \approx i_{d_ref}$  and  $i_{q_grid} \approx i_{q_ref}$ ; therefore,  $P(t) \approx P_{ref}(t)$  and  $Q(t) \approx Q_{ref}(t)$ . Taking this assumption into account and knowing that under steady-state conditions  $V_{d_grid}$  is constant, the reference commands for  $i_{dq}$  can be written as:

$$i_{d\_ref} = \frac{2}{3V_d} P_{ref}(t) \tag{3.9}$$

$$i_{q\_ref} = -\frac{2}{3V_d} Q_{ref}(t)$$

(3.10)

The control block diagrams of (3.9) and (3.10) generating the reference commands for the inner current controllers in Fig. 3.1 are shown in Fig. 3.2. The controllers for  $i_{d_grid}$  and  $i_{q_grid}$  are the ones explained in Section 3.3.

Fig. 3.2. Control block diagrams for the power controllers

#### 3.2.2 DC voltage controller at Terminal 1

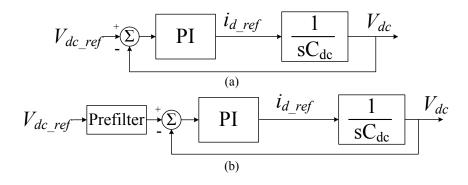

The dc voltage controller for the MMC is based on the dc controller described in [7] that provides a current reference on the d-axis for inner current controller in order to maintain the voltage of the dc link constant, as shown in Fig. 3.1. Therefore, the dc-voltage controller forms the outer loop, and the current controller forms the inner loop.

The controller was tuned first for a two-level rectifier and then implemented in the MMCbased terminal. For a two-level rectifier, the transfer function that is used to control the dc voltage across the dc-link capacitor is given by [7], [8]:

$$G_{dc}(s) = \frac{1}{sC_{dc}} \tag{3.11}$$

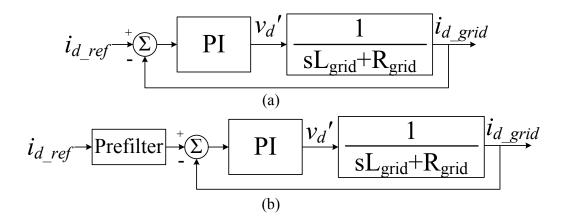

where  $C_{dc}$  is the capacitance of the dc-link capacitor. The capacitance for a two-level rectifier is calculated taking into the account the tradeoffs between ripple attenuation, provided by a high capacitance, and system dynamics, given by a lower capacitance [8]. The capacitance was calculated to be 30 mF by using (3-7) of [8] for a starting point, and then fine tuning its value via simulations using the model presented in Appendix A.2. A PI controller is implemented to control the plant in (3.11), as illustrated by Fig. 3.3(a).

Fig. 3.3. dc voltage controller block diagram with: (a) no prefilter added (b) a prefilter

added

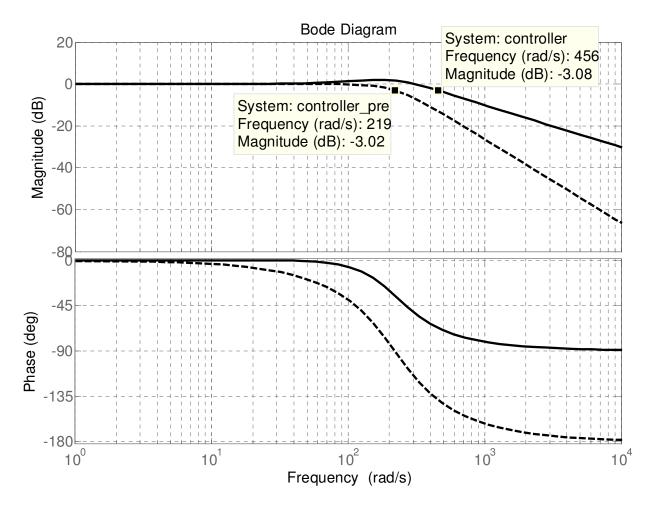

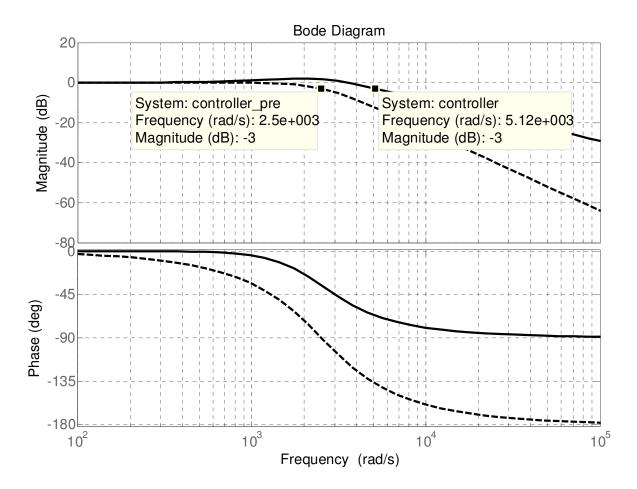

The design objectives for the voltage PI controller were selected as a damping factor of  $\xi = 0.707$  and a bandwidth of 219 rad/s (35 Hz). Using the Matlab<sup>TM</sup> code presented in Appendix A.3 the calculated values for the gains of the PI controller are  $k_{p\_dc} = 9.3 \ \Omega^{-1}$  and  $k_{i\_dc} = 1451 \ \Omega s^{-1}$  and its associated closed-loop Bode plot is shown in Fig. 3.4. The system represented by the solid line of Fig. 3.4 has no prefilter as in Fig. 3.3(a) and the crossover frequency is more than twice the desired design objective. The faster bandwidth can cause instability issues when the output of the dc voltage controller is connected to the inner current controller. Therefore, a prefilter is added to compensate for the dynamics of the system as shown in Fig. 3.3(b) and is calculated by [7]:

$$T_{\text{filter}}(s) = \frac{1}{1 + s\left(\frac{k_{\text{p}}}{k_{\text{i}}}\right)}$$

(3.12)

where  $k_p$  and  $k_i$  are the proportional and integral gains of the controller, respectively. The system performance with the prefilter, is shown by the dashed line in Fig. 3.4. The crossover frequency is as desired once the prefilter is added.

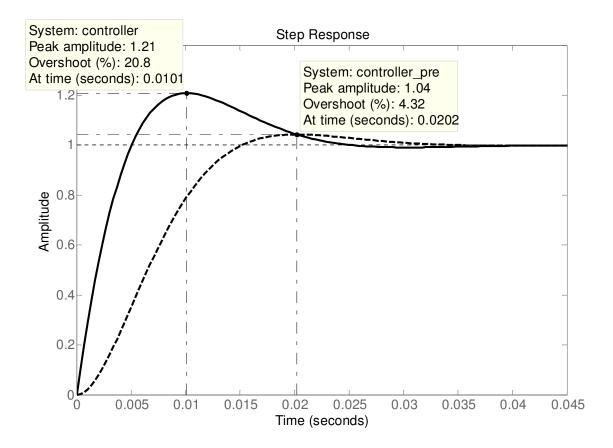

The prefilter improves the overshoot in the step response plot shown in Fig. 3.5. The response of the system in Fig 3.3(a) is plotted in a solid line, which has an overshoot of 20.8%. By adding the prefilter, the overshoot is reduced to 4.32%, as illustrated by the dashed line in Fig. 3.5. The addition of the prefilter increases the settling time from 0.022 s to 0.027 s (23%). This increase should not affect the performance of the controllers.

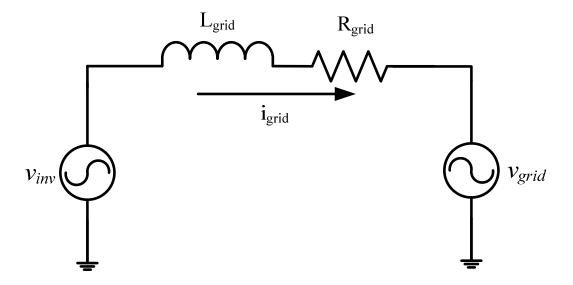

## 3.3 Inner Current Control

This section describes the current control equations described in [5], [7]-[10] and the tuning of the controller. For MMC-based terminals, this control technique assumes an infinite number of levels which leads to sinusoidal currents and voltages at the MMC ac output. Hence, the MMC

Fig. 3.4. Bode plot of the dc-voltage controller without prefilter (solid) and with prefilter

(dashed)

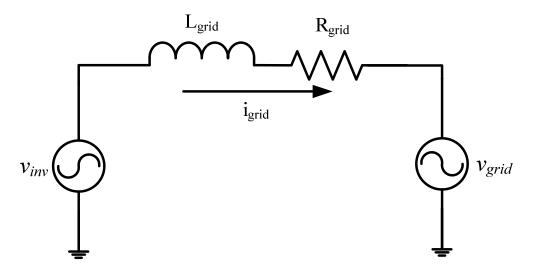

connection with the grid can be represented as in Fig. 3.6 and using Kirchhoff's voltage law yields:

$$v_{inv} = L_{grid} \frac{di_{grid}}{dt} + R_{grid} i_{grid} + v_{grid}$$

(3.13)

Fig. 3.5. Step response of the dc-voltage controller without prefilter (solid) and with

prefilter (dashed)

Fig. 3.6. Single-phase schematic of an ideal MMC connected to a grid in inverter mode

By means of the Park's Transformation [3], (3.13) can be written in a synchronously-rotating reference frame as:

$$L_{grid}\frac{d}{dt}(i_{d\_grid}) = v_{d\_inv} - v_{d\_grid} - R_{grid}i_{d\_grid} + L_{grid}\omega_o i_{q\_grid}$$

(3.14)

$$L_{grid} \frac{d}{dt} (i_{q\_grid}) = v_{q\_inv} - v_{q\_grid} - R_{grid} i_{q\_grid} - L_{grid} \omega_o i_{d\_grid}$$

(3.15)

where  $\omega_o$  is the angular frequency of the grid,  $L_{grid}$  is the grid inductance,  $v_{d\_inv}$  and  $v_{q\_inv}$  are the output voltages of the inverter in the d-q axes, and  $v_{d\_grid}$  and  $v_{q\_grid}$  are the grid voltages in the d-q axes.

The last terms in (3.14) and (3.15) show the typical cross-coupling term between the two axes; it must be eliminated in order to improve the system stability. This is accomplished by selecting inverter voltages as [7]:

$$v_{d\_inv} = v_d' + v_{d\_grid} - L_{grid}\omega_o i_{q\_grid}$$

(3.16)

$$v_{q\_inv} = v_q' + v_{q\_grid} + L_{grid}\omega_o i_{d\_grid}$$

(3.17)

where  $v_d$  and  $v_q$  are the outputs of PI controllers.

By inserting (3.16) and (3.17) into (3.14) and (3.15), respectively, and working into the Laplace domain, the following transfer function is obtained for the d-axis:

$$\frac{i_{d\_grid}}{v_{d}'} = \frac{1}{sL_{grid} + R_{grid}}$$

(3.18)

A similar equation may be obtained for the q-axis. Fig. 3.7 (a) shows the block diagram of the inner current controller for the d axis; the q axis can be represented similarly. The PI controller needs to be tuned to meet design requirements in terms of bandwidth and settling time for the system parameters in Table 3.1. The design requirements of the controller are set as follows [5]:

• Damping factor of:  $\xi = 0.707$

Fig. 3.7. Inner controller block diagram with: (a) no prefilter added (b) a prefilter added

• Bandwidth of: 10 times the dc-voltage controller and smaller than 5 times the angular switching frequency

The selected bandwidth for the controller is 2513 rads/s (400 Hz). This controller must be faster than the controller of Section 3.2 to decouple the dynamics of the state variables of both controllers. If the current controller is at least 10 times faster than the dc-voltage controller of the outer loop, then the current controller can be considered as an infinite bandwidth loop since it would be much faster than the outer loop [7]. Therefore, the current reference into the inner loop would change slowly enough so that the controller can track it without errors. With the given values for the damping and bandwidth and using the Matlab<sup>TM</sup> code presented in Appendix A.3 the calculated values for the PI controller gains are:  $k_{p_{-i}} = 99 \ \Omega$  and  $k_{i_{-i}} = 1.77 \times 10^5 \ \Omega/s$ .

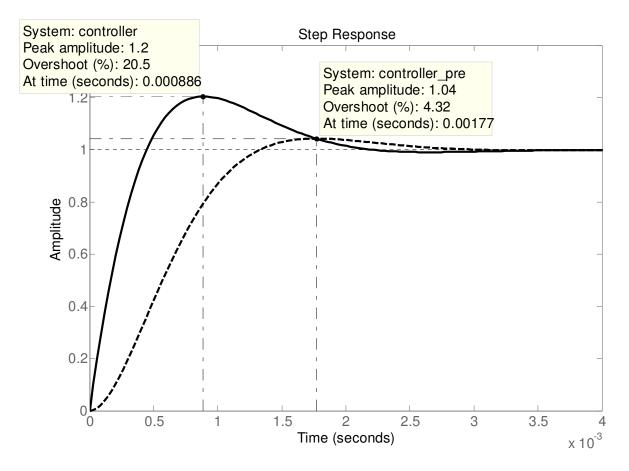

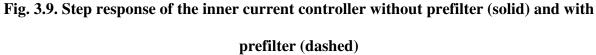

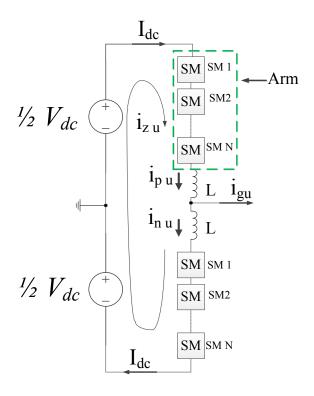

The closed-loop Bode plot of the system, shown in Fig. 3.8, is obtained using the calculated gains for the system of Fig. 3.7(a). The solid line in Fig. 3.8 corresponds to the system shown in Fig. 3.7(a); the dashed line corresponds to the system of Fig. 3.7(b). The crossover frequency of the system without the prefilter is 5.12 krad/s, wich is more than double the design target. Once

the filter is added, the bandwidth of the system is 2510 rad/s, which is the desired design target. Similar to Section 3.2.2, the prefilter also improves the step response of the system.

In Fig. 3.9, the solid line shows the step response of the system of Fig 3.7(a), and the dashed line shows the response of the system with the prefilter added, see Fig. 3.7(b). The overshoot is reduced from 20.5% without a prefilter to 4.32% with the prefilter. The tradeoff of the prefilter is that the settling time increases by 21% with the prefilter. The system still responds fast enough to react for load changes. In Fig. 3.8 and Fig. 3.9 the system is stable in a closed loop using

Fig. 3.8. Bode plot of the inner current controller without prefilter (solid) and with prefilter

(dashed)

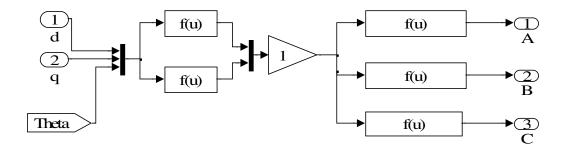

gains calculated for the controller. Therefore, these are the gains that will be used for the inner current controllers of the HVdc system illustrated in Fig. 3.10. The reference currents come from the controllers explained in Section 3.2. The two variables  $v_{d_inv}$  and  $v_{d_inv}$  are transformed into the abc frame by means of the inverse Park's Transformation to generate  $v_u^*$  for the PS-PWM algorithm controlling the switching devices.

Fig. 3.10. Inner current controller for the MMC

# 3.4 SM Capacitor Voltage and Circulating Current Control

As previously mentioned control of the SM capacitor voltage control and the circulating current are important to keep the system stable. This section is dedicated to analyze the controllers that make this possible. There are several techniques described in the MMC literature [2], [9]-[12] for controlling the SM capacitor voltages. After an evaluation, the technique presented in [2] and [10] is selected for this work, because of its capabilities of controlling the circulating current.

The main objectives of this section are to analyze the chosen technique and to explain the purpose of each of the three controllers which are:

- Capacitor average voltage control through circulating current control

- Balancing control of the instantaneous capacitor voltages

• Arm average voltage balancing control

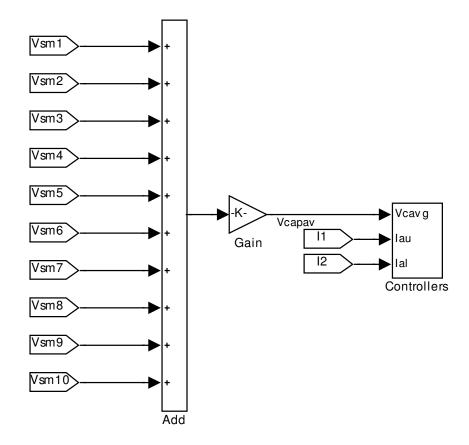

The MMC Matlab/Simulink<sup>™</sup> model used for selecting the gains of these three controllers is provided in Appendix A.4, as well as the blocks used for each controller implementation.

## 3.4.1 Capacitor average voltage control

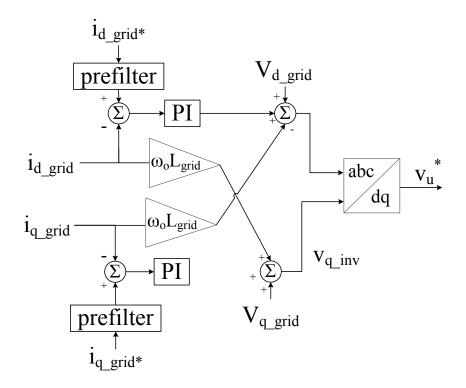

It has been demonstrated that during normal operation, the charging and discharging of the capacitors in the MMC produces a voltage difference between the dc link and the phase legs [12]. This voltage difference is associated with a phase circulating current  $i_{zu}$  that is illustrated in Fig. 3.11, which shows a single leg of an MMC. The phase circulating current is given by [2]:

$$i_{zu}(t) = \frac{i_{pu}(t) + i_{nu}(t)}{2}$$

(3.19)

where  $i_{pu}(t)$  and  $i_{nu}(t)$  are the top and the bottom currents of phase "u", which is the phase that the leg belongs to.

If it is not controlled  $i_{zu}$  raises the RMS value of the arms currents, thus, increasing the losses of the active and passive leg components, and creating disturbances during transients [12]. Reference [2] proposes to control the average capacitor voltage to generate a reference control  $i_{zu}$ , as illustrated in Fig 3.12. The capacitor average voltage is represented by  $\overline{V}_{cu}$ , where "u" is phase that the leg belongs to. For simplicity, the voltage balancing technique is explained for just one phase, but the same technique is applied to the other two phases.

The average capacitor voltage is calculated by:

$$\bar{V}_{c\,u} = \frac{1}{2N} \sum_{j=1}^{2N} v_{cju} \tag{3.20}$$

Fig. 3.11. Single-phase MMC leg

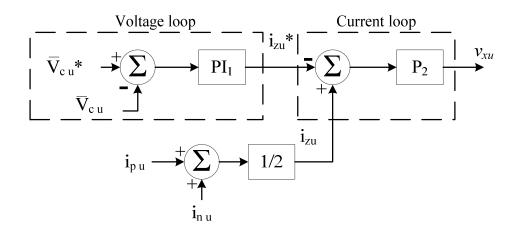

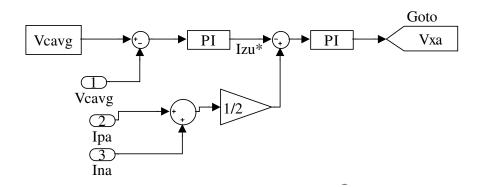

Fig. 3.12. Block diagram of the capacitor average voltage control approach

If the voltage drop across the arm inductors is neglected, the average capacitor voltage should be  $\frac{V_{dc}}{2N}$ . Taking this into account, [1] proposes the following control approach:

$$i_{zu}^{*}(t) = k_1(\bar{V}_{cu}^{*} + \bar{V}_{cu}) + k_2 \int (\bar{V}_{cu}^{*} + \bar{V}_{cu}) dt$$

(3.21)

$$v_{xu}(t) = k_3(-i_{zu}^* + i_{zu}) \tag{3.22}$$

where  $k_1$  and  $k_2$  are the proportional and integral gains of PI<sub>1</sub>, respectively, shown in Fig. 3.12 and  $k_3$  is the proportional gain of P<sub>2</sub>. A trial and error approach using the Matlab/Simulink<sup>TM</sup> model in Appendix A.4 was applied to select the gains starting with the values proposed in [10]  $(k_1 = 0.3 \text{ A/V}, k_2 = 3 \text{ A/(Vs)}$  and  $k_3 = 1 \text{ V/A}$ ). After several tests, with different gains, the best results were obtained with the values proposed in [10]. There are two loops in this controller, as presented in Fig. 3.12.

The output of the voltage loop produces the current reference  $i_{zu}^*$  necessary to force the average capacitor voltage to follow the reference the commanded voltage  $\overline{V}_{cu}^*$ . The current loop forces the circulating current  $i_{zu}$  to follow the reference command  $i_{zu}^*$  generated by the voltage loop. These two loops generate a voltage reference named  $v_{xu}$ . This strategy controls the average capacitor voltage and the circulating current without affecting the control of the phase current [2], [10], [12].

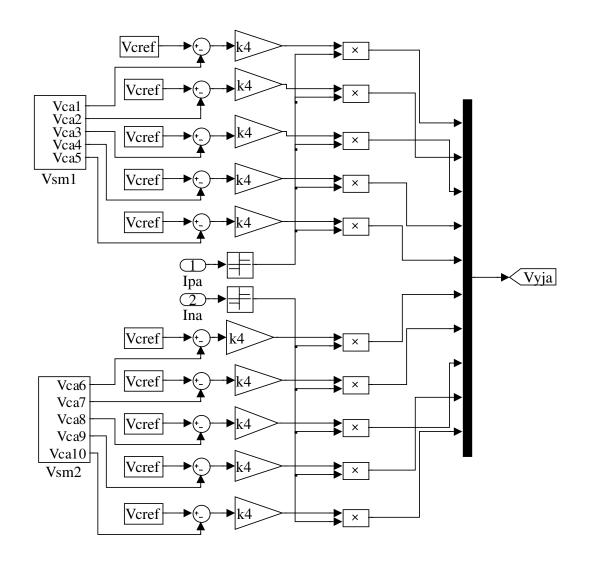

#### 3.4.2 Balancing control of the instantaneous capacitor voltage

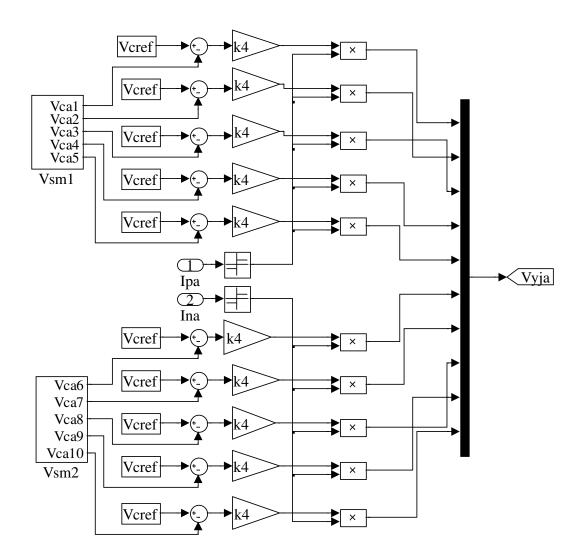

This controller forces the instantaneous voltage of the SM  $v_{cju}$  to follow the voltage reference  $v_{cju}^*$ , and thus, makes sure that the SM voltages are balanced. This controller uses the polarity of the currents  $i_{pu}$  and  $i_{nu}$  to select the sign of the controller output. For the upper arm, the SM capacitors are charging and power is transferred into the SM capacitors when  $i_{pu}$  is positive, while the SM capacitors are discharging and power transferred out of the SM capacitors when  $i_{pu}$  is negative. The same is true for the lower arm. The control block diagram of this controller is presented in Fig. 3.13 and its equations are [2]:

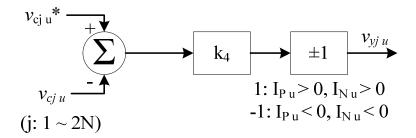

Fig. 3.13. Individual capacitor voltage balancing control block diagram

$$v_{yj\,u} = \pm 1 \, k_4 \left( v_{cju}^* + v_{cju} \right); \, 1: i_{p\,u} > 0, -1: i_{p\,u} < 0 \tag{3.23}$$

where  $v_{cju}^*$  given by  $\frac{V_{dc}}{N}$ , since the arm SMs operate in a complementary way,  $k_4$  is the proportional constant that is shown in Fig. 3.14. The value of the gain is selected with the same procedure as in Section 3.2.1. The conclusion of this process is that a gain  $k_4 = 0.5$ , proposed in [10], works well for this controller. The model used for testing for this gain is provided in Appendix A.4.

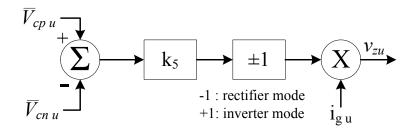

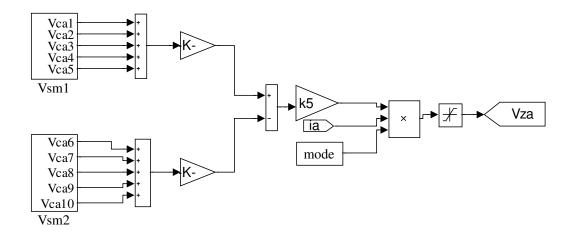

#### 3.4.3 Arm average voltage balancing control

Applying Routh-Hurwitz stability criterion to the previous two controllers provides that the system is unstable if the MMC operates as a rectifier [10]. To make the system stable for all operating modes, the controller shown in Fig. 3.14 is proposed in [10]. The control purpose is to minimize the difference between the average voltages of the upper  $\bar{V}_{cp\,u}$  and lower arm  $\bar{V}_{cn\,u}$ . The control law for this controller is as follows:

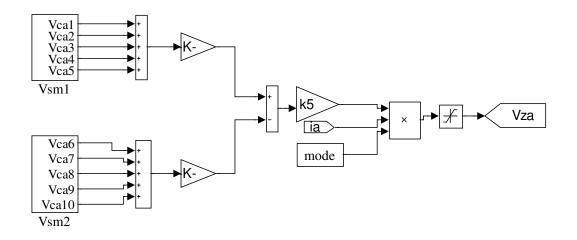

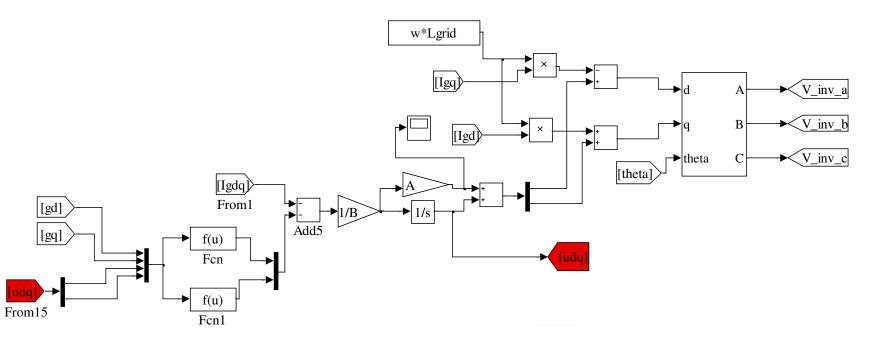

$$v_{zu} = \pm 1 k_5 \left( \bar{V}_{cp u} - \bar{V}_{cn u} \right) i_{g u}(t); \quad 1: inverter \ mode, \ -1: rectifier \ mode \qquad (3.25)$$

where  $i_{gu}(t)$  is the grid phase current corresponding to the arms being controlled and  $k_5$  is the proportional gain of the controller, selected to be 0.5 A<sup>-1</sup> [10], by using the same process as in

Fig. 3.14. Arm average voltage balancing control block diagram

Section 3.2.1. When the MMC is operating as an inverter,  $k_5$  is positive, and when is operating as a rectifier,  $k_5$  is negative [10].

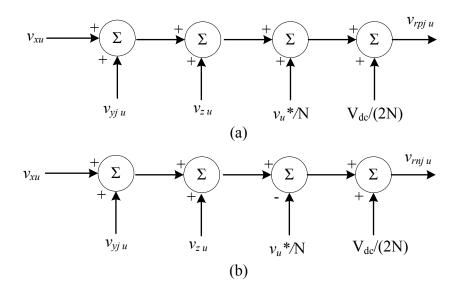

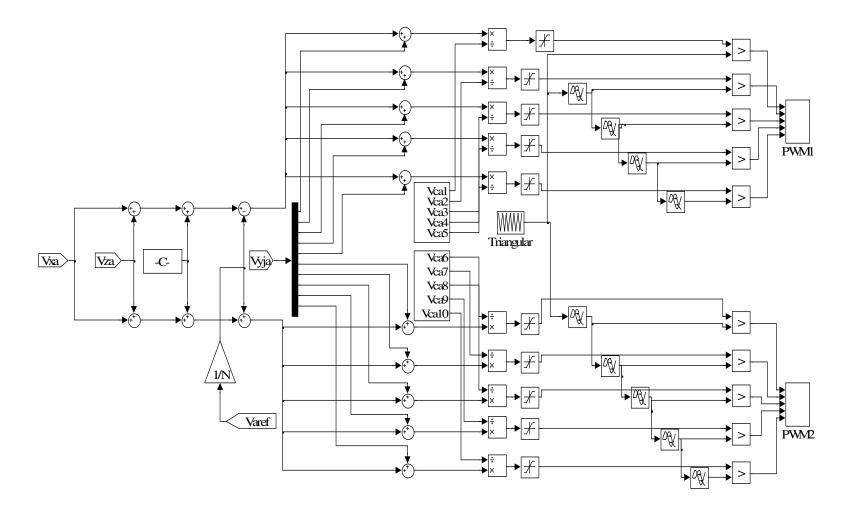

#### 3.5 Voltage Reference Generation

Once all the capacitor voltage controllers have been implemented, and the control voltages are produced by the current controllers, the reference voltage for switching the switches in a SM is formed as shown in Fig. 3.15. This reference voltage is the control voltage for the PS-PWM algorithm. Since the MMC arm operations are complementary, the references for the upper arm and the lower arm are also complementary. In Fig. 3.15  $v_{rpju}$  is the control voltage for a SM capacitor in the upper arm and  $v_{rnju}$  is the control voltage for a SM capacitor in the lower arm; these variables are given by:

$$v_{rpj\,u} = v_{xu} + v_{yju} + v_{zu} + \frac{v_u^*}{N} + \frac{v_{dc}}{2N}$$

(3.24)

$$v_{rnj\,u} = v_{xu} + v_{yju} + v_{zu} - \frac{v_u^*}{N} + \frac{V_{dc}}{2N}$$

(3.25)

where  $v_{xu}$ ,  $v_{yju}$  and  $v_{zu}$  are given by the controllers explained in previous sections. The variable  $v_u^*$  is generated by the controller explained in Sections 3.3. The term  $\frac{V_{dc}}{2N}$  in (3.24) and (3.25) is a voltage feedforward term which corresponds to half of the nominal SM voltage; the nominal SM voltage could be used as well. Making use of simulations it was determined that using  $\frac{V_{dc}}{2N}$

Fig. 3.15. Reference voltage generation: (a) top arm, (b) bottom arm

reduces the settling time of the overall capacitor voltage controller. The terms  $v_{rpju}$  and  $v_{rnju}$  are normalized by the instantaneous individual capacitor voltage, and then used as the control voltage for the PS-PWM to control the switching of the SMs.

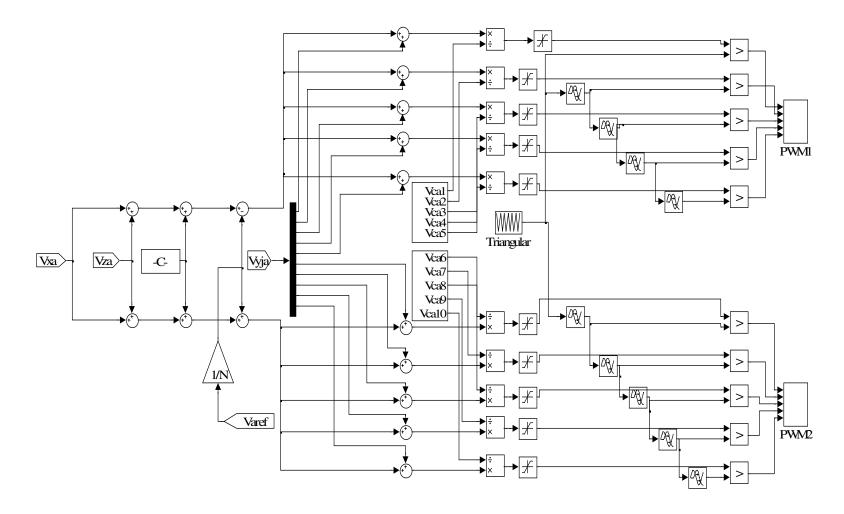

The Matlab/Simulink<sup>™</sup> implementation of Fig. 3.15 together with the PS-PWM algorithm to control the switches is depicted in Appendix A.4.

#### 3.6 Conclusions

Each of the controllers of the MMC-based HVdc terminal performs a different function and by the combination of all of them it is possible to control the active and reactive powers injected into a grid.

For the capacitor voltage controllers, it is important to control the circulating current between the legs and the dc-link, to reduce losses and ensure system stability. The arm-balancing voltage control is required to make the capacitor voltage controllers stable under all operating modes of the terminal. For the current and dc voltage controllers, the use of prefilters improves the system bandwidth and step response. Both controllers have been designed for a transfer function modeling the functioning of an MMC and need to be validated by simulations.

These controllers will be validated through system simulations in Chapter Four. The controllers will be also compared with a sensorless control technique for the inverter terminal that is described in Chapter Four.

# References