# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2012

# The Development and Packaging of a High-Density, Three-Phase, Silicon Carbide (SiC) Motor Drive

Jared Hornberger University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd Part of the <u>Electronic Devices and Semiconductor Manufacturing Commons</u>, and the <u>VLSI and</u> <u>Circuits</u>, <u>Embedded and Hardware Systems Commons</u>

### **Recommended** Citation

Hornberger, Jared, "The Development and Packaging of a High-Density, Three-Phase, Silicon Carbide (SiC) Motor Drive" (2012). *Theses and Dissertations*. 637. http://scholarworks.uark.edu/etd/637

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

# THE DEVELOPMENT AND PACKAGING OF A HIGH-DENSITY, THREE-PHASE, SILICON CARBIDE (SIC) MOTOR DRIVE

# THE DEVELOPMENT AND PACKAGING OF A HIGH-DENSITY, THREE-PHASE, SILICON CARBIDE (SIC) MOTOR DRIVE

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

By

Jared Martin Hornberger University of Arkansas Bachelor of Science in Electrical Engineering, 2002 University of Arkansas Master of Science in Electrical Engineering, 2004

> December 2012 University of Arkansas

#### ABSTRACT

Technology advances within the power electronics field are resulting in systems characterized by higher operating efficiencies, reduced footprint, minimal form factor, and decreasing mass. In particular, these attributes and characteristics are being inserted into numerous consumer applications, such as light-emitting diode lighting, compact fluorescent lighting, smart phones, and tablet PCs, to industrial applications that include hybrid, electric, and plug-in electric vehicles and more electric aircraft. To achieve the increase in energy efficiency and significant reduction in size and mass of these systems, power semiconductor device manufacturers are developing silicon carbide (SiC) semiconductor technology.

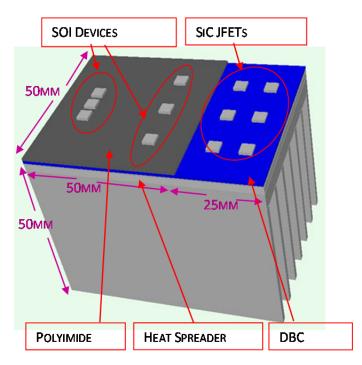

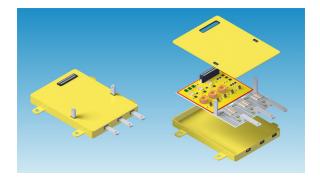

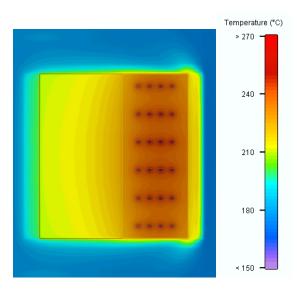

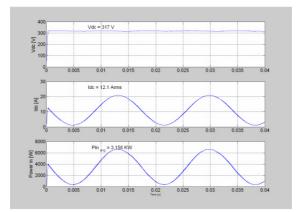

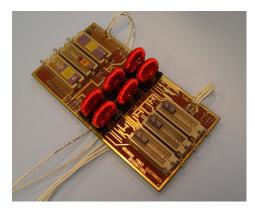

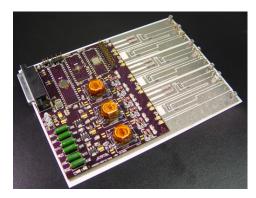

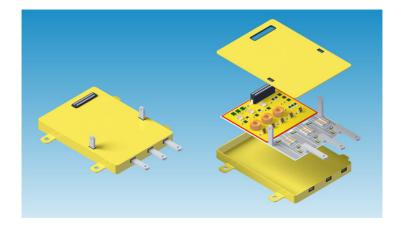

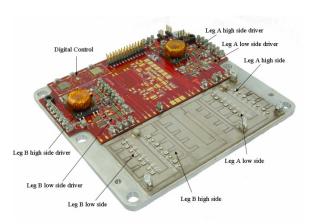

In this dissertation, the author discusses the design, development, packaging, and fabrication of the world's first multichip power module (MCPM) that integrates SiC power transistors with silicon-on-insulator (SOI) integrated circuits. The fabricated MCPM prototype is a 4 kW, three-phase inverter that operates at temperatures in excess of 250 °C. The integration of high-temperature metal-oxide semiconductor (HTMOS) SOI bare die control components with SiC power JFET bare die into a single compact module are presented in this work. The high-temperature operation of SiC switches allows for increased power density over silicon electronics by an order of magnitude, leading to highly miniaturized power converters.

This dissertation is organized into a compilation of publications written by the author over the course of his Ph.D. work. The work presented throughout these publications covers the challenges associated with power electronics miniaturization and packaging including highpower density, high-temperature, and high-efficiency operation of the power electronic system under study. This dissertation is approved for recommendation to the Graduate Council.

# **Dissertation Director:**

Dr. H. Alan Mantooth

**Dissertation Committee:**

Dr. Alexander B. Lostetter

Dr. Rick J. Couvillion

Dr. Simon S. Ang

Dr. William D. Brown

# DISSERTATION DUPLICATION RELEASE

I hereby authorize the University of Arkansas Libraries to duplicate this dissertation when needed for research and/or scholarship.

Agreed \_\_\_\_\_\_ Jared M. Hornberger

Refused \_\_\_\_\_\_\_\_\_\_Jared M. Hornberger

#### ACKNOWLEDGMENTS

Thanks first to my family for helping me through the last several years to achieve my goal of obtaining a doctoral degree. Thanks to my wife Anne and daughters Hannah, Ella, & Lydia for standing by me and supporting me. Thanks to my parents for teaching me the value of hard work and education and for always being there for me in whatever endeavor I take on.

I would like to thank my good friend Alex Lostetter for being an inspiration, a great leader, and great mentor. Without your help and support this goal of achieving a doctoral degree would not have happened. Thanks to my friends and co-authors; Sharmila Mounce, Brice McPherson, and Edgar Cilio, you have helped and have been an instrumental part in my research. Thanks to all at Arkansas Power Electronics International, Inc. for your help and encouragement.

Thanks to my advisor, Dr. Alan Mantooth, for your leadership and for supporting my research goals. Thanks to my other committee members, Dr. Alex Lostetter, Dr. Rick Couvillion, Dr. Simon Ang, and Dr. William Brown, for being there for me when I needed assistance. Additionally thanks to Dr. Kraig Olejniczak for your mentorship, for getting me started in graduate school, and for helping read through and edit this dissertation.

Finally, I give my appreciation to God and country for giving me the opportunities that have so greatly blessed my life and the life of my family. I'm humbled by the grace of God and his presence in my life. I'm grateful for the opportunity to live in the Unites States of America and for the freedoms that I have and enjoy from being a citizen of this great land.

# TABLE OF CONTENTS

| CHAPTER 1 INTRODUCTION                                              | . 1 |

|---------------------------------------------------------------------|-----|

| REFERENCES                                                          | . 2 |

| CHAPTER 2 RESEARCH DIRECTION                                        | . 3 |

| REFERENCES                                                          | . 5 |

| CHAPTER 3 SILICON-CARBIDE (SIC) SEMICONDUCTOR POWER ELECTRONICS FO  | R   |

| EXTREME HIGH-TEMPERATURE ENVIRONMENTS                               | . 7 |

| REFERENCES                                                          | 47  |

| CHAPTER 4 A NOVEL THREE-PHASE MOTOR DRIVE UTILIZING SILICON ON      |     |

| INSULATOR (SOI) AND SILICON-CARBIDE (SIC) ELECTRONICS FOR           |     |

| EXTREME ENVIRONMENT OPERATION IN THE ARMY FUTURE COMBAT             |     |

| SYSTEMS (FCS)                                                       | 51  |

| REFERENCES                                                          | 62  |

| CHAPTER 5 HIGH-TEMPERATURE SILICON CARBIDE (SIC) POWER SWITCHES IN  |     |

| MULTICHIP POWER MODULE (MCPM) APPLICATIONS                          | 65  |

| REFERENCES                                                          | 76  |

| CHAPTER 6 HIGH-TEMPERATURE INTEGRATION OF SILICON CARBIDE (SIC) AND |     |

| SILICON-ON-INSULATOR (SOI) ELECTRONICS IN MULTICHIP POWER           |     |

| MODULES (MCPMS)                                                     | 79  |

| REFERENCES                                                          | 94  |

| CHAPTER 7 PACKAGING OF A HIGH-TEMPERATURE SILICON CARBIDE (SIC)     |     |

| MULITCHIP POWER MODULE (MCPM)                                       | 97  |

| REFERENCES                                                          |     |  |

|---------------------------------------------------------------------|-----|--|

| CHAPTER 8 A HIGH-TEMPERATURE MULTICHIP POWER MODULE (MCPM)          |     |  |

| INVERTER UTILIZING SILICON CARBIDE (SIC) AND SILICON ON             |     |  |

| INSULATOR (SOI) ELECTRONICS                                         | 113 |  |

| REFERENCES                                                          | 129 |  |

| CHAPTER 9 A HIGH-TEMPERATURE SILICON CARBIDE (SIC) MULITCHIP POWE   | ER  |  |

| MODULE (MCPM) INVERTER FOR DOWN-HOLE APPLICATIONS                   | 132 |  |

| REFERENCES                                                          | 148 |  |

| CHAPTER 10 PACKAGING OF A HIGH-TEMPERATURE SILICON CARBIDE (SIC)    |     |  |

| THREE-PHASE 4KW MOTOR DRIVE                                         | 151 |  |

| REFERENCES                                                          | 168 |  |

| CHAPTER 11 A FULLY INTEGRATED 300°C, 4 KW, 3-PHASE, SIC MOTOR DRIVE |     |  |

| MODULE                                                              | 172 |  |

| REFERENCES                                                          | 186 |  |

| CHAPTER 12 SILICON CARBIDE POWER ELECTRONICS PACKAGING              | 189 |  |

| REFERENCES                                                          | 221 |  |

| CHAPTER 13 SUMMARY OF PUBLICATIONS                                  | 225 |  |

| REFERENCES                                                          | 235 |  |

| CHAPTER 14 CONCLUSIONS AND RECOMENDATIONS                           | 236 |  |

| APPENDIX                                                            | 237 |  |

# LIST OF PAPERS

- [1] J. Hornberger, A. B. Lostetter, K. J. Olejniczak, T. McNutt, S. M. Lal, and A. Mantooth, "Silicon-carbide (SiC) semiconductor power electronics for extreme high-temperature environments," in the Proc. of the IEEE Aerospace Conference, vol. 4, pp. 2538 – 2555, March 2004.

- [2] J. Hornberger, A. B. Lostetter, K. J. Olejniczak, S. Magan Lal, and A. Mantooth, "A Novel Three Phase Motor Drive Utilizing Silicon on Insulator (SOI) and Silicon-Carbide (SiC) Electronics for Extreme Environment Operation in the Army Future Combat Systems (FCS)," in the Proc. of the 37th International Symposium on Microelectronics (IMAPS 2004), vol. 2, pp. 649 – 654, November 2004.

- [3] J. Hornberger, S. Mounce, R. Schupbach, B. McPherson, H. Mustain, A. Mantooth, W. Brown, and A. B. Lostetter, "High-Temperature Integration of Silicon Carbide (SiC) and Silicon-on-Insulator (SOI) Electronics in Multichip Power Modules (MCPMs)," in the Proc. of the 11th European Conference on Power Electronics and Applications (EPE 2005), pp. 1-10, September 2005.

- [4] J. Hornberger, B. McPherson, E. Cilio, R. M. Schupbach, S. Mounce, A. B. Lostetter, and H. A. Mantooth, "Packaging of a High-Temperature Silicon Carbide (SiC) Mulitchip Power Module (MCPM)," in the Proc. of the 38th International Symposium on Microelectronics (IMAPS 2005), vol. 2, pp. 579 – 585, September 2005.

- [5] J. Hornberger, S. Mounce, R. Schupbach, H. A. Mantooth, and A. B. Lostetter, "High-Temperature Silicon Carbide (SiC) Power Switches in Multichip Power Module (MCPM) Applications," in the Proc. of the Fortieth IEEE Industry Applications Society Annual Meeting, vol. 1, pp. 393 – 398, October 2005.

- [6] J. Hornberger, E. Cilio, B. McPherson, R. Schupbach, A. Lostetter, and A. Mantooth, "A High-Temperature Silicon Carbide (SiC) Mulitchip Power Module (MCPM) Inverter for Down-Hole Applications," in the Proc. of the International Conference on High Temperature Electronics (HiTEC 2006), vol. 1, pp. 279 – 286, May 2006.

- [7] Jared M. Hornberger, Edgar Cilio, Roberto M. Schupbach, Alexander B. Lostetter, and H. Alan Mantooth, "A High-Temperature Multichip Power Module (MCPM) Inverter Utilizing Silicon Carbide (SiC) and Silicon on Insulator (SOI) Electronics," in the Proc. of the 37th IEEE Power Electronics Specialists Conference (PESC 2006), vol. 1, pp. 9 – 15, June 2006.

- [8] J. M. Hornberger, B. McPherson, E. Cilio, R. M. Schupbach, A. B. Lostetter, and H. A. Mantooth, "Packaging of a High-Temperature Silicon Carbide (SiC) Three-Phase 4 kW Motor Drive," in the Proc. of the 39th International Symposium on Microelectronics (IMAPS 2006), vol. 2, pp. 721 728, October 2006.

- [9] Jared M. Hornberger, Edgar Cilio, Brice McPherson, Roberto M. Schupbach, Alexander B. Lostetter, and H. Alan Mantooth, "A Fully Integrated, 4 kW, 3-Phase, SiC Motor

Drive Module," in the Proc. of the 38th IEEE Power Electronics Specialists Conference (PESC 2007), vol. 1, pp. 1048 – 1053, June 2007.

[10] Hornberger et al., "Silicon Carbide Power Electronics Packaging," Cressler J. D., Mantooth H. A., Extreme Environment Electronics 1st ed., Boca Raton, FL, CRC Press, 2012, Ch. 69, pp. 803-817.

#### **CHAPTER 1**

#### INTRODUCTION

Since the first silicon carbide (SiC) Schottky diode was introduced to the commercial market in 2001 [1], there have been many research facilities and commercial entities that have put forth much effort to bring to life SiC power electronic devices such as metal-oxide-semiconductor field-effect transistors (MOSFETs), junction field-effect transistors (JFETs), bipolar junction transistors (BJTs), and gate-turn-off (GTOs) thyristors. As a wide bandgap material, SiC has many enhanced capabilities over state of the art silicon (Si) power devices. For example, when compared to Si, SiC can operate at higher temperatures (up to 600 °C), higher switching frequencies (10-100 times), has decreased energy losses (1/10th), has a higher breakdown voltage (10 times that of Si), and is capable of higher current densities (3-4 times higher than Si) [2]. Together with the advantages of SiC and the advancements made to fabricate SiC power devices, the power electronics industry is undergoing a technology revolution where power electronic systems and applications can see an order of magnitude decrease in size and weight with a simultaneous increase in performance.

Applications that can benefit from SiC are widespread and all-encompassing in the area of power electronics. Some of these applications include, but are not limited to, electric motor drives for hybrid electric and electric vehicles; motor drives and power converters for aircraft, spacecraft, and space exploration vehicles; power converters for solar power, wind power, and geological exploration; and solid-state circuit breakers and current limiters for industrial electric transmission, distribution, and smart grid systems. Ultimately, any system that would see improvement from high-density, high-efficiency, or high-temperature power electronics would benefit from SiC. While significant effort has been dedicated to bringing these new SiC power electronic devices to life, resources to develop systems with SiC as well as the power electronic packaging that fully enable the benefits of SiC have been lacking. The work presented here by the researcher represents efforts to advance state of the art power electronic systems through the development of circuits, applications, and power electronic packaging.

# REFERENCES

- [1] Phlippen, F. and Burger, B., A New High Voltage Schottky Diode Based on Silicon Carbide (SiC), *Proceedings of EPE'01*, Graz, Austria, 2001.

- [2] Harris, Properties of Silicon-carbide, INSPEC, London, United Kingdom, 1995.

#### **CHAPTER 2**

## **RESEARCH DIRECTION**

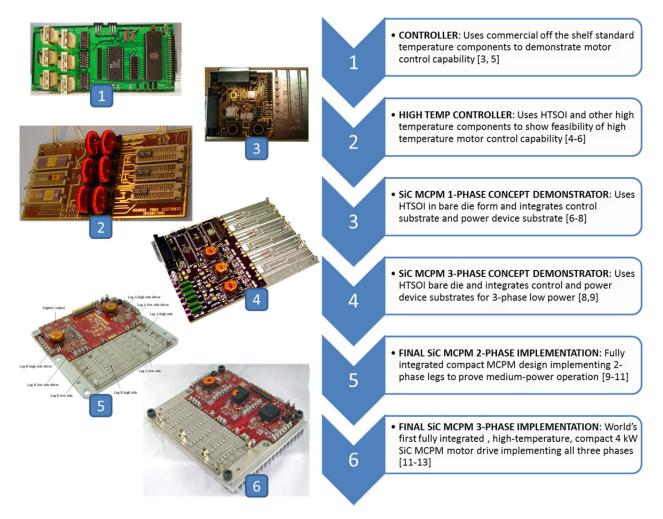

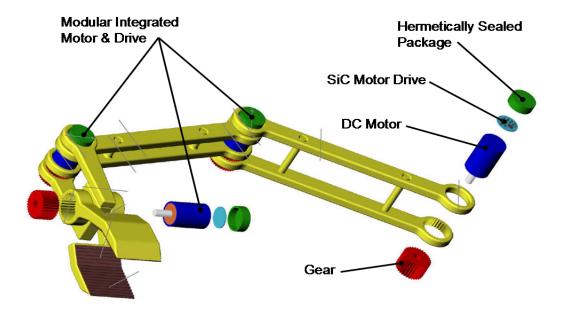

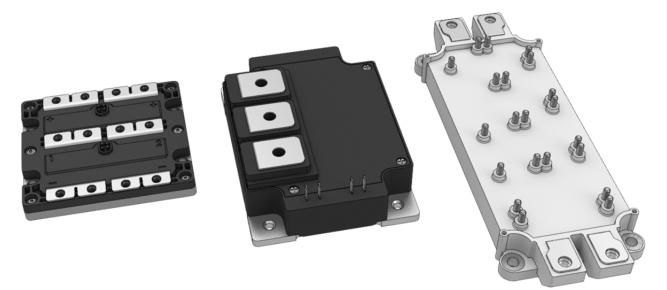

The goal of this research is to advance the field of power electronics by utilizing SiC power devices; to reach this goal there have been many steps and milestones achieved along the way. This dissertation is portrayed in the format where research goals, milestones, and results are discussed throughout several publications. Figure 2.1 depicts the path of the author to reach the ultimate goal of developing the world's first SiC multichip power module (MCPM) motor drive with integrated control capable of high-temperature operation above 250 °C.

The first goal was to develop a controller capable of three-phase operation and transition the design to high-temperature components. This work was conducted in the author's master's work [3].

The second goal was to transition the control circuitry to high-temperature components and to demonstrate controller operation at high temperature. The description of research relating to this second goal is described in [4-6].

After implementation of the controller at high temperature, the third goal was to implement the MCPM concept with a single-phase, low-power demonstrator transitioning from packaged board-level components to an integrated bare die form. This single-phase MCPM, research milestone three, is discussed in [6-8].

The fourth research milestone was to transition from a single-phase MCPM demonstrator to a three-phase, low-power MCPM demonstrator. Results for fabrication and testing of this demonstrator are discussed in [8, 9].

3

The fifth goal was to develop the fully-integrated final design of the high-temperature MCPM, and to test it for high-power operation in a single-phase implementation of the module. The results of this fifth research milestone are discussed in [9-11].

Finally, the fully-integrated, high-temperature, three-phase MCPM prototype was implemented at high-power and shown operational to > 250 °C. The results of research milestone six are discussed in [11-13].

**Figure 2.1:** Research milestones achieved through the course of developing a high-temperature three-phase motor drive from concept to tested prototype.

### REFERENCES

- [3] J. Hornberger, "A Novel 4-HP High-Temperature 3-Phase Induction Motor Drive Utilizing a Silicon-on-Insulator HT87C51 Microcontroller," Master's Thesis, University of Arkansas, Fayetteville, AR, 2004.

- [4] J. Hornberger, A. B. Lostetter, K. J. Olejniczak, T. McNutt, S. M. Lal, and A. Mantooth, "Silicon-carbide (SiC) semiconductor power electronics for extreme high-temperature environments," in the *Proc. of the IEEE Aerospace Conference*, vol. 4, pp. 2538 – 2555, March 2004.

- [5] J. Hornberger, A. B. Lostetter, K. J. Olejniczak, S. Magan Lal, and A. Mantooth, "A Novel Three Phase Motor Drive Utilizing Silicon on Insulator (SOI) and Silicon-Carbide (SiC) Electronics for Extreme Environment Operation in the Army Future Combat Systems (FCS)," in the *Proc. of the 37th International Symposium on Microelectronics* (IMAPS 2004), vol. 2, pp. 649 – 654, November 2004.

- [6] J. Hornberger, S. Mounce, R. Schupbach, H. A. Mantooth, and A. B. Lostetter, "High-Temperature Silicon Carbide (SiC) Power Switches in Multichip Power Module (MCPM) Applications," in the *Proc. of the Fortieth IEEE Industry Applications Society Annual Meeting*, vol. 1, pp. 393 – 398, October 2005.

- [7] J. Hornberger, S. Mounce, R. Schupbach, B. McPherson, H. Mustain, A. Mantooth, W. Brown, and A. B. Lostetter, "High-Temperature Integration of Silicon Carbide (SiC) and Silicon-on-Insulator (SOI) Electronics in Multichip Power Modules (MCPMs)," in the *Proc. of the 11th European Conference on Power Electronics and Applications* (EPE 2005), pp. 1 10, September 2005.

- [8] J. Hornberger, B. McPherson, E. Cilio, R. M. Schupbach, S. Mounce, A. B. Lostetter, and H. A. Mantooth, "Packaging of a High-Temperature Silicon Carbide (SiC) Mulitchip Power Module (MCPM)," in the *Proc. of the 38th International Symposium on Microelectronics* (IMAPS 2005), vol. 2, pp. 579 – 585, September 2005.

- [9] Jared M. Hornberger, Edgar Cilio, Roberto M. Schupbach, Alexander B. Lostetter, and H. Alan Mantooth, "A High-Temperature Multichip Power Module (MCPM) Inverter Utilizing Silicon Carbide (SiC) and Silicon on Insulator (SOI) Electronics," in the *Proc.* of the 37th IEEE Power Electronics Specialists Conference (PESC 2006), vol. 1, pp. 9 – 15, June 2006.

- [10] J. Hornberger, E. Cilio, B. McPherson, R. Schupbach, A. Lostetter, and A. Mantooth, "A High-Temperature Silicon Carbide (SiC) Mulitchip Power Module (MCPM) Inverter for Down-Hole Applications," in the *Proc. of the International Conference on High Temperature Electronics* (HiTEC 2006), vol. 1, pp. 279 – 286, May 2006.

- [11] J. M. Hornberger, B. McPherson, E. Cilio, R. M. Schupbach, A. B. Lostetter, and H. A. Mantooth, "Packaging of a High-Temperature Silicon Carbide (SiC) Three-Phase 4 kW Motor Drive," in the *Proc. of the 39th International Symposium on Microelectronics* (IMAPS 2006), vol. 2, pp. 721 728, October 2006.

- [12] Jared M. Hornberger, Edgar Cilio, Brice McPherson, Roberto M. Schupbach, Alexander B. Lostetter, and H. Alan Mantooth, "A Fully Integrated, 4 kW, 3-Phase, SiC Motor Drive Module," in the *Proc. of the 38th IEEE Power Electronics Specialists Conference* (PESC 2007), vol. 1, pp. 1048 – 1053, June 2007.

- [13] Hornberger et al., "Silicon Carbide Power Electronics Packaging," Cressler J. D., Mantooth H. A., *Extreme Environment Electronics 1st ed.*, Boca Raton, FL, CRC Press, 2012, Ch. 69, pp. 803-817.

### **CHAPTER 3**

#### SILICON-CARBIDE (SIC) SEMICONDUCTOR POWER ELECTRONICS FOR

#### **EXTREME HIGH-TEMPERATURE ENVIRONMENTS**

J. Hornberger, A. B. Lostetter, K. J. Olejniczak T. McNutt, S. Magan Lal, and A. Mantooth

© 2004 IEEE. Reprinted, with permission, from Hornberger et al, Silicon-Carbide (SiC) Semiconductor Power Electronics for Extreme High-Temperature Environments, IEEE Aerospace Conference, March 2004.

### ABSTRACT

This paper will discuss the current state of SiC electronics research at Arkansas Power Electronics International, Inc. (APEI) with regard to high-temperature environments and applications. The University of Arkansas (UA) researchers' modeling and characterization of SiC power devices for these high-temperature environments will also be discussed. Devices to be covered include SiC Schottky diodes, SiC power MOSFETs, and SiC static-induction-transistors (SITs). The paper will review the current application of these devices to the specific harsh environments of deep Earth drilling and combat electric vehicles, as well as outline APEI's research work into developing operational SiC motor drives for these systems. It is proposed that this technology development be transferred to NASA space exploration applications. Two areas within the NASA program that would find this technology highly beneficial are (1) probes and landers that must operate in high-temperature environments and (2) ultra-lightweight power electronics for satellite and spacecraft power converter systems.

#### **1. INTRODUCTION**

The past decade has seen an intense and steady increase into the research of the viability of SiC–based device technology. This technology has the potential to improve upon many of the

current limitations associated with silicon electronics, in particular, the limitations of silicon device switching speeds, junction temperatures, and power density.

The team of researchers from APEI and the University of Arkansas specialize in the development of silicon and silicon-carbide power electronics for harsh environment applications, including silicon Systems on a Chip (SoC) DC-DC converters for NASA-JPL, silicon-carbide motor drives for deep Earth geological exploration, and silicon-carbide motor drives for the U.S. Army Future Combat Systems (FCS) hybrid-electric combat vehicle program. The researchers are proposing to map over the developing silicon-carbide power electronics technology to the arena of space electronics and/or solar system exploration. There are two areas within the NASA program that would find this technology highly beneficial.

The first NASA area that would benefit from SiC technology is very specific. It is envisioned that SiC electronics would be of great benefit to probes and landers that must operate in high-temperature environments, such as the Venusian atmosphere. Venus' upper atmosphere is composed of a high concentration of sulfuric acid, and the surface environment exceeds temperatures of 460 °C at 92 bars of pressure. Silicon-carbide electronics could be used to drive small actuators and DC motors required to move robotic arms, spin soil drills, or drive the wheels of a Venus rover. Normal silicon electronics, even in a heavily shielded environment, would fail in a matter of hours under such conditions. This paper will present the idea that it is conceivable that SiC electronics could operate in the surface environment for an extended period of time with *little to no shielding or protection at all*. A lander's electronics composed exclusively of SiC would function days or weeks before failure, instead of hours, thus greatly increasing the scientific data acquisition capability of the overall system.

The second NASA area that could benefit from this technology, required on almost every piece of space hardware ranging from high-power solar array and fuel cell supplies to lowvoltage (3.3 V or 2.5 V) digital electronics, are DC-DC power electronics energy converters. Silicon-carbide power electronics have the potential to bring about enormous cost savings. SiC power switches, with reduced switching losses, would improve the overall electrical efficiency of onboard systems. The ability to operate at high junction temperatures would greatly reduce the size and weight of heatsinking strategies (by as much as an order of magnitude or more). The ability to switch at higher frequencies would result in large reductions in the size of capacitor, inductor, and magnetic components (again, perhaps by as much as an order of magnitude). Implementing these changes in conjunction with a modular (or building block) strategy similar to the U.S. Navy's power electronic building block (PEBB) program, with built in "intelligence," would result in easy-to-build, easily cascadable, power electronics systems with improved reliability and 1/10<sup>th</sup> the size and weight of today's design solutions. Reduction in size and weight means immediate savings in cost to launch, and improving modularity translates to a reduction in complexity, which again results in cost savings.

It is evident from these two applications alone that silicon-carbide electronics not only could map over to NASA functions, but due to NASA's specific and unique requirements, would become an excellent driver for cost savings and improved scientific exploration.

#### **2. SILICON-CARBIDE**

The utilization of discrete high-power SiC devices is set to revolutionize the power electronics industry and bring the benefit of improved efficiency, improved reliability, and reduced costs to the commercial markets. The 2001 European Power Electronics Conference in

9

Graz, Austria, was an unveiling: the world's first commercial SiC power diodes were made available to the private sector [1].

SiC is a wide bandgap semiconductor material capable of high temperature operation (theoretically up to ~600°C) [2]. When compared to silicon-based devices, SiC devices (e.g., Schottky diodes, *pn* diodes, static-induction-transistors, and power MOSFETs) possess a higher breakdown voltage (10 times that of Si), possess lower switching losses, are capable of higher current densities (approximately 3 to 4 times higher than Si or GaAs), and can operate at higher temperatures (approximately 5 times higher than Si) [4]. In short, SiC transistors have the potential to revolutionize the industry of power electronics.

The interests in SiC technology can be traced down to the comparison of the fundamental physics between it and silicon. First, as illustrated in Table I, SiC technology offers an order of magnitude higher breakdown electric field than Si. Higher breakdown electric field allows for thinner and more highly doped devices. Since a SiC device can be made thinner and doped higher, the diffusion length L, and lifetime  $\tau$  are reduced, and faster switching speeds (up to 10s of GHz) can be achieved With a higher electric breakdown field, SiC can surpass the voltage limits reached by Si power electronic devices by an order of magnitude. SiC power devices also have increased switching speeds because saturated electron drift is twice that of Si. Another contributing factor to switching speeds is electron mobility which in SiC is actually less than in Si and is a disadvantage at low voltages. However, the effect of saturated electron drift is dominant over electron mobility in high voltage devices and the overall effect is an increase in switching speeds. Additionally, SiC transistors with faster switching speeds, smaller drive currents, and smaller on resistances will have reduced power losses and increased electrical efficiency over silicon devices.

| Property                                                 | 6H SiC  | 4H SiC   | GaN                 | GaAs    | Si    |

|----------------------------------------------------------|---------|----------|---------------------|---------|-------|

| Energy Bandgap<br>(eV)                                   | 2.9     | 3.26     | 3.39                | 1.43    | 1.12  |

| Electric Field Breakdown<br>(x106 V/cm @ 1kV operation)  | 2.5     | 2.2      | 3.0                 | 0.30    | 0.25  |

| Dielectric Constant                                      | 9.6     | 9.7      | 9.0                 | 12.8    | 11.8  |

| Intrinsic Carrier Concentration,ni<br>(cm-3 @ Room Temp) | 10-6    | 8.2x10-9 | 1.9x10-10           | 2.1x106 | 1010  |

| Electron Mobility, μe<br>(cm2/V·s @ Room Temp)           | 330-400 | 700-980  | 1,000<br>2,000 2DEG | 8,500   | 1,400 |

| Hole Mobility, μh<br>(cm2/V·s @ Room Temp)               | 75      | 120      | 200                 | 400     | 450   |

| Saturated Electron Drift<br>(x107 cm/s @ E >2x105 V/cm)  | 2.0     | 2.0      | 3.0                 | 1.0     | 1.0   |

| CTE<br>(ppm/K)                                           | 4.5     | 5.1      | 4                   | 5.73    | 4.1   |

| Young's Modulus<br>GPa                                   | 400     | 400      | 181                 | 70      | 156   |

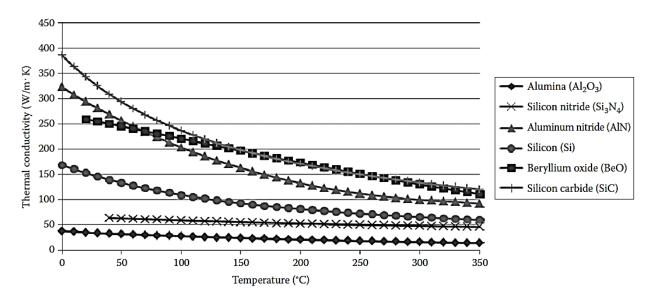

| Thermal Conductivity<br>(W/m K @ Room Temp)              | 490     | 370      | 130                 | 55      | 150   |

| Density<br>(g /cm3)                                      | 3.2     | 3.2      | 6.15                | 5.3     | 2.3   |

Table I. Fundamental properties of various semiconductors [3].

The second major advantage of SiC electronics is their potential to operate in extremely harsh environments, and in particular high-temperature environments, due to the large bandgap. This ability to operate at high temperatures, coupled with the excellent electrical efficiencies, gives SiC the potential to operate at very high power densities not achievable with Si electronics. This ability leads one to the immediate recognition that power electronics would benefit greatly from the implementation of SiC devices. The current commercially available SiC devices are Schottky diodes, and recently SiC MESFETs. SiC PiN diodes, power MOSFETs, gate-turn-on-thyristors (GTOs), and static-induction-transistors (SITs) are all currently under development by research and manufacturing organizations (such as Northrop-Grumman, Infineon, Cree, Army research lab, and Rockwell Scientific), although none of these devices have yet been released into the commercial marketplace. The increasing development of SiC opens up a world of possibilities in electronics design and applications that hitherto have been unthinkable.

## Improving SiC Technology

The first real interest in the use of silicon-carbide as an electronic substrate material dates back to the late 1950s, but it wasn't until the late 1980s and early 1990s that the research area truly began to gain momentum. This was when Nishino and Powell developed the heteroepitaxial growth of SiC crystals on Si substrates. The early and mid 1990s found the introduction of commercial grade SiC wafers of 4H-SiC and 6H-SiC polytypes [5].

The industry, however, is still plagued with unreliable and defective wafers, slowing much of the desired research in SiC device development. The two major reasons for crystal growth difficulties are: (1) conventional melt techniques (such as those used in silicon) cannot be utilized since SiC does not melt under reasonably attainable pressures and temperatures (SiC sublimes at temperatures above 1800 °C), and (2) different polytypes with different electrical characteristics can grow under identical conditions [6]. Current SiC wafers contain high defect densities, the most significant of which are tubular voids referred to as micropipes, which in turn limit the defect-free semiconductor surface area and thus the size of devices.

The current major areas of SiC development can be identified as follows:

1. *SiC wafer and substrate fabrication*—The key dominating issues here are in reducing the physical flaws and defect densities in the wafers (such as tubular voids and micropipes), and increasing wafer sizes for more cost effective fabrication.

2. *SiC physics and device development*—This means developing not only the theoretical design of SiC devices, but also the practical issues associated with layout and manufacturing processes and the building of the devices or ICs. Such issues that need improvement are ohmic contacts and strong dielectric oxide layers. One of the key steps in making discrete devices capable of withstanding high temperature is proper devices passivations.

3. *SiC device modeling*—The ability to develop and validate accurate device models is key in today's world of computer simulations. End users need to be able to simulate their circuit and system designs using device models or they are unlikely to apply the devices themselves.

4. *SiC packaging*—The key here is again high temperature. If the maximum hightemperature solder liquefies at 300 °C, then of what use is a 600 °C electronic device? The package not only has to operate at high temperatures but must be reliable as well if it is to be of any use. Currently, all areas of electronic packaging are highly deficient with regard to hightemperature operation and reliability.

5. *SiC applications*—Currently, the most promising applications are power-electronics systems and drives, RF modules, and simple sensors. The key here is the lack of availability of SiC devices. Without transistors on the commercial market, it is difficult to build and prove the application.

#### SiC Semiconductor Devices

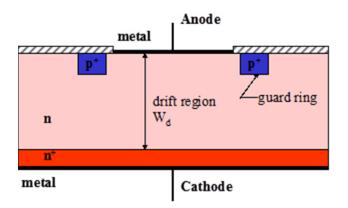

*SiC Diodes*—Recently, silicon-carbide (SiC) power devices have begun to emerge with performance that is superior to that of silicon (Si) power devices. For a given blocking voltage, SiC minority carrier conductivity-modulated devices, such as a PiN diode, show an improvement in switching speed by a factor of 100 as compared to Si, while majority carrier SiC devices show a factor of 100 times less in resistance compared to Si [7]. Prototype devices have already demonstrated improvements over Si technology for devices of various current and voltage ratings. Because power rectifiers are more easily produced than three terminal power devices, they have become the first commercially available SiC power devices. Figure 1 shows the cross section of a SiC Schottky diode. Generally speaking, there are three classes of SiC power rectifiers: (a) Schottky diodes, which offer extremely high switching speeds but suffer from high leakage current; (b) PiN diodes, which offer low leakage current but show reverse recovery charge during switching and have a large junction forward voltage drop due to the wide bandgap of 4H-SiC; and (c) Merged PiN Schottky (MPS) diodes, which offer Schottky-like on-state and switching characteristics, and PiN-like off-state characteristics [8]. It has been shown that a 1500 V SiC MPS diode provides superior performance over Si diodes with voltage ratings of 600 V to 1500 V [9], and that a SiC PiN diode has superior performance compared to Si diodes with voltage ratings from 1200 V to 5000 V [10].

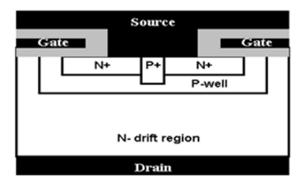

*SiC DiMOSFET*— Until recently, there have been no SiC transistors on the commercial market. These devices however, are under research and development by several manufacturers, including Northrop Grumman, Cree, Infineon, and Rockwell Scientific.

SiC power MOSFETs are expected to have advantages over existing Si technology similar to that of the above-mentioned SiC diodes, and are attractive for implementation as high-voltage, high-speed power devices. Figure 2 shows the simplified cross section of the unit cell structure of a recently introduced experimental 2 kV, 5A SiC DiMOSFET that has fast switching performance [11]. The structure of the DiMOSFET is similar to that of the VDMOSFET used for Si power MOSFETs, in that the p-well and  $n^+$  source regions typical of the VDMOSFET structures still exist in the DiMOSFET structure. The main difference between the two structures is that the DiMOSFET p-well and  $n^+$  source regions are much shallower than those of a Si VDMOSFET due to the lower impurity diffusion coefficients inherent in SiC.

In the on-state region of operation, electrons flow laterally from the  $n^+$  source through the MOSFET channel formed in the implanted p-well and then vertically between adjacent cells and

through the lightly doped drift layer to the drain contact. For a 2 kV Si MOSFET, the drift layer resistance dominates the on-resistance of the device, whereas the specific on-resistance is dominated by the channel resistance for the SiC DiMOSFET structure [11].

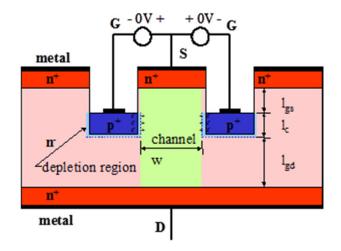

*SiC Static-Induction-Transistor (SIT)*—Power MOSFETs and Insulated Gate Bipolar Transistors (IGBTs) are normally-off devices and require positive voltage signals applied to the gate in order to turn the devices on into their forward conduction modes. On the other hand, SITs are normally-on devices and therefore require the application of a negative voltage signal to the gate in order to turn the device off. Figure 3 illustrates the structure of the SIT.

Figure 1. Cross section of SiC Schottky diode.

Figure 2. Cell structure for a 5 A, 2 kV SiC DiMOSFET

The SIT uses a recessed gate structure, where a large number of the source and gate regions are built up in parallel, thus allowing increased current flow through the device. The uniqueness of the SIT is that it can operate in both unipolar and bipolar modes, giving the user and applications engineer the choice between higher frequencies of operation or higher current sinking capabilities.

Figure 3. Cross- section of SIT structure

When 0 V is applied to  $V_{gs}$  of the device, the device is operating in its normally-on mode. In this mode, the drain and source are shorted through the n-type region. A small depletion region forms between the  $p^+/n^-$  interface, and the channel that forms has a width of the distance between the two depletion regions. When a voltage is applied between the drain and source, electrons flow from source to drain. The electrons are the majority carriers, and in this case, the only mechanism of current flow, and so the SIT is operating in a unipolar mode. The design of the SIT is optimized by minimizing the length of the channel  $l_c$  and the drain-drift region  $l_{gd}$ , while maximizing width and thus minimizing the on-resistance of the device.

As a negative voltage is applied to the gate with respect to the source, the depletion region of the pn-junction begins to grow. As the depletion region grows, the channel width is

reduced and the channel length is increased, thus restricting the flow of current while increasing the on-resistance. When a large enough reverse voltage is applied, the depletion regions grow to such an extent that they meet beneath the source, thus cutting off completely the flow of current.

Operating the SIT in the unipolar mode utilizes a similar control scheme as that developed for power MOSFET devices, since it is a voltage controlled device. The gate signal applied is 0 to  $V_t$  where  $V_t$  is positive for power MOSFETs and negative for SITs.

If more current handling capability is required however, the SIT can be operated in the bipolar mode, which increases power at the cost of complicating the gate drive and reducing switching frequency. This mode of operation can be achieved by applying a positive voltage signal to the gate with respect to the source. In this mode, the gate to source region is forward biased, thus essentially turning on the pn-junction (a diode) into conduction mode between the p<sup>+</sup> and the n<sup>-</sup> regions. This effect injects holes into the main body of the semiconductor and the channel, thus reducing the on-resistance of the device. It is obvious that in order to inject holes from the gate, a significant current capability must be available from the gate source— thus it is no longer simply a voltage control, but also a current control. This greatly complicates possible gate drive schemes.

#### **3.** CURRENT WORK

Researchers at APEI, Inc. and the University of Arkansas have performed extensive research in the area of SiC device applications, packaging, and modeling for power electronic systems. Work reviewed in this section includes device control for SiC SITs, half-bridge SiC SIT power stages, and a 3-phase control board for operation up to 250°C for use with geological exploration and the Army's FCS vehicles. Packaging techniques of high temperature electronics and SiC is overviewed, as well as the modeling of SiC diodes, MOSFETs, and SITs.

# Applications

The potential applications of SiC are widespread and all-encompassing in the area of power electronics. Military and space exploration vehicles are the first major applications that could significantly benefit from this technology. Control electronics and sensors of a jet or rocket engine that could be placed directly on or into the engine would be of great use. Also, a Venus probe could significantly benefit from SiC by being able to reliably perform experiments and collect data without failure soon after landing on the planet's surface. Additionally, the Army is looking for high power density motor drives for their hybrid-electric combat vehicles. Other high-performance applications to benefit would be nuclear power reactors, where sensors could endure the high-temperature and high-radiation environments; or petroleum and geological exploration, where electronics could be sent deep beneath the Earth in high-temperature borewells. Finally, any system that would see improvement from high-density motor drives would benefit from SiC.

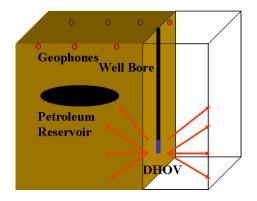

*Energy Exploration SiC Application*—Energy companies are interested in SiC power electronics. Deep Earth exploration encounters hostile environments and extreme temperatures in which it is difficult to place silicon electronics. With SiC, it is possible to send electronics downhole, thereby improving motor drive control and efficiency, increasing exploration and sensors' capabilities, and ultimately aiding in the discovery of previously hidden energy sources (such as large and wide, but shallow petroleum reservoirs).

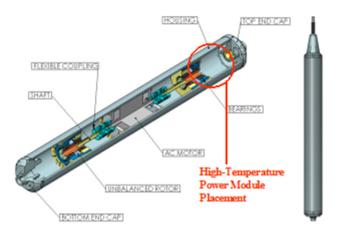

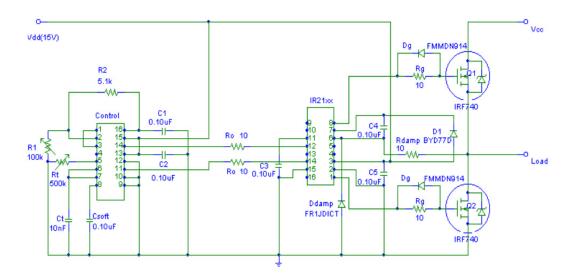

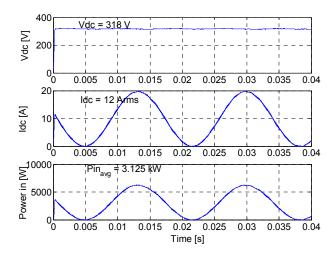

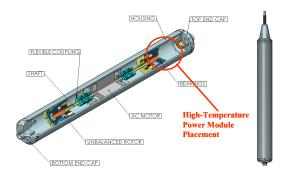

APEI, Inc. is currently working in conjunction with Cole Enterprises on a Down Hole Orbital Vibrator (DHOV) that will integrate a high-temperature motor drive and a 3-phase induction machine for use in geological exploration. The DHOV is currently used in industry but has a few drawbacks. Current technology relegates the control and motor drive electronics to operation on the surface. Developing the high-temperature technology would allow the integration of the electronics with the motor sources for use down-hole. Such a strategy would increase total power delivery capability and would enhance fine motor control (since the control electronics would not be located two miles away on the surface). These improvements would allow for higher accuracy and very fine mapping of the geological layers, thus greatly improving the chances of petroleum discovery. Figure 4 illustrates a 4 hp motor drive design developed by Cole Engineering, Inc. that is currently in production for petroleum industry clients.

Figure 4. Down hole orbital vibrator for use with 3-phase 4 hp induction machine.

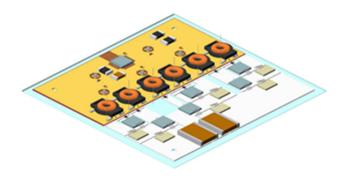

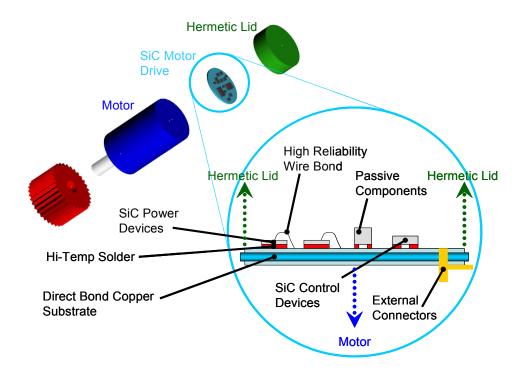

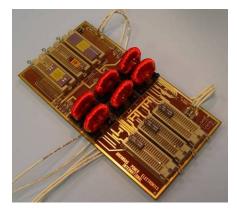

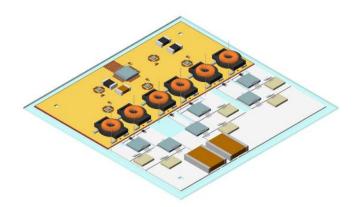

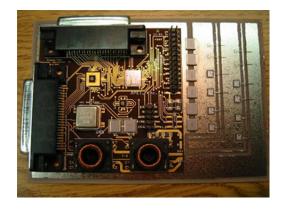

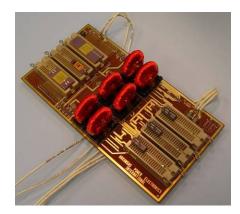

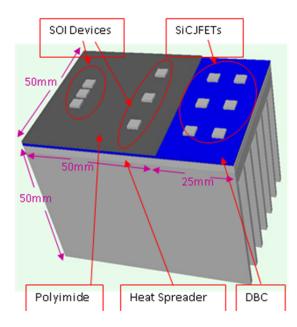

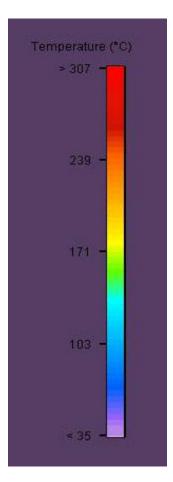

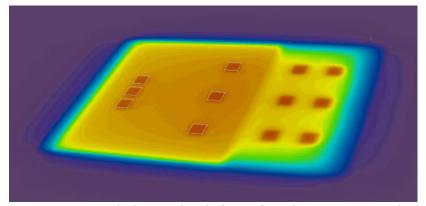

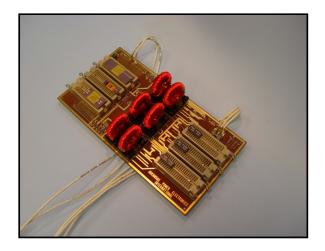

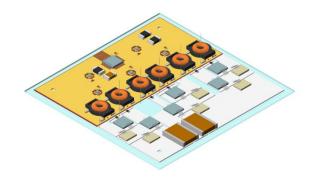

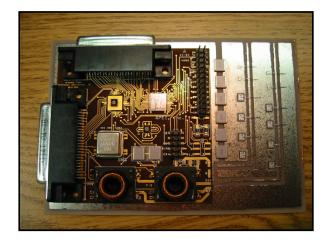

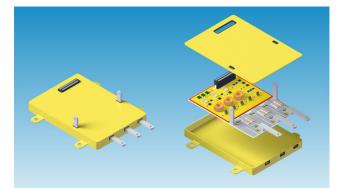

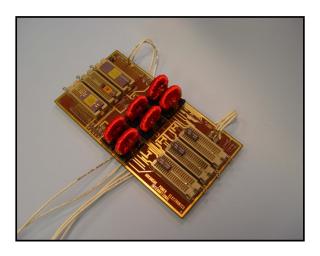

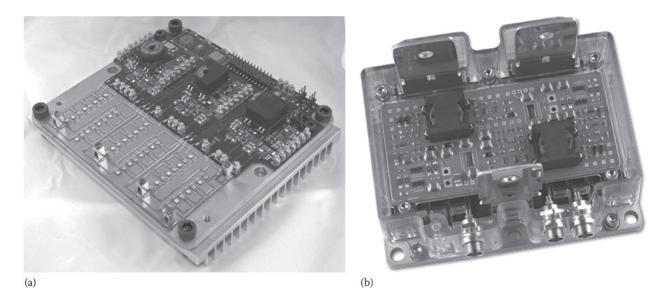

Current work under development by APEI, Inc. consists of miniaturizing the hightemperature control circuitry and combining it with SiC power switches (as shown in Figure 5) for placement inside the cylinder casing of the DHOV. The conceptualized drive would be a 2×2 inch square. Control components in bare die form would be mounted on a multi-layer substrate, such as polyimide or Rogers 4000, bonded on DBC with the power components. This multi-chip power module (MCPM) would miniaturize the 3-phase motor drive required by the DHOV and therefore will enable it to be placed inside the DHOV cylinder.

Figure 5. Miniaturized high-temperature control circuitry for DHOV.

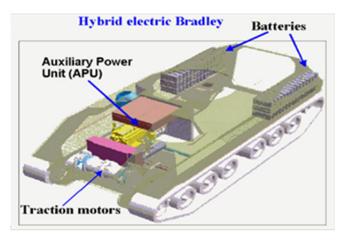

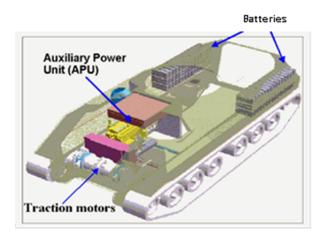

*SiC for military applications*—The U.S. military is interested in SiC power electronics for use in their hybrid-electric combat vehicles, such as the Bradley Fighting Vehicle in Figure 6. These combat vehicles must utilize high-power converters and motor drives that are capable of operating within harsh environmental parameters. Due to their increased thermal abilities and increased power densities, high-temperature motor drives can be integrated onto the motors and bulky heatsinks can be eliminated. This saves both weight and space in the combat vehicle.

Figure 6. Hybrid-electric Bradley combat vehicle.

The researchers have designed, built, and tested control circuitry for use with SiC power switching devices for the specific application to the Army's Future Combat Systems (FCS). The circuitry consists of Honeywell's line of HTMOS high temperature microelectronics with the core of the control circuitry provided by the HT83C51 microcontroller. Honeywell's silicon-on-

insulator (SOI) HTMOS parts are guaranteed to operate at 225 °C for a period of five years and at 300 °C guaranteed for one year. Honeywell's tests have shown that after five years, there is a 99.6% reliability rate on components that have been operating at 225 °C.

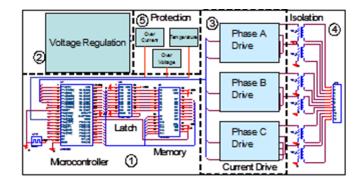

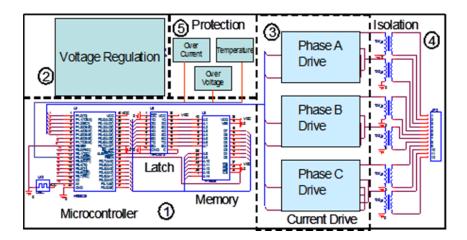

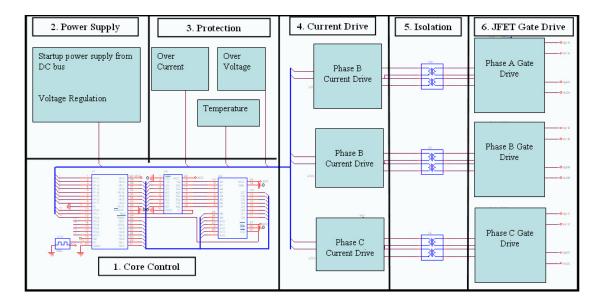

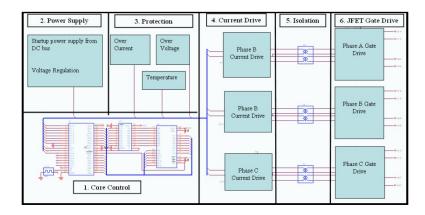

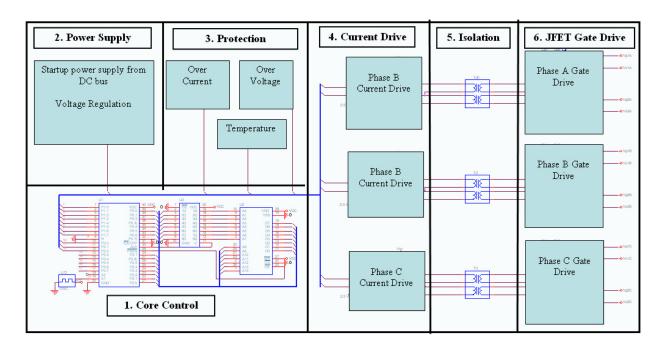

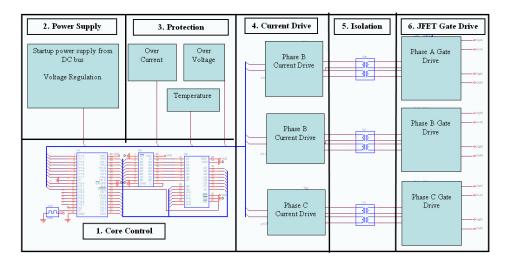

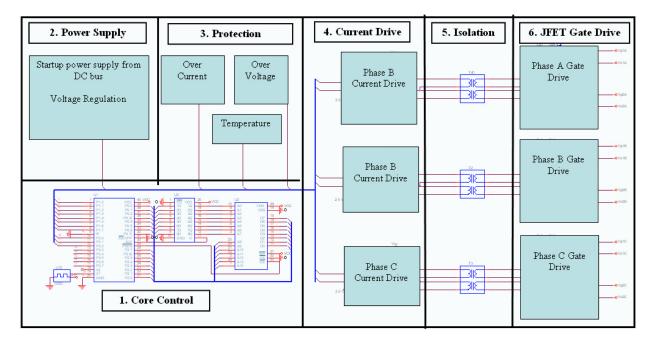

Figure 7. Block diagram of 3-phase controller.

The 3-phase controller consists of five main parts as shown in Figure 7.

(1) The core control consists of Honeywell's HT83C51 8-bit microcontroller. The microcontroller uses external RAM that is loaded with program memory before startup, thus increasing the versatility of the control algorithm.

(2) Next is the voltage supply regulation. Again, the HTMOS line supplies voltage regulators for 5, 10, or 15 V applications with an output current of 300 mA.

(3) Since the microcontroller is not capable of sourcing enough current to drive power devices, a current amplification circuit is implemented through the use of HT1104 operational amplifiers. Depending on what type of power switching device is used, this circuit will vary. A detailed circuit for driving SITs will be outlined later in this section.

(4) The isolation circuit serves three purposes; first to isolate the drive circuitry from noisy distortion caused by power switching, second to provide an increased gate drive capability

by doubling the voltage at its inputs, and third and most importantly, it allows for a floating voltage to be applied to the high-side power switch gates.

(5) Included with the control is protection from potential catastrophic failures such as over voltage, over current, and over temperature.

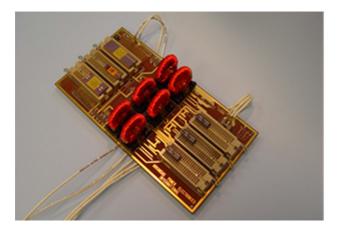

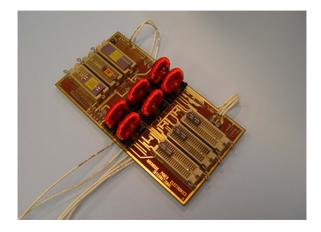

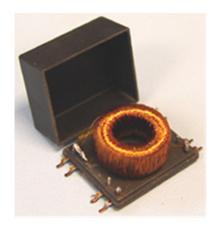

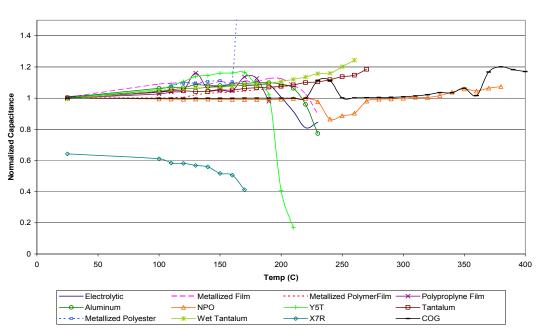

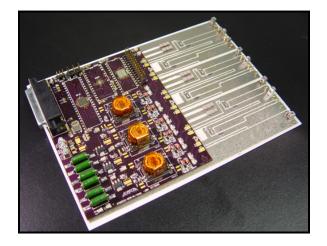

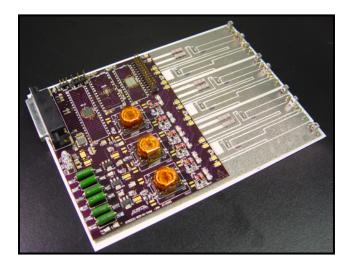

In order to complete the high-temperature prototype version of the control circuitry shown in Figure 8, passive components, such as capacitors, resistors, IC sockets, printed circuit boards (PCBs), and various other devices proper temperature ratings were utilized. Magnetic wire and high-temperature Magnesil toroidal core materials were utilized in the hand wound isolation transformers. High temperature burn-in zero insertion force (ZIF) sockets were used for all ICs in order to facilitate prototype testing and changes. High-temperature solders were obtained through Indalloy, and the high-temperature ICs were purchased from Honeywell.

Figure 8. 250 °C 3-phase motor control prototype.

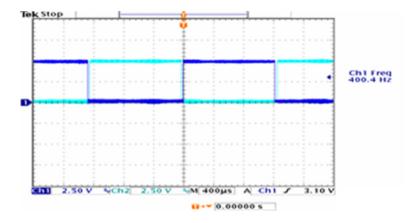

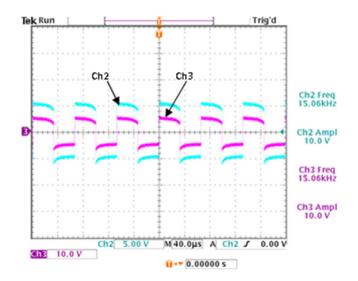

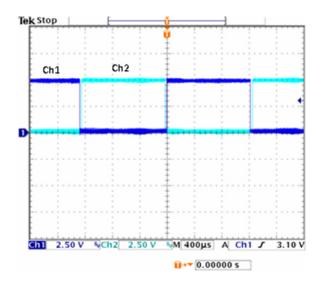

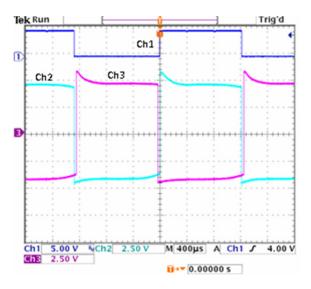

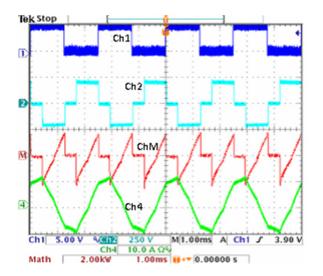

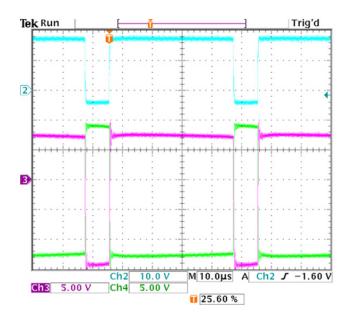

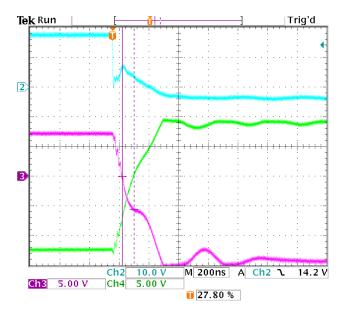

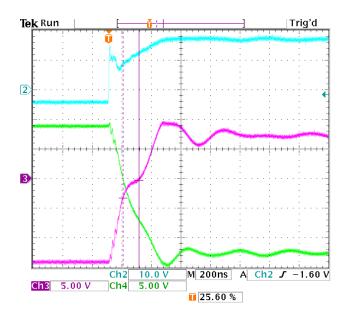

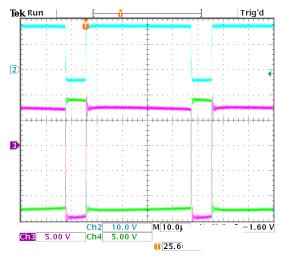

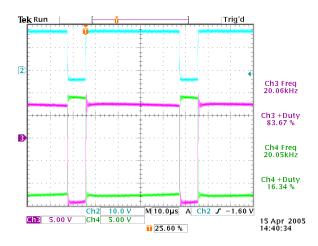

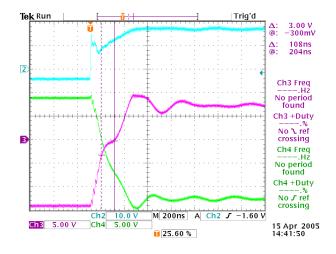

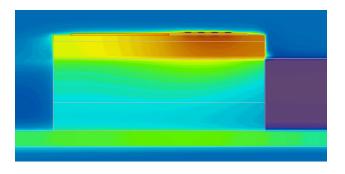

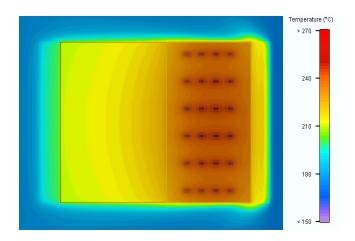

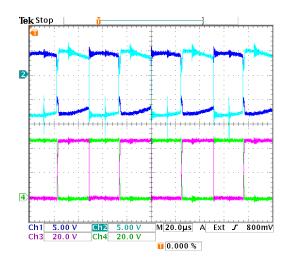

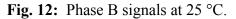

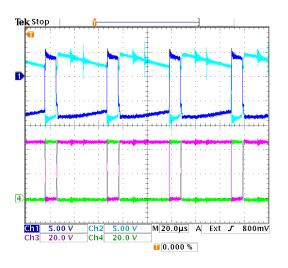

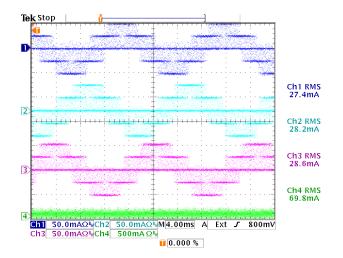

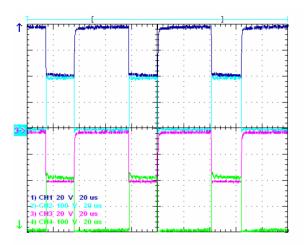

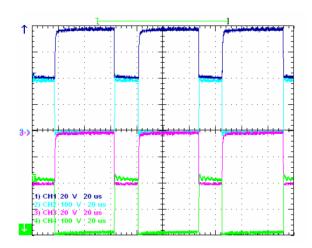

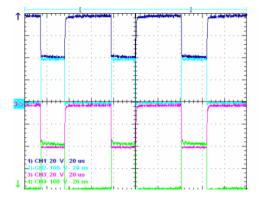

High-temperature testing of the control circuitry was completed and proven to drive a 3phase 4 hp induction machine under load. Figure 9 shows the control output of a single phase from the HT83C51 operating at 250 °C (Ch1 high side Ch2 low side). Additionally, Figure 10 is the gate drive signal output from the isolation transformers operating at 250 °C with Ch1 as the microcontroller output, and Ch2 and Ch3 as the high and low side respectively.

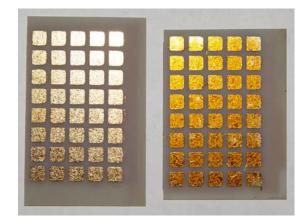

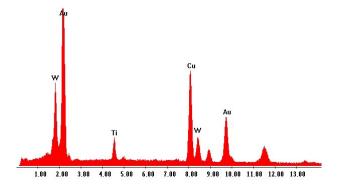

The authors are also working with Northrop-Grumman to verify certain device electrical switching characteristics, to develop high-temperature technology for SIT packaging, and most importantly, to verify full SIT operation in an industry (as opposed to military) viable application. The authors built a SiC SIT power stage on an aluminum-nitride direct bond copper substrate (nickel plated) [12]. The devices were mounted with a high-temperature Indalloy solder. Figure 11 illustrates a photograph of the SIT half-bridge 200 watt power stage.

Tek Stop Ch1 Freq 400.5 Hz Low signal amplitude Ch1 Freq 400.5 Hz Low signal amplitude Ch1 Freq 400.5 Hz Low signal amplitude

**Figure 9.** Output of HT83C51 operating at 250 °C

Figure 10. Output of transformers operating at 250 °C.

Figure 11. SiC SIT half-bridge.

Figure 12. SiC SIT half-bridge control circuitry.

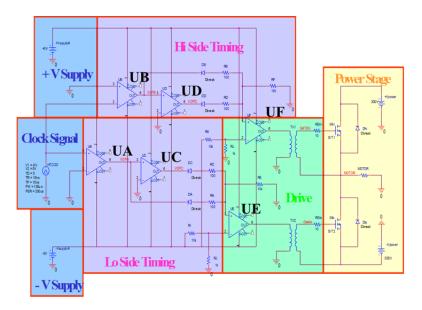

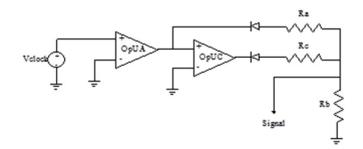

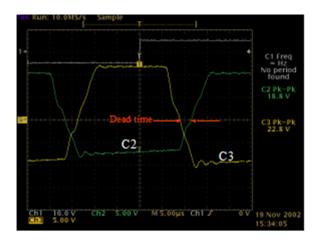

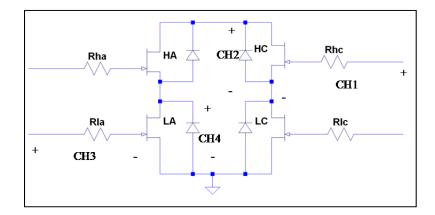

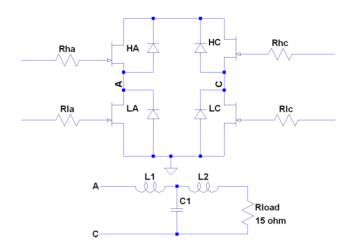

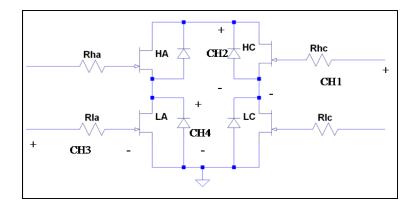

The drive circuit for the SiC SIT half-bridge was designed using Honeywell's HT1104 op-amps, and Cree SiC PiN diodes. The power half-bridge is composed of a high side and low side transistor, the gates of which are driven by respectively inverting control signals. In addition to the inversion, deadtime is required so both half-bridge power switches are off simultaneously for a short period of time.

Referring to Figure 12, the generated clock signal controls the ultimate timing of the pulse drive signal delivered to the high and low side transistor gates. The positive and negative voltage supplies are generated by high-temperature voltage regulators (Honeywell HTNREG and HTPREG).

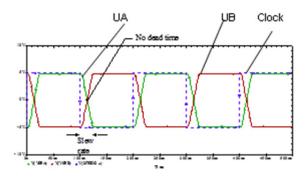

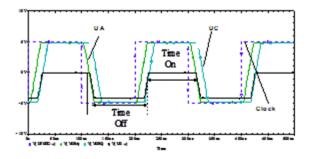

Initially, the clock signal is fed in parallel to op-amps UA and UB (low side and high side timing, respectively). Op-amp UB is set up as a rail-to-rail inverter thus inverting the clock signal, while Op-amp UA is simply a delay to keep the two signals timed together. These signals are illustrated in Figure 13. It is important to note that even though the signals are inverted, there is no deadtime present in the control.

The next step is then to insert the appropriate deadtime. For this purpose, the output of op-amp UA is fed into op-amp UC, and the output of op-amp UB is fed into op-amp UD (where UC and UD simply act as delays). The key to creating deadtime is in determining a method to AND the two signals (UA and UC for low-side) together. Ideally, this is shown in Figure 14. It is apparent that the off-time exceeds the on-time, and so when this function is carried out for the high-side signal as well as the low-side signal, there is a time period when both signals are off.

Figure 15 illustrates the circuit design developed by the researchers to achieve a mathematical AND. The resistors Ra, Rc (where Ra=Rc) and Rb (Rb=100·Ra) form a voltage divider and control the flow of current. The diodes utilized are Cree SiC bare die PiN diodes. Three cases for this circuit can arise.

(1) UA and UC outputs are both -5 V signals. In this case, current flows from ground to the op-amp output nodes of -5 V. Since Rb>>Ra, Rc, the majority of the voltage drop occurs across the Rb resistor, thus making the circuit output "signal"  $\approx -5$  V (off).

(2) UA and UC outputs are both +5 V signals. In this case, the two diodes block the flow of current from the +5 V nodes to ground. Since no current is flowing, the output "signal" is essentially grounded and is thus set to 0 V. It is important to remember that since the SITs are normally on devices; 0 V is an on-signal.

(3) One op-amp output is +5 V while the other is -5 V. In this case, the op-amp outputting the +5 V signal can be ignored, since the diode is blocking its current drive. The op-amp with the -5 V output is the controlling element, and current flows from ground to the -5 V node. Since Rb>>Ra or Rc, the majority of the voltage drop occurs across the Rb resistor, thus making the circuit output "signal"  $\approx -5$  V (off).

Due to the nature of the function of the timing circuit illustrated in Figure 15, the output "signal" is essentially a voltage signal with almost no current drive capability. Even though the SITs are operating as voltage-controlled devices, they still require some current drive to overcome the gate capacitance and switch them on. Due to this requirement, the low-side and high-side signals from op-amps UC and UD are fed into another set of op-amps, UE and UF respectively, of Figure 11's "drive" block. This inserts a current drive capability into the control signals (and returns the control to a +5 V to -5 V signal).

Figure 13. UA (green), UB (red), and clock (dashed) signals.

Figure 14. UA (green), UC (cyan), and clock (dashed) signals.

Figure 15. Mathematical AND circuit.

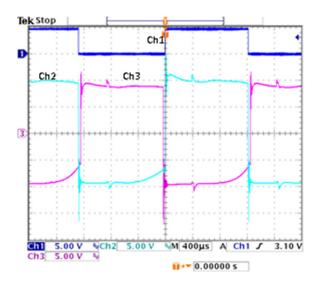

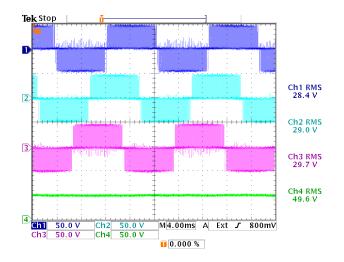

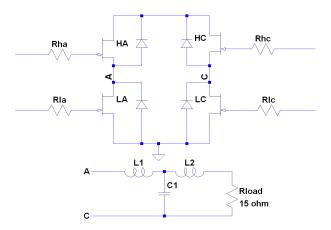

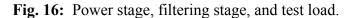

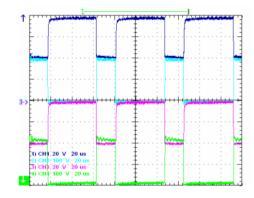

The signals are then fed to drive the isolation pulse transformers. Figure 16 illustrates the captured waveforms of the half-bridge gate drive signals generated by the control circuit, low (Ch2) and high (Ch3).

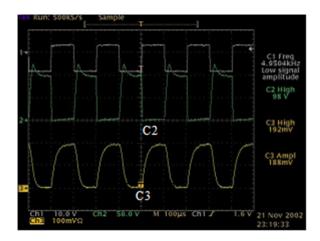

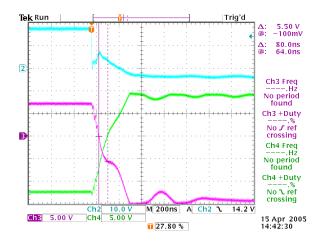

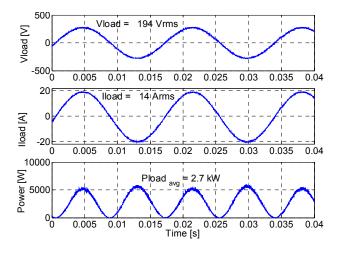

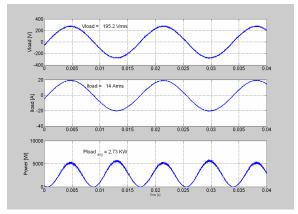

Figure 17 illustrates the captured waveforms of the SIT half-bridge operating at 200 watts. The Ch2 waveform is the high-side 100 V signal, and the Ch3 waveform is the hi-side 2 A signal (×10 current probe).

The results of the high temperature control circuit along with those of the SiC SIT based half-bridge prove that SiC devices can be driven at elevated temperatures and could therefore be integrated into industrial, military, and space applications. The next vital step to making these applications possible are to reduce size through specialized packaging techniques such as MCPMs.

# Packaging

As SiC power devices are introduced into the commercial market, there are a number of factors that will limit their full potential use, the most prominent of which is the issue of high-temperature packaging. The full utilization of the advantages of SiC power devices would mean operating them at their *peak power densities*, i.e., operating at power levels that would bring the

semiconductor junction temperature to 600 °C. A high-temperature power package is vitally needed that will be capable of achieving this.

Silicon-carbide power Schottky diodes have just recently entered the commercial market. Currently they are offered only in discrete packages with the identical environmental operational capability as those used to house silicon devices. SiC technology is a new medium, and so the current focus is upon utilizing the 10× improved electrical efficiencies associated with SiC over silicon (thus standard packages are currently being used). Little research has yet been devoted towards the development of high-temperature packages that will be capable of taking advantage of the 10× power density capabilities of the devices. This technology development will be vital for power electronics miniaturization and volume/weight reduction.

Figure 16. Gate drive control signals at 20 kHz.

Figure 17. High-side voltage and current signals.

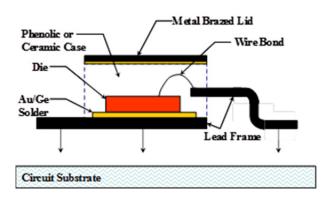

Figure 18. Schottky package cross-section

Figure 18 illustrates the cross section of a package design strategy under investigation by APEI, Inc. In this strategy, the case and baseplate lead frame are integrated and molded in a high-temperature Phenolic plastic (Phenolic is rated to over 400 °C and is used for transformer header electrical mounts) or ceramic. The bare-die SiC power device is mounted to a metal lead-frame via a very high-temperature solder such as 88Au-12Ge. The device is wire bonded to the lead post and a metal lid is brazed to the case. Packaging for SiC devices includes the investigation of high-temperature wire bonding, high-temperature die attach methods, and thermal stress analysis of the entire package. Additionally, advancements in the miniaturization of power electronic systems are seen through the use of multichip power modules (MCPM).

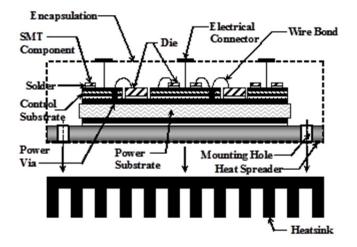

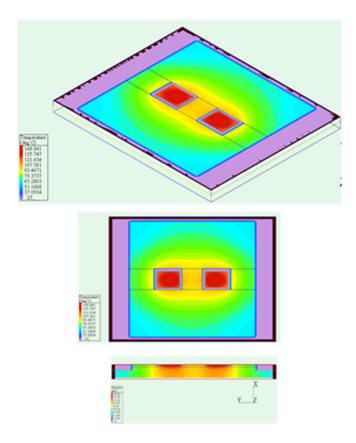

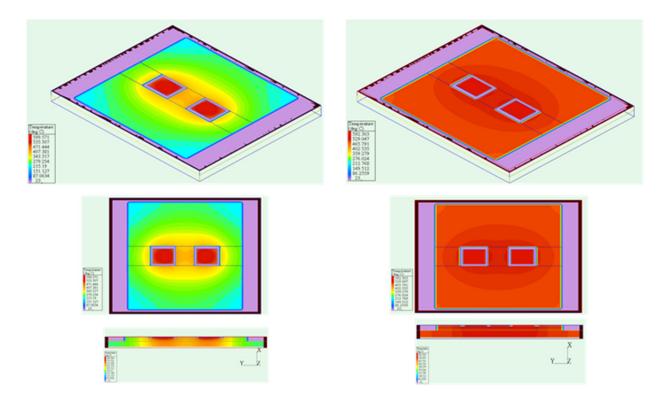

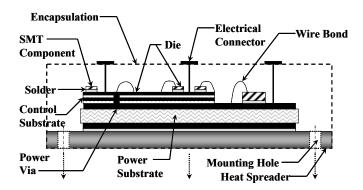

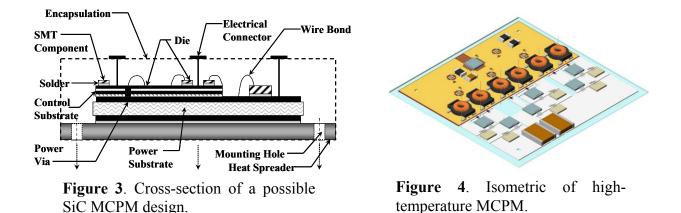

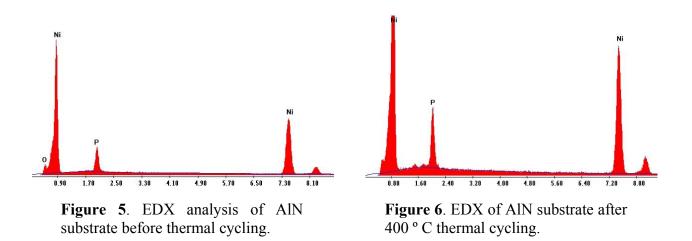

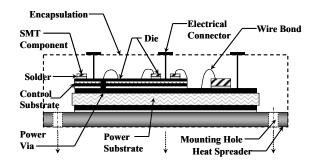

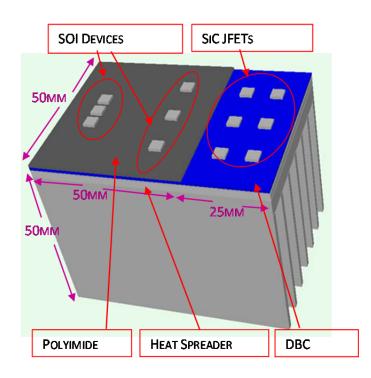

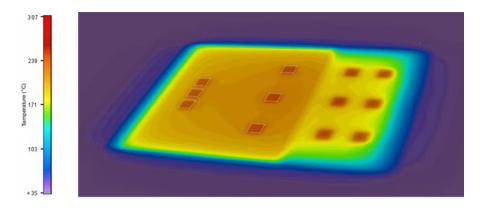

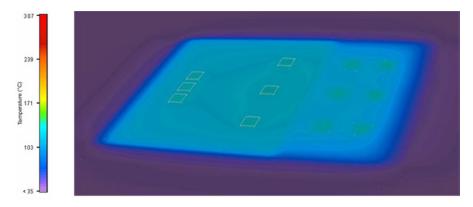

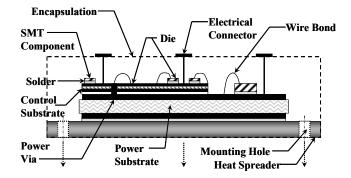

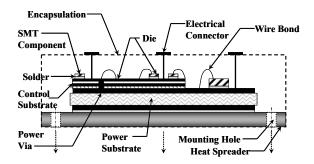

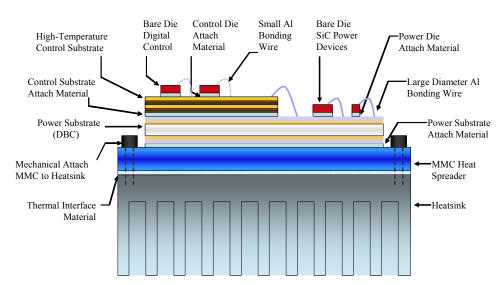

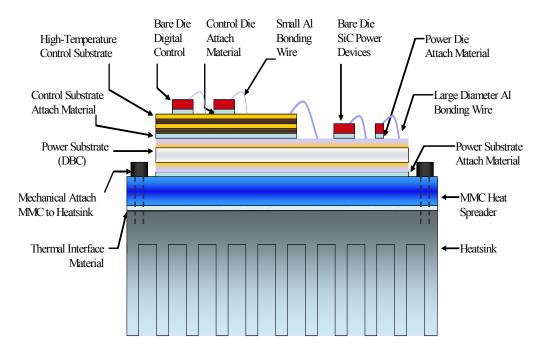

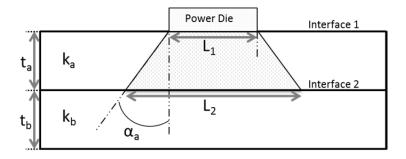

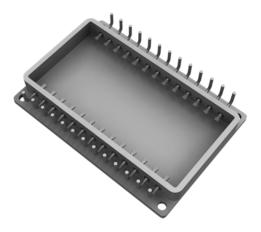

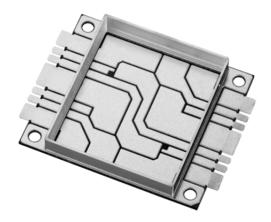

Since SiC devices are capable of operating into the GHz range, they offer a great reduction in the size of passive components such as capacitors, inductors, and other magnetic components. Integrating control and power layers into a single module would significantly reduce size, weight, and parasitic effects. This approach is a multichip power module in which multiple layers would be utilized to separate the power and control circuitry, as illustrated in Figure 19. The power module is built upon a metal-matrix-composite heatspreader, for which the material content has been specifically engineered to reduce the stresses of thermal expansion within the MCPM. A high-power substrate layer, such as direct-bond-copper (DBC), is utilized for its high current-carrying capability and significant thermal dissipation properties [14, 15]. The high-power SiC devices are mounted on this layer. High-temperature polyimide materials or LTCCs are utilized as the control layers, which are laminated upon the power layer. The control circuitry is gold plated in order to reduce oxidation and improve reliability, the control devices are then mounted on the top surface of the control layer, and electrical connections made between layers by vias.

It is clear that the use of SiC can reduce the size and weight of many circuits through the advantage of higher switching frequencies and through the use of advanced packaging techniques. Once a device has a suitable package, they can be characterized and models can be created for use in simulator tools.

### Modeling

In order for circuit designers to fully utilize the advantages of the new SiC power device technologies, compact models are needed in circuit and system simulation tools. SiC power device models with extracted parameter sets will be provided in circuit simulator libraries and will be used to provide insight into the performance advantages of SiC power diodes.

30

Figure 19. High-temp. SiC DC-DC converter design.

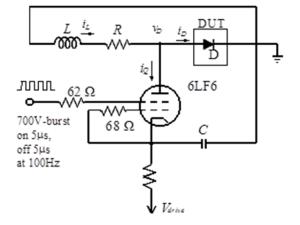

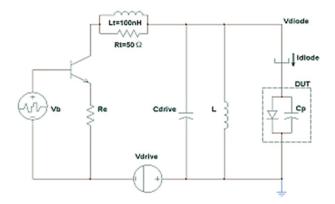

SiC diode model—The UA and the National Institute of Standards and Technology (NIST) researchers worked in collaboration to develop a SiC Schottky diode model. A novel high-speed reverse recovery test system developed at NIST was utilized for device characterization, and later for model validation. This test circuit is shown in Figure 20(a) and its equivalent circuit simulator model is shown in Figure 20(b). Figure 20(a) shows the test circuit used for characterizing the diodes for reverse recovery, and Figure 20(b) shows the behavioral representation including parasitic elements used for diode model validation. It is important to note that the test circuit in Figure 20(a) is well characterized, meaning that the values of all circuit components and parasitic elements are known. In order to operate the test circuit in Figure 20(a), first the vacuum tube is turned on to establish the test current  $i_L$  in the inductor L. Once the test current is reached, the tube is ramped off and the inductor current is commutated to the Device Under Test (DUT). To initiate the reverse recovery test, the tube is ramped on with a well controlled  $di_Q/dt$  at the tube anode. This results in a negative  $di_D/dt$  being applied to the DUT. As

the diode begins to recover, the diode voltage  $v_D$  rises toward the power supply voltage  $V_{drive}$  completing the recovery test.

The reverse recovery tests are performed for various values of forward diode current  $i_D$ , diode reverse bias power supply voltage  $V_{drive}$ ,  $di_D/dt$ , and  $dv_D/dt$ , where  $dv_D/dt$  is controlled by

Figure 20(a). High-speed diode reverse recovery test setup.

Figure 20(b). Equivalent behavioral circuit emulating test setup.

placing various driver capacitors across the DUT. By independently controlling  $V_{drive}$ ,  $di_D/dt$ ,  $dv_D/dt$ , and the forward diode current at turnoff, the new test circuit enables testing of the new SiC technology for the full range of conditions that occur for various application conditions. Varying the value of  $V_{drive}$  emulates the application conditions for circuits with different DC bus voltages, varying the value of  $di_D/dt$  emulates the application conditions of different speed anti-

parallel switching devices, and varying the value of  $dv_D/dt$  emulates the application conditions of using anti-parallel switching devices of different output capacitance. Also, varying the value of dv/dt aids in the determination of the portion of the diode recovery due to charge storage and the portion due to device capacitance. Varying the value of the forward diode current at turnoff aids in the determination of the portion of current that is due to emitter recombination and the portion that contributes to charge storage.

Results from this research were used to accurately model a new class of power devices, (PiN, Schottky, and MPS diodes with voltage ratings from 600 V to 10 kV and current ratings from 0.25 A to 20 A) and develop a parameter extraction sequence to enable the characterization of any SiC power diode. Parameters extracted from an MPS SiC diode are shown in Table II.

The SiC MPS diodes studied were designed such that the PiN diode does not turn on in normal forward bias operation. This type of operation is typically referred to as the junctionbarrier-controlled-Schottky (JBS) diode mode. The PN junctions serve only to shield the Schottky barrier from high electric fields, thus preventing Schottky barrier lowering and reducing leakage current.

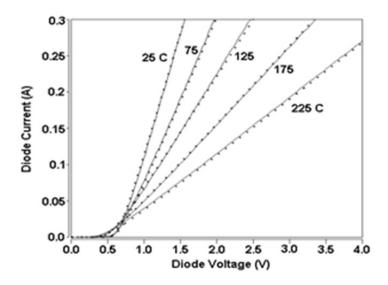

Figure 21 shows the simulated (dashed) and measured (solid) on-state characteristics for the 1500 V, 0.5 A (0.0045 cm<sup>2</sup>) SiC MPS diode for different temperatures in the range of 25 °C to 225 °C. In these curves, the built-in potential decreases with increasing temperature because the increasing thermal energy of electrons in the metal voltage. The decrease in slope of the onstate voltage curves with increasing temperature is indicative of the reduction of mobility with temperature for a majority carrier device.

Figure 22 shows the measured (solid) and simulated (dashed) reverse recovery waveforms of the MPS diode for three different di/dt values and no external driver capacitance.

33

In these figures, the initial measured forward current is 0.6 A and the diode is switched by applying a constant negative di/dt with the tube.

| Parameter | Parameter Name                                 | 0.5 A MPS    |

|-----------|------------------------------------------------|--------------|

| EG        | Bandgap / Barrier Height                       | 1.6          |

| VJ        | Built-in junction potential                    | 1.2          |

| CJO       | Zero-bias junction capacitance                 | 30p          |

| М         | P-N grading coefficient                        | 0.5          |

| FC        | Forward-bias depletion capacitance coefficient | 0.5          |

| RS        | Forward series contact resistance              | 2.85         |

| ISR       | Low-level recombination saturation current     | 4.26 · 10-13 |

| NR        | Low-level recombination emission coefficient   | 1            |

| XTIR      | ISR temperature exponent                       | 11.1         |

| NTR       | ISR thermal multiplication factor              | 2.1          |

| TRS1      | Linear RS temperature coefficient              | 1.45m        |

| TRS2      | Quadratic RS temperature coefficient           | 46.7µ        |

| GAMMA     | RS temperature exponent                        | 2.93         |

Table II. SiC MPS diode model parameters [16].

**Figure 21**. Simulated (dashed) and measured (solid) on-state characteristics for the 1500 V, 0.5A SiC MPS diode [16].

*SiC MOSFET Model*—The model used for the SiC MOSFET is based upon the latest version of the power MOSFET formulation utilized in the Hefner IGBT model [17]. The model has been enhanced by adding the temperature-dependent material properties of 3C-, 4H-, and 6H-SiC, which can be selected using the material-type parameter switch. The model contains features that have been shown to be important to describe the dynamic performance of vertical power MOSFETs including the two-phase nonlinear gate-drain overlap capacitance, negative gate voltage inversion of the gate-drain overlap, and nonlinear body-drain depletion capacitance. The MOSFET channel current expressions used in the model are unique in that they include (1) the channel regions at the corners of the square or hexagonal cells that turn on at lower gate voltages and (2) the enhanced linear region transconductance due to diffusion in the nonuniformly doped channel.

**Figure 22.** Measured (solid) and simulated (dashed) reverse recovery waveforms of the 1500 V SiC MPS diode for three different di/dt values and no external driver capacitance [16].

Recently, a software package called IGBT Model Parameter ExtrACtion Tools (IMPACT) was introduced to automate laboratory instrument control and parameter determination for IGBTs [18]. To extend IMPACT to be applicable to SiC power MOSFETs, a material-type switch was added to select and calculate the temperature-dependent properties of the material. for power MOSFETs, the IMPACT package reduces to three programs that extract the power MOSFET model parameters. These programs are SATMSR, which measures the saturation current versus gate voltage; LINMSR, which measures the linear region on-state voltage versus gate voltage for a constant drain current; and CAPMSR, which measures gate and gate-drain charge characteristics. The extraction sequence is performed over an applicable temperature range to extract the temperature coefficients of the model parameters.

The MOSFET model is used to describe the performance of a 2 kV, 5 A 4H-SiC Double implanted MOSFET (DiMOSFET) and to perform a detailed comparison with the performance of a widely used 400 V, 5 A Si Vertical Double-Diffused MOSFET (VDMOSFET). To do this, the model parameters are extracted for each device at several temperatures using the extraction sequence, Table III show the model parameters extracted at 25 °C. Figures 23 and 24 show the simulated and measured output characteristics for the 2 kV SiC and 400 V Si MOSFETs at 25 °C and 100 °C. The on-state resistance at 25 °C is similar between the Si and SiC MOSFETs, although the SiC device requires twice the gate drive voltage. Comparing the SiC and Si on-state curves, the Si curves are linear in the on-state region and have a pronounced change in curvature as the saturation or pinch-off region is approached.

The SiC curves, on the other hand, gradually transition from the linear region to the saturation region. In SiC MOSFETs, the epitaxial layer resistance is much smaller and the channel resistance is higher, thus making the MOSFET channel a more significant contributor to

the on-state voltage. This is due to the low channel surface mobility of SiC compared to Si. Because the SiC curves have less resistance in series with the MOSFET channel, the enhanced linear region transconductance model of [17] is essential for these devices. Furthermore, because the transconductance is much smaller for SiC, the on-state voltage is closer to the pinch-off voltage, and the model for the transition region is more important. At 100 °C, the Si device has a severe reduction in conduction capability, whereas the SiC on-resistance is only minimally affected. This occurs because the drift region resistance is a smaller portion of the on-state resistance in the SiC device and because the channel mobility does not decrease with temperature for the SiC device. In the SiC MOSFET, the channel mobility increases with temperature as more interface traps become occupied with the larger concentration of electrons available for conduction, whereas the bulk mobility decreases with temperature as carrier scattering dominates [19]. The resulting effect is an increase in channel conductance and an increase in the drift layer series resistance.

The results for the widely used 400 V, 5 A Si power VDMOSFET and a new 2 kV, 5 A SiC power DiMOSFET demonstrate good agreement between the model and experiment [7]. The IMPACT parameter extraction tools were extended to be applicable to the power MOSFET model parameter extraction sequence and the SiC material parameters. The new model provides insights into the SiC MOSFET performance and provides the capability to simulate the performance of the new technology in different circuit applications.

| Parameter                 |                   | er Si                        | SiC                                                                                                            |  |

|---------------------------|-------------------|------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| A                         |                   | $0.1 \ cm^2$                 | $0.06 \ cm^2$                                                                                                  |  |

| $W_b$                     |                   | 50 µm                        | 20 µm                                                                                                          |  |

| NĎ                        |                   | $3.1 \circ 10^{14}  cm^{-1}$ | $3 \circ 10^{15}  cm^{-3}$                                                                                     |  |

| $V_T$                     |                   | 3                            | 5.77 V                                                                                                         |  |

| $K_p$                     |                   | 3.4 V                        | $0.33 \ A/V^2$                                                                                                 |  |

| $\theta$                  |                   | $3.3 A/V^2$                  | $0.03 V^{-1}$                                                                                                  |  |

| $K_f$                     |                   | 0                            | 2                                                                                                              |  |

| $R_s$                     |                   | 1.7                          | $0.03 \Omega$                                                                                                  |  |

| K <sub>s</sub><br>Kfl     |                   | $0.02 \ \Omega$              | 0.07                                                                                                           |  |

| $dV_{tl}$                 |                   | 0.02 $32$                    | 2.5 V                                                                                                          |  |

| $P_{vf}$                  |                   | 0<br>0 V                     | 0.95                                                                                                           |  |

| $V_{Td}$                  |                   | 0.7                          | 0.95<br>0 V                                                                                                    |  |

| $A_{gd}$                  |                   | 3.4 V                        | $0.03 \ cm^2$                                                                                                  |  |

| $C_{gs}$                  |                   | $0.075 \ cm^2$               | 2.68 nF                                                                                                        |  |

| $C_{gs}$<br>$C_{oxd}$     | ,                 | 1.114 nF                     | 2.18 nF                                                                                                        |  |

| $V_{biga}$                |                   | 2.066 nF                     | 2.10 m <sup>2</sup><br>2.8 V                                                                                   |  |

| $F_{xjbe}$                |                   | 0.6 V                        | 0.5                                                                                                            |  |

| $F_{xjbi}$                |                   | 0.5                          | 0.75                                                                                                           |  |

| 1 xjbi                    | n                 | 0.5                          | 0.75                                                                                                           |  |

|                           | 10.0 <sub>T</sub> | Silicon Carbide 25C          |                                                                                                                |  |

|                           |                   | Model Vg=15 V                |                                                                                                                |  |

|                           | 8.0 -             | - Experiment                 | 13                                                                                                             |  |

| (A)                       | 6.0 -             |                              |                                                                                                                |  |

| Drain Current (A)         | 0.01              |                              |                                                                                                                |  |

| ain C                     | 4.0 -             |                              | 11                                                                                                             |  |

| ð                         |                   |                              |                                                                                                                |  |

|                           | 2.0 -             |                              | 9                                                                                                              |  |

|                           | 0.0               |                              |                                                                                                                |  |

|                           | 0                 | 0 2.0 4.0 6.0                | 8.0 10.0                                                                                                       |  |

| Drain Voltage (V)         |                   |                              |                                                                                                                |  |

| 10.0 1/07 - 0 - 1/1/ 1000 |                   |                              |                                                                                                                |  |

|                           | 10.0              | Silicon Carbide 100C         | 13                                                                                                             |  |

|                           | 8.0               | - Experiment Vg=15 V         | All and a second se |  |

| ŝ                         |                   |                              | 11                                                                                                             |  |

| Drain Current (A)         | 6.0 -             |                              |                                                                                                                |  |

| n<br>U                    | 4.0 -             |                              |                                                                                                                |  |

| Drai                      |                   |                              | 9                                                                                                              |  |

|                           |                   |                              |                                                                                                                |  |

**TABLE III.** Model parameters at 25 °C [7]

Figure 23. Silicon-carbide MOSFET simulated (dashed) and measured (solid) output characteristics as a function of gate voltage for (a) 25 °C and (b) 100 °C [7].

4.0 6.0 Drain Voltage (V)

2.0

0.0

0.0

2.0

10.0

8.0

**Figure 24**. Silicon MOSFET simulated (dashed) and measured (solid) output characteristics as a function of gate voltage for (a) 25 °C and (b) 100 °C [7].

# 4. MAPPING TO NASA APPLICATIONS

NASA is potentially interested in SiC power converters for in-situ probes and landers for harsh environments, or satellite and spacecraft applications to drive low-voltage digital and analog electronics from high-voltage power sources (such as the DC solar arrays). The advantage to NASA of an increased operational temperature range for spacecraft applications is the reduction of required heatsinks and heat exchangers, which are bulky, heavy components within the overall systems. Additionally, the increase in switching frequencies reduces the size of passive components and therefore the size of any DC-DC converter. This reduction would result directly in the saving of critical weight (along with its accompanying exorbitant launch costs).

# SiC for Harsh Environment Applications

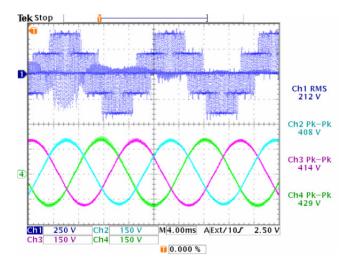

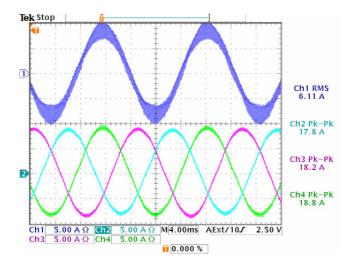

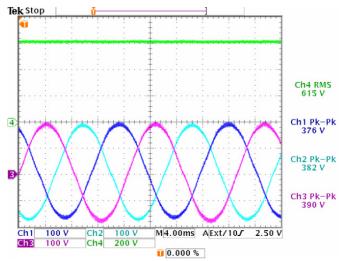

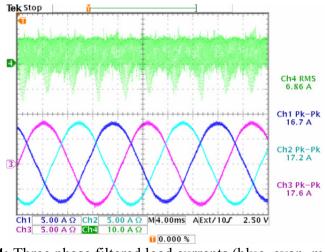

The atmosphere of Venus is one of the most extreme environments one could possibly hope to penetrate, survive, and explore. The atmosphere is corrosive with high concentrations of sulfuric acid cloud formations, and at the surface altitude, the average surface temperature is 464 °C at a pressure of 92 atmospheres. The chemical composition of the near-surface atmosphere is composed of 96.5% carbon dioxide, 3.5% nitrogen, and trace amounts of sulfur dioxide (150 ppm), argon (70 ppm), water (20 ppm), carbon monoxide (17 ppm), helium (12 ppm), and neon (7 ppm) [20]. Thus the main survivability and operational reliability factors for in-situ probes and landers are (1) electronics operation at ambient temperatures in excess of 464 °C, (2) hermetic electronic packages capable of withstanding 92 atmospheres of pressure in an environment at 464 °C, (3) hermetic packages capable of maintaining reliable integrity within the chemical composition environments described above, and (4) mechanical-electrical systems such as DC motors and actuators that are able to reliably operate in the above conditions.