#### Santa Clara University **Scholar Commons**

Engineering Ph.D. Theses

Student Scholarship

3-21-2017

# Supernode Transformation On Parallel Systems With Distributed Memory – An Analytical Approach

Yong Chen Santa Clara University

Follow this and additional works at: http://scholarcommons.scu.edu/eng phd theses

Part of the Computer Engineering Commons

#### Recommended Citation

Chen, Yong, "Supernode Transformation On Parallel Systems With Distributed Memory - An Analytical Approach" (2017). Engineering Ph.D. Theses. 8.

http://scholarcommons.scu.edu/eng\_phd\_theses/8

This Dissertation is brought to you for free and open access by the Student Scholarship at Scholar Commons. It has been accepted for inclusion in Engineering Ph.D. Theses by an authorized administrator of Scholar Commons. For more information, please contact rscroggin@scu.edu.

# Santa Clara University

Department of Computer Engineering

Date: March 21, 2017

I HEREBY RECOMMEND THAT THE THESIS PREPARED UNDER MY SUPERVISION BY

#### Yong Chen

**ENTITLED**

# Supernode Transformation On Parallel Systems With Distributed Memory

- An Analytical Approach

BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

OF

DOCTOR OF PHILOSOPHY IN COMPUTER ENGINEERING

Thesis Advisor

Chairman of Department

Thesis Reader

Thesis Reader

Thesis Reader

Thesis Reader

# **Supernode Transformation On Parallel Systems With Distributed Memory**

- An Analytical Approach

By

Yong Chen

#### **Dissertation**

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Computer Engineering in the School of Engineering at Santa Clara University, 2017

Santa Clara, California

# Acknowledgements

This dissertation, and my entire Ph.D. study, could have not been completed without the tremendous support from my family. The continued encouragement from my wife and my parents made the completion of my study possible.

Dr. Shang, my advisor, has been patiently providing suggestions, direction and guidance for my study.

Countless discussions, reviews ensured the progress of my study and the publication of the papers.

My doctoral committee members, Dr. Amer, Dr. Fang, Dr. Figueira, Dr. Tran, provided invaluable feedback that helped improve my study greatly.

# Supernode Transformation On Parallel Systems With Distributed Memory

#### - An Analytical Approach

Yong Chen

Department of Computer Engineering Santa Clara University Santa Clara, California 2017

#### **ABSTRACT**

Supernode transformation, or tiling, is a technique that partitions algorithms to improve data locality and parallelism by balancing computation and inter-processor communication costs to achieve shortest execution or running time. It groups multiple iterations of nested loops into supernodes to be assigned to processors for processing in parallel. A supernode transformation can be described by supernode size and shape. This research focuses on supernode transformation on multi-processor architectures with distributed memory, including computer cluster systems and General Purpose Graphic Processing Units (GPGPUs). The research involves supernode scheduling, supernode mapping to processors, and the finding of the optimal supernode size, for achieving the

shortest total running time. The algorithms considered are two nested loops with regular data dependencies. The Longest Common Subsequence problem is used as an illustration. A novel mathematical model for the total running time is established as a function of the supernode size, algorithm parameters such as the problem size and the data dependence, the computation time of each loop iteration, architecture parameters such as the number of processors, and the communication cost. The optimal supernode size is derived from this closed form model. The model and the optimal supernode size provide better results than previous researches and are verified by simulations on multi-processor systems including computer cluster systems and GPGPUs.

# TABLE OF CONTENTS

| 1. | INTRODUCTION                                                               | 4  |

|----|----------------------------------------------------------------------------|----|

| 2. | RELATED WORK                                                               | 7  |

| 2  | 2.1 SUPERNODE SCHEDULING, SIZE AND SHAPE                                   | 8  |

| 2  | 2.2 THE POLYHEDRAL MODEL AND AFFINE TRANSFORMATION                         | 10 |

| 2  | 2.3 SCHEDULING WITH FIXED PROCESSORS                                       | 11 |

| 2  | 2.4 Focus of This Research                                                 | 14 |

| 3. | MODELS AND TERMINOLOGY                                                     | 15 |

| 3  | 3.1 Algorithm Model                                                        | 15 |

| 3  | 3.2 Architecture Models                                                    | 17 |

|    | 3.2.1 Computer Cluster Systems                                             | 18 |

|    | 3.2.2 GPGPUs                                                               | 18 |

| 3  | 3.3 Linear Scheduling                                                      |    |

|    | 3.3.1 Example of the LCS problem scheduling on GPGPU                       |    |

| 3  | 3.4 Supernode transformation on multi-processor system with $P$ processors | 22 |

| 4. | TOTAL EXECUTION TIME WITH SUPERNODE TRANSFORMATION                         | 27 |

| 5. | SUPERNODE TRANSFORMATION ON COMPUTER CLUSTERS                              | 32 |

| 5  | 5.1 LEMMAS AND THEOREM                                                     |    |

|    | 5.1.1 Lemma A1                                                             | 33 |

|    | 5.1.2 Lemma A2                                                             | 34 |

|    | 5.1.3 Lemma A3                                                             | 34 |

|    | 5.1.4 Theorem                                                              | 35 |

| 5  | 5.2 Simulation                                                             | 35 |

| 6. | SUPERNODE TRANSFORMATION ON GPGPUS                                         | 40 |

|    | 6.1 Analytical Results                                                     |    |

| 6  | 6.2 LEMMAS AND THEOREM                                                     | 44 |

|    | 6.2.1 Lemma B1                                                             | 45 |

|    | 6.2.2 Lemma B2                                                             | 46 |

|    | 6.2.3 Lemma B3                                                             | 46 |

|    | 6.2.4 Theorem                                                              |    |

| 6  | 6.3 SIMULATION RESULTS                                                     |    |

| 6  | 6.4 Result Analysis                                                        |    |

| 6  | 6.5 The Selection of GPGUP Architecture Model Parameter $P$                | 52 |

| 7. | CONCLUSION                                                                 | 54 |

| 8. | FUTURE WORK                                                                | 55 |

| 9. | APPENDIX                                                                   | 56 |

|    | 9.1 Appendix A: Lemmas For Supernode Transformation On Cluster Systems     |    |

| -  | 9.1.1 Lemma A1                                                             |    |

|    | 9.1.2 Lemma A2                                                             |    |

|    | 9.1.3 Lemma A3                                                             |    |

| Ç  | 9.2 APPENDIX B: LEMMAS FOR SUPERNODE TRANSFORMATION ON GPGPUS              |    |

| 9.2.1 Lemma B1                                                              | 62  |

|-----------------------------------------------------------------------------|-----|

| 9.2.2 Lemma B2                                                              | 65  |

| 9.2.3 Lemma B3                                                              | 66  |

| 9.3 APPENDIX C: SOURCE CODE OF SUPERNODE TRANSFORMATION ON COMPUTER CLUSTER |     |

| Systems                                                                     | 68  |

| 9.3.1 Code Running on the Master Computer                                   | 68  |

| 9.3.2 Code Running on the Computing Nodes                                   |     |

| 9.3.3 Include File                                                          |     |

| 9.4 APPENDIX D: CODE ON GPGPUS                                              | 99  |

| 10. REFERENCES                                                              | 124 |

# List of Figures

| Figure 1: A Uniform Dependence Algorithm.                                              |    |

|----------------------------------------------------------------------------------------|----|

| Figure 2: Column-wise cyclic distribution of rectangular tiles on limited processors.  |    |

| Figure 3: A typical GPGPU memory hierarchy.                                            | 20 |

| Figure 4: The ten wavefronts of the linear schedule vector [1,1].                      | 21 |

| Figure 5: Two dimensional uniform dependence algorithm iteration space.                | 24 |

| Figure 6: Iteration space after supernode transformation.                              | 25 |

| Figure 7: Total execution times for different values of (m,n) on cluster.              | 38 |

| Figure 8: A LCS Supernode of size $w \times h$ and its dependent nodes.                | 42 |

| Figure 9: Total execution times of the LCS problem on GPGPU.                           | 49 |

| Figure 10: On a cluster system, the total execution time for a two-dimensional uniform |    |

| dependence algorithm $T$ is convex.                                                    | 58 |

#### 1. Introduction

Supernode partitioning, or tiling, is a transformation technique that groups a number of iterations in a nested loop in order to improve data locality and parallelism, thus ultimately improving execution performance on multi-processor systems. This paper addresses the problem of applying supernode transformation on multi-processor systems with distributed memory, including computer clustering system and the General Purpose Graphic Processing Units (GPGPUs), especially on finding the optimal supernode size to minimize the total running time.

In a parallel system with multiple processors, the total running time consists of two parts: the computation time and the communication time. An algorithm can be partitioned into supernodes or tiles where each supernode is assigned to one processor for parallel execution. If the supernode is too small (or too large), the communication time (or computation time) will dominate and the total running time is not minimized due to non-optimal data locality and parallelism. Finding the optimal supernode size to achieve optimized locality to minimize the total running time is critical in supernode transformation.

The algorithms considered in this paper are nested loops with regular data dependencies or uniform dependencies [5]. Such an algorithm can be described by its iteration index space consisting of all iteration index vectors of the loop nest, and a dependence matrix, consisting of all uniform dependence vectors as its columns. The Longest Common Subsequence Problem, the LCS problem [2], which has found wide applications, such as in bioinformatics or in computer science, is used to illustrate how to use supernode transformations to minimize the total running time.

The multi-processor architectures considered in this paper are computer cluster systems and the GPGPUs. A computer cluster consists of a set of loosely or tightly connected computers that work together to form a single computational unit. The computers of a cluster are usually connected to each other through fast local area networks. The clusters are formed to improve performance and availability over that of a single computer while still being much more cost-effective than single computers.

Another important computer architecture considered is the GPGPU system. Inside each GPGPU, there are multiple streaming multi-processors (SMs), each SM contains multiple cores for concurrent operations and these cores share a cache on the same chip. Then the SMs are connected at high level and share a global memory of a much larger size but with a much slower access speed.

The basic approach in this paper is as follows. Given an algorithm with two nested loops and a multi-processor distributed memory architecture with a fixed number of processors or GPGPU SMs, model for the total running time is established. This total running time is expressed as a function of the supernode size, algorithm parameters, such as the problem size and data dependence, the computation time of each loop iteration, architecture parameters, such as the number of processors/GPGPU SMs, and the communication cost. This estimated expression of the total running time is a convex function with two variables. By working on the derivatives, the optimal supernode size can be estimated.

The contributions of this research are as follow. For algorithms with two nested loops and regular dependences, a novel mathematical model for the total running time on multi-processor distributed memory systems is established, the model is closed form by

dividing solution space into three sub spaces. The total running time is expressed as a function of the supernode size, algorithm parameters such as the problem size and data dependence, the computation time of each loop iteration, architecture parameters such as the number of the computing nodes in cluster system, or the number of GPGPU blocks, and the communication cost. The optimal supernode size is obtained based on this model. This optimal supernode size leads to significant performance improvement than without using optimal supernode size, due to optimized locality, it leads to much better results than previous research.

The rest of this research report is organized as following. Section 2 summarizes the related work that has been done in the area of supernode transformation. Section 3 presents the algorithm and architecture models. Section 4 shows how the mathematical models of total running time for supernode transformation are established. Section 5 discusses how to obtain the optimal supernode size for the cluster system. Section 6 presents analytical and simulation results for the GPGPU architecture. Section 8 provides future work direction and section 9 contains additional information as appendix.

#### 2. Related Work

Irigoin and Troilet [4] proposed the supernode partitioning technique for multiprocessors in 1988 as a new restructuring method. The idea was to combine multiple loop iterations of perfectly nested DO loops in order to provide vector statements, parallel tasks, and data reference locality. They first defined hyperplane partitioning, then generalized it to partitioning with multiple hyperplanes. They gave conditions for valid partitioning, and other reasonable constraints on supernodes to ensure the supernodes were: 1) atomic, each tile is a unit of computation, all synchronization points are beginnings and ends of tiles; 2) identical, this is to allow for automatic code generation; 3) bounded, the number of points inside a tile to be bounded by a constant independent of the domain size. They only briefly discussed the choice of parameters of supernode partitioning. They noted that supercomputer architectures were too intricate to derive analytical expression for the partitioned program execution time. They listed a number of possible optimization goals, noting that these goals were often conflicting.

Since then, researchers have studied supernode transformation in different contexts. The research has been mostly focused on the model of the supernode transformation and how to use the model to construct the optimal supernode transformation. In general, supernode transformations can be described by the size, the shape and the relative ratio of the sides of each supernode. The communication cost can be modeled either as a constant where the start-up time dominates or as a linear function of the message size. To construct an optimal supernode transformation for a general algorithm with any convex index set, any dependence structure, and a general architecture is difficult or sometimes impossible. So researchers tried special cases. Also, the optimal solution is quite different

for the case where the number of processor cores is unlimited and the case where that number is given and fixed. Following paragraphs summarize the research development in supernode transformation.

#### 2.1 Supernode Scheduling, Size and Shape

Scheduling is one of the challenging problems in the parallel computing, hence lots of research on it. But even without supernode transformation, finding the optimal scheduling is hard. Sinharoy and Szymanski in [9] presented efficient algorithms for finding the optimum wavefront and for partitioning the optimum wavefront into sections to be assigned to arbitrary large array of processors. Their algorithms can be used for one or higher dimensional processor arrays. But these algorithms are complex even for a two-dimension array computation.

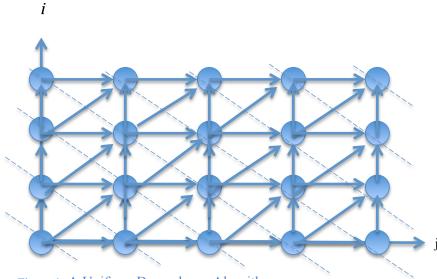

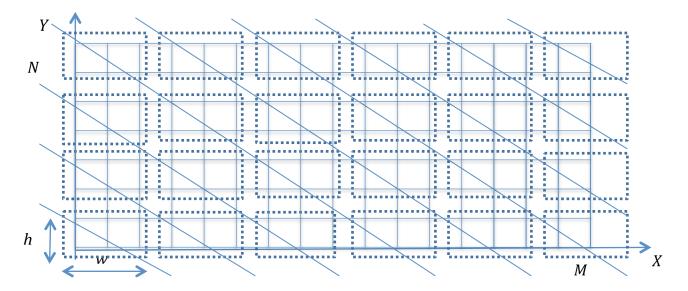

Shang and Fortes in [5] addressed the problem of identifying optimal linear schedules for uniform dependence algorithms to minimize their execution time. An algorithm can be thought of as a set of indexed computations. A uniform dependence algorithm is defined as an algorithm whose dependence vectors are uniform, where the data dependence vector is the difference of indexes where a variable is used and where that variable is generated. Figure 1 shows an example of a two-dimensional uniform dependence algorithm where each node is an indexed computation, the dependence vector is  $D = \begin{pmatrix} 1 & 1 & 0 \\ 0 & 1 & 1 \end{pmatrix}$ , the dashed lines are wavefronts on which computations are

independent of each other. They proposed procedures to find optimal linear schedules based on the mathematical solution of a nonlinear optimization problem.

Figure 1: A Uniform Dependence Algorithm

Hodzic and Shang in [1,11] presented an execution of tiles for uniform dependence algorithms using linear scheduling under the condition of largely enough processors available, where each processor executes all tiles along a specific dimension, with non-overlapping communication and computation phases. They discussed optimal supernode size and shape with a few interesting findings. First, they found the optimal supernode size is the ratio of the communication cost over the computation cost of one iteration of the original loop. Secondly, the supernode shape is a function of the cone spanned by all dependence vectors. Thirdly, the ratio of the lengths of supernode sides should be such that the index set after the supernode transformation should have equal side lengths. Based on their method, the optimal supernode transformation can be found for n dimensional algorithms with any number of dependence vectors.

In [27] Goumas et al. tried to improve the overall execution time of nested FOR-loops by using a modified linear scheduling, and by mitigating communication overhead by efficiently overlapping the communication and computation phases. They used Direct Memory Access (DMA) engines and network interfaces (NICs) that can work in parallel with the CPUs.

While Goumas's method applied to a cluster of single CPUs, Athanasaki et al. in [14] extended it to a cluster of symmetric multiprocessors (SMP nodes). They grouped together neighboring tiles along a hyperplane and these tiles are concurrently executed by the CPUs of the same SMP node, taking advantage of the fact that there is no need for tile synchronization and communication between intra-node CPUs.

#### 2.2 The Polyhedral model and Affine Transformation

The Polyhedral Model is a mathematical framework for affine loop nest analysis and optimization [30,31,32]. It treats an instance of a statement in the loop as an integer point or lattice point in the space called polyhedron. The affine transformations on polytope, based on Linear Algebra and Integer Linear Programming, cause a sequence of complex loop transformations aiming for the improvements such as parallelism and data locality. Supernode transformation or tiling, as one of the key transformations, fits in this model well: it improves data locality by grouping points in the iteration space into supernodes that can be loaded in cache of processors for easy and fast reuse. It also improves parallelism by partitioning the iteration space into independent supernodes that are executed concurrently and atomically on processors, thus reducing communication. In

[37,38], Lim et al. proposed an algorithm to find the optimal affine partition that maximizes the degree of parallelism with the minimum communication in programs with arbitrary loop nests and affine data accesses, and used this algorithm for blocking to improve data locality. In [39] Ahmed et al. presented an approach for synthesizing transformations to enhance locality in imperfectly nested loop via affine embedding functions. In [33] Bondhugula et al. presented an end-to-end automatic integer linear optimization framework that finds good ways of supernode transformation in polyhedral model for parallelism and locality using affine transformations. The key part is to create an affine form cost function that represents the number of hyperplanes the dependence traverses along the hyperplane normal. This cost function is a measurement of reuse distance and also the communication cost if the hyperplane is used to generate supernodes for parallelization and used as a processor space dimension. By minimizing this cost function, they found supernode (or tiling) hyperplanes that not only minimize reuse distances and improve data locality, but also minimize communication volume thus improving parallelism.

#### 2.3 Scheduling with Fixed Processors

While many researches assumed unlimited number of processors or SMP nodes available [1,11,14], this assumption does not hold true in practice. The servers nowadays have fixed or limited number of cores, GPGPUs have limited number of SMs. For this reason, researchers studied supernode transformation with fixed processors.

Ohta et al. in [26] discussed the tile scheduling with limited number of physical

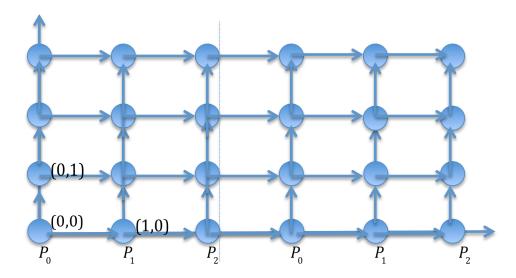

processors. When there are P processors available and interconnected as a ring, a computation domain of two-dimensional rectangle of size  $M \times N$  can be partitioned into rectangular  $w \times h$  tiles with tiles' edges parallel to the axes, when the dependence vector after the tile transformation is  $\begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}$ , the best mapping of tiles is as follows: tiles are assigned via column-wise cyclic distribution, that is, tile (i, j) is allocated to processor  $j \mod P$ . The execution starts with processor  $P_0$  at tile (0,0), after the computation, the result is sent to the adjacent processor  $P_1$ , then concurrently  $P_0$  computes tile (0,1) and  $P_1$  computes tile (1,0), and this process continues, until  $P_0$  finishes all the tiles on column 0, then it moves to column P and continues computation. The column-wise processor assignment is shown in Figure 2.

Based on this scheduling and mapping, Ohta et al. further derived the optimal tile size as follows, assuming non-overlapping computation and communication phases:

$$(w,h) = (\frac{M}{P}, \sqrt{\frac{Na}{Mt}}), \ T_{opt} = (\sqrt{N(\frac{Mt}{P} + b)} + \sqrt{aP})^2$$

(1)

where P denotes number of processors, t denotes the computation time per iteration, and a is the communication startup time and b being the coefficient of message size, linear to h.

Apparently, the cyclic column-wise assignment makes sense due to its load-balancing tile distribution. In [15], Calland et al. demonstrated cyclic column-wise assignment is the best solutions among all possible distributions of tiles to physical processors for a two-dimensional computation domain, with the condition that the computation cost of a tile is greater than its communication cost. They further improved the scheduling and

execution time by overlapping communication and computation phases.

Figure 2: Column-wise cyclic distribution of rectangular tiles on limited physical processors. Assuming P=3. Processor  $P_0$  finishes column 0, then moves to column 3.

But the cyclic column-wise assignment not only has the restriction that the computation cost of a tile needs be greater than its communication cost, it also does not provide the best solution in case of heterogeneous computing platforms. Boulet et al. in [17] handled this problem by aiming at load-balancing the work while not introducing idle time. They presented efficient scheduling and mapping strategies that are asymptotically optimal.

In [16] Athanasaki et al. further proposed four different methods for scheduling tiled iteration spaces onto a clustered system with a fixed number of SMP nodes, namingly the cyclic, the mirror, the cluster and the retiling scheduling.

#### 2.4 Focus of This Research

The cyclic column-wise allocation of processors is regarded as the best scheduling solution when there are limited processors, due to its load-balancing nature. But as mentioned earlier, it has one restriction: the computation cost of a supernode has to be greater than its communication cost. This may not always be true since CPU performance has been increasing dramatically, especially with the advent of GPGPUs, which has very powerful computing capability, the computation and communication ratio may become very small. Let's take a look at a hypothetical case: assume a computation domain of  $M \times N = 60 \times 60$ , available processors P = 6. Let a = 400, b = 0 and t = 1 in (1). Then based on (1), the optimal  $(w,h) = (\frac{M}{P}, \sqrt{\frac{Na}{Mt}}) = (10,20)$ , and  $T_{opt} = (\sqrt{N(\frac{Mt}{P} + b)} + \sqrt{aP})^2 = 5400$ .

But if the scheduling is wavefront-wise, and if (w,h) = (12,20), the domain size becomes  $5 \times 3$  after transformation. Giving that the longest wavefront is 3, each wavefront can be processed within one  $T_{tile}$  since there are more processors than supernodes on any wavefront, note  $T_{tile} = T_{comp} + T_{comm}$ ,  $T_{comp} = wht$ ,  $T_{comm} = a + bh$ . The total execution time  $T = \text{total_num_of_wavefronts} \times T_{tile} = (5+3-1)*(12*20*1+400)=4480$ . This result is less and better than the  $T_{opt} = 5400$  obtained via cyclic column-wise scheduling. The reason for this better result is the enhanced data locality.

The goal of this research is to apply supernode transformation and linear scheduling to multi-processor system architectures, including computer cluster systems and GPGPUs, to find the optimal solution that is suitable no matter what the communication and computation ratio is. The research work involves following areas: linear scheduling, tiles to computing nodes or GPGPU blocks mapping, total running time model, optimal supernode size, applied algorithms, cluster system and GPGPU architectures and simulations. The objective of this research is to minimize the total running time. The total running time consists of communication time between supernodes and computation time within supernodes, representing parallelism and data locality respectively. By obtaining the time optimal solution, we not only improve the data locality and parallelism, but also optimize locality for an optimal balance between data locality and parallelism thus achieving optimal result.

### 3. Models and Terminology

Models for applications or algorithms, parallel computer systems and the mapping from the application to the target parallel system are presented in this section. Some concepts and terms that are necessary to understand this paper are introduced. An example is presented to illustrate different concepts and ideas throughout the paper.

## 3.1 Algorithm Model

An algorithm is modeled as a set of indexed computations, and a set of data dependence. An indexed computation corresponds to a loop iteration in the algorithm. The *dimension of the algorithm s* corresponds to the number of the nested loops in the algorithm. A data dependence is established if one computation uses data generated by another computation, and is represented by a dependence vector that is the difference of two indexes of the computations. In this paper, only algorithms with regular dependence are considered, and such algorithms are called *uniform dependence algorithms* where the dependence vectors are constant. Uniform dependence algorithms can be described by two parameters (J,D): J is the set of all iteration index vectors, D is a matrix of  $s \times q$  for a s dimensional algorithm with s dependences, and each column is a dependence vector. Detailed description of uniform dependence algorithms can be found in [5]

The two-sequence LCS problem is used to illustrate the algorithm model and is defined as following [2]: given two input sequences:  $X = (x_1, x_2 ... x_M)$  and  $Y = (y_1, y_2 ... y_N)$  with M and N being the sizes of each sequence, the LCS problem is to find the length of the longest common sequence, denoted as  $LCS(X_M, Y_N)$ . For example, LCS("ABCBDAB","BDCABA") = 4 where the longest common subsequence is underlined. A LCS recursion is presented below where  $LCS(X_i, Y_j)$  is the length of the longest common subsequence of two sub sequences  $X_1, ... X_i$  and  $Y_1, ... Y_j$ .

$$LCS(X_{i}, Y_{j}) = \begin{cases} 0 & \text{if } i = 0 \text{ or } j = 0 \\ LCS(X_{i-1}, Y_{j-1}) + 1 & \text{if } x_{i} = y_{j} \\ \max(LCS(X_{i}, Y_{j-1}), LCS(X_{i-1}, Y_{j})) & \text{if } x_{i} \neq y_{j} \end{cases}$$

A dynamic programming algorithm calculating LCS from [10] is shown in (2). This algorithm has two nested loops. Therefore, the LCS algorithm is two dimensional or s=2. Each index vector is a two dimensional vector  $\begin{bmatrix} i \\ j \end{bmatrix}$  corresponding to an iteration

$$(i,j)$$

and  $J = \left\{ \begin{bmatrix} i \\ j \end{bmatrix}, 1 \le i \le M, 1 \le j \le N \right\}$ . There are three data dependence vectors in the

LCS and  $D = \begin{pmatrix} 1 & 1 & 0 \\ 0 & 1 & 1 \end{pmatrix}$  where each column represents one dependence vector. The

dependence graph is shown in Figure 1 where each point represents an iteration and an arrow represents a data dependence between two iterations of the algorithm in (2). Because the LCS has uniform dependence, the dependence graph is regular. The execution time to process each iteration (i,j) is denoted as  $t_c$ . Thus the LCS is modeled by parameters  $(J,D,M,N,t_c)$ .

for

$$(i=0; i \le M; i++)$$

for  $(j=0; j \le N; j++)$ {

$if (i==0||j==0)$

$c[i][j]=0;$

$else if (x[i]==y[j])$

$c[i][j]=c[i-1][j-1]+1;$

$else$

$c[i][j]=max(c[i][j-1],c[i-1][j]);$

}

#### 3.2 Architecture Models

In this research, two important multi-processor distributed memory computer architectures are considered, they are cluster systems and the GPGPUs.

#### 3.2.1 Computer Cluster Systems

First, computer cluster architecture is considered. In a computer cluster system, there are two types of computers: a master computer and computing computers (also called computing nodes). The master computer breaks the algorithm into small tasks and sends them to computing nodes to process in parallel. The master computer manages the cluster and coordinates computing nodes such as synchronization due to dependence considerations.

The number of the computing nodes is modeled as the number of processors, denoted as P, the communication time a computing node takes to receive dependent data from other computing nodes is denoted as  $t_r$ , and the time a computing node takes to send resultant data to other nodes is denoted as  $t_s$ . Therefore, a computer cluster system is modeled by parameters  $(P, t_r, t_s)$ .

#### 3.2.2 GPGPUs

Another architecture considered is GPGPUs. GPGPUs employ Single Instruction, Multiple Thread (SIMT) parallel execution model, where multiple independent threads execute concurrently using a single instruction, this provides excellent concurrent processing capability. In 2006, Nvidia developed CUDA programming model to promote

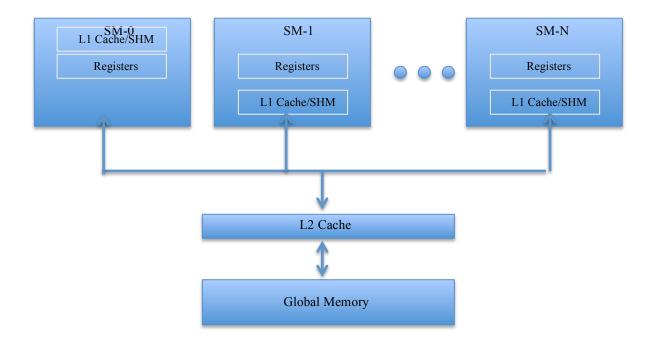

the use of its GPGPUs. At the core of CUDA programming model are three key abstractions: a hierarchy of thread groups, a memory hierarchy, and barrier synchronization. A CUDA program launches a grid of blocks, the blocks reside and run on GPU's streaming multiprocessors (SMs), and each block contains a group of concurrent threads. A block can be thought of as a cluster of threads that run cooperatively while still independently. All threads run the same code with different data, differentiated by block id and thread id. GPGPUs have a tiered memory hierarchy shown in Figure 3. Each SM has a large and unified register file and a L1 cache, to be used by threads privately, and a local memory of low latency called shared memory that is accessible and shared by all threads within the block running on this SM. This fast shared memory provides great data locality improvement opportunity for algorithms. A larger L2 cache is provided and shared among all SMs to service all load and store from/to global memory. The global memory is a very large memory accessible by all threads but has high latency. The goal of this research is to obtain optimal execution time for algorithms by optimizing data locality via optimal use of GPGPU parallel processing capability and fast on-chip shared memory.

Moving data between threads in a block on a SM and the global memory incurs significant cost, due to the high latency of global memory. To improve performance, in addition to the L2 cache, GPGPUs use coalescing technique for memory access to the global memory. The global memory accesses by threads of a block are coalesced into a single memory transaction when the words accessed by threads lie in the same segment, i.e., within a certain memory space with contiguous addresses. The memory segment size

s is 32 bytes if threads access 1-byte words, or 64 bytes when accessing 2-byte words and 128 bytes when accessing 4-byte or 8-byte words.

Figure 3: A typical GPGPU memory hierarchy. It contains a global memory and L2 cache shared by all blocks, a L1 cache private to threads, and a shared memory SHM shared by threads within the blocks.

Let P be the size of the grid, that is, the number of blocks/clusters, and  $t_s$  and  $t_r$  be the times each block spends on saving data to and retrieving data from the global memory, respectively. Therefore, a GPGPU can be modeled by parameters  $(P, t_s, t_r, s)$ .

## 3.3 Linear Scheduling

A linear schedule is a mapping from the multi-dimensional iteration vectors in the iteration space J into a one-dimensional execution time space. This mapping is expressed as a linear function f that involves a multiplication of a row vector  $\Pi$ , called

linear schedule vector, by each and every column vector in the iteration space. In other words, an iteration with index vector j is assigned to execute at time  $\prod j$ . A linear schedule has to respect data dependences. That is, if an iteration depends on another iteration, a feasible linear schedule should schedule the latter iteration to execute before the former one. As described in [5], a linear schedule vector  $\prod$  is *feasible* if  $\prod d_j > 0$ , j = 1,...,q. Another concept associated with a linear schedule is its wavefronts in the iteration space. All iterations that are assigned to the same execution time form a wavefront. More description of linear schedule can be found in [5].

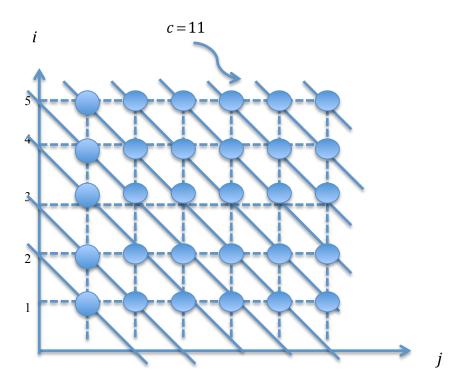

Figure 4: The ten wavefronts of the linear schedule vector [1,1] for the two-dimensional uniform dependency algorithm in Figure 1, with N=5, M=6 and c=2,...,11.

For the two dimensional iteration space in Figure 1, a feasible linear schedule vector is [1,1], and the corresponding feasible linear schedule is  $f([i,j]^t)=[1,1][i,j]^t=i+j$ . The

entire iteration space is partitioned into wavefronts  $\left\{\begin{bmatrix} i \\ j \end{bmatrix}: i+j=c \right\}$  where c=2,...,N+M. Note all iterations (i,j) on the same wavefront are independent and can

c=2,...,N+M. Note all iterations (i,j) on the same wavefront are independent and can be executed at the same time in parallel, provided there are enough computing nodes available. Figure 4 shows a two-dimensional iteration space with N=5 and M=6, it is partitioned by ten wavefronts with c=2,...,11.

#### 3.3.1 Example of the LCS problem scheduling on GPGPU

The linear schedule  $f([i,j]^t) = [1,1][i,j]^t = i+j$  can be applied to LCS problem to ensure feasible and maximum parallelism, it is the traditional way of exploiting the parallelism in diagonal direction [36]. In [35] J. Yang et al. proposed an efficient approach to schedule iterations row by row by first changing the data dependency in the score table used by the dynamic programming algorithms for higher degrees of parallelism to take advantage of GPGPU's parallel processing capability. This approach is shown to be three times faster than the traditional way in [36].

3.4 Supernode transformation on multi-processor system with *P* processors

22

To see the motivation of supernode transformation, let's examine the different executions of the LCS problem. The first is the sequential execution by a single processor and the total execution time is  $MNt_c$ , because there are MN iterations and each iteration takes  $t_c$  time. In the parallel processing, all the iterations on the same wavefront are executed in parallel assuming there are enough processors. There are two phases: computation phase when the processor calculates an iteration in time  $\boldsymbol{t}_{c}$  and communication phase when the processor sends and receives data from other processors with communication time  $t_{comm} = t_r + t_s$ . Hence the execution time of each wavefront is  $t_c + t_{comm}$ . There are M + N - 1 wavefronts, so the total execution time is  $(t_c + t_{comm})(M+N-1)$ . If  $t_c = 1$ ,  $t_{comm} = 100$ , M = 100, N = 1000, then the sequential is  $MNt_c = 10^5$  and the parallel time execution execution time is  $(t_c + t_{comm})(M+N-1) = 101*1099 > 10^5$ . This means the parallel execution time is even worse than the sequential one.

Supernode transformation is to optimize data locality by addressing the problem of unbalanced computation and communication costs. Instead of assigning one iteration to a processor, a set of neighboring iterations are grouped as a supernode and assigned to a processor. This way, the iterations in the same supernode are processed faster on the same processor, and the number of wavefronts is reduced and the system will spend less time on communication so the total execution time is minimized. For example, for the two dimensional iteration space in Figure 5 with each intersection being an iteration, one possible supernode transformation is w=3 and h=2, thus six iterations are grouped to

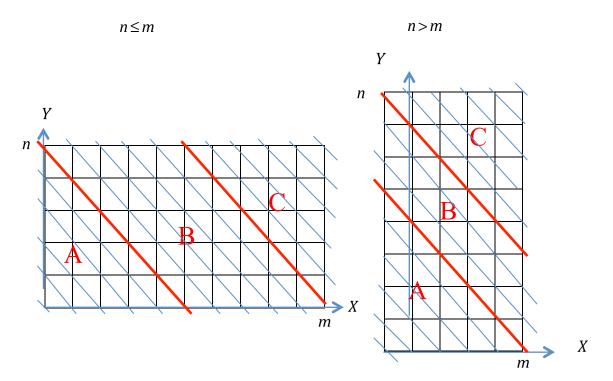

form a supernode. The iteration space after the supernode transformation is shown in Figure 6. There are two possible cases:  $n \le m$  and n > m.

Figure 5: Two dimensional uniform dependence algorithm iteration space, each intersection is an iteration. Each dotted-line rectangle of  $w \times h$  is a supernode, or a tile.

A supernode can be described by two parameters: the size and the shape. In [11], it is proven that the rectangular is the best shape for the two dimensional uniform dependence algorithms because it is the minimal parallelogram covering the cone of all dependence vectors. Therefore, for the two dimensional uniform dependence algorithms, the supernode shape and size can be defined by a rectangular of width w and height h. Thus their supernode transformation can be modeled by (f, w, h) where f is the linear schedule and w and h are the supernode sizes in X and Y directions.

**Figure 6**: Iteration space after supernode transformation, each intersection is a supernode. There are two cases: n < m and  $n \ge m$ .

This research is to apply supernode transformation (f, w, h) to two dimensional uniform dependence algorithms (J, D) on cluster system  $(P, t_r, t_s)$  or GPGPUS  $(P, t_s, t_r, s)$  for time optimal execution enabled by optimal locality. For this purpose four key parameters are formally introduced here for later modeling use:

$t_{sn}$  - the time used to process one supernode, including both computation and communication time by one computing node. It is a function of  $(w, h, t_c, t_s, t_r)$ . T - total execution or running time, our goal is to minimize this value.  $t_s$  - the problem size in  $t_s$  direction after transformation, so  $t_s$  -  $t_s$  and  $t_s$  -  $t_s$  and  $t_s$  -  $t_s$

n - the problem size in Y direction after transformation, so  $n = \frac{N}{h}$ , and  $n \in [1,N]$ .

Without losing generality, this research focuses on the case where  $n \ge m$ . The iteration space after supernode transformation can be divided into three regions A, B and C, as shown in Figure 6. When  $n \ge m$ , in region A, there are m wavefronts and the number of supernodes in wavefronts increases from one to m. In region B, there are n-m-1 wavefronts and the number of supernodes in each wavefront is a constant m. In region C, there are m wavefronts and the number of supernodes in wavefronts decreases from m to one.

## 4. Total Execution Time With Supernode Transformation

In this section, an execution model for a given two dimensional uniform dependence algorithm (J,D) on a multi-processor system such as a cluster system  $(P,t_r,t_s)$  or GPGPU  $(P,t_s,t_r,s)$  is established. Based on this model, a novel closed form expression of the total execution time T is derived. This expression is used in the later sections to guide the selection of the optimal supernode transformations.

To respect the data dependence, the execution has to start at the first wavefront with only one supernode at the lower left corner in region A in Figure 6, and moves towards the upper right corner in region C, the execution of wavefront c can not start until all the wavefronts 1,...,c-1 are executed. The mapping of the supernodes on a wavefront to the processors (computing nodes in cluster, or GPGPU blocks) is as follows: assuming the current wavefront c has  $\mu$  supernodes, then the entire wavefront c is divided into  $\left\lceil \frac{\mu}{P} \right\rceil$  contiguous sections, each section has p supernodes, with the exception that the last section may have fewer than p supernodes. The sections are executed sequentially and each section is processed by p processors in parallel, with one processor handling one supernode. So some processors may be idle when processing the last section, since there may be fewer than p supernodes. When a processor processes a supernode, it first takes  $t_r$  time to retrieve dependent data in earlier wavefronts such as c-1 or c-2 from other computing nodes of the cluster, or from main memory of GPGPU. Then the execution

enters into computation phase by computing  $w \cdot h$  iterations in supernode. Finally it takes  $t_s$  time to send the computation results to other computing nodes in the cluster, or back to the main memory of the GPGPU, for computing wavefronts such as c+1. Thus the execution time of one wavefront is  $t_s \cdot \left\lceil \frac{\mu}{P} \right\rceil$  where  $t_s$  is the time for a computing node of the cluster, or a block of the GPGPU, to process one supernode. Here in both data retrieving and sending phases, communication startup time is assumed to be dominant, so communication cost is fixed.

Let  $T_A$  be the total execution time for all wavefronts in region A,  $T_B$  for region B and  $T_C$  for region C. So  $T = T_A + T_B + T_C$ , and since  $T_A = T_C$ ,  $T = 2T_A + T_B$ .

For region A, the execution starts from lower left corner where the number of supernodes is one, then it moves towards the upper right direction until it reaches the wavefront with number of supernodes m. Thus:  $T_A = \sum_{c=1}^m \left[ \frac{c}{P} \right] t_{sn} = t_{sn} \sum_{c=1}^m \left[ \frac{c}{P} \right]$ .

Let m=kP+r where  $k \in Z^+$ ,  $Z^+$  being the set of all positive integers, r being the remainder,  $r \in [0,P-1]$ . Let  $v=k+1=\left\lceil \frac{m}{P}\right\rceil$ . In region A, there are m wavefronts, for each wavefront c in the first set of P wavefronts, where  $c \in [1,P]$ ,  $\left\lceil \frac{c}{P} \right\rceil = 1$ . For each wavefront c in the second set of P wavefronts, where  $c \in [P+1,2P]$ ,  $\left\lceil \frac{c}{P} \right\rceil = 2$ , and so

on. For wavefronts c where  $c \in [(k-1)P+1, kP]$ ,  $\left\lceil \frac{c}{P} \right\rceil = k$ . For the last r wavefronts

where  $c \in [kP+1, kP+r]$ ,  $\left\lceil \frac{c}{P} \right\rceil = k+1 = v$ . Thus:

$$T_{A} = t_{sn} \left( \underbrace{1 + 1 + \dots + 1}_{p} + \underbrace{2 + 2 + \dots + 2}_{p} + \dots + \underbrace{k + k + \dots + k}_{p} + \underbrace{v + v + \dots + v}_{r} \right)$$

$$= t_{sn} \left( \underbrace{m - r}_{P} + 1 \right) \left( \underbrace{m + r}_{2} \right)$$

(3)

For  $T_B$ , the total number of wavefronts in region B is n-m-1. Each wavefront has m supernodes and the number of execution sections is  $\left\lceil \frac{m}{P} \right\rceil$ . So:

$$T_{B} = t_{sn}(n-m-1) \left\lceil \frac{m}{P} \right\rceil \tag{4}$$

therefore:

$$T = 2T_A + T_B = t_{sn} \left( \frac{m - r}{P} + 1 \right) (m + r) + t_{sn} (n - m - 1) \left[ \frac{m}{P} \right]$$

(5)

To get a closed form for T, let's consider the following three cases:

Case 1:  $m \le P$ . This happens when k=1 and r=0, or k=0 and  $r \in [1, P-1]$ . Giving

$$\left[\frac{m}{P}\right] = 1$$

, the total execution time based on (5) is:

$$T_{m \le P} = t_{sn}(n+m-1) \tag{6}$$

Case 2:  $m \ge P$ , m = kP, r = 0. Giving  $\left\lceil \frac{m}{P} \right\rceil = k$ , equation (5) becomes:

$$T_{m=kP} = t_{sn}(n+P-1)\frac{m}{P}$$

(7)

Case 3:

$$m \ge P$$

,  $m = kP + r$ ,  $r \in [1, P - 1]$ . In this case,  $\left\lceil \frac{m}{P} \right\rceil = \frac{m - r}{P} + 1$ , so equation (4)

becomes:

$$T_{B} = t_{sn}(n - m - 1)(\frac{m - r}{P} + 1)$$

(8)

Therefore, the total execution time in (5) becomes:

$$T_{m=kP+r} = t_{sn} \left( \frac{m-r}{P} + 1 \right) (n+r-1)$$

(9)

Equations (3)-(9) form the mathematical foundation for the optimal solution of supernode transformation, and are summarized as following:

$$T = \begin{cases} t_{sn}(n+m-1) & 1 \le m \le P, m \le n \le N \\ t_{sn}(n+P-1)\frac{m}{P} & m = kP, k \ge 1, m \le M, m \le n \le N \\ t_{sn}(\frac{m-r}{P}+1)(n+r-1) & m = kP+r, k \ge 1, 1 \le m \le M, m \le n \le N, 1 \le r \le P-1 \end{cases}$$

(10)

The goal of this research is to find the optimal solution  $(m_0, n_0)$  that minimizes the total execution time T. In the following sections, supernode transformation is applied to two multi-processor distributed memory systems: computer cluster systems and GPGPUs. Equations (3)-(10) above are used to find the optimal solution that minimizes the total execution time T. Note the model applies to two dimensional uniform

dependence algorithms with rectangular iteration space, with non-overlapping communication and computation phases.

# 5. Supernode Transformation On Computer Clusters

This section discusses supernode transformation on computer cluster system  $(P,t_r,t_s)$ , especially the finding of the optimal solution  $(m_0,n_0)$  of two dimensional uniform dependence algorithm. The optimal solution minimizes the total execution time expressed in (10).

In (10),  $t_{sn}$  is the execution time of one supernode on one computing node of the cluster. As mentioned in section 3, the execution of one supernode has three phases: data reading phase that takes time  $t_r$ , computing phase, and data saving phase that takes time  $t_s$ . For a supernode with a rectangular shape  $w \times h$  and processed by one computing node, the computing time is  $w \cdot h \cdot t_c$  where  $t_c$  is the computation time of one iteration. Let  $A = MNt_c$  and  $B = t_s + t_r$ , then:

$$t_{sn} = t_r + wht_c + t_s = \frac{A}{mn} + B \tag{2}$$

The basic idea of how to find the optimal solution of T in (10) is as follows. The solution space of  $m \in [1, M]$  is divided into three subspaces  $S_1$ ,  $S_2$  and  $S_3$ , where:  $S_1 = \{m : m \in [1, P]\} \qquad , \qquad S_2 = \{m : m = kP, k \in Z^+, P \le m \le M\} \qquad , \qquad \text{and} \qquad S_3 = \{m : m = kP + r, k \in Z^+, P \le m \le M, 1 \le r \le P - 1\} \text{.} \text{ The best solution in each subspace is identified, and then the optimal solution is obtained by comparing these best solutions of the three subspaces.}$

## 5.1 Lemmas and Theorem

In the following, three lemmas are introduced followed by the main theorem presenting the optimal solution. The theorem is proved by these three lemmas, while the proof of these lemmas can be found in Appendix A in section 9. Equations numbered (A x) are from Appendix A.

For subspace  $S_1$ , according to (10) and (11), the total execution time T is:

$$T_{m \le p}(m,n) = (\frac{A}{mn} + B)(n+m-1)$$

(A0)

As discussed in the Appendix A,  $T_{m \le P}(m,n)$  is convex in [2,P], and has at most one minimum point, or stationary point. If there exists such a stationary point, it is denoted as  $(m_e,n_e)$ . Let  $(2,n_{b2})$  and  $(P,n_{bP})$  be two points in  $S_1$  such that  $\frac{\partial T}{\partial n}(2,n_{b2})=0$ ,  $\frac{\partial T}{\partial n}(P,n_{bP})=0$ . Let  $(m_1,n_1) \in S_1$  be the local minimum point, that is,  $T(m_1,n_1)=\min\{T(m,n):m\in S_1\}$ , then  $(m_1,n_1)$  can be found by Lemma A1.

#### 5.1.1 Lemma A1

In the solution subspace  $S_1 = \{m : m \in [1,P]\}$ , if the stationary point  $(m_e, n_e)$  exists,  $(m_1, n_1) \in \{(m_e, n_e), (1,1)\}$ . Otherwise,  $(m_1, n_1) \in \{(2, n_{b2}), (P, n_{bP}), (1,1)\}$ , where

$$n_e = \sqrt{\frac{(m_e - 1)A}{m_e B}}$$

,  $n_{b2} = \sqrt{\frac{A}{2B}}$ ,  $n_{bP} = \sqrt{\frac{(P - 1)A}{PB}}$

Lemma A1 provides a candidate set for  $(m_1, n_1)$ . The candidate with the lowest T value is the local minimum point. Equation (A5) from Appendix A is used to obtain  $m_e$  in [2,P]:

$$B^{2}m^{5} - B^{2}m^{4} - 2ABm^{3} + 2ABm^{2} + (A^{2} - AB)m - A^{2} = 0$$

(A5)

Equation (A5) is a polynomial with one variable, real coefficients, and odd degree. So (A5) must have at least one real root [12]. (A5) may have more than one real root because some extraneous roots may be generated during processing. However, as discussed in Appendix A, (A5) has at most one valid real root. For a root  $m_{root}$  and its corresponding  $n_{root}$ , if they satisfy  $\frac{\partial T}{\partial m} = 0$  and  $\frac{\partial T}{\partial n} = 0$  for (A0), then  $m_e = m_{root}$ . Otherwise,  $(m_e, n_e)$  does not exist.

## 5.1.2 Lemma A2

In the solution subspace  $S_2 = \{m : m = kP, 1 \le k, m \le M\}$ , T defined in (10) takes minimum at  $(m_2, n_2) = (P, \sqrt{\frac{A(P-1)}{PB}})$ . Note m = P is also in solution subspace  $S_1$ .

## 5.1.3 Lemma A3

For any m in the solution subspace  $S_3 = \{m : m = kP + r, 1 \le k, m \le M, 1 \le r \le P - 1\}$ ,  $T_{m=kP+r}$  defined in (10) is always greater than  $T_{m=P}$  in solution subspace  $S_1$ .

#### 5.1.4 Theorem

In a cluster system with fixed P computing nodes, the total execution time is minimized with supernode size  $(m_0, n_0)$  that equals  $(m_1, n_1)$  defined in Lemma A1.

Proof: According to Lemma A3, the optimal solution is not in  $S_3$ . Lemma A2 tells that the local minimum solution of  $S_2$  is at  $m_2 = P$  which is also in solution subspace  $S_1$ . So the optimal solution is in solution subspace  $S_1$ . Thus  $(m_0, n_0) = (m_1, n_1)$ .

In the above discussion,  $m_e$ ,  $n_e$ ,  $n_e$ ,  $n_{b2}$  and  $n_{bP}$  might be real numbers instead of integers. Then the nearest integer value will be used as the best integer solution for the convex function  $T_{m \le P}$ , denoted by symbol  $\left[ \right]$ . For example, when  $m_e$  is not an integer, then we get  $m_e = \left[ m_e \right]$ .

## 5.2 Simulation

Simulations are conducted to find the optimal supernode size with the shortest running time for the LCS problem of size (600,1200). A multi-core system is used to simulate a cluster system. The system used is a  $X86\_64$  8 CPU server with 8 cores, the kernel release is 3.13.0-55-generic. The operating system is Ubuntu 14.04.2 LTS. One core is designated as the master computer node and six cores are used as computing nodes, hence P=6. The master computer and computing nodes reside on their dedicated cores via Linux  $sched\_setaffinity()$  call. To facilitate more efficient communication and provide synchronization between computing nodes, the computing nodes communicate with the

master computer only. The master computer drives the entire workflow, starts and initializes all computing nodes. For each execution of a section of a wavefront, the master computer sends dependent data to each and every computing node via Unix sockets in time  $t_r$ , receives results from these computing nodes in time  $t_s$  after the computations are completed, and provides synchronization between computing nodes. The time each computing node spends on computation of one supernode is  $w \cdot h \cdot t_r$ .

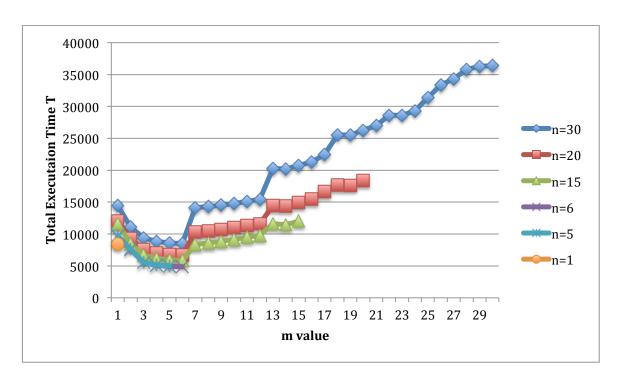

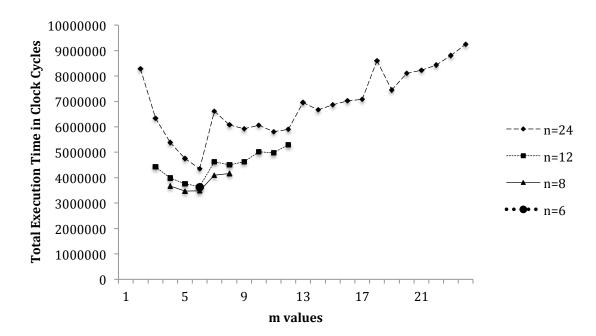

All possible pairs of (m,n) are exhaustively tested. In the simulation, M=600, N=1200, so there are  $600\times1200$  possible pairs of (m,n). The results are partially shown in the table below. In the table, a row corresponds to a particular value of m ranging from 1 to n. The six columns correspond to particular values of n=30, 20, 15, 6, 5 and 1. For example, the total execution time for (m,n)=(2,30) is  $11103 \, \mu s$ . The table shows that the total execution time at (m,n)=(6,6) is the shortest. The test results are also curved in Figure 7.

| $m(\leq n)$ | n=30  | n=20  | n=15  | n=6  | n=5  | n=1  |

|-------------|-------|-------|-------|------|------|------|

| 1           | 14474 | 12084 | 11662 | 9719 | 9752 | 8502 |

| 2           | 11103 | 9277  | 8439  | 7557 | 7658 |      |

| 3           | 9412  | 7570  | 6699  | 5551 | 5556 |      |

| 4           | 8837  | 7021  | 6169  | 5108 | 5140 |      |

| 5           | 8583  | 6779  | 5936  | 4923 | 4970 |      |

| 6           | 8489  | 6688  | 5850  | 4867 |      |      |

| 7           | 14141 | 10286 | 8360  |      |      |      |

| 8           | 14294 | 10470 | 8577  |      |      |      |

| 9           | 14529 | 10726 | 8857  |      |      |      |

| 10          | 14788 | 10996 | 9146  |      |      |      |

| 11          | 15101 | 11319 | 9483  |      |      |      |

| 12          | 15404 | 11628 | 9802  |      |      |      |

| 13 | 20313 | 14485 | 11588 |  |  |

|----|-------|-------|-------|--|--|

| 14 | 20197 | 14358 | 11455 |  |  |

| 15 | 20728 | 14910 | 12031 |  |  |

| 16 | 21294 | 15496 |       |  |  |

| 17 | 22451 | 16692 |       |  |  |

| 18 | 25553 | 17696 |       |  |  |

| 19 | 25501 | 17640 |       |  |  |

| 20 | 26241 | 18406 |       |  |  |

| 21 | 27031 |       |       |  |  |

| 22 | 28602 |       |       |  |  |

| 23 | 29383 |       |       |  |  |

| 24 | 29323 |       |       |  |  |

| 25 | 31355 |       |       |  |  |

| 26 | 33376 |       |       |  |  |

| 27 | 34347 |       |       |  |  |

| 28 | 35799 |       |       |  |  |

| 29 | 36283 |       |       |  |  |

| 30 | 36383 |       |       |  |  |

Table 1: Total execution times for different values of (m,n) on a cluster system P=6 for the LCS problem of size 600x1200. For example, the total execution time for (m,n)=(2,30) is 11103.

So  $(m_0,n_0)=(6,6)$ , or (w,h)=(100,200), is the optimal supernode size, and the shortest total execution time is 4867us, out of which, the total communication time recorded from simulation is 2118us, and the total computation time is 2749us.

Figure 7: Total execution times for different values of (m,n) on cluster with P=6 for the LCS problem of size 600x1200. Six n values are shown. The chart indicates when (m,n)=(6,6), as indicated in the purple curve, T is the smallest.

To find the analytical value for  $(m_0, n_0)$  from theorem, parameters  $t_r + t_s$  and  $t_c$  are needed. Giving that the total communication cost is 2118us, and there are m+n-1 wavefronts, the communication cost per supernode is calculated as following:

$$t_s + t_r = 2118/(m+n-1) = 193 us$$

For computation cost  $t_c$ , because the total computation cost is  $2749\,us$ , there are m+n-1 wavefronts, and each wavefront needs one execution section which costs  $w\cdot h\cdot t_c$ :

$$t_c = total\_comp\_time / ((m+n-1) \cdot w \cdot h) = 2749 / (11*100*200) = 0.012 us$$

So  $A = MNt_c = 8640$ , and  $B = t_s + t_r = 193$ . Then equation (A5) produces 5 roots: -7, -6, 1, 6 and 7. Root -7, -6, 1 and 7 are not valid since they are not in the valid range of [2,*P*] which is [2,6]. So only m = 6 is the valid root.

When m=6,

$$n = \left[ \sqrt{\frac{(m-1)A}{mB}} \right] = 6$$

,  $\frac{\partial T}{\partial m} (m_{root=6}, n_{root=6}) = 0$  and  $\frac{\partial T}{\partial n} (m_{root=6}, n_{root=6}) = 0$ .

So  $(m_a, n_a) = (6,6)$  is the stationary point. Thus according to (A0):

$$T(6,6) = (\frac{A}{mn} + B)(n+m-1) = (\frac{8640}{6 \cdot 6} + 193)(6+6-1) = 4763$$

Then based on Lemma A1, there is a special point (1,1) that needs to be checked:

$$T(1,1) = (\frac{A}{mn} + B)(n+m-1) = (\frac{8640}{1 \cdot 1} + 193)(1+1-1) = 8833$$

According to Theorem, point (6,6) yields smaller T than the point (1,1), hence it is the optimal point. The analytical optimal solution (6,6) exactly matches the simulation results, and its total running time  $4763\,us$  is very close to the simulation minimum result of  $4867\,us$ .

If the cyclic column-wise assignment in section 2.3 were used,  $T_{opt}$  would be 5181. Note  $a = t_r + t_s$  and b = 0. So this research provides better result, without any restriction.

For the hypothetical case in section 2.3, per the theorem,  $(m_0, n_0) = (2,2)$ , and  $T_{opt} = 3900$  which is much better than 5400 obtained using cyclic column-wise assignment.

# 6. Supernode Transformation on GPGPUs

This section discusses the supernode transformation on GPGPUs. The two-sequence LCS problem is used as an example to show how to use supernode transformation to map applications to a GPGPUs with the total execution time minimized. Equations of total execution times developed in section 4 apply to GPGPU architectures as well. However, the execution time of one supernode  $t_{sn}$  is different from the one in section 5 and is derived in section 6.1.

## 6.1 Analytical Results

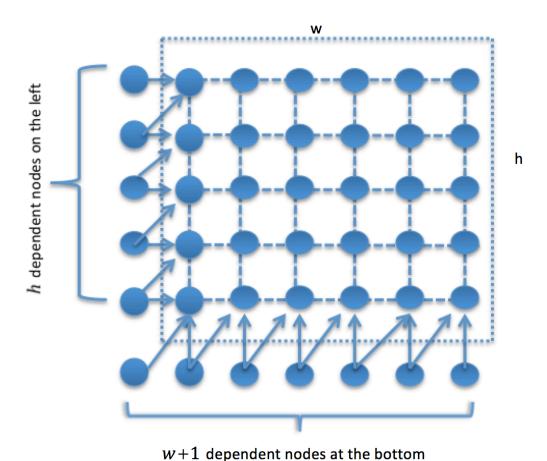

The execution of a two dimensional uniform dependence algorithm such as LCS on a GPGPU is modeled as follows. A supernode with size  $w \times h$  is assigned to a block running on a GPGPU SM. When a block is launched, it first reads in the dependent data for this supernode from the global memory in time  $t_r$ , then it processes the iterations inside the supernode. Note the dependence graph of this supernode is similar to the one in Figure 1, so the iterations are processed by wavefronts from lower-left corner to upperright corner, and there are w+h-1 wavefronts inside a supernode. The results of the iterations on each wavefront are stored in the shared memory of the block on the SM, and are used by the subsequent dependent wavefronts. After all wavefronts in the supernode are processed, the results for all iterations of the supernode in the shared memory are saved back to the global memory in time  $t_s$ .

Giving there are many threads inside each block/SM, the computations of iterations on one wavefront inside the supernode can be done in parallel, assuming inside each block, the number of threads is equal to or greater than the maximum number of iterations on any wavefront. Then all the iterations on the same wavefront are processed in parallel thus the execution time of one wavefront is  $t_c$ . The communication cost is ignored because the communication happens between threads and is done by accessing the shared memory on the same chip. Hence the total computation time of one supernode is  $(w+h-1)\cdot t_c$ .

Next the communication costs  $t_s$  and  $t_r$  of each supernode are discussed. When a block is launched for a supernode, the first thing the threads in the block do is to read in the dependent data of the iterations on the boundary of the supernode from the global memory. As shown in Figure 8, supernode of size  $w \times h$  depends on h iterations on the left of the supernode and w+1 iterations at the bottom in the original iteration space.

For the w+1 dependent iterations to the bottom, w+1 threads are used to read their data into the block from the global memory, one thread for each iteration. Since the w+1 data are stored consecutively in the global memory, the w+1 reads are coalesced into  $\left\lceil \frac{w+1}{s} \right\rceil$  memory segment transactions, note s is the memory segment size. So the total

reading time is  $\left\lceil \frac{w+1}{s} \right\rceil t_m$ , where  $t_m$  is one memory transaction time between the global memory and a GPGPU block. For the h dependent iterations on the left, they are not consecutive in the global memory, so each iteration data takes one memory transaction to

read. Hence it takes  $ht_m$  to read these h data. So it takes  $\left\lceil \frac{w+1}{s} \right\rceil t_m + ht_m$  time to read in the data of the dependent iterations for a supernode.

Figure 8: A LCS Supernode of size  $w \times h$  and its dependent nodes. The supernode is inside the dashed-line rectangular, while the dependent nodes are on the left and at the bottom.

According to (2), there are w symbols from X sequence, and h symbols from Y sequence needed in the LCS computation for a supernode. So it takes  $\left\lceil \frac{w}{s} \right\rceil \cdot t_m$  and

$\left\lceil \frac{h}{s} \right\rceil \cdot t_m$  time to read these symbols in a coalesced way. Hence for a supernode, the  $t_r$  is expressed as:

$$t_r = \underbrace{\left[\frac{w+1}{s}\right] \cdot t_m + ht_m}_{\text{for bottom and left dependent iterations}} + \underbrace{\left[\frac{w}{s}\right] \cdot t_m + \left[\frac{h}{s}\right] \cdot t_m}_{\text{for X and Y sequences symbols}}$$

When the computations of a supernode are done, the results of all iterations in the supernode, not just those of boundary nodes, are saved back into the global memory. Each iteration generates one datum to be saved into the global memory, note s consecutive data in a row can be coalesced into one memory transaction. Therefore, for the s data on one row, s memory segment transactions are needed, and this process is repeated s times to finish the entire supernode, so for a supernode, s and s the supernode s

$$t_{sn} = \underbrace{(w+h-1)t_{c}}_{computation \ time} + h\underbrace{\left[\frac{w}{s}\right]t_{m} + \left[\frac{w+1}{s}\right]t_{m} + ht_{m} + \left[\frac{w}{s}\right]t_{m} + \left[\frac{h}{s}\right]t_{m}}_{communication \ cost}$$

$$(11)$$

To simplify the analysis, all ceiling functions are removed. The error analysis due to this approximation is in section 5.3. Also  $w = \frac{M}{m}$  and  $h = \frac{N}{n}$ , then:

$$t_{sn} = \underbrace{\left(\frac{M}{m} + \frac{N}{n} - 1\right)t_{c}}_{computation time} + \underbrace{\left(\frac{N}{n} + 1\right)\frac{M}{sm}t_{m} + \frac{M}{m} + 1}_{communication cost} + \underbrace{\frac{N}{n}t_{m} + \frac{N}{sn}t_{m}}_{communication cost} = \underbrace{\frac{A}{m} + \frac{B}{n} + \frac{C}{mn} - D}_{communication cost}$$

(12)

where

$$A = M(t_c + \frac{2t_m}{s}), B = N(t_c + (1 + \frac{1}{s})t_m), C = \frac{MNt_m}{s}, D = t_c - \frac{t_m}{s}$$

(13)

The basic idea of finding the optimal solution of T in (10) on GPGPUs is similar to that of in section 5, as follows. The solution space of  $m \in [1,M]$  is divided into three subspaces  $S_1$ ,  $S_2$  and  $S_3$ :  $S_1 = \{m : m \in [1,P]\}$ ,  $S_2 = \{m : m = kP, k \in Z^+, P \le m \le M\}$ ,  $S_3 = \{m : m = kP + r, k \in Z^+, P \le m \le M, 1 \le r \le P - 1\}$ . The best solution in each subspace is identified, and then the optimal solution is obtained by comparing these best solutions of the three subspaces.

## 6.2 Lemmas and Theorem

Three lemmas are introduced which lead to theorem that presents the optimal solution of supernode transformation on GPGPUs. The theorem is proved based on these lemmas. Please refer to Appendix B for the proof of these lemmas. Equations numbered (Bx) are from Appendix B.

For subspace  $S_1$ , according to (10) and (12), the total execution time T is:

$$T_{m \le p}(m,n) = (\frac{A}{m} + \frac{B}{n} + \frac{C}{mn} - D)(n+m-1)$$

(B0)

As discussed in the Appendix B,  $T_{m \le P}(m,n)$  is convex in [2,P], and has at most one minimum point, or stationary point. If there exists such a stationary point, it is denoted as  $(m_e,n_e)$ . Let  $(2,n_{b2})$  and  $(P,n_{bP})$  be two point in  $S_1$  such that  $\frac{\partial T}{\partial n}(2,n_{b2})=0$ ,

$\frac{\partial T}{\partial n}(P, n_{bp}) = 0 \quad \text{Let} \quad (m_1, n_1) \in S_1 \quad \text{be the local minimum point, that is,}$   $T(m_1, n_1) = \min\{T(m, n) : m \in S_1\} \quad \text{Then } (m_1, n_1) \quad \text{can be found by Lemma B1.}$

## 6.2.1 Lemma B1

In the solution subspace  $S_1 = \{m : m \in [1, P]\}$ , if the stationary point  $(m_e, n_e)$  exists,  $(m_1, n_1) \in \{(m_e, n_e), (1, 1)\}$ , otherwise,  $(m_1, n_1) \in \{(2, n_{b2}), (P, n_{bP}), (1, 1)\}$ , where

$$n_{e} = \sqrt{\frac{Bm_{e}^{2} + (C - B)m_{e} - C}{A - Dm_{e}}}, n_{b2} = \sqrt{\frac{2B + C}{A - 2D}}, n_{bp} = \sqrt{\frac{B \cdot P^{2} + (C - B)P - C}{A - DP}}$$

Lemma B1 provides a candidate set for  $(m_1, n_1)$ . The candidate yielding the lowest T value is the local minimum point. Equation (B5) from Appendix B is used to obtain  $m_e$  in [2,P]:

$$a_1 m^7 + a_2 m^6 + a_3 m^5 + a_4 m^4 + a_5 m^3 + a_6 m^2 + a_7 m + a_8 = 0$$

(B5)

where A,B,C,D are constants defined in (13), and constants  $a_1,a_2,a_3,a_4,a_5,a_6,a_7$  are defined in terms of A,B,C,D in (B6) in Appendix B.

Equation (B5) is a polynomial in one variable with real coefficients and odd degree. So (B5) must have at least one real root [12]. (B5) may have more than one root because some extraneous roots may be generated during processing. However, as discussed in Appendix B, (B5) has at most one valid real root. For a root  $m_{root}$  and its corresponding

$n_{root}$ , if they satisfy  $\frac{\partial T}{\partial m} = 0$  and  $\frac{\partial T}{\partial n} = 0$  for (A0), then  $m_e = m_{root}$ . Otherwise,  $(m_e, n_e)$  does not exist.

#### 6.2.2 Lemma B2

In the solution subspace  $S_2 = \{m : m = kP, 1 \le k, m \le M\}$ , T defined in (10) takes minimum at  $(m_2, n_2) = (P, \sqrt{\frac{(BP+C)(P-1)}{A-DP}})$ . Note  $m_2 = P$  is also in subspace  $S_1$ .

## 6.2.3 Lemma B3

For any m in the solution subspace  $S_3 = \{m: m = kP + r, 1 \le k, m \le M, 1 \le r \le P - 1\}$ ,  $T_{m=kP+r}(m,n)$  defined in (10) is always greater than  $T_{m=p}(m,n)$  in subspace  $S_1$ .

## 6.2.4 Theorem

On GPGPU system  $(P, t_s, t_r, s)$ , the total execution time of algorithm (J, D) is minimized with supernode size  $(m_0, n_0)$  that equals  $(m_1, n_1)$ , as defined in Lemma A1.

Proof: according to Lemma B3, the optimal solution is not in  $S_3$ . Lemma B2 tells that the local best solution of  $S_2$  is at  $m_2 = P$  which is also in solution subspace  $S_1$ . So the optimal solution is in solution subspace  $S_1$ . Thus  $(m_0, n_0) = (m_1, n_1)$ .

## 6.3 Simulation results

Simulations are conducted to find the optimal supernode size with the shortest running time for the LCS problem of size (M,N)=(600,1200), using Nvidia's GeForce GTX 760 GPGPU. Its base clock is 980MHz and it has 6 SMs. The simulations use a one-dimension grid of size 6, thus P=6. For each execution of a wavefront section, a one-dimension grid of blocks is launched, and each block handles one supernode. Nvidia's CUDA provides API clock64() for precise time measuring in the unit of clock cycles, it is used in the simulations to record the total execution time t and the communication time  $t_s + t_r$ .

In the simulation, all possible pairs of (m,n) are tested. Hence, there are  $600 \times 1200$  possible pairs of (m,n). But in practice, Nvdia GPGPUs have a limit in the shared memory size. For example, the GeForce GTX 760 used in the simulation has 48KB shared memory size. This means there is one more restriction in the supernode size to ensure the entire supernode can be loaded in the shared memory for computation, that is,  $w \cdot h \cdot z < 48KB = 49152$  bytes, where z is the size of each iteration value in the shared memory. In simulation, the value of each iteration is stored as "short integer" which occupies 2 bytes of storage, thus z = 2. Apparently (m,n) = (1,1) can not be the optimal solution since it treats the entire problem space as one supernode of size  $600 \times 1200 \times 2 > 48KB$ , so it has to be partitioned into smaller supernodes to take advantage of GPGPU's shared memory for faster and more efficient execution.

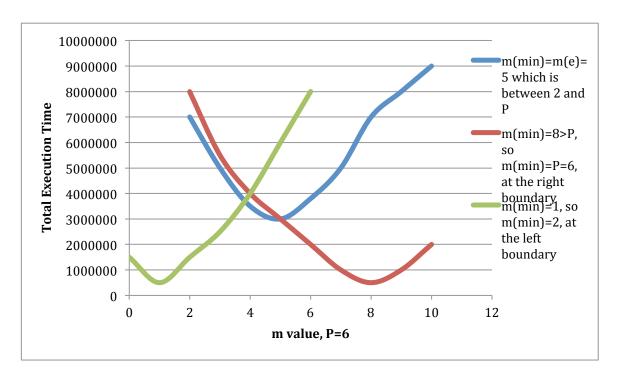

The test results are partially shown in Table 2. In Table 2, a row corresponds to a particular value of m ranging from 1 to 24. The four columns correspond to particular values of n=24, 12, 8 and 6. The total execution times T from simulations are recorded and shown. For example, T for m=3, n=24 is 6,339,434 clock cycles. The tests show when (m,n)=(5,8), with the corresponding (w,h)=(123,152), the total execution time T=3,320,364 clock cycles is the shortest, out of which the total save/read time  $t_s+t_r$  recorded is 358,704 clock cycles. The simulation results are also curved in Figure 9. Note there are some empty cells in the table because they require more shared memory than 48KB. For example, when m=1 and n=24, the corresponding w and w are 600 and 50, then  $w \cdot h \cdot z = 600 \cdot 50 \cdot 2 > 48KB$ .

| $m \le n$ | n=24    | n=12    | n=8     | n=6     |

|-----------|---------|---------|---------|---------|

| 1         |         |         |         |         |

| 2         | 8278296 |         |         |         |

| 3         | 6339434 | 4427573 |         |         |

| 4         | 5387489 | 3989307 | 3664786 |         |

| 5         | 4755731 | 3764232 | 3472624 |         |

| 6         | 4351107 | 3650690 | 3480312 | 3615454 |

| 7         | 6613261 | 4630957 | 4097116 |         |

| 8         | 6072377 | 4507131 | 4164922 |         |

| 9         | 5922144 | 4628155 |         |         |

| 10        | 6067154 | 5014499 |         |         |

| 11        | 5806633 | 4977027 |         |         |

| 12        | 5900364 | 5289875 |         |         |

| 13        | 6961389 |         |         |         |

| 14        | 6666499 |         |         |         |

| 15        | 6863515 |         |         |         |

| 16        | 7016888 |         |         |         |

| 17        | 7078705 |         |         |         |

| 18        | 9600376 |         |         |         |

| 19 | 7449397 |  |  |

|----|---------|--|--|

| 20 | 8101262 |  |  |

| 21 | 8231596 |  |  |

| 22 | 8425767 |  |  |

| 23 | 8802064 |  |  |

| 24 | 9250178 |  |  |

Table 2: Total execution times of the LCS problem for different values of (m,n) on a Nvidia GeForce GTX 760 GPGPU. For example, the total execution time for (m,n)=(3,24) is 6,339,434 clock cycles.

Note Figure 9 shows recurring curve segments slanting upward to the right, the size of each segment is m. According to (B7) from Appendix B,  $T_{m=kP}$  is:

$$T_{m=kP} = (A + \frac{B}{n}m + \frac{C}{n} - Dm)(n + P - 1)(\frac{1}{P})$$

(B7)

Figure 9: Total execution times of the LCS problem for different values of (m,n) on a Nvidia GeForce GTX 760 GPGPU. Results for four n values are displayed. The chart indicates when (m,n)=(5,8), as indicated in the green curve, T is the smallest.

Giving that

$$\frac{B}{n} > D$$

,  $T_{m=kP} > 0$ , so  $T_{m=kP}$  increases along with  $k$ , that is,  $T_{(k+1)P} > T_{kP}$ ,

thus the graph slants upward to the right.

Then for all m between  $T_{m=kP}$  and  $T_{m=(k+1)P}$ , based on (B9) from Appendix B:

$$T_{m=kP+r} = \frac{HP(k+1)(r+G)}{(kP+r)P} + E(k+1)(r+G)$$

(B9)

Where  $1 \le r < P$  and H, E, G are constants with G = n - 1. It's easy to show

$$T_{m=kP+r}^{"} = -\frac{2H(k+1)(kP-G)}{(kP+r)^3}$$

with respect to r. Giving that  $G = n-1 \ge m-1 = kP+r-1$ ,

$T_{m=kP+r}^{"}>0$  for all  $r\in[2,P)$ , as shown as convex curves in each segment. When r=1,  $T_{m=kP+r}^{"}=0$ ,  $T_{m=kP+1}$  thus can be larger or smaller than  $T_{m=kP+r,r\in[2,P)}$ .

Now let's check the optimal solution according to theorem. Based on the simulation, the optimal point is (w,h)=(123,152), that is  $(m_0,n_0)=(5,8)$ , and T(5,8)=3,320,364 clock cycles, out of which, the total  $t_r+t_s$  for all wavefronts is 358,704 clock cycles. Given that there are m+n-1 wavefronts, each wavefront only needs one round of execution since  $m_0 < P$ , and each execution costs one  $t_{sn}$  to complete, out of which  $(w+h-1)\cdot t_c$  time is on computation, thus  $t_c$  is calculated as:

$$t_c = \frac{T(5,8) - total(t_s + t_r)}{(m+n-1)(w+h-1)} = \frac{3320364 - 358704}{(5+8-1)(123+152-1)} = 901 \text{ clock cycles}$$

Similarly, the total communication cost is  $(t_r + t_s) \cdot (m+n-1)$ , and equation (12) gives out the communication cost  $t_r + t_s$  in  $t_{sn}$ , thus:

$$\underbrace{(\frac{MN}{smn}t_{m} + \frac{2M}{sm}t_{m} + \frac{N}{n}(1 + \frac{1}{s})t_{m} + \frac{1}{s}t_{m}}_{communication of one round execution}(m+n-1) = 358704$$

Two bytes are used to store computation results in the simulation, so the memory segment size is 64 bytes [3], or s = 32. So:

$$t_{m} = \frac{358704}{\left(\frac{600*1200}{32*5*8} + \frac{2*600}{32*5} + \frac{1200}{8}(1 + \frac{1}{32}) + \frac{1}{32}\right)(5+8-1)} = 41.3 \text{ clock cycles}$$

Parameters in (13) are then obtained: A=542149, B=1132309, C=929250, D=900. With these values, (B5) gives five real roots: -653.8, -30.455, -2.249, 5.18, 30.861. Apparently only root 5.18 is in valid range, thus  $m_e=m_{root}=5.18$ , and per Lemman B1:

$$n_e = \left[ \sqrt{\frac{Bm_e^2 + (C - B)m_e - C}{A - Dm_e}} \right] = \left[ 7.3 \right] = 7$$

Thus  $(m_e, n_e) = (5.18,7) \approx (5,7)$  which is close to the simulation result (5,8).

Same simulations were also conducted on GeForce GTX Titan X, a higher end GPGPU with 24 SMs. The tests show similar results with a better optimal value of 2416220 clock cycles, a 27% improvement even compared to using GTX 760.

## 6.4 Result Analysis

According to (B0),  $T_{m \le p}(5,7) = (\frac{A}{m} + \frac{B}{n} + \frac{C}{mn} - D)(m+n-1) = 3254220$ , it is very close to the exhaustive test result of 3320364. This proves the mathematical model is reasonably correct.

While there is no existing formula for column-wise assignment on GPGPUs that can be used for comparison, the basic assumption of column-wise assignment is all available processors participate in the execution. The exhaustive tests show when m=P=6, the shortest running time is 3615454 clock cycles, which is much worse than the optimal result by this research.

The efficient algorithm in [35] is an improved approach running LCS on GPGPU, but it does not use supernode transformation to take advantage of improved data locality and parallelism. The simulations on the same GPGPU show it takes 12731633 clock cycles to complete the LCS problem of the same problem size, which is about 3.8 times of the result of the optimal solution of this research.

## 6.5 The Selection of GPGUP Architecture Model Parameter P

The GPGPU architecture parameter P is modeled as one-dimension grid size, that is, the number of blocks. In simulation it is set to P=6, which is the number of SMs on GPGPU. Though this parameter shows up in equation (10) hence it impacts the value of optimal solution  $(m_0, n_0)$ , simulations show it does not affect the total execution time T much. Table 2 shows different P values and their corresponding shortest total execution time T via exhaustive tests.

| P=6     | P = 12  | P = 24  | P = 30  | P = 48  | P = 72  |

|---------|---------|---------|---------|---------|---------|

| 3320364 | 3311516 | 3271551 | 3271625 | 3271625 | 3275971 |

| P=96    | P = 120 | P = 144 | P = 168 | P = 192 |         |

| 3288002 | 3308869 | 3315377 | 3315723 | 3321326 |         |

Table 3: Total execution time obtained using exhaustive tests under different P. The difference is <1.5% showing the grid size has little impact on the result, due to the efficient block scheduling of GPGPU.

This is because Nvidia's GPGPU is quite efficient in scheduling blocks and threads on its hardware multi-streaming processors. When one group of threads (a warp) stalls on a memory operation, GPGPU will switch it out and switch in another group of threads efficiently. So All processors in GPGPU are productive, irrespective of the number of blocks, as long as there is enough parallelism (threads) to keep them busy.

## 7. Conclusion