| Title                   | Characterisation and modelling of degradation mechanisms in RF MEMS capacitive switches during hold-down operation                                                      |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Author(s)               | Ryan, Cormac                                                                                                                                                            |  |  |

| <b>Publication date</b> | 2016                                                                                                                                                                    |  |  |

| Original citation       | Ryan, C. 2016. Characterisation and modelling of degradation mechanisms in RF MEMS capacitive switches during hold-down operation. PhD Thesis, University College Cork. |  |  |

| Type of publication     | Doctoral thesis                                                                                                                                                         |  |  |

| Rights                  | © 2016, Cormac Ryan.  http://creativecommons.org/licenses/by-nc-nd/3.0/                                                                                                 |  |  |

| Embargo information     | No embargo required                                                                                                                                                     |  |  |

| Item downloaded from    | http://hdl.handle.net/10468/3644                                                                                                                                        |  |  |

Downloaded on 2017-09-05T00:27:41Z

# Ollscoil na hÉireann

NATIONAL UNIVERSITY OF IRELAND, CORK

# CHARACTERISATION AND MODELLING OF DEGRADATION MECHANISMS IN RF MEMS CAPACITIVE SWITCHES DURING HOLD-DOWN OPERATION

A thesis presented to

The National University of Ireland

for the degree of

Doctor of Philosophy

by

Cormac Ryan, B. Sc., M. Sc.

Supervised by: Dr. Russell Duane & Dr. Zbigniew Olszewski

Tyndall National Institute

June 2016

"They don't think it be like it is, but it do"

- Oscar Charles Gamble

#### **ABSTRACT**

RF MEMS switches represent an attractive alternative technology to current mechanical (e.g. coaxial and waveguide) and solid-state (e.g. PIN diode and FET transistor) RF switch technologies. The materials and fabrication techniques used in MEMS manufacture enable mechanically moveable devices with high RF performance to be fabricated on a miniature scale. However, the operation of these devices is affected by several mechanical and electrical reliability concerns which limit device lifetimes and have so far prevented the widespread adoption and commercialisation of RF MEMS. While a significant amount of research and development on RF MEMS reliability has been performed in recent years, the degradation mechanisms responsible for these reliability concerns are still poorly understood. This is due to the multi-physical nature of MEMS switches where multiple mechanical and electrical degradation mechanisms can simultaneously affect device behaviour with no clear way of distinguishing between their individual effects. As such, little progress has been made in proposing solutions to these reliability concerns. While some RF MEMS switches have recently been commercialised, their success has come at the expense of decreased performance due to design changes necessarily imposed to prevent device failure. However, more high performance switches could be developed if the mechanisms responsible for reliability problems could be understood and solved.

The work of this thesis is focussed on the isolation and study of individual reliability mechanisms in RF MEMS capacitive switches. A bipolar hold-down technique is used to minimise the effects of dielectric charging and allow mechanical degradation to be studied in isolation in aluminium-based capacitive switches. An investigation of mechanical degradation leads to the identification of grain boundary sliding as the physical process responsible for the decreased mechanical performance of a switch. An alternative material for the switch movable electrode is investigated and shown to be mechanically robust.

The effects of dielectric charging are isolated from mechanical degradation using mechanically robust switches. The isolated investigation of dielectric charging leads to the identification of two major charging mechanisms which take place at the bulk and surface of the dielectric, respectively. The exchange of charge from interface traps is identified as the physical mechanism responsible for bulk dielectric charging. An investigation of surface dielectric charging reveals how this reliability concern depends on the structure and design of a switch. Finally, electrical and material means of minimising dielectric charging are investigated.

The findings and results presented in this thesis represent a significant contribution to the state-of-the-art understanding of RF MEMS capacitive switch reliability. By implementing the design changes and material solutions proposed in this work, the performance and lifetime of RF MEMS capacitive switches can be greatly improved.

### **ACKNOWLEDGEMENTS**

I would like to thank everyone I have encountered over the last 5 years of my life for all the fun, advice, help, guidance, support or distraction that you have provided. No matter how large or small your contribution may have been, it has led me to this point and to the achievement of this work and for that I am eternally grateful.

I owe a huge debt of gratitude to my supervisors Russell and Oskar without whom none of this would have been possible. They were always there to advise me, teach me or just be patient with me when times were tough and I have learned many invaluable lessons from them. Hugh thanks also to Ruth and Conor and the other members of the wider HSI group.

Thanks also to the lab manager Eoin Sheehan and all the staff from the Silicon and III-V fabrication facilities for providing me with such interesting devices to study over the years. I would especially like to thank Alan Blake for all his advice and expertise which were fundamental to this process.

I would also like to thank IT, Noel & Miriam in the canteen and the wider staff of Tyndall for keeping everything running so smoothly.

Thank you to Jim Greer and Orla Slattery for putting together the structured PhD programme, and to all of the lecturers and project partners who were involved along the way.

Thank you also to all of the friends I have made in Tyndall over the years. Specifically to the various members of the tea and lunch groups I have mingled with over the years, and to the ever-glorious Tyndall Taggers.

Finally I would like to thank my family. I really couldn't have done this without you. You are a constant source of love and support and you are the rock on which I stand. This thesis is dedicated to you.

This research has been conducted with the financial support of Science Foundation Ireland under grant number **SFI 10/RFP/ECE2883**. Additional contributions have also been made by the European Space Agency and for that I am grateful.

# **TABLE OF CONTENTS**

| Abstract                    |                                                                      | i   |

|-----------------------------|----------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENT             | S                                                                    | iii |

| TABLE OF CONTENTS.          |                                                                      | iv  |

|                             |                                                                      |     |

| CHAPTER 1 IN                | TRODUCTION                                                           | 1   |

| 1.1 WHAT ARE MEN            | 1S?                                                                  | 1   |

| 1.2 THESIS MOTIVAT          | ION                                                                  | 2   |

| 1.3 THESIS ORGANISA         | ATION                                                                | 3   |

|                             |                                                                      |     |

| CHAPTER 2 RF                | MEMS Switch Technology                                               | 5   |

| 2.1 Introduction            |                                                                      | 5   |

| 2.2 WHY RF MEMS             | Switches?                                                            | 5   |

| 2.3 RF MEMS TECH            | NOLOGY AT TYNDALL NATIONAL INSTITUTE                                 | 15  |

| 2.3.1 MEMS Fab              | prication                                                            | 17  |

| 2.3.2 Electrome             | chanical Model of Switch Operation                                   | 21  |

| 2.4 Introduction t          | O RF MEMS RELIABILITY AND RESEARCH AIMS                              | 25  |

| 2.5 SUMMARY                 |                                                                      | 28  |

|                             |                                                                      |     |

| CHAPTER 3 RF                | MEMS CAPACITIVE SWITCH RELIABILITY - THEORY AND RESEARCH STATUS      | 29  |

| 3.1 Introduction            |                                                                      | 29  |

| 3.2. CAPACITIVE SWI         | TCH FAILURE DURING HOLD-DOWN OPERATION                               | 30  |

| 3.2.1 C-V Shift E           | ffect due to Uniform Dielectric Charge                               | 31  |

| 3.2.2 C-V Narro             | wing Effect due to Non-Uniform Dielectric Charge                     | 42  |

| 3.2.3 C-V Narro             | wing Effect due to Mechanical Degradation                            | 48  |

| 3.3 Status of Rese <i>a</i> | ARCH ON THE ISOLATION OF DEGRADATION MECHANISMS IN RF MEMS CAPACITIV | /E  |

| SWITCHES                    |                                                                      | 51  |

| 3.3.1 Dielectric            | Charging Isolation Methods                                           | 51  |

| 3.3.2 Mech    | nanical Degradation Isolation Methods                              | 55        |

|---------------|--------------------------------------------------------------------|-----------|

| 3.4 PROBLEM S | STATEMENT AND RESEARCH AIMS                                        | 56        |

| 3.5 Summary   |                                                                    | 57        |

|               |                                                                    |           |

| CHAPTER 4     | MECHANICAL RELIABILITY                                             | 58        |

| 4.1 INTRODUCT | FION                                                               | 59        |

| 4.2 MEASUREN  | лент of Mechanical Degradation                                     | 60        |

| 4.2.1 The E   | Bipolar Hold-Down Stress Method                                    | 60        |

| 4.2.2 Expe    | rimental Validation of the Bipolar Hold-Down Method on Titanium Sw | itches 63 |

| 4.2.3 Chara   | acterisation of the Bipolar Hold-Down Method on Aluminium Switches | 567       |

| 4.3 CHARACTER | RISATION OF MECHANICAL DEGRADATION                                 | 75        |

| 4.3.1 The 0   | Creep Effect                                                       | 75        |

| 4.3.2 The \   | /iscoelastic Effect                                                | 80        |

| 4.3.3 Temp    | perature Acceleration of the Viscoelastic Effect                   | 82        |

| 4.4 MATERIAL  | SOLUTION TO MECHANICAL DEGRADATION                                 | 85        |

| 4.4.1 Devi    | ce Fabrication                                                     | 86        |

| 4.4.2 Devic   | ce Characterisation                                                | 86        |

| 4.5 SUMMARY   |                                                                    | 89        |

|               |                                                                    |           |

| CHAPTER 5     | DIELECTRIC CHARGING CHARACTERISATION                               | 89        |

| 5.1 INTRODUCT | FION                                                               | 90        |

| 5.2 PRELIMINA | ry Charging Characterisation                                       | 91        |

| 5.3 BULK CHAR | RGING CHARACTERISATION AT LOW ELECTRIC FIELDS                      | 94        |

| 5.3.1 Curre   | ent Transients in MIM Devices                                      | 98        |

| 5.4 MODELLING | G THE TRANSIENT SILC EFFECT IN RF MEMS CAPACITIVE SWITCHES         | 104       |

| 5.4.1 Mode    | el Derivation                                                      | 104       |

| 5.4.2 Mode    | el Verification                                                    | 107       |

| 5.5 SUMMARY   |                                                                    | 110       |

| CHAPTER 6        | INITIAL EXPERIMENTAL INVESTIGATION OF SURFACE CHARGING AI METHODS FOR BULK DIELECTRIC CHARGING | ND SOLUTION<br>110 |

|------------------|------------------------------------------------------------------------------------------------|--------------------|

| 6.1 Introduction | NC                                                                                             | 111                |

| 6.2 MEASUREME    | NT & ANALYSIS METHODS                                                                          | 112                |

| 6.3 TRANSIENT C  | CHARGING ANALYSIS                                                                              | 116                |

| 6.4 STEADY-STA   | TE CHARGING ANALYSIS                                                                           | 119                |

| 6.4.1 Test St    | ructure Design to Reduce Surface Charging                                                      | 121                |

| 6.4.2 Test St    | ructure Experimental Results and Analysis                                                      | 123                |

| 6.5 METHODS TO   | ) SOLVE BULK CHARGING                                                                          | 126                |

| 6.5.1 Therm      | al Annealing                                                                                   | 127                |

| 6.5.2 Modifi     | ed PECVD SiO <sub>2</sub> Recipe                                                               | 128                |

| 6.5.3 Native     | Oxide Test Structures                                                                          | 131                |

| 6.5.4 Electri    | cal Solution to Bulk Charging                                                                  | 136                |

| 6.6 SUMMARY      |                                                                                                | 137                |

|                  |                                                                                                |                    |

| CHAPTER 7        | CONCLUSIONS & FUTURE WORK                                                                      | 138                |

| 7.1 THESIS SUMI  | MARY                                                                                           | 139                |

| 7.2 CONCLUSION   | IS                                                                                             | 141                |

| 7.3 FUTURE WO    | RK                                                                                             | 144                |

|                  |                                                                                                |                    |

| APPENDIX A       | LIST OF PUBLICATIONS ARISING FROM THIS WORK                                                    | 145                |

|                  |                                                                                                |                    |

| Deserves         |                                                                                                | 4.47               |

| REFERENCES       |                                                                                                | 147                |

I, Cormac Ryan, certify that this thesis is my own work and I have not obtained a degree in this university or elsewhere on the basis of the work submitted herein.

Cormac Ryan

# **CHAPTER 1: Introduction**

#### 1.1 WHAT ARE MEMS?

The inspiration for Micro-Electro-Mechanical Systems or MEMS technology is said to have originated from the renowned physicist Richard Feynman who spoke about the possibilities of making small but moveable machines during his 1959 lecture entitled "There's plenty of room at the bottom". To encourage research into this area, he offered a prize of \$1000 to the first person who could successfully make a working electric motor measuring only 1/64 of an inch in size. This prize was claimed less than a year later and thus the age of micromachines was born. Research and development into the miniaturization of electronic components and movable machines continued throughout the following decades, with several examples of MEMS technologies demonstrating the viability of the emerging field.

In general, MEMS technology can be described as miniature mechanical structures (such as suspended bridges, beams, cantilevers or membranes) which are designed to sense or change some property of their immediate environment. The movement of these micronscale (1  $\mu$ m = 0.000001 m) mechanical components creates, or is caused by, an electrical signal. The sensing and actuation ability provided by these devices has many potential applications in widely-varying fields such as physics, optics, chemistry and biology. Many MEMS devices have achieved commercial success as the print heads in inkjet printers, accelerometers for airbag deployment in cars, as well as gyroscopes and inertial measurement units for mobile phone, tablet and video game interfaces.

Another area where MEMS technology is expected to find widespread use is in the field of radio-frequency (RF) communications. Modern smartphones and emerging tuneable devices require high-performance and low-loss reconfigurable resonant circuits to meet the growing demands of ubiquitous connectivity placed on device manufacturers by consumers and consumer applications. With their unique ability to integrate electronic components with three-dimensional movement, RF MEMS are poised as a key enabling technology for the realisation of virtually parasitic-free RF components and reconfigurable circuits. While several examples of RF MEMS-enabled tuneable components such as phase shifters, filters and impedance-matching networks have already been demonstrated, many challenges in the design and fabrication of RF MEMS remain to be overcome.

A device of particular interest to RF designers and engineers is an RF switch – a device which, as its name suggests, allows the transmission of a radio-frequency signal to be turned on or off. Conceptually this is a relatively simple device; it consists of two parallel metal plates, one of which can move with respect to the other. The position of these plates determines whether a signal can flow or is blocked. Signal transmission is achieved through ohmic (metal-metal) or capacitive (metal-dielectric-metal) contact between the plates. Their three-dimensional metal structure and mechanical movement combine to create RF switches with very low insertion loss and high isolation at microwave frequencies, while their fabrication methods are similar to those used in standard CMOS manufacturing and allow for high volume batch fabrication. Additionally, RF MEMS switches are small in size and weight and consume almost no power when they are operated using electrostatic actuation.

These advantageous properties allow RF MEMS switches to compete successfully with traditional electromechanical and semiconductor technologies and make them very suitable components for use in portable devices and wireless communications applications. Due to their outstanding commercial potential and high RF performance there is a significant amount of research being performed on MEMS switches amongst leading universities, research centres and semiconductor manufacturing companies including Lehigh University, IMEC, Robert Bosch, ST-Microelectronics, Texas Instruments and Hewlett Packard. Significantly, RF MEMS ohmic and capacitive switches have recently been commercialised by Analog Devices, WiSpry Inc. and Cavendish Kinetics.

#### 1.2 THESIS MOTIVATION

While some examples of RF MEMS ohmic and capacitive switches have successfully been commercialised, the widespread adoption of this technology is stymied by several on-going reliability concerns which threaten the long-term operation of these devices. The operation of these switches is determined by the interaction of several fundamental electronic and mechanical forces which can be influenced by many detrimental mechanisms. Mechanical degradation of the moveable components can change the operational parameters of a switch over time, while the accumulation of charge in the dielectric layer of a capacitive switch can affect the forces acting on a device and cause it to fail in the ON or OFF state. While the successful commercialisation of ohmic switches suggests that mechanical concerns have been solved, capacitive switches have only achieved commercial success by removing or restricting contact with the dielectric layer — a key component which

determines the high RF performance of a switch. As such, the high RF performance of these devices has been sacrificed in exchange for more reliable operation and therefore more research and development is required before the full potential of RF MEMS capacitive switches can be unlocked.

This thesis investigates the mechanical and electrical reliability concerns of RF MEMS capacitive switches by investigating the fundamental physical mechanisms responsible for these effects. The major goal of this work is to contribute to the state-of-the-art understanding and improvement of RF MEMS reliability. This work is performed solely on devices fabricated at Tyndall National Institute; however, it is envisioned that the experimental methodology, physical understanding and solutions developed herein can be applied to other RF MEMS technologies across the wider field of research.

#### 1.3 THESIS ORGANISATION

This chapter briefly introduces MEMS technology and describes the motivation behind this research. The rest of the thesis is organised as follows:

**Chapter 2** introduces RF MEMS ohmic and capacitive switches and highlights their attractive properties by comparison with existing commercial RF switches. The fabrication process and theory of operation of capacitive switches is described in detail and their main reliability issues are briefly introduced.

**Chapter 3** describes the effects of mechanical degradation and dielectric charging on the operational characteristics of a capacitive switch. A review of the current research status and understanding of degradation mechanisms in RF MEMS capacitive switches during hold-down operation is provided and the main goals and research methodology of this work are defined.

**Chapter 4** presents the results of an experimental investigation into mechanical degradation in RF MEMS capacitive switches. This investigation is performed using an electrical test method which minimises the effects of dielectric charging during device operation. Experimental results which validate this method are presented, and the physical processes of mechanical degradation in RF MEMS capacitive switches are identified. The characterisation of a material solution to the problem of mechanical degradation is also described.

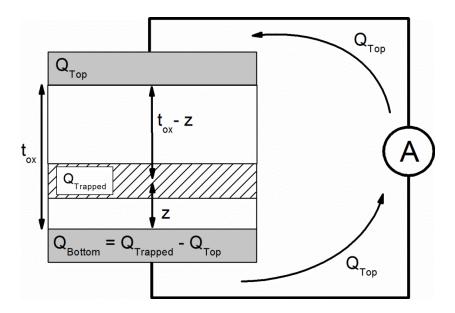

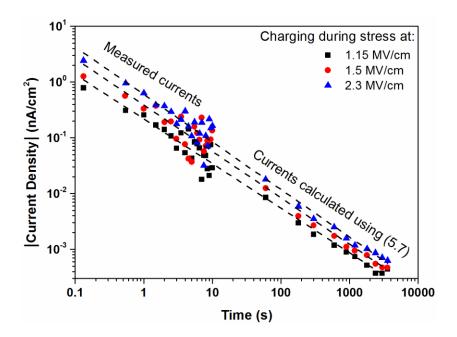

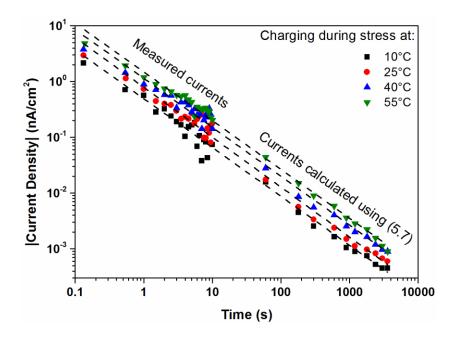

Chapter 5 describes the results of an experimental investigation into dielectric charging in RF MEMS capacitive switches. Fixed metal-insulator-metal devices are used to measure the charging and discharging currents across metal/dielectric interfaces and the knowledge gained by studying these currents is used to create a simple 1D model of dielectric charging in RF MEMS capacitive switches. Experimental verification of this model is provided and the physical process of bulk dielectric charging is identified.

**Chapter 6** describes the measurement and analysis of dielectric charging at high electric fields in RF MEMS capacitive switches. Different capacitive switch test structures are used to identify the sources of surface charging at high electric fields, while a more limiting reliability concern is linked to the mechanism of bulk dielectric charging identified in Chapter 5. A novel material solution is proposed to eliminate this process and improve the reliability of RF MEMS capacitive switches.

Finally, **Chapter 7** reviews the main results achieved during this work, summarises their contribution to the state-of-the-art understanding of RF MEMS reliability and suggests some possible directions for future work.

# **CHAPTER 2:**

# RF MEMS SWITCH TECHNOLOGY

#### 2.1 Introduction

A brief introduction to RF MEMS and the motivation behind this research was given in Chapter 1. This chapter provides a more detailed description of RF MEMS switch technology and is organised as follows. Section 2.2 describes the motivation for research into RF MEMS capacitive switches by comparing their performance with the alternative RF switches which are commercially-available today. RF MEMS capacitive switches have the potential to be the highest-performing RF switches; however, more work is required to improve their reliability before they can be commercialised. Following this, the RF MEMS capacitive switches which are studied in this thesis are described in detail in Section 2.3. A step-by-step description of their fabrication methods is presented, before the physics behind their principle of operation is used to derive the equations for the pull-in and pull-out voltage — two parameters which will be studied extensively throughout this work. Finally, the subject of RF MEMS reliability is introduced in Section 2.4 before the chapter concludes in Section 2.5.

#### 2.2 WHY RF MEMS SWITCHES?

The term Radio Frequency (RF) is used to describe microwave signals with frequencies in the range of 3 kHz to 300 GHz which are used in a broad spectrum of radio communication applications. One of the highest volume RF device types in use today are switches which can control the flow of RF signals along transmission paths. Typical microwave applications include wireless communication systems (e.g. mobile phones), navigation systems (e.g. Global Positioning System – GPS), test equipment (e.g. Vector Network Analyser – VNA) and many others. Many varieties of RF switches are commercially available and can be divided into three main categories;

- 1. electromechanical relays,

- 2. solid-state switches,

- 3. Micro-Electro-Mechanical-Systems (MEMS) switches.

Electromechanical relays are widely used in the fields of test equipment or space communication where high performance is an important requirement, while smaller, faster and more reliable solid-state switches find use in consumer electronics such as mobile phones. The third RF switch technology, MEMS, combines the excellent RF performance of traditional electromechanical relays with the small size and integration capability of solid-state devices [1]. For many years RF MEMS switches were considered to be an emerging technology; however, their recent commercialisation by several companies has proven their maturity and applicability in several RF applications [2-4]. A brief description of each technology is given below.

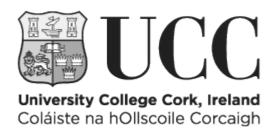

Electromechanical relays such as coaxial and waveguide switches are mechanical switches which physically close or open an electrical circuit to control the propagation of a RF signal. In the ON-state, the signal flows through the device while in the OFF-state the signal is blocked. A simplified schematic of an electromechanical relay along with an actual device is shown in Figure 2.1 (a) and 2.1 (b), respectively. Four different elements are incorporated into the design of an electromechanical switch; an electromagnet, a moveable armature, a spring and a set of electrical contacts. When a current flows along the coiled wire in the figure, electromagnetic induction in the solenoid causes the armature to move into the closed position under the influence of an induced magnetic field. When the solenoid current is turned off, the magnetic field vanishes and the armature returns to the open position under the restoring force of the spring.

Figure 2.1: Schematic drawing of an electromechanical relay (a) and an actual electromechanical RF switch [5] next to a US 10 cent coin for comparison (b).

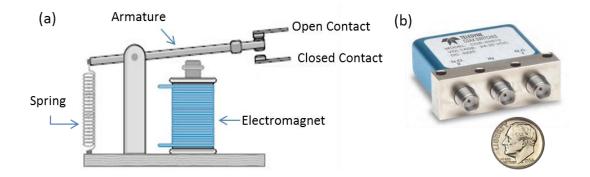

An alternative switching technology exists in the form of solid-state RF switches. One example of a commonly-used solid-state switch is the PIN diode which is drawn schematically in Figure 2.2 [6]. Solid-state switches can also be created using field-effect transistors (FETs); however, for brevity only the PIN diode is discussed here. A PIN diode is

made from a layer of intrinsic semiconductor with very high resistivity that is sandwiched between a layer of highly doped p-type semiconductor and a layer of highly doped n-type semiconductor. A schematic device is shown in Figure 2.2 (a). Under reverse bias conditions the intrinsic layer is depleted of charges and the device exhibits high resistance (the device is in the OFF-state). When the diode is forward biased, positive charges from the p-type region and negative charges from the n-type region are injected in to the intrinsic layer which results in lowering the device resistance (the device is in the ON-state). The circuit diagrams and equivalent circuits of a PIN diode in the OFF and ON state are shown in Figure 2.2 (b) [6].

Figure 2.2: Schematic view of a solid-state PIN diode (a). Circuit diagrams and the equivalent circuits of a PIN diode under reverse-biased (OFF) and forward-biased (ON) conditions (b).

One of the most common performance specifications of RF switches is the ON-state resistance. Electromechanical relays typically have the lowest ON-state resistance due to the metal-based contact used in these devices. For example, values in the range of tens of  $m\Omega$  are common for electromechanical switches, while solid-state devices with semiconductor-based switching have an ON-state resistance in the range of hundreds of  $m\Omega$ . In RF switches, the ON-state resistance is encapsulated in the term "insertion loss" which is expressed in decibels and which is a measure of the power lost by a microwave signal as it flows through a device [7]. Lower levels of insertion loss mean that less signal power is lost during transmission and this can be achieved by minimizing the ON-state resistance of a switch.

Another important performance specification of RF switches is the amount of power lost by a signal through unwanted transmission in the OFF-state. Solid-state switches minimise unwanted losses by maximising the resistance of the intrinsic layer during the OFF-state. However, parasitic capacitive coupling can result in signal leakage through this layer [8]. The amount of signal power lost through an electromechanical switch is extremely low due to the physical separation between the switch contacts in the OFF-state. However, capacitive coupling across the air gap can result in parasitic signal losses, especially as the frequency of the signal increases. In RF switches the property of a device which determines signal loss in the OFF-state is called "isolation" and is measured in decibels. A higher isolation means that less signal flows through the switch when it is in the OFF-state and this can be achieved by maximising the OFF-state resistance or minimising the OFF-state capacitance.

In summary, the advantages of electromechanical relays over solid-state switches are that they provide better RF characteristics over a wider frequency range, with lower insertion loss due to metal contact and higher isolation levels due to air-gap separation [9]. However, the lack of moving parts in a solid-state switch leads to faster switching speeds (µs vs. ms) and improved long-term reliability with more consistent RF performance as the switch contacts do not degrade over time. Additionally, solid-state switches can be manufactured more cost effectively than electromechanical relays using high-volume semiconductor-based processes which also result in much smaller devices than bulky electromechanical relays (mm³ vs. cm³). Therefore, electromechanical relays are most often used in low volume applications with high-performance RF specifications where the cost and size of the equipment is not a primary concern.

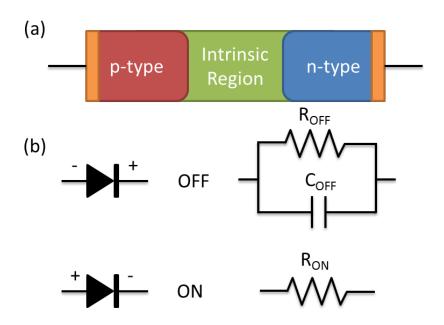

The third RF switching technology is MEMS and a simplified diagram of a MEMS switch with a metal to metal (ohmic) contact is shown in Figure 2.3 (a). MEMS ohmic switches operate on the same principle as electromechanical relays; an electrical stimulus causes movement of a metal armature which closes or opens the circuit, thereby allowing or preventing the transmission of a RF signal. However, unlike traditional electromechanical relays, the movement of a MEMS switch armature is most often accomplished using electrostatic actuation which will be described in Section 2.3.2.

Figure 2.3: Schematic drawing of a MEMS ohmic switch in the OFF-state (a) and in the ON-state (b). A packaged die containing 400 MEMS ohmic switches placed on top of a US 10 cent coin for comparison, courtesy of General Electric (c).

RF MEMS switches are fabricated using surface micromachining and lithography techniques which are similar to those used in the fabrication of solid-state devices [10]. MEMS processing involves the deposition, patterning and etching of individual material layers to create micron-scale freestanding mechanical structures. The fabrication steps used in the creation of MEMS devices are discussed in detail in Section 2.3.1. The use of metal contacts and the physical separation between the switch electrodes means that the insertion loss and isolation of MEMS switches are comparable to traditional electromechanical switches, while the small size and weight of MEMS devices is an advantageous property derived from the use of solid-state manufacturing techniques [11]. A comparison between the properties of RF MEMS ohmic switches, electromechanical relays and PIN diodes is shown in the following table. Further details can be found in [12].

Table 2.1: A comparison between the physical and RF properties of three different RF switch technologies.

| Property          | Electromechanical | PIN Diode  | MEMS Ohmic       |

|-------------------|-------------------|------------|------------------|

|                   | Relay [5, 13]     | [14]       | Switch [4, 15]   |

| Insertion Loss    | Low               | Medium     | Low              |

| Isolation         | High              | Low        | Medium           |

| ON Resistance     | Low               | High       | Medium           |

| Signal Range      | DC – 40 GHz       | DC – 3 GHz | DC – 11 GHz      |

| Switching Speed   | Slow              | Very Fast  | Fast             |

| Size              | Large             | Small      | Small            |

| Weight            | Heavy             | Light      | Light            |

| Cost per unit     | \$100-1000        | \$0.08     | \$10-100 desired |

| Lifetime (Cycles) | 10 Million        | Billions   | 5 Billion        |

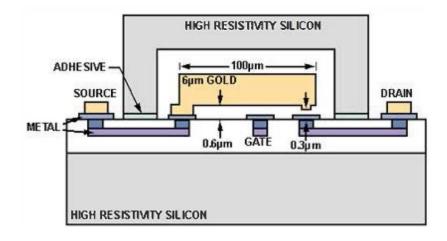

By comparison with existing RF switch technologies it can be seen that RF MEMS are a very attractive alternative to traditional electromechanical and solid-state switches. A significant amount of research and development has been performed on MEMS devices and has culminated in the recent commercialisation of an ohmic switch by Analog devices [4, 15]. A diagram of this switch is shown in Figure 2.4. The device is constructed from a surface micromachined gold cantilever which is suspended 0.6 µm above the actuation (gate) electrode. Despite the small air-gap, the switch requires an actuation voltage of 80 V which is supplied by a co-packaged application specific integrated circuit (ASIC). Electrostatic actuation of the cantilever is achieved by applying the voltage between the beam and the gate electrode, and further details of this actuation mechanism are given in Section 2.3.2. The high actuation voltage and the use of a platinum group metal in the contact areas provide the switch with a low ON-state resistance of 1.5  $\Omega$ . Once the devices have been fabricated they are hermetically sealed using a wafer capping process to improve the switch reliability and lifetime. A discussion of RF MEMS reliability is given in Section 2.4. Targeted application areas include RF instrumentation such as switching matrices and vector network analysers where wide bandwidth, low loss switching is required.

Figure 2.4: Diagram of the commercial ohmic switch from Analog devices [4].

#### RF MEMS Capacitive Switches (Variable Capacitors)

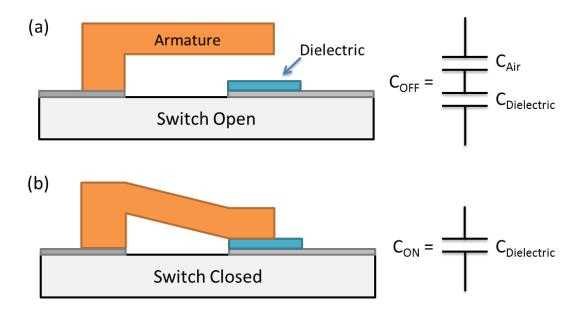

Another type of RF MEMS switch operates by changing the capacitance of a transmission line and this is known as a capacitive switch or a digital variable capacitor (varactor). A schematic diagram of a capacitive switch with simplified circuit models is shown in Figure 2.5. In general, capacitive switches are very similar in design and operation to ohmic switches. The mechanical principle of operation is the same in both devices whereby the moving electrode lies in one of two available positions that define the switch ON or OFF state. However, capacitive switches incorporate a dielectric layer between the moveable metal and contact electrode so that a metal-insulator-metal structure is formed after switch actuation. The dielectric layer prevents any DC signal from passing through the switch, but allows low-loss switching of high-frequency signals to be performed [11]. As such, capacitive switches and varactors are expected to find use in different applications to ohmic switches where capacitance changes are required to tune RF signals in wireless and satellite communications systems, as well as high-frequency instrumentation and radar applications [16]. Further details on capacitive switches can be found in Section 2.3.

Figure 2.5: Schematic drawing of a RF MEMS capacitive switch in the OFF-state (a) and in the ON-state (b). Simplified circuit models are provided to the right of the figure.

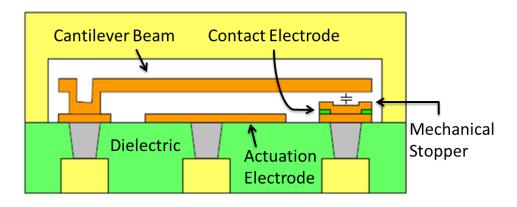

RF MEMS capacitive switches for mobile phone applications have recently been released by WiSpry [17] and Cavendish Kinetics [18]. A diagram of the capacitive switch from Cavendish is shown in Figure 2.6. The switch is made from a bulk micromachined metal cantilever which is fully integrated within the back-end of a CMOS fabrication process. Electrostatic actuation is used to control the switch; a voltage applied between the beam and a central actuation electrode causes the cantilever to deflect and change the capacitance of the switch. However, mechanical stoppers at the contact electrode prevent the complete closure of the switch such that the variable capacitance is determined by the size of the airgap between the cantilever and the contact electrode. Therefore, this is an air-based variable capacitor.

Figure 2.6: Graphical representations of the air-based capacitive switch by Cavendish Kinetics [2].

The commercial product offered by Cavendish Kinetics features arrays of these capacitive switches which can provide a high-resolution digitally-controlled variable capacitance [19]. These capacitive tuners are currently in use in several smartphones including the ZTE Nubia Z9 [20]. The capacitive switch from WiSpry is targeted at similar applications in the tuneable RF front-end market [3].

Variable capacitors can also be fabricated using different technologies such as ferroelectric varactors [21] or by placing low-loss switches in series with fixed capacitors (switched passives) [1]. For example, low-loss semiconductor switches using PIN diodes can be used to connect or disconnect arrays of fixed capacitors to achieve a digitally-controlled variable capacitance. Ferroelectric materials such as barium-strontium-titanate (BST) are used to linearly tune a capacitance over a small range by changing the electric permittivity as a function of the applied electric field [22]. A figure of merit recently defined by WiSpry [3] allows different capacitor technologies to be compared based on their performance metrics. This figure of merit is given as

$$FOM = \frac{1}{C_{on}R_{on}} \times \frac{C_{on}}{C_{off}} \times \frac{C_{on}}{Area} \times V_{rms}^{2},$$

(2.1)

where a high FOM is associated with high performance. The first term on the right hand side of equation (2.1) represents the Q-factor of a device which indicates the performance of a switch in terms of signal losses. For a given on-state capacitance  $C_{on}$ , the value of Q can be maximised by minimising the value of  $R_{on}$ . The second term on the right hand side of equation (2.1) is the capacitance ratio of the device. Again for a given  $C_{on}$  this value can be maximised by minimising  $C_{off}$ , where a low  $C_{off}$  contributes to high isolation, while a high  $C_{on}$  is essential to create a low-impedance path for the RF signal. Thus, the capacitance ratio of a device also represents the performance of a switch in terms of signal losses; however, a trade-off exists between maximising the Q-factor and capacitance ratio of a device. The third term in equation (2.1) represents the capacitance density of a device, or the cost of achieving a certain tuning range in terms of overall die area. The final  $V_{rms}^2$  term represents the power-handling ability of a tuneable capacitor. Detailed comparisons of several different tuneable capacitor technologies can be found in [1, 3, 21] and these are summarised in the following table.

Table 2.2: Tuneable capacitor technology comparison, adapted from [1, 3, 21].

| Technology            | MEMS              | BST                  | Silicon on Insulator |

|-----------------------|-------------------|----------------------|----------------------|

| Implementation        | Digital Capacitor | Analog Variable Cap. | Switched Passives    |

| Cap. Ratio            | 2-100             | 2-3                  | 3-5                  |

| Q-Factor              | 50-400            | 30-150               | 30-150               |

| Linearity, IIP3 (dBm) | >60               | 10-35                | 10-35                |

| FOM                   | 100+              | <10                  | 10+                  |

An additional parameter which is important for the comparison of tuneable capacitors is the linearity of a device. Very linear devices create almost no distortion of an RF signal as it passes through, while intermodulation products generated in nonlinear devices can corrupt the transmitted signal. The three-dimensional design of RF MEMS digital capacitors contributes to the very high linearity reported in Table 2.1, as the ON-state capacitance of the MEMS switch does not vary with voltage, while the low mechanical resonant frequency of the moveable component cannot physically react to the passage of a high-frequency signal and creates no distortion [23]. Modern BST and semiconductor-based varactors are also very linear devices; however, their voltage-dependent capacitance leads to a lower linearity than MEMS switches [21].

In conclusion, it can be stated that high-performance capacitive tuners are devices with a low series resistance, a high tuning range and high linearity. The freedom of design of RF MEMS capacitive switches allows each of these criteria to be fulfilled [11] and results in the largest figure of merit of the different technologies described in Table 2.2. By examining equation (2.1), it can be seen that the figure of merit of a RF MEMS capacitive switch can be maximised by increasing the on-state capacitance of a device. This can be achieved through intimate contact between the RF electrode and a dielectric layer in the ON-state. Thus, the intermetal dielectric layer is an essential component for the realisation of high-performance RF MEMS capacitive switches. However, the commercial devices which have been released to-date avoid the use of intermetal dielectric layers in favour of air-based capacitive tuning (as employed by Cavendish Kinetics [19]) or else use mechanical stoppers to prevent intimate contact between the moveable metal and dielectric (as used by WiSpry [17]). The reason for this deliberate decrease in on-state capacitance and RF performance is due to the accumulation of charge in the dielectric layer of a capacitive switch during

operation which poses a significant threat to the reliability and lifetime of these devices [24-33].

In addition to the decreased performance caused by the lack of an intermetal dielectric in RF MEMS capacitive switches and varactors, the switch lifetime during hold-down operation has not been published for the majority of commercial devices. This is a key performance indicator for a number of applications such as redundancy switches for satellites and test instrumentation which are required to maintain their electromechanical performance and guarantee switch actuation after 10 years [34]. While the ohmic and capacitive switches commercialised by Analog Devices and Cavendish Kinetics have demonstrated cycling lifetimes of over 1 billion cycles [4, 19], only Analog Devices have reported an estimated hold-down lifetime for their ohmic switch of 7.2 years [4]. However, this is below the hold-down lifetime of 10 years or more which is required for commercial and military applications [34].

Improving the poor hold-down reliability of RF MEMS switches is hampered by a lack of understanding of the failure modes of a switch during down-state operation, even for commercial devices which have removed the intermetal dielectric layer for improved reliability. Therefore, the goal of this work is to develop an in-depth understanding of the failure modes of dielectric-based RF MEMS capacitive switches during hold-down operation. This work is performed using capacitive switches which were specifically designed at Tyndall National Institute to investigate the impact of the intermetal dielectric degradation and charging on switch performance. A description of this technology along with details of its fabrication and physics of operation is given in the next section. A discussion of the reliability concerns of RF MEMS capacitive switches during hold-down operation is given in Chapter 3; while more a more general introduction to the area of RF MEMS reliability is given in Section 2.4.

#### 2.3 RF MEMS TECHNOLOGY AT TYNDALL NATIONAL INSTITUTE

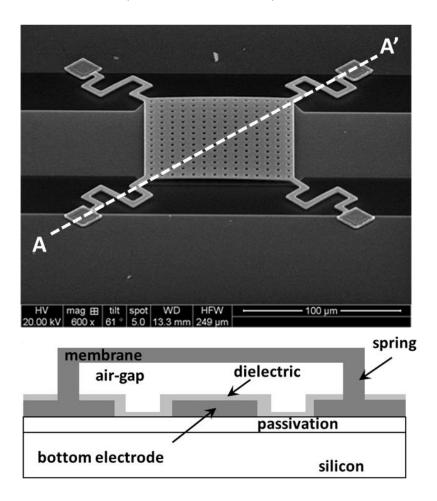

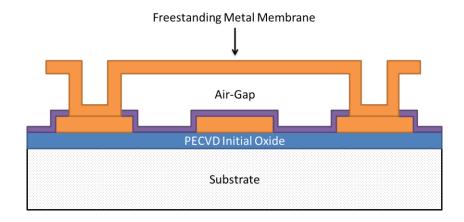

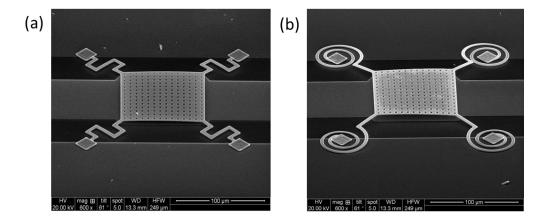

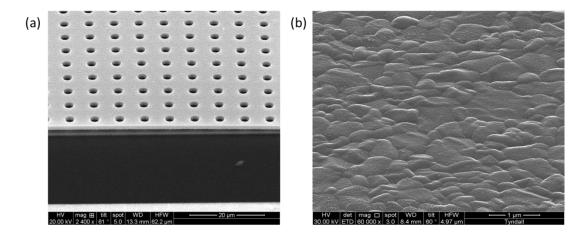

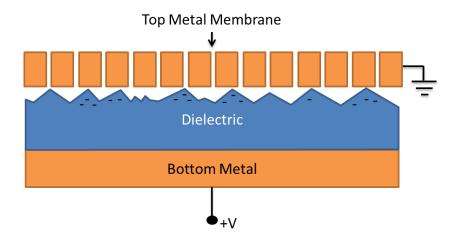

A scanning electron microscope (SEM) image and cross-section of a typical RF MEMS capacitive switch fabricated in Tyndall are shown in Figure 2.6. The switch consists of a moveable metal membrane which is suspended by four supporting tethers over the central line of a co-planar waveguide (CPW) structure. The membrane measures  $100x100 \, \mu m^2$  and is composed of 1  $\mu$ m thick aluminium. Holes of  $2x2 \, \mu$ m are incorporated into the membrane to reduce gas damping effects [11] and to aid in sacrificial layer removal (see

next section). The membrane is suspended approximately 2.5-3  $\mu$ m into the air. A voltage applied between the membrane and the central line of CPW causes the switch to close forming a metal-dielectric-metal structure. The typical measured actuation voltage of such a device lies in the range of 10-25 V depending on the size of the air gap and the tether design used. The CPW line is designed to have an impedance of 50  $\Omega$ , and the bottom metal used to define the CPW is 0.5  $\mu$ m thick aluminium alloyed with 1% silicon (Al/1%Si).

Figure 2.7: SEM image and cross-section of a capacitive switch with meander tethers fabricated at Tyndall. The cross-section is measured along the line A-A' as shown in the SEM image.

A dielectric layer of 130 nm is deposited on top of the CPW. This layer is present on the switch featured in Figure 2.7, but is transparent in the SEM image. The dielectric used is typically silicon dioxide ( $SiO_2$ ) with a relative permittivity of 3.9. When the switch is open this arrangement results in an up-state capacitance  $C_{UP}$  of approximately 50 fF. The theoretical down-state capacitance  $C_{DOWN}$  is 2.66 pF when calculated using the model of an ideal metal-dielectric-metal capacitor; however, poor contact between the movable membrane and the top surface of the dielectric results in a considerably reduced down-state capacitance. Measured  $C_{DOWN}$  values of  $100x100~\mu m^2$  devices vary between

300-900 fF depending on the extent of the bottom electrode roughness. The basic steps used to create these structures are outlined in the following section.

#### 2.3.1 MEMS Fabrication

The MEMS devices used in this work are fabricated using a technique known as surface micromachining [10]. This process involves the deposition and selective etching of individual material layers to create functional devices. The process used in Tyndall National Institute has been developed to be CMOS-compatible so that MEMS devices can be incorporated on top of completed CMOS wafers without having to remove the wafers from the clean room.

The fabrication steps necessary to create Tyndall MEMS technology are described in the following order; preparation of the substrate and bottom metal definition, dielectric passivation, sacrificial layer deposition, top metal definition and finally sacrificial layer removal.

#### **Substrate Preparation**

The default substrates used in this work are low resistivity P-type silicon wafers. Prior to switch fabrication, the wafers are cleaned and an initial layer of 500 nm  $SiO_2$  is deposited by Plasma-Enhanced Chemical Vapour Deposition (PECVD). This oxide layer is deposited to electrically isolate the finished MEMS devices from the substrate material.

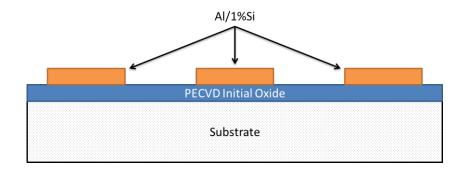

Following this, a layer of Al/1%Si sputtered on top of the initial oxide to a thickness of  $0.5~\mu m$ . The Al/1%Si layer is patterned and etched to define the bottom metal electrodes of the MEMS switches which in this case form a CPW structure. At this point, the wafers are ready for dielectric deposition and a wafer at this stage of device fabrication in pictured in Figure 2.8.

Figure 2.8: Schematic representation of the first three layers of a fabricated device.

#### **Dielectric Passivation**

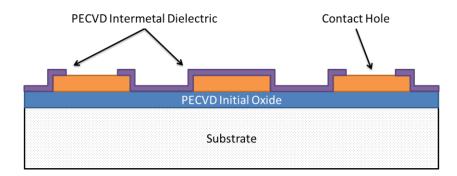

The typical dielectric used in this work is PECVD  $SiO_2$  deposited to a thickness of approximately 130 nm. Other dielectrics which may also be used include PECVD silicon nitride (SiN) and aluminium oxide ( $Al_2O_3$ ) deposited by an alternative technique called atomic layer deposition (ALD). After deposition the oxide is patterned by exposing and selectively developing a layer of photoresist, as before. The dielectric is removed over regions where the switch membrane will be electrically connected to the CPW, and also from other regions of the CPW for device probing and wire-bonding purposes. A schematic representation of a device after this stage of the process is shown in Figure 2.9.

Figure 2.9: Cross-section of a device after the intermetal dielectric has been deposited and etched.

#### Sacrificial Layer Deposition

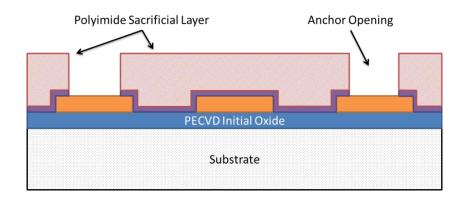

The sacrificial layer is a fundamental step in surface micromachining as it allows three-dimensional freestanding structures to be defined. In this case the sacrificial layer is formed using a polymer material known as polyimide (PI 2545). The polyimide is deposited onto a wafer by spin-coating to a thickness of approximately 3  $\mu$ m before it is cured in an oven to solidify. The polyimide is patterned using photoresist exposition and development steps, before it is etched using oxygen plasma to define openings for the supporting anchors of the switch membrane. This stage of the fabrication process is shown in Figure 2.10.

Figure 2.10: Schematic drawing of a device after the polyimide deposition and patterning process.

The final thickness of the polyimide layer after etching and resist removal is in the range of  $2.5-3~\mu m$ . The thickness of this layer is critically important in MEMS fabrication as it defines the height of the device air-gap and hence the operational characteristics of a finished switch. Any roughness or inhomogeneity of the top surface of the polyimide may also negatively affect the topography of the top metal in the next fabrication step.

### **Top Metal Definition**

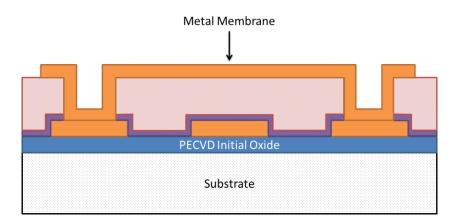

Once the polyimide has been appropriately prepared the top metal is deposited using an RF sputter technique. Different metal targets may be used in the sputtering process to deposit various materials. Examples of metals used in the Tyndall process include aluminium and titanium. The metal deposition is performed at room temperature to minimize the creation of residual stress in the membrane. The switches used in this work have all been fabricated with a top metal thickness of 1  $\mu$ m. After deposition, the top metal is patterned and etched to form the primary structural layers of the MEMS switches. A cross-section of a device after top metal deposition and etching is shown in Figure 2.11.

Figure 2.11: Cross-section of a device after deposition and patterning of the top metal.

#### Sacrificial Layer Removal

The release etch of the polyimide sacrificial layer is the final step in MEMS fabrication. This is achieved by placing the wafer into an oxygen plasma system at room temperature, where the polyimide is gradually removed during repeated etching cycles. Once the sacrificial layer has been completely removed the top metal is able to move freely and is only suspended by the four supporting tethers. A cross-section of a fully-processed capacitive switch is shown in Figure 2.12.

Figure 2.12: Schematic cross-section of a fully-processed capacitive switch after sacrificial layer removal.

The schematic drawings featured in the previous images are simplified descriptions of the capacitive switches which are useful for describing particular features of device design or operation. However, all capacitive switches used in this work are suspended on four springs similar to the device shown in Figure 2.7. Variations in device design include the use of different supporting tethers to alter the spring constant and operational parameters of a switch. The following images show close-up details of fully-processed capacitive switches captured using a scanning electron microscope.

Figure 2.13: SEM images of fully-processed capacitive MEMS switches. A meander-type switch over a CPW (a) and a spiral-type switch over a CPW (b).

## 2.3.2 Electromechanical Model of Switch Operation

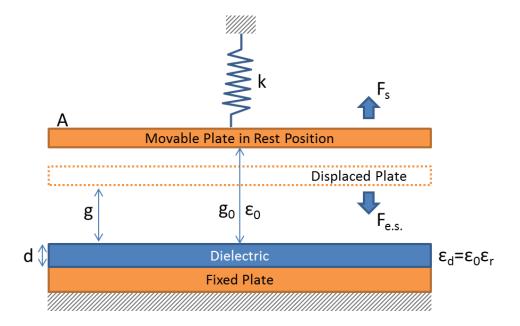

A simple one-dimensional model of a capacitive switch is shown in Figure 2.14.

Figure 2.14: Simple 1D model of an RF MEMS capacitive switch.

In this model, the movable membrane of a capacitive switch is represented by a rigid metal plate of area A which is suspended from a fixed point by a linear spring. The representation of the moveable membrane as a rigid plate is justified by simulation results which revealed that the majority of bending takes place in the supporting tethers while the membrane remains relatively flat throughout device actuation [35]. The linear spring has an effective spring constant k which is used in lieu of the four supporting tethers and accounts for the bending and stretching of deformed beams [11]. The movable metal plate is positioned directly over a fixed metal plate with a dielectric on top such that the structure forms a parallel-plate capacitor with capacitance given by

$$C = \frac{\varepsilon_0 A}{g + \frac{d}{\varepsilon_r}},$$

(2.2)

where g is the distance between the metal plates,  $\varepsilon_0$  is the permittivity of air, and d &  $\varepsilon_r$  are the thickness and relative dielectric constant of the dielectric layer. Equation (2.2) results from a series combination of the air and dielectric capacitances. When a voltage is applied between the two metals, an attractive electrostatic force is generated which attempts to bring the top moveable metal into contact with the bottom dielectric. The magnitude of this attractive force is given by

$$F_{e.s.} = \frac{1}{2} \frac{dC}{dg} V^2 = -\frac{1}{2} \frac{\varepsilon_0 A V^2}{\left(g + \frac{d}{\varepsilon_c}\right)^2},$$

(2.3)

where V is the applied voltage and (2.2) has been differentiated to obtain  $\dfrac{dC}{dg}$  . When a

voltage is applied to the switch, the induced attractive electrostatic force must compete with the restoring force generated by the spring as it is stretched beyond its rest position. The magnitude of this restoring force is given by Hooke's law as

$$F_{s} = -k(g_{0} - g), \tag{2.4}$$

where  $g_0$  is the size of the air-gap when no voltage is applied. As the applied voltage is increased and the distance g between the metals varies, the magnitudes of the electrostatic and restoring forces also vary. The electrostatic force increases as  $\frac{1}{g^2}$  while the restoring force increases linearly with g so that eventually a point is reached where the attractive electrostatic force overcomes the restoring spring force and the top membrane moves into contact with the dielectric layer.

The applied voltage needed to close the switch is known as the actuation or pull-in voltage,  $V_{Pl}$ . An expression for this voltage can be obtained by forming a force balance equation using equations (2.3) and (2.4)

$$\frac{1}{2} \frac{\varepsilon_0 A V^2}{\left(g + \frac{d}{\varepsilon_s}\right)^2} = k \left(g_0 - g\right),\tag{2.5}$$

and rearranging the resulting expression to generate the following equation (2.6)

$$V = \sqrt{\frac{2k}{\varepsilon_0 A} \left(g_0 - g\right) \left(g + \frac{d}{\varepsilon_r}\right)^2} \ . \tag{2.6}$$

By differentiating (2.6) with respect to g and solving the resulting expression when  $\frac{dV}{dg} = 0$  it is found that the critical point of the force balance equation occurs when the membrane has been deflected by approximately 1/3 of the original air-gap [36]. Inserting this value into (2.6) yields the following expression for the pull-in voltage

$$V_{PI} = \sqrt{\frac{8k}{27\varepsilon_0 A} \left(g_0 + \frac{d}{\varepsilon_r}\right)^3} . \tag{2.7}$$

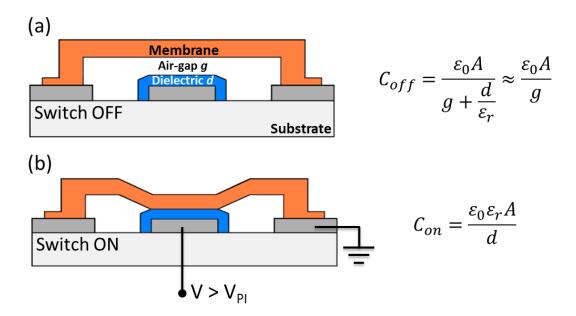

A schematic drawing of a capacitive switch in the OFF- and ON-state is shown in Figure 2.15, where a voltage greater than the pull-in voltage has been applied to the bottom metal.

Figure 2.15: Schematic drawing of a RF MEMS capacitive switch in the off-state with no bias applied (a) and in the on-state when a voltage greater than the pull-in voltage has been applied to the bottom metal (b). Expressions for the OFF and ON state capacitances are provided to the right of the figure.

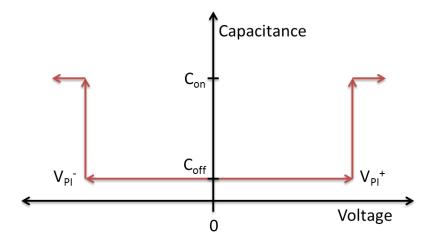

On a capacitance-voltage graph the pull-in phenomenon can be identified as a sudden increase in the value of the capacitance as the voltage is increased and the membrane moves from the up-state (i.e. air-based capacitance) to the down-state (i.e. dielectric-based capacitance). Since the electrostatic force is attractive regardless of whether a positive or negative voltage has been used, the pull-in point should be symmetrical about the zero volt mark. A representation of an ideal capacitance voltage (C-V) curve is shown in Figure 2.16.

Figure 2.16: An idealised C-V curve of a MEMS capacitive switch. The evolution of the capacitance as the membrane moves from the up-state to the down-state is indicated with red arrows. In reality the off-state capacitance would not be constant but would increase slightly as the voltage approached the pull-in point.

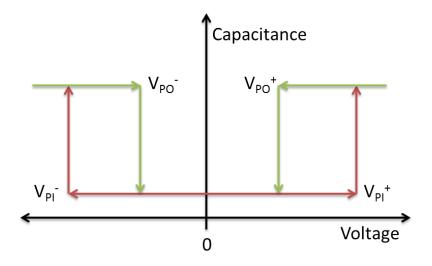

The membrane will stay in the down-state as long as a sufficiently high voltage is applied to the device. However, the magnitude of the electrostatic force in the down-state is significantly higher than in the up-state because the distance between the electrodes is now equal to the oxide thickness. Therefore, the membrane will remain in the down-state even if the voltage is reduced below the  $V_{\text{Pl}}$ . As the voltage is lowered further the magnitude of the electrostatic force decreases until the restoring spring force is greater than the attractive electrostatic force and the switch re-opens. The point at which this occurs is known as the pull-out point and the corresponding voltage is known as the pull-out voltage,  $V_{\text{PO}}$ . The difference between the pull-in and pull-out voltage results in a distinctive hysteresis of the C-V curve, as shown for an ideal capacitive switch in Figure 2.17.

Figure 2.17: Full C-V curve of an ideal MEMS capacitive switch, showing the hysteresis between the pull-in and pull-out voltages. The evolution of the pull-out phenomenon is indicated with green arrows.

An expression for the pull-out voltage can be found by setting g=0 in equation (2.6). Solving for V results in the following expression

$$V_{PO} = \sqrt{\frac{2k}{\varepsilon_0 A} g_0 \left(\frac{d}{\varepsilon_r}\right)^2} . \tag{2.8}$$

The pull-in and pull-out voltages derived in this section are widely used to characterise the reliability of RF MEMS capacitive switches. These threshold voltages change over time as a result of various degradation mechanisms and this is the subject of intense study [29, 30, 32, 37-45]. A brief introduction to the subject of RF MEMS reliability is given in the following section.

### 2.4 Introduction to RF MEMS Reliability and Research Aims

In previous years, the commercialisation of RF MEMS switches was hindered by several reliability concerns which affected the long term operation of these devices. The recent commercialisation of ohmic and capacitive switches by several companies indicates that the majority of these reliability concerns have been addressed [4, 17, 18]. However, as outlined in Section 2.2, on-going reliability concerns are preventing the commercialisation of high-performance capacitive switches which make use of intermetal dielectric layers. Indeed, the International Technology Roadmap for Semiconductors (MEMS Chapter) highlighted the continuing need to enhance the reliability and lifetime of RF MEMS switches as the biggest roadblock to their commercialisation [46]. Furthermore, the lack of

understanding of the physics of failure in these devices was identified as the primary contributing factor to their on-going reliability concerns. The failure mechanisms of RF MEMS capacitive switches can be broadly classified into extrinsic failures induced by environmental effects and intrinsic failure mechanisms caused by material degradation and these are briefly described in the following sections.

#### **Extrinsic Reliability Issues**

Many studies have shown that the lifetime of capacitive switches is influenced by the ambient conditions to which a MEMS device is exposed [47-56]. Environmental reliability concerns such as humidity and the effect of contaminants are extrinsic failure mechanisms which can be avoided by sealing devices in hermetic packages under vacuum or dry-air environments. Research into cost-effective MEMS packaging techniques is currently underway but is outside the scope of this thesis [57-61]. Moreover, the commercial devices described earlier prove that manufacturable packaging solutions have been found. Therefore, unless the package should fail, environmental concerns are no longer considered a threat to RF MEMS reliability under normal operating conditions. Additionally, while unpackaged devices are investigated in this work, all experiments are performed in a controlled dry-air environment so that environmental reliability concerns are not expected to be an issue.

#### **Intrinsic Reliability Issues**

While extrinsic failure mechanisms have been reduced, intrinsic failures due to material degradation are still being researched. These degradation mechanisms depend on the type of stress applied to a device. Initial studies were concerned with metal fatigue and fracture during cycling operation [30, 62]. However, if the moving elements of MEMS switches are designed to be several hundred microns long, while the extent of their vertical deflection is limited to several microns then mechanical failure due to fracture is not a problem [11]. Additionally, the absence of fatigue as a failure mechanism in RF MEMS has been demonstrated by the long-term cycling reliability of ohmic and capacitive switches [63-67], some of which have been shown to survive for up to 100 billion cycles without failure [68]. Early-stage capacitive switches fabricated at Tyndall National Institute have also been shown to survive for over 5 billion switching cycles without a significant change in their operational parameters [69]. The experiment had to be stopped due to time constraints on the measurement equipment and not due to device failure. Therefore, fatigue and fracture are not considered to be failure mechanisms of the capacitive switches used in this work.

As mentioned in Section 2.2, the failure modes of RF MEMS switches during hold-down operation are less well understood. For capacitive switches which use intermetal dielectric layers, the hold-down lifetime is affected by both mechanical and electrical failure mechanisms [44, 62, 70]. Mechanical degradation mechanisms such as creep and viscoelasticity can change the material properties of moveable elements during prolonged hold-down operation [71-73], while the accumulation of charge in the dielectric layers of a capacitive switch changes the electrostatic force acting on a switch membrane over time [74]. As expected from the force-balance procedure used to derive equations (2.3) – (2.7), any change in the mechanical restoring force or attractive electrostatic force as a result of mechanical degradation or dielectric charging causes a change in the pull-in and pull-out voltages of a switch.

A significant amount of research on RF MEMS reliability has been performed by studying time-dependent changes of a device C-V curve under various hold-down stress conditions [47, 49, 51, 75-91]. Initial studies attributed the observed pull-in and pull-out voltage changes to the effects of dielectric charging as mechanical degradation was assumed to be negligible [83, 92-95]. Initial research work performed by Olszewski attributed the reduction in magnitude of the pull-in and pull-out voltages (C-V narrowing) of a capacitive switch to a dielectric charging mechanism because mechanical degradation was assumed to be absent [92]. However, more recent work by Olszewski on this subject proved that mechanical degradation of the switch membrane was responsible for the observed C-V narrowing effect [96]. Additionally, recent work by other groups has shown that mechanical degradation processes such as creep and viscoelasticity are present in the thin films used in MEMS devices [97, 98].

Therefore, research groups now acknowledge that both dielectric charging and mechanical degradation effects can occur simultaneously during hold-down operation [99]. Recent research has assumed that more than one degradation mechanism is occurring in the switch and has focussed on devising ways of separating the two major reliability concerns (dielectric charging from mechanical degradation or vice versa), as unless this is achieved, individual degradation mechanisms that occur in each reliability domain cannot be properly characterised. These methods involve the creation of new measurement and analysis techniques [41, 79, 80, 100-104] or the isolated measurement of mechanical and electrical effects on dedicated test structures [71, 105-108]. A discussion of these state-of-the-art research techniques will be provided in the next chapter.

In spite of the large amount of research performed on RF MEMS reliability to date, no individual mechanical or dielectric degradation mechanisms during hold down operation have been identified in capacitive switches. It is the aim of this thesis to isolate, identify and provide solutions for these degradation mechanisms.

#### 2.5 SUMMARY

This chapter has shown that RF MEMS can be an attractive alternative to existing RF switch technologies. Examples of recently commercialised ohmic and capacitive switches were provided. The fabrication method, physics and theory needed to understand the operation of a capacitive switch was described. The concept of RF MEMS reliability was introduced, and the reliability concerns of mechanical degradation and dielectric charging were defined as the main reasons for the delayed commercialisation of high-performance capacitive switches. These reliability concerns are active during hold-down operation, and their simultaneous presence has thus far prevented the characterisation of individual degradation mechanism in RF MEMS capacitive switches.

The following chapter will show how key device parameters change during hold-down operation as a result of mechanical degradation and dielectric charging, and will discuss how these changes may be used to identify the responsible mechanism. The state-of-the-art research techniques which are used to isolate individual reliability concerns will be discussed and a description of the research aims and methodology of this work will be provided.

## **CHAPTER 3:**

## RF MEMS CAPACITIVE SWITCH RELIABILITY

### - THEORY AND RESEARCH STATUS

#### 3.1 Introduction

The unknown reliability of RF MEMS capacitive switches during hold-down operation has been identified as one area of concern which is preventing the widespread adoption and commercialisation of this technology. Despite the demonstrated high cycling lifetime of commercial switches, hold-down lifetimes of up to 10 years have still not been achieved owing to a lack of understanding of the physical processes responsible for the intrinsic failure mechanisms of a switch. Therefore, the degradation mechanisms of capacitive switches during hold-down operation need to be investigated in order to develop a deeper understanding of the physics of failure and to create novel solutions for the improvement of device reliability.

The objective of this chapter is to describe the current research status and understanding of degradation mechanisms in RF MEMS capacitive switches during hold-down operation and is organised as follows. Section 3.2 describes the intrinsic failure mechanisms of RF MEMS capacitive switches which are determined by changes in the pull-in and pull-out voltages of a switch over time. Following this, several models which were created to explain these parametric shifts are described. While these models allowed significant progress to be made in the measurement and characterisation of RF MEMS capacitive switch reliability, very little progress has been made in the identification of the underlying physical processes responsible for material degradation in capacitive switches. A discussion of this is provided in Section 3.3 where more recent methods of isolating different degradation mechanisms are described. Finally the research aims of this work are described in Section 3.4 before the chapter is summarised in Section 3.5.

#### 3.2. CAPACITIVE SWITCH FAILURE DURING HOLD-DOWN OPERATION

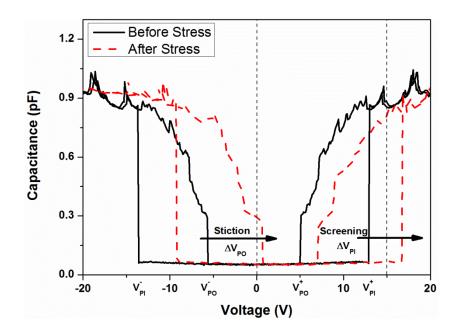

Section 2.4 of the previous chapter briefly introduced the subject of RF MEMS reliability and stated that mechanical degradation and dielectric charging cause time-dependent changes in the pull-in and pull-out voltages of a capacitive switch. Over an extended period of time, these changes can cause switch failure in one of two ways; stiction or screening. Stiction occurs when the pull-out voltage crosses over the 0 V axis such that the membrane remains fixed in the down-state even when no bias is applied to a switch, as shown in Figure 3.1. The additional failure mode known as screening occurs when a change in the pull-in voltage causes the switch parameters to lie outside a specified maximum range. An example of this is also shown in Figure 3.1 where the positive pull-in voltage has increased beyond +15 V while a switch may not be designed to operate beyond this limit.

Figure 3.1: Measured shift in the C-V curve of a Tyndall capacitive switch leading to failure due to stiction and screening.

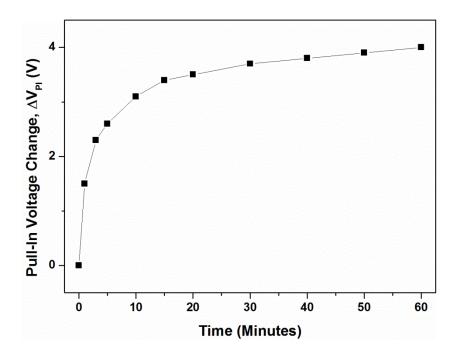

While Figure 3.1 shows the initial and final states of a switch C-V curve after a hold-down experiment, transient changes in the device C-V curve can also be used to monitor degradation of the switch parameters. An example of a transient  $\Delta V_{Pl}$  graph is shown in Figure 3.2. To obtain this data, a hold-down stress was applied to a device for a set period of time before a C-V sweep was performed to measure the pull-in voltage. The hold-down stress was then resumed for another set period of time and the stress/measurement process continued. A transient  $\Delta V$  graph is formed when the accumulated change in the pull-in or pull-out voltage is plotted against the time of the experiment and graphs such as these are used extensively throughout this thesis.

Figure 3.2: Transient change in the pull-in voltage of a capacitive switch in response to a hold-down stress over one hour. The actuation voltage was interrupted to perform C-V sweeps after 1, 3, 5, 10, 15, 20, 30, 40, 50 and 60 minutes.

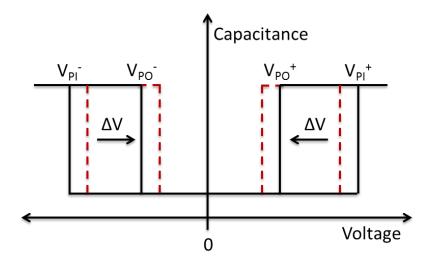

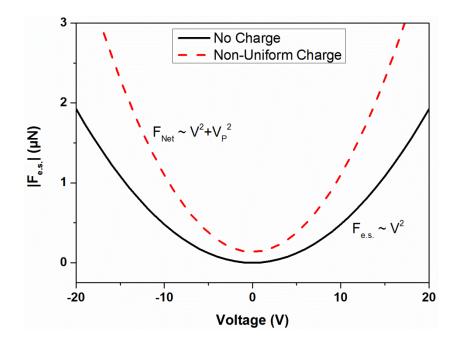

Researchers have studied transient changes of the switch pull-in and pull-out voltages in order to monitor the degradation mechanisms of a switch and have observed that the transient behaviour can broadly follow either a C-V shift effect where all the parameters shift in one direction or a C-V narrowing effect where all the parameters reduce in magnitude [42, 68, 76, 100, 109-112]. Analytical models have been developed in the literature to explain the causes of C-V shift and narrowing [113, 114] and the derivation and application of these models is described in the following sections.

#### 3.2.1 C-V Shift Effect due to Uniform Dielectric Charge

The C-V curve of an ideal capacitive switch which is symmetric about the 0 V axis was shown in Figure 2.18. This C-V curve is representative of a switch with no charge in the dielectric whose pull-in and pull-out voltages are only governed by the restoring force of the supporting tethers and the electrostatic force generated as a result of the applied bias. However, in reality, parasitic charge can exist within the dielectric layer which changes the electrostatic force between the membrane and the dielectric [74]. The presence of an additional electrostatic force causes all four threshold voltages of a device to change in what is known as the C-V shift effect. In a capacitive switch, the C-V shift effect can be recognised as the simultaneous movement of all four threshold voltages along the voltage axis in either the positive or the negative direction such that the C-V curve is no longer

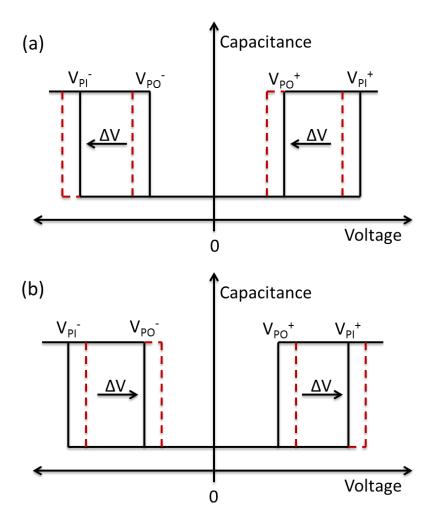

symmetrical about 0 V. The direction of shift depends on the biasing scheme and the net polarity of charge within the dielectric, and for a uniform charge distribution the shift magnitude is necessarily equal for all four threshold voltages. A representation of this is shown in Figure 3.3.

Figure 3.3: The C-V curves of an ideal capacitive switch showing a left-shift (a) and a right-shift (b) due to dielectric charging.

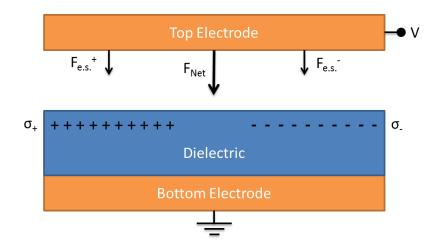

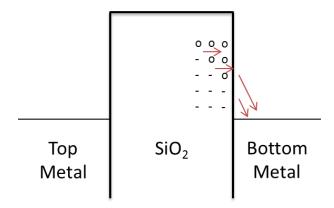

Parasitic charge can be created in the dielectric during processing [115] or may be added to the dielectric during switch operation [43, 47, 74, 88, 104, 109-111, 116-120]. The influence of this charge on the device threshold voltages can be understood by considering the simple case of uniform dielectric charging pictured in Figure 3.4 [113].

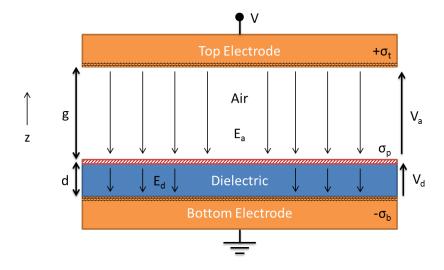

Figure 3.4: Schematic representation of a MEMS capacitive switch with a uniform distribution of parasitic charge at the top surface of the dielectric.

In Figure 3.4 a parasitic charge density  $\sigma_p$  is located at the top surface of a dielectric of thickness d and the charge densities on the top  $+\sigma_t$  and bottom  $-\sigma_b$  electrodes are arranged so that the capacitor is electrically neutral

$$\sigma_t + \sigma_b + \sigma_p = 0. ag{3.1}$$

The charge densities at the top and bottom metal are supplied by the voltage source  $\,V\,$  . As a result of these charge densities, the electric fields in the air-gap and dielectric are

$$E_a = \frac{\sigma_t}{\varepsilon_0},\tag{3.2}$$

$$E_d = \frac{-\sigma_b}{\varepsilon_0 \varepsilon_r} = \frac{\sigma_t + \sigma_p}{\varepsilon_0 \varepsilon_r}.$$

(3.3)

The voltage applied to the capacitor is divided between the air-gap and dielectric such that

$$V = E_a g + E_d d. ag{3.4}$$

By substituting (3.2) and (3.3) into equation (3.4) an expression for the charge density on the top electrode as a function of the applied voltage and parasitic charge density can be obtained

$$\sigma_{t} = \frac{V - \frac{\sigma_{p}d}{\varepsilon_{0}\varepsilon_{r}}}{\frac{g}{\varepsilon_{0}} + \frac{d}{\varepsilon_{0}\varepsilon_{r}}}.$$

(3.5)

An equation for the electrostatic force experienced by the membrane of a capacitive switch as a result of an applied voltage was given in Chapter 2 as

$$F_{e.s.} = -\frac{1}{2} \frac{\varepsilon_0 A V^2}{\left(g + \frac{d}{\varepsilon_r}\right)^2}.$$

(3.6)

Re-arranging this equation reveals that

$$F_{e.s.} = -\frac{A}{2\varepsilon_0} \left(\frac{\varepsilon_0}{g + \frac{d}{\varepsilon_r}}\right)^2 V^2, \tag{3.7}$$

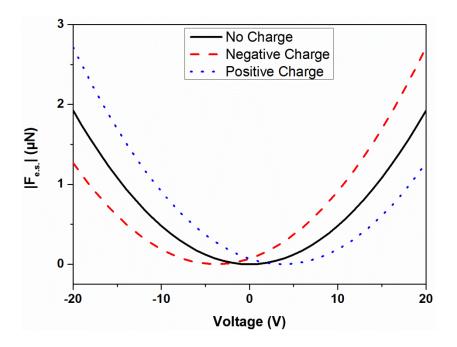

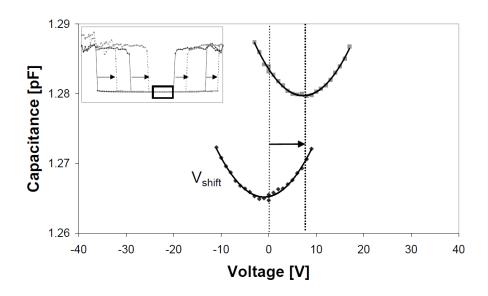

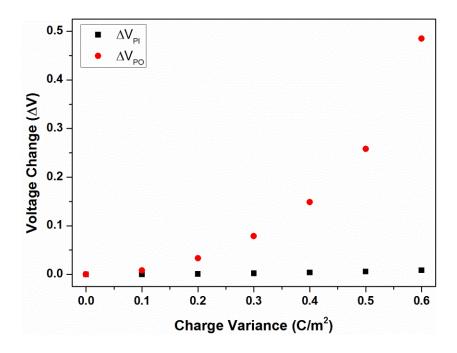

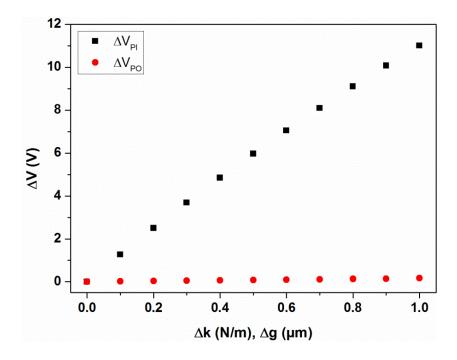

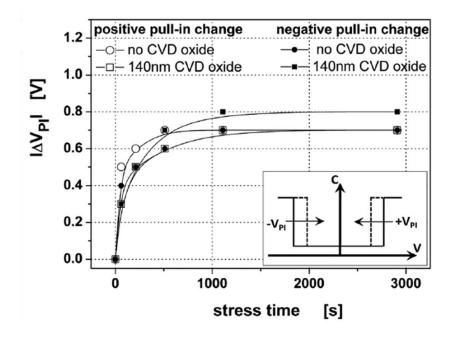

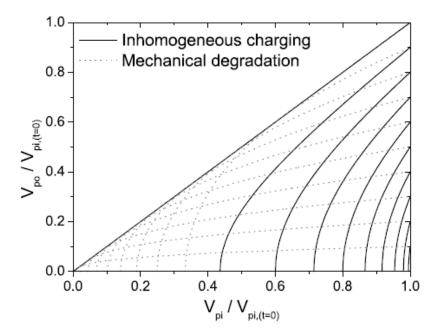

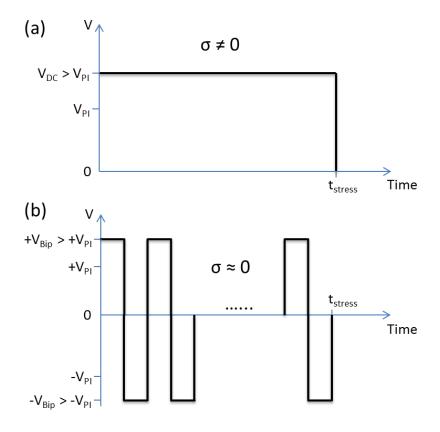

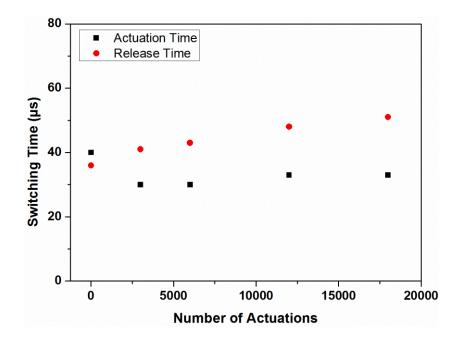

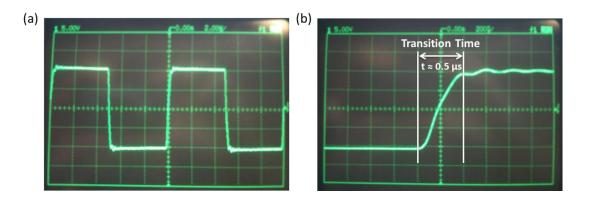

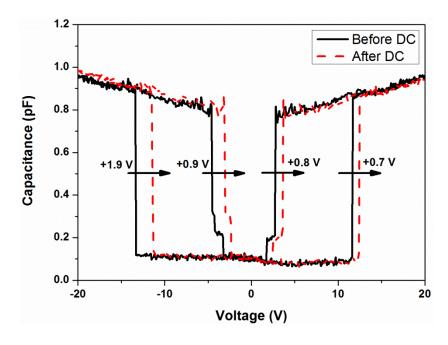

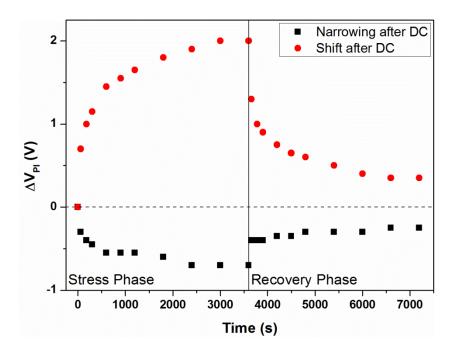

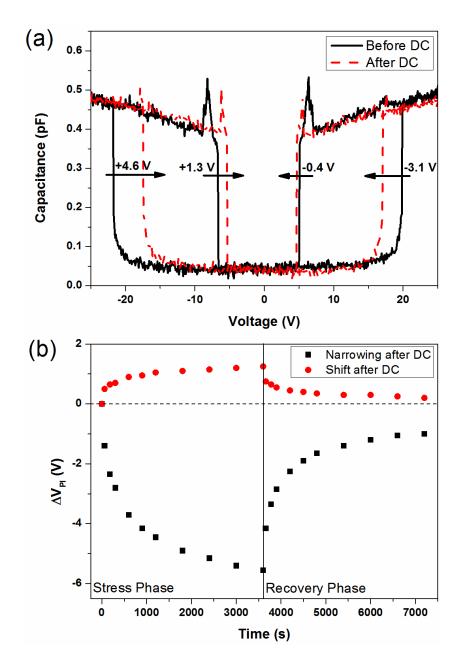

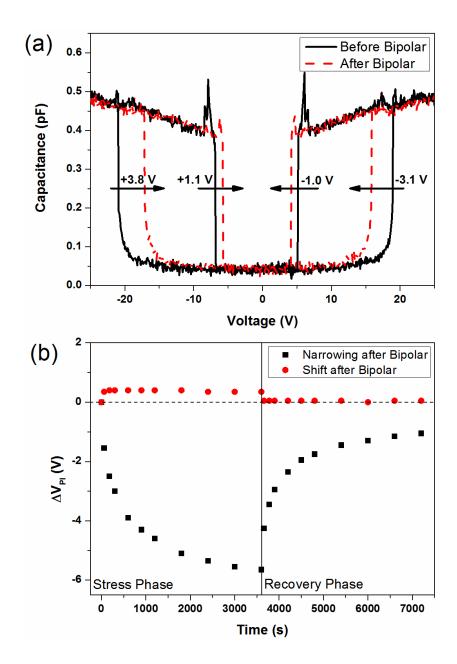

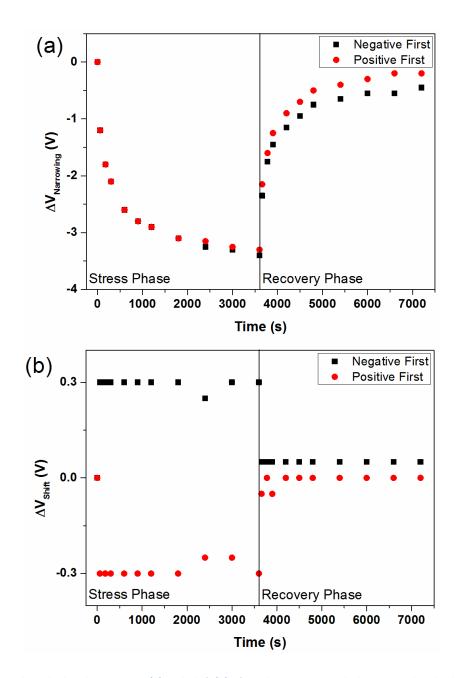

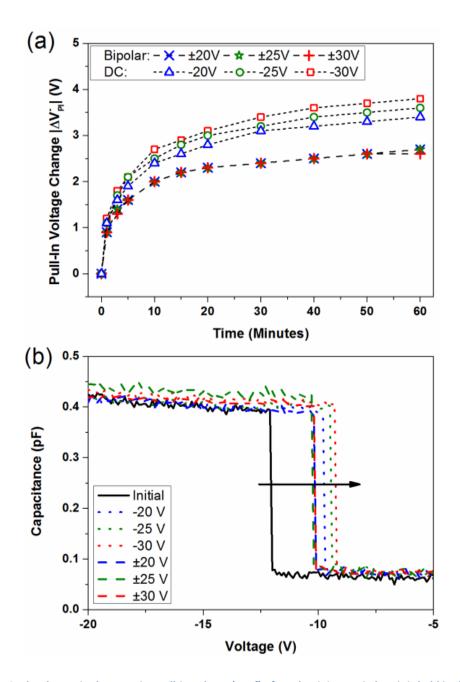

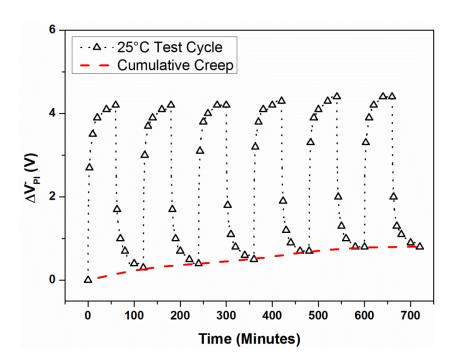

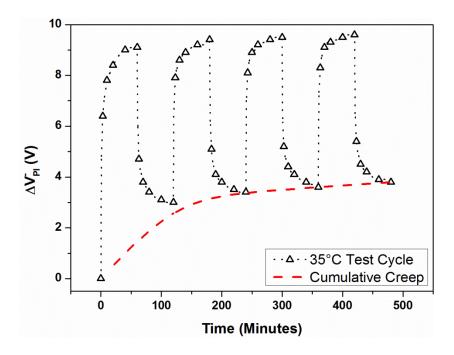

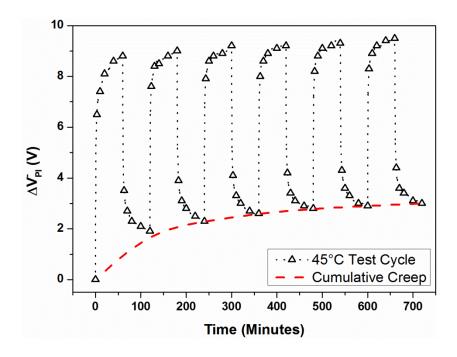

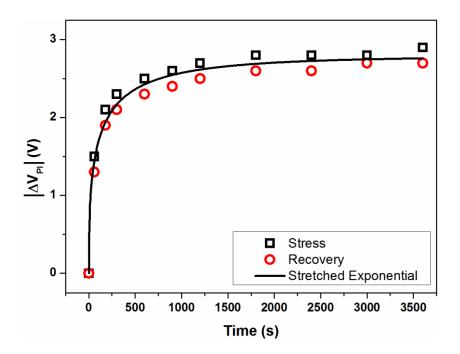

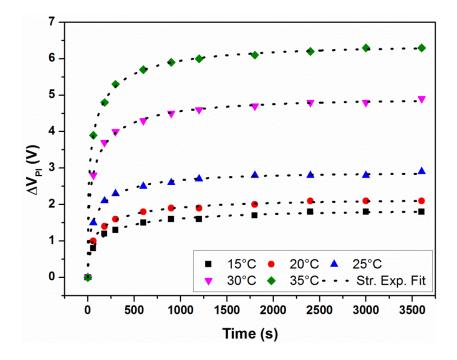

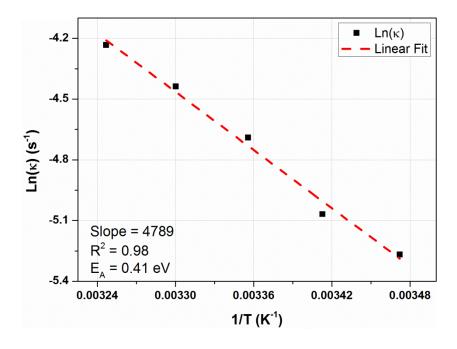

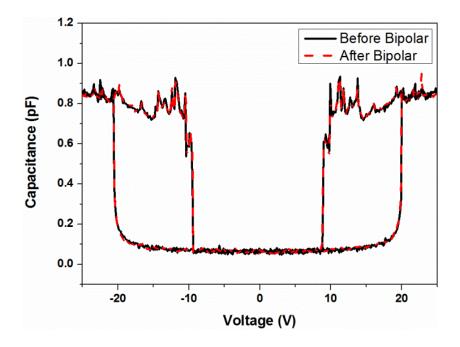

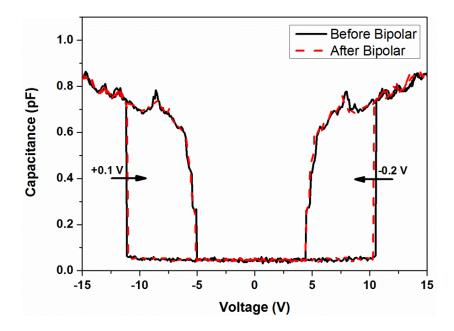

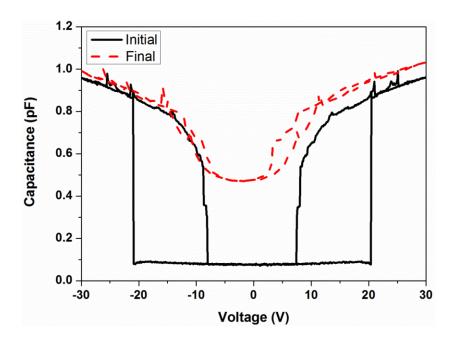

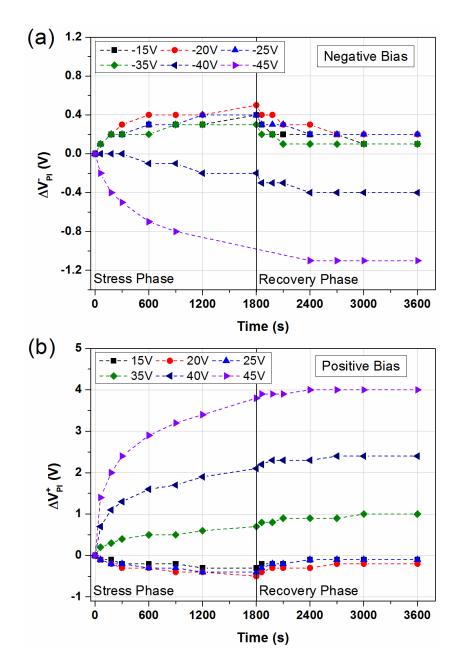

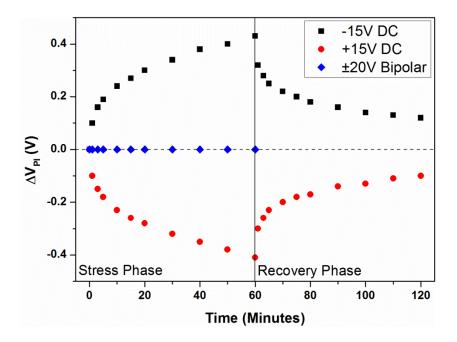

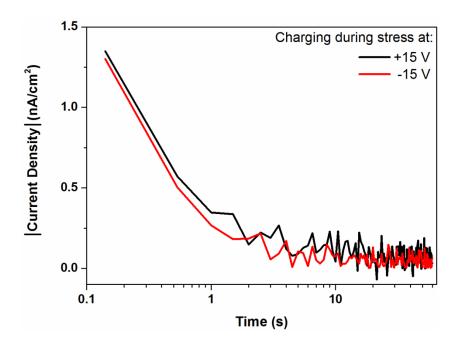

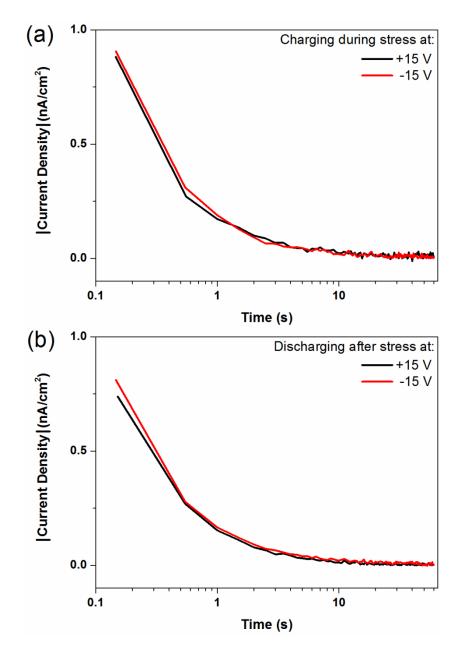

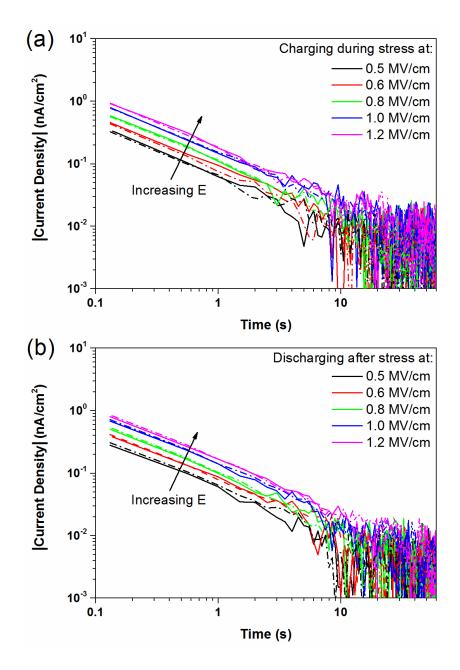

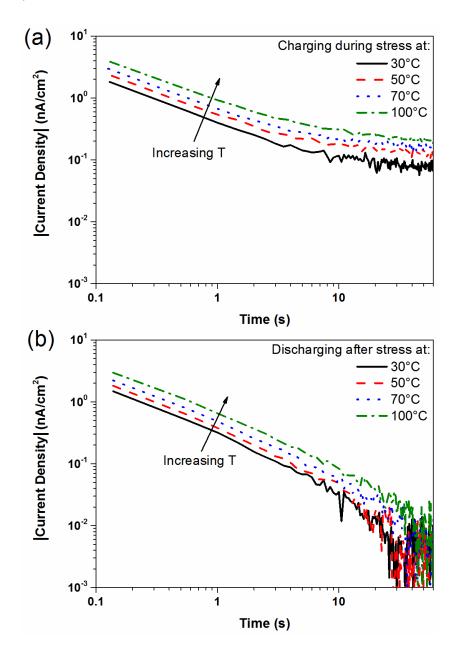

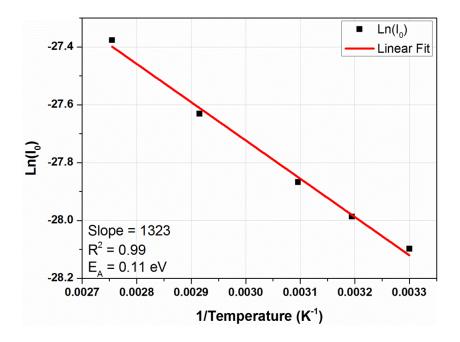

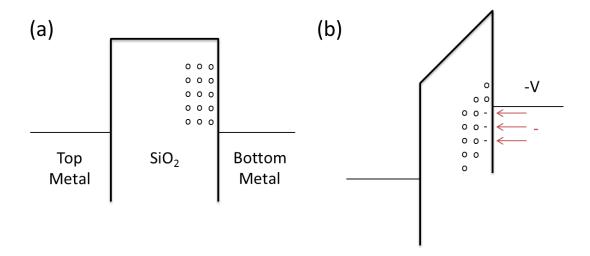

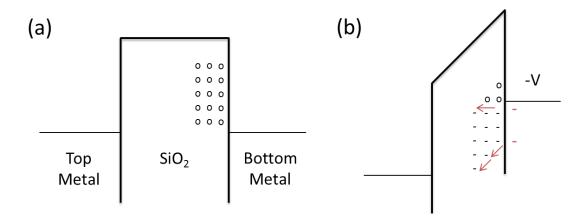

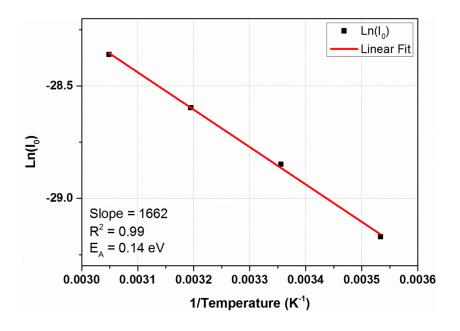

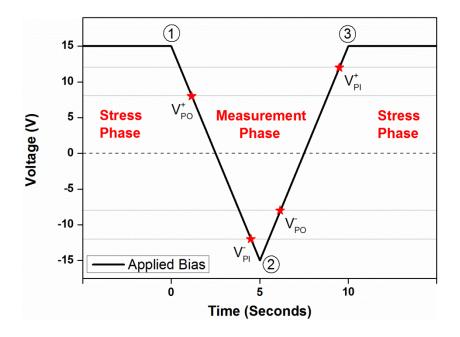

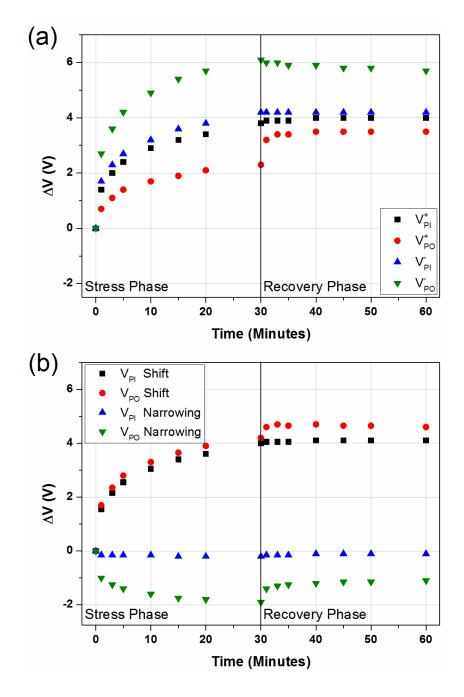

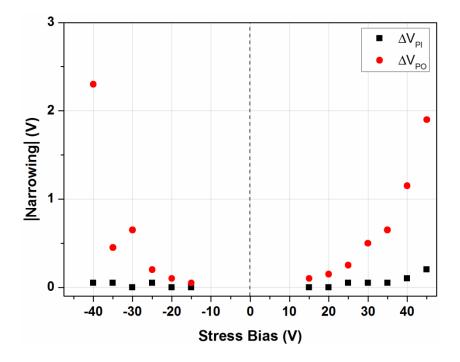

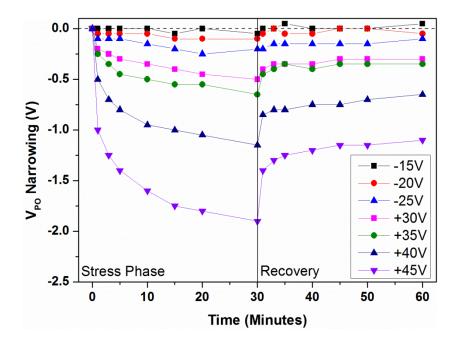

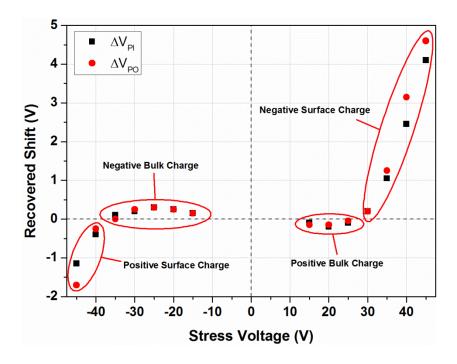

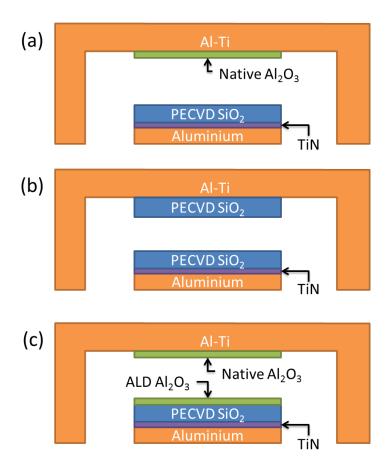

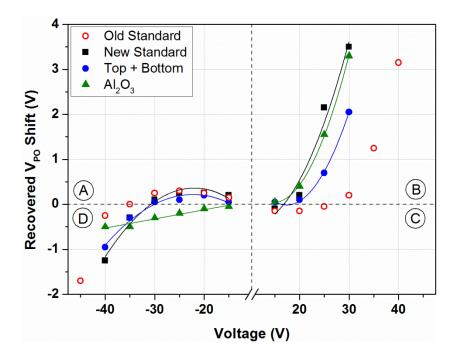

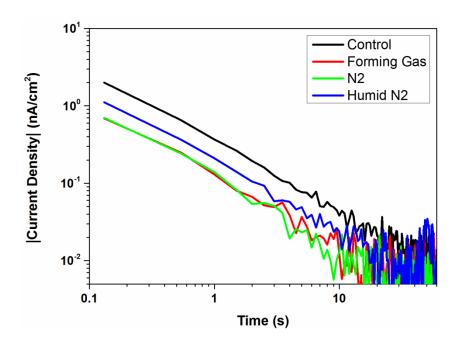

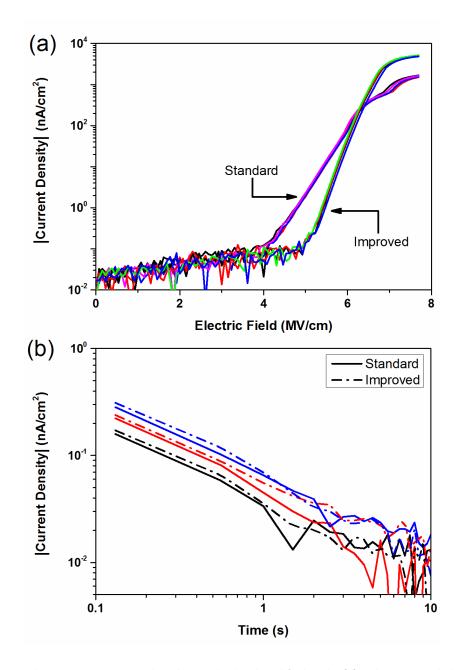

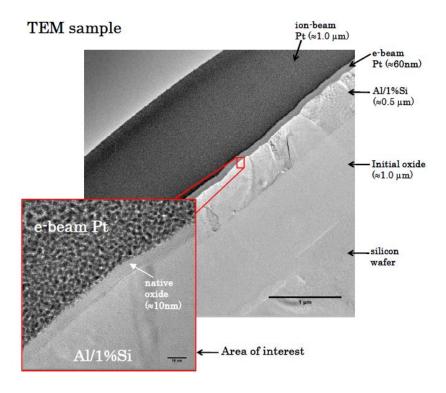

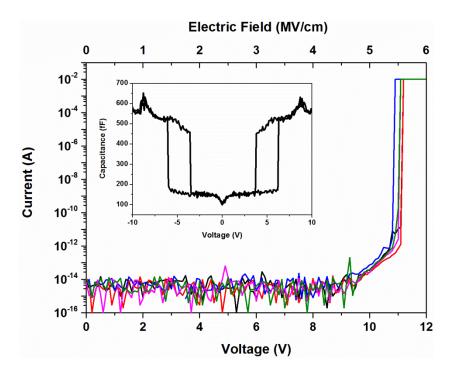

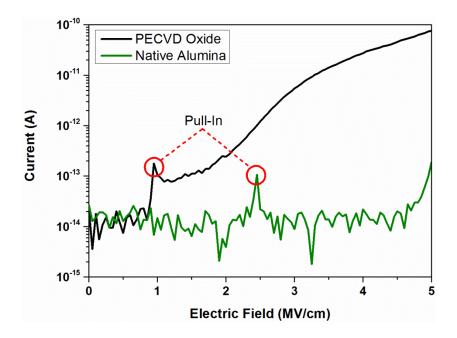

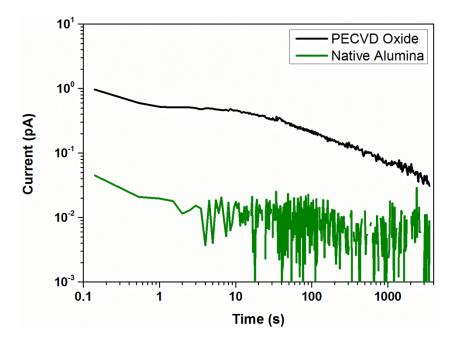

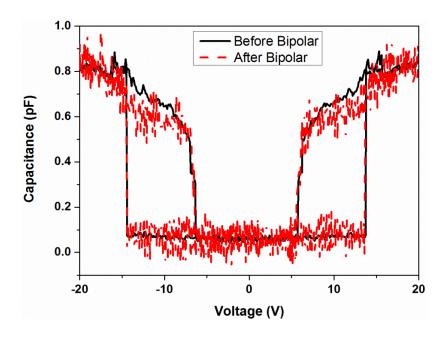

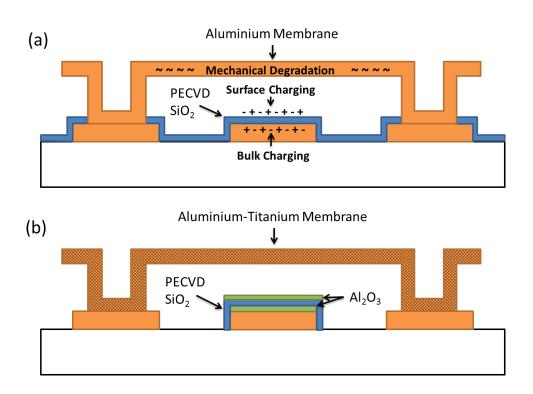

where the expression in brackets can be recognised from Chapter 2 as the total capacitance per unit area of the device, arising from a series combination of the air and dielectric capacitances. Since the charge on a capacitor is given by Q=CV and the charge on the top plate is the induced charge  $\sigma_{t}$ , expression (3.7) may be re-written in a more compact form as