#### Microwave CMOS VCOs and Front-Ends - using integrated passives on-chip and oncarrier

| Törmänen, Markus |  |  |  |

|------------------|--|--|--|

|                  |  |  |  |

2010

#### Link to publication

Citation for published version (APA):

Törmänen, M. (2010). Microwave ĆMOS VCOs and Front-Ends - using integrated passives on-chip and oncarrier. Department of Electrical and Information Technology, Lund University.

Total number of authors:

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## **Microwave CMOS VCOs and Front-Ends**

- using integrated passives on-chip and on-carrier

Markus Törmänen

**Lund 2010**

Department of Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 LUND SWEDEN

No. 25 ISSN 1654-790X

© Markus Törmänen 2010. Produced using LATEX Documentation System. Printed in Sweden by *Tryckeriet i E-huset*, Lund. April 2010.

## **Abstract**

The increasing demand for high data rates in wireless communication systems is increasing the requirements on the transceiver front-ends, as they are pushed to utilize more and wider bands at higher frequencies. The work in this thesis is focused on receiver front-ends composed of Low Noise Amplifiers (LNAs), Mixers, and Voltage Controlled Oscillators (VCOs) operating at microwave frequencies.

Traditionally, microwave electronics has used exclusive and more expensive semiconductor technologies (III-V materials). However, the rapid development of consumer electronics (e.g. video game consoles) the last decade has pushed the silicon CMOS IC technology towards even smaller feature sizes. This has resulted in high speed transistors (high  $f_T$  and  $f_{max}$ ) with low noise figures. However, as the breakdown voltages have decreased, a lower supply voltage must be used, which has had a negative impact on linearity and dynamic range. Nonetheless, todays downscaled CMOS technology is a feasible alternative for many microwave and even millimeter wave applications.

The low quality factor (Q) of passive components on-chip usually limits the high frequency performance. For inductors realized in a standard CMOS process the substrate coupling results in a degraded Q. The quality factor can, however, be improved by moving the passive components off-chip and integrating them on a low loss carrier. This thesis therefore features microwave front-end and VCO designs in CMOS, where some designs have been flip-chip mounted on carriers featuring high Q inductors and low loss baluns. The thesis starts with an introduction to wireless communication, receiver architectures, front-end receiver blocks, and low loss carrier technology, followed by the included papers.

The six included papers show the capability of CMOS and carrier technology at microwave frequencies: Papers II, III, and VI demonstrate fully integrated CMOS circuit designs. An LC-VCO using an accumulation mode varactor is presented in Paper II, a QVCO using 4-bit switched tuning is shown in Paper III, and a quadrature receiver front-end (including QVCO) is demonstrated in paper VI. Papers I and IV demonstrate receiver front-ends using low loss baluns on carrier for the LO and RF signals. Paper IV also includes a front-end using single-ended RF input which is converted to differential form in a novel merged LNA and balun. A VCO demonstrating the benefits of a high Q inductor on carrier is presented in Paper V.

# Sammanfattning (in Swedish)

De ökande kraven på högre datahastigheter inom trådlös kommunikation ställer allt högre krav på både radiosändare och mottagare, då dessa behöver utnyttja fler frekvensband med större bandbredd vid högre frekvenser. Fokus i denna avhandling ligger på högfrekvensdelen av radiomottagaren, som består av lågbrusförstärkare, blandare, och oscillatorer vid mikrovågsfrekvenser.

Traditionellt har mikrovågselektronik använt sig av exklusiva och dyra halvledarteknologier (III-V material). Den snabba elektronikutvecklingen för konsumentprodukter (t.ex. TV-spelkonsoler) har det senaste årtiondet påskyndat utvecklingen av den kiselbaserade CMOS teknologin. Detta har lett till små och snabba transistorer (hög  $f_T$  och  $f_{max}$ ) med låg brusfaktor. Samtidigt tål transistorerna inte så höga spänningar och den lägre matningspänningen har tyvärr en negativ effekt på linjäriteten och det dynamiska området. Trots detta är dagens moderna CMOS-teknologi lämplig för många mikrovågs- och även millimetervågstillämpningar.

Ofta begränsar förlusterna (på grund av lågt Q-värde) i de passiva komponenterna kretsens prestanda vid högre frekvenser. Speciellt för induktanser i en standard CMOS process bidrar den elektromagnetiska kopplingen till substratet till ett lägre Q-värde. Genom att flytta de passiva komponenterna från chipet till en bärare med låga förluster kan Q-värdet förbättras avsevärt. I denna avhandling presenteras kretsar med lågbrusförstärkare, blandare och oscillatorer i CMOS-teknologi på mikrovågsfrekvenser. En del av kretsarna har monterats på bärare med induktanser och baluner med låga förluster.

Avhandlingen börjar med en introduktion till trådlös kommunikation, arkitekturer för mottagare, blocken i mottagaren, bärarteknologi med låga förluster, och följs av de sex inkluderade vetenskapliga artiklarna.

# **Contents**

| Abstract                                | V     |

|-----------------------------------------|-------|

| Sammanfattning (in Swedish)             | vii   |

| Contents                                | ix    |

| Preface                                 | xi    |

| Acknowledgments                         | xiii  |

| List of Acronyms                        | XV    |

| List of Symbols                         | xvii  |

| Introduction                            | 1     |

| 1 Thesis Outline                        |       |

| 2 Radio Receiver Architectures          | 7<br> |

|                                         | 13    |

| 3.1 CMOS Oscillators                    |       |

| 3.2.2 The Gilbert Cell & Passive Mixers |       |

| 3.4 Survey of Front-ends                | 29    |

| 4 System-on-Package Technology          |       |

|     | 4.1 On-Chip Passives                                                    | 33 |

|-----|-------------------------------------------------------------------------|----|

|     | 4.2 Postprocessed Inductors                                             | 34 |

|     | 4.3 Carrier Technology                                                  | 34 |

|     | 5 Discussion and Future Work                                            | 39 |

|     | References                                                              | 41 |

| Ι   | A 20-GHz 130-nm CMOS Front-End using Baluns on Glass Carrier            | 51 |

| II  | A 25-GHz Differential LC-VCO in 90-nm CMOS                              | 59 |

| III | A 24-GHz LC-QVCO in 130-nm CMOS using 4-bit Switched Tuning             | 67 |

| IV  | Two 24 GHz Receiver Front-ends in 130-nm CMOS using SOP Technology      | 75 |

| V   | A 24 GHz VCO with 20 % tuning range in 130-nm CMOS using SOP Technology | 83 |

| VI  | A 24-GHz Quadrature Receiver Front-end in 90-nm CMOS                    | 91 |

## **Preface**

This thesis summarizes my academic work in the Analog/RF group at the department of Electrical and Information Technology, Lund University, for the Ph.D. degree in Circuit Design. The thesis consists of two parts, where the first part is a general introduction to the research area, and the second part is the included research papers, listed below:

- M. Törmänen and H. Sjöland, "A 20-GHz 130-nm CMOS Front-End using Baluns on Glass Carrier," *IEEE Proc. 2nd International Conference on Signals, Circuits & Systems, SCS 2008*, pp. 1-4, Nov. 2008, Hammamet, Tunisia.

- M. Törmänen and H. Sjöland, "A 25-GHz Differential LC-VCO in 90-nm CMOS," *IEEE Proc. Asia Pacific Conference on Circuits and Systems, APCCAS 2008*, pp. 554-557, Nov. 30 Dec. 9, 2008, Macao, China.

- M. Törmänen and H. Sjöland, "A 24-GHz LC-QVCO in 130-nm CMOS using 4-bit Switched Tuning," *IEEE Proc. International Conference on Microelectronics, ICM* 2008, pp. 462-465, Dec. 2008, Sharjah, United Arab Emirates.

- M. Törmänen and H. Sjöland, "Two 24 GHz Receiver Front-ends in 130-nm CMOS using SOP Technology," *IEEE Proc. Radio Frequency Integrated Circuits Symposium*, *RFIC 2009*, pp. 559-562, June 2009, Boston, Massachusetts, USA.

- M. Törmänen and H. Sjöland, "A 24 GHz VCO with 20 % tuning range in 130-nm CMOS using SOP Technology," *IEEE Proc. Radio Frequency Integrated Circuits Symposium, RFIC 2009*, pp. 473-476, June 2009, Boston, Massachusetts, USA.

- M. Törmänen and H. Sjöland, "A 24-GHz Quadrature Receiver Front-end in 90-nm CMOS," *IEEE Proc. Asia Pacific Microwave Conference, APMC 2009*, Dec. 2009, Singapore.

#### **Related publications**

The following papers contain overlapping, complementing, and additional material, but are not considered part of this thesis.

- M. Törmänen and H. Sjöland, "A 26-GHz LC-QVCO in 0.13-um CMOS," *IEEE Proc. Asia Pacific Microwave Conference, APMC 2007*, pp. 1769-1772, Dec. 2007, Bangkok, Thailand.

- M. Törmänen and H. Sjöland, "A 25-GHz Low Phase Noise LC-VCO," Proc. SSoCC 2008, May 2008, Gnesta, Sweden.

- K. K. Lee, C. Bryant, M. Törmänen, and H. Sjöland, "A 65-nm CMOS ultralow-power LC quadrature VCO," *IEEE Proc. NORCHIP 2009*, Nov. 2009, Trondheim, Norway.

- M. Törmänen and H. Sjöland, "A 24 GHz SOP VCO with 20 % tuning range," GigaHertz Symposium 2010, March 2010, Lund, Sweden.

- M. Törmänen and H. Sjöland, "K-band Receiver Front-ends in  $0.13\mu m$  CMOS using Carrier Technology," Proc. SSoCC 2010, May 2010, Kolmården, Sweden.

# Acknowledgments

During my time as a graduate student I have met many people that contributed in one way or another to this thesis, but to mention them all here is impossible and I restrict myself to those that have had substantial impact on this work.

I have been fortunate to be part of the Analog/RF Cicuit Design group at the Dept. of Electrical and Information Technology, Lund University. During this time it has been a privilege working with a highly competent supervisor, Prof. Henrik Sjöland, whos knowledge and experience in the field is extensive. His enthusiasm to attack various problems has been very inspiring.

I would like to thank both current and former colleagues in the Analog/RF group for a productive and relaxed atmosphere, and also their friendship. In particular, my travel companions to different parts of the world: Andreas Axholt, Johan Wernehag, Martin Anderson, and Ellie Cijvat. Peter Sjöblom, Niklas Troedsson, Fredrik Tillman, and Peitro Andreani for all fruitful discussions. A special thanks to Roland Strandberg for sharing my interest in hunting and target shooting. I would also like to thank the people at Ericsson Research in Mölndal, particularly Harald Jacobsson, Lars Aspemyr and Mingquan Bao, for a good collaboration at the start of my Ph.D. studies.

I am very grateful for the help and support from the faculty, the technical staff, and the administration at the department. Especially, Göran Jönsson for introducing me to RF electronics during my undergraduate studies, Bertil Larsson for giving me the opportunity to lecture the Advanced Analog Electronics course, Lars Hedenstjerna for all mechanical assistance, Martin Nilsson for PCB manufacturing, Stefan Molund for CAD support, Erik Jonsson for UNIX/Linux support, and Pia Bruhn for her help with various administrative tasks. A special thanks also to Lars Olsson for proofreading this thesis.

Finally, I would like to thank my wife Kristina for her endless love and support, and my family for supporting me in the pursuit for higher education.

This work has been funded by Ericsson AB and the VINNOVA Industrial Excellence Center - System Design on Silicon (SoS).

Martius Tornamen

# **List of Acronyms**

ADC Analog-to-Digital Converter

AM Amplitude Modulation

BB Baseband

BCB Benso-Cyclobutene

BEOL Back End of Line

BER Bit Error Rate

BSF Band Select Filter

CG Common Gate

CMOS Complementary Metal Oxide Semiconductor

CPW Co-Planar Wave Guide

CS Common Source

CSF Channel Select Filter

DAC Digital-to-Analog Converter

DC Direct Current

DSP Digital Signal Processor

F Noise Factor

FET Field Effect Transistor

FOM Figure of Merit

$FOM_T$  Figure of Merit taking tuning range into account

GaAs Gallium Arsenide

GND Ground

IC Integrated Circuit

ICP<sub>1dB</sub> Input referred 1dB Compression Point

IF Intermediate Frequency

${\rm IIP}_2 \qquad {\rm Input\ referred\ Second-Order\ Intercept\ Point}$

IIP<sub>3</sub> Input referred Third-Order Intercept Point

IM Intermodulation

IRF Image Reject Filter

xvi List of Acronyms

ISF Impulse Sensitivity Function

IP<sub>2</sub> Second-Order Intercept Point

IP<sub>3</sub> Third-Order Intercept Point

IRR Image Rejection Ratio

LNA Low Noise Amplifier

LPF Low Pass Filter

LO Local Oscillator

mHEMT Metamorphic High Electron Mobility Transistor

MIM Metal Insulator Metal

MMIC Monolithic Microwave Integrated Circuit

MOS Metal Oxide Semiconductor

NF Noise Figure

NMOS N-channel Metal Oxide Semiconductor

NR Noise Ratio

$NR_{tot}$  The Total Noise Ratio

PA Power Amplifier

PCB Printed Circuit Board

PM Phase Modulation

PMOS P-channel Metal Oxide Semiconductor

Q Quality factor

QAM Quadrature Amplitude Modulation

QVCO Quadrature Voltage Controlled Oscillator

RF Radio Frequency

SiO<sub>2</sub> Silicon Dioxide

SMD Surface Mounted Device

SoC System on Chip

SOP System on Package

TCR Temperature Coefficient of Resistivity

VCO Voltage Controlled Oscillator

V<sub>DD</sub> Supply Voltage

WLP Wafer Level Package

# **List of Symbols**

$C_{gs}$  Gate to source parasitic capacitance  $C_{ad}$  Gate to drain parasitic capacitance

$\Delta f$  Offset frequency

$\Delta\omega$  Angular offset frequency

$\epsilon$  Amplitude error in an image reject architecture

$f_0$  Resonance frequency

$f_c$  Center frequency

$f_{IF}$  Intermediate frequency

$f_{IM}$  Image frequency

$f_{LO}$  Local oscillator frequency

$f_{max}$  Maximum oscillation frequency

$f_{RF}$  Radio frequency

$f_T$  Transition frequency  $\gamma$  Body effect coefficient

$g_{ds}$  Drain to source conductance

$g_{ds0}$  Drain to source conductance at  $V_{DS} = 0$

$G_m$  Effective transconductance

$g_m$  Transconductance

$g_{mb}$  Body transconductance

I DC current

I+ In phase positive signalI- In phase negative signal

$\lambda$  Wavelength

L Transistor channel length

$\mathcal{L}(\Delta\omega)$  Phase noise at certain offset frequency

$\omega$  Angular frequency

$\omega_0$  Resonance angular frequency  $\omega_T$  Angular transition frequency

xviii List of Symbols

| $\theta$  | Phase error in an image reject architecture                         |

|-----------|---------------------------------------------------------------------|

| $P_{DC}$  | DC power consumption                                                |

| Q+        | Quadrature phase positive signal                                    |

| Q-        | Quadrature phase negative signal                                    |

| $q_{max}$ | Maximum charge in the LC-VCO resonance tank                         |

| S         | Number of symbols                                                   |

| s         | complex angular frequency or Laplace transform variable             |

| $S_{ing}$ | Power spectral density of induced gate noise (input referred)       |

| $S_{iw}$  | Power spectral density of white noise (output referred)             |

| $S_{vg}$  | Power spectral density of input noise voltage $(1/f \ {\rm noise})$ |

| $V_0$     | Differential peak to peak voltage of an LC-VCO resonator            |

| W         | Transistor width                                                    |

| Y         | Admittance                                                          |

| $Z_{in}$  | Input impedance                                                     |

# Introduction

# **Chapter 1**

## **Thesis Outline**

#### 1.1 Motivation

The history of wireless communication started in the late 19<sup>th</sup> century pioneered by men like Heinrich Hertz, Alexander Popov, and Guglielmo Marconi. The technological development has since then been very rapid, specially in the last two decades of cellular communication. Today's increasing demand for higher data rates is pushing wireless communication systems to utilize more and wider bands at higher frequencies. At the same time as the performance must increase, low cost and small size implementations are necessary to be commercially successful.

The III-V technologies, e.g. GaAs, are the obvious technologies of choice for microwave applications as they offer low noise, high speed, and high breakdown voltages. However, they do not meet the low cost requirements for large scale production. Being used for virtually all digital circuits, CMOS is the dominating IC technology today, and the large volumes result in low cost. The evolution of CMOS towards even smaller and faster devices has made it a viable technology for cost sensitive radio systems operating also at microwave and millimeterwave frequencies. This has also opened the possibility to design fully integrated SoCs, where the microwave frontends, data converters (ADC/DAC), and DSPs can be placed on the same chip. However, as the speed ( $f_T$  and  $f_{max}$ ) of CMOS transistors has increased with technology scaling, the breakdown voltages have decreased, and shorter channel length devices produce more low frequency noise which imposes challenges for the designer. Even with a fast high performance CMOS technology the performance of microwave circuits is usually limited by the losses of on-chip passive components. Moving the passives from the chip to a low loss carrier can help to improve the performance, but it also requires good knowledge of the package transition parasitics.

The focus of this thesis is on the receiver front-end. Different front-ends using differential topologies, consisting of low noise amplifiers (LNAs) and mixers, have been designed in CMOS technology. The dies have been flip-chip mounted to carriers featuring low loss baluns to generate the differential signals needed by the chip. Differential and quadrature voltage controlled oscillators (VCOs) have also been designed in CMOS, where one VCO makes use of a low loss on-carrier inductor to achieve high phase noise performance. A fully integrated CMOS quadrature receiver

front-end consisting of LNAs, mixers, and a QVCO is also demonstrated.

This thesis is not meant to be a text book on wireless communication nor RF electronics as very good ones exist in litterature, e.g. [1–3]. However, to put the work in this thesis into perspective, an introduction to wireless communication, receiver architectures, front-end receiver blocks, and low loss (high Q) passive components is presented in the following chapters.

#### 1.2 Organisation of the Thesis

#### **Chapter 1 - Thesis Outline**

Starts with a motivation to the work followed by a presentation of how the thesis is organized.

#### **Chapter 2 - Radio Receiver Architectures**

Begins with a short introduction to wireless communication and the basic principles and building blocks of a modern radio transceiver. The heterodyne, image reject, and direct conversion receiver architectures are described.

#### **Chapter 3 - Receiver Front-end Considerations**

The different blocks of the radio receiver front-end are treated here. Differential topologies of CMOS VCOs, low-loise amplifiers and mixers are treated, as well as the effect on the received information caused by their imperfections.

#### Chapter 4 - System-on-Package Technology

This chapter describes passive microwave components. As the Q-value for on-chip passives is quite limited it can be benefitial to move them off-chip. Postprocessed inductors are also discussed. Finally, VCOs and front-ends using carrier integrated passives are demonstrated with a few examples.

#### **Chapter 5 - Discussion and Future Work**

This chapter discusses the research results and suggests some ideas for future improvements and work with carrier technology.

#### **Included Papers**

Microwave front-ends and VCOs are demonstrated in the included papers with some designs using System-on-Package (SOP) technology. All of the circuits in the included papers have been designed, fabricated, and measured.

Papers II, III, and VI demonstrate the capability of fully integrated CMOS circuit designs. An LC-VCO using an accumulation mode varactor is presented in Paper II, a QVCO using 4-bit switched tuning is shown in Paper III, and a quadrature receiver front-end (including QVCO) is demonstrated in paper VI.

Papers I and IV demonstrate SOP receiver front-ends using low loss baluns on carrier for the LO and RF signals. Paper IV also includes a front-end using single-ended RF input, which is converted to differential form in a novel on-chip merged LNA and balun. A SOP VCO demonstrating the benefits of a high Q inductor on carrier is presented in Paper V, where the VCO achieves a 20% tuning range at 24GHz with excellent phase noise performance.

# Chapter 2

## **Radio Receiver Architectures**

This chapter presents a brief introduction to wireless communication and the most common radio receiver architectures used today. Some advantages and drawbacks of the different receiver architectures are also discussed.

#### 2.1 Wireless Communication

A basic system for wireless communication is illustrated in Figure 1. It consists of a transmitter, a communication channel, and a receiver. In the transmitter the information to be sent is modulated on a radio frequency (RF) carrier and amplified by a power amplifier (PA) before it is transmitted through the antenna. In the communication channel the signal gets attenuated and subjected to noise and interference. To be able to receive the attenuated signal it is amplified in the receiver front-end, where it is also downconverted to a lower frequency, called intermediate frequency (IF). After reducing interference by filtering, the signal can finally be demodulated. The demodulator is often digital, consisting of an analog to digital converter (ADC) and a digital signal processer (DSP). In order for the demodulator to detect the transmitted information correctly, the front-end must cope with the impaired signal from the channel and convert it to a signal that fits the demodulator. In a digital system, the bandwitdh the system must handle is proportional to the baseband (BB) signal bitrate. With an increasing demand on high data rates, wireless communication systems are therefore pushed to use more and wider frequency bands, which are available at higher frequencies. More details on wireless communication can be found in e.g. [1].

**Figure 1:** An illustration of radio transmission

#### 2.2 Receiver Achitectures

The task of the receiver front-end is to supply the input of the demodulator, normally the ADC, with an amplified, frequency downconverted and filtered signal from which the transmitted information can be detected. The downconversion is achieved by multiplying the RF signal with a local oscillator (LO) signal in the mixer, which results in first order output signals located at the sum and difference frequencies. The difference frequency, or intermediate frequency (IF),  $f_{IF} = |f_{RF} - f_{LO}|$ , becomes a new carrier of the downconverted received RF signal. One problem is that an interferer located at the image frequency will also be downconverted to the same IF. For high-side injection ( $f_{LO} > f_{RF}$ ) the image frequency will be located at  $f_{IM} = f_{RF} + 2 \cdot f_{IF}$ , and for low-side injection ( $f_{LO} < f_{RF}$ ) at  $f_{IM} = f_{RF} - 2 \cdot f_{IF}$ . This image signal problem has to be dealt with in the receiver.

The three most common receiver architectures are presented briefly in the the following sections; the heterodyne receiver, the image reject receiver, and the direct conversion/homodyne receiver. The main difference between these architectures is the way the image signal is handled. A more detailed description of receiver achitectures can be found in e.g. [2, 3].

#### 2.2.1 The Heterodyne Receiver

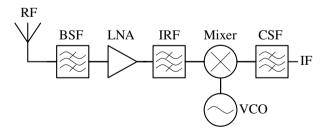

The heterodyne receiver architecture [4] is shown in Figure 2. Like all the receiver architectures presented here, it has a band select filter (BSF) that attenuates interferers outside the received band. The BSF precedes the low noise amplifier (LNA), where the RF signal is amplified before it is filtered by the image reject filter (IRF). The RF signal is then downconverted to an IF in the mixer by multiplying with a local oscillator (LO) signal. Due to the image frequency problem described above the IRF has to be placed before the mixer, because after the mixer an interferer at the image frequency can not be separeted from the downconverted RF signal as they will both be at the same IF. The purpose of the channel select filter (CSF) is to then filter out the channel to be demodulated.

Figure 2: The heterodyne receiver architecture

A trade-off, again due to the image problem, has to made in choosing the IF. The

CSF is a bandpassfilter at the IF, with a Q value proportional to the IF. Thus the lower the IF, the better for the CSF. However, the IF must be chosen larger than half the width of the received band, since otherwise the image signal will be in-band and can not be filtered out. Furthermore, if the minimum IF is chosen (equal to half the width of the received band), the IRF filter has to be very sharp (have high order). Thus, a higher IF has to be chosen, and a compromise has to be made between the IRF and the IF blocks (CSF, amplification, and detector). Due to the stringent filtering required, the filters are usually not possible to implement on-chip, and they are thus quite costly.

A possibility to relax the requirements on the different blocks is to perform the downconversion in two steps. This type of architecture is usually referred to as the double-conversion heterodyne receiver. However, with two IFs the receiver complexity and cost increases as another filter, mixer, and LO signal is needed.

#### 2.2.2 The Image Reject Receiver

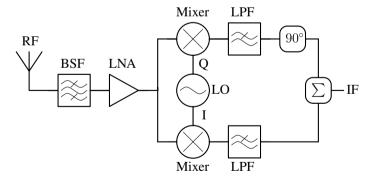

The image reject receiver architecture allows the image to be inside the band. This enables a low IF to be used, reducing the requirement for a high Q in the IF filter. The principle of image rejection is to first employ complex downconversion by mixers fed by quadrature LO signals. The down-converted IF outputs from the two mixers are then phase shifted and added. The image signals will then cancel whereas the wanted IF signals from the two branches add in phase.

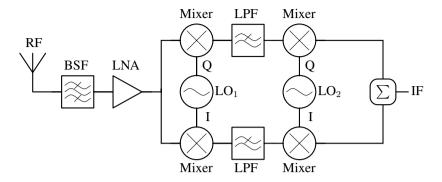

Two common architectures, the Hartley (1928) [5] and the Weaver (1956) [6], are shown in Figures 3 and 4, respectively. A 90° phase shift is introduced in one of the branches of the Hartley receiver, while the Weaver structure instead utilizes a double complex downconversion.

Figure 3: The hartley image reject receiver architecture

Both phase and amplitude mismatch result in reduced image rejection, thus it is important that the two branches are well matched and that the LO signal has a good quadrature accuracy. An equation for the image rejection ratio (IRR) is derived in [2]

Figure 4: The weaver image reject receiver architecture

and shown in (1),

$$IRR = \frac{1 + 2(1 + \epsilon)\cos(\theta) + (1 + \epsilon)^2}{1 - 2(1 + \epsilon)\cos(\theta) + (1 + \epsilon)^2} \approx \frac{4}{\epsilon^2 + \theta^2} \bigg|_{\text{small } \epsilon \text{ and } \theta}$$

(1)

where  $\epsilon$  is the relative amplitude (gain) mismatch and  $\theta$  the phase imbalance (in radians).

If the I and Q branches are kept separated in the front-end, the image rejection (phase shift and addition) can also be performed in the digital baseband.

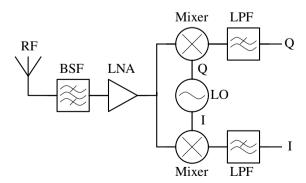

#### 2.2.3 The Direct Conversion / Homodyne Receiver

The direct conversion or homodyne receiver [7], sometimes also referred to as the zero-IF receiver, presents yet another way to deal with the image signal problem, see Figure 5. This is accomplished by choosing the LO signal frequency equal to that of

Figure 5: The homodyne receiver architecture

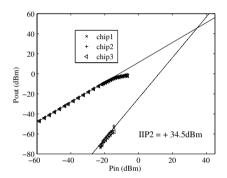

the RF signal, setting the IF equal to zero (DC) and thus making the signal to receive its own image. The channel select filtering becomes easier as the mixer outputs just have to be low pass filtered before the demodulator. Since the image signal is never stronger than the signal to receive, the mismatch of the I and Q branches is not as critical as in the image reject receiver. The drawback, however, is that since the signal after down-conversion is centered at DC, the architecture is sensitive to flicker noise (1/f noise) and DC-offsets. Low frequency disturbance can also be caused by interfering signals through even order non-linearities and self-mixing. The requirements on the second order non-linearity of the mixer are therefore very stringent in homodyne receivers. As the gain is typically quite high before the ADC in the demodulator, even small DC-offsets can saturate the ADC input or the amplifiers preceeding it.

# Chapter 3

### **Receiver Front-end Considerations**

The receiver front-end is the first part of the radio receiver. It receives the high frequency signal from the antenna. The front-end's purpose is to amplify, frequency down-convert, and filter the signal while adding as little noise and other impairments as possible to the signal, so that the transmitted information can be retrieved by the succeeding stages. CMOS voltage controlled oscillators (VCOs), low-noise amplifiers (LNAs), and mixers are briefly treated in this chapter, as well as the effects on the received information caused by their imperfections. A more comprehensive treatment can be found in e.g. [2] or [3].

#### 3.1 CMOS Oscillators

Oscillators are circuits that generate an output signal at a certain frequency with a DC power supply as the only source. The frequency can be controlled typically by a voltage, making the oscillator a voltage controlled oscillator (VCO). The output signal is usually used as a local oscillator (LO) signal in mixers to produce a downconverted intermediate frequency (IF) signal from the input radio frequency (RF) signal.

Generally oscillators can be divided into two types, relaxation and harmonic (tuned) oscillators. The relaxation oscillators, e.g. Schmitt trigger using positive feedback and ring oscillators, can be used to produce different periodic waveforms. They do not use large on-chip inductors and are thereby small in size, but unfortunately they are not suitable for RF applications requiring low phase noise. Harmonic oscillators, e.g. differential LC, Clapp, Colpitts, Hartley, and Pierce oscillators have better phase noise performance and sinusoidal output waveform due to the filtering provided by the resonator, and they are suitable for RF applications. The oscillator designs included in this thesis are based on the differential LC oscillator topology, which is the topology covered briefly in the following sections.

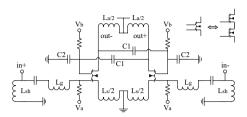

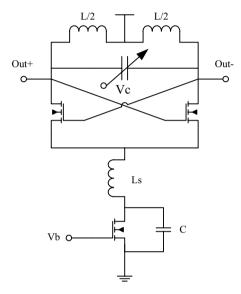

#### 3.1.1 Differential LC oscillator

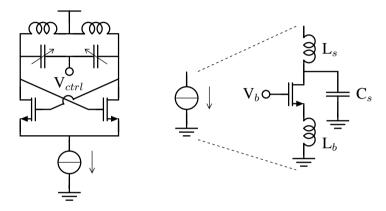

The differential LC oscillator is depicted in Figure 6. The cross-coupled transistors provide a negative resistance to overcome the losses in the resonator composed of the varactor and inductor. A stable oscillation is reached when the integrated losses over one cycle in the resonator are exactly compensated for by the energy supplied by the

negative resistance of the differential pair. In theory [3], a minimum net startup loop gain of one is required for the oscillator to start. However, in practice the loop gain must be chosen a few times larger than one to ensure startup, since the gain of the differential pair will be compressed at large signal levels. If the startup loop gain is not sufficiently large, full oscillation amplitude will therefore not be reached. This would result in degraded phase noise and potentially reduced mixer performance due to insufficient LO amplitude. Fortunately, startup loop gain is rarely a problem in the CMOS differential oscillator, where the output signal is connected directly to the transistor gate terminals.

Figure 6: Differential LC oscillator

By using a first order model of the differential pair, it can be shown that the differential admittance provided by the transistors is as shown in (2).

$$Y = \frac{1}{2} \left( -g_m + sC_{gs} + 4sC_{gd} \right) \tag{2}$$

#### **MOS Varactor**

The frequency tuning of the oscillator can be accomplished by changing either the inductance or the capacitance of the resonator, as the resonance angular frequency is given by  $\omega_0 = \frac{1}{\sqrt{LC}}$ . Typically, the capacitance is made tunable. The variable capacitor, called varactor, is often realized as an MOS varactor using either NMOS or PMOS transistors. With the drain and source terminals connected together, and the bulk terminal at GND (NMOS) or  $V_{DD}$  (PMOS), the tunable capacitance is achieved through the potential difference between the gate and drain-source terminals. The tuning range is similar for both NMOS and PMOS varactors, but the parasitic resistance is lower for the NMOS device, although it can be more sensitive to substrate-induced noise due to the lack of a separate p-well. This type of devices is often referred to as

inversion-mode varactors, since they operate in the inversion (and depletion) region of the MOS transistor.

Another common MOS varactor is the accumulation-mode varactor [8], which operates in the accumulation and depletion regions. Based on the PMOS transistor, with the  $p^+$  doped diffusions of the drain and source replaced by  $n^+$  well contacts, the accumulation-mode varactor offers a low series resistance.

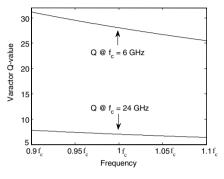

An important parameter for the varactor is the Q-factor, where the MOS varactors typically offer higher quality factors than reverse biased PN junction based varactors. Since the losses are dominated by the series resistance, the quality factor is inversely proportional to the frequency,  $Q=1/\left(\omega_0 CR\right)$ . The use of minimum channel length devices maximizes the Q since the channel resistance is then minimized. Short fingers are then necessary to reduce the series gate resistance. However, due to bias independent gate-source and gate-drain overlap capacitances, the maximum to minimum capacitance ratio  $\left(C_{max}/C_{min}\right)$  is reduced for short channel lengths. A  $C_{max}/C_{min}$  ratio of about 3 can be achieved typically by MOS varactors. The Q-factor improves with technology scaling, but at the same time the  $C_{max}/C_{min}$  ratio decreases due to parasitic overlap capacitances.

The non-linearity of the varactor is also a problem, because amplitude noise can be converted into phase noise by the varactor [9]. The MOS varactors, with their step-like characteristics, have strong non-linearities. The larger the tuning range and varactor gain, the larger the AM to PM noise conversion. To reduce this effect, a smaller continuously tuned varactor combined with fixed (linear) capacitors that can be switched in and out or the resonator can be used [10]. The small varactor then only has to be large enough to ensure continuous frequency coverage between the different states where different capacitors are switched in.

#### **Source Node Filtering**

Noise from several harmonics and DC (1/f) contribute to the oscillator phase noise around  $\omega_0$ , which is further discussed in section 3.1.2. To improve the phase noise performance a possible implementation of the tail current source is also shown in Figure 6. This source node filtering technique is composed of the source node inductor  $L_s$ , capacitor  $C_s$ , and the FET [11]. The tail current source should have high impedance at  $2\omega_0$ , thus inductor  $L_s$  is to resonate the parasitics of the source node at  $2\omega_0$ , and capacitor  $C_s$  shorts the high frequency noise from the FET to ground. The FET can be used to control the VCO to be in the current-limited region or the voltage-limited region. Usually the best performance is achieved if the VCO is operating in the current limited region, on the border of being in the voltage limited region [12]. This maximizes both the resonator energy and the power efficiency.

The filtering technique described above prevents tail current noise at  $2\omega_0$  from creating phase noise, but low frequency tail current noise can cause amplitude noise which is converted to phase noise by the nonlinearities of the varactor. In [13], a large off-chip inductor ( $L_b$  in Figure 6) is used to suppress also the low frequency 1/f noise.

#### Noise in the MOS transistor

The different noise sources in the MOS transistor determine the achievable noise performance of the front-end. The main sources of noise in the MOS transistor are: thermal channel noise, 1/f noise, gate-induced noise, and noise from parasitic resistances. The thermal noise has a white power spectral density  $(S_{iw})$  and is due to random thermal movement of electrons and holes in the channel.

The low frequency 1/f noise (flicker noise) is the dominating noise source at low frequencies. The origin of the noise is still discussed and different theories exist: random fluctuation of the number of charges in the channel due to the trapping and releasing of charges in the Si-SiO<sub>2</sub> interface [14], and variations in phonon scattering resulting in mobility variations over time [15]. The equivalent gate voltage spectral density is  $S_{vg}(f) \sim 1/(WLf)$ , where it can be seen that the transistor width (W) and length (L) have a large impact on the 1/f noise.

The gate-induced current noise is due to the capacitive coupling of random potential variations in the channel [16],  $S_{ing} \sim (\omega C_{gs})^2$ . The gate-induced current noise increases with the square of frequency, but is typically not a concern in oscillators, even if they operate at high frequencies. In the very common inductively source-degenerated low noise amplifier, on the other hand, this noise is often dominant [17].

A more comprehensive treatment of the MOS transistor and the noise sources in the transistors different regions of operation can be found in e.g. [18].

#### 3.1.2 Phase Noise

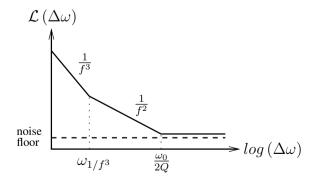

In 1966 Leeson presented an empirical phase noise model [19]. The model covers three regions of the phase noise spectrum;  $1/f^3$ ,  $1/f^2$ , and the thermal noise floor, as illustrated in Figure 7. According to Leeson the phase noise of an oscillator can be modelled by (3),

Figure 7: Phase noise versus offset frequency on a log-log axis

$$\mathcal{L}\left(\Delta\omega\right) = 10 \log_{10} \left\{ \frac{2FkT}{P_s} \cdot \left[ 1 + \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2 \right] \cdot \left( 1 + \frac{\Delta\omega_{1/f^3}}{|\Delta\omega|} \right) \right\}$$

(3)

where  $P_s$  is signal power in the resonance tank,  $\omega_0$  the angular resonance frequency (carrier),  $\Delta\omega$  the angular frequency offset from the carrier, k the Boltzmann constant, and T the temperature in Kelvin. At a given offset frequency the phase noise can be improved by increasing the carrier power in the resonator or the resonator Q value, which appears squared in the model. Another important parameter is the circuit dependent noise factor, F, which is always larger than 1. For the LC oscillator topology in Figure 6, with the ideal current source replaced by an NMOS transistor, an expression for the noise factor (4) was found by Rael [20],

$$F = 1 + \frac{4\gamma RI}{\pi V_0} + \gamma \frac{4}{9} g_{m,cs} R \tag{4}$$

where  $V_0$  is the differential peak to peak voltage in the resonator,  $g_{m,cs}$  the current source transconductance, I the DC current, R the parallel resistance of the resonator at resonance, and  $\gamma$  the transistor channel noise factor which is bias dependent and varies over the oscillation cycle [21]. If we assume that the resonator in Figure 6 is fed with an ideal square wave from the differential pair  $(V_0 = \frac{4}{\pi}RI)$  and assume an ideal noiseless current source, equation (4) simplifies to:

$$F = 1 + \gamma \tag{5}$$

which is the minimum noise factor for the differential LC oscillator.

In 1998, Hajimiri presented a phase noise formula based on the impulse sensitivity function (ISF) [22]. The ISF,  $\Gamma$ , is a dimensionless, frequency- and amplitude-independent periodic function which describes the sensitivity of the oscillator phase to a unit impulse. Hajimiris phase noise formula is shown is (6)-(7) where the 1/f noise is neglected and white noise is assumed.

$$\mathcal{L}(\Delta\omega) = 10 \log_{10} \left( \frac{\frac{\overline{i_n^2}}{\Delta f} \sum_{n=0}^{\infty} c_n^2}{4q_{max}^2 \Delta \omega^2} \right)$$

(6)

$$\sum_{n=0}^{\infty} c_n^2 = \frac{1}{\pi} \int_0^{2\pi} |\Gamma(x)|^2 dx = 2\Gamma_{rms}^2$$

(7)

The coefficients  $c_n$  are real valued coefficients for the different harmonics and  $q_{max}$  is the charge of the resonance tank. Combining (6) and (7) yields (8), which represents the phase noise spectrum of an arbitrary oscillator in  $1/f^2$  region [22].

$$\mathcal{L}(\Delta\omega) = 10 \log_{10} \left( \frac{\Gamma_{rms}^2}{\mathsf{q}_{max}^2} \cdot \frac{\overline{\mathsf{i}_n^2}/\Delta f}{2\Delta\omega^2} \right)$$

(8)

#### 3.1.3 Figures of Merit

The performance of oscillators can be compared by calculating the figure of merit (FOM) [23], which describes the phase noise performance versus power consumption as shown in (9),

$$FOM = 10 \log_{10} \left( \left( \frac{\omega_0}{\Delta \omega} \right)^2 \frac{1}{10^{\frac{\mathcal{L}(\Delta \omega)}{10}} P} \right)$$

(9)

where P is the power consumption of the oscillator in mW. In order also to take the tuning range of the oscillator into account, the expression (9) can be modified to (10), [24].

$$FOM_T = 10 \log_{10} \left( \left( \frac{\omega_0 \cdot tuning(\%)}{10 \cdot \Delta \omega} \right)^2 \frac{1}{10^{\frac{\mathcal{L}(\Delta \omega)}{10}} P} \right)$$

(10)

#### 3.1.4 Survey of Oscillators

The advances in CMOS processing during the last decade has improved the performance of RF ciruits in general, and ocillators in particular. A brief overview of some differential and quadrature oscillators at microwave frequencies will be given in this section. However, more state-of-the-art designs exist than are cited here.

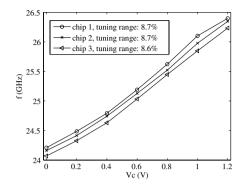

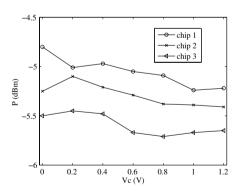

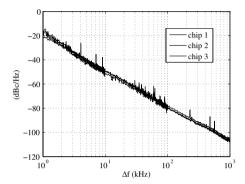

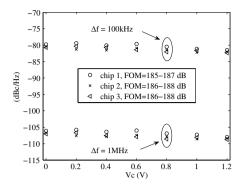

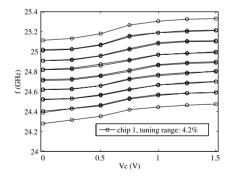

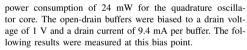

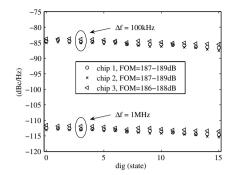

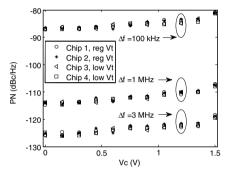

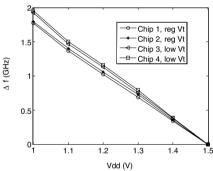

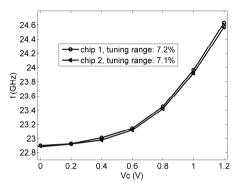

Technology scaling has improved the perfomance of VCOs operating at higher frequencies mainly by improvements in  $f_T$  and  $f_{max}$  resulting in higher transistor switching speed. Thick interconnects also make it possible to design high Q onchip inductors and baluns, thus the varactors are usually the limiting factor for phase noise performance at microwave frequencies. Some microwave CMOS oscillators achieving a high phase noise figure of merit (FOM) are published in: (186dB) [25], (190dB) [26], and (199dB) [27]. The oscillator in [27] is fabricated in a 90nm CMOS process, but it is also postprocessed using a high-Q inductor on top of insulating Benso-Cyclobutene (BCB) material, which minimizes the substrate losses. A CMOS LC-VCO, using an accumulation mode varactor, achieving a FOM between 185-188dB is demonstrated in Paper II. In Paper V a 24GHz LC-VCO, using a high Q glass carrier inductor and two cascaded frequency doublers, achieves a wide 20% tuning range combined with a FOM of 191dB.

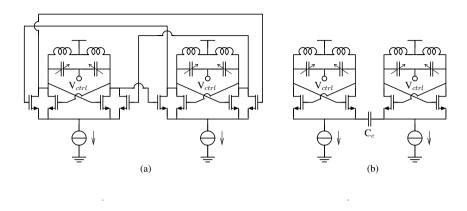

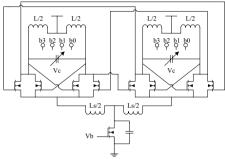

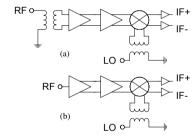

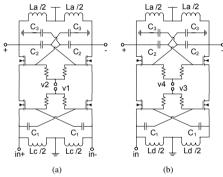

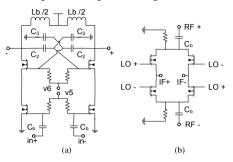

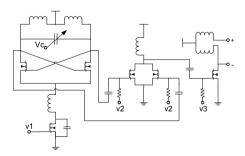

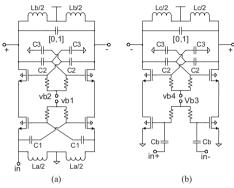

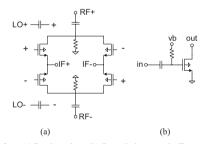

Modern radio receivers with direct conversion or low-IF architectures require quadrature LO signals. The quadrature LO generation can be done in a number of different ways: one is to use quadrature voltage controlled oscillators (QVCOs). The original QVCO topology proposed in [28] is shown in Figure 8(a). The two LC-VCO cores are locked to oscillate in quadrature through coupling transistors in parallell with the switch transistors. This topology is commonly referred to as the P-QVCO. In Figure 8(b) the two LC-VCOs are locked to oscillate in quadrature through the source node coupling capacitor  $C_c$ , [29]. Another common QVCO topology is the series coupled QVCO, S-QVCO, which was proposed in [30]. The S-QVCO topology has the coupling transistors stacked in series with the switch transistors, with their gates

3.2 LNAs & Mixers 19

**Figure 8:** (a) The original QVCO. (b) QVCO coupled to oscillate in quadrature by means of  $C_c$

connected to the other LC resonance tank. Other LC-QVCO topologies have also been proposed, however, they are similar to those described since they are all based on the idea of injection locking two LC-VCOs to operate in quadrature. The quadrature signal generation can also be performed by converting the differential output signal from a VCO to a quadrature signal with a passive or active polyphase filter [31–33]. This approach typically occupies less area than a QVCO, but the passive polyphase filter attenuates the signal and may require buffer amplifiers, whereas the active polyphase filter can have a high power consumption. Another approach is to feed the differential VCO output signal to a frequency divider, obtaining a quadrature signal at half the VCO frequency. The double frequency VCO and divider occupy much less area than a QVCO, however, the frequency divider can have a substantial power consumption and be very difficult to realize at microwave frequencies.

QVCOs based on the topologies in Figure 8(a) and (b) are demonstrated in Papers III and VI, respectively.

#### 3.2 LNAs & Mixers

In the receiver front end the signal from the antenna is first passed through a band select filter (BSF) before entering the low noise amplifier (LNA). The purpose of the BSF is to attenuate out-of-band interferers. In-band interference, however, will not be suppressed, and the LNA must thus be able to amplify weak signals in presence of strong in-band interferers. It has to provide sufficient amplification to overcome the noise of subsequent stages, while itself adding as little noise as possible. To meet the requirements of the preceeding filter, the LNA also has to provide a resistive input impedance, often  $50\Omega$ . The purpose of the mixer is to frequency downconvert

the signal, since at lower frequency it is easier to implement gain, filtering and demodulation. Like the low noise amplifier, the mixer should have a low noise and high linearity. Since the signal is amplified by the LNA before reaching the mixer, the linearity is generally most critical in the mixer.

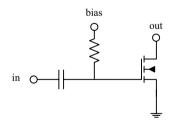

#### 3.2.1 The CS & CG LNAs

This section describes the common-source (CS) and common-gate (CG) low noise amplifiers. The amplifiers described here use differential topologies, since these are used in the front-ends of the included papers. In general, differential topologies are known to have better linearity and stability than their single-ended counterparts, at the expense of higher power consumption, chip area, and possible need for baluns.

#### The CS LNA

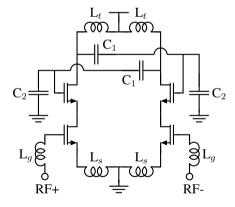

A differential CS amplifier is shown in Figure 9. The CS amplifier is the topology that provides the best noise performance at frequencies well below the transit frequency,  $\omega_T$ . The input forms a series resonance circuit composed of  $L_g$ ,  $L_s$ , and  $C_{gs}$ . At resonance the input impedance is resistive, given by (11).

Figure 9: Differential CS LNA using capacitive cross coupling

$$Z_{in,res} = \frac{g_m}{C_{qs}} L_s = \omega_T L_s \tag{11}$$

As can be seen the input impedance is proportional to the source inductance  $L_s$ . Impedance match can thereby be achieved by choosing  $L_s$  properly. The gate inductance  $L_g$  is then chosen to resonate with  $L_s$  and  $C_{gs}$  at the operating frequency  $\omega_0$  according to (12).

3.2 LNAs & Mixers 21

$$L_g = \frac{1}{\omega_0^2 C_{qs}} - L_s \tag{12}$$

If the Q factor of the input series resonance circuit (13) is high the input is quite narrow band. A high Q will also make the voltage gain Q times higher compared to the CG amplifier and result in reduced input referred thermal noise from the transistor. Unfortuanately it will also degrade the linearity, increase the sensitivity to the input matching, and increase the input referred gate induced noise.

$$Q = \frac{1}{2R_s\omega_0 C_{as}} \tag{13}$$

The minimum noise factor for an impedance matched CS LNA is given in (14),

$$F_{min,CS} = 1 + \frac{2\omega_0}{\sqrt{5}\omega_T} \sqrt{\gamma \,\delta\left(1 - |c|^2\right)} \tag{14}$$

where the parameters for a long channel device are typically:  $\gamma$  equal to 2/3,  $\delta$  equal to 4/3, and the correlation coefficient for drain and gate induced noise |c| equal to 0.395, [34]. For short channel devices, the parameters for  $\gamma$  [35] and  $\delta$  [18] can be considerably larger. The noise factor of a source degenerated CS amplifier was also studied in [17]. The expression derived for  $F_{min}$ , with a given Q for the series input resonance circuit, is shown in (15). Note that in this work an additional lossless capacitor is inserted between the gate and source. This reduces the contribution of the gate-induced noise, however, at the cost of reduced gain, which makes this technique less attractive at microwave frequencies.

$$F_{min,CS} \approx 1 + \frac{1}{Q} \cdot 4\beta'^{1/4} \left(\frac{\gamma'}{12}\right)^{3/4} \sqrt{\frac{2\omega_0}{3\mu'_{eff}R_sI_{ds}}} L \tag{15}$$

In (15),  $\beta'$  represents the gate induced noise factor,  $\gamma'$  the channel current noise factor,  $R_s$  the generator resistance, and L the channel length of the transistor [17].

The effective transconductance for an impedance matched, source inductor degenerated, CS amplifier is given in (16) [3]. As can be seen in the equation a high effective transconductance requires a high  $\omega_T/\omega_0$  ratio. The transit frequency, and thus the effective transconductance, will improve with technology scaling. This will result in improved high frequency gain.

$$G_{m,CS} = \frac{1}{2R_s} \cdot \frac{g_m}{C_{qs}\omega_0} = \frac{1}{2R_s} \cdot \frac{\omega_T}{\omega_0}$$

(16)

The CS input transistor can be stacked with a cascode CG transistor as shown in Figure 9. The CG transistor increases the isolation between the input and output of the LNA, which results in improved stability and reduced LO leakage. Unfortunately,

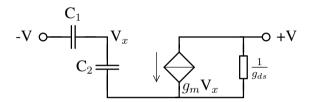

at microwave frequencies short channel length transistors must be used for high frequency performance, resulting in poor isolation due to an increased drain-source conductance  $(g_{ds})$ . Also shown in Figure 9 is a capacitive cross coupling technique using capacitors  $C_1$  and  $C_2$ . This capacitive cross-coupling is used to increase the differential isolation by cancelling the currents due to the drain-source conductance for differential signals. By using the simplified small signal schematic in Figure 10 it can be shown that cancellation is achieved when the capacitance ratio  $C_2/C_1$  is equal to the cascode transistor intrinsic gain minus one (17).

Figure 10: Small signal schematic illustrating capacitive cross coupling

$$\frac{C_2}{C_1} = \frac{g_m}{g_{ds}} - 1 \tag{17}$$

There are also some drawbacks with the cascode transistor. It reduces the voltage headroom and adds noise. With increasing frequency the impedance of the node between the CS and CG transistors drops due to parasitic capacitance, which makes the topology more sensitive to noise from the cascode transistor. However, the parasitic capacitance can be minimized by a layout where the CS transistor drain and CG transistor source junctions are shared [36]. The result is a 'double-gate' device with low parasitic capacitance. The topogy in Figure 9, utilizing a 'double-gate' device, is used in the front-end of Paper I.

#### The CG LNA

The CG amplifier provides a more broadband input matching. A single CG transistor amplifier has a resistive input impedance that equals  $1/(g_m + g_{mb}) \approx 1/g_m$  (neglecting the load resistance) when the parasitic capacitance at the source node is resonated by an inductor. The input becomes quite broadband since the Q of the input is fairly low, the parallel resonance circuit being loaded by the input resistance,  $1/g_m$ . A commongate amplifier has a minimum noise factor given by (18) [3],

$$F_{min} = 1 + \frac{\gamma}{\alpha} \cdot \frac{1}{g_m R_s} = 1 + \frac{\gamma}{\alpha} \tag{18}$$

where input impedance matching is assumed and  $\alpha$  is equal to  $g_m/g_{ds0}$ , with  $g_{ds0}$  being the drain-source conductance at  $V_{DS}=0$ . For long channel devices  $\alpha$  is equal

3.2 LNAs & Mixers 23

to one, but it is reduced for short channel devices [18].

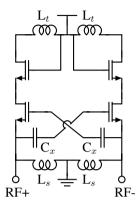

Figure 11: Differential CG LNA using capacitive cross coupling

A differential CG amplifier is shown in Figure 11, where a differential source node inductor is used to resonate the input parasitics. A capacitive cross-coupling technique using capacitors  $C_x$  is also employed, where capacitors  $C_x$  are larger than  $C_{gs}$ . The capacitive cross-coupling has many benefits as it improves the gain and noise performance of the CG amplifier [37, 38]. The effective transconductance is doubled (19), and the noise from the input transistors can thereby be reduced (20). The effective input impedance at resonance is given by (21) [38].

$$G_{m,CG} = 2q_m \tag{19}$$

$$F_{min,CG} = 1 + \frac{\gamma}{2\alpha} \tag{20}$$

$$Z_{in,CG,res} = \frac{1}{2g_m} \tag{21}$$

The expression for the noise factor (20) assumes that the input impedance is matched to the source impedance for maximum power transfer. However, if some mismatch can be accepted, a lower noise factor can be obtained by increasing  $g_m$ . This was demonstrated in [39], where a noise figure reduction of 1.4dB was achieved by accepting an  $S_{11}$  of -12dB.

The differential CG LNA of Figure 11, also using the capacitive cross-coupling of Figure 9 at the output for increased differential isolation, is demonstrated in the frontends of Papers IV and VI. The front-end in Paper IV also presents a novel merged LNA and balun using a CG input stage.

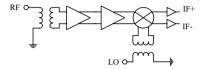

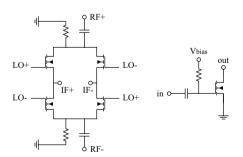

#### 3.2.2 The Gilbert Cell & Passive Mixers

The purpose of the mixer in a receiver front-end is to downconvert the RF signal to a lower frequency, where it is easier to apply amplification, filtering and detection. Transistor based mixers dominate in integrated circuits thanks to their high performance. In this section the double-balanced active Gilbert and passive mixers, both MOS transistor based, are briefly treated. The term double-balanced means that the RF, LO, and IF signals are all differential. The undesired LO signal component is then cancelled at the IF output thanks to mixer symmetry.

#### Gilbert mixer

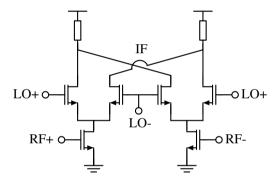

The double-balanced active Gilbert mixer is depicted in Figure 12. The RF input voltage is first converted to an RF signal current by the input transistors. The mixing action is then achieved by switching the RF current so that it is connected either straight or cross-coupled to the differential load.

Figure 12: Double-balanced Gilbert mixer

By assuming that the LO-driven transistors behave as perfect switches, the differential output current can be regarded as the multiplication of the current from the transconductor with a unit amplitude square wave at the LO frequency. From a Fourier expansion the fundamental tone amplitude of the square wave can be found and the conversion transconductance calculated (22) [3].

$$G_{conv} = \frac{2}{\pi} g_m \tag{22}$$

The Gilbert mixer is active and therefore it can provide power gain. The draw-back is that it consumes DC power, and that it generates 1/f noise. The 1/f noise is particularly harmful in homodyne receivers, and is generated mainly by the random modulation of the conduction angle of the switches (the time instants of mixer

3.2 LNAs & Mixers 25

switching) [40]. Other important noise sources are the channel thermal noise of the transistors, and noise of the load itself. The switch transistors produce most noise during switching, when all switches are on simultaneously. A larger LO amplitude shortens the switching time, and thereby reduces the noise. It is difficult to calculate the noise figure of mixers by hand due to the large signal operation involved, so special methods have been developed e.g. [41]. The linearity is also difficult to predict by hand, but it is investigated in [42] by treating the mixer as a periodically time-varying weakly nonlinear circuit.

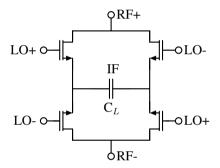

#### Passive mixer

The passive double-balanced mixer is shown in Figure 13. Contrary to the current mixing used by the Gilbert mixer, voltage mixing is performed by the passive mixer. Note, however, that by using a low impedance IF load also the passive mixer can be operated in the current mode.

Figure 13: Double-balanced passive mixer

The on-chip load is usually capacitive and the conversion gain (loss) is dependent on the wave form of the LO signal. For a square wave LO signal the conversion gain is given by (23), whereas the voltage gain is higher for a sinusoidal LO drive (24) [3].

$$A_{cv,sq} = \frac{2}{\pi} \tag{23}$$

$$A_{cv,sin} = \frac{\pi}{4} \tag{24}$$

The on-resistance of the switches occurs in series with the load. A certain transistor width is therefore required to meet the noise requirements. Both the noise figure and linearity (IP3) depend on the width of the switches and the LO drive, since the on-resistance must be low and constant [3]. A bootstrapping technique to improve

the linearity by making the on-resistance less signal dependent is proposed in [43]. A detailed analysis of the passive mixer is found in [44].

Compared to the Gilbert mixer the passive mixer has better linearity, does not consume DC power, and has no 1/f noise. However, the passive mixer does not provide power conversion gain. The choice of which type of mixer to use for a receiver depends on the system requirements. In the front-end designs of Papers I, IV, and VI, low 1/f noise was of high importance, therefore a passive mixer topology was used.

#### 3.3 Front-end imperfections

As described earlier the main performance parameters of the front-end are those related to the gain, noise figure, and linearity. The power consumption is, of course, also a very important parameter, especially for battery operated devices. The following sections describe how the front-end noise figure and linearity can be calculated, and which blocks of the front-end have most influence on different performance parameters.

#### 3.3.1 Noise Figure

Noise limits the sensitivity of the receiver front-end, which can be defined as the minimum input signal amplitude required to produce an output signal with the minimum signal-to-noise ratio needed to detect the transmitted information. The noise ratio or noise factor for any system can be described according to (25),

$$NR = \frac{(S/N)_i}{(S/N)_o} \tag{25}$$

where the  $(S/N)_i$  and  $(S/N)_o$  is the signal-to-noise ratio measured at the input and output, respectively. In [45] Friis presented a formula (26) to calculate the total noise factor for a system consisting of n cascaded blocks,

$$NR_{tot} = NR_1 + \frac{NR_2 - 1}{A_{p,1}} + \frac{NR_3 - 1}{A_{p,1}A_{p,2}} + \dots + \frac{NR_n - 1}{A_{p,1}A_{p,2} \dots A_{p,n-1}}$$

(26)

where  $NR_x$  and  $A_{p,x}$  represent the noise factor and available power gain of block x, numbered from the antenna, respectively. As can be seen in (26), a high front-end noise performance requires a high gain and low noise in the first block, the LNA. If the LNA gain is high, noise from subsequent stages will have less influence, and  $NR_{tot}$  is dominated by the noise from the LNA. The noise figure (NF) is the decibel equivalent of the noise ratio,  $NF = 10 \log (NR)$  [46].

#### 3.3.2 Linearity

The linearity of RF front-ends is measured for intermodulation (IM) distorsion, rather than harmonic distorsion like in audio amplifiers, due to the rather low bandwidth

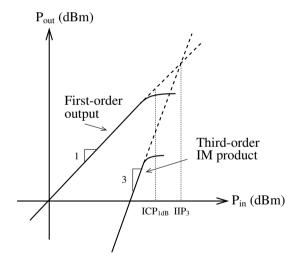

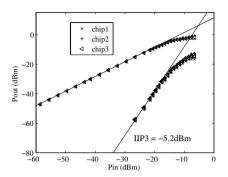

to carrier frequency ratio of typical receiver front-ends. The linearity of the frontend puts a limit to how strong in-band interferers can be handled. For differential topologies the distorsion is usually dominated by the third-order IM product. Other odd-order IM producs also exist but third order typically dominates. Two tones at the input with frequencies  $f_1$  and  $f_2$  can produce downconverted third-order IM products in the wanted frequency band at the output with frequencies  $f_{LO} - (2f_2 - f_1)$  and  $f_{LO} - (2f_1 - f_2)$ . The third-order IM products can be plotted in the intercept diagram of Figure 14. The figure shows the power at the output of the first-order (linear) outputs and of the third-order IM product. They are shown on a logarithmic scale versus input power. The 1dB compression point, usually called ICP<sub>1dB</sub> when referred to the input, is defined when the first order output power (at  $f_{LO} - f_1$  and  $f_{LO} - f_2$ ) deviates by 1dB from the ideal (linear) extrapolated line. The third-order intercept point is defined as where the two extrapolated lines from the first-order output and third-order IM product cross. The input referred third-order intercept point IIP<sub>3</sub> is also shown in Figure 14. Even-order IM products also exist. Typically they cause disturbancies at or near DC due to rectification of amplitude modulated interferers, which is a major concern in direct conversion receivers. Fortunately even-order nonlinearities can be kept small by the use of differential (balanced) topologies, where the IP<sub>2</sub> is usually limited by mismatch between differential paths. To calculate the linearity requirements it is necessary to know what worst case scenarios must be handled, that is what sensitivity level must be maintained for different interference.

Figure 14: Intercept diagram

The dynamic range of the front-end can be defined as the input power range where the front-end is useful, with the lower limit set by the noise floor and the upper limit by the compression point.

In terms of linearity, a total IIP $_3$  of the front-end can be calculated if the gain and IIP $_3$  is known for all the included blocks (27) [2, 3],

$$\frac{1}{\text{IIP}_{3,tot}^2} = \frac{1}{\text{IIP}_{3,1}^2} + \frac{A_{v,1}^2}{\text{IIP}_{3,2}^2} + \dots + \frac{(A_{v,1}A_{v,2} \dots A_{v,n-1})^2}{\text{IIP}_{3,n}^2}$$

(27)

where  $A_{v,x}$  is the voltage gain of block x. The equation shows that, contrary to (26), the gain of the first stage should be low to get a high  $IIP_{3,tot}$ . Thus, a trade-off has to be made as simulataneous optimization for low noise and high linearity is not possible. Note that in equation (27) no filtering is assumed between the blocks, whereas in a practical radio receiver progressively sharper filtering is typically applied through the signal chain.

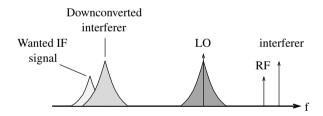

#### 3.3.3 Phase Noise - Reciprocal Mixing

The oscillator should have good spectral purity, i.e. low phase noise. Otherwise a strong in-band interferer, close to the wanted RF signal, can be down-converted and smeared out in frequency. The down-converted interferer could then partly mask or completely overlap the wanted RF signal, resulting in erroneous detection of the transmitted information in the receiver. This is known as reciprocal mixing and is illustrated in Figure 15.

**Figure 15:** An illustration of reciprocal mixing

#### 3.3.4 Imperfections exposed on the received information

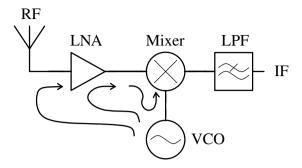

The isolation between different blocks of the front-end is important as leakage can cause DC offsets at the mixer output due to the LO or the RF signal mixing with itself. This is usually referred to as self-mixing and is illustrated in the block diagram of Figure 16. The LO signal can leak to the mixer or LNA input and result in a DC offset after being mixed with itself. Similarly, the RF signal can leak to the LO input and

**Figure 16:** Front-end self-mixing

cause a DC offset. The leakage on-chip is usually through substate coupling, capacitive coupling, or even inductive coupling. The DC offsets can saturate the following low frequency amplifiers and the ADC. It is particularly harmful in direct conversion receivers as was described in section 2.2.3.

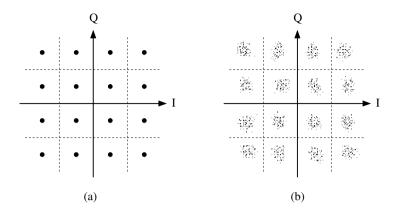

Quadrature amplitude modulation (QAM) is a common modulation scheme used in wireless communication systems. An ideal constellation diagram, using 16-QAM, is shown in Figure 17(a). Each dot in the figure is a symbol value. Each symbol represents 4 bits, since it can have  $2^4$  different values. Also shown, with dashed lines, are the decision boundaries. If noise is added in the front-end, the constellation diagram could look like in Figure 17(b), where the dots in the noise clouds represent different received symbols. The noise makes error free detection hard, especially close to the decision boundaries. Additionally, the constellation diagram is also affected by oscillator phase noise (through random phase variations) and interferers (through front-end non-linearities and limited filter selectivity), making it even harder to detect the transmitted information correctly.

Since the transmitted information typically includes redundant information through coding, the transmisson and the detection do not have to be entirely error free. However, a certain maximum bit error rate (BER) is in general specified for a digital communication system.

#### 3.4 Survey of Front-ends

A short overview of some state-of-the-art microwave and millimeterwave front-ends is given in this section along with a description of the front-ends included in this thesis. More state-of-the-art designs exist than can be cited here.

In 2002 Guan *et al.* [47] presented a 24GHz CMOS receiver front-end achieving 27.5dB conversion gain and 7.7dB NF at 5GHz IF while dissipating 64.5mW. In the following years a lot of research was put into CMOS front-ends, also to push them to higher frequencies [48–51]. The 65nm CMOS front-end in [51], also including an on-

**Figure 17:** 16-QAM constellation diagrams, (a) ideal and (b) perturbed by noise

chip ADC, achieves a NF of 7dB at 60GHz with 198mW power consumption ( $P_{DC}$ ). Using GaAs mHEMT technology Gunnarsson *et al.* in [52] demonstrated a 60GHz receiver with a 12.9dB conversion gain and 7.2dB NF at 450mW  $P_{DC}$ , and in [53] a 220GHz MMIC receiver achieving 8.4dB NF.

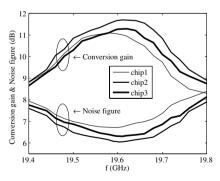

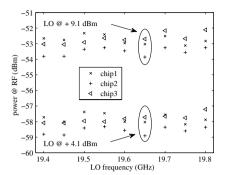

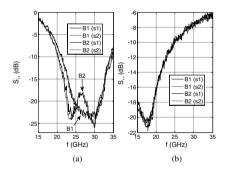

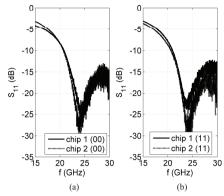

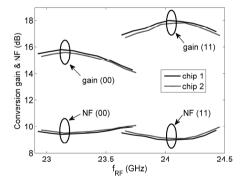

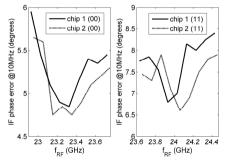

The fully differential front-ends of Papers I and IV use low loss baluns on a glass carrier (covered in Chapter 4) to generate the differential LO and RF input signals. A single-ended RF input front-end is also demonstrated in Paper IV, where only an LO input balun is used on the carrier. The front-end in Paper I uses a common source topology for the input LNA stage and achieves an overall NF of 7dB at 38mW  $P_{DC}$ , whereas the more broadband common gate topology is used in Paper IV. The fully differential front-end of Paper IV achieves 21dB conversion gain and 7.8dB NF at 28.6mW  $P_{DC}$ , and the one using single-ended RF input achieves 15dB conversion gain and 8.5dB NF at 33.8mW  $P_{DC}$ .

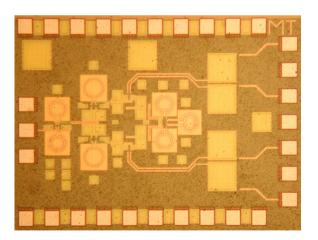

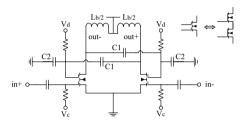

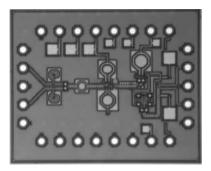

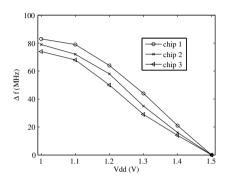

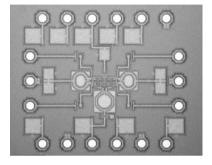

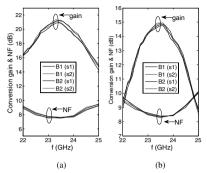

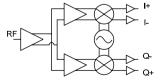

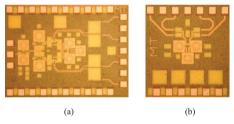

An on-chip quadrature receiver front-end at 24GHz in 90nm CMOS (including QVCO) is demonstrated in Paper VI, the front-end die photograph is shown in Figure 18. The RF input is single-ended, but is converted to differential form in the first LNA. The LNAs have two bands of operation within the QVCO tuning range, and the front-end measures 18dB conversion gain and 8.9dB NF at 64mW  $P_{DC}$  in the higher band.

The performance of the microwave and millimeter wave receiver front-ends is summarized in Table 1.

| Ref.     | Technology                       | f     | NF   | Gain   | $IIP_3$ | ICP <sub>1dB</sub> | P <sub>DC</sub> |

|----------|----------------------------------|-------|------|--------|---------|--------------------|-----------------|

|          |                                  | (GHz) | (dB) | (dB)   | (dBm)   | (dBm)              | (mW)            |

| Paper I  | $0.13 \mu m$ CMOS SOP            | 20    | 7.0  | 11     | -5.2    | -16                | 38              |

| Paper IV | $0.13 \mu \text{m}$ CMOS SOP     | 24    | 7.8  | 20.7   | -12.6   | -23.3              | 28.6            |

| Paper VI | 90nm CMOS                        | 24    | 8.9  | 18     | -11     | -23                | 64              |

| [47]     | $0.18\mu\mathrm{m}$ CMOS         | 24    | 7.7  | 27.5   |         |                    | 64.5            |

| [48]     | $0.13 \mu \text{m CMOS}$         | 60    | 12.5 | 28*    |         | -22.5              | 9               |

| [49]     | 90nm CMOS                        | 60    | 8.4  | 22     |         |                    | 144             |

| [50]     | 65nm CMOS                        | 60    | 9.2  | 14.5   |         | -24.4              | 134             |

| [51]     | 65nm CMOS                        | 60    | 7.0  | 45-79* |         | -38.5              | 198             |

| [52]     | $0.15 \mu \mathrm{m}$ GaAs mHEMT | 60    | 7.2  | 12.9   | -10     | -17                | 450             |

| [53]     | $0.1 \mu \mathrm{m}$ GaAs mHEMT  | 220   | 8.4  | 1.8    |         |                    |                 |

**Table 1:** Some published receiver front-end results

Figure 18: Quadrature receiver front-end in 90nm CMOS

<sup>\*</sup>Voltage gain

## **Chapter 4**

## **System-on-Package Technology**

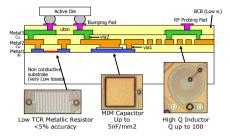

The performance of the different building blocks in CMOS front-ends is usually limited by the on-chip passive components. Unfortunately the passive components also have a high cost since they, mainly inductors, occupy a majority of the integrated circuit area. Even with the rapid technology scaling, with Moore's law saying that the number of transistors will double on a given circuit area about every two years, the passive components do not scale much. The following sections therefore discuss on-chip passives, postprocessed inductors, and carrier technology for System-on-Package (SOP) .

#### 4.1 On-Chip Passives

As was mentioned above the on-chip passive components usually limit the performance due to their low Q values. For monolithic inductors the losses are due to the series resistance of the metal trace and resistive losses in the substrate due to capacitive and inductive coupling. The losses of the wire can be lowered by using a top metal with thick copper metallization instead of aluminum, however, this is not always supported by the foundries for standard fabrication processes. By shunting more metal levels the resistance can also be lowered, but this unfortuanately increases the capacitive coupling and lowers the self resonance frequency of the inductor. To reduce the substrate losses a high resistivity, lightly doped, substrate can be used. Furthermore, a patterned ground shield in the poly or metal 1 layer can be used to block the capacitively coupled substrate losses at the expense of a slightly reduced inductor self resonance frequency.

Inductors can be realized with a number of different geometries e.g. spiral, differential, bondwire, or transmission line stubs. Differential geometries are preferred over spriral since they occupy less area for a given inductance, and can have a higher Q value. Bondwire inductors have high Q but the inductance is hard to predict accurately due to uncertainty of the bondwire length, thus they are seldom used at high frequencies. The transmission line stubs also offer fairly high Q and are more common in millimeter-wave circuits, where their length is short enough to be practical. The quality factor of on-chip inductors tends to increase with operating frequency, as the equivalent series resistance increases less with frequency than the reactance.

For MOS varactors on the other hand the Q value is inversely proportional to

frequency. The reason is that the losses are dominated by the frequency independent series resistance, and that the reactance of a capacitor is inversely proportional to the frequency. The Q will, however, improve with technology scaling as the channel gets shorter, but the capacitance tuning ratio will also drop since parasitics will then have more impact on the overall capacitance. The varactor Q is usually limiting the phase noise performance for microwave and millimeter wave oscillators. More about MOS varactors can be found in section 3.1.1.

#### 4.2 Postprocessed Inductors

By placing the inductors on top of the back-end-of-line (BEOL) metal layers the distance to the chip substrate is increased, which results in higher Q. It is performed by depositing a thick dielectric, usually BCB, and metal above the BEOL passivation layer. This is also referred to as postprocessing or wafer level packaging (WLP). Due to the lower resolution requirements, the mask cost is lower for WLP than for a standard IC process. In [27] a microwave CMOS VCO achieved a FOM of 199dB using postprocessed inductors. A patterned ground shield can also be used, with great benefit, with a postprocessed inductor as demonstrated in [54], where the Q factor of a 1.4nH inductor at 5GHz was doubled to 40 by the use of a patterned ground shield in the poly layer.

#### 4.3 Carrier Technology

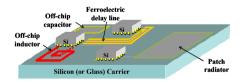

Moving the passives completely off-chip to a low loss carrier is another feasible way to achieve high Q passive components. The general idea of the System-on-Package (SOP) concept [55] is to improve the performance by moving critical passive components from the chip to a low loss carrier. Depending on the carrier technology different components can be realized, e.g. inductors, baluns, capacitors, antennas, and tunable ferroelectric components.

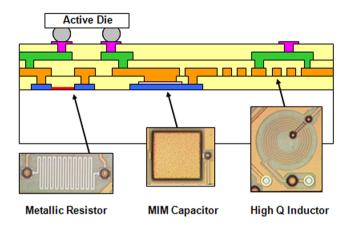

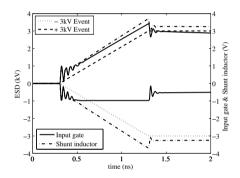

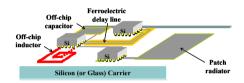

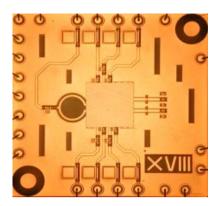

The process stack-up of the glass carrier technology used in the SOP designs of Papers I, IV, V, is shown in Figure 19 [56]. As can be seen in the figure the active die is flip-chip mounted to the glass carrier, which is optimized for high Q RF passive components. The carrier features three metal layers on a non conductive substrate which offers very low losses. Different high Q components can be realized, e.g. metallic resistors (with better than 5% accuracy), MIM capacitors (up to 5nF/mm²), and high Q thick copper inductors (Q up to 100).

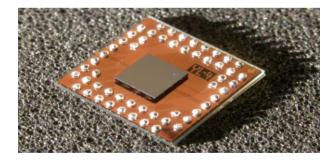

Flip-chip mounting is used extensively in high performance applications and is the method of choice for silicon microwave circuits. Soldering is typically used to join the active die - stud bump - carrier, since it offers high reliability, self-alignment, and a good electrical connection [57]. The chip to carrier assembly can be done with a standard pick and place machine for SMD components before the package is put through the oven. The carriers can also be bumped for flip-chip mounting on a common motherboard (PCB), see Figure 20.

Figure 19: Process stack-up (STMicroelectronics)

Figure 20: Bumped carrier for flip-chip mounting on a motherboard [58]

Reliable models for the chip to carrier transitions are vital at microwave frequencies, otherwise package parasitics can seriously degrade the performance. The stud bumps used have a height of  $50\mu m$ . According to EM simulations the transition from chip to a  $50\Omega$  line on the carrier can be modelled by a shunt capacitance of 60-70fF, dependent on e.g. line distance to signal ground and the position of bridges over CPW lines.

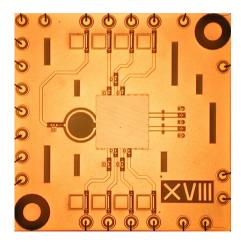

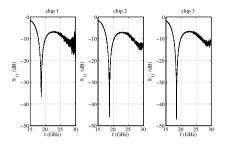

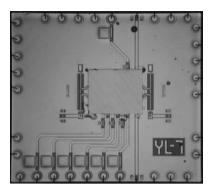

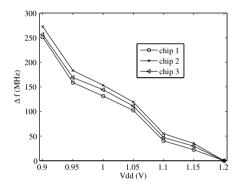

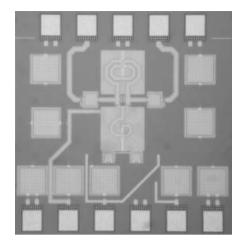

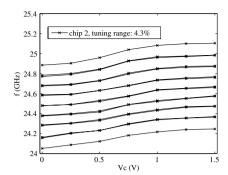

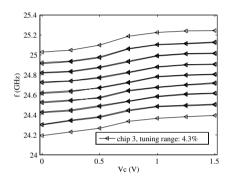

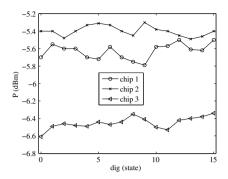

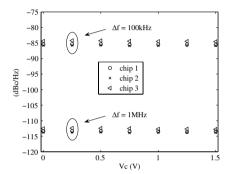

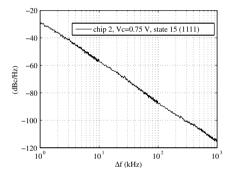

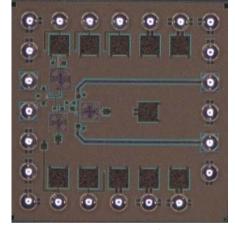

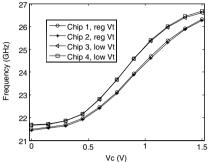

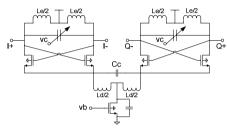

A SOP 24GHz VCO with 20% tuning range (Paper V) is shown in Figure 21. The oscillator core operates at 6GHz and is followed by two cascaded on-chip frequency doublers. The oscillator core utilizes a differential high-Q inductor on the carrier, which is visible to the left of the chip. The lower core frequency reduces the impact of package transition parasitics and the losses due to large on-chip MOS varactors as the Q is inversely proportional to frequency. The VCO output was probe measured on the carrier and the DC signals were wirebonded to a PCB. The VCO achieves an FOM of 191dB and an FOM $_T$  of 197dB, which is comparable to [59] where ferroelectric varactors were used to achieve an FOM of 191dB and an FOM $_T$  of 195dB. The ferroelectric varactors have low losses (Q higher than 50) but they require high control voltages [60].

Figure 21: 24GHz 20% tuning range SOP VCO (5x5mm<sup>2</sup>)

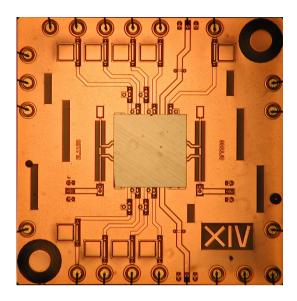

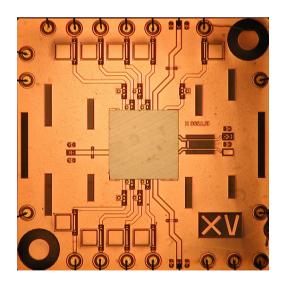

A fully differential 24GHz CMOS front-end (Paper IV) using low loss baluns on carrier is shown in Figure 22. The baluns are used generate differential RF and LO input signals to the chip, and they exhibit an insertion loss of only 0.3dB at the frequencies of interest. In measurements the RF and LO signals were connected by Cascade Infinity GSG probes, whereas the DC and low frequency IF signals were wirebonded from the carrier to a PCB. A SOP front-end using single-ended (SE) input and another type of balun for the LO signal (Paper IV) is depicted in Figure 23, where the RF input CPW line can be seen to the left of the chip.

**Figure 22:** A fully differential SOP front-end (5x5mm<sup>2</sup>)

**Figure 23:** A SOP front-end with SE input (5x5mm<sup>2</sup>)

### Chapter 5