# LUND UNIVERSITY

### **Electrical Characterization of Integrated InAs Nano-Structures**

Astromskas, Gvidas

2010

#### Link to publication

Citation for published version (APA): Astromskas, G. (2010). Electrical Characterization of Integrated InAs Nano-Structures. Lund University (Media-Tryck).

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00 THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ENGINEERING

### ELECTRICAL CHARACTERIZATION OF INTEGRATED INAS NANO-STRUCTURES

### GVIDAS ASTROMSKAS

# LUNDS UNIVERSITET

### Lunds Tekniska Högskola

Division of Solid State Physics LTH 2010

| Organization<br>LUND UNIVERSITY                                     | Document name<br>DOCTORAL DISSERTATION |  |

|---------------------------------------------------------------------|----------------------------------------|--|

| Deparment of Solid State Physics<br>Division of Solid State Physics | Date of issue November 4, 2010         |  |

| Box 118<br>S-221 00 Lund<br>Sweden                                  | Sponsoring organization                |  |

| Author(s)<br>Gvidas Astromskas                                      |                                        |  |

| Title and subtitle                                                  |                                        |  |

Electrical characterization of Integrated InAs nano-structures

Abstract

This thesis analyzes the electrical properties of InAs nano-structures, that are integrated into different materials and geometries. The thesis describes integration related issues of InAs, the epitaxial synthesis of the InAs nano-structures and summarizes experimental techniques for analysis of electrical properties of the integrated structures. InAs thin films, nanowires and membranes are investigated to determine their electrical quality.

The thin films (> 300 nm thick) are integrated onto GaAs substrates using overgrowth over the tungsten patterns. Such integration method allows varying the area of the surface pinning region within the material to measure the extent of this region in InAs. A carrier saturation is observed when the tungsten density is increased which allows determining the effective length of the surface pinning region to be under 400 nm.

InAs nanowire capacitors are investigated to measure their doping density and doping profile. The capacitance of the nanowire capacitors exhibits non parabolic band behavior and a full depletion, in contrast to conventional MOS capacitors. The threshold voltage of the fully depleted nanowires is extracted to determine doping density and dopant distribution profile within a nanowire. It is shown that dopants incorporate preferentially at the nanowire surface and the surface doping concentration is higher than in the nanowire bulk. Also, capacitance transients are analyzed to show the presence of traps in the oxide.

InAs metamorphic films are integrated onto GaSb buffer layer to evaluate the relation between the quality of the buffer layer and the InAs. It is observed, that metamorphic InAs membranes (23 nm thick) are highly resistive, while thicker membranes (90 nm thick) can be measured by Hall Effect measurements. The mobility of 90 nm membranes is found be 2700 cm2/Vs, which indicates a loss of the metamorphic lattice. It is shown that the resistivity of thin membranes is highly sensitive to surface treatment.

Key words: InAs, Fermi level pinning, GaSb, overgrowth, Hall mobility, nanowire capacitance, DLTS, threshold voltage, epitaxial growth

Classification system and/or index termes (if any):

| Supplementary bibliographical information: |                         | Language<br>English       |

|--------------------------------------------|-------------------------|---------------------------|

| ISSN and key title:                        |                         | ISBN<br>978-91-7473-062-3 |

| Recipient's notes                          | Number of pages         | Price                     |

|                                            | Security classification |                           |

Distribution by (name and address)

I, the undersigned, being the copyright owner of the abstract of the above-mentioned dissertation, hereby grant to all reference sources permission to publish and disseminate the abstract of the above-mentioned dissertation.

Signature

Date 2010 11 04

THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ENGINEERING

### ELECTRICAL CHARACTERIZATION OF INTEGRATED INAS NANO-STRUCTURES

### **GVIDAS ASTROMSKAS**

### LUNDS UNIVERSITET

Lunds Tekniska Högskola

DIVISION OF SOLID STATE PHYSICS LTH, LUND UNIVERSITY SWEDEN 2010

FACULTY OPPONENT: PROFESSOR CARL-MIKAEL ZETTERLING

Academic dissertation which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Tuesday, the  $14^{th}$  of December 2010, at 10.15 in lecture hall B, at the Department of Physics, Sölvegatan 14A, Lund.

Electrical characterization of integrated InAs nano-structures

Division of Solid State Physics Faculty of Engineering Lund University PO Box 118 SE-221 00 Lund Sweden

© Gvidas Astromskas 2010 All rights reserved Printed in Sweden by Mediatryck, Lund, 2010

# LIST OF PUBLICATIONS

This thesis is based on the following peer-reviewed publications and submitted manuscripts, which are appended at the end of this thesis. The author's contribution is described below each article.

### Paper I: Electrical characterization of thin InAs films grown on patterned W/GaAs substrates

Gvidas Astromskas, L. Reine Wallenberg, and Lars-Erik Wernersson Journal of Vacuum Science and Technology B 27 (2009) 2222

I made the W patterned samples, performed epitaxial overgrowth, etched the mesa structure to form Hall devices, measured the Hall effect and wrote the article

#### Paper II: InAs nanowire metal-oxide-semiconductor capacitors

Stefano Roddaro, Kristian Nilsson, Gvidas Astromskas, Lars Samuelson, Lars-Erik Wernersson, Olov Karlström, Andreas Wacker Applied Physics Letters **92** (2008) 253509

I arranged a capacitance measurement setup to detect signal from nanowire capacitors and actively participated in discussion.

#### Paper III: Doping Incorporation in InAs Nanowires characterized by Capacitance Measurements

v

Gvidas Astromskas, Kristian Storm , Olov Karlström , Philippe Caroff , Magnus T. Borgstrom , Lars-Erik Wernersson Journal of Applied Physics **108** (2010) 054306

I arranged a low temperature CV setup, performed CV measurements in a wide temperature range, analyzed the data and wrote the article.

Paper IV: Temperature and frequency characterization of InAs Nanowire and HfO2 interface using Capacitance Voltage method Gvidas Astromskas, Kristian Storm, Philippe Caroff, Magnus Borgström,

Erik Lind, Lars-Erik Wernersson Microelectronic Engineering accepted for publication

I measured the nanowire CV characteristics at a wide frequency range, analyzed the data and I wrote the article.

#### Paper V: Transient studies in InAs/HfO2 Nanowire Capacitors Gvidas Astromskas, Kristian Storm, Lars-Erik Wernersson submitted to Applied Physics Letters

I measured the capacitance transients of nanowire capacitors, performed deep level transient spectroscopy measurements, analyzed the data and wrote the draft of the article.

#### Paper VI: Analyzing the capacitance-voltage measurements of vertical wrappedgated nanowires

Olov Karlström, Andreas Wacker, Kristian Nilsson, Gvidas Astromskas, Stefano Roddaro, Lars Samuelson, Lars-Erik Wernersson Nanotechnology **19** (2008) 435201

I arranged the setup for nanowire capacitance measurements and participated actively in the discussion.

#### Paper VII: MOVPE-grown InAs/GaSb layers and membranes on GaAs

Gvidas Astromskas, B. Mattias Borg, and Lars-Erik Wernersson manuscript, to be submitted

I performed AFM and Hall measurements of samples, analyzed the electrical data and wrote the article.

### Related publications not included in this thesis

- 20 GHz wavelet generator using a gated tunnel diode M. Egard, M. Arlelid, E. Lind, G. Astromskas, L.-E. Wernersson, IEEE Microwave and Wireless Components Letters 19 (2009) 386.

- Applications of SU-8 in the development of a Single Ion Hit Facility N. Arteaga-Marrero, G. Astromskas, M.G. Olsson, M. Elfman, P. Kristiansson, E.J.C. Nilsson, C. Nilsson, J. Pallon Nuclear Instruments and Methods in Physics Research B 267 (2009) 2117.

- 3. Temperature dependence of GaSb overgrowth of tungsten on GaSb (001) substrates using MOVPE G. Astromskas, M. Jeppsson, P. Caroff, L.-E. Wernersson IEEE 20th International Conference On Indium Phosphide And Related Materials (2008) 354

- Heterogeneous integration of InAs on W/GaAs by MOVPE G. Astromskas, L. Wernersson Journal of Physics: Conference Series, 100 (2008) 042043

viii

# ABBREVIATIONS

| AlSb    | Aluminum Antimonide                                   |

|---------|-------------------------------------------------------|

| $AsH_3$ | Arsine                                                |

| CV      | Capacitance Voltage                                   |

| CVD     | Chemical Vapor Deposition                             |

| DLTS    | Deep Level Transient Spectroscopy                     |

| GaAs    | Gallium Arsenide                                      |

| GaSb    | Gallium Antimonide                                    |

| InAs    | Indium Arsenide                                       |

| InGaAs  | Indium Gallium Arsenide                               |

| InP     | Indium Phosphide                                      |

| InSb    | Indium Antimonide                                     |

| MIS     | Metal Insulator Semiconductor                         |

| MISFET  | Metal Insulator Semiconductor Field Effect Transistor |

| MOS     | Metal Oxide Semiconductor                             |

| MOVPE   | Metal Organic Vapor Phase Epitaxy                     |

| NID     | Not Intentionally Doped                               |

| HEMT    | High Electron Mobility Transistor                     |

| TBAs    | Tertiary Butyl Arsine                                 |

| TEGa    | Triethyl Gallium                                      |

| TEM     | Transmission Electron Microscope                      |

| TMGa    | Trimethyl Gallium                                     |

| TMI     | Trimethyl Indium                                      |

| TMSb    | Trimethyl Antimony                                    |

### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my supervisor Lars-Erik Wernersson, who gave me the opportunity to carry out this work under his guidance. Also, I would like to thank Erik Lind for his continuous support through almost every day of my research. This thesis has come to light only with the help and contribution from my research colleagues. I especially want to thank Mattias Borg for his suggestion to print the process travelers. This made the difference between trying and experimenting. Phillipe Caroff is a key person for to discuss about epitaxy, research, physics, human relations and other important elements of a PhD student's life. Also, Mikael Edgard must be acknowledged, as his hard work makes splendid high speed devices. I am also in debt to the department of Solid State Physics for providing me with an excellent work place, an outstanding laboratory equipment and a friendly environment to spend the working days. I want to mention Ivan, Mariusz, Lena, Mona and Sören for providing the help when I needed it.

I want to thank my family for their dedication, especially Eimantas for being the driving force to pursue the studies.

Also, my life in Lund would be impossible without ever helping friends. I am very grateful to spend time with Alexander, Audrius, Henrik, Justas, Oleg, Nataliya, Natalia, Ramūnas, Sveta, Valeria and Vaida.

xi

A cknowledgments

# CONTENTS

| 1                     | Introduction                                                 | 1             |  |  |

|-----------------------|--------------------------------------------------------------|---------------|--|--|

| 2 Integration of InAs |                                                              |               |  |  |

| -                     | 2.1 Integration options                                      | <b>5</b><br>5 |  |  |

|                       | 2.2 Mobility of integrated InAs                              | 6             |  |  |

| 3                     | Epitaxial growth                                             | 9             |  |  |

|                       | 3.1 Basics of epitaxy                                        | 9             |  |  |

|                       | 3.2 Heteroepitaxial growth                                   | 10            |  |  |

|                       | 3.3 Epitaxial overgrowth                                     | 11            |  |  |

|                       | 3.4 Nanowire growth                                          | 12            |  |  |

|                       | 3.5 Epitaxial growth in MOVPE                                | 13            |  |  |

| 4                     | Electrical measurement techniques for thin films             | 15            |  |  |

|                       | 4.1 Nanowire Capacitance Voltage characteristics             | 15            |  |  |

|                       | 4.2 Multilayer Hall mobility                                 | 17            |  |  |

| 5                     | Nanowire CV characterization                                 | <b>21</b>     |  |  |

|                       | 5.1 Undoped nanowire CV characteristics                      | 21            |  |  |

|                       | 5.2 Nanowire doping level                                    | 23            |  |  |

|                       | 5.3 Nanowire capacitance transients                          | 24            |  |  |

| 6                     | Characterization of Overgrown InAs                           | 25            |  |  |

|                       | 6.1 Overgrowth                                               | 25            |  |  |

|                       | 6.2 Electrical Characterization of overgrown InAs/W patterns | 27            |  |  |

| 7                     | InAs membranes on GaSb buffer layers                         | 29            |  |  |

|                       | 7.1 GaSb buffer growth                                       | 29            |  |  |

|                       | 7.2 InAs integration onto GaSb                               | 30            |  |  |

| Bi                    | Bibliography                                                 | 32            |  |  |

# Introduction

1

We live in a world, made of many different materials. They have particular mechanical, optical, electrical and thermal properties, which we can exploit, modify, suppress or enhance to suit our purpose. A type of materials, called semiconductors allow controlling their electrical, optical, magnetic and thermal properties only with the effect of electrical power, not larger then the provided by an AA battery. This makes them very convenient for building electronic components, that later are much used in our everyday items, like computers, phones, washing machines, cars and other electrical appliances. And all this is thanks to our understanding of electrical properties of semiconductors.

This thesis is focused on the investigation of the electrical properties of a semiconductor material, called Indium Arsenide (InAs). InAs has a narrow band gap of 0.354eV and a high mobility of 18000  $cm^2/Vs$  at room temperature [1]. The mobility is eighteen times larger than the mobility of Silicon, of which the vast majority of electronic components are made.

The mobility quantifies how well the electrons respond to the applied electric potential. The higher value indicates that the control of the electron current is easier in InAs based devices as compared to Silicon. This is the basic reason why high sensitivity and high frequency performance is expected from InAs devices.

InAs is currently used for making very sensitive magnetic field sensors [2]. But it can have other applications, for example the terrestrial thermal imaging and high speed electronic devices [3]. Actually, a 640 GHz operation of low power InAs channel HEMT is already reported [4].

In order to make InAs based electronic devices, we have to consider their size. Large devices do not mean better performance, as small structures take less space, are cheaper, consume less power and can even operate faster (for example, smaller devices have lower parasitic capacitances and resistances). Of course, small size means less volume, therefore less current and less power. Low power is actually desirable, because devices consume less energy and produce less heat, therefore being more efficient. The current loss can be compensated by combining more nano devices together, or making the devices more sensitive. The high mobility electrons can respond well even to weaker electric fields, therefore higher sensitivity is expected from nano-sized InAs structures. Also, the narrow band gap of InAs allows electron control with less power. This is why InAs is an interesting material at small dimensions.

Of course, sensitive devices produce weak signals; which then have to be amplified

to the levels, used by other electronic components. This requires integrating nano-sized structures with larger devices, that are more powerful. Therefore the integration is a way to get the best of two worlds: to combine a conventional technology with its advanced measurement and processing techniques with sensitive nano devices. However, when nanostructures are integrated onto desired substrates, it is no longer certain that they can keep their high sensitivity, as integration can reduce mobility. Lower quality means lower mobility therefore it is important to identify the sources, that cause quality loss during integration. For epitaxial nano-structures, like InAs, the typical quality loss is related to the defect formation during epitaxial growth. The bulk structures also suffer from defect formation, but there it is understood how defects affect the quality. Nano structures are more sensitive to defects, but it is not clear how much the defects affect their properties. On the other hand, nano-structures can be used as a tool to identify the most important defects and to better understand their formation.

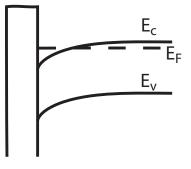

The drawback of nano-structures is their large surface to volume ratio. The surface is expected to affect the properties of nano structures, including the mobility. In the InAs case, the surface is known to exhibit a surface phenomena, called Fermi level pinning [5]. At the surface the Fermi level is fixed over the conduction band minimum  $(E_C)$  as opposed to the more common case where the Fermi level is under the conduction band and forms a Schottky contact instead. The pinning creates a conductive surface layer, which has to be evaluated in nano-sized InAs structures.

Figure 1.1: Band diagram illustrating the Fermi level pinning at the InAs surface

The pinning is illustrated in Figure 1.1. Such band configuration increases the sheet electron concentration at the InAs surface to as high as  $(4 \cdot 10^{12} \ cm^{-2})$  [6] allowing creating ohmic contacts to InAs with almost any metal. However, the surface mobility is estimated to be 2400  $cm^2/Vs$  [7] and is much lower than in the bulk. The low mobility is attributed to scattering by the surface states, that create the pinning effect [8]. Therefore the low mobility indicates that there can be an upper limit to the scaling of InAs when the surface scattering starts to dominate in nano sized InAs structures. The effect might be detrimental to device performance, although currently it is considered to be advantageous

as it allows easily making good ohmic contacts to InAs structures [9]. Also, typical electrical characterization methods are developed for the bulk materials, where surface has negligible influence. Therefore they need to be reevaluated to include the surface effects.

The text of this thesis is organized as follows:

Chapter 2 describes in more detail the integration methods for InAs nano-structures. Chapter 3 provides information about epitaxial growth, which is the method of choice for creating and integrating InAs structures.

Chapter 4 describes the techniques for measuring the electrical characteristics of nanosized InAs structures.

Chapter 5 provides a background to the articles II-IV that deal with CV measurements. The key results are presented and the doping level determination method in nanowires is explained.

Chapter 6 provides a background for paper I, where overgrown InAs is investigated to determine the surface influence onto mobility. The overgrowth process is briefly explained, together with the method of testing the surface layer mobility.

Chapter 7 introduces the InAs grown on buffer layers to determine how defects influence the quality of InAs.

Introduction

# Integration of InAs

High quality InAs is easily grown in conventional epitaxy reactors, especially when grown on InAs substrates. The growth on native substrate is virtually defect free, ensuring high mobility. However, the InAs substrate is highly conductive, which acts as unwanted leakage path, making the substrate unsuitable for electronic components. To remove the substrate leakage, InAs has to integrated onto a wide gap material, as they have lower intrinsic carrier concentration. A suitable candidate is AlSb, which has a band gap of  $1.58 \ eV$ , more than four times larger than that of the InAs. It also has a lattice constant of  $6.13\text{\AA}$ , therefore this substrate is nearly lattice matched to the  $6.058\text{\AA}$  InAs lattice. However poor substrate quality and strong reactivity to atmospheric oxygen makes it currently unavailable for device applications [10]. GaSb is also nearly lattice matched to InAs, but exhibits a narrow band gap of  $0.72 \ eV$ , leading to high substrate conductance as well. Therefore InAs has to be integrated to lattice mismatched GaAs or InP substrates but at the cost of dislocation generation.

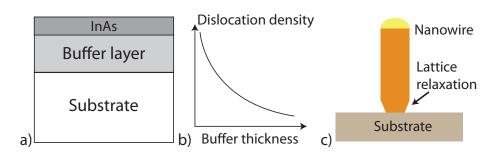

In order to integrate the material onto the lattice mismatched substrate, a few integration methods are available. The first option is growing a thick buffer layer, so that the generated dislocations can form loops and stop propagating [11]. The schematic of the integration using a buffer layer is shown in Figure 2.1a. The substrate is first covered with thick (typically >  $1\mu m$  thick) layer of the buffer material and then finished by a thin layer on top. Commonly used buffer materials to integrate InAs are: InAs itself, GaSb, AlSb, InPSb or InGaAs. The advantage of the buffer layer technology is that it makes planar layers and therefore it is compatible with standard processing and measurement techniques.

### 2.1 Integration options

A typical buffer layer is characterized by the curve shown in Figure 2.1b, where the dislocation density decreases with increasing buffer thickness. Dislocations form at the substrate/buffer interface and then propagate through the buffer layer to the top layer. However, as dislocations propagate through the layer, they are likely to form dislocation loops, that stop their propagation [12]. Particularly useful are (100) substrates, where threading dislocations tend to propagate at  $60^{\circ}$  angle, making it easier to form a loop. In some cases, it is even possible to achieve  $90^{\circ}$  threading dislocations, that slide parallel

2

Figure 2.1: a) Schematic of the integration using buffer layer b) Schematic of the dislocation density vs. the buffer layer thickness. c) Schematic of the mismatch relaxation by nanowire diameter expansion

to the buffer/surface [13]. However, as a consequence of propagation, even thick buffer layers will not be defect free. The dislocation propagation can also be reduced by using step graded buffers, where the interface between heterostructures with different lattice constants tend to change the dislocation propagation direction [14]. To stop the propagation, the overgrown layers can be used, where the mask blocks the dislocation propagation path [15].

Another option for integrating nano-sized InAs structures is a nanowire growth. InAs nanowires already are grown on GaAs [16], InP [17] and Si [18] substrates. The small diameter of the nanowire allows lateral relaxation of the lattice mismatch, as shown in Figure 2.1c. The relaxation prevents the formation of threading dislocations [19], although stacking faults and twin boundaries can still be present under non optimized growth conditions [20]. It is important to mention that a typical InAs nanowire contains both wurtzite and zinc blende crystal structures [21], while the bulk InAs is found only as zinc-blende. The different crystal structure leads to formation of stacking faults and twin, which affect the quality of the nanowires. Also, the wurtzite crystal structure has a band gap of  $0.54 \ eV$  instead of the  $0.354 \ eV$  band gap of zinc blende InAs.

The vertical geometry of nanowires also opens a few new design possibilities. For example a better channel control can be achieved when the wrap around gate are used [22]. This can even allow the use of a higher mobility channel present in the undoped nanowires, without sacrificing the device current by the lack of doping [23].

### 2.2 Mobility of integrated InAs

It is interesting to compare which integration method gives better quality material. Also, whether the dislocation scattering is stronger than the surface scattering.

Typical studies that investigate the influence of dislocation density on the quality of integrated InAs, vary the thickness of the buffer layers and then measure the mobility.

When thick buffers layers are used (> 4  $\mu$ m), even a 60 nm thin InAs layer have the bulk mobility, if the surface states are suppressed by a GaSb cap [24]. However the epitaxial growth of thick layers is more expensive than the bulk growth, therefore thinner layers are desired, though they contain more dislocations. Also, the surface to volume ratio becomes larger, thus the pinning starts affecting the measurements. Also, only few measurements of the surface mobility are done [25].

In one of the measurements, two thin (20 nm) InAs membranes with different dislocation densities are measured [26]. The thin layers ensures a strong influence of surface to the mobility. As determined on low dislocation density membrane, mobility of the thin membrane exceeds 7000  $cm^2/Vs$  [26,27], while for membrane with higher dislocation density the mobility lowers to 3000  $cm^2/Vs$ . This shows that the dominant electron scatterer in the buffer layer based integration process remains the dislocation density. Therefore a desired outcome of the integration process is the reduction of dislocation density in InAs thin films.

It is interesting to compare this value with nanowire integrated InAs structures. Mobility of nanowires cannot be obtained by conventional Hall measurements, instead the field mobility is extracted from nanowire transistor measurements using a MIS model. The values obtained by this method reach 11 500  $cm^2/Vs$  at a room temperature [28] for InAs nanowire with an InP shell, which suppresses the surface pining. However, the nanowire mobility is diameter dependent and decreases to 2000  $cm^2/Vs$  for a 20 nm InAs nanowire [29]. This value can be increased to 5200  $cm^2/Vs$  if the defect density is reduced [30]. These results indicate that the nanowire growth has to be optimized to reduce the stacking fault density. Also a careful surface control is required to obtain good quality devices.

The Hall and field mobilities are not equivalent, as the Hall mobility represents the bulk carrier scattering, while the field mobility is also affected by the surface scattering. The relation between the two is expressed as  $\mu_{Hall} = r_h \cdot \mu_{field}$ , where  $r_H$  is called a Hall scattering factor. The value of  $r_H$  in InAs varies between 1 and 1.3 [31,32]. If the  $r_H$  factor is unaccounted (as is often done), then the field mobility can underestimate the Hall mobility for up to 30%.

Integration of InAs

# Epitaxial growth

This thesis analyzes InAs nano-structures that are integrated epitaxially by three different methods: buffer layer, overgrowth and nanowire growth. Therefore this chapter presents the basics of epitaxial growth and explains the properties of each integration method. The epitaxial growth was performed using a Metal Organic Vapor Phase Epitaxy reactor, which is an industry standard growth technology. Therefore, the last section provides a short introduction to MOVPE growth and reactor related growth parameters.

### 3.1 Basics of epitaxy

Epitaxy is a process to create high quality crystalline structures of various materials. The term epitaxy comes from the Greek roots epi, meaning "above", and taxis, meaning "in ordered manner", so it can be translated "to arrange upon". During the epitaxial growth, the atoms order themselves onto the existing surface to create a new mono crystalline layer. The ordering occurs by diffusion, therefore the layer growth is slow. A typical growth rate 1  $\mu m/h$ , which corresponds to 2.4 mm/day. On the other hand, the slow growth makes it easy to control the size of nano-structures.

Three factors are required for epitaxial growth:

- 1. a substrate,

- 2. a source material,

- 3. the ability to control the growth process.

The substrate is a flat piece of a single-crystal with the periodic order of atoms, which acts as a very precise template for the atoms. The source material forms strong intra molecular bonds (for example, covalent bonds) to the substrate atoms, causing the growing layer to follow the order of the substrate atoms and make a new crystalline layer. To achieve this and control the process, a growth reactor is used, where the supply of source material, the substrate temperature and the reactor pressure are controlled.

3

### 3.2 Heteroepitaxial growth

Heteroepitaxy is a type of epitaxial growth where the substrate and the grown layer are of different compounds, for example growth of InAs on GaAs. In order to achieve high quality heteroepitaxial growth, three major factors have to be considered:

- 1. lattice constant mismatch,

- 2. crystallographic orientation of the substrate,

- 3. interface type.

The lattice mismatch is the most common cause for defect formation in the heteroepitaxial structures. In order to maintain epitaxial relation, the growing layer aligns according to the lattice of the substrate. However, this creates an electrostatic force, as atoms are away from their equilibrium bond positions for the lattice mismatched layer. This force leads to the buildup of the strain energy in the growing layer. While the strain energy is under the energy threshold for the dislocation formation, the growing layer has the same parallel lattice constant as the substrate and is called metamorphic. If too much strain is present, the atoms cannot follow the order of the substrate and instead redistribute themselves to minimize the total energy, forming a dislocation. This process is a type of plastic relaxation and is the main mechanism for defect formation during heteroepitaxial growth. As the growth proceeds, the new layer follows the order of the deformed layer, therefore the dislocation propagates throughout the growing structure.

The maximum thickness for a stable metamorphic layer is called the critical thickness. The critical thickness for the InAs grown on GaSb is found to be of up to 3000 Å [33]. The mismatch between the lattices of InAs and GaSb is 0.65%, which should correspond to the critical thickness of 200 Å [34], according to the Matthews-Blakeslee model [35]. A better fit to experimental data is obtained if other dislocation generation models are used, for example People-Beans [36] which account for the screw dislocations [37].

The lattice mismatch also can be relaxed by the change of the growth mode. When misfits are larger than 2%, in most cases the epitaxial growth mode changes from layer by layer mode to 3D growth. Under the 3D growth mode, the islands are created, which have much greater capability of reducing strain compared to dislocations [38]. By continuing the growth, islands increase in size forming a layer by coalescence. But due to random sizes and positions, the atomic ordering is distorted, leading to defect formation during island coalescence. This is the main drawback of the 3D growth mode.

The different compounds can have different crystal phases therefore their crystallographic orientations can be different. For example, InAs nanowires have a wurtzite structure, but are grown on zinc blende InAs substrates. This distorts the epitaxial information and can lead to the formation of stacking faults and twin planes [39]. Also some strain is likely to be present. Heteroepitaxial growth allows choosing the interface type at the transition between one material to another, for example between InAs and GaSb. In this example, there are two possible interface combinations: GaAs like and InSb like, with InSb interface being superior [40].

### 3.3 Epitaxial overgrowth

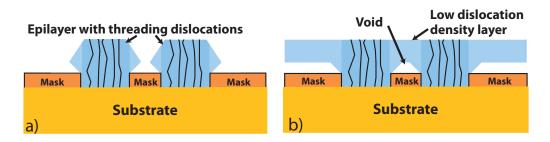

Epitaxial growth normally occurs over the whole substrate and ensures a good uniformity of the growing layer. However, it is sometimes desirable to reduce the growth area by a mask and perform a selective area epitaxy. The conditions for selective epitaxy are chosen such, that source material nucleates only on the unmasked parts of the substrate, and no nucleation occurs on the polycrystalline mask. This is achieved when the critical-nuclei radius on the mask is larger than on the substrate. Epitaxial overgrowth is a special case of selective area epitaxy, when the growing layer completely covers the mask. But the layer does not nucleate or grow on the mask, instead it extends from the substrate by a lateral growth.

The overgrowth can be separated into two steps: lateral growth over the mask and layer planarization, illustrated in Figure 3.1. Over the mask, the crystal grows both laterally and vertically at the same time, forming facets at the crystal edge. The facet will be outward if the lateral growth rate exceeds the vertical growth rate or inward if the vertical growth rate is higher than the lateral growth rate. If inward facets meet, a void is formed, while outward facets tend to coalesce void free. Also, the facets have to conform to the Wulff theory of the stable crystal shapes [41], therefore multiple facets are present over the mask. If facets of different orientation meet then a grain boundary is formed. As the facet orientation is determined by the thermodynamic equilibrium, the growth parameters, like temperature and/or partial pressure, can be tuned to obtain desired facets shapes.

Figure 3.1: a) Schematic of the facet types: inward and outward. Schematic of epitaxial planarization process when: a) the lateral growth rate is higher than the vertical one  $((R_{111} > R_{001}))$ , b) the lateral growth is lower than the vertical one  $((R_{111} < R_{001}))$

As illustrated in Figure 3.1b and c the planarization occurs when the lateral growth fronts (A') meet from both sides of the mask. There are two ways for planarization:

1.  $R_{111} > R_{001}$  - the lateral growth rate is higher compared to the vertical one as shown in Figure 3.1b. In this case the growth front A' moves closer to the opposing

growth front with increasing layer thickness. When it reaches the opposing growth front, the surface becomes planar.

2.  $R_{111} < R_{001}$  - when the lateral growth rate is lower than the vertical one, the layer planarization is also possible [42] as shown in Figure 3.1c. Here the growth front A' is moving away from the opposing growth front. The planarization occurs when the growth front A meets another growth front, created on the other mask. To achieve full planarization by this method, the mask pattern has to be periodic.

Figure 3.2: Schematic of the heteroepitaxial overgrowth process for dislocation reduction: a) before overgrowth and b) after overgrowth.

The epitaxial overgrowth is used to reduce the dislocation density in heteroepitaxial growth. As defects can not penetrate the mask, the overgrown areas result in better crystal quality, as shown in Figure 3.2. The lattice mismatch generates a large amount of dislocations to relieve strain, but the laterally growing edge follows the epitaxial order of the relaxed layer. This method is successfully used for reducing threading dislocation density in GaN. Although, grain boundaries and voids can still be present [43].

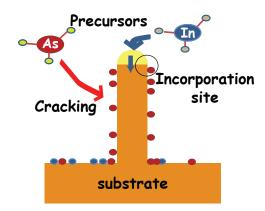

### 3.4 Nanowire growth

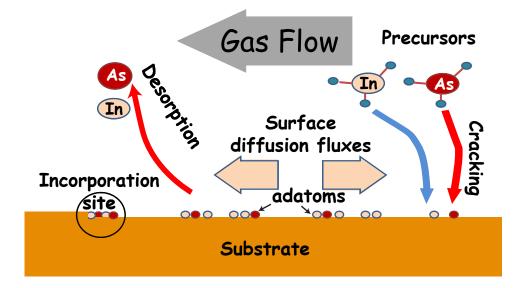

Typical nanowires are vertically standing high aspect ratio semiconductor structures. In order to grow a nanowire, the epitaxial process is tuned to enhance locally the vertical growth rate. To achieve this, a typical nanowire is grown on a native  $\{111\}$  substrate where the lateral growth rate is suppressed by lowering the growth temperature to  $(450 - 470 \ ^{o}C)$ . To enhance the vertical growth rate a Au particle is placed on the substrate. During the growth, the particle becomes supersaturated with group III element, for example In, leading to a locally increased source material concentration. The group V element, for example As, is not soluble in the Au particle, and therefore is supplied to incorporation site by the surface diffusion. This forms a triple phase boundary at the incorporation site [44], where In and As combines to form an InAs layer under the particle. As a result the Au particle is lifted upwards during the growth, thus creating a typical nanowire as shown in Figure 3.3. As the growth continues, the nanowire develops

Figure 3.3: Schematics of InAs nanowire growth.

side facets, that are normally oriented along the {110} directions. In the simplest case, these side facets consist of {111} micro-facets [45], which have a slow growth rate. This suppresses the lateral growth on the nanowire walls to obtain tapering free nanowires. By raising the growth temperature it is possible to enhance the lateral growth rate and make for example, core/shell nanowires [46].

### 3.5 Epitaxial growth in MOVPE

Metal Organic Vapor Phase Epitaxy (MOVPE) is a type of Chemical Vapour Deposition (CVD) epitaxial reactor that uses metal organic source materials. The CVD technology uses gas molecules in the fluid flow regime, where molecules can interact with each other. The interaction can result in forming undesired compounds, thus deteriorating the growth quality. This is avoided by carefully choosing source materials (also called precursors) that are chemically stable at ambient conditions and only react at elevated temperatures. The probability of parasitic reactions is also lowered by diluting the growth precursors with carrier gases such as  $H_2$  or  $N_2$ . The carrier gas also creates a laminar gas flow in the CVD reactor to improve the growth uniformity and to further reduce the mixing of gases. Suitable precursors for CVD growth are metal-organic molecules, that mostly come in the form of  $(CH_3)_x R$ , where R is the metal ion There are two major advantages with these precursors [47]:

- 1. growth reactions will normally form only gaseous compounds, like methane, which are easy to pump out from the reactor,

- 2. a wide variety of metals can be combined into Metal-Organic molecules.

Examples of the metal-organic sources are Trimethyl-Indium (TMI), Trimethyl-Antimony (TMSb) and Trimethyl-Gallium (TMGa), while Arsenic (As) can be supplied in the metal-

organic form as Tertiarybutyl-Arsine(TBAs) or as a hydride  $(AsH_3)$  [48]. These sources are routinely used for growing InAs or GaSb.

Figure 3.4: The schematic of the growth process inside the MOVPE reactor.

The MOVPE growth process is schematically shown in Figure 3.4. The carrier gas flow transports precursor molecules to the substrate in a gas mixture. When the precursors reach the substrate, the methyl bonds crack due to the high temperature of the substrate (typical ranges are from 400 to 800 °C) releasing the metal atom. It is important to mention, that the cracking efficiency is normally greatly enhanced if the precursor molecule is in direct contact with the substrate [49]. Therefore the substrate acts not only as a template, but also as a catalyst for cracking. After the cracking is complete (for example, TMI has to release three methyl groups in sequence), the gaseous (organic) parts of the molecule is pumped away. The metal atom now becomes an adatom, which means that it is physisorbed to the surface. The adatom diffuses on the substrate until finding a suitable incorporation site, like a monolayer step or any other non-uniformity on the substrate.

As group III elements are likely to clump together and form metallic particles, it is important to have excess group V elements near the incorporation site. Therefore a V/III ratio is normally much higher than one to ensure the excess. Also, cracking efficiencies vary between different precursors, so the ratio is adjusted to account for that. The excess adatoms can desorb from the substrate by overcoming the physisorption energy barrier and return to the gas phase. The desorption sets the upper limit of the growth temperature, while the lower limit is set by the need to have high diffusion rate and high cracking efficiency.

# Electrical measurement techniques for thin films

In this thesis, two of the common methods for evaluating the electrical properties of semiconductor materials are used. These techniques are Hall measurements and Capacitance-Voltage characterization. Hall effect measurement is a standard technique to evaluate mobility, carrier type and carrier concentration, while Capacitance measurements reveal information about carrier density, their spatial distribution and oxide properties. This technique is also easily extended to evaluate interface trap densities. However, InAs nanostructures present a few difficulties for these standard characterization techniques. The capacitance of the nanowire structures exhibit non parabolic band effects and full depletion, while Hall measurements in thin films have to account for the surface pinning layer as well leakages from other layers, present in the integrated structures.

The first section presents what changes in the Capacitance Voltage characteristics when InAs nanowires are measured compared to the standard MOS structures. Second section describes the multilayer Hall mobility.

### 4.1 Nanowire Capacitance Voltage characteristics

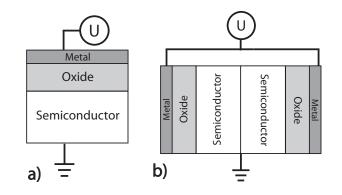

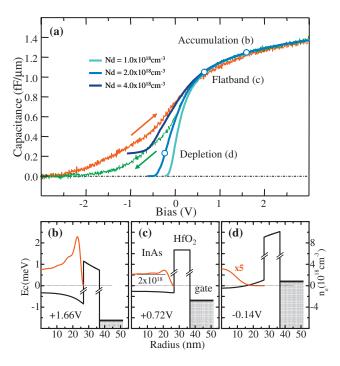

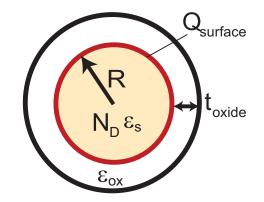

A typical structure for performing CV measurements is a Metal Oxide Semiconductor (MOS) capacitor, as shown in Figure 4.1a. The oxide and the metal layer are deposited on the prepared semiconductor sample to form a capacitor. The oxide is chosen to have a large dielectric constant and a large band gap (> 3 eV) in order to act as a good insulator. When a bias U is applied, the capacitance of the MIS structure depends on the voltage because the depletion layer varies inside the semiconductor. The depletion layer is a virtually carrier free region, therefore extending the oxide. As the width of the depletion layer increases, the measured capacitance decreases, creating a CV profile, shown in Figure 4.2a as a dashed line.

The nanowire MIS capacitor can be constructed by joining two MIS capacitors at their backsides, as shown in Figure 4.1b. This increases the oxide/semiconductor area, therefore allowing a higher capacitive coupling to the channel. However, the CV profile of a planar capacitor and the nanowire capacitor differ.

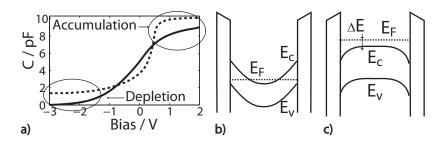

First, a near zero depletion capacitance can be measured in nanowires, as is shown in

Figure 4.1: Schematics of a) Metal-Insulator-Semiconductor (MIS) and b) a nanowire MIS capacitor structures.

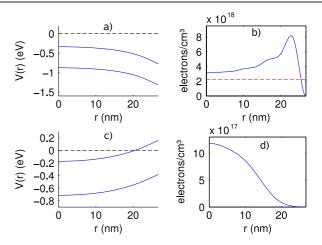

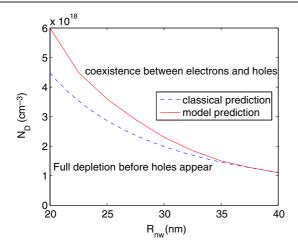

Figure 4.2a. This is not observed for the planar MOS capacitors, as a hole inversion limits the extent of the depletion layer, leading to a non zero  $C_{depletion}$ . But the nanowire can be thinner than the maximum depletion width, therefore no hole inversion is created in the radial direction. For example, for the InAs the maximum depletion layer width exceeds 20 nm at a  $10^{18} \ cm^{-3}$  doping level. Therefore the full depletion is expected for all small diameter nanowires. If a higher bias is applied, the Fermi level will cross the intrinsic carrier energy level, creating the inversion layer, as shown in Figure 4.2b. However, the position of this layer will be at the bottom of the nanowire stem. The area occupied by the inversion layer remains small due to the small diameter of the nanowire, therefore the near zero capacitance will be observed.

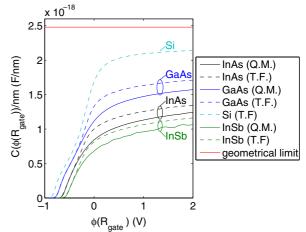

A second difference in the CV profile is related to the specific material property of InAs. InAs exhibits non-parabolic band structure [50], which leads to low density of states. Therefore electrons fill higher states in the conduction band, and noticeably raise the Fermi level. This subsequently increases the potential difference between the metal and the semiconductor, thus lowering the capacitance. Therefore the accumulation capacitance of InAs nanowire as well as other InAs structures is lower than the geometrical limit [51]. As electrons fill higher states at higher positive bias, the separation between the Fermi level and the conduction band ( $\Delta E$  in Figure 4.2c) increases and an increasing accumulation capacitance is measured instead of saturation.

The full depletion condition has an advantage for analyzing the nanowire CV characteristics, as under this situation there are no electrons to affect the potential distribution in the nanowire. In a depleted nanowire, the voltage will drop only over the uncompensated charges, that in most cases are donors, which then will be proportional to their number. This allows defining a threshold voltage at a point when the capacitance becomes zero. The threshold voltage can then be compared, for example, for nanowires with different doping levels. Such analysis is more convenient as a standard model requires calculating electron distribution using non-parabolic bands and solving the Poisson equation for that

Figure 4.2: a) A typical CV curve of the n-type InAs nanowire MIS capacitor (solid line) and planar MOS capacitor (dashed line). InAs nanowire band structure at b) depletion c) accumulation. Here, U is an applied bias,  $E_F$ ,  $E_C$  and  $E_V$  are a Fermi level, a conduction band and a valence band, respectively.  $\Delta E$  is the separation between the conduction band and the Fermi level.

distribution in the radial geometry just to get the doping level.

The threshold voltage method can also be expanded to evaluate the surface trap density. The basic idea is that charges at the surface and charges inside the nanowire scale at different rates for different nanowire diameters. The bulk area increases as  $\pi r^2$ , while the surface scales only as  $2\pi r$ , with r being the nanowire radius, analysis of threshold voltage diameter dependence can reveal dopant distribution profile. Apparently, this also means that the nanowire threshold voltage is diameter dependent, while in the planar MOS case no size dependence is expected.

### 4.2 Multilayer Hall mobility

The Hall effect is used as a basic semiconductor film characterization technique to obtain the carrier concentration and the carrier mobility. The Hall effect is measured when the carrier current is deflected by the Lorentz force due to the magnetic field  $(\vec{F} = q(\vec{E} + \vec{v} \times \vec{B}))$ . The deflection creates a carrier density gradient in the film, which results in a potential difference perpendicular both to the current flow and the magnetic field directions. The potential difference is then measured as the Hall voltage  $(V_H)$ , which is inversely proportional to the electron density. Depending on the carrier type, the sign of  $V_H$  changes, being positive for holes, and negative for electrons. Once the carrier concentration has been determined, the mobility is obtained from a conductance relationship:  $\sigma = en\mu$ .

However, the current in InAs films can have more than one path: bulk conduction, surface layer conduction [52–54] and defect conduction [55,56]. Therefore the conductivity becomes a sum expressed as  $\sigma = \sum_{i} en_{i}\mu_{i}$  and the Hall effect also has to be expanded to include multiple conductances. In general, the Hall effect is also magnetic field dependent [57]:

$$V_H = \frac{R_H I B}{h}; \ R_H = \frac{1}{en} \tag{4.1}$$

$V_H$ : Hall voltage I: carrier current B: magnetic induction h: sample thickness  $R_H$ : Hall constant n: carrier density e: electron charge

$$R_H(B) = \sum_i \frac{\sigma_{xy}/B}{\sigma_{xx}^2 + \sigma_{xy}^2} \tag{4.2}$$

$$\sigma_{xx} = \sum_{i} \frac{en_{i}\mu_{i}}{1 + (\mu_{i}B)^{2}}$$

(4.3)

$$\sigma_{xy} = \sum_{i} \frac{en_{i}\mu_{i}^{2}B}{1 + (\mu_{i}B)^{2}}$$

(4.4)

$R_H$ : Hall coefficient  $\sigma_{xx}$ : longitudinal conductance tensor  $\sigma_{xy}$ : transverse conductance tensor e: electron charge  $n_i$ : carrier concentration of  $i_{th}$  carrier species  $\mu_i$ : mobility of  $i_{th}$  carrier species

At small magnetic fields, when  $\mu_i B \ll 1$ ,  $R_H$  becomes B field independent, leading to the classical Hall effect. However, when multiple conduction paths exist, the Hall coefficient remains magnetic field dependent. To separate each contribution we can analyze this dependence, as the influence from high mobility carriers is quenched due to the  $(1 + (\mu B)^2)$  denominator and a step like behavior is obtained [58]. At strong magnetic field, the Hall constant is dominated by the lower mobility carriers. With the use of the magnetic field dependent longitudinal and transverse conductances, the contributions of each current path can be extracted from wide range magnetic field sweeps data [59]. However, the procedure requires considerable effort to obtain good measurements and to correctly extract the results. Therefore it is useful to have an approximation for the multiple conduction relation, valid at low magnetic fields [60]:

$$R_H = R_{Hb} \frac{d_b}{(d_b + d_l)} \left(\frac{\sigma_b}{\sigma_t}\right)^2 + R_{Hl} \frac{d_l}{(d_b + d_l)} \left(\frac{\sigma_l}{\sigma_t}\right)^2 \tag{4.5}$$

$$\sigma_t = \sigma_b + \sigma_l \tag{4.6}$$

$R_{Hb}$ : Hall coefficient of buffer layer  $d_b$ : thickness of the buffer layer  $\sigma_b$ : conductivity of the buffer layer  $\sigma_t$ : conductivity of the integrated structure  $R_{Hl}$ : Hall coefficient of thin film  $d_l$ : thickness of the thin film  $\sigma_l$ : conductivity of the thin film

In this case the approximation is expressed for the structure consisting of two layers - the buffer and a thin film. Here, the total Hall coefficient of the sample is a sum of the respective Hall coefficients of each species, multiplied by their respective contributions to conductance. This formula is suitable to design experiments as it allows estimating whether a classical Hall effect measurement is sufficient, or a more detailed analysis will be required. However, one has to be careful in applying this expression to evaluate the mobility of separate species. If a high mobility carrier is present, then the  $(1 + \mu_i^2 B^2)$  denominator makes the high mobility contribution to  $R_H$  non-linear, thus making the linear addition in the approximation inaccurate. In such a case a full two conducting layer  $R_H$  expression has to be considered [61]:

$$R_{H} = \frac{(d_{b} + d_{l}) \left[ (R_{Hb}\sigma_{b}d_{b} + R_{Hl}\sigma_{l}d_{l}) + R_{Hb}R_{Hl}\sigma_{b}^{2}\sigma_{l}^{2}(R_{Hl}d_{l} + R_{Hb}d_{l})B^{2} \right]}{(\sigma_{b}d_{b} + \sigma_{l}d_{l})^{2} + \sigma_{b}^{2}\sigma_{l}^{2}(R_{Hl}d_{l} + R_{Hb}d_{l})B^{2}}$$

(4.7)

It is also important to note, that the mobility of a particular carrier type itself can be affected by more than a single type of scattering. The most common ones are polar optical phonon and impurity scatterings [62,63]. In this case, the mobility is expressed as:  $\frac{1}{\mu_i} = \frac{1}{\mu_{imp}} + \frac{1}{\mu_{pol}}$ , where  $\mu_{imp}$  and  $\mu_{pol}$  are impurity and polar phonon scattering limited mobilities. Fortunately, these scattering types are temperature sensitive therefore their effect is observed only in temperature dependent Hall measurements [64, 65].  ${\it Electrical}$  measurement techniques for thin films

# Nanowire CV characterization

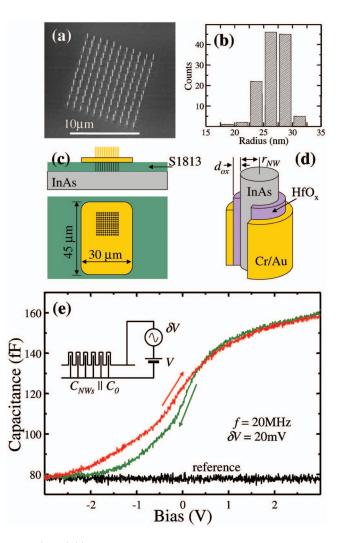

High quality InAs nanowires are routinely grown and used for building functioning Metal Insulator Semiconductor Field Effect Transistors (MISFET) [17, 66–68]. These devices already show performance of  $f_{max} = 7 \ GHz$ , and are even integrated to Si substrates. However, little is known about the properties of the oxide and the oxide/semiconductor interface in nanowires. Basic properties like the magnitude of capacitance, the doping level and the trap density so far has not been determined for nanowires with gate structure.

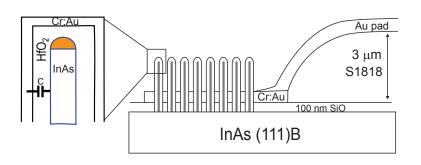

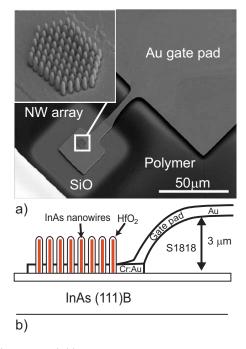

A challenge is that the small size of the nanowire devices leads to small capacitances, which in turn are hard to measure. The capacitance can be as low as a few femto Farads [69, 70], which is below the detection limit of typical measurement equipments. Gated single nanowires have been measured using low noise equipment up to 20 kHz frequencies [29], but the frequency region is not suitable for investigating narrow gap InAs capacitors [71]. This requires building nanowire capacitor structures measurable by conventional equipment.

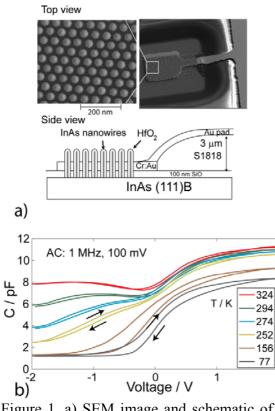

### 5.1 Undoped nanowire CV characteristics

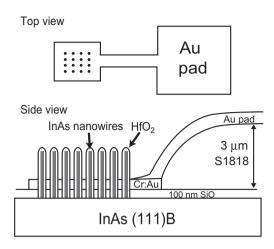

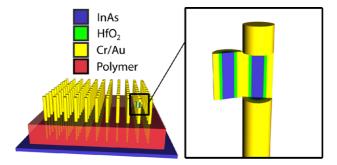

Figure 5.1: Schematic of the nanowire capacitor

A simplest solution to increase the nanowire capacitance to a measurable  $0.5 - 10 \ pF$

### 5

level, is connecting an array of identical nanowires in parallel as shown in Figure 5.1 There still remains a parasitic capacitance from the pad, that is used to connect probes to the capacitor array. To reduce it, the gate pad is raised from the substrate, reducing the pad capacitance to  $300 \ fF$ .

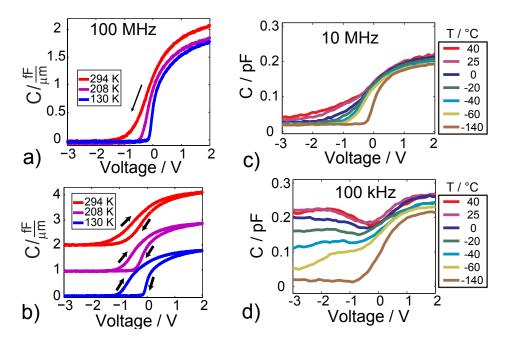

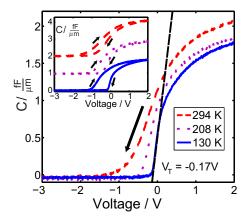

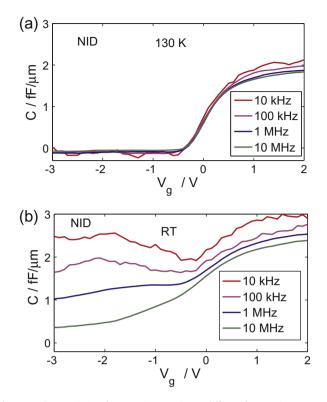

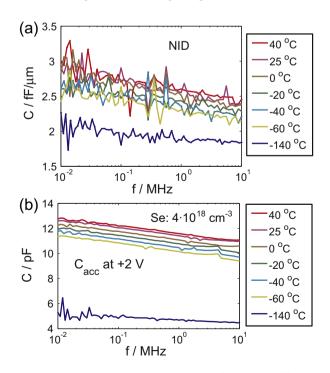

The measured CV characteristics of such InAs nanowire capacitor are shown in Figure 5.2a. For the not intentionally doped nanowires, the depletion capacitance reaches zero at all temperatures up to room temperature. It also contains a temperature activated stretch-out region, which is attributed to the interface traps [72]. The accumulation capacitance does not saturate as expected due to the non parabolic band structure of InAs. The accumulation capacitance is temperature sensitive, but this cannot be attributed to the intrinsic carrier generation, as the doping level in NID InAs nanowires is  $8 \cdot 10^{17} \text{ cm}^{-3}$ , which is much larger than the  $5 \cdot 10^{15} \text{ cm}^{-3}$  carrier density for intrinsic InAs [1]. Also, as nanowire InAs is a wurtzite instead of a zinc blende, the larger band gap should lower the intrinsic carrier concentration even more. The temperature variation of the accumulation capacitance is therefore attributed to traps present in the  $HfO_2$ .

Figure 5.2: CV characteristics of undoped nanowire capacitor: a) CV curves, measured in DOWN sweep direction at different temperatures at 100 MHz. b) Nanowire CV hysteresis at different temperatures. The hysteresis loops are offset vertically for easier comparison c) CV characteristics at 10 MHz and d) 100 kHz

InAs nanowire CV profiles have a considerable hysteresis at all temperatures, as shown

in Figure 5.2b. The UP sweep curve (the voltage is ramped from -2 V to +2 V) is observed to be temperature independent, while the DOWN sweep curve (the voltage is ramped from +2 V to -2 V) stretches with increasing temperature. As only the semiconductor is expected to be temperature sensitive, the DOWN sweep is therefore related to the response from the oxide/semiconductor interface. The UP sweep is then attributed to the charge movement inside the  $HfO_2$  oxide.

CV measurements at different frequencies are shown in Figure 5.2 c and d. It is clear, that both temperature and frequency increases the stretch-out. The increase in the depletion capacitance can be related to the hole inversion layer. However, a full depletion is expected before the increase of capacitance when only the inversion layer is present. The measurements at 100 kHz show that the capacitance decreases little during voltage sweep, indicating that the trap response is stronger than the minority carrier response at this frequency. At higher frequencies the nanowire becomes fully depleted showing that the hole inversion layer is negligible.

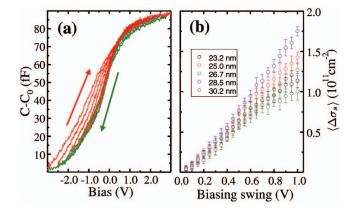

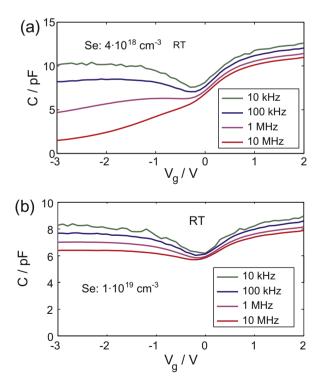

#### 5.2 Nanowire doping level

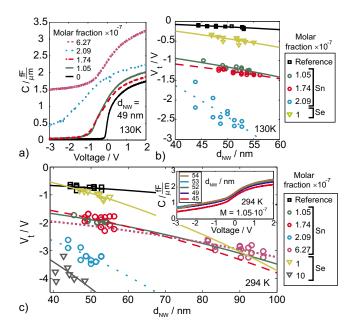

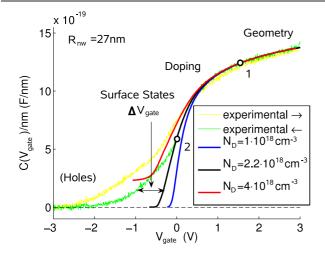

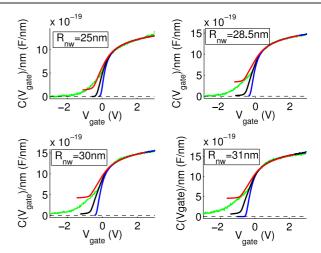

The CV characterization is a standard technique to extract the doping density, as the capacitance is proportional to the electron density in the semiconductor. A typical method is to determine the threshold voltage from  $1/C^2$  plot vs Voltage and calculate the doping concentration  $(N_D)$  using a standard MOS model. However, the radial geometry of the nanowires and the non parabolic bands makes it complicated to determine the exact capacitance behavior with applied voltage. Instead, the use of fully depleted nanowires offers a simpler solution.

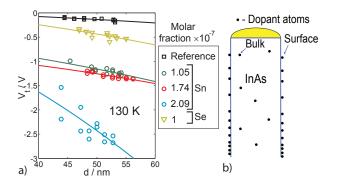

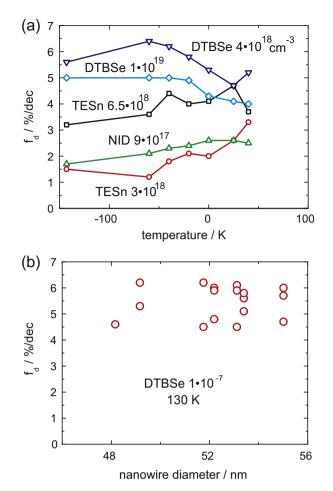

Figure 5.3: a)  $V_T$ - $d_{nw}$  plot for Sn and Se doped nanowire capacitors b) Schematic of dopant distribution in InAs nanowire

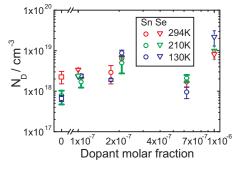

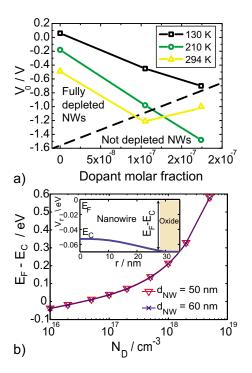

In the fully depleted nanowire, the threshold voltage  $(V_T)$  is proportional to the uncompensated charge density only.  $V_T$  is extracted by making a linear fit to the CV profile and plotted vs a nanowire diameter (d), as shown in Figure 5.3a. It is apparent that  $V_T$  is diameter dependent, as the nanowire area increases with  $\pi r^2$ , which means that the number of charges per area increase at the same rate. Therefore the increase in the slope means that more charges are present in the nanowire, implying a higher doping level.

It is also clear, that not only the slope of the  $V_T - d$  curves increases, but also different doping levels cause a large shift of the threshold voltage. However, the shift of threshold voltage with higher dopant flow can not be related to the doping level as this is accounted by the slope of the curve. Therefore the shift has to be related to the dopant distribution profile. In analogy with standard MOS theory, the shift is attributed to the surface charge. This means, that doped nanowires contain charges not only inside it, but on the nanowire side facets as well. Interestingly, there are more charges on the surface than in the bulk of the nanowire. This is why there is a clear separation between different  $V_T - d$  curves, as otherwise they should extend from the same origin. The important result is that dopants tend to preferentially incorporate at the nanowire surface, as shown in Figure 5.3b. A similar dopant distribution is observed in Ge nanowires, where the effect is enhanced by a lateral growth [73].

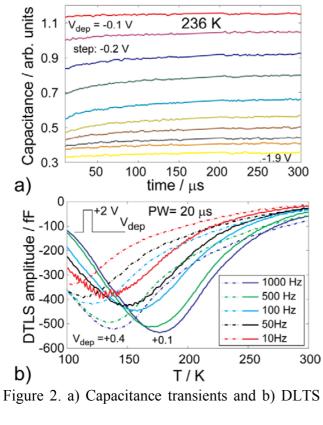

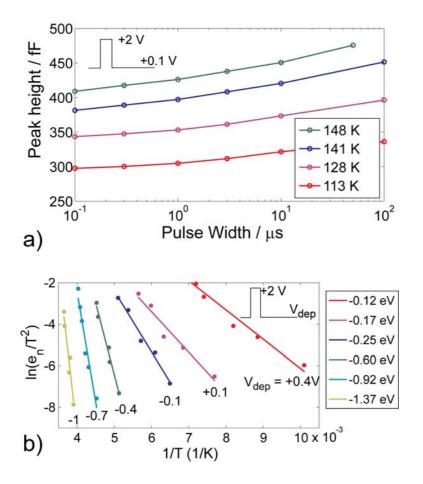

#### 5.3 Nanowire capacitance transients

The capacitance hysteresis means that there is a time component, which is attributed to the electron release by a Schottky-Read-Hall process. To measure capacitance transients, first, a bias pulse is applied to push the capacitor into the accumulation. During this pulse, the traps are filled with electrons. Second, the bias is lowered in order to create a depletion layer. As the Fermi level is lowered to the band gap, the electrons, located in traps above the Fermi level are emitted, causing a change in the depletion layer width and therefore a capacitance transient. The rate of the transient is proportional to the difference in energy between the trap position and the conduction band. The rate therefore contains information about the energy of the trap.

The rate of capacitance transients can be measured using Deep Level Transient Spectroscopy (DLTS). This measurement technique sets the rate window, within which the transients can be detected and determines the temperature of the detected transient. By measuring transients at different rate windows, the temperature spectrum of the transient rate is obtained. As the rate is exponential to the trap energy level, the spectra is analyzed using Arrhenius plots to obtain the trap energy.

The DLTS measurements reveal a bias dependent trap energy, which exceeds the band gap of the InAs. Such behavior is unexpected, as the trap energy is determined by the separation between the level of the trap and the conduction band. As more negative bias is applied the Fermi level can be lowered to scan states deeper within the band gap, but as it approaches the valence band, the deep level traps can now emit their electrons directly to the valence band. However such situation is outside the bounds of the standard model. Still, the standard model can be applied to analyze data while Fermi level is above the mid gap. It is observed that traps with activation energy levels of 0.25 eV are present in  $InAs/HfO_2$  interface

# Characterization of Overgrown InAs

For nano-sized InAs structures, the pinning effect can be the dominant conduction mechanism. Therefore it is important to quantify the extent of the pinning within the material and evaluate how it affects the mobility of the structure. Overgrown metal patterns increase considerably the surface area within the semiconductor material, thus affecting the semiconductor properties. For example the conductance can be tuned by several orders of magnitude in GaAs [74] due to the carrier depletion around the overgrown metal pattern. Similarly the increased surface area within InAs should enhance the Fermi level pinning. Therefore overgrown metal patterns are integrated within the thin InAs layers. A well overgrown structure can increase the surface area in InAs in a controlled fashion, without affecting the crystalline structure or the defect density, thus allowing measuring the surface contribution to the thin film properties. As tungsten is thermally stable in InAs [75], and there is little expected W diffusion during low temperature growth [76], tungsten is chosen as a mask for the overgrowth. This chapter presents the tungsten overgrowth by the InAs on a GaAs substrate.

#### 6.1 Overgrowth

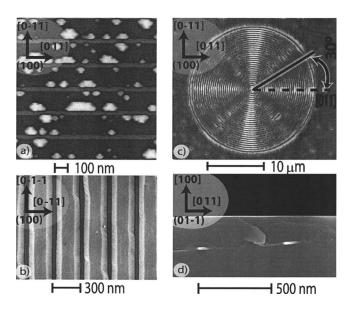

In order to enhance surface to volume ratio, a thin InAs film is required. Therefore InAs has to be grown on semi-insulating substrate to avoid the substrate conduction, present in narrow gap substrates. A GaAs substrate is chosen as it allows easy transition to the InAs growth. However, GaAs is strongly lattice mismatched to InAs, therefore the growth is heteroepitaxial. Also the growth mode changes to 3D island growth, which can hamper the planarization. To overcome these difficulties, the growth parameters are investigated to obtain a successful overgrowth.

The overgrowth is done in a layer by layer growth mode, therefore the 3D growth mode has to be changed. This is best done by reducing the growth temperature to 500  $^{\circ}C$  as it reduces the Stranski-Krastanow island size distribution and increases their density. To obtain a layer, the islands have to coalesce, which is achieved at a low V/III ratio due to enhancement of the growth of the underlying wetting layer [77]. Of course, threading dislocations are created in the process, due to the nature of mismatched growth.

After the layer by layer growth mode is achieved, W patterns can be incorporated. W is placed directly on the GaAs substrate, as this does not hinder a successful overgrowth.

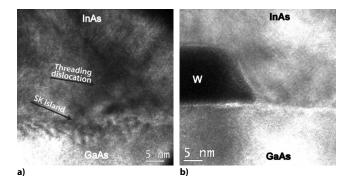

6

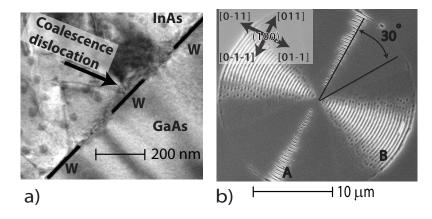

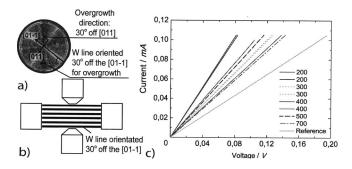

The overgrown InAs film is void free as shown in Figure 6.1a, but coalescence dislocations form over the W pattern during planarization. It is clear that their density is proportional to the number of W lines, and maximum two dislocations are generated over one tungsten line. The origin of the coalescence dislocation is attributed to different film relaxation on the left and right side of the tungsten film, thus epitaxial information no longer matches when the two growth fronts meet.

Figure 6.1: W patterns overgrown by InAs on GaAs substrate. a) TEM image of the overgrown W pattern, b) SEM image of overgrown concentric circles of tungsten.

As shown in Figure 6.1b, the tungsten lines are placed in concentric circles, which are overgrown by InAs. The overgrowth is preferential in a particular direction, determined to be  $30^{\circ}$  off the [011], while in others directions, a formation of  $\{111\}$  ridges is observed, as a  $\{111\}$  surface has the slowest growth rate.

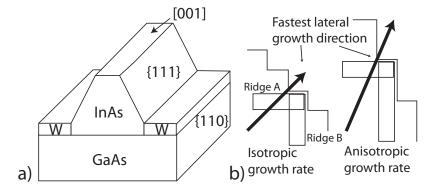

To understand the origin of the preferential overgrowth direction, we have to analyze ridges A and B, that form along the [011] and [011] directions, respectively, marked in Figure 6.1b. Both of these ridges have {111} side facets, as shown in Figure 6.2a, but the side facets of A ridge are In terminated, while for the B ridge, they are As terminated. As In terminated surface has higher growth rate than the As terminated surface, therefore the A ridge is more overgrown and is shorter compared to the B ridge, as seen in Figure 6.1b.

The presence of W lines disturbs the thermodynamic equilibrium shape of the ridge, forcing the crystal to orient itself along the tungsten pattern. The new crystal shape along the tungsten line is composed of both A and B ridges, creating a vicinal surface, as shown in Figure 6.2b. As only A and B ridges are possible under low temperature growth conditions, the crystal edge forms kinks, composed only of A and B ridges. The preferential overgrowth direction is then along the highest kink density, as vicinal surfaces enhance the lateral growth rate. However due to asymmetry of the ridge length in InAs (Figure 6.2b), the number of kinks is largest not at the  $45^{\circ}$  angle, but at an angle closer

to the [011] direction. Therefore the preferential overgrowth direction in InAs is along the  $30^{\circ}$  off the [011] [78].

Figure 6.2: a) Schematic of the {111} ridge, formed between W lines. b) Schematic of the vicinal surface formation required for overgrowth

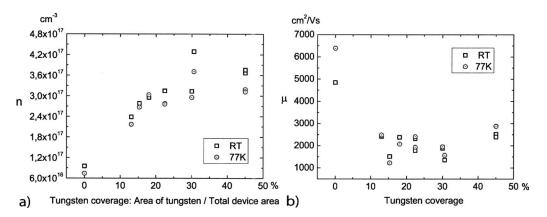

# 6.2 Electrical Characterization of overgrown InAs/W patterns

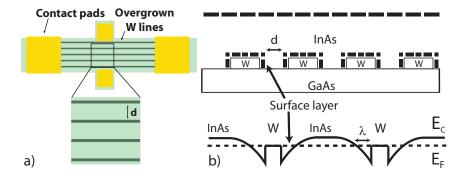

In order to evaluate the effect of the surface pinning in InAs, a simple device is used, shown in Figure 6.3a, where the overgrown W lines are placed parallel to each other and separated by a spacing d. By varying d, the density of the tungsten pattern is varied systematically, and thus the area of the surface pinning layer. It is therefore expected that at large d, the overgrown pattern has no effect on the material, while at lower d the overgrown surface area increases, affecting the electrical conduction of the device.

The measured overgrown devices have up to 5 times higher conductance, compared to the device without tungsten. This is much more, than the expected 15% increase due to the conductivity of the tungsten. Therefore the conductivity is related to the tungsten-semiconductor interface. Hall measurements reveal that the carrier concentration increases with increasing tungsten density and then saturates at  $3.5 \cdot 10^{17} \text{ cm}^{-3}$ . The saturation indicates that there is an effective length ( $\lambda$ ) of the surface pinning region, present around each tungsten line, as shown in Figure 6.3b and c. However, the mobility does not vary with the tungsten density and also is lower than the mobility of tungsten free device. First, this allows dismissing the influence of coalescence dislocations, as their density is higher when more tungsten is present. The mobility is therefore attributed to the surface pinning region, which is the dominant conduction path in the device. Even if the tungsten density is increased, the Hall signal is still dominated by the surface, therefore no mobility change is observed.

Figure 6.3: a) Schematic of overgrown device for Hall measurements. d is the distance between tungsten lines, while the line width is kept fixed. b) Schematic of the structure and the band diagram of the overgrown InAs.

## InAs membranes on GaSb buffer layers

Thin InAs films with bulk mobility are obtained using buffer layers but at the expense of the buffer thickness, which exceeds > 4  $\mu m$  [24]. However, such thick buffer makes it difficult to integrate InAs with other devices on the substrate due the large difference in height between the substrate and InAs layer. It is also very expensive and time consuming to grow thick layers in any epitaxial reactor. On the other hand, InAs is a high mobility semiconductor, and not all electronic applications require the highest possible mobility. Therefore it is interesting to learn whether InAs can be integrated using thin buffer layers and determine how much the mobility is lowered due to the lower structural quality of the buffer.

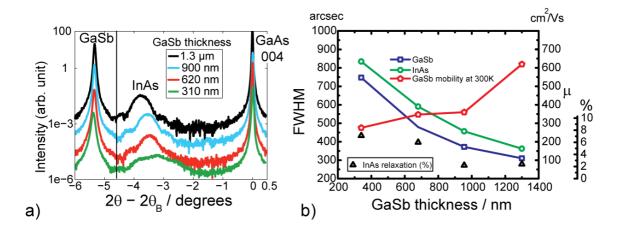

#### 7.1 GaSb buffer growth

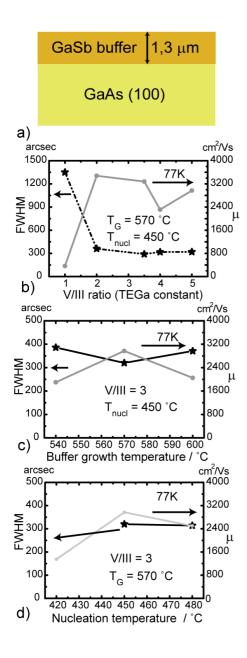

The GaSb is chosen as it has a lattice constant of 6.095 Å, which is only 0.6% lattice mismatched to InAs layer. This leads to a large critical thickness and more than a few monolayers of InAs can be grown directly on GaSb. As epitaxial growth conditions tend to be reactor dependent, a growth of GaSb has to be optimized before starting to investigate the quality of InAs. The growth optimization also establishes a baseline of quality for the buffer material. Typical parameters for optimization are growth temperature, V/III ratio and nucleation temperature. As GaSb is grown on GaAs, the growth mode is again 3D, therefore a low temperature nucleation is used to change the mode to layer by layer one. The low temperature nucleation increases the density of GaSb islands on GaAs surface to favor the transition.

The growth of GaSb is not trivial, as Sb tends to segregate and coat surfaces with an Sb monolayer. This means that during the growth, the Sb adatoms have to bind to Ga atoms without creating an excess. Ga atoms also cannot be oversupplied, as then they will start forming Ga droplets, deteriorating the growth. To avoid this, both the V/III ratio and the growth temperature are optimized. The optimum growth conditions are 450  $^{o}C$  for nucleation temperature, 3 for V/III ratio and 570  $^{o}C$  for buffer layer growth temperature.

7

#### 7.2 InAs integration onto GaSb

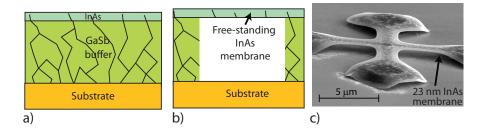

In order to have a reference of a consistent quality, metamorphic InAs film is chosen, that have the same lattice constant as the GaSb layer. This means that defect density in both layers is expected to be the same as well. If thicker InAs layers are grown, then they relax their metamorphic lattice and generate additional defects in the process. A 23 nm film thickness was chosen as it is under the critical thickness according to a conservative Mathews-Blackeslee model [35]. A conservative critical thickness is used to ensure that the dislocations in GaSb do not enhance the relaxation of the InAs metamorphic layer.

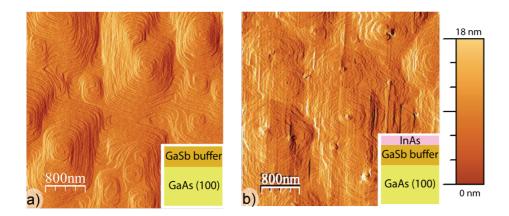

To vary the quality of the buffer layer, the dislocation density is changed by varying the thickness of GaSb buffer layers. As InAs is metamorphic, the dislocation density depends directly on the defect density in the buffer layer, as shown in Figure 7.1a. Therefore a relation between the structural quality of the buffer layer and InAs layer can be evaluated. The quality of both layers is known to be proportional to each other, but in this way it can be quantified as well.

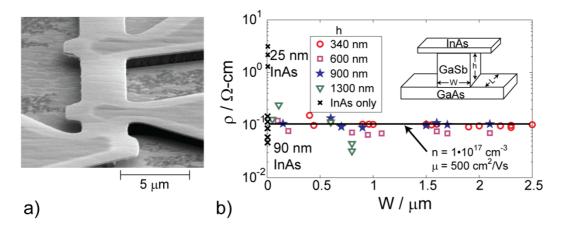

Figure 7.1: a) Schematic of a grown InAs/GaSb structure. b) Schematic of the free-standing InAs membrane. c) SEM image of a free-standing InAs membrane for Hall measurements.

To establish a relation between the quality of the buffer and the InAs, first the InAs layer is selectively etched away. The remaining GaSb layer is measured and mobility is shown to be proportional to the structural quality as expected. The second step is to remove the GaSb layer by selective etch, as shown in 7.1b and measure InAs membranes. This removes the large substrate conduction, but retains the metamorphic lattice of InAs. As shown in Figure 7.1c, the the edges of the InAs membrane are bent downwards, although the bending should be upwards, as InAs is tensile strained. The downward bend is attributed to the Van der Waals forces between the etching liquid and the InAs membrane. However, membrane bridges are flat and also do not bend in the middle, which indicates that the structure has not relaxed.

The electrical measurements on membranes reveal that thin InAs structures are highly resistive. High resistivity normally means low material quality. If thicker (90 nm thick) membranes are measured than resistivity is much lower and a mobility of 2000  $cm^2/Vs$  is obtained. Therefore the high resistivity of the thin membranes should be related to the

membrane processing, but not a sign of a low quality. By passivating the surface of thin membranes with sulfur solution, the resistivity of membranes is lowered about 5 times. This decrease indicates that thin membranes are very sensitive to surface treatments. However, even passivated structures are still moderately resistive, indicating that the passivation is not sufficient. The possible approach is to investigate membranes with thicknesses of about 50 nm, as these are shown to be conductive [27]. Although it is not clear whether these layers will still be under the critical thickness to remain metamorphic after the membrane processing.

Therefore currently it is established that structural qualities of InAs and GaSb layers are directly proportional to each other. It is expected that the electrical quality will follow this relation as well, which is shown to be valid at least for the GaSb buffer layer.

InAs membranes on GaSb buffer layers

### Bibliography

- [1] "Information available at http://www.ioffe.ru/SVA/NSM/Semicond/,"

- [2] A. K. R. Hosseini, "Introducing a High Sensitive Hall Effect Sensor," Engineering and Technology, vol. 39, pp. 431–434, 2008.

- [3] H. Kroemer, "The 6.1 Åfamily (InAs, GaSb, AlSb) and its heterostructures: a selective review," *Physica E*, vol. 20, pp. 196 – 203, 2004.

- [4] D.-H. Kim and J. A. Del Alamo, "30-nm InAs PHEMTs with fT = 644 GHz and fmax = 681 GHz," *IEEE Electron Device Letters*, vol. 31, pp. 806 – 808, 2010.

- [5] L. O. Olsson, C. B. M. Andersson, M. C. Håkansson, J. Kanski, L. Ilver, and U. O. Karlsson, "Charge Accumulation at InAs Surfaces," *Physical Review Letters*, vol. 76, pp. 3626 9, 1996.

- [6] M. Noguchi, K. Hirakawa, and T. Ikoma, "Intrinsic electron accumulation layers on reconstructed clean InAs(100) surfaces," *Physical Review Letters*, vol. 66, pp. 2243 – 6, 1991.

- [7] L. F. J. Piper, T. D. Veal, M. J. Lowe, and C. F. McConville, "Electron depletion at InAs free surfaces: Doping-induced acceptorlike gap states," *Physical Review B*, vol. 73, pp. 195321 – 1, 2006.

- [8] H. Hasegawa, H. Ohno, H. Ishii, T. Haga, Y. Abe, and H. Takahashi, "Origin and properties of interface states at insulator-semiconductor and semiconductorsemiconductor interfaces of compound semiconductors," *Applied Surface Science*, vol. 41-42, pp. 372 – 82, 1989.

- [9] T. C. Shen, G. B. Gao, and H. Morkoc, "Recent developments in ohmic contacts for III-V compound semiconductors," vol. 10, pp. 2113 – 32, 1992.

- [10] R. Pino, Y. Ko, and P. Dutta, "Adhesion-free growth of AlSb bulk crystals in silica crucibles," *Journal of Crystal Growth*, vol. 290, pp. 29 – 34, 2006.

- [11] W. R. M. A. Herman and H. Sitter, Epitaxy: Physical Principles and Technical Implementation. Springer, New York, 2004.

- [12] J. C. P. Chang, T. P. Chin, C. W. Tu, and K. L. Kavanagh, "Multiple dislocation loops in linearly graded  $In_xGa_{1-x}As$  ( $0 \le x \le 0.53$ ) on GaAs and  $In_xGa_{1-x}P$  ( $0 \le x \le 0.32$ ) on GaP," Applied Physics Letters, vol. 63, pp. 500 – 2, 1993.

- [13] S. Huang, G. Balakrishnan, A. Khoshakhlagh, A. Jallipalli, L. Dawson, and D. Huffaker, "Strain relief by periodic misfit arrays for low defect density GaSb on GaAs," *Applied Physics Letters*, vol. 88, pp. 131911 – 1, 2006.

- [14] S. Mendach, C. M. Hu, C. Heyn, S. Schnüll, H. P. Oepen, R. Anton, and W. Hansen, "Strain relaxation in high-mobility InAs inserted-channel heterostructures with metamorphic buffer," *Physica E: Low-dimensional Systems and Nanostructures*, vol. 13, pp. 1204 – 7, 2002.

- [15] J. Li, J. Bai, J. Park, B. Adekore, K. Fox, M. Carroll, A. Lochtefeld, and Z. Shellenbarger, "Defect reduction of GaAs epitaxy on Si (001) using selective aspect ratio trapping," *Applied Physics Letters*, vol. 91, pp. 21114 – 1, 2007.

- [16] D. Forbes, S. Hubbard, R. Raffaelle, and J. S. McNatt, "Au-catalyst-free epitaxy of InAs nanowires," *Journal of Crystal Growth*, vol. 312, pp. 1391 – 5, 2010.

- [17] M. Egard, S. Johansson, A.-C. Johansson, K.-M. Persson, A. W. Dey, B. M. Borg, C. Thelander, L.-E. Wernersson, and E. Lind, "Vertical InAs Nanowire Wrap Gate Transistors with  $f_t > 7$  GHz and  $f_{max} > 20$  GHz," *Nano Letters*, vol. 10, pp. 809 812, 2010.

- [18] T. Tanaka, K. Tomioka, S. Hara, J. Motohisa, E. Sano, and T. Fukui, "Vertical surrounding gate transistors using single InAs nanowires grown on Si substrates," *Applied Physics Express*, vol. 3, p. 025003, 2010.

- [19] K. Kavanagh, "Misfit dislocations in nanowire heterostructures," Semiconductor Science and Technology, vol. 25, p. 024006, 2010.