### LUND UNIVERSITY

### Novel Processing and Electrical Characterization of Nanowires

Storm, Kristian

2013

Link to publication

Citation for published version (APA): Storm, K. (2013). Novel Processing and Electrical Characterization of Nanowires.

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study or recorder.

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

### Novel Processing and Electrical Characterization of Nanowires

Kristian Storm | Division of Solid State Physics | Department of Physics | Lund University

# Novel Processing and Electrical Characterization of Nanowires

### Doctoral Thesis

### **Kristian Storm**

Faculty Opponent Prof. Daniel Dapkus University of Southern California USA

### LUND UNIVERSITY

Department of Physics Division of Solid State Physics Lund, Sweden, 2013

Academic Dissertation which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Friday, April 19<sup>th</sup> at 13.15 in Rydbergsalen, Sölvegatan 14, Lund, for the degree of Doctor of Philosophy in Engineering.

| Organization                                                      | Document name                         |                           |  |

|-------------------------------------------------------------------|---------------------------------------|---------------------------|--|

| LUND UNIVERSITY                                                   | DOCTORAL DISSERTATION                 |                           |  |

| LUND UNIVERSITI                                                   |                                       | non                       |  |

| Department of Physics                                             | April 19, 2013                        | Date of issue             |  |

| Department of Physics                                             | April 19, 2015                        |                           |  |

| Division of Solid State Physics                                   |                                       |                           |  |

| P.O. Box 118                                                      |                                       |                           |  |

| SE-221 00 Lund                                                    |                                       |                           |  |

|                                                                   |                                       |                           |  |

|                                                                   |                                       |                           |  |

| Author(s)                                                         | Sponsoring organization               |                           |  |

| Kristian Storm                                                    |                                       |                           |  |

| Title and subtitle                                                |                                       |                           |  |

| Novel Processing and Electrical Characterization of Nanowire      | 26                                    |                           |  |

| Tover Processing and Electrical Characterization of Manowire      |                                       |                           |  |

| Abstract                                                          |                                       |                           |  |

| This thesis investigates novel electrical nanowire characteriza   | tion tools and devices. Conv          | entional characterization |  |

| methods, long available to bulk semiconductor samples, have       |                                       |                           |  |

| The first part of the thesis describes the development of Hall e  |                                       |                           |  |

| tool for nanowires. It is shown that Hall effect measurements     |                                       |                           |  |

| self-aligned lifting layer. By combining experimental data wit    |                                       |                           |  |

| distribution under the influence of a magnetic field, the carrier |                                       |                           |  |

| We found that the nanowire shell exhibits a doping gradient a     |                                       |                           |  |

| inhomogeneity is important to account for and engineer when       |                                       |                           |  |

| innonlogeneity is important to account for and engineer when      | making devices using ini in           | anownes.                  |  |

| The second part of the thesis demonstrates how capacitance-v      | oltage measurements can be            | performed on arrays of    |  |

| InAs nanowires. Using a novel device structure, the capacitan     |                                       |                           |  |

| parasitic capacitances. A model was developed to simulate the     |                                       |                           |  |

| fitted to the experimental data to extract the doping concentrat  |                                       |                           |  |

| capacitance-voltage sweeps was used to calculate the trap den     |                                       |                           |  |

| capacitance-voltage sweeps was used to calculate the trap den     | sity close to the mas-mo <sub>2</sub> | diciceurie interrace.     |  |

| Finally, studies of gate effects in nanowires are presented. We   | e demonstrate how the gating          | efficiency is improved by |  |

| means of wrapped or semiwrapped gates on nanowires. Field-        |                                       |                           |  |

| described that exhibit both ambipolar behavior and gating effi    |                                       |                           |  |

| properties were used to fabricate a field-effect diode, a device  |                                       |                           |  |

| incorporation in the active region. We also demonstrate how r     |                                       |                           |  |

| equipped with a fully wrapped gate electrode. This device was     |                                       |                           |  |

| research in which a uniform gating effect is desired.             | s developed as part of a plan         | orm to perform basic      |  |

| Key words                                                         |                                       |                           |  |

| Nanowires, Processing, Characterization, InAs, InP, Hall effe     | ct Canacitance Gate LED               | Transistor                |  |

| Classification system and/or index terms (if any)                 | er, cupacitance, Gate, LED,           | 1141010101                |  |

| Chastilitation system and/or index terms (if any)                 |                                       |                           |  |

|                                                                   |                                       |                           |  |

|                                                                   |                                       |                           |  |

| Supplementary bibliographical information                         |                                       | Language                  |  |

|                                                                   |                                       | English                   |  |

|                                                                   |                                       |                           |  |

|                                                                   |                                       | 1                         |  |

| ISSN and key title                                                |                                       | ISBN                      |  |

|                                                                   |                                       | 978-91-7473-482-9         |  |

| Recipient's notes                                                 | Number of pages                       | Price                     |  |

|                                                                   | 135                                   |                           |  |

|                                                                   | Security classification               |                           |  |

|                                                                   |                                       |                           |  |

| Distribution by (name and address)                                |                                       |                           |  |

I, the undersigned, being the copyright owner of the abstract of the above-mentioned dissertation, hereby grant to all reference sources permission to publish and disseminate the abstract of the above-mentioned dissertation.

Signature \_\_\_\_\_

Date 2013-03-19

### Novel Processing and Electrical Characterization of Nanowires

Kristian Storm

Doctoral Thesis 2013

### LUND UNIVERSITY

Division of Solid State Physics Department of Physics Lund University

### Novel Processing and Electrical Characterization of Nanowires

© 2013 Kristian Storm

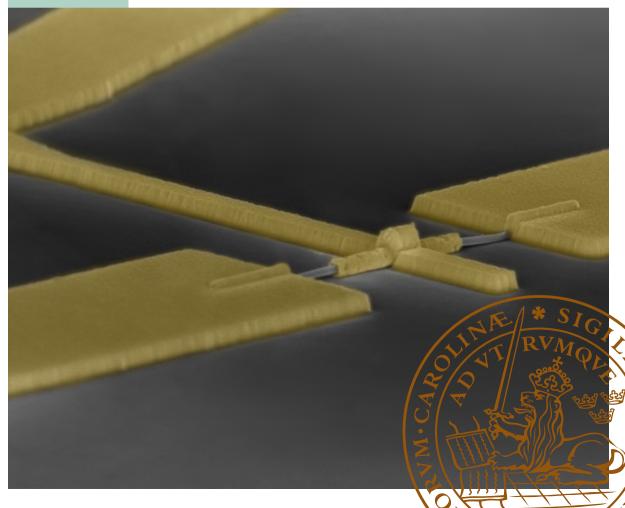

Cover: SEM image of a laterally oriented InAs nanowire with a fully wrapped gate electrode.

Division of Solid State Physics Department of Physics Faculty of Engineering, LTH Lund University P.O. Box 118 SE-221 00 Lund Sweden

http://www.ftf.lth.se

ISBN 978-91-7473-482-9

### Contents

| Al                                   | Abstract iii                             |                                                                                                                                                                                                                                                                                               |                                                                                              |  |  |

|--------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| Populärvetenskaplig sammanfattning v |                                          |                                                                                                                                                                                                                                                                                               |                                                                                              |  |  |

| $\mathbf{Li}$                        | st of                                    | papers                                                                                                                                                                                                                                                                                        | vii                                                                                          |  |  |

| Al                                   | obrev                                    | viations                                                                                                                                                                                                                                                                                      | $\mathbf{x}\mathbf{i}$                                                                       |  |  |

| 1                                    | <b>Intr</b><br>1.1<br>1.2                | oduction         The emergence of nanowire research         Nanowire applications         1.2.1         Nanowire field-effect transistors         1.2.2         Light-emitting diodes                                                                                                         | $     \begin{array}{c}       1 \\       2 \\       4 \\       5 \\       6     \end{array} $ |  |  |

|                                      | $\begin{array}{c} 1.3\\ 1.4 \end{array}$ | 1.2.3       Solar cells          Challenges in nanowire characterization          Aim of the thesis                                                                                                                                                                                           |                                                                                              |  |  |

| <b>2</b>                             |                                          | l effect measurements                                                                                                                                                                                                                                                                         | 11                                                                                           |  |  |

|                                      | 2.1                                      | Classical Hall effect measurements                                                                                                                                                                                                                                                            | 11<br>13                                                                                     |  |  |

|                                      | 2.2                                      | Hall effect in nanowires2.2.12D Poisson simulations2.2.23D current-continuity modeling2.2.3Experimental nanowire Hall characteristics2.2.4Limits for nanowire Hall measurements                                                                                                               | 14<br>17<br>19<br>20<br>22                                                                   |  |  |

|                                      | 2.3                                      | Other single-nanowire characterization tools2.3.1Single-nanowire LEDs2.3.2Multiple-probe measurements                                                                                                                                                                                         | $23 \\ 23 \\ 24$                                                                             |  |  |

| 3                                    | Cap                                      | acitance–voltage characterization                                                                                                                                                                                                                                                             | <b>27</b>                                                                                    |  |  |

|                                      | 3.1<br>3.2                               | MOS interfacesNanowire capacitorsNanowire capacitor design considerations3.2.1Nanowire capacitor design considerationsNanowire capacitor design considerations3.2.2HysteresisHysteresis3.2.3Capacitance simulationsNanowire capacitors3.2.4Progress in nanowire capacitorsNanowire capacitors | 27<br>30<br>32<br>34<br>35<br>38                                                             |  |  |

| <b>4</b>     | Gat          | ate control in nanowires 39                           |           |  |

|--------------|--------------|-------------------------------------------------------|-----------|--|

|              | 4.1          | Gate control of semiconductors                        | 39        |  |

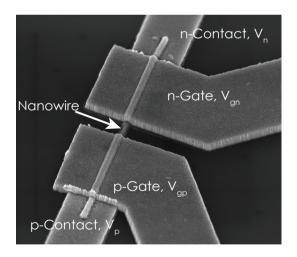

|              | 4.2          | The dual-gate field-effect diode                      | 41        |  |

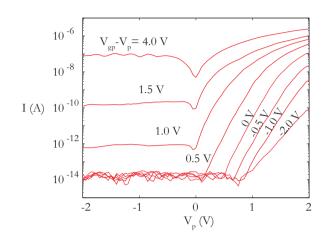

|              |              | 4.2.1 Individual carrier control with $\Omega$ -gates | 42        |  |

|              |              | 4.2.2 Operation of the field-effect diode             | 44        |  |

|              | 4.3          | Lateral wrap-gated nanowire devices                   | 45        |  |

| 5            | Con          | cluding remarks and outlook                           | <b>49</b> |  |

| $\mathbf{A}$ | Der          | ivations                                              | 53        |  |

|              | A.1          | Cylindrically symmetric p–n junctions                 | 53        |  |

|              | A.2          | Hall effect simulation framework                      | 55        |  |

|              | A.3          | Conductivity tensor                                   | 57        |  |

| Ac           | knov         | vledgments                                            | 59        |  |

| Bi           | Bibliography |                                                       | 61        |  |

### Abstract

This thesis investigates novel electrical nanowire characterization tools and devices. Conventional characterization methods, long available to bulk semiconductor samples, have been adapted and transferred to the nanowire geometry. The first part of the thesis describes the development of Hall effect measurements, an entirely new characterization tool for nanowires. It is shown that Hall effect measurements can be performed on InP core–shell nanowires using a self-aligned lifting layer. By combining experimental data with results from simulations of band diagrams and current distribution under the influence of a magnetic field, the carrier density in the n-type nanowire shell can be determined. We found that the nanowire shell exhibits a doping gradient along the length of the nanowire. This doping inhomogeneity is important to account for and engineer when making devices using InP nanowires.

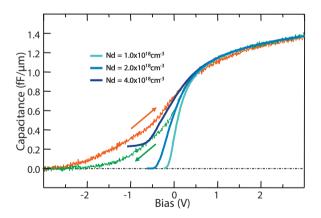

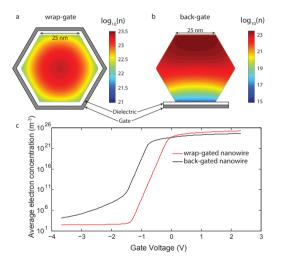

The second part of the thesis demonstrates how capacitance–voltage measurements can be performed on arrays of InAs nanowires. Using a novel device structure, the capacitance signal from the nanowires can be distinguished from parasitic capacitances. A model was developed to simulate the capacitance–voltage behavior of the nanowires and was fitted to the experimental data to extract the doping concentration. Furthermore, the hysteresis observed in the capacitance–voltage sweeps was used to calculate the trap density close to the InAs–HfO<sub>2</sub> dielectric interface.

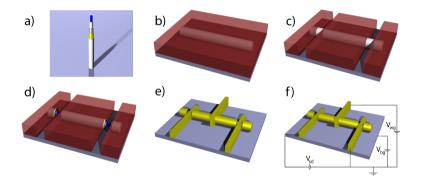

Finally, studies of gate effects in nanowires are presented. We demonstrate how the gating efficiency is improved by means of wrapped or semiwrapped gates on nanowires. Field-effect transistors made from InP nanowires are described that exhibit both ambipolar behavior and gating efficiency only 13% lower than the theoretical limit. These properties were used to fabricate a field-effect diode, a device in which a p–n junction is formed without any doping incorporation in the active region. We also demonstrate how nanowires positioned laterally on a substrate can be equipped with a fully wrapped gate electrode. This device was developed as part of a platform to perform basic research in which a uniform gating effect is desired.

iv

### Populärvetenskaplig sammanfattning

Nanoteknik och nanotrådar omnämns ofta media idag, men vad är egentligen en nanotråd, och vad kan den användas till? Dagens datorer, lysdioder och solceller är till stor del beroende av *halvledare*. En halvledare är ett kristallint material där man enkelt kan ändra ledningsförmågan. Man kan dels bestämma ledningsförmågan när materialet tillverkas genom att tillföra ytterst små koncentrationer av andra ämnen, *dopämnen*, och dels efter att materialet formats till en komponent, med hjälp av elektriska fält. Denna egenskap hos halvledare är ytterst användbar och har möjliggjort såväl datorrevolutionen, som den sett ut de senaste 50 åren, som dagens effektiva lysdioder och solceller. Det i särklass mest kända halvledarmaterialet är kisel som används i bland annat integrerade kretsar och solceller, men det finns många andra grundämnen och kombinationer av grundämnen som också är halvledare.

Nanotrådarna som undersöks i den här avhandlingen är också uppbyggda av halvledarmaterial. Istället för kisel har två andra halvledare undersökts, nämligen InP (indium-fosfid) och InAs (indium-arsenid). Nanotrådar skiljer sig från de "klassiska" halvledarna genom att de är formade till en tunn tråd istället för att tillverkas i en stor klump. Detta medför flera fördelar jämfört med det klassiska sättet att tillverka halvledare. Nanotrådar har en väldigt liten diameter, i storleksordningen 50 nm eller en tusendel av diametern av ett hårstrå. Denna lilla diameter gör att man kan kombinera olika material, vilka vanligtvis är svåra att kombinera i klassisk halvledarteknologi, i olika lager i nanotråden utan att defekter uppstår i kristallstrukturen. Detta medför nya användningsområden och gör det även möjligt att optimera existerande komponenter ytterligare.

Under det senaste decenniet har forskningen på nanotrådar accelererat kraftigt och det har blivit möjligt att tillverka nanotrådar i många olika sorters halvledarmaterial. Det har även upptäckts hur man kan tillföra dopämnen till nanotrådar för att ändra deras ledningsförmåga och därmed tillverka nanotrådskomponenter som anpassas för olika tillämpningar. Trots att kunskapen om hur man tillverkar nanotrådar i olika material och med olika elektriska egenskaper utvecklats snabbt, har möjligheten att i detalj undersöka och mäta dessa egenskaper släpat efter. Det är dels de små dimensionerna hos nanotrådarna och dels deras tredimensionella form som gör det besvärligt att utveckla verktyg för att karaktärisera dem. Denna avhandling handlar om hur vi utvecklat metoder för att elektriskt karaktärisera nanotrådar. Klassiska mätmetoder, som länge funnits tillgängliga för traditionella halvledarmaterial, har anpassats för att kunna användas på nanotrådar. Två av dessa, Hall- och kapacitans-karaktärisering, är metoder som används rutinmässigt på klassiska halvledarmaterial.

I en Hallmätning kör man en ström genom provet man är intresserad av och lägger samtidigt på ett magnetfält. Elektronerna som färdas genom provet påverkas av magnetfältet och det uppstår en spänning, en *Hallspänning*, vinkelrätt mot strömriktningen. Denna spänning kan mätas och från storleken på spänningen är det möjligt att beräkna koncentrationen av elektroner i provet. Denna egenskap är viktig att mäta eftersom den bestämmer ledningsförmågan hos halvledaren. Första delen av avhandlingen beskriver hur metoden anpassats och nu för första gången kan tillämpas på nanotrådar. Nanotrådarna som undersöks med Hallmätningar är främst tänkta att ingå som det aktiva elementet i lysdioder och solceller.

Kapacitansmätningar är en annan mätmetod som används på klassiska halvledare. För att göra kapacitansmätningar isolerar man först halvledaren med t.ex. en oxid och lägger sedan en metallkontakt ovanpå oxiden. När man lägger på en positiv spänning på metallkontakten dras det elektroner till ytan på halvledaren. Kapacitansen i provet är ett mått på hur många elektroner som dras till ytan per volt spänning som läggs på metallkontakten. Genom att mäta kapacitansen kan man beräkna olika egenskaper såsom koncentrationen av elektroner i halvledaren samt antalet elektronfällor i den isolerande oxiden och även för gränsytan mellan halvledaren och oxiden. I andra delen av avhandlingen beskrivs hur denna mätmetod anpassades och för första gången användes på nanotrådar som står upprätt på en provplatta.

Slutligen beskrivs hur en nanotrådstransistor kan tillverkas på ett helt nytt sätt. En transistor är beroende av en så kallad gate, en styrterminal som används för att öppna eller stänga flödet av ström. De transistorer som hittills tillverkats av nanotrådar är vanligtvis två olika sorter; antingen står ett stort antal trådar upp på provet och medger därför att den gate som används till trådarna har optimal verkningsgrad, eller så tillverkas de av enskilda trådar som ligger ner på ett prov. I det senare fallet har det tidigare inte varit möjligt att använda en gate som är lika optimal som när trådarna står upp. I den sista delen av avhandlingen beskrivs hur en ny tillverkningsmetod utvecklats för att kunna göra en gatekontakt i en optimal geometri till enskilda nanotrådar som samtidigt ligger ner på ett prov.

Arbetena som presenteras i den här avhandlingen utökar verktygslådan som finns tillgänglig för forskare som arbetar med nanotrådar. Detta leder till mer kunskap om hur man tillverkar och förbättrar avancerade nanotrådskomponenter och bidrar förhoppningsvis till att dessa finner tillämpningar inom solceller, lysdioder och transistorer.

### List of papers

The author changed his last name from Nilsson to Storm during the course of his PhD studies.

### I. Spatially resolved Hall effect measurement in a single semiconductor nanowire

K. Storm, F. Halvardsson, M. Heurlin, D. Lindgren, A. Gustafsson, P. M. Wu, B. Monemar and L. Samuelson Nature Nanotechnology 7, 718-722 (2012)

I helped coordinate the project, took part in all measurements, performed the simulations and wrote the paper.

#### II. InAs nanowire metal-oxide-semiconductor capacitors

S. Roddaro, **K. Nilsson**, G. Astromskas, L. Samuelson, L-E. Wernersson, O. Karlström and A. Wacker Aplied Physics Letters 92, 253509 (2008)

I contributed actively to planning the project, sample process development, measurements and discussions and participated in writing the paper.

### III. Analysing the capacitance–voltage measurements of vertical wrapped-gated nanowires

O. Karlström, A. Wacker, **K. Nilsson**, G. Astromskas, S. Roddaro, L. Samuelson and L-E. Wernersson Nanotechnology 19, 435201 (2008)

I participated actively in sample preparation, measurements and discussions and took part in writing the paper.

#### IV. Gate-induced Fermi level tuning in InP nanowires at efficiency close to the thermal limit

K. Storm, G. Nylund, M. Borgström, J. Wallentin, C. Fasth, C. Thelander and L. Samuelson

Nano Letters 11, 1127-1130 (2011)

I planned and took a leading role in processing and measurements and I wrote the paper.

#### V. Dual-gate induced InP nanowire diode

K. Storm, G. Nylund, M. Borgström, J. Wallentin, C. Fasth, C. Thelander and L. Samuelson AIP Conf. Proc. 1399, 279-280 (2011)

I helped coordinate and plan the project, took a leading role in processing and measurements and I wrote the paper.

#### VI. Realizing Lateral Wrap-Gated Nanowire FETs: Controlling Gate Length with Chemistry Rather than Lithography

K. Storm, G. Nylund, L. Samuelson and A. P. Micolich Nano Letters 12, 1-6 (2012), including cover artwork

I designed the structure, took a leading role in process development and electrical characterization, and participated actively in other measurements, discussions and in writing the paper.

The following papers are not included, because of overlapping content or because they deal with topics beyond the scope of this thesis.

### VII. Doping Incorporation in InAs nanowires characterized by capacitance measurements

G. Astromskas, **K. Storm**, O. Karlström, P. Caroff, M. Borgström and L-E. Wernersson

Journal of Applied Physics 108, 054306 (2010)

### VIII. Temperature and frequency characterization of InAs nanowire and $HfO_2$ interface using capacitance–voltage method

G. Astromskas, **K. Storm**, P. Caroff, M. Borgström, E. Lind and L-E. Wernersson Microelectronic Engineering 88, 444–447 (2011)

### IX. Scanning gate imaging of quantum dots in 1D ultra-thin InAs/InP nanowires

E. E. Boyd, **K. Storm**, L. Samuelson and R. M. Westervelt Nanotechnology 22, 185201 (2011)

#### X. Transient studies on InAs/HfO2 nanowire capacitors

G. Astromskas, **K. Storm** and L-E. Wernersson Applied Physics Letters 98, 013501 (2011)

#### XI. Growth of vertical InAs nanowires on heterostructured substrates S. Roddaro, P. Caroff, G. Biasiol, F. Rossi, C. Bocchi, K. Nilsson, L. Fröberg,

J. B. Wagner, L. Samuelson, L-E. Wernersson and L. Sorba Nanotechnology 20, 285303 (2009)

#### XII. A Comparative Study of the Effect of Gold Seed Particle Preparation Method on Nanowire Growth

M. E. Messing, K. Hillerich, J. Bolinsson, K. Storm, J. Johansson, K. A. Dick, K. Deppert

Nano Res 3, 506-519 (2010)

XIII. Charge pumping in InAs nanowires by surface acoustic waves S. Roddaro, E. Strambini, L. Romeo, V. Piazza, K. Nilsson, L. Samuelson and F. Beltram Semicond. Sci. Technol 25, 024013 (2010)

### XIV. Electrical and optical properties of InP nanowire ensemble $\mathrm{p}^+ - \mathrm{i} - \mathrm{n}^+$ photodetectors

H. Pettersson, I. Zubritskaya, N. T. Nghia, J. Wallentin, M. T. Borgström, K. Storm, L. Landin, P. Wickert, F. Capasso and L. Samuelson Applied Physics Lettters 98, 013501 (2011)

XV. A cathodoluminescence study of the influence of the seed particle preparation method on the optical properties of GaAs nanowires

A. Gustafsson, K. Hillerich, M. E. Messing, **K. Storm**, K. A. Dick, K. Deppert and J. Bolinsson

Nanotechnology 23, 265704 (2012)

### XVI. Geometric model for metalorganic vapor phase epitaxy of dense nanowire arrays

B. M. Borg, J. Johansson, K. Storm and K. Deppert

Journal of Crystal Growth 366, 15-19 (2013)

#### XVII. Transparently Wrap-Gated Semiconductor Nanowire Arrays For Studies of Gate-Controlled Photoluminescence

G. Nylund, **K. Storm**, H. Torstensson, J. Wallentin, D. Hessman and L. Samuelson

Submitted, ICPS 2012 Conference proceedings

### Abbreviations

| C-V                 | Capacitance–Voltage                               |

|---------------------|---------------------------------------------------|

| $\operatorname{CL}$ | Cathodoluminescence                               |

| CMOS                | Complementary Metal–Oxide–Semiconductor           |

| EBL                 | Electron Beam Lithography                         |

| FET                 | Field-Effect transistor                           |

| LED                 | Light-Emitting Diode                              |

| MOSFET              | Metal–Oxide–Semiconductor Field–Effect transistor |

| SEM                 | Scanning Electron Microscope                      |

xii

# Chapter 1 Introduction

In his groundbreaking 1959 lecture *There's plenty of room at the bottom*, Prof. Richard Feynman considered how the ability to directly manipulate individual atoms could lead to scientific breakthroughs in semiconductor physics, chemistry and biology. In one example, he described the requirements for writing the entire 24-volume *Encyclopedia Britannica* on the head of a pin: Each page would need to be scaled down by a factor of 25 000 in both dimensions. Although the method described by Feynman—writing each letter or a representation of the letter in metal—does not lead to a commercially viable storage medium, it did offer a challenge that has inspired many of the semiconductor research efforts of the last 55 years.

Let us see how far we have come since this original proposal. By estimating the word count to be 44 million, an average of 5 letters per word and 1 byte necessary to store each letter, the space required to store all the text in *Encyclopedia Britannica* amounts to roughly 220 MB. The record in commercial hard disk drives as of October 2012 is 1.5 Tbits/in<sup>2</sup>.<sup>1</sup> At this memory density, the head of the pin could hold approximately 580 MB, well surpassing the requirement. Feynman would be pleased indeed to see the original challenge realized in a commercial device of today!

This miniaturization has to a large extent been driven by the computer industry. Each generation of computer hardware has performed better than its predecessor, mainly thanks to the ability to scale the size of the basic building block, the transistor. From a size of about  $10 \,\mu\text{m}$  in the 1970s, the gate length of transistors is today down to tens of nanometers, with almost 2 billion transistors packed on each semiconductor die.

There is, however, a fundamental change taking place in the industry today. For half a century, computing performance has been improved mainly by transistor scaling. We are now at a point where layers in the transistors are only a couple of atoms thick. It will soon be impossible to continue scaling the transistor in the

$<sup>^{1}\</sup>mathrm{http://phys.org/news/2012-10-tdk-hard-breakthrough-areal-density.html, accessed Feb 12, 2013.$

straightforward manner that has been possible since the development of the first integrated circuits.

### 1.1 The emergence of nanowire research

The focus has thus shifted toward other ways to improve semiconductor devices. To this end, novel transistor geometries are being investigated, and semiconductor nanowires are promising candidates. As we will see, nanowires also exhibit properties that make them interesting for a wide range of application areas. Nanowires are thin wires with a diameter on the nanometer scale and essentially no limitation lengthwise, although they are commonly of the order of a few micrometers in length. The nanowire research field started in the 1960s [1]. Although not "nanowires" in the strictest sense, *silicon whiskers*, rod-like structures with a diameter and submicrometer range, were grown by Wagner and Ellis using a gold catalyst on silicon substrates. In their paper, the Vapor–Liquid–Solid growth process was proposed, a method still used to grow semiconductor nanowires with a metal catalyst.

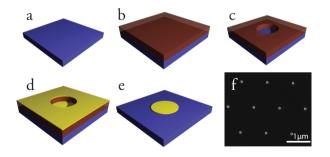

In Vapor–Liquid–Solid growth, a metal catalyst, commonly gold, is placed on the surface of a semiconductor wafer. There are many ways to deposit gold particles on substrates, for example by letting a thin evaporated gold film selforganize into particles [2] or by using size-selected aerosol particles [3]. A common modern technique is shown in Fig. 1.1. An electron beam lithography (EBL) system is used to expose tiny holes in a resist film, and gold is deposited by thermal evaporation under high vacuum conditions (Fig. 1.1a–e). A scanning electron microscope (SEM) image of the resulting pattern of gold particles is shown in Fig. 1.1f.

Figure 1.1: Definition of gold particles with EBL. A semiconductor substrate (a) is covered by a thin resist film (b). An EBL is used to expose small dots in the film (c), and gold is evaporated (d). The sample is submerged in a solvent, which removes the resist and all gold except in the exposed regions (e). SEM image of the final particle pattern (f). Gold particles appear gray on a black background.

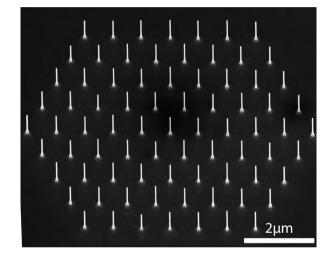

The sample is then loaded into a growth reactor. Nanowires can be grown by many methods, for example chemical beam epitaxy (CBE) [4], metal-organic vapor-phase epitaxy (MOVPE) [5] or molecular beam epitaxy (MBE) [6]. As the sample is heated, and growth material such as trimethylindium and tertiarybutylarsine in the case of InAs epitaxial growth is added to the chamber, the growth material is preferentially collected by the gold droplet. The material then precipitates at the bottom of the droplet, causing a pillar-like structure to grow, with the gold droplet riding on top. The diameter of the nanowire is primarily determined by the size of the gold droplet, and is typically designed to be less than 150 nm. Figure 1.2 shows an SEM image of an array of InAs nanowires standing vertically on a substrate. The nanowires in this example have an average diameter of 40 nm and length of  $1 \,\mu$ m. The nanowires can either be processed as-is or broken off and transferred to a different substrate for further processing.

Figure 1.2: SEM image of an array of InAs nanowires.

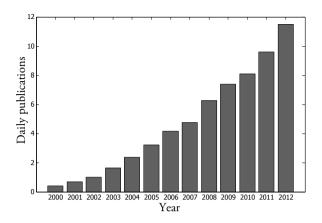

In the years following the discovery by Wagner and Ellis, the materials available for nanowire growth were extended to include GaP [7], Ge [8], GaAs [9] and InAs [10], but progress was relatively slow, and nanowires had still not attracted the attention necessary for accelerated research efforts. In the early to mid 1990s, the nanowire research started to gain momentum, in particular owing to the successful efforts reported by the Hiruma group at Hitachi [11–13] on growth of GaAs and InAs nanowires, and the Lieber group at Harvard developing growth of carbide [14] and oxide [15] nanowires. In 2002, independent reports of heterostructured nanowires from the Samuelson group [4, 16, 17], the Lieber group [18] and the Yang group [19] were published, enabling further exciting experiments. Over the last decade, the research field of semiconductor nanowires has experienced a tremendous expansion. Figure 1.3 shows the number of *daily* journal publications containing the search term *nanowires*.<sup>2</sup> It is evident that the subject of nanowires is a heavily researched one, showing no trace of diminishing growth.

<sup>&</sup>lt;sup>2</sup>Collected using http://www.sciencedirect.com

Figure 1.3: Number of daily journal publications containing the search term nanowires.

### 1.2 Nanowire applications

Why are nanowires interesting to study? They offer many benefits not readily available to bulk materials. This enables applications and optimizations difficult to realize in classical semiconductor systems. Thanks to their small footprint, crystal strain can be relaxed at the periphery of the nanowire [17–20]. This allows growth of non-lattice-matched materials not easily combined in the bulk geometry, such as the InP/InAs [16] and Si/Ge [21] material systems. Combined with the nanometer dimensions attainable using nanowires, this enables studies of fundamental quantum mechanical model systems [16, 22, 23] as well as integration of optically active materials on Si [24]. The development of radial nanowire heterostructures allows growth along crystal directions difficult or expensive to realize in planar epitaxial growth, for example along the nonpolar  $\{1\bar{1}00\}$  m-plane of GaN [25, 26]. Finally, the near-cylindrical symmetry of nanowires lends itself naturally to electric gates that are wrapped around the entire semiconductor, enabling field-effect transistors [27, 28] and tunnel field-effect transistors [29] with the promise of optimized gate control, enhanced switching speed and lowered energy consumption.

Many of these inherent benefits of nanowires have already been translated into exciting devices that enable new physics or potential new commercial applications. Technologies enabling patterning of samples for growth of nanowires in ordered arrays, such as EBL, illustrated in Fig. 1.1, or even more promising, nano-imprint lithography [30], now allow the growth of highly optimized nanowire arrays over large-area substrates. These recent developments open up the possibility for largescale production of nanowires and may enable implementation of nanowires in commercially viable devices.

#### 1.2.1 Nanowire field-effect transistors

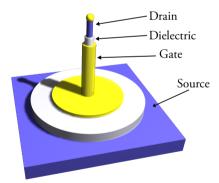

In a field-effect transistor (FET) the gate is used to open or close a channel in the semiconductor between the source and the drain terminals. To gate the device efficiently, the coupling of the gate to the channel needs to be optimized. Nanowires promise optimal gate control thanks to their near-cylindrical symmetry. This is quantitatively described in Section 4.1, but originates from the fact that gating a semiconductor is more efficient if the gate couples to the entire periphery of the transistor channel, as opposed to only acting from one side. This well-known fact has instigated numerous experiments where so-called *wrap-gate* or *gate-all-around* devices have been modeled, fabricated and analyzed.

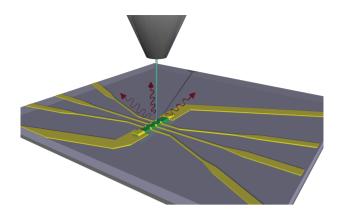

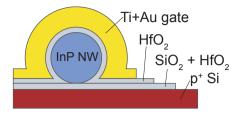

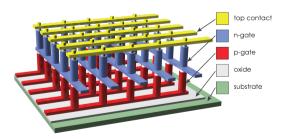

In the wrap-gate design, an electric insulator is deposited onto the semiconducting nanowire, and the structure is then embedded in a gate electrode that wraps around the entire periphery of the nanowire (see Fig. 1.4). One of the first devices of this type was a vertical InAs nanowire transistor comprising multiple nanowires connected in parallel, demonstrated by Bryllert et al. [27]. This incited an intense research effort generating numerous publications. Notable papers describe a refined FET with a 50 nm gate length [31], InAs nanowire FETs integrated on silicon [28], silicon nanowire FETs [32] and high-frequency InAs devices integrated on silicon [33, 34]. Furthermore, complementary metal–oxide–semiconductor (CMOS) circuits have been realized in single nanowires [35, 36].

Figure 1.4: Illustration of the components of a vertical nanowire wrap-gate transistor. The nanowire is insulated by a gate dielectric such as  $HfO_2$  and capped with a conductive gate electrode. Typically, the source and drain are formed by electrical connections to the substrate and the tip of the nanowire.

Traditional metal–oxide–semiconductor field-effect transistors (MOSFETs) have a minimum inverse subtreshold slope of 60 mV/dec at room temperature, causing high off-currents at low drive voltage. This makes them unsuitable for low-power applications. To this end, nanowires have also shown promise for novel transistor designs such as the tunnel FETs demonstrated in silicon [37–40] and InP/GaAs [41] that promise an inverse subthreshold slope far below the 60 mV/dec limit. Other types of low-power transistors such as impact-ionization transistors using multiple gates are also being investigated in nanowire systems [42], reaching an impressive inverse subthreshold slope of 5 mV/dec.

One main driving force behind these experiments is further CMOS transistor scaling, in which it is necessary to solve issues such as high leakage current while maintaining high drive current. The optimized gate geometry is an attractive route, and the fact that Intel has already implemented the trigate transistor structure in their 22 nm node, a transistor geometry in which the gate is partially wrapped around the semiconductor channel, is a clear indication that geometries with optimized gate control are also of interest for commercial applications.

#### 1.2.2 Light-emitting diodes

Conventional light-emitting diodes (LEDs) can now be made with emission wavelengths spanning the entire visible spectrum. High-efficiency LEDs emitting in the blue and green range are primarily made from the InGaN material system, whereas yellow, orange and red LEDs are primarily made from AlGaInP. Red and blue LEDs can be made with high luminous efficiency, whereas improving the efficiency of green LEDs remains challenging. This is sometimes referred to as the green gap. The InGaN material system can in principle cover the entire visible spectrum; however, the luminous efficiency rapidly drops for In compositions higher than 30%. This originates from the lattice mismatch between InN and GaN, together with the polarization fields present along the c-plane, the direction primarily used for InGaN LED growth. The polarization fields separate the electron-hole pairs in the LED quantum wells, decreasing the efficiency, an effect whose severity increases with increasing In content.

GaN nanowires grown in the c-direction, however, have nonpolar m-plane side facets [43]. It is believed that these m-plane facets allow high-efficiency electroluminescence and may enable one of the first commercially viable nanowire LED devices. Many nanowire implementations of LEDs have already been realized, for example cross-nanowire InP LEDs [44, 45], axial InP/InAs LEDs [46], radial GaN LEDs [47] and radial GaP LEDs [48], and multiple companies are working on developing commercially viable GaN LEDs, including the Lund-based GLO and the Grenoble-based HelioDEL.

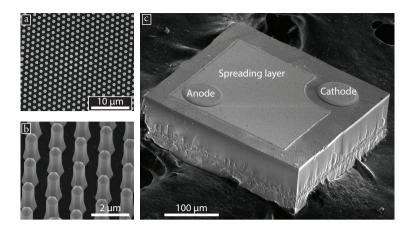

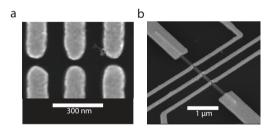

Figure 1.5 shows SEM images of GaN nanowires implemented in nanowire LEDs by the GLO AB company. Nano-imprint lithography is used to produce openings in a  $Si_3N_4$  film, and core-shell n-p junction nanowires with an active quantum well region are grown on 2 in wafers. Figure 1.5a and b show the uniformity and detail of as-grown GaN nanowires. The finished die, shown in Fig. 1.5c, consists of an anode, a cathode and an indium tin oxide transparent current spreading layer.

Figure 1.5: GaN nanowire LED made by GLO AB.  $\boldsymbol{a}$  and  $\boldsymbol{b}$  array of GaN nanowires grown through a nano-imprint-lithography-defined mask on a 2 in wafer.  $\boldsymbol{c}$  Finished LED die showing anode, cathode and indium tin oxide current spreading layer.

The nonpolar m-plane facets of the nanowires grown in the c-direction promise light emission from nonpolar active regions, which alleviates the problems associated with the green gap. Together with strain relaxation offered by nanowires [49], this enables more efficient green, amber and red emitters made from the InGaN material system. Figure 1.6 shows GaN nanowire LEDs made by GLO emitting in the blue, green, amber and red spectrum regions. Another interesting aspect of nanowire emitters is the increased effective active area compared to substrate area. This enables higher luminous flux per unit area of LED die.

These benefits do not, however, come without challenges. The geometry makes nanowire LEDs complicated to process compared to their planar counterparts. Furthermore, careful engineering of the nanowire contacts and quantum wells must take place to ensure a homogeneous injection current density along the nanowire m-plane facets.

Figure 1.6: GaN nanowire LEDs made by GLO AB, emitting in the blue, green, amber and red wavelength regions.

#### 1.2.3 Solar cells

The amount of solar power impinging on the earth corresponds to a couple of thousand times the power consumption of modern society [50]. Harvesting a small portion of this energy is therefore an attractive option, providing a "free" energy source without significant greenhouse gas emission or other environmental impacts. To utilize this enormous energy resource, cheap solutions must be found to produce reliable solar cells of high efficiency. Expensive multijunction solar cells are currently able to convert solar energy to electricity with an efficiency of 37.7% for cells that do not use sunlight concentration and 44% for those with concentration [51]. The record for solar cells produced on cheaper Si substrates is currently 25.0% [51].

One of the main problems of combining high-efficiency III/V solar cells with cheap Si substrates in the planar geometry is lattice mismatch, causing crystal defects that act as recombination centers. Nanowires offer the opportunity to realize these material combinations with much less strict restrictions on lattice constant matching. Over the last few years, nanowire solar cells in various material systems such as GaAs [52] and InP [50, 53, 54] have been implemented. Recently, a new record for nanowire solar cells was set at 13.8% using InP nanowires [55]. In that paper, it was shown that, with only 12% surface coverage of nanowires, the cells delivered 83% of the photocurrent density of corresponding planar solar cells. This remarkable observation originates in the fact that arrays of nanowires allow higher absorption than their planar counterpart. Furthermore, a novel fabrication method using aerotaxy was recently demonstrated [56] that, if it proves possible to implement for solar cell applications, offers cheap mass production of nanowires. Although many challenges remain before the devices are commercially viable, nanowires appear to be an attractive route to highly efficient and cheap solar energy harvesting.

#### **1.3** Challenges in nanowire characterization

It is clear that nanowires have many advantages not easily attainable in conventional bulk devices and promise novel device implementations. One of the most important, if not *the* most important, technological development necessary for fabricating and optimizing devices is the ability to precisely engineer and characterize doping profiles in the material. The ability to control the conductivity, and hence the potential landscape, of both axial and radial nanowire structures is crucial for the realization of most practical devices. The ability to characterize the material properties accurately is essential for device optimization.

The technology to dope semiconductor nanowires both n-type and p-type has been actively researched in the last two decades, and it is now possible to perform in-situ n-type and p-type doping of Si, Ge and essentially all III–V nanowires [57]. However, despite the progress in doping nanowire material, the ability to electrically quantify the carrier density of nanowires remains in the development stage.

The most common method involves fabricating MOSFET devices from the nanowires of interest, and studying their transfer characteristics. By determining the maximum transconductance,  $g_m = \partial I_{sd} / \partial V_g$ , from the source–drain current  $I_{sd}$  and gate voltage  $V_g$  of the transistor, the mobility,  $\mu$ , can be deduced from

$$\mu = g_m \frac{L^2}{V_{sd}C}$$

where L is the channel length,  $V_{sd}$  is the source–drain voltage and C is the gate– channel capacitance. Once the mobility is known, the carrier density n can be determined from the relation  $\sigma = qn\mu$ , where  $\sigma$  is the material conductivity and q is the elementary charge.

This method, however, suffers from a number of limitations. The source and drain contact resistances should be lower than the channel resistance in the linear transconductance regime, and the gate capacitance must be accurately calculated. Owing to the nonmetallic density of states of moderately doped semiconductors [58–61], as well as the nonideal device geometries often used (see Section 4.1), the gate capacitance is difficult to estimate accurately, leading to errors in the mobility and doping calculations. Furthermore, field-effect measurements probe the mobility close to the surface of the semiconductor where surface scattering may have a substantial effect [62]. This is different from Hall measurements in bulk samples, in which the extracted mobility represents bulk carrier scattering. Although the Hall mobility and field-effect mobility can be correlated for different materials [63, 64], this is seldom done, resulting in the calculations yielding a lower bound for the mobility.

### 1.4 Aim of the thesis

This thesis describes the development of processing and characterization methods for nanowires. It specifically covers three aspects:

- Spatially resolved Hall effect measurements on single nanowires.

- Capacitance-voltage measurements on arrays of nanowires.

- Manipulation of the Fermi level in nanowires using wrapped and semiwrapped gates.

In Chapter 2 it is shown how the Hall effect can be used to quantify both carrier density and carrier mobility with spatial resolution in core–shell InP nanowires (Paper I). Hall measurements are traditionally used to characterize 2D epitaxial layers and is an extremely useful method that has never before been used on nanowire systems.

In Chapter 3, capacitance–voltage (C–V) measurements on nanowires are described (Papers II and III). C–V measurements have conventionally been used for the characterization of bulk semiconductors, and this chapter describes how the C–V method was applied to arrays of InAs nanowires for the first time.

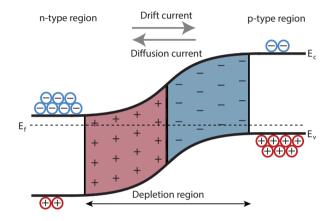

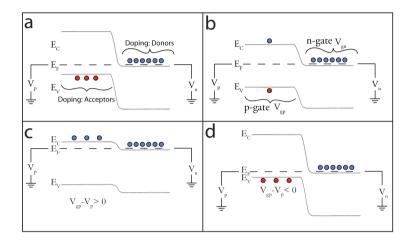

Finally, in Chapter 4, gated nanowire devices are explored in more detail (Papers IV, V and VI). The field-effect method was applied to InP nanowires to measure the carrier mobility, and from the resulting MOSFETs, ambipolar behavior was demonstrated in the nanowires. This enabled the fabrication of a *field-effect diode*, a device in which two gates are used to induce a p-n junction in a nanowire without the need for impurity doping of the active region. A new process is also described that allows a fully wrapped gate to be implemented on a nanowire that is laterally positioned on a substrate.

# Chapter 2 Hall effect measurements

Material characterization and control in nanowires have yet to reach the level of bulk semiconductor materials, despite many years of ever more intense research efforts (see Fig. 1.3). High controllability over growth parameters such as doping incorporation, carrier mobility, material composition and growth rate is essential for fabricating more advanced devices for basic research and moving past the proofof-concept level for applied devices. To attain higher control and better material quality, powerful and routinely utilized characterization techniques are necessary. Unfortunately, the 3D nature of the nanowire geometry has long meant that the use of conventional electrical characterization techniques has been challenging. The ability to measure material properties accurately has therefore struggled to keep up with the rapid expansion of this research field.

Two key methods long used for the characterization of conventional bulk epitaxial layers are C–V spectroscopy and Hall measurements. In this chapter we discuss how Hall measurements are implemented on nanowires (Paper I). The Hall effect enables spatially resolved determination of carrier density and mobility and is a technique that has previously been unavailable to the nanowire community. We then discuss in Chapter 3 how C–V measurements can be implemented on nanowires.

#### 2.1 Classical Hall effect measurements

Hall measurements are conventionally and routinely used to characterize semiconductor epitaxial layers and metal samples. This useful characterization method originates from the fact that a particle of charge q moving at velocity  $\bar{v}$  in an electric field  $\bar{E}$  and a magnetic field  $\bar{B}$  experiences the Lorentz force  $\bar{F}$ ,

$$\bar{F} = q \left( \bar{E} + \bar{v} \times \bar{B} \right)$$

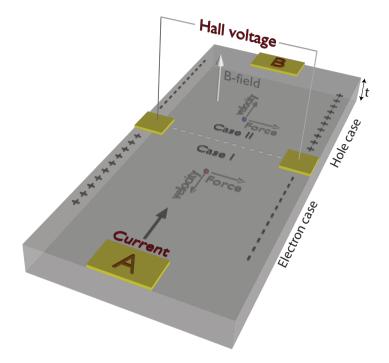

Assume we source a current I through a slab of semiconductor of thickness t as shown in Fig. 2.1.

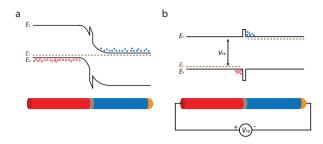

Figure 2.1: Illustration of the Hall principle. A charged particle experiences a force due to an applied magnetic field. The case for negatively charged electrons carrying the current is shown as Case I, and that for positively charged holes as Case II.

A magnetic field is applied perpendicular to the sample plane, and the current I is passed along the sample from terminal A to terminal B. Two electrodes oriented on opposite sides of the sample, on a line perpendicular to the current flow, are used to measure the Hall voltage  $V_H$  across the sample. For an n-type semiconductor of electron concentration n, the current is predominantly carried by electrons. This is illustrated in Case I in Fig. 2.1. Owing to the applied magnetic field, an electron moving from terminal B to terminal A will experience a force perpendicular to the current direction. For macroscopic samples in the nonballistic regime, electrons are curved between each scattering event. This gives rise to an inhomogeneous charge distribution in the sample and an electric field directed perpendicular to the current flow as illustrated in the figure. The resulting Hall voltage  $V_H$  can be derived as

$$V_H = \frac{BI}{qnt} \tag{2.1}$$

where B is the magnitude of the magnetic field. The corresponding case for a p-doped semiconductor, in which holes are dominant charge carriers, is illustrated in Case II. The Hall voltage measured in the case of hole conduction is identical in magnitude but with opposite sign. This is thus a convenient method to determine both the type of charge carrier in the sample and for determining the carrier density

by varying either the magnetic field B or the sourced current I. Once the carrier density is known, the mobility can be calculated from four-point measurements using the Drude conduction model

$$\sigma = q \left( n\mu_n + p\mu_p \right)$$

where p is the hole density and  $\mu_n$  and  $\mu_p$  are the electron and hole mobility, respectively.

#### 2.1.1 Hall measurements for small samples

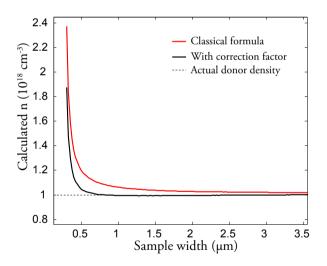

Measurements of the Hall effect in small samples introduce some challenges not present in a macroscopic sample. One of the main challenges arises because the physical dimensions of the Hall voltage-sensing terminals cannot be considered to be infinitesimal compared to the size of the sample. In the derivation of Eqn. (2.1) it is assumed that the distance between the Hall voltage terminals is equal to the width of the sample. We can easily check the validity of this approximation as the width of the sample is gradually decreased while maintaining a constant contact size. Figure 2.2 shows a simulation for a planar slab of semiconductor of thickness 200 nm, contact size  $50 \times 50 \text{ nm}^2$  and electron concentration  $10^{18} \text{ cm}^{-3}$ .

Figure 2.2: Illustration of breakdown of validity of Eqn. (2.1). When the contact size is no longer infinitesimal compared with the sample width, the classical formula returns erroneous results. Taking the finite contact size into account improves the result but is nevertheless inadequate for the regime of sample width below  $\sim 500$  nm.

The width of the sample is gradually changed, and the carrier concentration, calculated using the classical formula in Eqn. (2.1) from the simulated Hall voltage, is plotted on the vertical axis (red curve). For a sample width larger than a few micrometers, we see that Eqn. (2.1) approaches the correct result. In the regime

below  $1\,\mu\text{m}$ , however, we obtain erroneous results with an overestimated carrier density due to the finite size of the terminals.

However, Eqn. (2.1) can easily be partially mended by taking into account the finite contact size. The resulting equation modifies 2.1 by introducing a correction factor  $w_c/w$ , where  $w_c$  is the distance between the points at which the Hall terminals probe the potential and w is the width of the sample

$$V_H^* = \frac{BI}{qnt} \cdot \frac{w_c}{w} \tag{2.2}$$

From Fig. 2.2, we find that the modified expression (black curve) correctly extracts the carrier density down to approximately 500 nm sample width. However, it still does not adequately describe a nanowire system, in which the dimensions are typically smaller by a factor of two. As described in Section 2.2, simulation tools can be used to more accurately calculate the carrier density from the experimental data.

#### 2.2 Hall effect in nanowires

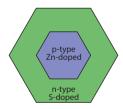

Nanowires offer additional challenges for performing Hall measurements. Not only are we measuring a small sample, but we also need to take into account the complex nanowire geometry. In Paper I, Hall measurements on nanowires are demonstrated. For this study, InP nanowires were grown by metal-organic vapor-phase epitaxy. The growth takes place by first growing a p-type core on a nano-imprint lithography patterned substrate, using Zn as dopant. The sample is then taken out of the reactor, the gold catalyst is removed by KI/I<sub>2</sub> etching and an n-type shell is grown radially on top of the core using S as dopant material (see Fig. 2.3).

Figure 2.3: Illustration of the cross-section of metal-organic vapor-phase-grown InP nanowires used for the Hall measurements.

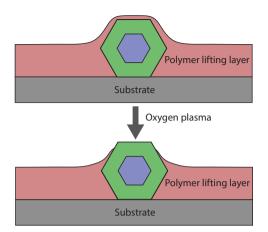

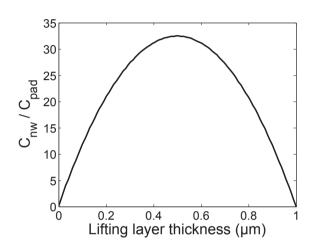

The nanowires are then transferred to an insulated silicon substrate, and metal connections are defined with EBL. The relatively large diameter of approximately 200–300 nm of these radial structures makes it challenging to directly deposit electrical contacts, owing to the vertices of the hexagonal nanowire cross-section causing discontinuities in the metal film. A novel lifting layer was therefore designed (see Fig. 2.4).

Figure 2.4: Definition of the self-aligned polymer lifting layer.

This lifting layer is defined by spinning a diluted photoresist thin film onto the sample. The thin film automatically aligns itself to the highest feature of the nanowire. By a short oxygen plasma process, the top facet of the nanowire is exposed, while the rest of the nanowire remains embedded in the polymer. This process, similar in concept to a previously published method using spin-on glass [65], allows contacts to be defined by EBL with high resolution and is one of the key enablers of the nanowire Hall measurements.

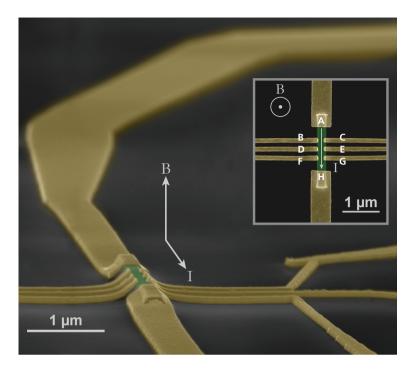

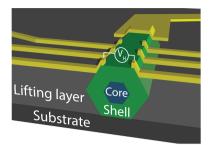

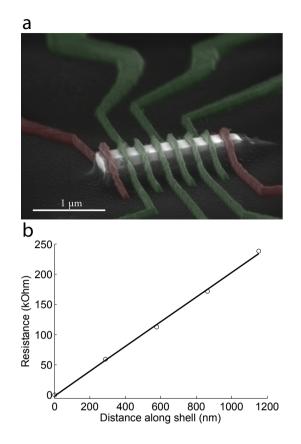

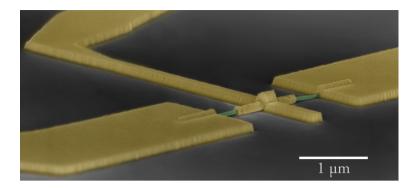

After the polymer layer has been deposited, the Hall devices are defined by a single EBL step combined with metal evaporation and lift-off. The resulting device is shown in Fig. 2.5. In this system, the current is sourced through the ntype shell of the nanowire using terminals AH (inset), and the pairwise terminals BC, DE and FG are used to measure the Hall voltage as a magnetic field is applied perpendicular to the substrate plane. Figure 2.6 shows an illustration of the crosssection of the device.

It is not immediately obvious that Eqn. (2.2) accurately describes the complex geometry of a nanowire system. In the core–shell geometry of the radially grown nanowire device, the layer probed by the Hall measurements forms a hexagonal thin film in contrast to the planar films traditionally characterized with the Hall method. Furthermore, the nanowire p–n junction gives rise to a depletion region that will affect the effective electrical thickness of the shell.

Figure 2.5: The device used to measure Hall voltage in a core-shell InP nanowire. The inset shows details of the terminal layout.

We can rewrite Eqn. (2.2) in a more general form that is also applicable to the nanowire geometry:

$$V_H^* = \frac{Bj}{qn} w_c \tag{2.3}$$

where j is the current density in the shell of the nanowire. It is fairly clear from the previous sections that an analytical approach to Hall effect measurements in nanowires has its inherent shortcomings. With the exception of cases in which the current is carried in a very thin layer close to the surface, such as the surface accumulation layer in InAs [66] where the resulting Hall voltage can be calculated from a resistor network model [67], the Hall effect in nanowires is nontrivial to calculate. Not only are nanowires small samples, in which the assumption of infinitesimal contact points compared to the sample size is no longer valid, but they also have a nontrivial geometry that further complicates the analysis. It is thus helpful to employ simulation methods to investigate how Hall effect measurements in a nanowire should be interpreted.

Figure 2.6: Details of the design of the Hall device.

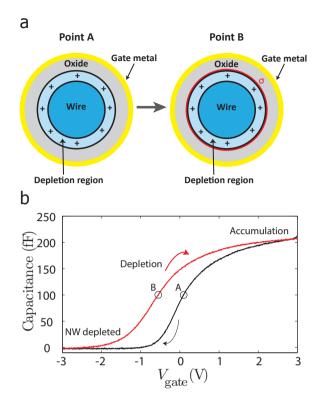

#### 2.2.1 2D Poisson simulations

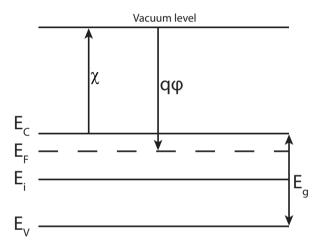

Owing to the radial p-n junction present in this system, it is important to carefully consider how the properties of this junction may affect the conduction through the shell. The main contribution from the p-n junction is a decrease in the effective electrically active area due to the depletion region extending into the nanowire shell. In a conventional planar p-n junction, the Poisson equation can easily be solved analytically within the depletion approximation to find the depletion width. This has the well-known result that the impurity doping concentration of the lowdoped side determines the extension of the depletion region,  $W_d$ , according to

$$W_d = \sqrt{\frac{2\varepsilon}{q} \left(\frac{N_A + N_D}{N_A \cdot N_D}\right) (V_{bi} - V_a)} \approx \underbrace{\sqrt{\frac{2\varepsilon}{q} \frac{1}{N_D} (V_{bi} - V_a)}}_{p^+ - n} \approx \underbrace{\sqrt{\frac{2\varepsilon}{q} \frac{1}{N_A} (V_{bi} - V_a)}}_{p - n^+}$$

(2.4)

for the cases of a p<sup>+</sup>-n ( $N_A >> N_D$ ) and a p-n<sup>+</sup> ( $N_D >> N_A$ ) junction. In Eqn. (2.4)  $N_A$  is the acceptor concentration on the p-side,  $N_D$  is the donor concentration on the n-side,  $\varepsilon$  is the material permittivity,  $V_{\rm bi}$  is the built-in voltage of the junction and  $V_a$  is the voltage applied to the p-side.

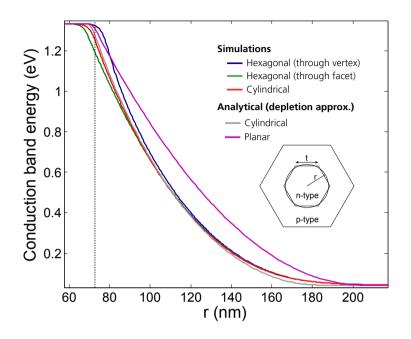

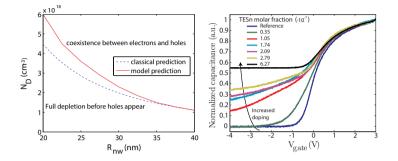

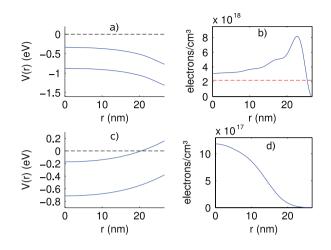

We now compare the validity of different models to evaluate the effect from the junction in the case of a hexagonal  $p^+$ -n core-shell nanowire. We can simplify the discussion by approximating the hexagonal cross-section of a nanowire as a cylinder. Finding the solution for a cylindrically symmetric p-n junction is not as straightforward as the planar case, but it is possible with a combination of analytical and numerical approaches (see Appendix A.1 for a derivation). To illustrate the effect of the junction, Fig. 2.7 shows a comparison between simulated and analytical solutions for the conduction band energy for hexagonal, cylindrical and planar one-sided p<sup>+</sup>-n junctions with core p-type doping  $5 \cdot 10^{18}$  cm<sup>-3</sup> and shell n-type doping  $10^{17}$  cm<sup>-3</sup>, calculated for an InP nanowire system. The simulations were done in the COMSOL Multiphysics environment.<sup>1</sup> Details on the simulation framework can be found in Appendix A.2. The potential for the hexagonal p-n junction has been evaluated along two paths: through the hexagon vertex and

<sup>&</sup>lt;sup>1</sup>http://www.comsol.com

through the facet. For the cylindrical case, a radius  $r_j$  inscribed as shown in the inset with equivalent area as the core hexagon,  $\pi r_j^2 = \frac{3\sqrt{3}}{2}t^2$ , where t is the side length of the hexagon, is used as the metallurgical position of the junction.

Figure 2.7: Solutions for the conduction band in InP hexagonal, cylindrically symmetric and planar p-n junctions. The Fermi level is set at 0 eV and the side length of the hexagonal core is t = 80 nm. The dotted line marks the position of the metallurgical  $p^+-n$  junction for the cylindrically symmetric case.

From Fig. 2.7, a number of conclusions can be drawn. As expected, the potentials evaluated through the vertex and the facet of the hexagonal p-n junction differ owing to the asymmetry of the geometry. The simulated potential for the cylindrical p-n junction acts as an average model for the hexagonal geometry, becoming approximately identical to both hexagon potentials at large radii. Furthermore, the analytical solution to the cylindrical p-n junction agrees reasonably well with the simulated cylindrical potential, except at the edges of the depletion region. We can thus conclude that the cylindrical approximation may be adequate for estimates of the depletion width for one-sided p-n junctions, but that the differences between the hexagonal case must be kept in mind. Finally, we note that the depletion approximation for a planar p-n junction has significant error throughout the depletion region and cannot satisfactorily be used to approximate the cylindrical p-n junction.

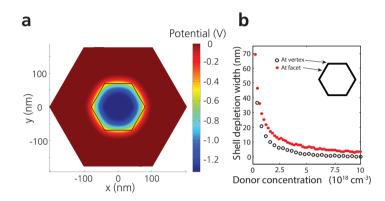

We now return to the nanowire p–n junction discussed in Section 2.2. Figure 2.8 shows a simulation of the potential for a matching core acceptor and shell donor concentration of  $1 \cdot 10^{18} \,\mathrm{cm}^{-3}$ . The solid hexagon in Fig. 2.8a shows the

position of the metallurgical junction. We find that the depletion region extends into the shell of the InP core–shell nanowire and may thus affect the analysis of the experimental Hall data. However, a closer look at the depletion width dependence on shell donor concentration reveals that the effect on electrical shell thickness is less than 5% for a shell doping higher than  $1 \cdot 10^{18} \text{ cm}^{-3}$ . For low donor concentration, this effect must therefore be taken into account, whereas it is negligible for higher donor concentrations.

Figure 2.8: **a** Simulation of the potential distribution in a radially grown InP nanowire p-n junction intended for Hall effect measurements. **b** The extension of the depletion region in the shell is calculated as a function of shell donor concentration.

#### 2.2.2 3D current-continuity modeling

Once the effective electrical thickness of the nanowire shell is known, the hexagonal shell is approximated as a conductive medium. As a current is fed through the length of the shell, we need to solve for the current distribution  $\bar{J}(\bar{r})$  and potential  $V(\bar{r})$  in the medium under the influence of a magnetic field. Here,  $\bar{J}$  and V are related by Ohm's law

$$\bar{J} = -\bar{\sigma} \cdot \nabla V$$

where  $\bar{\sigma}$  is the conductivity tensor

$$\bar{\sigma} = \sigma_0 \left( \begin{array}{ccc} \frac{1}{1+(\omega\tau)^2} & -\frac{\omega\tau}{1+(\omega\tau)^2} & 0\\ \frac{\omega\tau}{1+(\omega\tau)^2} & \frac{1}{1+(\omega\tau)^2} & 0\\ 0 & 0 & 1 \end{array} \right)$$

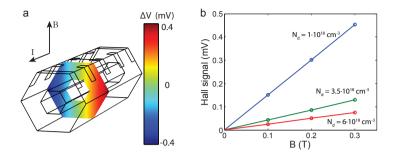

which takes into account the magnetic field  $\overline{B} = (0, 0, B)$  through the cyclotron radius  $\omega = qB/m$ , where *m* is the mass of the particle. See Appendix A.3 for a derivation and a discussion of the conductivity tensor. Figure 2.9a shows the design for the COMSOL simulations. By adjusting the dimensions of the hexagonal shell and the Hall terminals to match the experimental conditions, the Hall voltage can be simulated as a function of current and carrier density.

Figure 2.9: 3D current-continuity simulations. **a** The dimensions of the structure are chosen to correspond to the dimensions in the processed sample. An example of the simulated potential distribution is shown in the cross-section of the nanowire. **b** Examples of simulations for various doping densities.

Figure 2.9b shows Hall voltage simulations for three carrier densities of the InP nanowire shell. This data can then be used to fit the experimental Hall data.

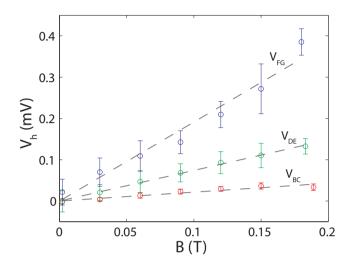

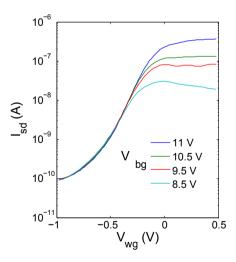

#### 2.2.3 Experimental nanowire Hall characteristics

Figure 2.10 shows experimental Hall data for the device design demonstrated in Fig. 2.5. The three datasets correspond to measurements between the different terminal pairs BC, DE and FG. Running the simulations described in the previous sections yields carrier densities of  $5.6 \cdot 10^{18} \text{ cm}^{-3}$ ,  $1.7 \cdot 10^{18} \text{ cm}^{-3}$  and  $7.5 \cdot 10^{17} \text{ cm}^{-3}$  at the three different positions, respectively. These results can be compared with the carrier densities obtained by using the analytical approximation in Eqn. (2.3), which yields  $3.3 \cdot 10^{18} \text{ cm}^{-3}$ ,  $9.9 \cdot 10^{17} \text{ cm}^{-3}$  and  $4.5 \cdot 10^{17} \text{ cm}^{-3}$  from the same data. The analytical approach does yield reasonable, although slightly underestimated, values. These results indicate that the shell exhibits a doping gradient along the axis of the nanowire. This is somewhat surprising, but one explanation may be local height variations in the effective V/III ratio during growth. This effect is known in GaAs and has been shown in previous studies [68].

One way to verify the Hall measurements is to switch the current direction and redo the Hall measurements. However, the devices are highly rectifying, making this type of measurement challenging. This rectification is believed to arise from the contact resistances at terminals A and H. The direction of rectification is consistent with the nanowire end closest to terminals FG being rectifying and of high resistance, indicating a lower doping concentration in this region. This is thus consistent with the experimental Hall data. Furthermore, four-point conductivity measurements along nanowires grown on the same substrate indicates similar behavior in material conductivity, providing further evidence that a doping gradient does exist in the nanowire shell. It has been predicted that engineering of the doping concentration along the nanowire axis must be performed to optimize nanowire devices such as LEDs [69]. It is therefore of interest to study, and to control, this behavior and utilize it to produce optimally performing nanowire devices.

Figure 2.10: Experimental data from Hall measurement on a single-nanowire device.

One of the main benefits of the platform used to perform Hall measurements is the ability to employ optical characterization tools on the same set of samples. Additional measurements provide supplementary information on the optical properties of the nanowires. One of these tools is cathodoluminescence (CL).

In CL measurements, a beam of electrons from an SEM is used to excite the semiconductor material. The photons emitted from the semiconductor are then collected and analyzed. Thanks to the ability to focus the electron beam onto a small area, this method allows position-dependent optical measurements. CL measurements have previously been used to study, for example, how the seed particle preparation method affects the optical properties of GaAs nanowires [70] and how various axial and radial heterostructures affect carrier diffusion in GaAs and AlGaAs nanowires [71], as well as to study quantum dot structures in nanowires using CL combined with transmission electron microscopy [72].

In Paper I, CL was used to further study the carrier density gradient discovered using the Hall measurements. The setup used to perform the measurements is illustrated in Fig. 2.11. It was found that the peak emission wavelength shifted as a function of position on the nanowire. By correlating this shift with a theoretical model [73], the conclusion that a doping gradient was present in the nanowire shell was further corroborated.

Figure 2.11: Illustration of the setup used for cathodoluminescence measurements.

#### 2.2.4 Limits for nanowire Hall measurements

There are essentially two aspects that govern the range of applicability of the nanowire Hall measurements: the range of nanowire diameters that can be incorporated into Hall devices, and the magnitude of the Hall voltage. The main concern of Hall device fabrication for small diameters is the procedure of aligning the terminals to the nanowire. As shown in Fig. 2.12, using the current fabrication procedure, it is possible to produce Hall terminals with a separation of less than 30 nm and to align the terminals to nanowires of diameter 80 nm. However, to apply the structure to 80 nm or smaller nanowires, the process must be further optimized to attain a satisfactory yield. This can be achieved, for example, with optimized alignment markers [74].

Figure 2.12: SEM images showing the limitations of the Hall measurements. **a** Hall terminals of spacing  $\sim 30$  nm. **b** These closely spaced terminals can be aligned to nanowires of 80 nm diameter.

Using the relation  $j = qn\mu V_l/l$ , where  $V_l$  is the longitudinal voltage necessary to reach a given current level, and l is the length of the sample, we can rewrite Eqn. (2.3) as

$$\frac{dV_h}{dB} = \frac{\mu V_l w_c}{l}$$

to briefly discuss the limitations of the Hall measurements. In this somewhat naïve model, the Hall signal  $dV_h/dB$  is proportional to both the carrier mobility  $\mu$  and the applied longitudinal voltage  $V_l$ . The mobility depends on multiple factors, but the doping incorporation has greatest influence, with mobility decreasing as doping incorporation increases [75]. Thus, increasing the doping concentration increases the current density for a given applied longitudinal voltage, but the Hall signal will still decrease owing to the decrease in mobility. The second factor,  $V_l$ , does not take into account the contact resistivity. For low doping concentrations, the contact resistivity will increase and eventually prevent Hall measurements from being performed. We thus expect a range of carrier densities to be measurable using the Hall technique, but further studies are necessary to determine the exact range of application of the method.

#### 2.3 Other single-nanowire characterization tools

As we have seen, using the Hall effect to characterize nanowires provides useful information on doping incorporation and carrier density. There are, however, other related single-nanowire electrical characterization tools that have been or are being developed. In this section we take a brief look at two of these emerging technologies.

#### 2.3.1 Single-nanowire LEDs

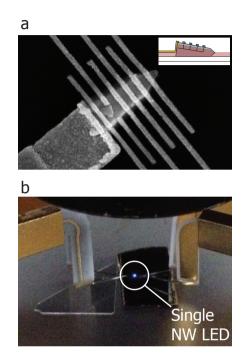

As mentioned in Chapter 1, intense efforts are being invested in developing nanowire LEDs. For most low-power commercial applications, with LEDs in the mW range, each LED die must contain thousands of nanowires connected in parallel. However, for research and development purposes it is of interest to study single nanowires intended for LED integration. This enables studies of inhomogeneous light emission as well as emission properties that are not averaged over the thousands of nanowires in the die implementation.

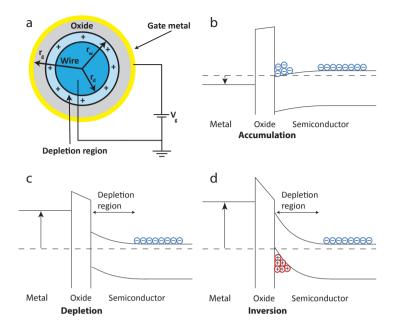

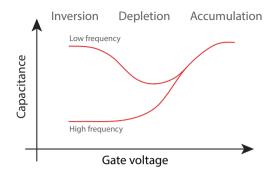

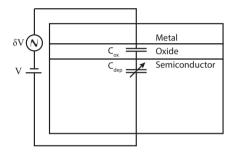

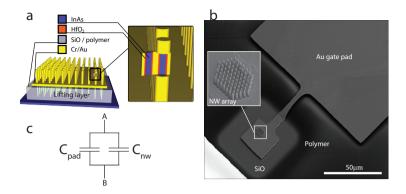

The example presented in this section is based on GaN/InGaN nanowires and performed in collaboration with GLO AB. The InGaN material system allows emission primarily in the blue-green wavelength range and is expected to be one of the first material systems implemented in a commercial nanowire LED. Similar to the InP nanowires presented earlier in this chapter, the GaN nanowires are core–shell systems. They differ, however, in polarity, in which the core is grown n-type and the shell is grown p-type. The active LED layer is sandwiched between the n-type core and the p-type shell.