### UNIVERSIDAD DE NAVARRA ESCUELA SUPERIOR DE INGENIEROS SAN SEBASTIÁN

### Design of Efficient Viterbi Decoders for Communication Transceivers: IEEE 802.11a case study

#### DISSERTATION

submitted for the Degree of Doctor of Philosophy by  ${\bf ARITZ\ ALONSO\ DOMINGO}$

under the supervision of

Andoni Irizar Picón and Ainhoa Cortés Vidal

Donostia-San Sebastián, July 2016

What we call the beginning is often the end. And to make an end is to make a beginning.

The end is where we start from.

T.S.Elliot

他會走回早已消逝的歲月 那塊楨著灰塵的彼璃, 如果他能衝破 他一直在懷念著過去的一切. 看得到,抓不著. 積著茯塵的玻璃 彷佛隔著一塊 那些消逝了的歲月

## Acknowledgement

Decía Constantino Cavafis en su poema Ítaca que cada persona debía aspirar a que su viaje fuese largo y fecundo. En mi caso, concluir esta tesis ha sido un largo camino que he recorrido en compañía de gente que ha dejado una fuerte impronta en mí. Por medio de estas primeras líneas me gustaría expresar mi agradecimiento a todas ellas.

En primer lugar quiero dar las gracias a mis padres, por haber recorrido conmigo este camino día a día, en los momentos buenos y los no tan buenos. Por haberse sentido ilusionados ante lo que hacía y ayudarme a levantarme cada vez que tropezaba. Por haberme dado la oportunidad de llegar hasta aquí y el esfuerzo que les ha supuesto. En definitiva, por ayudarme a ser quien soy hoy. Gracias.

A mis familiares, a los que están y estuvieron, en especial a mis tíos Eugenio y Rosa y a mi primo Pablo, por haberme motivado a seguir adelante y las muestras de cariño que me han dado durante todos estos años.

A Maite y Juan, por el interés y apoyo desinteresado que me han demostrado.

A Aurelia, porque, no importa la distancia, haber sido una amiga desde que tengo uso de memoria.

Quiero agradecer también a los compañeros con los que he coincidido durante estos años en Tecnun/CEIT en el desarrollo de esta tesis. A los miembros del Área de Comunicaciones y Tratamiento Digital de la Señal, Igone, Fanfi, Luis, Koldo, Ramón, Esti, Naiara, Borja y Pilar, quiero agradecerles lo mucho que he aprendido junto a ellos y la oportunidad que me han brindado para crecer tanto personal como profesionalmente. A Markos, por estar siempre dispuesto a echar una mano o discutir nuestros gustos ci-

nematográficos. A las chicas del laboratorio, Ainara, Ainhoa, Leti y Marta, por haber sido las mejores compañeras que he podido tener.

Agradezco también las horas que he pasado en compañía del grupo del café, a Aitor, Ane Miren, Borja, David, Gurutz, Jon y Lexuri, por haber hecho de estos años una travesía mucho más amena. Me llevo de vosotros los recuerdos más bonitos de estos años. En especial quiero agradecer a Iker, quien me ha demostrado ser un auténtico amigo, y estar siempre dispuesto a ayudarme.

A mis nuevos compañeros de Farsens, en especial a Dani e Ibon, por la ayuda que me han brindado para terminar esta tesis y el interés que han demostrado en ella.

A Ainhoa Cortés quiero agradecerle el esfuerzo y dedicación que me ha dedicado en estos últimos meses de redacción y por haber arrojado luz ante el recurrente temor a enfrentarse al folio en blanco.

Y por último quiero dar mi más sincero agradecimiento a Andoni Irizar, quien, literalmente, me ha acompañado desde el primer día en que pisé la Universidad hasta el momento en que defienda este proyecto de tesis que tienes entre manos. Él es en gran medida el responsable de que en primer lugar llegase a ser ingeniero y, posteriormente, tuviese la oportunidad de realizar el doctorado. Gracias.

## Summary

Forward error correcting techniques have become fundamental tools to obtain robust and reliable communication networks. In this reward, convolutional coders belong to a family of codes used in applications such as deep space communications, LTE, GSM, UWB and WLAN. The Viterbi algorithm is a maximum likelihood decoder for convolutional codes. It operates recursively and in each iteration it discards the less probable messages that can have been transmitted. It is estimated that the Viterbi decoder is the most complex entity of the receiver chain of a multicarrier transceiver.

In this research work the architecture of a flexible and parameterizable Viterbi decoder is presented. This flexibility allows us to quickly modify our architecture so that it decodes any given convolutional code. This way we can easily compare our implementation with other alternatives found in the literature. The decoder description does not make use of external or proprietary IPs, so the decoder can be easily ported to any FPGA manufacturer or ASIC technology.

The Viterbi decoder is one of the most important building blocks of the receiver chain of a transceiver, and its performance is a clear indicator of the Bit Error Rate (BER) or Packet Error Rate (PER) we can expect from the system. The parametrization of our decoder implementation allows us to make trade offs between the complexity, area resource utilization, achievable clock speed and decoding capacity of the transceiver. However, making such a parametrical analysis, specially when the entire transceiver architecture is being analyzed under different channel configurations, is a time consuming task. In order to overcome this limitation, in this research work a fast Hardware in the Loop (HiL) evaluation platform has been designed. This platform allows us to quickly compare different decoder configurations and evaluate the performance of the transceiver architecture

in which they are embedded. The HiL platform has proven to significantly reduce the simulation time of other alternatives such as RTL simulators.

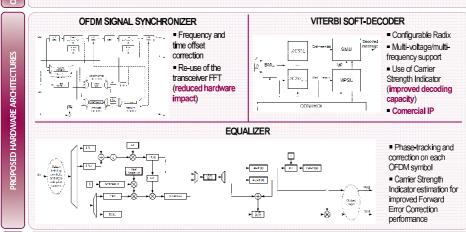

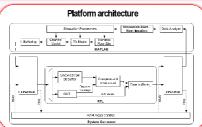

The case study of the parametrical analysis has been WLAN 802.11a. In this research work the sources of a WLAN 802.11a compliant transceiver have been obtained. The transceiver architecture is functional up to the MAC layer of the standard, and it includes complex components such as a time and offset synchronizer and equalizer and phase offset tracker. Also, during this research work a simple hardware oriented demapping algorithm has been proposed.

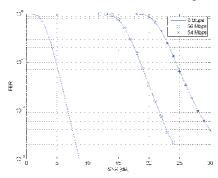

By means of the HiL platform, the Viterbi decoder architecture has been optimized in terms of area resource utilization and its PER performance curves have been obtained for different transmission modes supported by the WLAN standard.

## Contents

| A  | cknov | wledgement                                     | iii                    |

|----|-------|------------------------------------------------|------------------------|

| Su | ımma  | ary                                            | $\mathbf{v}$           |

| Co | onter | nts                                            | vii                    |

| Li | st of | Figures                                        | хi                     |

| Li | st of | Tables                                         | $\mathbf{x}\mathbf{v}$ |

| Li | st of | Abbreviations                                  | кiх                    |

| 1  | Intr  | roduction                                      | 1                      |

|    | 1.1   | Introduction                                   | 1                      |

|    | 1.2   | Outline of the research work                   | 3                      |

| 2  | Stat  | te of the art                                  | 5                      |

|    | 2.1   | Introduction                                   | 5                      |

|    | 2.2   | Viterbi decoder                                | 6                      |

|    |       | 2.2.1 Convolutional codes                      | 6                      |

|    |       | 2.2.1.1 Parallelization of convolutional codes | 12                     |

|    |       | 2.2.2 Viterbi algorithm                        | 14                     |

vii

viii Contents

|   |     |         | 2.2.2.1     | Adaptiv    | re Viterbi Algorithm                       | 26 |

|---|-----|---------|-------------|------------|--------------------------------------------|----|

|   |     | 2.2.3   | Viterbi o   | decoder b  | ouilding blocks                            | 26 |

|   |     |         | 2.2.3.1     | Branch     | Metric Unit                                | 27 |

|   |     |         | 2           | .2.3.1.1   | Hard decoder                               | 29 |

|   |     |         | 2           | .2.3.1.2   | Soft decoder                               | 30 |

|   |     |         | 2.          | .2.3.1.3   | Carrier Strength Indicator aware decoders  | 31 |

|   |     |         | 2.2.3.2     | Add-Co     | mpare-Select Unit                          | 32 |

|   |     |         | 2.2.3.3     | Survivo    | r Path Unit                                | 34 |

|   |     |         | 2           | .2.3.3.1   | Register exchange implementation           | 36 |

|   |     |         | 2.          | .2.3.3.2   | Traceback implementation                   | 38 |

|   |     | 2.2.4   | Viterbi o   | decoder i  | mplementations                             | 41 |

|   |     |         | 2.2.4.1     | Area eff   | icient Viterbi decoders                    | 41 |

|   |     |         | 2.2.4.2     | Data th    | roughput enhanced Viterbi decoders         | 45 |

|   |     |         | 2.2.4.3     | Latency    | optimized Viterbi decoders                 | 50 |

|   |     |         | 2.2.4.4     | Reconfig   | gurable Viterbi decoders                   | 52 |

|   | 2.3 | Hardw   | vare-in-the | e-Loop si  | mulations                                  | 57 |

|   |     | 2.3.1   | Introduc    | ction      |                                            | 57 |

|   |     | 2.3.2   | HiL sim     | ulation cl | naracteristics                             | 57 |

|   |     | 2.3.3   | HiL sim     | ulation us | se cases                                   | 59 |

|   |     |         | 2.3.3.1     |            | ry of the Hardware-in-the-Loop plate cases | 63 |

|   | 2.4 | Conclu  | uding Rer   | narks      |                                            | 65 |

| 3 | Obj | ectives | S           |            |                                            | 67 |

|   | 3.1 | Introd  | luction     |            |                                            | 67 |

|   | 3.2 | Figure  | es of merit | t          |                                            | 68 |

|   |     | 3.2.1   | PER         |            |                                            | 68 |

|   |     |         |             |            |                                            |    |

Contents ix

|   |      | 3.2.2 Metric $\Phi$                        | 69  |

|---|------|--------------------------------------------|-----|

|   | 3.3  | Objectives                                 | 70  |

|   | 3.4  | Scope of this work                         | 71  |

| 4 | Vite | erbi decoder architecture                  | 73  |

|   | 4.1  | Introduction                               | 73  |

|   | 4.2  | Top level Viterbi decoder entity           | 74  |

|   | 4.3  | Viterbi decoder components                 | 79  |

|   |      | 4.3.1 Branch Metric Unit (BMU)             | 79  |

|   |      | 4.3.2 Add-Compare-Select Unit (ACSU)       | 84  |

|   |      | 4.3.3 Survivor Path Unit (SPU)             | 91  |

|   |      | 4.3.3.1 Minimum Path Unit                  | 96  |

|   |      | 4.3.3.2 SPU core                           | 100 |

|   |      | 4.3.3.2.1 Register Exchange implementation | 102 |

|   |      | 4.3.3.2.2 Traceback implementation         | 103 |

|   | 4.4  | Concluding remarks                         | 109 |

| 5 | Har  | rdware-in-the-Loop simulations             | 111 |

|   | 5.1  | Introduction                               | 112 |

|   | 5.2  | WLAN 802.11a transceiver                   | 112 |

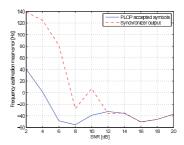

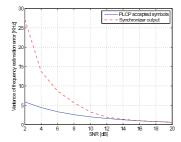

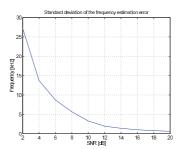

|   |      | 5.2.1 Synchronizer                         | 116 |

|   |      | 5.2.2 Demapper                             | 117 |

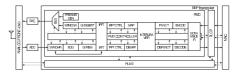

|   | 5.3  | Hardware-in-the-Loop simulator             | 124 |

|   | 5.4  | Parametrical study                         | 129 |

|   | 5.5  | Results                                    | 135 |

|   | 5.6  | Concluding remarks                         | 139 |

| 6 | Res  | m cults                                    | 141 |

| X | Co | ontents |

|---|----|---------|

|   |    |         |

|              | 6.1   | Introduction                            | 141 |

|--------------|-------|-----------------------------------------|-----|

|              | 6.2   | Viterbi decoder implementation results  | 141 |

|              | 6.3   | Concluding remarks                      | 157 |

|              |       |                                         |     |

| 7            | Con   | clusions and areas for further research | 159 |

|              | 7.1   | Conclusions                             | 159 |

|              | 7.2   | Areas for further research              | 164 |

| Re           | efere | nces                                    | 167 |

| $\mathbf{A}$ | Pub   | dications                               | 181 |

|              | A.1   | International Conference papers         | 183 |

|              | A.2   | National Conference papers              | 223 |

# List of Figures

| Cł | apte      | er 1                                                           | 1  |  |  |  |

|----|-----------|----------------------------------------------------------------|----|--|--|--|

| Cŀ | Chapter 2 |                                                                |    |  |  |  |

|    | 2.1       | Simplified block diagram of a communication system             | 6  |  |  |  |

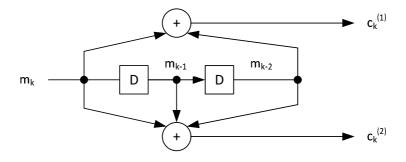

|    | 2.2       | Example convolutional encoder with R=1/2                       | 8  |  |  |  |

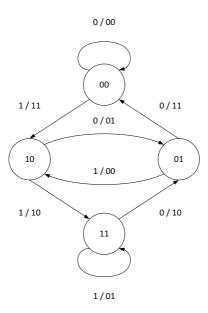

|    | 2.3       | State diagram                                                  | 10 |  |  |  |

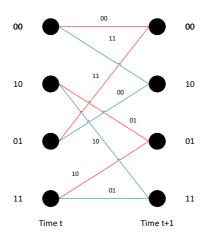

|    | 2.4       | One-state Trellis                                              | 11 |  |  |  |

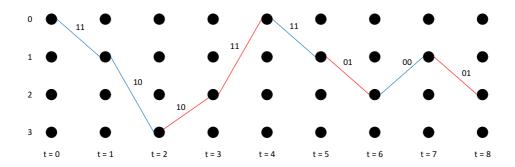

|    | 2.5       | Example path in the Trellis diagram                            | 12 |  |  |  |

|    | 2.6       | Example convolutional encoder with parallelization index $p=2$ | 13 |  |  |  |

|    | 2.7       | Parallel Trellis diagram                                       | 14 |  |  |  |

|    | 2.8       | Path extension at time instant $t = 1 \dots \dots \dots$       | 18 |  |  |  |

|    | 2.9       | Path extension at time instant $t=2$                           | 18 |  |  |  |

|    | 2.10      | Path extension at time instant $t=3$                           | 19 |  |  |  |

|    | 2.11      | Survivor path selection at time instant $t=3$                  | 19 |  |  |  |

|    | 2.12      | Path extension at time instant $t = 4$                         | 20 |  |  |  |

|    | 2.13      | Survivor path selection at time instant $t=4$                  | 20 |  |  |  |

|    | 2.14      | Path extension at time instant $t = 5$                         | 21 |  |  |  |

|    | 2.15      | Survivor path selection at time instant $t=5$                  | 21 |  |  |  |

|    | 2.16      | Path extension at time instant $t = 6 \dots \dots \dots$       | 22 |  |  |  |

xii List of Figures

| 2.17   | Survivor path selection at time instant $t=6$                                                 | 22 |

|--------|-----------------------------------------------------------------------------------------------|----|

| 2.18   | Path extension at time instant $t = 7$                                                        | 23 |

| 2.19   | Survivor path selection at time instant $t=7$                                                 | 23 |

| 2.20   | Path extension at time instant $t = 8$                                                        | 24 |

| 2.21   | Survivor path selection at time instant $t=8$                                                 | 24 |

| 2.22   | Survivor path with minimum accumulated metric of the decode process                           | 25 |

| 2.23   | Decoded message ${\bf r}$                                                                     | 25 |

| 2.24   | Simplified block diagram of a Viterbi decoder                                                 | 27 |

| 2.25   | Block diagram of an OFDM transceiver                                                          | 28 |

| 2.26   | Block diagram of the Branch Metric Unit (BMU)                                                 | 29 |

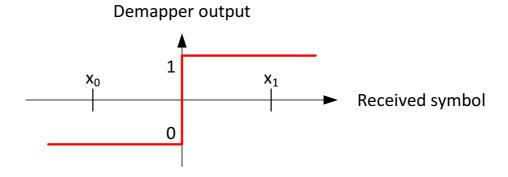

| 2.27   | Demap function of a hard decoded bits                                                         | 30 |

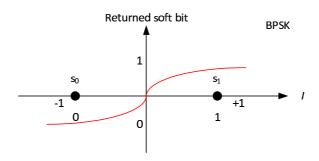

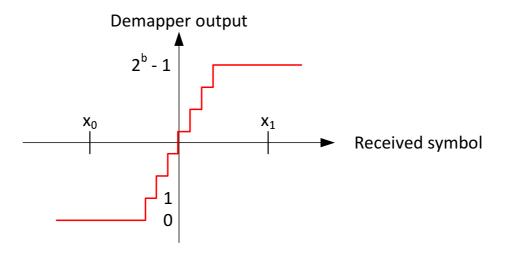

| 2.28   | Demap function of a soft decoded bits                                                         | 31 |

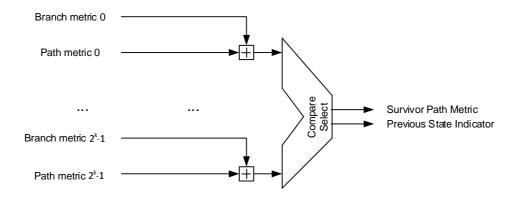

| 2.29   | ACS unit block diagram                                                                        | 33 |

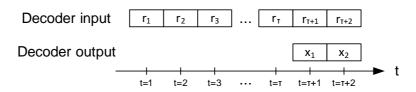

| 2.30   | Viterbi decoder latency                                                                       | 35 |

| 2.31   | Register exchange implementation example. Register values at $t=5$                            | 36 |

| 2.32   | Register exchange implementation example. Data shift at time intant $t=6$                     | 37 |

| 2.33   | Register exchange implementation example. Shift register content update at time instant $t=6$ | 38 |

| 2.34   | Register exchange implementation example. Store decoded bits at time instant $t=6$            | 38 |

| 2.35   | Traceback implementation example. Memory contents                                             | 39 |

| 2.36   | Traceback implementation example. Traceback step $\ \ldots \ \ldots$                          | 40 |

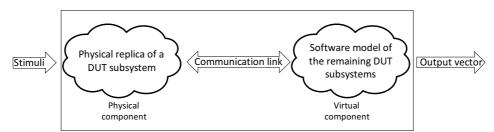

| 2.37   | Simplified block diagram of a HiL simulation                                                  | 58 |

| Chapte | er 3                                                                                          | 67 |

List of Figures xiii

| Chapte | er 4                                                                                                                                                                            | 73         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

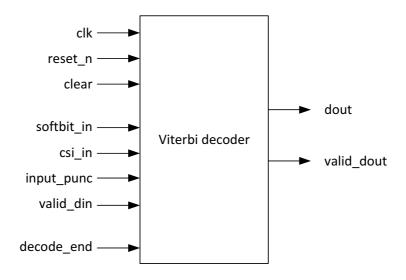

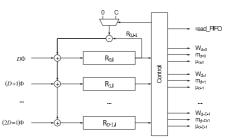

| 4.1    | Top level Viterbi decoder                                                                                                                                                       | 74         |

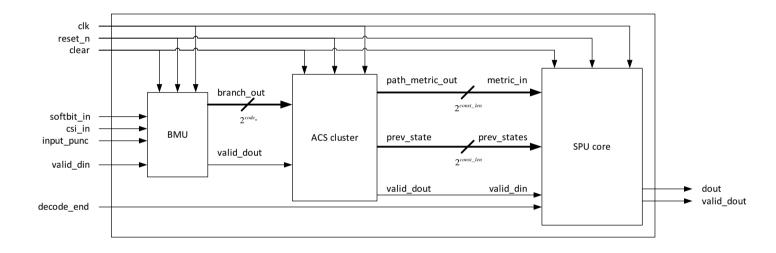

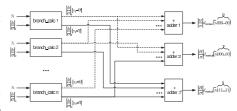

| 4.2    | Block diagram of the Viterbi decoder architecture                                                                                                                               | 78         |

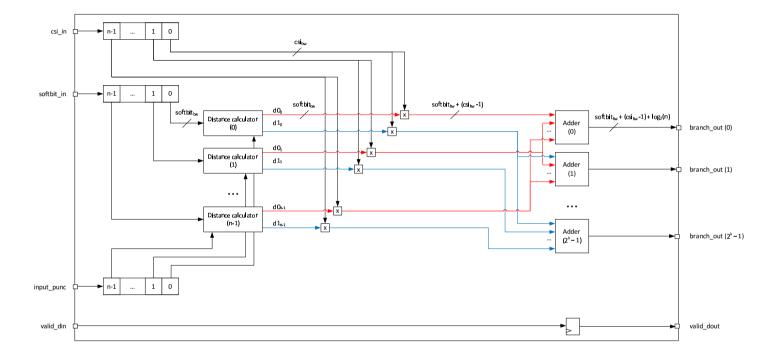

| 4.3    | Block diagram of the CSI aware BMU                                                                                                                                              | 83         |

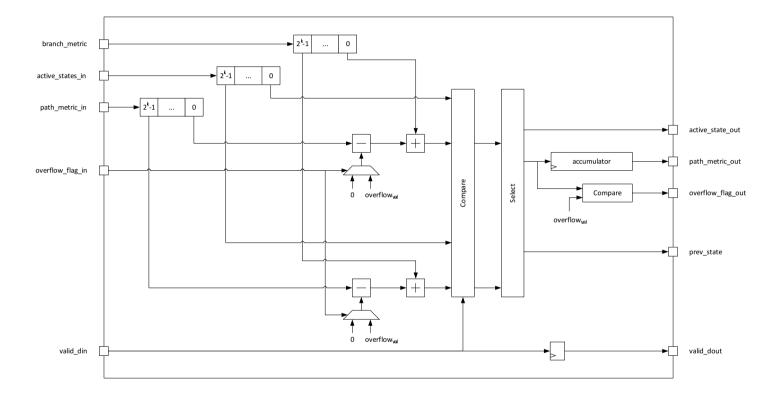

| 4.4    | Block diagram of the Add-Compare-Select unit                                                                                                                                    | 89         |

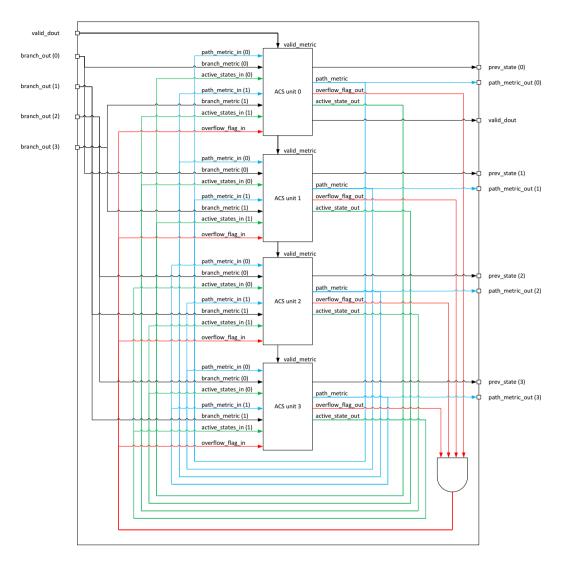

| 4.5    | Add-Compare-Select (ACS) cluster. Interconnection of the different ACS units for the trellis diagram of figure 2.4                                                              | 90         |

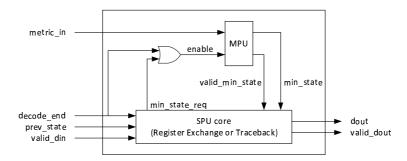

| 4.6    | Survivor Path Unit (SPU) top level view                                                                                                                                         | 91         |

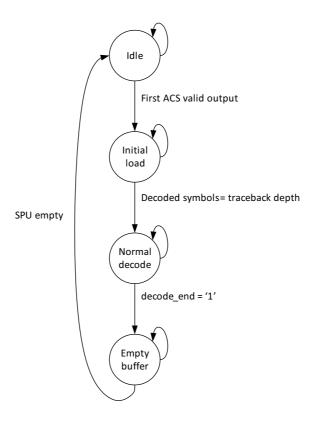

| 4.7    | Global Finite State Machine (FSM) of the SPU                                                                                                                                    | 95         |

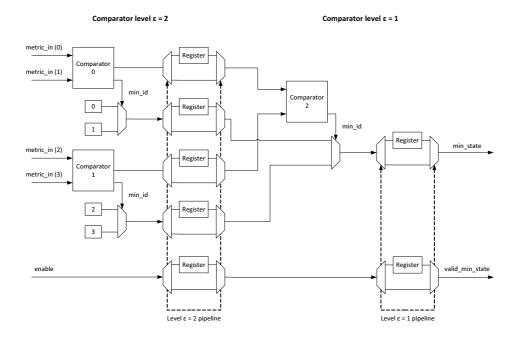

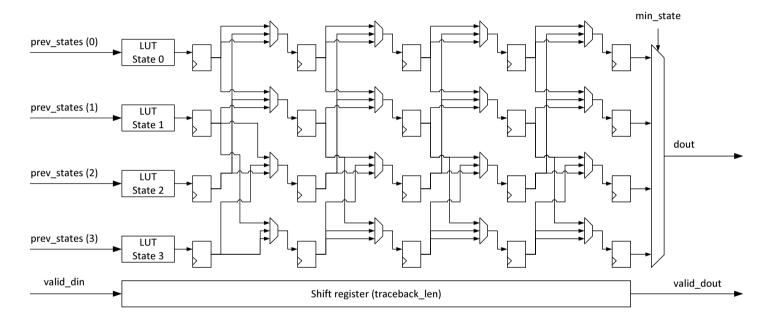

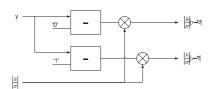

| 4.8    | Block diagram of the Minimum Path Unit (MPU) for $constr \ Jen = 2 \dots \dots$ | =<br>98    |

| 4.9    | Register exchange SPU for $constr \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                                                                                        | =<br>06    |

| 4.10   | Block diagram of an element implementing the traceback SPU10 $$                                                                                                                 | 07         |

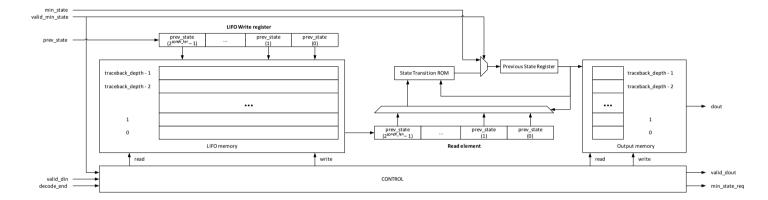

| 4.11   | Timing diagram of the traceback implementation of the SPU $10^{\circ}$                                                                                                          | 08         |

| Chapte | er 5 11                                                                                                                                                                         | l <b>1</b> |

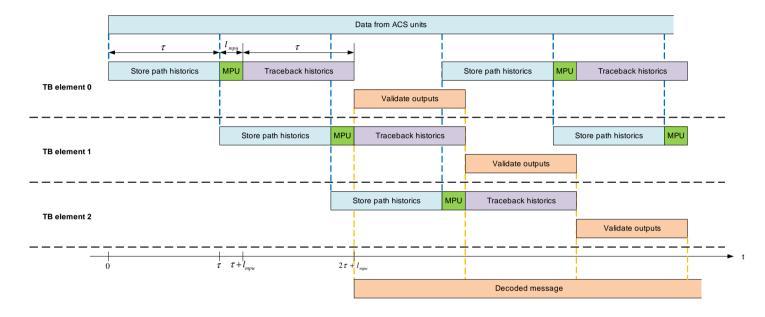

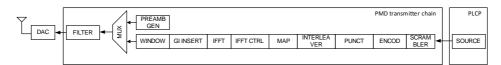

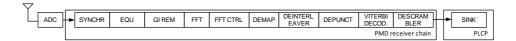

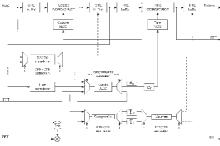

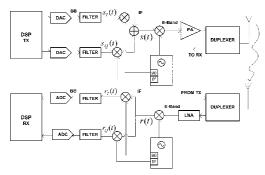

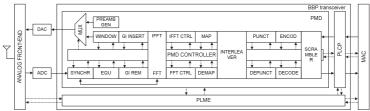

| 5.1    | Block view of the transceiver                                                                                                                                                   | 13         |

| 5.2    | Transmitter chain block diagram of the Physical Medium Dependent (PMD)                                                                                                          | 13         |

| 5.3    | Receiver chain block diagram of the PMD                                                                                                                                         | 14         |

| 5.4    | Block diagram of the transceiver architecture                                                                                                                                   | 15         |

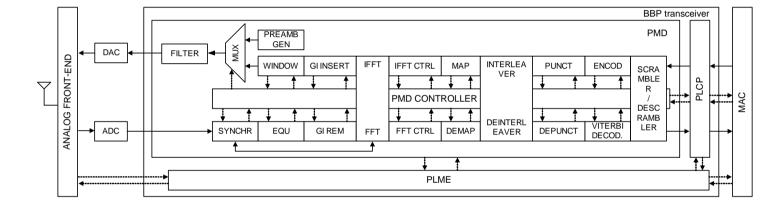

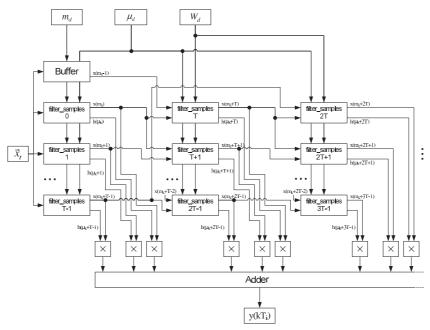

| 5.5    | Architecture of the synchronizer                                                                                                                                                | 18         |

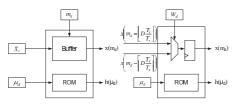

| 5.6    | Hard demapping                                                                                                                                                                  | 18         |

| 5.7    | Soft demapping                                                                                                                                                                  | 19         |

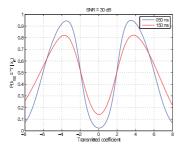

| 5.8    | Simulation set-up to analyze coefficient dispersion 12                                                                                                                          | 20         |

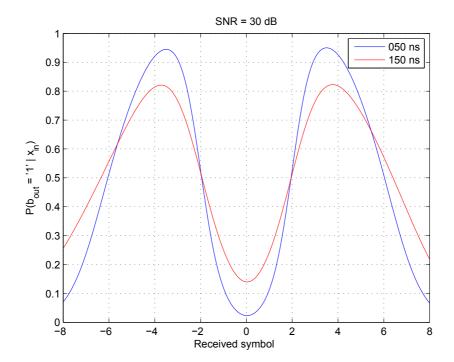

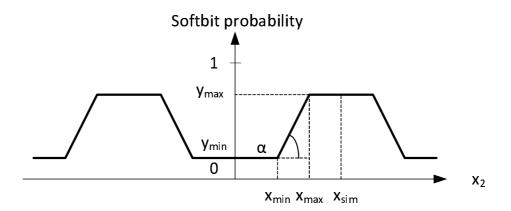

| 5.9    | Example of a demapping function                                                                                                                                                 | 21         |

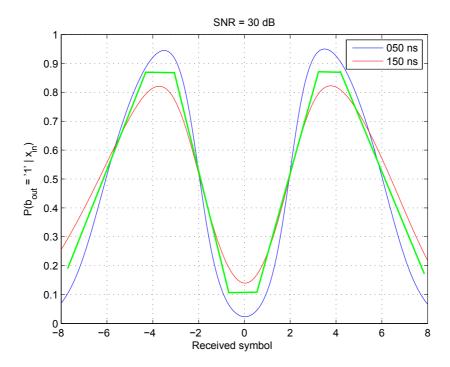

| 5.10   | Linear approximation of the demapping function in figure 5.9 12                                                                                                                 | 22         |

xiv List of Figures

| 5.11   | Demapping parameters for softbit 3 and 6 on 64-QAM                         | 123 |

|--------|----------------------------------------------------------------------------|-----|

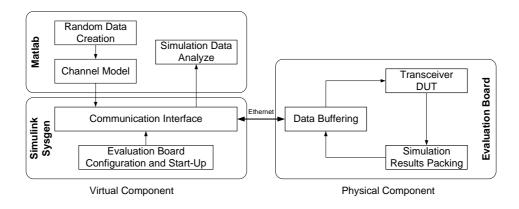

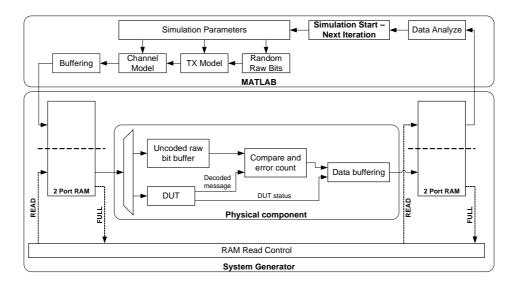

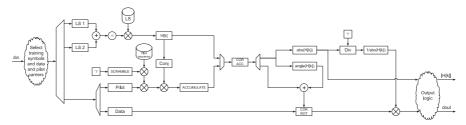

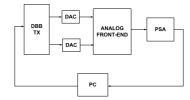

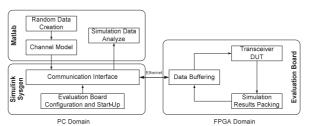

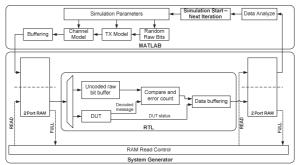

| 5.12   | Architecture of the fast simulator system                                  | 125 |

| 5.13   | Simulation flow dissection                                                 | 126 |

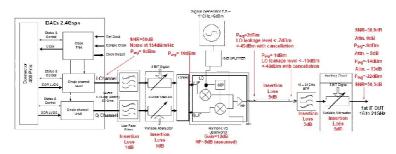

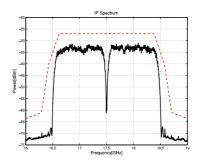

|        | Implementation of the Hardware-in-the-Loop (HiL) simulation platform       | 128 |

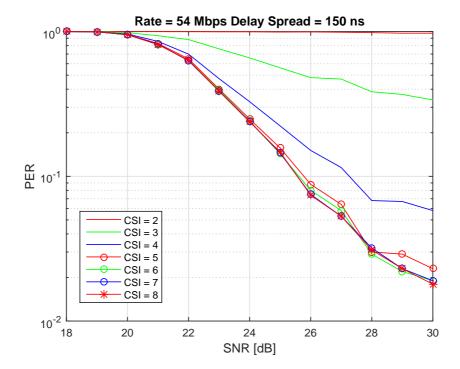

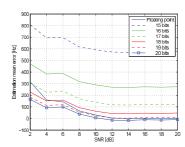

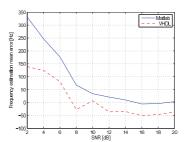

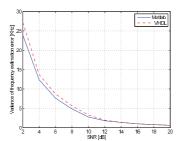

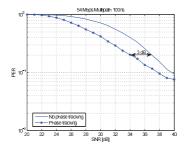

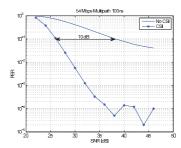

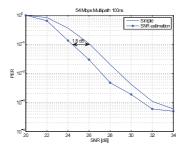

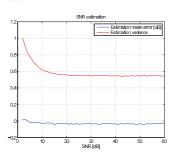

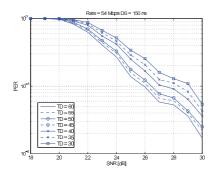

| 5.15   | Influence of the precision in CSI over the PER of the system               | 131 |

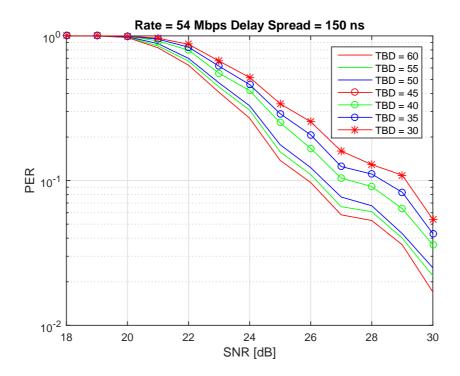

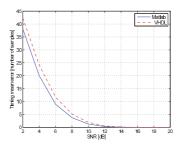

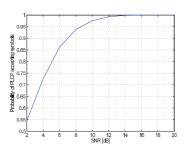

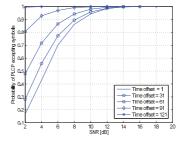

|        | Influence of the traceback depth of the decoder over the PER of the system | 132 |

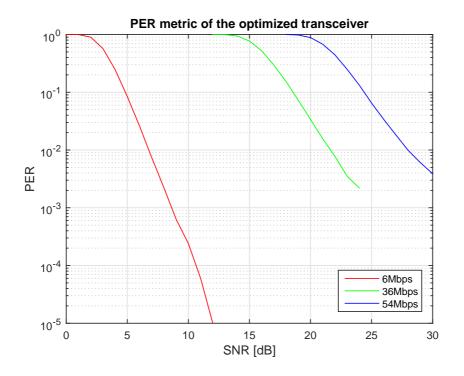

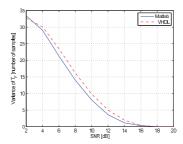

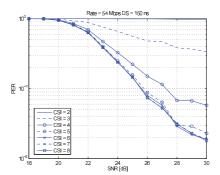

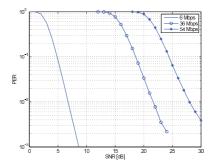

| 5.17   | PER of the optimized transceiver                                           | 136 |

| Chapte | r 6                                                                        | 141 |

| Chapte | Chapter 7                                                                  |     |

| Chapte | r A                                                                        | 181 |

## List of Tables

| Cł | apte | er 1                                                                                                                                                 | 1  |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Cł | apte | er 2                                                                                                                                                 | 5  |

|    | 2.1  | Generated codewords for the parallel convolutional encoder<br>(p = 2)                                                                                | 15 |

|    | 2.2  | Hamming distances between all possible 3-bit wide codewords                                                                                          | 16 |

|    | 2.3  | Comparison of normal and adaptive ACSs with $code_n = 2$ , $code_k = 1$ and $softbit_{bw} = 3$ in Xilinx xc3s50 Field Programmable Gate Array (FPGA) | 43 |

|    | 2.4  | Summary of adaptive Viterbi decoders found in the literature implementing hard-decoding with $k=1$ and $n=2$                                         | 44 |

|    | 2.5  | Resource utilization of ACSs of different radices for convolutional codes with $k=1$                                                                 | 48 |

|    | 2.6  | Gate count comparison of different radix-4 ACSs at different clock speeds in [BK13]                                                                  | 48 |

|    | 2.7  | Gate count comparison of different radix-4 ACSs at their achievable maximum clock speed in [BK13]                                                    | 49 |

|    | 2.8  | Logic area and throughput comparison of Viterbi decoders implementing type-1 ACSs of different radixes in [VNS12a]                                   | 50 |

|    | 2.9  | Summary of the latency of FPGA Viterbi decoder implementations found in the literature with $R=k/n=1/2$                                              | 51 |

|    |      |                                                                                                                                                      |    |

xvi List of Tables

|    | 2.10  | implementation results of the Xilinx Viterbi decoder [XiII1c] with $R = k/n = 1/2$ , $\nu = 6$ , $\tau = 96$ and 3 soft bits on a Virtex-6 6VLX75T-3 FPGA | 55 |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 2.11  | Implementation results of the Xilinx Viterbi decoder [Xil11c] with $R=k/n=1/2,~\nu=6,~\tau=96$ and 3 soft bits on a Spartan-6 XC6SÑX45T-2 FPGA            | 55 |

|    | 2.12  | Implementation results of the Xilinx Viterbi decoder [Xil11c] with $R=k/n=1/2,~\nu=6,~\tau=96$ and 3 soft bits on a Virtex-5 5VLX30-3 FPGA                | 56 |

|    | 2.13  | Summary of HiL platforms                                                                                                                                  | 64 |

| Cl | napte | er 3                                                                                                                                                      | 67 |

| Cl | napte | er 4                                                                                                                                                      | 73 |

|    | 4.1   | Generics of the top level Viterbi decoder                                                                                                                 | 75 |

|    | 4.2   | Input ports of the Viterbi decoder                                                                                                                        | 76 |

|    | 4.3   | Output ports of the Viterbi decoder                                                                                                                       | 77 |

|    | 4.4   | Generics of the Branch Metric Unit (BMU) $\dots$                                                                                                          | 80 |

|    | 4.5   | Input ports of the BMU $\hdots$                                                                                                                           | 81 |

|    | 4.6   | Output ports of the BMU                                                                                                                                   | 81 |

|    | 4.7   | Calculation of branch metrics in the BMU                                                                                                                  | 82 |

|    | 4.8   | Generics of the ACS unit                                                                                                                                  | 85 |

|    | 4.9   | Input ports of the ACS unit                                                                                                                               | 85 |

|    | 4.10  | Output ports of the ACS unit                                                                                                                              | 86 |

|    | 4.11  | Generics of the SPU                                                                                                                                       | 92 |

|    | 4.12  | Input ports of the SPU                                                                                                                                    | 93 |

|    | 4.13  | Output ports of the SPU                                                                                                                                   | 94 |

|    | 4.14  | Generics of the MPU                                                                                                                                       | 96 |

|    | 4.15  | Input ports of the MPU                                                                                                                                    | 97 |

List of Tables xvii

| 4   | 4.16 | Output ports of the SPU                                                                                                                                              | 97  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4   | 4.17 | Pipeline examples of the MPU for $\nu=2$                                                                                                                             | 99  |

| 4   | 4.18 | Generics of the SPU core                                                                                                                                             | 100 |

| 4   | 4.19 | Input ports of the SPU core                                                                                                                                          | 101 |

| 4   | 4.20 | Output ports of the SPU core                                                                                                                                         | 102 |

| Cha | apte | r 5                                                                                                                                                                  | 111 |

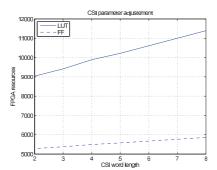

| 5   | 5.1  | Hardware utilization of the transceiver architectures for various values of $csi_{bw}$ with $\tau=60$ and $acs_{xtr\_bw}=7$                                          | 133 |

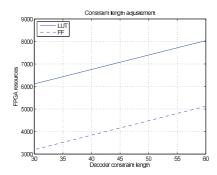

| Ę   | 5.2  | Hardware utilization of the transceiver architectures for various values of $\tau$ with $csi_{bw}=5$ and $acs_{xtr\_bw}=2$                                           | 134 |

| Ę   | 5.3  | PER of different WLAN 802.11a transceivers                                                                                                                           | 137 |

| Cha | apte | r 6                                                                                                                                                                  | 141 |

| (   | 6.1  | Area and speed comparison of Viterbi decoder implementations with $code_n=2,\ code_k=1,\ constr\_len=6$ and $traceback\_depth=18$ on Xilinx xa3s500-ecpg132-4 FPGA . | 143 |

| (   | 5.2  | Area and speed comparison of normal and adaptive ACSs with $code_n = 2$ , $code_k = 1$ and $softbit_{bw} = 3$ in Xilinx xc3s50 FPGA                                  | 145 |

| (   | 3.3  | Data throughput comparison between Viterbi decoders with $code_k = 1$ , $code_n = 2$ , $\nu = 6$ , $softbit_{bw} = 1$ and $\tau = 35$ on different Xilinx FPGA       | 146 |

| (   | 6.4  | Implementation results of a Viterbi decoder with $code_k = 1$ , $code_n = 2$ , $constr \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                        | 147 |

| 6   | 3.5  | Throughput comparison of adaptive Viterbi decoders and the proposed implementation on different Xilinx FPGAs                                                         | 148 |

| 6   | 6.6  | Implementation results of a Viterbi decoder with $code_k = 1$ , $code_n = 2$ , $constr\_len = 6$ and $softbit_{bw} = 1$ in different                                 |     |

xviii List of Tables

| 6.7       | Implementation results of a Viterbi of the Xilinx reconfigurable Viterbi decoder with $code_k = 1$ , $code_n = 2$ , $constr_len = 6$ , $\tau = 96$ and $softbit_{bw} = 3$ in a Xilinx xc6vlx75t-3 FPGA.          |     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.8       | Implementation results of a Viterbi of the Xilinx reconfigurable Viterbi decoder with $code_k=1, code_n=2, constr\_len=6, \tau=96$ and $softbit_{bw}=3$ in a Xilinx xc6slx45t-2 FPGA .                           |     |

| 6.9       | Implementation results of a Viterbi of the Xilinx reconfigurable Viterbi decoder with $code_k=1, code_n=2, constr\_len=6, \tau=96$ and $softbit_{bw}=3$ in a Xilinx xc5vl30-3 FPGA                               |     |

| 6.1       | Implementation results of a reconfigurable Viterbi decoder with maximum parameters defined as $code_k = 5$ , $code_n = 6$ , $constr\_len = 8$ , $\tau = 96$ and $softbit_{bw} = 1$ in a Xilinx xc5vlx330t-1 FPGA | 152 |

| 6.1       | Implementation results of a Viterbi decoder with $code_k = 1$ , $code_n = 2$ , $constr \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                                                                    | 153 |

| 6.1       | 2 Implementation results of a Viterbi decoder with $code_k = 1$ , $code_n = 2$ , $constr \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                                                                  | 154 |

| 6.1       | 3 Decoder comparison in terms of $\Phi$ comparison $1/2$                                                                                                                                                         | 155 |

| 6.1       | 4 Decoder comparison in terms of $\Phi$ comparison $2/2$                                                                                                                                                         | 156 |

| Chapter 7 |                                                                                                                                                                                                                  |     |

| Chapter A |                                                                                                                                                                                                                  |     |

## Glossary

ACS Add-Compare-Select

ADC Analog to Digital Converter

AGC Automatic Gain Control

ASIC Application Specific Integrated Circuit

**AWGN** Additive White Gaussian Noise

**BBP** Base Band Processor

**BER** Bit Error Rate

**BMU** Branch Metric Unit

BPSK Binary Phase-Shift Keying

CiL Controller-in-the-Loop

**CDMA** Code Division Multiple Access

**CLB** Configurable Logic Block

**CORDIC** Coordinate Rotation Digital Computer

**CPU** Central Processing Unit

CRC Cyclic Redundant Check

CSI Carrier Strength Indicator

**DAC** Digital to Analog Converter

**DUT** Device Under Test

xx List of Tables

**DVB-T** Terrestrial Digital Video Broadcasting

FIR Finite Impulse Response

**FEC** Forward Error Correction

**FFT** Fast Fourier Transform

**FIFO** First-In First-Out

**FPGA** Field Programmable Gate Array

**FSM** Finite State Machine

**GSM** Global System for Mobile communications

**GPS** Global Positioning System

**GPU** Graphics Processing Unit

HiL Hardware-in-the-Loop

**HDL** Hardware Description Language

IC Integrated Circuit

**IFFT** Inverse Fast Fourier Transform

IIR Infinite Impulse Response

**IoT** Internet of Things

IP Intellectual Property

**ISI** Inter-Symbol Interference

JTAG Joint Test Action Group

LAN Local Area Network

**LIFO** Last-In First-Out

LSB Least Significant Bit

**LUT** Look-up Table

MAC Medium Access Control

List of Tables xxi

MMC Modular Multilevel Converter

MPU Minimum Path UnitMSB Most Significant Bit

**OFDM** Orthogonal Frequency Division Multiplexing

**PER** Packet Error Rate

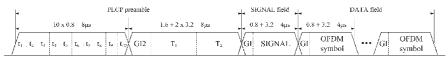

PLCP Physical Layer Convergence Protocol

PLME Physical Layer Management Entity

PMD Physical Medium Dependent

**PPDU** PLCP Protocol Data Unit

PRNG Pseudo Random Number Generator

**QAM** Quadrature Amplitude Modulation

RAM Random Access Memory

**ROM** Read-Only Memory

**RRC** Root Raised Cosine

RSSI Received Signal Strength Indicator

RTL Register Transfer Level

**SAIF** Switching Activity Interface File

SDR Software Defined Radio

SNR Signal-to-Noise Ratio

SoC System-on-Chip

**SPU** Survivor Path Unit

UI User Interface

UWB Ultra Wide Band

VHDL VSIC (Very High Speed Integrated Circuits) Hardware

Description Language

WLAN Wireless Local Area Network

# List of Symbols

| $\lceil x \rceil$   | Largest integer not greater than $x$                                           |

|---------------------|--------------------------------------------------------------------------------|

| $\lfloor x \rfloor$ | Smallest integer not less than $x$                                             |

| $\epsilon$          | Comparator level in the MPU                                                    |

| ν                   | Constraint length of the convolutional code                                    |

| au                  | Traceback depth of the convolutional decoder                                   |

| Φ                   | Figure of merit used to compare decoder architectures                          |

| ζ                   | Comparator identifier at level $\epsilon$ in the MPU                           |

| k                   | Number of bits that are loaded into to the convolutional coder per clock cycle |

| $l_{mpu}$           | Latency in clock cycles of the Minimum Path Unit (MPU)                         |

| m                   | Number of bits coded in a QAM constellation point                              |

| n                   | Number of coded bits generated by the convolutional coder per clock cycle      |

| p                   | Parallelization ratio of the ACSU                                              |

| R                   | Coding rate                                                                    |

| T                   | Threshold of the adaptive Viterbi algorithm                                    |

| $N_{max}$           | Number of survivor paths per iteration in the adaptive Viterbi algorithm       |

| $\mathbf{c}$ | Source coded symbol                         |

|--------------|---------------------------------------------|

| m            | Source uncoded symbol                       |

| $\mathbf{r}$ | Received symbol                             |

| x            | Demapped received symbol                    |

| G(x)         | Transfer function of the convolutional code |

# CHAPTER 1

### Introduction

#### Contents

| 1.1 | Introduction                 | 1 |

|-----|------------------------------|---|

| 1.2 | Outline of the research work | 3 |

#### 1.1 INTRODUCTION

For the last decades new and more complex digital system have appeared on a yearly basis as predicted by Moore's observation [Moo65]. However, the possibility of designing more complex Integrated Circuits (ICs) has not only be limited to increase their performance on a very specific task. On the contrary: the miniaturization requirements of new devices such as smartphones, tablets or phablets (or those which will become common under the newly coined Internet of Things (IoT)) have only been achieved when technology has been mature enough to integrate into a single chip devices as diverse as Central Processing Units (CPUs), Graphics Processing Units (GPUs), Digital to Analog Converters (DACs), Analog to Digital Converters (ADCs) and wireless transceivers. These ICs are known as System-on-Chips (SoCs).

With the advent of advanced touch-control User Interfaces (UIs) the mobile market has experienced a significant growth that continues nowadays, with several reports [AMJ<sup>+</sup>14a, AMJ<sup>+</sup>14b, Chu14, CMS14, Cis14] forecasting shipments between 1.8 and 2.2 milliard units for the year 2015.

As SoCs grew in complexity and performance, end user began to demand application and services with higher bandwidth consumption. High reliable communication systems are necessary for the development applications and services. In this scenario, forward error correcting techniques are fundamental tools that provide robustness to digital communication links.

Convolutional coders are one of the first codes for which an optimum decoding algorithm was discovered. They are preferred over block codes such as Turbo codes for their superior performance with comparable complexity decoding architectures.

The Viterbi algorithm is a maximum likelihood decoder for convolutional codes. It operates recursively and in each iteration it discards the less probable messages that can have been transmitted. It is estimated that the Viterbi decoder is the most complex entity of the receiver chain of a multicarrier transceiver.

Since its discovery, Viterbi decoders have become a fundamental cornerstone in many communication systems. Back in 1986, V.32 modems used an 8 state convolutional code to obtain a coding gain of about 3.5 dB. V.34, an updated revision of the standard, used 16 to 64 state convolutional codes to achieve coding gains of 4.0 to 4.5 dBs [FBEM96]. The Viterbi algorithm is known also for being the first coding scheme used in deep space communications in the Pioneer program [CHIW98]. At the dawn of the new millennia, Viterbi decoders were implemented in around one milliard cell phones worldwide [Jr.05], and a contemporary survey carried out by Qualcomm [Pad05] indicated that approximately 10<sup>15</sup> bits were decoded by Viterbi decoders on video broadcast applications.

The Viterbi decoder proposals found in the literature aim at optimizing its description in areas such as area and power consumption, decoding capacity or achievable maximum frequency. These goals are generally mutually exclusive and do not analyse their impact on the overall decoder performance.

The purpose of this research work is to obtain, verify and optimize a Viterbi decoder description with respect to the transceiver architecture in which it will be used. Wireless Local Area Network (WLAN) 802.11a will be used as the case study of the research work.

#### 1.2 OUTLINE OF THE RESEARCH WORK

In the following, the organization of this PhD dissertation is outlined:

#### Chapter 2: State of the art

This chapter summarizes the State of the Art of Viterbi decoders. First, convolutional codes are introduced. Next, the Viterbi algorithm is described. Following, the basic building blocks of hardware Viterbi decoders are enumerated. Finally, Viterbi decoder hardware implementations found in the literature are listed.

#### Chapter 3: Objectives

This chapter states the main objective of this research work and decomposes it into partial objectives. It also presents the figrues of merit that will be used to compare the different Viterbi decoder architectures found in the literature with that developed in this research work.

#### Chapter 4: Viterbi decoder architecture

The chapter describes the hardware architecture of the Viterbi decoder implemented in this research work. Both register exchange and traceback implementations are proposed.

#### Chapter 5: Hardware-in-the-Loop simulations

This chapter describes a Hardware in the Loop simulation platform used to perform a parametrical analysis of the Viterbi decoder and introduces the WLAN 802.11a compliant transceiver, the case study of this research work, hardware modules. The Viterbi decoder is embedded within the WLAN 802.11a compliant transceiver description and then a parametrical analysis of the entire system is performed using the Hardware-in-the-Loop (HiL) simulator to find a balance between system performance and resource utilization. Once the transceiver architecture has been optimized, a more thorough analysis is executed using the HiL platform to obtain the Packet Error Rate (PER) performance curves of the system under multipath fading channels.

#### Chapter 6: Results

This chapter compares the Viterbi decoder description developed in this research work with other proposals found in the literature.

#### Chapter 7: Conclusions and areas for further research

This chapter presents the conclusions of this research work and possible areas for further research.

# CHAPTER 2

### State of the art

| 2.1        | Introduction                        |  |

|------------|-------------------------------------|--|

| 2.2        | Viterbi decoder 6                   |  |

| 2.3        | Hardware-in-the-Loop simulations 57 |  |

| <b>2.4</b> | Concluding Remarks 65               |  |

|            | -                                   |  |

#### 2.1 INTRODUCTION

The continuous advances in integration processes have allowed the deployment of cheaper, more complex digital circuits. At the same time, these new devices have boosted the appearance of applications and services that demand high bandwidth mobile communications. Error correction techniques are fundamental and powerful tools that allow the deployment of highly reliable communication systems.

The Viterbi algorithm, named after Andrew James Viterbi [Vit67], is the key decoding algorithm of convolutionally encoded messages. It is used in a wide range of applications such as speech recognition, LTE, Physical Downlink Control Channel (PDCCH), CDMA and GSM digital cellular, dial-up modems, satellite, deep-space communications [Doo10], Ultra Wide

Band (UWB) communication schemes and 802.11 wireless Local Area Networks (LANs).

Among all the available algorithms aimed at decoding convolutional codes the Viterbi is the most resource intensive. However, it is capable of performing maximum likelihood decoding. A significant research work effort is maintained up to this day aimed at identifying new, optimized hardware architecture implementations of the algorithm.

Analyzing these architectures is a very time consuming task, specially when the decoder is embedded in a communication transceiver. The hardware implementation must not only be verified, but its decoding capacity must be measured in various channel configurations (noise level, multipath delay spread, ...) and, if the communication system allows it, different transmission rates supported by the transceiver. Consequently, the entire system (transceiver architecture and surrounding channel) should be considered when the architecture of the transceiver is being optimized to meet certain area, power consumption or decoding capacity criterion.

#### 2.2 VITERBI DECODER

This section presents the state of the art of Viterbi decoders. First convolutional codes are disclosed. Next, the Viterbi algorithm is introduced. Following, the building blocks of Viterbi decoders are described and finally the different implementations of Viterbi decoders are presented.

#### 2.2.1 CONVOLUTIONAL CODES

A simplified view of the operation of a communication system is depicted in figure 2.1.

Figure 2.1: Simplified block diagram of a communication system

Viterbi decoder 7

In the transmitter side of the communication system, a data source generates messages  $\mathbf{m}$ . Each message  $\mathbf{m}$  is represented as a vector of k symbols. The symbols of  $\mathbf{m}$  can belong to any alphabet, although in digital communications they are generally considered to be bits.

To minimize the probability of errors during data transmission most communication systems implement Forward Error Correction (FEC) mechanisms. The block responsible of protecting the message  $\mathbf{m}$  against the mismatches of the channel is the encoder. The encoder takes the binary message  $\mathbf{m}$  and produces an output n bit wide codeword  $\mathbf{c}$ , where n > k. The ratio R = k/n is known as the coding rate of the encoder and it can be seen as a tradeoff between the redundancy added to the original message and the capacity of detecting errors during transmission: codes with low R are more redundant and offer more opportunities to detect and correct erroneous bit sequences, but transmit less source data bits per encoded bit.

The transmitter serializes codeword bits in a parallel-to-serial block so that a single encoded bit is transmitted per channel use. In figure 2.1 we have assumed a channel that simply adds Additive White Gaussian Noise (AWGN) to the transmitted signal. At the receiver side, the inverse process is performed. A serial-to-parallel block takes the detected signal and generates a received vector  $\mathbf{r}$  of n bits. Note that due to the AWGN in the channel, the codeword  $\mathbf{c}$  and received vector  $\mathbf{r}$  are not necessarily the same.

A decoder takes the received vector  $\mathbf{r}$  and, based on the knowledge of the coding rules at the *encoder*, tries to identify which message  $\mathbf{m}$  was originally transmitted. The guess generated by the decoder is labelled  $\mathbf{x}$  in figure 2.1.

The Bit Error Rate (BER) is a performance metric of such a communication system. It is the ratio between the number of bits  $\mathbf{m}$  and  $\mathbf{x}$  differs and the length of the message  $\mathbf{m}$ .

Convolutional codes are one of the earliest codes for which effective decoding algorithms were developed. They are viewed as *stream codes* since generally they operate on continuous streams of bits not partitioned in discrete message blocks or packets. In practice they are preferred to block codes (for example, Turbo codes) because, at a comparable encode/decode complexity, they provide excellent performance [Moo05]. The name *convo-*

*lutional* code comes from the fact that the operation of these codes can be seen as filtering or convolution.

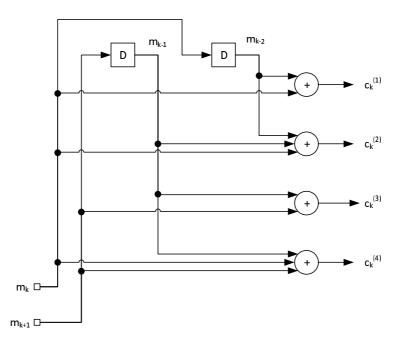

Let us take for example the architecture of an encoder implementing a R=1/2 convolutional code in figure 2.2. Being a R=1/2 code, every instant of time the convolutional encoder takes a one-bit input *message* and generates a two-bit output *codeword*. As it can be seen, a convolutional encoder consists basically of a shift register and a set of n XOR gates.

Figure 2.2: Example convolutional encoder with R=1/2

The number of registers in the shift register of the convolutional encoder is known as the constraint length  $\nu$  of the code. In essence, the convolutional encoder operates as a Finite State Machine (FSM). Each instant of time a new input message bit is fetched into the encoder and the content of its register is shifted one position to the right. The content of the shift register represents the *state* of the FSM. For a convolutional code with a constraint length  $\nu$ , the total number of possible states in the encoder is  $2^{\nu}$ .

The output codeword of the encoder is calculated every time instant as the XOR operation between the input of the encoder at that time instant and the logical value of certain positions in the shift register. The transfer function G(x) of the convolutional code is the matrix representation of the elements that are taken into account when calculating the output of the encoder. The elements of the transfer function matrix G(x) are generally expressed in polynomials of x. The degrees of the terms of the polynomial indicate the positions in the shift register that are considered to calculate the codeword. The highest degree of the polynomial is then  $\nu$ , and the input to the encoder represents the independent term of the polynomial.

Viterbi decoder 9

For the encoder in figure 2.2 we have that

$$G(x) = [m_k + m_{k-2} m_k + m_{k-1} + m_{k-2}]$$

=  $[1 + x^2 1 + x + x^2]$  (2.1)

In general, G(x) is a  $k \times n$  matrix. Since in our example k = 1 and n = 2, we have that the transfer function matrix in (2.1) is a two-element row vector.

Not all the convolutional codes can be represented by polynomials. An encoder that has only polynomial entries in its transfer function matrix is said to be a *feedforward* encoder or a Finite Impulse Response (FIR) encoder. An encoder that has rational functions in its transfer function matrix is said to be a *feedback* or Infinite Impulse Response (IIR) encoder.

For feedforward encoders, it is common to indicate the connection polynomials as vectors of numbers representing the *impulse response* of the encoder. The binary representation of the transfer function of equation (2.1) is represented by the vectors

$$G(x) = [m_k + m_{k-2} m_k + m_{k-1} + m_{k-2}]$$

= [[101] [111]] (2.2)

where the Most Significant Bit (MSB) of the binary vector represents the input to the encoder and the Least Significant Bit (LSB) of the binary vector indicates the  $\nu$ -th element of the shift register of the encoder.

These binary vectors are often expressed compactly in octal form, where the triplets of bits are represented using the integers from 0 to 7. In this form, the encoder in (2.1) is represented as

$$G(x) = [[101] \quad [111]] = [5 \quad 7]$$

(2.3)

A convolutional code is unequivocally represented by the triplet  $(n, k, \nu)$  and its transfer function G(x).

For encoding and decoding purposes, there are two helpful representations of the transfer function of a convolutional code: the *state* diagram and the *trellis* diagram.

The state diagram of the convolutional code is a graph that depicts the state transitions and the generated codewords as a function of the input bits to the encoder. Figure 2.3 shows the state diagram of the example convolutional encoder presented in figure 2.2.

Figure 2.3: State diagram

Each state transition is represented with an arrow connector. Above each arrow two quantities separated by slashes are annotated. The leftmost quantity is the input to the encoder at a given time instant that triggers the state transition. The rightmost quantity is the generated codeword due to the state transition.

For example, from figure 2.3, we can deduce that when the convolutional encoder is at state "01" it will transition to state "00" when a logical zero is applied to its input. In this transition the encoder will generate the codeword "11". Otherwise, if a logical one is applied to the encoder, then it will transition to state "10" and generate the output codeword "00".

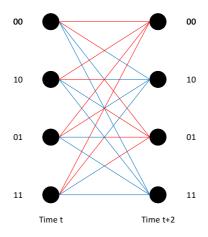

The trellis diagram of the convolutional code is a rearrangement of the former state diagram where the notion of time instant is added to the state transitions. Let us consider the trellis diagram of our example convolutional code depicted in figure 2.4.

Figure 2.4: One-state Trellis

The diagram shows two sets of all the possible states of the encoder. The leftmost column is the initial state of the convolutional encoder at time instant t. The rightmost column is the final state of the convolutional encoder after the transition has occurred at time instant t+1. In the figure initial and final states are connected by coloured lines. The color of these lines represent the logical value of the input to the encoder at the initial time instant: a red line indicates a logical zero input bit and a blue line represents a logical one input bit. Above each line the codeword generated due to the state transition is written.

One-state transition trellis diagrams such as that in figure 2.4 are stacked one after the other to represent the evolution of the encoder over a specific time interval. For example, if our example encoder, beginning at the initial state "00", were to encode the message  $\mathbf{m} = [1, 1, 0, 0, 1, 0, 1, 0]$ , the trellis diagram shown in figure 2.5 would be generated.

In the figure above the binary representation of the states of the encoder have been substituted by their corresponding unsigned decimal representation. The colored line in the figure represents a path through the trellis that unequivocally identifies the encoding of the message  $\mathbf{m}$ .

As it can be deduced from these diagram representations of the convolutional code, there is a very tight connection between the input message  $\mathbf{m}$  to the encoder, the generated output codeword  $\mathbf{c}$  and the state trans

Figure 2.5: Example path in the Trellis diagram

sition sequence depicted by the *path* through the trellis diagram. For a given initial state condition in the convolutional encoder, knowing any of the former sequences (input message, output codeword or path through the trellis) implies the knowledge of the remaining sequences.

Thus, a convolutional decoder is the block that, based on the received codeword signal **r**, tries to identify the path in the trellis that originated it. After the most probable path in the trellis has been identified, the decoder reconstructs the original message by identifying the state transitions in the trellis path with the inputs to the encoder that trigger them.

### 2.2.1.1 Parallelization of convolutional codes

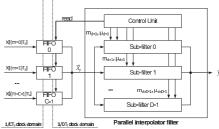

Some decoding algorithms are based on parallel implementation of the convolutional encoder. Whereas a serial convolutional encoder takes a binary word of k bits and generates a codeword of n bits, a parallel implementation of the convolutional encoder takes a block of p consecutive input binary words of k bits and generates a block of p codewords of n bits.

For the same input message  $\mathbf{m}$ , both serial and parallel encoder implementations produce identical outputs. Consequently, the two encoder implementations have identical constraint length  $\nu$  and number of states  $2^{\nu}$ . The implementation of the parallel convolutional encoder is modified slightly to accommodate to the increased number of inputs and outputs. For the example convolutional encoder introduced in this chapter, its parallel implementation with p=2 is shown in figure 2.6.

**Figure 2.6:** Example convolutional encoder with parallelization index p = 2

From the figure, input port  $m_k$  corresponds to the input of the serial encoder at time instant t and input port  $m_{k+1}$  corresponds to the input of the serial encoder at time instant t+1. Similarly, output ports  $c_k^{(1)}$  and  $c_k^{(2)}$  of the parallel encoder correspond to the output of the serial encoder at time instant t and output ports  $c_k^{(3)}$  and  $c_k^{(4)}$  of the parallel encoder correspond to the output of the serial encoder at time instant t+1.

The trellis diagram of the parallel implementation of the convolutional encoder is obtained by rearranging the states of the serial implementation. The trellis diagram of the parallel implementation of the example convolutional encoder with p=2 is shown in figure 2.7.

For the parallel encoder, the lines connecting the initial and final states of the trellis diagram are split into p colored segments. The color of the first segment indicates the logical value of the binary message word at time instant t=0. A red line indicates that at that time instant a logical zero was input to the parallel convolutional encoder. A blue line, on the other

Figure 2.7: Parallel Trellis diagram

hand, indicates that a logical one was input to the parallel convolutional encoder. The color of the last segment indicates the logical value of the message input to the parallel convolutional encoder at time instant t = p-1.

The generated codewords due to the state transitions in the parallel implementation of the convoluitonal encoder with p=2 are shown in table 2.1.

There is a limit in the level of parallelization p that can be obtained in the convolutional code. The parallelization p must never surpass the constraint length  $\nu$  of the code. Otherwise, different input messages blocks would produce identical state transition, and therefore, the decoding process would become infeasible.

#### 2.2.2 VITERBI ALGORITHM

The Viterbi algorithm was proposed by Andrew Viterbi [Vit67], but it was not until [For73] that its optimality as a maximum likelihood sequence decoder was appreciated. Communication system applications include examples such as maximum likelihood sequence estimation in the presence of Inter-Symbol Interference (ISI) [For72] and optimal reception of spread-spectrum multiple access communications [Ver84]. It has also been used for hidden Markov modeling [DPH93] and survey applications [MS00].

| Initial/End state | 00   | 10   | 01   | 11   |

|-------------------|------|------|------|------|

| 00                | 0000 | 0011 | 1101 | 1110 |

| 10                | 0111 | 0100 | 1010 | 1001 |

| 01                | 1100 | 1111 | 0001 | 0010 |

| 11                | 1011 | 1000 | 0110 | 0101 |

**Table 2.1:** Generated codewords for the parallel convolutional encoder(p=2)

The key idea behind the Viterbi algorithm is that a coded sequence  $\mathbf{c} = [c_0, c_1, \ldots]$  or its associated received input sequence  $\mathbf{r} = [r_0, r_1, \ldots]$  in figure 2.1 corresponds to a single path through the encoder trellis. Due to mismatches in signal reception, the received sequence  $\mathbf{r}$  may not correspond with the same path through the trellis. Moreover, the received sequence may imply an *illegal* path through the trellis. A path that includes states transitions other than those defined by the state diagram of the code.

The Viterbi algorithm tries to find the legal path through the trellis that is closest to the received sequence  $\bf r$ . Instead of taking a brute force approach, where all the possible paths through the trellis would need to be compared with the received sequence  $\bf r$ , the Viterbi algorithm operates in an efficient, recursive form. In each decoding time instant the algorithm selects a set of only  $2^{\nu}$  paths among all the possible paths that can be generated up to that point. The  $2^{\nu}$  paths that the Viterbi algorithm selects in each iteration are known as the  $survivor\ paths$  at that time instant. There is one survivor path per state in the convolutional code. Every decoding time, all possible paths that converge to a given state and are not the  $survivor\ path$  are discarded by the Viterbi algorithm for further analysis.

Competing paths ending at a same state in the encoder are compared in terms of their *metrics*. Encoder sequences that differ significantly to the received sequence have a higher metric cost than encoder sequences that resemble the received sequence. Consequently, the Viterbi algorithm selects the paths with minimum metric. Typically, the Hamming distance is the preferred method when calculating the metrics. The Hamming distance

|     | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 000 | 0   | 1   | 1   | 2   | 1   | 2   | 2   | 3   |

| 001 | 1   | 0   | 2   | 1   | 2   | 1   | 3   | 2   |

| 010 | 1   | 2   | 0   | 1   | 2   | 3   | 1   | 2   |

| 011 | 2   | 1   | 1   | 0   | 3   | 2   | 2   | 1   |

| 100 | 1   | 2   | 2   | 3   | 0   | 1   | 1   | 2   |

| 101 | 2   | 1   | 3   | 2   | 1   | 0   | 2   | 1   |

| 110 | 2   | 3   | 1   | 2   | 1   | 2   | 0   | 1   |

| 111 | 3   | 2   | 2   | 1   | 2   | 1   | 1   | 0   |

**Table 2.2:** Hamming distances between all possible 3-bit wide codewords

between two binary vectors (or points) is the number of positions in which their logical values differ. Table 2.2 shows the Hamming distance between all possible 3-bit codewords. The metric of the survivor path ending at a given state of the encoder is known as the *path metric* of that state.

When the decoding time advances, the Viterbi algorithm extends the survivor paths of the previous time instant with the transitions described by the trellis diagram of the coder. The metrics of the new candidate paths are calculated by adding the path metric of their precursor state with the branch metric of the transition: the Hamming distance between the codeword of the state transition (defined in the trellis diagram) and the received sequence  $\bf r$  at that time instant. For each of the  $2^{\nu}$  states, the algorithm selects, among all the possible transitions defined by the trellis, the path with minimum accumulated metric.

Let us better illustrate the operation of the Viterbi algorithm by means of an example extracted from [Moo05]. Consider again the example convolutional encoder described in figure 2.2. The state and trellis diagrams of this encoder were given in figures 2.3 and 2.4.

When the data sequence

$$m = [1, 1, 0, 0, 1, 0, 1, 0, \dots]$$

=  $[m_0, m_1, m_2, m_3, m_4, m_5, m_6, m_7, \dots]$

is applied to the encoder it generates the following codewords:

$$\mathbf{c} = [11, 10, 10, 11, 11, 01, 00, 01, \dots]$$

$$= [\mathbf{c}_0, \mathbf{c}_1, \mathbf{c}_2, \mathbf{c}_3, \mathbf{c}_4, \mathbf{c}_5, \mathbf{c}_6, \mathbf{c}_7, \dots]$$

The coded output sequence is transmitted through a channel. Due to the noisy characteristics of this channel the binary representation of the received sequence  $\mathbf{r}$  and the codewords  $\mathbf{c}$  differ. Let us assume that during the signal transmission, the received sequence becomes

$$\mathbf{r} = [11, 10, \underline{0}0, 1\underline{0}, 11, 01, 00, 01, \ldots]$$

$$= [\mathbf{r}_0, \mathbf{r}_1, \mathbf{r}_2, \mathbf{r}_3, \mathbf{r}_4, \mathbf{r}_5, \mathbf{r}_6, \mathbf{r}_7, \ldots]$$

where the underlined bits in  $\mathbf{r}$  indicate the positions where the logical values of the codewords  $\mathbf{c}$  have toggled their values.

The Viterbi algorithm operates as follows.

At time instant t=0 the sequence  ${\bf r}_0=11$  is received. It is known that state 0 is the initial state of the convolutional coder. Based on the trellis diagram (figure 2.4) of the convolutional code, we know that only states 0 and 1 can be reached at time instant t=1 from the initial state of the encoder. The generated codewords due to these transitions are "00" and "11" respectively. The Viterbi algorithm calculates the path metrics of these hypothetical transitions as the Hamming distance between the received sequence ( ${\bf r}_0=11$ ) and the generated output codewords. In our case, the path metrics are 2 and 0 respectively. As a result, at time instant t=1 there are only 2 possible paths, with metrics 0 and 2, as shown in the figure 2.8.

The metric that converges to a specific state in a given instant of time are known as the *branch metric* of the state at that time instant.

**Figure 2.8:** Path extension at time instant t = 1

At time instant t=1 the sequence  $\mathbf{r}_1=10$  is received. Again, all existing paths are extended at time t=2 as defined by the trellis diagram by adding the path metric to each branch metric. Note that at time t=2, a total of 4 paths are available, each ending in one of the 4 possible states of the trellis

Figure 2.9: Path extension at time instant t = 2

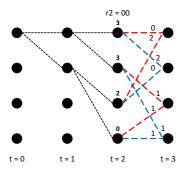

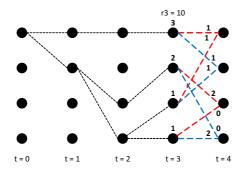

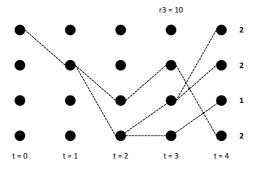

At time instant t=2 the sequence  $\mathbf{r}_2=00$  is received. Once again, each path is extended by adding the path metric to each branch metric. In the figure 2.10, the branch metric of each path is represented by the value above each state at time instant t=2, and the branch metrics of all path possible paths to time instant t=3 are the value above the doted colored lines

**Figure 2.10:** Path extension at time instant t = 3

Note that at time t=3 there are several possible paths that end up in the same node of the trellis diagram. The Viterbi algorithm selects the paths with the best (lowest) accumulated metric at each node, as these are the paths that are closer to the received sequence  $\mathbf{r}$ . These paths are known as the survivor paths at time instant t=3. The remaining paths will be discarded for further analysis. After the survivor paths have been selected, the trellis diagram becomes as follows:

Figure 2.11: Survivor path selection at time instant t = 3

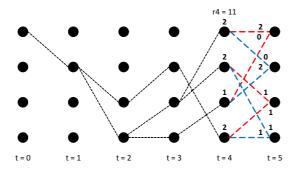

At time instant t=3 the sequence  ${\bf r}_3=10$  is received. The algorithm continues extending the paths by adding the path metric to each branch metric

Figure 2.12: Path extension at time instant t = 4

As before, the paths with best (lowest) metric at each state are selected.

Figure 2.13: Survivor path selection at time instant t = 4

If we observe the previous figure, we will notice a fundamental characteristic of the survivor paths: from now on all the survivor paths share an identical set of state transitions in the trellis. Indeed, all the survivor paths at time instant t=4 share a common state transition from state 0 to state 1 at the beginning of the encoding.

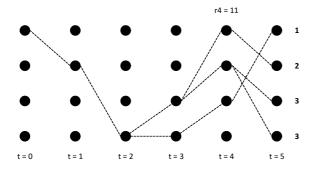

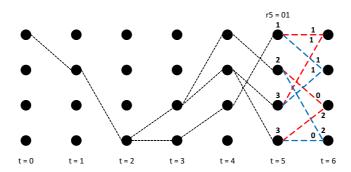

The decoding process continues. At time instant t=4 the sequence  $\mathbf{r}_4=11$  is received. The paths are extended by adding the path metric to each branch metric

Figure 2.14: Path extension at time instant t = 5

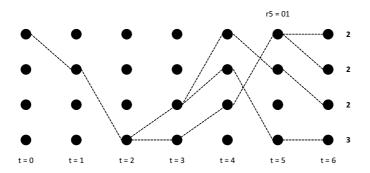

This time, there are several paths ending in states 2 and 3 with the same minimum (best) metric of 3. Since only one path must be selected, the survivor paths can be chosen randomly or using a pre-defined rule. In this case the selection algorithm has no impact on the decoding capability and performance of the Viterbi algorithm. The next figure depicts the selected survivor paths

Figure 2.15: Survivor path selection at time instant t = 5

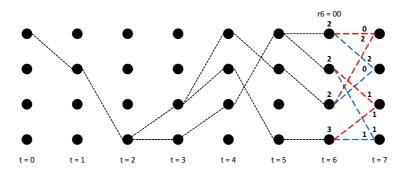

At time instant t = 5 the sequence  $\mathbf{r}_5 = 01$  is received.

Figure 2.16: Path extension at time instant t = 6

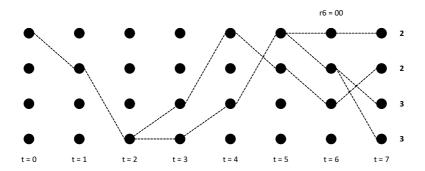

After survivor path selection, the state transition diagram becomes:

Figure 2.17: Survivor path selection at time instant t = 6

At time instant t=6 the sequence  ${\bf r}_6=00$  is received.

Figure 2.18: Path extension at time instant t = 7

After survivor path selection, the state transition diagram becomes:

Figure 2.19: Survivor path selection at time instant t = 7

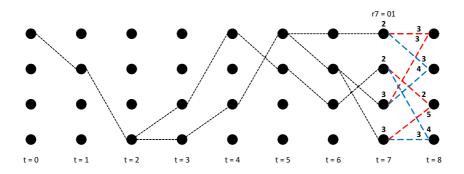

At time instant t=7 the sequence  $\mathbf{r}_7=01$  is received.

Figure 2.20: Path extension at time instant t = 8

After survivor path selection, the state transition diagram becomes:

Figure 2.21: Survivor path selection at time instant t = 8

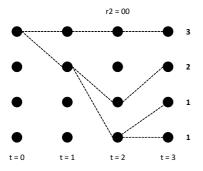

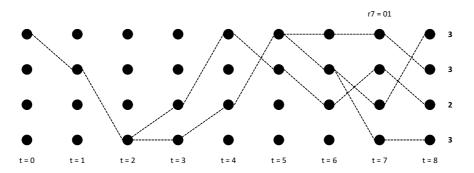

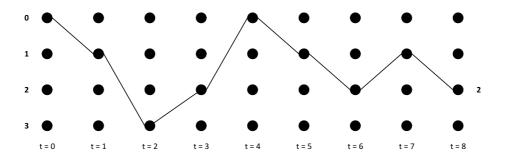

The decoding is completed after the reception of sequence  $\mathbf{r}_7$  by selecting the state at the last stage with best (lowest) metric.

Figure 2.22: Survivor path with minimum accumulated metric of the decode process

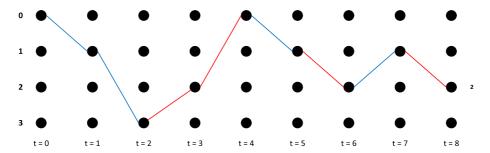

Beginning with this last state, the trellis diagram is traversed backwards along the survivor path until the first stage in the encoding process is reached, and then it is traversed forwards once more along the survivor path while the input message sequence that originates the obtained state transitions is calculated.

The colored line in the figure below represents the reconstructed message **m** after the Viterbi algorithm has been applied to the received message **r**. Red lines correspond to a logical zero in the message sequence, while blue lines represent logical ones in the message sequence.

Figure 2.23: Decoded message r

Comparing the previous result with the contents in figure 2.5 we observe that the Viterbi algorithm can successfully decode an erroneously received noisy sequence  ${\bf r}$ .

## 2.2.2.1 Adaptive Viterbi Algorithm

The adaptive Viterbi algorithm [MW96] is a variation of the classic algorithm. It is aimed at reducing the power consumption and memory requirements of decoders implementing the Viterbi algorithm [VPG13, BSK<sup>+</sup>13, BSL11b].

The adaptive Viterbi algorithm adds two additional criterions when selecting the survivor paths. First, a threshold T is defined. All candidate paths whose accumulated branch metric exceeds (is worse than) this threshold are automatically discarded for further analysis. Even the survivor path of a given state can be discarded if its accumulated metric exceeds this value. Secondly, the number of survivor paths stored at each decoding iteration is reduced from  $2^{\nu}$  to a value  $N_{max}$ . From the set of survivor paths not exceeding the predefined threshold T, only the first  $N_{max}$  paths with best (lowest) accumulated metric are considered for further analysis.

Several Adaptive Viterbi decoders can be found in the literature [STGB02a, TSR+05a, LDZL11a, CC01, STGB02b].

### 2.2.3 VITERBI DECODER BUILDING BLOCKS

From the example of the previous section, we deduce that the key operations performed by the Viterbi algorithm are the following:

- To calculate the branch metrics between the input sequence  $\mathbf{r}$  at a given time instant t and all the possible codewords generated by the encoder.

- To extend the survivor paths at time instant t-1 with the state transitions defined by the trellis diagram and calculate the metrics of all these candidate paths as the addition of the branch metric of the precursor state and the branch metric due to the state transition at time instant t.

- To select the path with minimum accumulated metric among all the candidate paths ending at a given state in the encoder at time instant t and to repeat this setp will all the  $2^{\nu}$  states in the code.

- To Store into memory the new set of survivor paths.

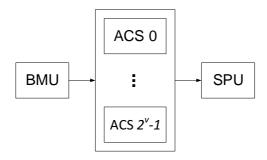

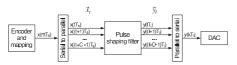

Figure 2.24 shows the typical block architecture of a Viterbi decoder. The architecture is divided into the following functional blocks:

Figure 2.24: Simplified block diagram of a Viterbi decoder

- The Branch Metric Unit (BMU) is responsible for calculating the Hamming distances between the received sequence **r** and all the possible codewords of the code.

- A set of 2<sup>ν</sup> Add-Compare-Selects (ACSs) (one per state in the code) extend the metrics that reach each state in the code by adding the accumulated path metric to the branch metric associated with the state transitions defined in the state and trellis diagrams in figures 2.3 and 2.4, compare the resulting metrics and select the survivor path as the path reaching the state with best (lowest) accumulated metric.

- The Survivor Path Unit (SPU) updates the historic of survivor paths with the outcome of the ACSs and regenerates the estimated message sequence  $\mathbf{x}$ .

The following sections describe each functional block in detail.

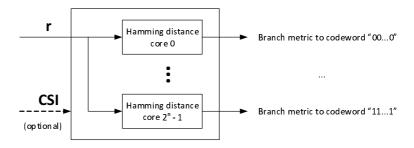

## 2.2.3.1 Branch Metric Unit

The BMU calculates the branch metrics for all state transitions defined in the trellis diagram of the code. It does so by calculating the Hamming distances between the received sequence  ${\bf r}$  and all possible codewords in

the convolutional code. For binary convolutional codes with coding rates R=k/n=1/2 the total number of codewords generated by the encoder is  $2^n$ .

The metrics calculated by the BMU can be improved if the functional blocks in the receiver chain provide the decoder with further information about the received signal. For this discussion we will need to expand the initial transceiver architecture first introduced in figure 2.1.

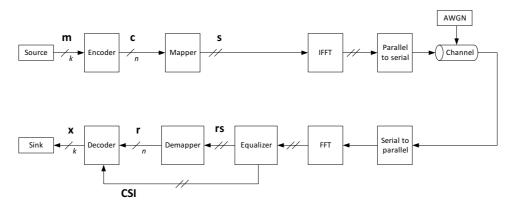

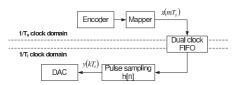

Figure 2.25: Block diagram of an OFDM transceiver

Figure 2.25 depicts a basic block diagram of an Orthogonal Frequency Division Multiplexing (OFDM) based communication system. The key differences between this architecture and the early transceiver shown in figure 2.1 are the following:

- The codeword generated by the convolutional encoder is loaded into a mapper. This unit takes a block of m codeword bits and generates a symbol  $\mathbf{s}$  of an M-ary Quadrature Amplitude Modulation (QAM) constellation, where  $M=2^m$ .

- The set of constellation points its loaded into an Inverse Fast Fourier Transform (IFFT) unit. The IFFT is the core element of OFDM based communication systems, as it performs both modulation and frequency multiplexion.

- At the receiver side, a Fast Fourier Transform (FFT) core demodulates the received signal and generates a set of complex symbols.

These symbols are affected by the impulse response of the channel. The channel response is different for all the subcarrier frequencies of the OFDM modulation. An *equalizer* is needed to estimate and compensate this effect.

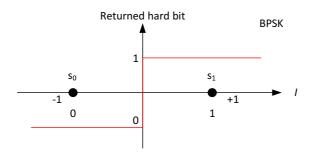

• Finally, a *demapper* takes the equalized complex symbols and returns the binary representation of the constellation points that are closer in Euclidean distance to them.

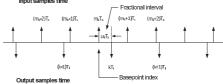

Figure 2.26 shows the basic architecture of a BMU. As it can be seen, an array of  $2^n$  elements calculate in parallel all the branch metrics in the trellis diagram for the input sequence  $\mathbf{r}$ . An optional input port labelled CSI provides the BMU the channel estimation on multicarrier transceivers.

Figure 2.26: Block diagram of the Branch Metric Unit (BMU)