# A STATISTICAL STT-RAM DESIGN VIEW AND ROBUST DESIGNS AT SCALED TECHNOLOGIES

by

## **Yaojun Zhang**

B.S. Microelectronics, Shanghai Jiaotong University, 2008M.S. Electrical Engineering, University of Pittsburgh, 2010

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

## **Doctor of Philosophy**

University of Pittsburgh

2017

## UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Yaojun Zhang

It was defended on

November 19, 2016

and approved by

Yiran Chen, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Hai Li, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Ching-Chung Li, Ph.D., Professor, Department of Electrical and Computer Engineering

Ervin Sejdic, Ph.D., Assistant Professor, Department of Electrical and Computer Engineering

Mingui Sun, Ph.D., Professor, Department of Neurological Surgery

Dissertation Advisors: Yiran Chen, Ph.D., Associate Professor, Department of Electrical and Computer Engineering,

Co-Advisor, Hai Li, Ph.D., Associate Professor, Department of Electrical and Computer

Engineering

## A STATISTICAL STT-RAM DESIGN VIEW AND ROBUST DESIGNS AT SCALED TECHNOLOGIES

Yaojun Zhang, PhD

University of Pittsburgh, 2017

Rapidly increased demands for memory in electronic industry and the significant technical scaling challenges of all conventional memory technologies motivated the researches on the next generation memory technology. As one promising candidate, spin-transfer torque random access memory (STT-RAM) features fast access time, high density, non-volatility, and good CMOS process compatibility. In recent years, many researches have been conducted to improve the storage density and enhance the scalability of STT-RAM, such as reducing the write current and switching time of magnetic tunneling junction (MTJ) devices. In parallel with these efforts, the continuous increasing of tunnel magneto-resistance(TMR) ratio of the MTJ inspires the development of multi-level cell (MLC) STT-RAM, which allows multiple data bits be stored in a single memory cell. Two types of MLC STT-RAM cells, namely, parallel MLC and series MLC, were also proposed. However, like all other nano-scale devices, the performance and reliability of STT-RAM cells are severely affected by process variations, intrinsic device operating uncertainties and environmental fluctuations. The storage margin of a MLC STT-RAM cell, i.e., the distinction between the lowest and highest resistance states, is partitioned into multiple segments for multi-level data representation. As a result, the performance and reliability of MLC STT-RAM cells become more sensitive to the MOS and MTJ device variations and the thermal-induced randomness of MTJ switching.

In this work, we systematically analyze the impacts of CMOS and MTJ process variations and MTJ resistance switching randomness that induced by intrinsic thermal fluctuations. Then, we analyzed the extension of STT-RAM cell behaviors from SLC (single-level-cell) to MLC (multi-level-cell). With the detail analysis study of STT-RAM cells, we proposed several error reduction

design, such as ADAMS structure, and FA-STT structure. In which, *ADAMS* can be dynamically configured between the high-reliable (HR) mode and the high-capacity (HC) mode upon the real-time system requirement: For the performance and reliability critical applications, ADAMS switches to HR mode. For the capacity critical applications, ADAMS switches to HC mode. The ADAMS cell is broken into two "1T1J" cells that can work independently, offering the similar performance and reliability to conventional STT-RAM design.

### TABLE OF CONTENTS

| PRI | EFACE                                                  |

|-----|--------------------------------------------------------|

| 1.0 | <b>INTRODUCTION</b> 1                                  |

| 2.0 | PRELIMINARY 3                                          |

|     | 2.1 STT-RAM Basics                                     |

|     | 2.2 Process Variations                                 |

|     | 2.3 Thermal Fluctuation in MTJ switching               |

| 3.0 | SINGLE-LEVEL CELL OPERATION ANALYSIS                   |

|     | 3.1 Write Errors of an STT-RAM cell                    |

|     | 3.1.1 Persistent Errors                                |

|     | 3.1.1.1 Geometry Variations of Transistor and MTJ      |

|     | 3.1.1.2 Fluctuation of Magnetic Anisotropy             |

|     | 3.1.2 Quantitative Analysis on Persistent Write Errors |

|     | 3.1.3 Non-Persistent Errors                            |

|     | 3.1.3.1 Thermal Fluctuations                           |

|     | 3.1.3.2 Temperature Dependency                         |

|     | 3.1.4 Statistical Write Error Rate Analysis            |

|     | 3.1.5 Array Level Analysis                             |

|     | 3.2 Read Errors of an STT-RAM cell                     |

|     | 3.2.1 Persistent Error: Sensing Errors                 |

|     | 3.2.2 Non-Persistent Error: Read Disturbance           |

|     | 3.2.3 Read Error Rate Analysis                         |

|     | 3.2.4 Reading Analysis of a STT-RAM Array              |

|     | 3.3 STT-RAM Design Space Exploration of Reliability Optimization. | 28 |

|-----|-------------------------------------------------------------------|----|

|     | 3.3.1 Oxide Layer Thickness Design Specification                  | 28 |

|     | 3.3.2 Word-line Override Designs                                  | 31 |

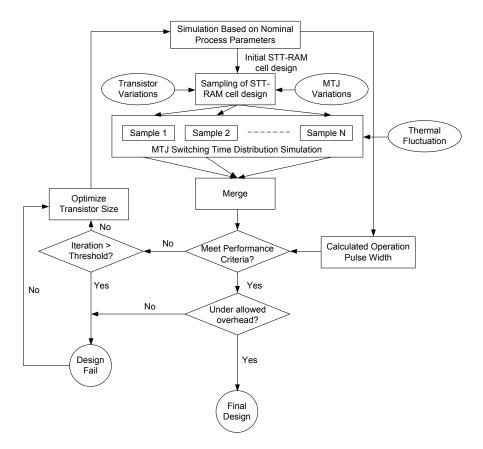

|     | 3.4 STT-RAM Cell Design Optimization Flow                         | 32 |

| 4.0 | MULTI-LEVEL CELL OPERATION ANALYSIS                               | 34 |

|     | 4.1 Variability Sources in MLC STT-RAM Designs                    | 34 |

|     | 4.1.1 Process Variations in MLC                                   | 35 |

|     | 4.1.2 Thermal Fluctuations                                        | 35 |

|     | 4.2 Readability Analysis of MLC MTJs                              | 36 |

|     | 4.2.1 Nominal Analysis of the Readability of MLC MTJs             | 36 |

|     | 4.2.2 Statistical Analysis of the Readability of MLC MTJs         | 38 |

|     | 4.2.2.1 Optimization of Parallel MLC MTJs                         | 38 |

|     | 4.2.2.2 Optimization of Series MLC MTJs                           | 40 |

|     | 4.3 Writability Analysis of MLC MTJs                              | 41 |

|     | 4.3.1 Write Mechanism of MLC STT-RAM Cells                        | 41 |

|     | 4.3.2 Impacts of Thermal Fluctuations                             | 42 |

|     | 4.3.3 Write Operations of Parallel MLC MTJs                       | 43 |

|     | 4.3.4 Write Operations of Series MLC MTJs                         | 46 |

| 5.0 | DIFFERENTIAL SENSING SCHEME TO IMPROVE THE READ PERFOR-           |    |

|     | MANCE OF STT-RAM                                                  | 48 |

|     | 5.1 motivation                                                    | 48 |

|     | 5.2 ADAMS Technology                                              | 48 |

|     | 5.2.1 Regular Differential Sensing Scheme (RDAMS)                 | 49 |

|     | 5.2.2 Asymmetric Differential Cell Structure (ADAMS)              | 50 |

|     | 5.2.3 Read and Write Robustness of ADAMS                          | 50 |

|     | 5.2.3.1 Read robustness                                           | 50 |

|     | 5.2.3.2 Write robustness                                          | 51 |

|     | 5.2.4 Asymmetric SenAmp and Latch Design                          | 51 |

|     | 5.2.4.1 Asymmetric SenAmp                                         | 51 |

|     | 5.2.4.2 Asymmetric Latch                                          | 53 |

|     | 5            | .2.5 Reconfigurable Scheme STT-RAM            | 54 |

|-----|--------------|-----------------------------------------------|----|

|     | 5.3 A        | ADAMS Design Optimization and Analysis        | 55 |

|     | 5            | 3.1 Write Operation Analysis                  | 55 |

|     |              | 5.3.1.1 Asymmetric Write Analysis             | 55 |

|     |              | 5.3.1.2 Definition of Write Error Rate        | 56 |

|     |              | 5.3.1.3 Write Optimization of ADAMS           | 58 |

|     | 5            | 3.2 Read Operation Analysis                   | 60 |

|     |              | 5.3.2.1 Read Reliability Analysis             | 60 |

|     |              | 5.3.2.2 Read Latency Analysis                 | 64 |

| 6.0 | OTH          | ER PROPOSED STT-RAM IMPROVEMENT WORKS         | 66 |

|     | 6.1 E        | Basic Concept of FA-STT                       | 66 |

|     | 6.2 F        | A-STT Read Scheme                             | 68 |

|     | 6            | 5.2.1 Self-reference Sensing Scheme in FA-STT | 68 |

|     | 6            | 2.2.2 Read Operation Analysis                 | 70 |

|     |              | 6.2.2.1 Read disturbance                      | 70 |

|     |              | 6.2.2.2 Sensing margin                        | 72 |

|     | 6.3 F        | A-STT Write Scheme                            | 73 |

|     | 6            | .3.1 Field-assisted MTJ Switching             | 73 |

|     | 6            | 3.3.2 Write Performance Evaluation            | 74 |

|     | 6            | .3.3 Write Error Rate                         | 76 |

|     | 6.4 L        | Layout Design Consideration                   | 77 |

|     | 6.5 0        | GSHE Spin Logic Structure                     | 78 |

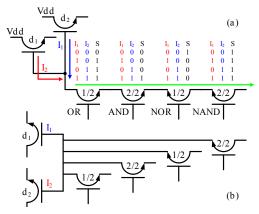

|     | 6            | 5.1 Basic Logic Functions                     | 78 |

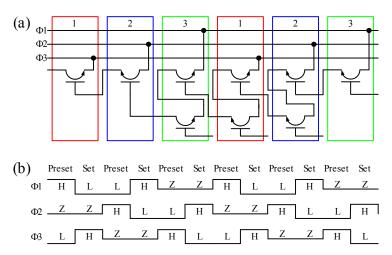

|     | 6            | 5.5.2 GSHE Logic Operation Scheme             | 80 |

|     | 6.6 E        | Diode-GSHE Structure                          | 82 |

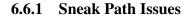

|     | 6            | 6.1 Sneak Path Issues                         | 82 |

|     | 6            | 6.2 Proposed Diode-GSHE Structure             | 83 |

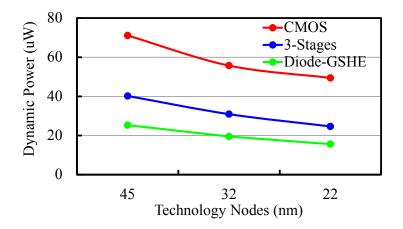

|     | 6.7 <b>C</b> | Case Study                                    | 84 |

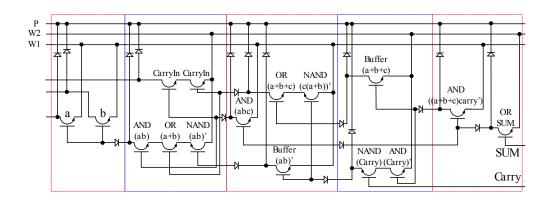

|     | 6            | 7.1 Full Adder Design                         | 84 |

|     | 6            | 0.7.2 Experimental Results                    | 86 |

| 7.0 | CONCLUSION | [ | • | <br>• | <br>• | • | • | • | • | • | <br> | • | • | • | • | • | • | • | • |  |  | • | • | • | • • | 89 |

|-----|------------|---|---|-------|-------|---|---|---|---|---|------|---|---|---|---|---|---|---|---|--|--|---|---|---|-----|----|

| BIB | LIOGRAPHY  |   |   |       | <br>• |   |   |   |   |   | <br> |   |   |   |   |   |   |   |   |  |  |   |   |   |     | 90 |

### LIST OF TABLES

| 1 | Summary of Device Parameters                                           | 8  |

|---|------------------------------------------------------------------------|----|

| 2 | MTJ Write Current Distribution Under Process Variations                | 10 |

| 3 | Summary of Variation Contribution [34]                                 | 12 |

| 4 | Summary of Device Parameters                                           | 56 |

| 5 | Design Parameters                                                      | 69 |

| 6 | Comparison of write error rates under 10ns write period                | 76 |

| 7 | Control Signal of Diode-GSHE Structure                                 | 83 |

| 8 | Summary of GSHE MTJ Parameters                                         | 86 |

| 9 | Comparison of Full Adders between CMOS Circuit and Proposed Diode-GSHE |    |

|   | Circuit.                                                               | 87 |

### LIST OF FIGURES

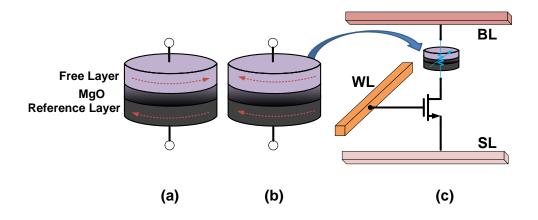

| 1  | MTJ Structure (a) Anti-parallel (high resistance state). (b) Parallel (low resistance |    |

|----|---------------------------------------------------------------------------------------|----|

|    | state). (c) 1T1J STT-RAM cell structure                                               | 4  |

| 2  | Examples of the driving strength distribution of the NMOS transistor in the STT-      |    |

|    | RAM cell: (a) $1 \rightarrow 0$ . (b) $0 \rightarrow 1$                               | 13 |

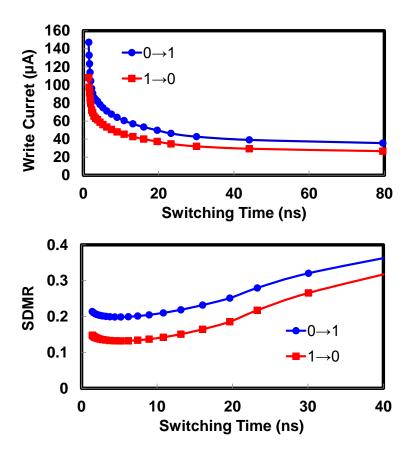

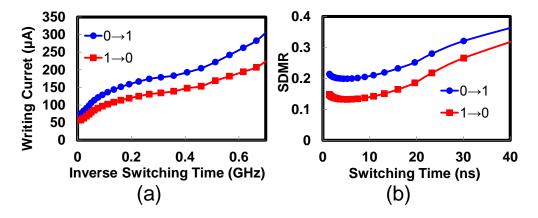

| 3  | (a) Switching current vs. Switching time mean. (b) Switching time mean vs. SDMR       |    |

|    | (Switching time standard deviation/Mean Ratio)                                        | 15 |

| 4  | Perpendicular MTJ. (a) Switching current vs. Switching time mean. (b) Switching       |    |

|    | time mean vs. SDMR                                                                    | 17 |

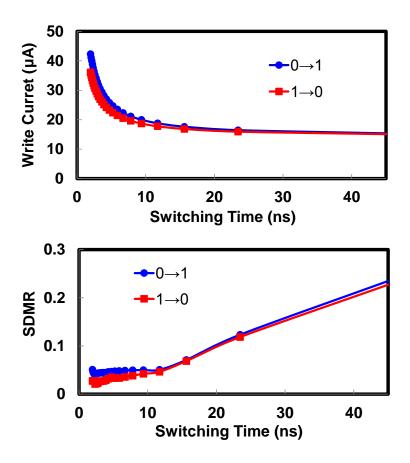

| 5  | (a) MTJ Critical Switching Current vs. Switching Time under Varying Temperature,      |    |

|    | (b)Threshold Switching Time against Temperature                                       | 18 |

| 6  | (a) Error Rate for 10ns Write Pulse Width, (b) Error Rate for 20ns Write Pulse        |    |

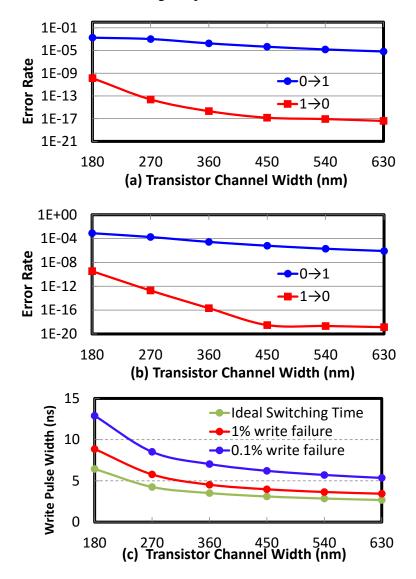

|    | Width, (c) 1% and 0.1% error rate of writing '1'                                      | 19 |

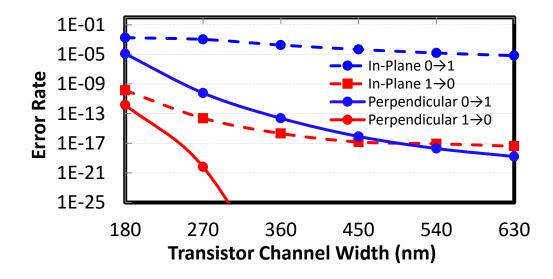

| 7  | In-plane and perpendicular STT-RAM write error rate comparison under 10ns write       |    |

|    | pulse width.                                                                          | 21 |

| 8  | Transistor channel length distribution map for a STT-RAM array                        | 22 |

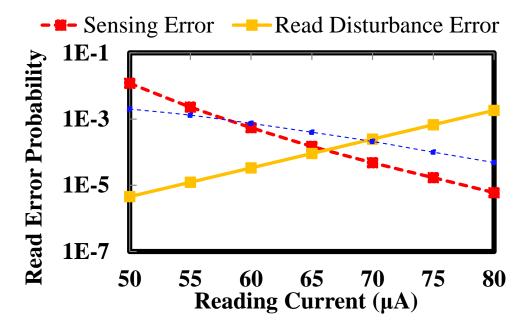

| 9  | Probability of Sensing Error and Read Disturbance under different read current.       |    |

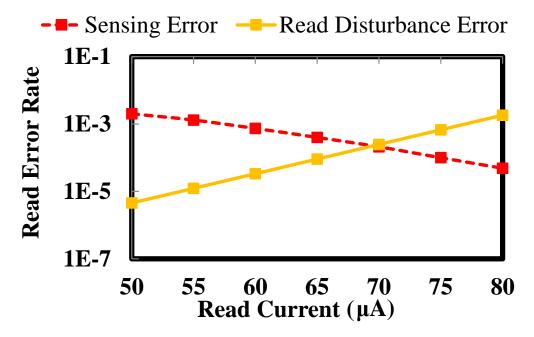

|    | $T_{read} = 5ns.$                                                                     | 24 |

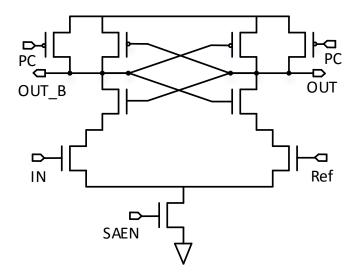

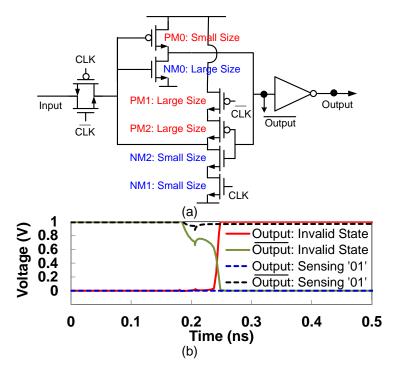

| 10 | Sense amplifier design.                                                               | 26 |

| 11 | Probability of Sensing Error and Read Disturbance in a STT-RAM array                  | 27 |

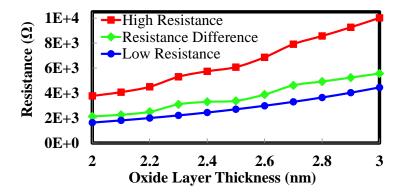

| 12 | Resistance states and resistance difference changes with oxide layer thickness        | 28 |

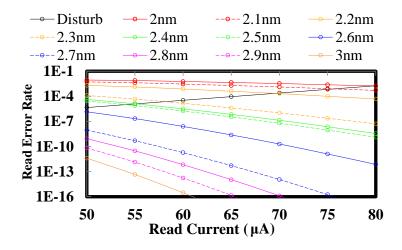

| 13 | Sensing error rate and disturbance error rate when oxide layer thickness varies       | 29 |

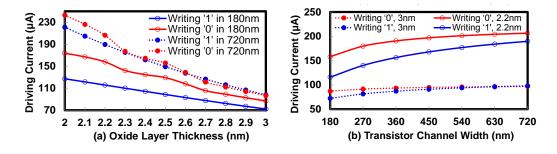

| 14                   | (a) NMOS driving ability varies with oxide layer thickness. (b) NMOS driving                                                                                                                                                     |                            |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                      | ability varies with transistor channel width.                                                                                                                                                                                    | 29                         |

| 15                   | Write error rate under different oxide layer thicknesses.                                                                                                                                                                        | 30                         |

| 16                   | Comparison between original design and override design in writing '1'                                                                                                                                                            | 31                         |

| 17                   | Precess Variation Aware STT-RAM Design Flow.                                                                                                                                                                                     | 32                         |

| 18                   | Four state resistance distributions of (a) Parallel MLC MTJ and (b) Series MLC                                                                                                                                                   |                            |

|                      | MTJ, optimized by nominal design method                                                                                                                                                                                          | 38                         |

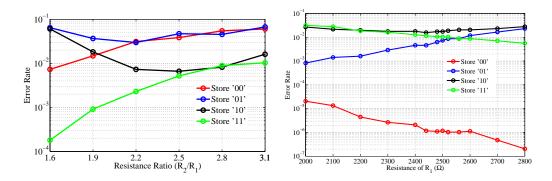

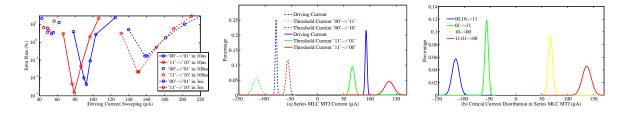

| 19                   | (a) Error Rate vs. $R_2/R_1$ Ratio Sweep, (b)Error Rate vs. Resistance of Hard Domain                                                                                                                                            |                            |

|                      | Sweep                                                                                                                                                                                                                            | 40                         |

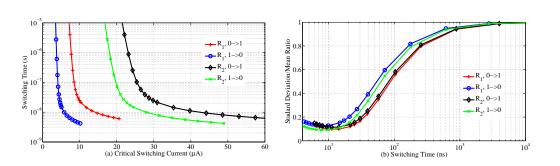

| 20                   | Switching properties of the two domains for a parallel MLC MTJ. (a) switching                                                                                                                                                    |                            |

|                      | time vs. switching current. (b) switching time standard deviation vs. switching                                                                                                                                                  |                            |

|                      | current                                                                                                                                                                                                                          | 43                         |

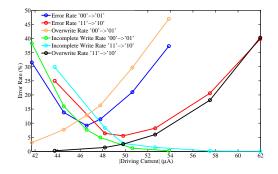

| 21                   | Writing error rate in parallel MLC STT-RAM cell at $T_w = 10$ ns. Notes: The total                                                                                                                                               |                            |

|                      | error rate is not necessarily equal to the sum of incomplete error and overwrite error,                                                                                                                                          |                            |

|                      | which are the errors overwriting the hard domain or incurring the incomplete soft                                                                                                                                                |                            |

|                      |                                                                                                                                                                                                                                  |                            |

|                      | domain flipping, respectively.                                                                                                                                                                                                   | 45                         |

| 22                   | domain flipping, respectively                                                                                                                                                                                                    | 45                         |

| 22                   |                                                                                                                                                                                                                                  | 45                         |

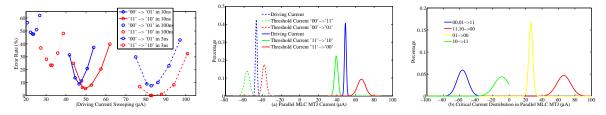

| 22                   | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold                                                                                                                                              |                            |

| 22<br>23             | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-                                                        |                            |

|                      | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold current distributions of resistance state trasitions for the parallel MLC MTJ.(b) Dependent transitions. (c) Independent transitions.        |                            |

|                      | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold<br>current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-<br>pendent transitions. (c) Independent transitions |                            |

|                      | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold<br>current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-<br>pendent transitions. (c) Independent transitions | 45                         |

| 23                   | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold<br>current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-<br>pendent transitions. (c) Independent transitions | 45<br>46                   |

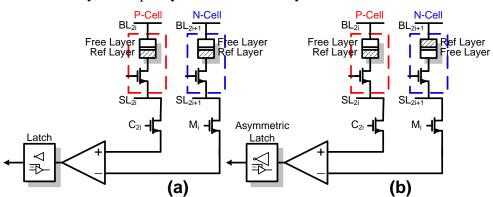

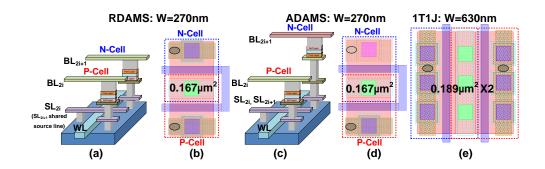

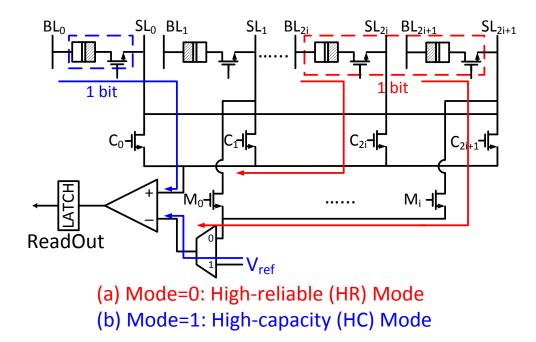

| 23<br>24             | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold<br>current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-<br>pendent transitions. (c) Independent transitions | 45<br>46<br>49             |

| 23<br>24             | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold<br>current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-<br>pendent transitions. (c) Independent transitions | 45<br>46<br>49             |

| 23<br>24<br>25       | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold<br>current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-<br>pendent transitions. (c) Independent transitions | 45<br>46<br>49<br>50       |

| 23<br>24<br>25       | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold<br>current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-<br>pendent transitions. (c) Independent transitions | 45<br>46<br>49<br>50<br>52 |

| 23<br>24<br>25<br>26 | (a)Writing error rate in a parallel MLC STT-RAM cell at different $T_w$ , Threshold<br>current distributions of resistance state trasitions for the parallel MLC MTJ.(b) De-<br>pendent transitions. (c) Independent transitions | 45<br>46<br>49<br>50<br>52 |

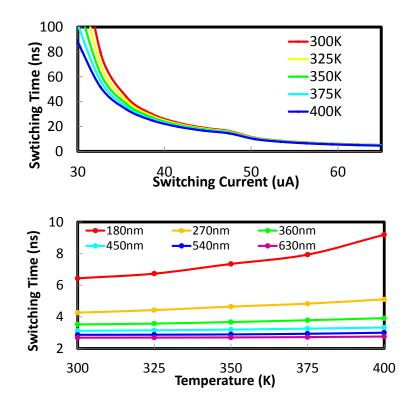

| 29 | (a) Switching current vs. Inverse of switching Time. (b) Switching time mean vs        |    |

|----|----------------------------------------------------------------------------------------|----|

|    | Standard deviation and mean ratio (SDMR).                                              | 55 |

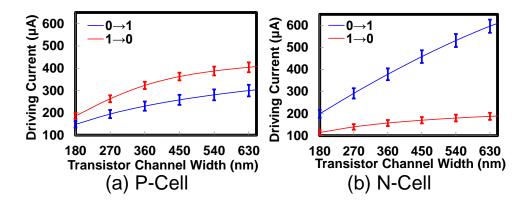

| 30 | MTJ switching current vs. NMOS transistor size. (a) P-cell. (b) C-cell                 | 56 |

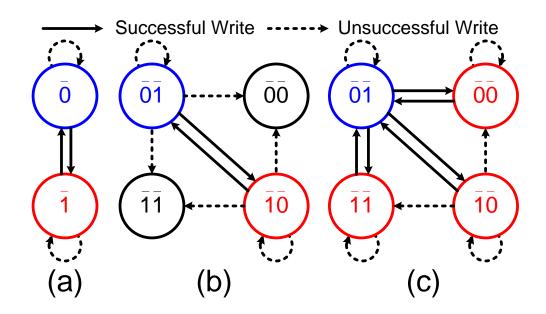

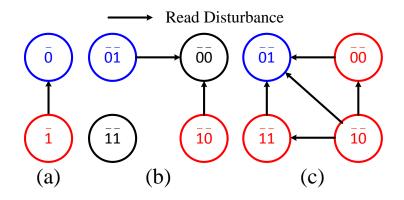

| 31 | STT-RAM writing state. (a) 1T1J. (b) RDAMS. (c) ADAMS                                  | 57 |

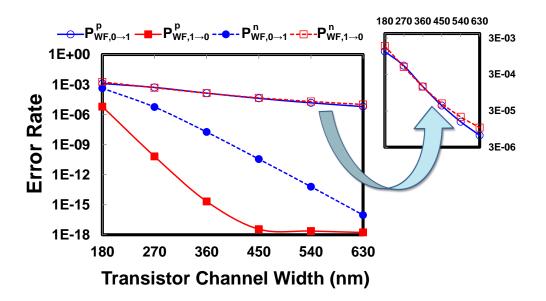

| 32 | Write error rate at 10ns write pulse width.                                            | 58 |

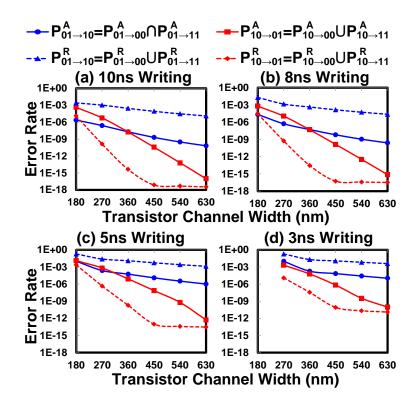

| 33 | Write error rates of the RDAMS and ADAMS cells when the write pulse width is           |    |

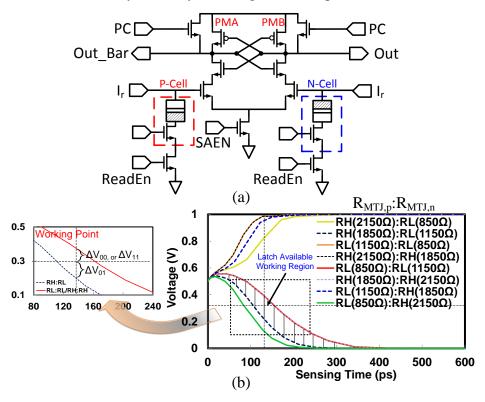

|    | set to (a) 10ns; (b) 8ns; (c) 5ns; and (d) 3ns                                         | 59 |

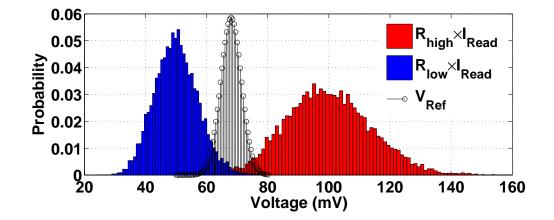

| 34 | Example of BL voltages distribution of a 1T1J cell                                     | 60 |

| 35 | STT-RAM reading state. (a) 1T1J. (b) RDAMS. (c) ADAMS                                  | 61 |

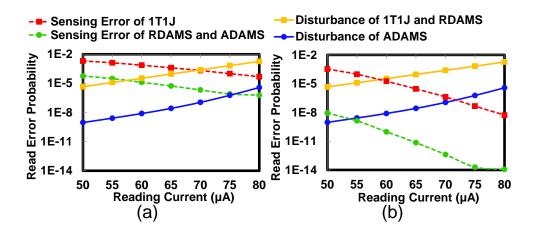

| 36 | Sensing errors and disturbance errors of different cell structures. (a) Without redun- |    |

|    | dancy. (b) With 3% redundancy.                                                         | 63 |

| 37 | (a) Latency distribution of SenAmps. (b) SenAmp latency, latch latency and total       |    |

|    | read latency of the ADAMS cell.                                                        | 65 |

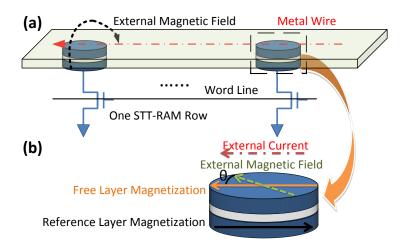

| 38 | (a) 3D view of FA-STT scheme. (b) MTJ intermediate resistance state generation.        | 67 |

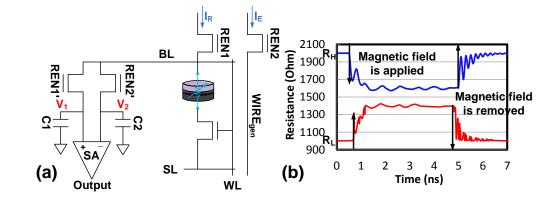

| 39 | (a) Self-reference circuit design. (b) MTJ resistance during read operation            | 68 |

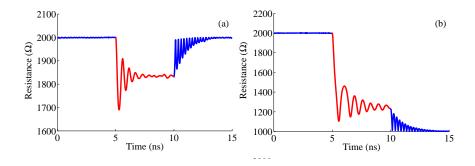

| 40 | (a) Intermediate state generation. (b) Read disturbance of intermediate state          | 70 |

| 41 | (a) MTJ resistance changes in reading '0'. (b) MTJ resistance changes in reading '1'.  | 71 |

| 42 | MTJ resistance change under different magnetic field applying speed                    | 71 |

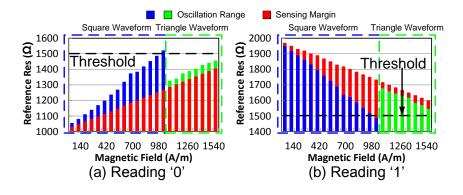

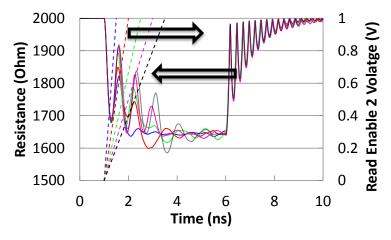

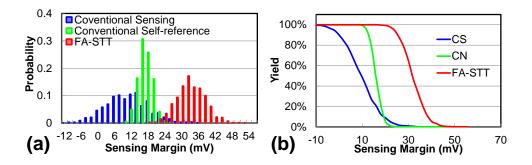

| 43 | (a) Sensing margin distributions. (b) Memory yields under different sensing margins.   | 72 |

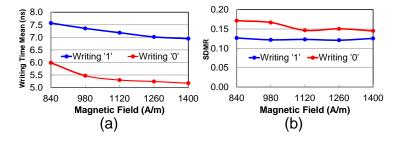

| 44 | (a) The mean of MTJ switching time vs. the magnetic field. (b) The SDMR of MTJ         |    |

|    | switching time vs. the magnetic field.                                                 | 73 |

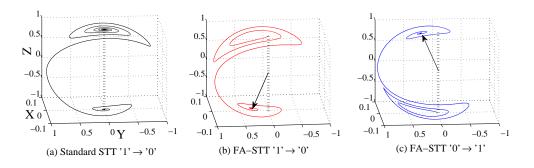

| 45 | The motion behavior of MTJ free layer magnetization: (a) the standard STT-RAM          |    |

|    | $1 \rightarrow 0$ ; (b) FA-STT $1 \rightarrow 0$ ; and (c) FA-STT $0 \rightarrow 1$    | 75 |

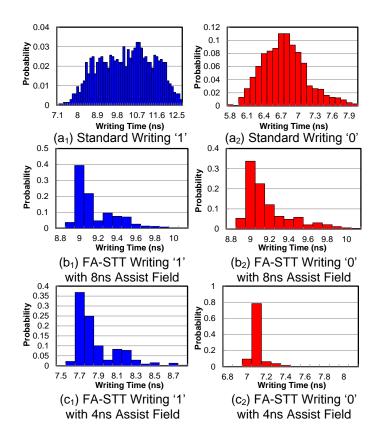

| 46 | The write time distributions.                                                          | 75 |

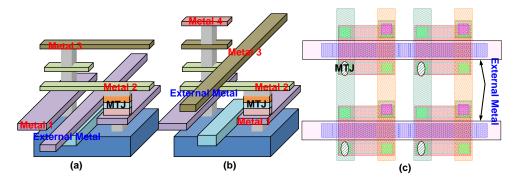

| 47 | 3D View of External Metal Placing.                                                     | 78 |

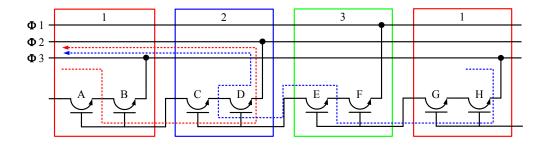

| 48 | Examples of Basic Logic Functions. (a) Serial Connection, (b) Parallel Connection.     | 79 |

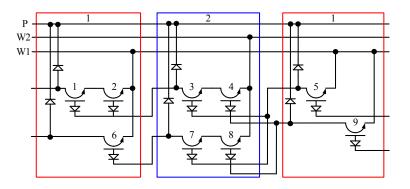

| 49 | (a) Circuit of Three-stage Operation Scheme, (b) Control Signal Diagram.               | 81 |

| 50 | An example of a real case where current sneaks through undesired paths                 | 82 |

| 51 | Proposed Diode-GSHE Structure.                                                         | 83 |

| 52 | Example of Diode-GSHE Based Full Adder.                                                | 85 |

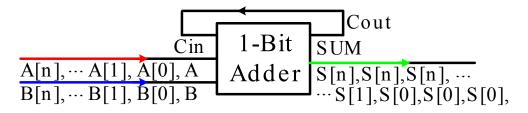

| 53 | N-bit Adder Structure basd on 1-bit Adder.                      | 85 |

|----|-----------------------------------------------------------------|----|

| 54 | Dynamic Power Consumption Under 22nm, 34nm, and 45nm tech nodes | 86 |

#### PREFACE

Among many people who helped me with this work, I first thank my advisor, Dr. Yiran Chen, for his relentless support throughout the entire duration of my graduate research, which forms the foundation of this dissertation. It was him who invited me to his excellent research group in which I initiated my first research project and have been actively participated during my PhD program. His instructive advice helped me to build my research experiences from ground up and follow the right direction since then. His strong enthusiasm motivates me to concentrate on my high performance computing research. Without his help, I could have never done this work.

Second, I would like to thank Dr. Hai Li, who has co-advised my research work for over five years of my graduate study. Her encouragement at the early stage of my work made me feel warm and helped me through the hard times. It was from her words I gained the confidence to pursue a PhD degree. Her patient guidance and directions not only helped me to conquer the difficulties I have experienced in my research work but also equipped me with valuable capabilities necessary for conducting research. From her, I have learned many useful techniques including presentation/reasoning skills, academic paper writing, research idea formulating, etc.

I also thank Professor Ching-Chung Li, Professor Ervin Sejdic and Professor Mingui Sun for being on my program committee and giving me constructive advice on this dissertation. I highly appreciate their time spent on reviewing the dissertation.

#### **1.0 INTRODUCTION**

Conventional memory technologies, i.e., SRAM, DRAM, and Flash, have achieved a remarkable success in modern electronic industry. As the semiconductor fabrication technology approaches 20nm range, the disadvantages of those technologies has become more and more prominent, i.e., the high leakage power of SRAM and DRAM, the poor endurance performance of NAND Flash, and the generally degraded device reliability. Hence, the research on emerging memory technologies have been triggered to look for alternative process scaling paths. As a promising candidate, spin-transfer torque random access memory (STT-RAM) aims the embedded memory and on-chip cache applications [27, 36, 41]. In an STT-RAM cell, data is stored as the resistance states of a magnetic tunneling junction (MTJ) device [8]. Compared to other competing technologies such as Phase-Change RAM (PCRAM), Resistive RAM (RRAM) and Ferromagnetic RAM (FeRAM), STT-RAM offers faster (nanoseconds) read access time, better CMOS process compatibility, as well as the common properties such as zero standby power, small memory cell size, and good scalability etc. [25].

As technology scales, the STT-RAM density and power consumption improve, followed by the increased process variations. The impacts of the process variations on STT-RAM cell designs, including the MOS transistor device variations, MTJ geometry and resistance variations, have been analyzed by [33, 17]. Meanwhile, the intrinsic device operating uncertainties of STT-RAM, i.e., the thermal fluctuation in the MTJ switching, is aggravated when the working temperature varies in a large range, which was also analyzed in [22]. In previous work, pure CMOS device process variation aware statistical analysis method with the consideration of the MTJ geometry variations is done in [33, 17]. And [22] has proposed some combined circuit and magnetic-level STT-RAM model that can simulate the interaction between MOS transistor and MTJ without taking into account process variations. In our work, we systematically analyze the impacts of both the

device parameter fluctuations of MTJ and transistors, and intrinsic MTJ operating uncertainties on the performances and the reliabilities of STT-RAM cells. In this work, we quantitatively study the influences of thermal fluctuation and process variation on the MTJ switching performance, and extended it from Single level cell (SLC) to multi-level cell (MLC). In Multi-level cell (MLC) STT-RAM, two MLC STT-RAM structures (parallel and serial) are analyzed. Also, by leveraging our proposed STT-RAM cell model, we establish a statistical design flow that can optimize both the persistent and non-persistent errors in STT-RAM design. Finally, two error reduction design and one improved device structure are introduced to improving the existing challenges in STT-RAM technology.

The rest of the paper is organized as follows: We briefly introduce preliminary background on STT-RAM and its variation resource in Chapter 2. In Chapter 3, we start with presenting the analysis of operation errors in single level cell (SLC) STT-RAM. Then, based on the understanding of SLC, multi-level cell (MLC) STT-RAM analysis will be demonstrated in Chapter 4. In Chapter 5, we will give a novel differential sensing design called ADAMS to reduce the read error of STT-RAM. Besides that, we will also present several other error reduction design in 6 And last is our conclusion in Chapter 7.

#### 2.0 PRELIMINARY

#### 2.1 STT-RAM BASICS

Spin-transfer torque random access memory (STT-MRAM) uses magnetic tunneling junction (MTJ) devices to store the information. A MTJ has two ferromagnetic layers (FL) and one oxide barrier layer (BL). The resistance of MTJ depends on the relative magnetization directions (MDs) of the two FLs. When their MDs are parallel or anti-parallel, the MTJ is in its low or high resistance state, as illustrated in Fig. 1.  $R_h$  and  $R_l$  are usually used to denote the high and the low MTJ resistance, respectively. Tunneling magneto-resistance (TMR) is defined as  $(R_h - R_l)/R_l$ , which presents the distinction between the two resistance states.

In a MTJ, the MD of one FL (reference layer) is pinned while the one of the other FL (free layer) can be flipped by applying a polarized write current though the MTJ. For example, the switching from low resistance state ("0") to high resistance state ("1") can be realized by applying a current from B to A, as shown in Fig. 1. A larger write current can shorten the MTJ switching time by paying the additional memory cell area overhead: In the popular "1T1J" (one-transistor-one-MTJ) cell structure (see Fig. 1(c)), the MTJ write current is supplied by the NMOS transistor. Increasing the write current requires a larger NMOS transistor. Also, the increased write current raises the breakdown possibility of the MTJ device.

#### 2.2 PROCESS VARIATIONS

The CMOS process variations that contribute to the variability of the driving strength of the NMOS transistor in an "1T1J" STT-RAM cell structure include random dopant fluctuations (RDFs), line-

Figure 1: MTJ Structure (a) Anti-parallel (high resistance state). (b) Parallel (low resistance state).(c) 1T1J STT-RAM cell structure.

edge roughness (LER), shallow-trench isolation (STI) stress, and the geometry variations of transistor channel length/width. Besides the geometry variations, most of the CMOS process variations are reflected as the threshold voltage deviations. The random variation of the threshold voltage is prominent in the scaled CMOS technology and can severely affect circuit stability and performance. It is known that the relative deviations of MOS transistor parameters reduce when the transistor size increases.

CMOS process variations affect not only the driving strength of the MOS transistor but also its equivalent resistance. The relative deviations of MOS transistor parameters reduce when the transistor size increases. The major sources of MTJ device variations include: 1) MTJ shape variations; 2) MgO thickness variations; and 3) normally distributed localized fluctuation of magnetic anisotropy  $K = M_s \cdot H_k$  [25]. The first two factors cause the variations of the MTJ resistance and the MTJ switching current by changing the bias conditions of the NMOS transistor. The third factor is the intrinsic variation of magnetic material that affects the MTJ switching threshold current density (Eq. 2.1) and the magnetization stability barrier height (Eq. 2.2) [25].

$$J_{C0} = \left(\frac{2e}{\hbar}\right)\left(\frac{\alpha}{\eta}\right)\left(t_F M_s\right)\left(H_k \pm H_{ext} + 2\pi M_s\right)$$

(2.1)

$$\Delta = \frac{K_u V}{k_B T} = \frac{M_s H_k V \cos^2(\theta)}{k_B T}$$

(2.2)

Here, the switching threshold current density  $J_{C0}$  is the minimal current density that causes the MTJ resistance flipping in the absence of any external magnetic field at 0K; *e* is the electron charge;  $\alpha$  is the damping constant;  $M_s$  is the saturation magnetization;  $t_F$  is the thickness of the free layer;  $\hbar$  is the reduced planck's constant;  $H_k$  is the effective anisotropy field including magneto crystalline anisotropy and shape anisotropy;  $H_{ext}$  is the external field;  $\eta$  is the spin transfer efficiency; T is working temperature;  $K_B$  is Boltzmann constant; and V is MTJ element volume.

#### 2.3 THERMAL FLUCTUATION IN MTJ SWITCHING

Device variations are introduced by the uncertainties during the manufacturing process. After the device is fabricated, the device parameters are fixed and their impacts on the circuit performance are deterministic. Besides the device variations of MOS transistor and MTJ, the MTJ switching performance is also affected by the intrinsic thermal fluctuations. In general, the impact of thermal fluctuations can be modeled by the thermal induced random field  $h_{fluc}$  in stochastic Landau-Lifshitz-Gilbert (LLG) equation (Eq. 2.3) [8, 2, 9] as

$$\frac{d\vec{m}}{dt} = -\vec{m} \times (\vec{h}_{eff} + \vec{h}_{fluc}) + \alpha \vec{m} \times (\vec{m} \times (\vec{h}_{eff} + \vec{h}_{fluc})) + \frac{\vec{T}_{norm}}{M_s}$$

(2.3)

Where  $\vec{m}$  is the normalized magnetization vector. Time *t* is normalized by  $\gamma M_s$ ;  $\gamma$  is the gyromagnetic ratio and  $M_s$  is the magnetization saturation.  $\vec{h}_{eff} = \frac{\vec{H}_{eff}}{M_s}$  is the normalized effective magnetic field.  $\vec{h}_{fluc}$  is the normalized thermal agitation fluctuating field at finite temperature which represent the thermal fluctuation.  $\alpha$  is the LLG damping parameter.  $\vec{T}_{norm} = \frac{\vec{T}}{M_s V}$  is the spin torque term with units of magnetic field. And the net spin torque  $\vec{T}$  can be obtained through microscopic quantum electronic spin transport model. Under the intrinsic thermal fluctuations, the MTJ switching time becomes unrepeatable and follows a distribution. As we shall show in the next Section, this distribution is also affected by the MTJ and NMOS transistor device variations and causes the asymmetric STT-RAM cell switching at two switching directions.

#### 3.0 SINGLE-LEVEL CELL OPERATION ANALYSIS

#### 3.1 WRITE ERRORS OF AN STT-RAM CELL

STT-RAM errors mainly include two types – operational error and retention error. In this paper, we mainly focus on the the operational error as normally the STT-RAM is designed with very high retention time to cover the concerned storage time span, e.g., 10 years. Based on the occurrence behaviors, operational errors of an STT-RAM cell can be further divided into two types: persistent error and non-persistent error. In memory design, persistent errors denote the errors that happen deterministically and can be repeated after the chip is fabricated. On the contrary, non-persistent errors denote the transient failures incurred by intermittent events and cannot be repeated deterministically.

#### 3.1.1 Persistent Errors

The persistent error in STT-RAM write is referred to as the errors incurred by insufficient MTJ write current and MTJ switching threshold current variation, which are induced by the process variations of the NMOS transistor and the MTJ, respectively.

**3.1.1.1 Geometry Variations of Transistor and MTJ** Without considering any power rail bounces, when programming an STT-RAM cell, the write current through the MTJ is mainly determined by the size of the NMOS transistor and the MTJ resistance. The first order approximation of the MTJ write current deviation generated from the process variations W (transistor channel width), L (transistor channel length),  $V_{th}$  (threshold voltage), and  $R_{MTJ}$  (equivalent resistance of

| Device     | Parameters                        | Mean                | Std. Dev.              |

|------------|-----------------------------------|---------------------|------------------------|

|            | Channel Length L                  | 45nm                | 2.25nm                 |

| Transistor | Channel Width W                   | design dependent    | 2.25nm                 |

|            | Threshold Voltage V <sub>th</sub> | 0.466V              | $\delta V_{th0}$ =30mV |

|            | MgO Thickness $	au$               | 2.2nm               | 2% of mean             |

|            | Cross Section A                   | $40 \times 90 nm^2$ | 5% of mean             |

| MTJ        | Perpendicular CS $A_P$            | $45 \times 45 nm^2$ | 570 OF Incan           |

|            | Low Resistance $R_l$              | 2000Ω               |                        |

|            | High Resistance $R_h$             | 4500Ω               |                        |

#### Table 1: Summary of Device Parameters

MTJ) can be expressed as:

$$(\sigma I_{MTJ})^{2} = \left(\frac{\sigma I_{MTJ}}{\sigma W} |_{W=W_{0}} \sigma W\right)^{2} + \left(\frac{\sigma I_{MTJ}}{\sigma L} |_{L=L_{0}} \sigma L\right)^{2} + \left(\frac{\sigma I_{MTJ}}{\sigma V_{th}} |_{V_{th}=V_{th0}} \sigma V_{th}\right)^{2} + \left(\frac{\sigma I_{MTJ}}{\sigma R_{MTJ}} |_{R_{MTJ}=R_{MTJ0}} \sigma R_{MTJ}\right)^{2}.$$

(3.1)

Here  $W_0$ ,  $L_0$  and  $V_{th0}$  are the nominal values of NMOS transistor width, length and threshold voltage, respectively. The standard variation of the threshold voltage  $V_{th}$  decreases when the transistor size increases, say,  $\sigma V_{th} \propto 1/\sqrt{WL}$ . In this work, we select PTM 45nm technology as our reference technology node in the simulations. Assuming a high-performance NMOS transistor is used,  $\sigma V_{th0}$ is set to 30mV with the mean of channel length  $L_0 = 45$  nm [37]. The standard deviations of W and L ( $\sigma$ W and  $\sigma$ L) are both set to 5% of the minimal transistor length (= 45*nm*). The details of the parameters adopted in our simulations are summarized in TABLE 1.

The MTJ resistance  $R_{MTJ} \propto e^{\tau}/A$ , where  $\tau$  is the tunneling oxide thickness and A is the MTJ surface area. The variations of both  $\tau$  and A follow Gaussian distributions [17].  $\Delta V_{MTJ} = I_{MTJ} \cdot R_{MTJ}$  is the voltage drop across the MTJ where  $I_{MTJ}$  is the current through the MTJ. Hence,  $V_{ds} = V_{dd} - \Delta V_{MTJ}$  is a function of  $I_{MTJ}$ .

Based on the recent experimental results in [7], in our simulations, we choose the nominal values of  $R_L$  and  $R_H$ , or  $R_{L0}$  and  $R_{H0}$  as 2000 $\Omega$  and 4500 $\Omega$ , respectively. We also assume that the standard deviations of  $\tau$  and A are 2% or 5% of their means [17], as shown in TABLE 1.

The MTJ size are modeled by the equations from [40] as:

$$H_K = M_S (N_b - N_a).$$

(3.2)

$$N_a = \frac{4\pi}{m^2 - 1} \left[ \frac{m}{\sqrt{m^2 - 1}} ln(m + \sqrt{m^2 - 1}) - 1 \right].$$

(3.3)

$$N_b = 2\pi - \frac{N_a}{2}.$$

(3.4)

$$m = \frac{a}{b}.$$

(3.5)

Here *a* and *b* are the length and width of the MTJ nanopillar.  $N_a$  and  $N_b$  are the demagnetization factor along the longer a-axis and shorter b-axis, respectively. In a perpendicular MTJ, there is no shape anisotropy since a = b,  $N_a = N_b$ .

Meanwhile, we assume the variations of MTJ and CMOS devices are independent because these two types of devices are fabricated at different layers with different processes.

**3.1.1.2 Fluctuation of Magnetic Anisotropy** Different from CMOS device variations and MTJ geometry variations that directly affecting MTJ write current, localized fluctuation of MTJ magnetic anisotropy results in the variations of switching threshold current density  $J_{C0}$ . In the concerned MTJ switching time range (from a few *ns* to hundreds *ns*), our magnetic model shows that the fluctuation of MTJ magnetic anisotropy causes a standard deviation of the MTJ switching threshold current density about 2% of its nominal value.

| Transistor | $V_{\rm e}(V)$ | Nominal          | $0 \rightarrow 1S tand$ | lardDeviatio | $n(\mu A)$ | $0 \rightarrow 1S tand$ | lardDeviatio | n/Mean |

|------------|----------------|------------------|-------------------------|--------------|------------|-------------------------|--------------|--------|

| Size       | $V_{ds}(V)$    | $I_{MTJ}(\mu A)$ | MOS only                | MTJ only     | Both       | MOS only                | MTJ only     | Both   |

| 90nm       | 0.8498         | 75.12            | 7.53                    | 1.01         | 7.61       | 10.03%                  | 1.35%        | 10.13% |

| 180nm      | 0.7685         | 115.7            | 10.61                   | 3.12         | 11.11      | 9.17%                   | 2.70%        | 9.60%  |

| 270nm      | 0.7201         | 139.9            | 11.63                   | 4.84         | 12.87      | 8.31%                   | 3.46%        | 9.20%  |

| 360nm      | 0.6877         | 156.1            | 12.46                   | 5.71         | 14.02      | 7.98%                   | 3.66%        | 8.98%  |

| 450nm      | 0.6643         | 167.8            | 12.71                   | 7.25         | 14.72      | 7.64%                   | 4.32%        | 8.77%  |

| 540nm      | 0.6465         | 176.7            | 12.77                   | 8.25         | 15.20      | 7.23%                   | 4.67%        | 8.60%  |

| 630nm      | 0.6323         | 183.8            | 12.83                   | 9.02         | 15.68      | 6.98%                   | 4.91%        | 8.53%  |

| 720nm      | 0.6208         | 189.6            | 12.93                   | 9.61         | 16.10      | 6.82%                   | 5.07%        | 8.49%  |

| Transistor | $V_{\star}(V)$ | Nominal          | $1 \rightarrow 0S tand$ | lardDeviatio | $n(\mu A)$ | $1 \rightarrow 0S tand$ | lardDeviatio | n/Mean |

| Size       | $V_{ds}(V)$    | $I_{MTJ}(\mu A)$ | MOS only                | MTJ only     | Both       | MOS only                | MTJ only     | Both   |

| 90nm       | 0.5629         | 97.15            | 9.08                    | 0.39         | 9.09       | 9.35%                   | 0.40%        | 9.36%  |

| 180nm      | 0.2893         | 157.9            | 10.27                   | 1.37         | 10.35      | 6.50%                   | 0.87%        | 6.55%  |

| 270nm      | 0.1914         | 179.7            | 9.64                    | 4.07         | 10.42      | 5.36%                   | 2.26%        | 5.80%  |

| 360nm      | 0.1431         | 190.4            | 8.42                    | 6.37         | 10.46      | 3.73%                   | 2.86%        | 4.42%  |

| 450nm      | 0.1143         | 196.8            | 7.18                    | 7.75         | 10.57      | 3.65%                   | 3.94%        | 5.20%  |

| 540nm      | 0.0952         | 201.1            | 3.90                    | 10.03        | 10.23      | 1.48%                   | 4.99%        | 5.37%  |

| 630nm      | 0.0815         | 204.1            | 2.84                    | 10.96        | 11.31      | 1.39%                   | 5.37%        | 5.54%  |

| 720nm      | 0.0713         | 206.4            | 2.77                    | 11.53        | 11.85      | 1.34%                   | 5.59%        | 5.74%  |

Table 2: MTJ Write Current Distribution Under Process Variations

#### 3.1.2 Quantitative Analysis on Persistent Write Errors

We perform Monte-Carlo simulations to quantitatively study the persistent write errors in STT-RAM cell design with PTM 45nm technology [3]. A Verilog-A MTJ model was created for process variation analysis and the assumptions of the process variations are listed in TABLE 1. All simulations were conducted under Cadence Spectre Analog environment.

Three scenarios are simulated to study the impacts of different process variation sources on the driving ability of the NMOS transistor in STT-RAM cells with different transistor sizes, including:

- 1. Case 1 (MOS variation only): Assuming no MTJ geometry variations and only NMOS transistor process variations are considered;

- Case 2 (MTJ variation only): Assuming no NMOS transistor process variations and only MTJ geometry variations are considered;

- 3. Case 3 (Both Variations): Both MTJ and NMOS transistor process variations are considered.

TABLE 2 summarizes our simulation results. For every cases,  $V_{dd} = 1.0V$ . Both MTJ switching directions (parallel to anti-parallel, or '0 $\rightarrow$ 1' and anti-parallel to parallel, or '1 $\rightarrow$ 0') are simulated because the NMOS transistor has different biasing conditions at these two switching directions. For every simulated transistor size, 1000 Monte-Carlo simulations are conducted.

In "MOS variation only" case, when the MTJ switches from '0' to '1', the NMOS transistor always works at its saturation region. Increasing transistor width W reduces the NMOS transistor resistance as well as the  $V_{ds}$ . However, the reduction of  $V_{ds}$  is very moderate even all the coefficients corresponding to each transistor process variations in Eq. (3.1) become larger. It leads to a larger standard deviation of MTJ write current even though the variations of  $V_{th}$  decreases. In the case that MTJ switches from '1' to '0', the NMOS transistor works at saturation region first when its width is small. However, following the increase of the channel width, NMOS transistor will change its working region from saturation to linear.  $V_{ds}$  reduces very sharply (even possibly below  $V_{th}$ ), as shown in TABLE 2. Combining with the decrease of  $\sigma V_{th}$ , the coefficients of transistor process variations in Eq. (3.1) reduce when the transistor width increases.

In "MTJ variation only" case, the coefficient of MTJ variation in Eq. (3.1) always increases when transistor size (and hence,  $I_{MTJ}$ ) increases. Moreover, because of the higher  $I_{MTJ}$ , a larger MTJ write current variation is induced by MTJ variations in 1 $\rightarrow$ 0' switching compared to '0 $\rightarrow$ 1' switching under the same NMOS transistor size. Due to the same reason (and also the reduction of  $\sigma V_{th}$ ), the MTJ variation induced MTJ write current deviation becomes more prominent when the NMOS transistor size becomes larger.

When both the MTJ and NMOS transistor variations are considered, the contributions of different device variations to the MTJ driving current are mainly represented by the following four terms in Eq. (3.1) as [34]:

$$S_{1} = \left(\frac{\partial I}{\partial W}\right)^{2} \cdot \sigma_{W}^{2}, S_{2} = \left(\frac{\partial I}{\partial L}\right)^{2} \cdot \sigma_{L}^{2},$$

$$S_{3} = \left(\frac{\partial I}{\partial R}\right)^{2} \cdot \sigma_{R}^{2}, S_{4} = \left(\frac{\partial I}{\partial v_{th}}\right)^{2} \cdot \sigma_{v_{th}}^{2}.$$

(3.6)

|       | Variation             | Monoto       | $W \to \infty$      |

|-------|-----------------------|--------------|---------------------|

|       | $S_1$                 | $\downarrow$ | $S_1 \rightarrow 0$ |

|       | $S_2$                 | $\nearrow$   | $S_2 \rightarrow 0$ |

|       | <i>S</i> <sub>3</sub> | 1            | $\max S_3$          |

|       | $S_4$                 | $\nearrow$   | $S_4 \rightarrow 0$ |

|       | $S_1$                 | $\downarrow$ | $S_1 \rightarrow 0$ |

| ,,1,, | <i>S</i> <sub>2</sub> | 1            | $\max S_2$          |

|       | <i>S</i> <sub>3</sub> | 1            | $\max S_3$          |

|       | <i>S</i> <sub>4</sub> | $\nearrow$   | $S_4 \rightarrow 0$ |

Table 3: Summary of Variation Contribution [34]

Based on short-channel BSIM model [34], the MTJ driving current supplied by a NMOS transistor working in saturation region can be calculated by:

$$I = \frac{\beta}{1 + \frac{1}{v_{sat}L} (V_{dd} - IR)} \cdot \left[ (V_{dd} - V_{th}) (V_{dd} - IR) - \frac{a}{2} (V_{dd} - IR)^2 \right].$$

(3.7)

Here  $\beta = \mu_0 C_{ox} \frac{W}{L}$ ,  $\mu_0$  is electron mobility,  $C_{ox}$  is gate oxide capacitance per unit area, *a* is body-effect coefficient, and  $v_{sat}$  is carrier velocity saturation.

TABLE 3 shows the changing trends of  $S_1$  to  $S_4$  at both switching directions when the transistor channel width W increases. For each  $S_i$  ( $i = 1 \sim 4$ ) that do not monotonically changes when W increases, a larger  $S_i$  corresponds to more contribution to the MTJ driving current variation. The limits of each  $S_i$  when W is approaching infinite are also listed in TABLE 3. It clearly shows that the residual values of  $S_1$ – $S_4$  at '0 $\rightarrow$ 1' switching is larger than that at '1 $\rightarrow$ 0' switching when  $W \rightarrow \infty$ . In other words, '0 $\rightarrow$ 1' switching suffers from a larger MTJ driving current variation than '1 $\rightarrow$ 0' switching when the NMOS transistor is large. Furthermore, the mean of the MTJ write current of ' $0\rightarrow 1$ ' switching is always lower than that of ' $1\rightarrow 0$ ' switching at all simulated transistor sizes. Therefore, the STDR (standard deviation vs. mean ratio) of the MTJ switching time of ' $0\rightarrow 1$ ' switching is always larger than that of ' $1\rightarrow 0$ ' switching.

As also shown in TABLE 2, following the increase of the NMOS transistor size, the ratio between the means of the MTJ write currents at both switching directions, i.e.,  $I_{MTJ,mean}^{0\to1}/I_{MTJ,mean}^{1\to0}$ , decreases. It is because that the driving ability of the NMOS transistor quickly saturates when  $V_{gs}$  reduces. However, the ratio between the standard deviations of the MTJ write currents, i.e.,  $\sigma_{I_{MTJ}}^{0\to1}/\sigma_{I_{MTJ}}^{1\to0}$ , slightly increases when the NMOS transistor size grows. These two trends indicate the aggravation of STT-RAM cell switching asymmetry when the NMOS transistor size increases.

Figure 2: Examples of the driving strength distribution of the NMOS transistor in the STT-RAM cell: (a)  $1\rightarrow 0$ . (b)  $0\rightarrow 1$ .

We note that the analytical expression in Eq. (3.1) is able to provide reasonable estimation on the distribution of the MTJ write current by assuming the MTJ write current follows Gaussian distribution. The results of Monte-Carlo simulation and analytical estimation of the MTJ write current distributions for the NMOS transistor with W = 270nm and 720nm, respectively, are compared in Fig. 2.

Without considering thermal fluctuations, the MTJ write current  $I_{MTJ}$  must be larger than the critical MTJ switching current  $I_C$  to ensure a successful write. However, thermal fluctuation induced operational randomness makes this statement invalid. In the next section, we will discuss the impact of thermal functions on the write reliability of STT-RAM cells.

#### 3.1.3 Non-Persistent Errors

The critical MTJ switching current at both switching directions, i.e.,  $I_{C,0\rightarrow1}$  and  $I_{C,1\rightarrow0}$ , are affected by thermal fluctuations. Thermal fluctuation is a purely random process that cannot be deterministically repeated, and induces non-persistent errors in STT-RAM operations.

**3.1.3.1 Thermal Fluctuations** Our simulation results of the MTJ switching current vs. the mean and the SDMR of the MTJ switching time are depicted in Fig. 3. The original device parameters are extracted from a 40nm×90nm elliptical MTJ device and have been carefully scaled to the 45nm technology. The results of both switching directions are included.

Since the switching process of a MTJ can be categorized into three working regions based on its switching time range, different fitting equations are generated for each time range as follows: For a long switching time (> 10ns):

$$I_{C1}(t_w) = I_{C0}(1 - (1/\Delta)ln(t_w/\tau_0)).$$

(3.8)

Here,  $t_w$  is switching time;  $\tau_0$  is relaxation time.

For an ultra-short switching time (< 3ns):

$$I_{C3}(t_w) = I_{C0} + C \ln(\pi/2\theta).$$

(3.9)

Figure 3: (a) Switching current vs. Switching time mean. (b) Switching time mean vs. SDMR (Switching time standard deviation/Mean Ratio).

Here C is a fitting parameter,  $\theta$  is the initial angle between the magnetization vector and the easy axis, n is a fitting parameters.

When the MTJ switching time is in the intermediate region  $(3ns < t_w < 10ns)$ , a dynamic reversal that combines the precessional and thermally activated switching occurs [8]. Based on the simulation results of our macro-magnetic model, we derive a fitting function of the critical MTJ switching current  $I_{C2}$  for this time range as:

$$I_{C2}(t_w) = 30(I_{C3}(3n) - I_{C1}(10n))/t_w + (10I_{C3}(3n) - 3I_{C1}(10n))/7.$$

(3.10)

Fig. 3(a) shows the simulation results of the means of the MTJ switching current and the nominal switching time in both '1 $\rightarrow$ 0' (red) and '0 $\rightarrow$ 1' (blue) switching's using the same MTJ configuration in the previous simulations. Thermal fluctuation influences the MTJ magnetic switching process and causes the variations of MTJ switching time. When MTJ is operating in a relatively long time region (> 10ns), thermal fluctuation is dominated by the thermal component of internal energy; when MTJ working in a short time region (< 10ns), thermal fluctuation is dominated by the thermal fluctuation is dominated by the thermally active initial angle of procession [37].

Under a certain threshold write current, the MTJ write latency is not fixed but suffers from the thermal fluctuation induced variations. This uncertainty may cause unsuccessful writes if the MTJ device fails to switch before the write pulse is removed. Fig. 3(b) shows the distribution of MTJ switching time at both '1 $\rightarrow$ 0' and '0 $\rightarrow$ 1' switching's. The distinction between the means of MTJ switching time at two switching directions with the same switching current can be explained as the asymmetric impacts of tunneling spin polarization *P* and follows:

$$\frac{J_{C0}^{0\to1}}{J_{C0}^{1\to0}} = \frac{1+P^2}{1-P^2}.$$

(3.11)

Here  $J_{C0}^{0\to 1}$  and  $J_{C0}^{1\to 0}$  denotes the MTJ switching threshold current density at the switching of '0 $\rightarrow$ 1' and '1 $\rightarrow$ 0', respectively.

The difference in the standard deviations of the MTJ switching time at two switching directions, however, is caused by the asymmetric influences of thermal agitation fluctuating field  $\vec{h}_{fluc}$ . A larger MTJ switching time deviation is observed in '0 $\rightarrow$ 1' switching than '1 $\rightarrow$ 0' switching.

We found when the MTJ works at a long switching time range (>40ns, or switched by a low current), the standard deviation of the MTJ switching time for both switching directions are high. Following the decrease of the MTJ switching time, the standard deviation of the MTJ switching time reduces first and then raises again. It is due to the reduced thermal impacts and the increased impact of the spin torque term  $\vec{T}_{norm}$  on MTJ switching under a high switching current. In general, when the nominal MTJ switching time decreases, its standard deviation decreases first and then increases. The minimal SDMR of the MTJ switching time occurs around  $t_w = 10ns$ .

Figure 4: Perpendicular MTJ. (a) Switching current vs. Switching time mean. (b) Switching time mean vs. SDMR.

As aforementioned, PMTJ has a lower switching threshold current density than in-plane MTJ. Similar to Fig. 3, the simulation results of the nominal switching current and the SDMR of the switching time for a 65nm×65nm PMTJ are illustrated in Fig. 4(a) and Fig. 4(b), respectively. Here the size of the PMTJ is adopted from [7], which does not choose the minimal pitch of the technology node due to other circuit design concerns. Compared to in-plane MTJ, PMTJ significantly reduces the requirement of switching current due to the smaller switching threshold current density. The switching current difference between writing '1' and writing '0' also becomes smaller, indicating that PMTJ has a more symmetric switching performance. However, writing '1' ( $^{\circ}O\rightarrow$ 1', blue line) still requires a larger current than writing '0' ( $^{\circ}1\rightarrow$ 0', red line). On the other hand, PMTJ comes with a much smaller switching time variation though its changing trend is the same as that of in-plane MTJ. In general, the SDMRs of the switching time of PMTJ at both MTJ switching directions are very close: writing '1' has a slightly larger switching time variation then writing '0' ( $^{\circ}$

when the write current is small due to the asymmetric thermal effect on perpendicular anisotropy. Nonetheless, compared to in-plane MTJ, PMTJ has a better balanced switching performance at different directions.

Figure 5: (a) MTJ Critical Switching Current vs. Switching Time under Varying Temperature, (b)Threshold Switching Time against Temperature.

**3.1.3.2 Temperature Dependency** The switching performance of a MTJ improves when working temperature raises. Higher temperature degrades the magnetization stability barrier height (Eq. 2.2) and reduces the critical MTJ switching current and/or the switching time. Fig. 5(a) shows the relationship between the critical MTJ switching current and the switching time under different temperatures for the adopted PMTJ. The impacts of temperature variations are more significant in long working time region: the thermal impact on the MTJ switching performance is more prominent when the MTJ switching current is low, compared to the impact of spin-torque.

We also simulated the temperature sensitivity of the nominal switching time of the MTJ driven by the NMOS transistor with different sizes, as shown in Fig. 5(b). Only the mean values of the switching performances are analyzed with temperature variation. The MTJ switching time increases when the temperature raises. Since the driving ability of NMOS transistors becomes worse when operating in a high temperature environment, the result actually indicates that the improvement of MTJ magnetic switching performance cannot compensate the driving ability loss of the NMOS transistor when the working temperature increases.

Figure 6: (a) Error Rate for 10ns Write Pulse Width, (b) Error Rate for 20ns Write Pulse Width, (c) 1% and 0.1% error rate of writing '1'.

#### 3.1.4 Statistical Write Error Rate Analysis

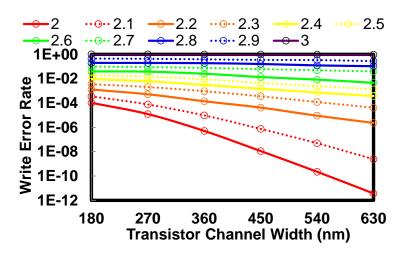

The write error rate of an STT-RAM cell can be defined as the probability that the write access to the STT-RAM cell cannot complete within a certain write pulse width. Thus, a Monte-Carlo simulation is conducted by generating 1,000 STT-RAM cell driving ability samples (reflecting the persistent errors) and 1,000 MTJ switching time sampling for thermal fluctuation simulations (modeling the non-persistent errors) on each sample of the STT-RAM cell driving ability.

Fig. 6(a) and Fig. 6(b) shows our simulation results of STT-RAM cell write error rates for both writing "1" and "0" at 300K, when the write pulse width is set at 10ns and 20ns, respectively. Except for the ambient temperature, all other aforementioned variation sources, including the device variations of NMOS transistor and MTJ and the thermal fluctuations are taken into account in our simulations. Increasing the transistor size can effectively suppress write error rate by raising the MTJ write current. Due to the asymmetric cell structure, the NMOS transistor provides less current to the MTJ during '0 $\rightarrow$ 1' switching than '1 $\rightarrow$ 0' switching. However, '0 $\rightarrow$ 1' switching requires higher MTJ switching current than '1 $\rightarrow$ 0' switching, and becomes the limiting factor of write error rate. The effectiveness of sizing up the NMOS transistor for error rate reduction degrades when the transistor size is large because the NMOS driving ability becomes saturated due to the reduced  $V_{ds}$ .

Fig. 6(c) shows the required write pulse width (MTJ switching time) for the write error rates of 1% and 0.1% when the NMOS transistor size varies. For comparison purpose, the ideal results based on the nominal device parameters without considering thermal fluctuations are also presented. Significant differences are observed between the ideal and the actual performance of the MTJ: the required write pulse width when the variations are considered can be multiple times longer than the ideal result, depending on the targeted error rate.

Figure 7: In-plane and perpendicular STT-RAM write error rate comparison under 10ns write pulse width.

We also simulated write error rate of perpendicular STT-RAM cells. Fig. 7 shows write error rates of both in-plane STT-RAM and perpendicular STT-RAM under a 10ns write pulse width. Since the required switching current of perpendicular STT-RAM cell is much less than that of in-plane STT-RAM cell, under the same transistor size, the write error rate of perpendicular STT-RAM is much smaller than the one of in-plane STT-RAM. To maintain a certain level write error rate, perpendicular STT-RAM can achieve a much higher cell density than in-plane STT-RAM.

#### 3.1.5 Array Level Analysis

Variabilities in STT-RAM cell, e.g., geometry variations of transistor and MTJ size, occurs in both random and systematic sources. Systematic variations usually demonstrate strong spatial correlations, that means the neighbour cell variation are much smaller than two cells far apart.

In this section, we use VARIUS to generate distributions of variabilities of STT-RAM array [26] with spatial correlations. Both inter-die and intra-die variations are considered. Particularly, the inter-die variation is reflected as the fluctuation of the mean value of the variability ( $\mu_{(die)}$ )) while the intra-die variation is shown as the standard deviation ( $\sigma_{(die)}$ ) which includes all the parameters that affected by process variation, i.e.  $\sigma_W$ ,  $\sigma_L$  and  $\sigma_R$ .  $\rho$  is the spatial correlation coefficient which decreases when the distance between two cells increases. Furthermore, parameters

$\phi$  defines the maximum distance where two cell can correlate. Cells that distance between each other is longer than  $\phi$  are assumed to have no correlations. The correlation range is radius of the die, when  $\phi$  is 0.5 as in our simulation, only the cell at the center is affected by the whole die.

We repeatly ran VARIUS to generate a  $1k \times 1k$  array by using statistic tool R. The parameter set including (W, L, and  $R_{(MTJ)}$ ) of each cell in the array follows intra-die and inter-die variations, and these variations are assumed to follow Gaussian distribution.

As an example, Fig. 8 shows two generated sample sets of transistor channel length distribution map and histogram for a STT-RAM with  $\sigma_L = 0.05 * L$ ,  $and\mu(die) = 0.02 * L$ . The values of transistor channel length are represented by the color lightness: lighter color indicates longer transistor length. For example, area A has the shortest transistor channel length, which behaves a strongest driving ability, on the other hand, longest channel length happens in area B, correspondingly, area B has the worst driving ability.

Figure 8: Transistor channel length distribution map for a STT-RAM array.

To systematically calculate the array error rate, we assume that the power supply that applied to each cell is the same. Thus the error rate will only be affected by the same resources, persistent and non-persistent error as describe above. Also using transistor channel length as an example, in single cell analysis we assume that the standard deviation of 45nm is 2.25nm as shown in Table 1. Although 2% inter-die variation and spatial correlation is considered in the simulation, based on the histogram also shows in Fig. 8, the standard deviation is still 2.25nm. Since all the parameter has the same mean, and standard deviation, we can easily conclude that writing error rate will maintain the same as single cell analysis.

# 3.2 READ ERRORS OF AN STT-RAM CELL

Read operations of STT-RAM are also affected by both persistent and non-persistent variations. On the one hand, process variations of peripheral circuit (e.g., sense amplifier) and variation of equivalent resistance of NMOS transistor and MTJ affect the sensing margin of STT-RAM; On the other hand, thermal fluctuation will cause the MTJ resistance switches when read voltage/current is applied. Such a non-persistent error that randomly occurs in read operations is usually referred to as read disturbance. As a result, read errors of STT-RAM can be classified into two kinds of errors: sensing error which is persistent error and read disturbance error which is non-persistent error.

## 3.2.1 Persistent Error: Sensing Errors

In traditional current-sensing STT-RAM read scheme, for instance, a read current  $I_{read}$  is injected into the memory cell. The generated bit-line voltage is then compared to a reference voltage to read out the MTJ resistance state. The generated sense margin, which can be measured by the voltage difference between the bit-line voltage and the reference voltage, is proportional to  $I_{read} \cdot R_L \cdot TMR$ . Certain sense margin must be maintained in STT-RAM read operations to overcome the device mismatch in the sense amplifier and keep the sensing errors at a minimum level.

When  $I_{read}$  is small, the generated sense margin of STT-RAM will be very limited if the MTJ resistance and/or TMR is fixed. The degraded sense margin may incur sensing errors if the device

variation of sense amplifier is large. Since the process variations of CMOS technology become more and more severe when manufacturing technology scales, readability may replace the write failure to serve as the limiting factor of STT-RAm design reliability. It is necessary to conduct a detailed analysis on the robustness degradation of the STT-RAM read operations and explore the optimization of MTJ scaling from the readability perspective.

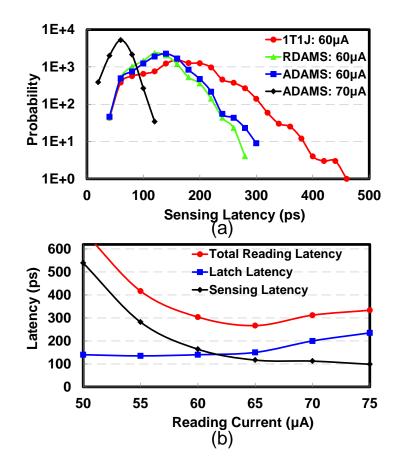

Figure 9: Probability of Sensing Error and Read Disturbance under different read current.  $T_{read} = 5ns$ .

We define the sense margin as the voltage difference actually generated on the two inputs of the sense amplifier. A large sensing margin generally implies a low sensing error rate. Because of process variations, the sense margin observed by the sense amplifier must be large enough to overcome the device mismatch in the sense amplifier.

The sensing errors occur when the voltage difference on the inputs of the sense amplifier cannot overcome the device mismatch of the circuit. The red line in Fig. 9 shows the sensing error rates of an in-plane STT-RAM cell when changing  $I_{read}$ . Here the device variations of both MTJ and NMOS transistor are included in our simulation. The adopted device parameters are shown in TABLE. 1. Following the increase of  $I_{read}$ , the sensing error rate reduces rapidly. It is because with the same  $R_L$  and TMR, increasing the  $I_{read}$  will raise the sensing margin, or say,  $I_{read} \cdot \Delta R$ .

#### 3.2.2 Non-Persistent Error: Read Disturbance

The resistance state of the MTJ may be flipped by the read current. Since the read current is usually small, the MTJ switching performance in STT-RAM read operations can be modeled by Eq. (3.8). The switching probability of the MTJ, hence, can be approximated by:

$$P_{sw} = 1 - exp\{-\frac{T_w}{\tau_0}exp[-\frac{1}{\Delta}(1 - I_{read}/I_{c0})]\}.$$

(3.12)

Eq. (3.12) clearly shows that the MTJ switching probability is a function of the critical switching current  $I_{c0}$ , the switching time  $\tau_p$ , and the applied current  $I_{read}$ . Fig. 9 also shows the simulated STT-RAM cell read disturbance rate under different read currents (the yellow line). The read disturbance quickly increases when  $I_{read}$  raises. Note that here the read current is applied for 5ns.

#### 3.2.3 Read Error Rate Analysis

It is obvious that the probability of STT-RAM read disturbance and sensing errors follow an opposite trend during STT-RAM design optimization: On the one hand, when increasing the read current or read lantency, sensing error will reduce due to the enlarged sensing margin or more robust sensing process; On the other hand, increasing the read current or read latency will also raise the occurrence probability of read disturbance. Hence, it is possible to find an optimal point that can achieve the minimum total read error rate. In general, read error rate of an STT-RAM cell can be expressed as:

$$P(Re_e) = P(Sen_e) + P(Dis_e) - P(Sen_e) \times P(Dis_e).$$

(3.13)

Here  $P(Re_e)$ ,  $P(Sen_e)$ , and  $P(Dis_e)$  represent the probability of total read error rate, sensing error rate, and read disturbance rate, respectively.

In Fig. 9, the optimum read current that achieves the minimum total read error rate  $(2.1 \times 10^{-4})$  is 70µA. Deviating from this optimum value will quickly raise either the sensing error rate or read disturbance rate.

Note that this conclusion is valid only for the sensing time of 5ns, which is the minimum sensing time that is required to charge the sense amplifier for a read current larger than 50uA. Reducing the sensing time will cause a higher requirement of sensing current.

## 3.2.4 Reading Analysis of a STT-RAM Array

Same as array level writing operation simulation, we generated a array using statistic tool R. To demonstrate the impacts of sensing margin and variation, we used a basic and popular sense amplifier design in STT-RAM arrays as shown in Fig. 10 which is shared by each column of 1k bit cells. Only conventional sensing scheme is adopted. We note that, the performance and reliability can always be further improved by a better SA design. The Sense amplifier we used here was tuned for best possible performance in typical process corner by sizing of the transistors. We also assume that the sense amplifier is placed very close to the array to reduce the affect of routing delays. Thus, for each parameter of transistor width, length and threshold voltage, a 1009 × 1009 array is generated, we pick a 1009 × 1000 matrix among the array, and using the 1*K* × 1*K* numbers as our sample array, and the rest 9 × 1*K* represents the parameter ratio of a sense amplifier. Since every column has its own sensing reference, the reference should be adjustable to have the optimize value for its own column instead of using  $\frac{R_h+R_l}{2}$  for the whole array.

Figure 10: Sense amplifier design.

A Monte Carlo simulation that can read out every bit of the entire array has been developed to systematically analysis the read error rate for STT-RAM array. To accurately model a random noise that may cause a mismatch in sense amplifier, we applied a random noise voltage (from -0.1V to 0.1V) to the output node of the sense amplifier as shown in Fig. 10. Since the simulation determine

a success read or a read failure based on whether readout result is same as the value stored in the cell, it is very difficult to differential a sensing error that is caused by a not enough sensing margin, or mismatch by noise, thus, we count both these read failure as sensing error in here. Since it is impossible to run through all the bit cells, we also assume that each cell that its sensing margin is large enough, i.e.  $\leq 30mV$ , will always perform a successful reading. We accumulated the results and calculated the final read error rate based on all the roles above.

Fig. 11 shows one Monte Carlo simulation results of a STT-RAM array that generate as above. Compare with read error in the single cell analysis, the read error is higher when the read current is small, however when the read current is increasing, the error rate is largely reduced. It is obvious that with small sensing margin, the error is also increased by the mismatch and noise of the sense amplifier. On the other hand, when sensing margin increases, and effect on amplifiers are reduced. The read error rapidly reduce since every column is compared with its own reference. Especially when spatial correlation are token into account, most of cells in each column are biased from the same direction compare with typical value. The results can be further improved by optimizing the distribution of sense amplifier connections.

Figure 11: Probability of Sensing Error and Read Disturbance in a STT-RAM array.

## 3.3 STT-RAM DESIGN SPACE EXPLORATION OF RELIABILITY OPTIMIZATION.

## 3.3.1 Oxide Layer Thickness Design Specification

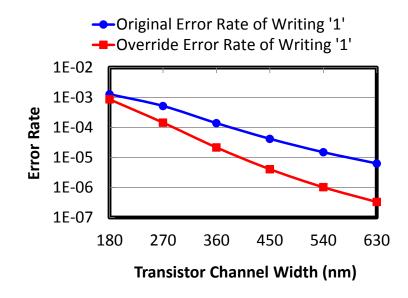

Increasing the sensing margin can enhance the read reliability of STT-RAM. As aforementioned, the sensing margin is a product of read current and MTJ resistance difference. Sec. 3.2 concludes that the read current cannot be greatly increased when read disturbance is taken into account. Hence, a more viable way to enhance the sensing margin is increasing the MTJ resistance difference.

One approach to increase the MTJ resistance difference is to raise the MTJ resistance value (i.e.,  $R_{high}$  and  $R_{low}$ ) while still maintaining the similar TMR by increasing the thickness of oxide layer. This method may reduce the write current applied to the MTJ during write operation and harm the write reliability of the STT-RAM cell (see Section 3.1). In addition, the TMR of the MTJ will slightly change with the thickness of oxide layer. Nonetheless, it has been proved that such a TMR degradation can be controlled within a small range [20]. To analyze the potential benefit of optimizing the thickness of the oxide layer in STT-RAM readability enhancement, we performed the relevant simulations by sweeping the thickness of the oxide layer from 2nm to 3nm. The corresponding TMR keeps above 100%.

Figure 12: Resistance states and resistance difference changes with oxide layer thickness.

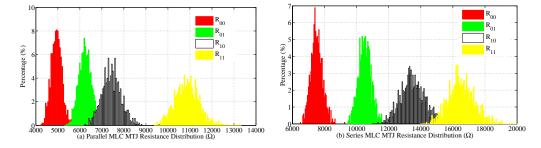

Fig. 12 shows the changes of the high and the low resistance states, and the resistance difference of the MTJ when oxide layer thickness varies. When the oxide layer thickness increases from 2nm to 3nm, the MTJ resistance can vary up to 2.78×. The resistance difference keeps increasing, well-controlled TMR degradation [38] leads to more than doubled sensing margin.

Figure 13: Sensing error rate and disturbance error rate when oxide layer thickness varies.

Although the standard deviation of the oxide layer thickness variation is smaller (2%) than that of other horizontal process variations (5%), the impact of oxide layer thickness variation on MTJ resistance is still significant because of the exponential relation between these two parameters. Fig. 13 depicts both sensing error rate and read disturbance error rate of an STT-RAM cell when the oxide layer thickness varies. Note that the read disturbance error rate is determined by the amplitude of the read current and independent on the oxide layer thickness. As a comparison, the sensing error rate is greatly reduced by increasing the oxide layer thickness, which leads to the improved MTJ resistance difference. As the process variation induced MTJ resistance variability keeps almost the same, the improved MTJ resistance difference generates larger sensing margin.

Figure 14: (a) NMOS driving ability varies with oxide layer thickness. (b) NMOS driving ability varies with transistor channel width.