Université de Toulouse

# En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut National Polytechnique de Toulouse (INP Toulouse)

Discipline ou spécialité :

Réseaux, Télécommunications, Systèmes et Architecture

### Présentée et soutenue par :

Mme LAURE ABDALLAH le mercredi 5 avril 2017

Titre :

Worst-case delay analysis of core-to-IO flows over many-cores architectures

Ecole doctorale :

Mathématiques, Informatique, Télécommunications de Toulouse (MITT)

Unité de recherche : Institut de Recherche en Informatique de Toulouse (I.R.I.T.)

**Directeur(s) de Thèse :** M. CHRISTIAN FRABOUL

M. MATHIEU JAN

**Rapporteurs :**

M. LAURENT GEORGE, ESIEE NOISY LE GRAND Mme ISABELLE PUAUT, UNIVERSITE RENNES 1

Membre(s) du jury : M. LAURENT GEORGE, ESIEE NOISY LE GRAND, Président M. CHRISTIAN FRABOUL, INP TOULOUSE, Membre M. JEROME ERMONT, INP TOULOUSE, Membre M. MARC GATTI, THALES AVIONICS, Membre M. MATHIEU JAN, CEA SACLAY, Membre

### Acknowledgements

I would like to extend my sincere gratitude to all the reviewers for accepting to evaluate this work: to Mr. Laurent Georges, Professor at the University of Paris-Est, and Mrs Isabelle Puaut, Professor at the University of Rennes 1, who very kindly agreed to be the scientific evaluators of this thesis. My earnest thanks are also due to Mr. Marc Gatti, Research Director at Avionics Thales, for accepting to be a member of the jury.

I have an immense respect, appreciation and gratitude towards my advisors: Mr. Mathieu Jan, Research Engineer at CEA LIST, Mr. Jérôme Ermont, Associate Professor at INP-ENSEEIHT, and Mr. Christian Fraboul, Professor at INP-ENSEEIHT, for their consistent support and for sharing their invaluable knowledge, experience and advice which have been greatly beneficial to the successful completion of this thesis.

Thanks to all L3S team members for the occasional coffees and discussions especially during our "PhD Days".

I would also like to thank my friends Damien, Briag, Sarah, Jad, Hadi and Marcelino for their support and all our happy get-togethers and for uplifting my spirit during the challenging times faced during this thesis.

I am particularly grateful to my friends Ola and Mohammad for their priceless friendship and precious support, and for continuously giving me the courage to make this thesis better.

Last but definitely not least, I am forever indebted to my awesomely supportive parents, my wonderful sisters, Layal, Reem and Ghina, and my beloved brother Wassim, for inspiring and guiding me throughout the course of my life, and hence this thesis.

### Abstract

Many-core architectures are more promising hardware to design real-time systems than multicore systems as they should enable an easier mastered integration of a higher number of applications, potentially of different level of criticalities. In embedded real-time systems, these architectures will be integrated within backbone Ethernet networks, as they mostly provide Ethernet controllers as Input/Output(I/O) interfaces. Thus, a number of applications of different level of criticalities could be allocated on the Network-on-Chip (NoC) and required to communicate with sensors and actuators. However, the worst-case behavior of NoC for both inter-core and core-to-I/O communications must be established. Several NoCs targeting hard real-time systems, made of specific hardware extensions, have been designed. However, none of these extensions are currently available in commercially NoC-based many-core architectures, that instead rely on wormhole switching with round-robin arbitration. Using this switching strategy, interference patterns can occur between direct and indirect flows on many-cores. Besides, the mapping over the NoC of both critical and non-critical applications has an impact on the network contention these core-to-I/O communications exhibit.

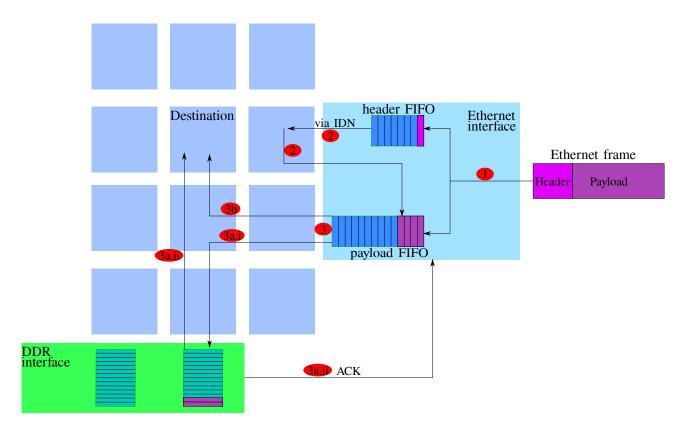

These core-to-I/O flows (coming from the Ethernet interface of the NoC) cross two networks of different speeds: NoC and Ethernet. On the NoC, the size of allowed packets is much smaller than the size of Ethernet frames. Thus, once an Ethernet frame is transmitted over the NoC, it will be divided into many packets. When all the data corresponding to this frame are received by the DDR-SDRAM memory on the NoC, the frame is removed from the buffer of the Ethernet interface. In addition, the congestion on the NoC, due to wormhole switching, can delay these flows. Besides, the buffer in the Ethernet interface has a limited capacity. Then, this behavior may lead to a problem of dropping Ethernet frames. The idea is therefore to analyze the worst case transmission delays on the NoC and reduce the delays of the core-to-I/O flows.

In this thesis, we show that the pessimism of the existing Worst-Case Traversal Time (WCTT) computing methods and the existing mapping strategies lead to drop Ethernet frames due to an internal congestion in the NoC. Thus, we demonstrate properties of such NoC-based wormhole networks to reduce the pessimism when modeling flows in contentions. Then, we propose a mapping strategy that minimizes the contention of core-to-I/O flows in order to solve this problem.

We show that the WCTT values can be reduced up to 50% compared to current state-of-theart real-time packet schedulability analysis. These results are due to the modeling of the real impact of the flows in contention in our proposed computing method. Besides, experimental results on real avionics applications show significant improvements of core-to-I/O flows transmission delays, up to 94%, without significantly impacting transmission delays of core-to-core flows. These improvements are due to our mapping strategy that allocates the applications in such a way to reduce the impact of non-critical flows on critical flows. These reductions on the WCTT of the core-to-I/O flows avoid the drop of Ethernet frames.

### Résumé

Les architectures pluri-coeurs sont plus intéressantes pour concevoir des systèmes en temps réel que les systèmes multi-coeurs car il est possible de les maîtriser plus facilement et d'intégrer un plus grand nombre d'applications, potentiellement de différents niveau de criticité. Dans les systèmes temps réel embarqués, ces architectures peuvent être utilisées comme des éléments de traitement au sein d'un réseau fédérateur car ils fournissent un grand nombre d'interfaces Entrées/Sorties telles que les contrôleurs Ethernet et les interfaces de la mémoire DDR-SDRAM. Aussi, il est possible d'y allouer des applications ayant différents niveaux de criticités. Ces applications communiquent entre elles à travers le réseau sur puce (NoC) du pluri-coeur et avec des capteurs et des actionneurs via l'interface Ethernet. Afin de garantir les contraintes temps réel de ces applications, les délais de transmission pire cas (WCTT) doivent être calculés pour les flux entre les coeurs ("inter-core") et les flux entre les coeurs et les interfaces entrées/sorties ("core-to-I/O"). Plusieurs réseaux sur puce (NoCs) ciblant les systèmes en temps réel dur ont été conçus en s'appuyant sur des extensions matérielles spécifiques. Cependant, aucune de ces extensions ne sont actuellement disponibles dans les architectures de réseaux sur puce commercialisés, qui se basent sur la commutation wormhole avec la stratégie d'arbitrage par tourniquet. En utilisant cette stratégie de commutation, différents types d'interférences peuvent se produire sur le réseau sur puce entre les flux. De plus, le placement de tâches des applications critiques et non critiques a un impact sur les contentions que peut subir les flux "core-to-I/O". Ces flux "core-to-I/O" parcourent deux réseaux de vitesses différentes: le NoC et Ethernet. Sur le NoC, la taille des paquets autorisés est beaucoup plus petite que la taille des trames Ethernet. Ainsi, lorsque la trame Ethernet est transmise sur le NoC, elle est divisée en plusieurs paquets. La trame sera supprimée de la mémoire tampon de l'interface Ethernet uniquement lorsque la totalité des données aura été transmise. Malheureusement, la congestion du NoC ajoute des délais supplémentaires à la transmission des paquets et la taille de la mémoire tampon de l'interface Ethernet est limitée. En conséquence, ce comportement peut aboutir au rejet des trames Ethernet. L'idée donc est de pouvoir analyser les délais de transmission pire cas sur les NoC et de réduire leurs délais afin d'éviter ce problème de rejet.

Dans cette thèse, nous montrons que le pessimisme de méthodes existantes de calcul de WCTT et les stratégies de placements existantes conduisent à rejeter des trames Ethernet en raison d'une congestion interne sur le NoC. Des propriétés des réseaux utilisant la commutation "wormhole" ont été définies et validées afin de mieux prendre en compte les conflits entre les flux. Une stratégie de placement de tâches qui prend en compte les communications avec les I/O a été ensuite proposée. Cette stratégie vise à diminuer les contentions des flux qui proviennent de l'I/O et donc de réduire leurs WCTTs.

Les résultats obtenus par la méthode de calcul définie au cours de cette thèse montrent que les valeurs du WCTT des flux peuvent être réduites jusqu'à 50% par rapport aux valeurs de WCTT obtenues par les méthodes de calcul existantes. En outre, les résultats expérimentaux sur des applications avioniques réelles montrent des améliorations significatives des délais de transmission des flux "core-to-I/O", jusqu'à 94%, sans impact significatif sur ceux des flux "intercore". Ces améliorations sont dues à la stratégie d'allocation définie qui place les applications de manière à réduire l'impact des flux non critiques sur les flux critiques. Ces réductions de WCTT des flux "core-to-I/O" évitent le rejet des trames Ethernet.

# Contents

| A | cknov | wledgements                                         | i   |

|---|-------|-----------------------------------------------------|-----|

| A | bstra | act                                                 | iii |

| R | ésum  | né                                                  | v   |

| 1 | Intr  | roduction                                           | 1   |

|   | 1.1   | Motivation                                          | 1   |

|   | 1.2   | Contributions                                       | 4   |

|   | 1.3   | Publications                                        | 5   |

| 2 | Net   | work-on-Chip for real-time service                  | 7   |

|   | 2.1   | NoC components                                      | 8   |

|   | 2.2   | Real-time systems                                   | 9   |

|   | 2.3   | NoC concepts and real-time requirements             | 10  |

|   |       | 2.3.1 Latency and Quality-of-Service                | 11  |

|   |       | 2.3.2 Main concepts impacting the latency           | 12  |

|   |       | 2.3.3 Main concepts impacting the design complexity | 18  |

|   | 2.4 | Assumed NoC architecture                                   | 21              |

|---|-----|------------------------------------------------------------|-----------------|

| 3 | Rel | ated works around Worst Case Traversal Time (WCTT)         | 25              |

|   | 3.1 | WCTT over wormhole networks                                | 26              |

|   |     | 3.1.1 Priority-based wormhole networks                     | 26              |

|   |     | 3.1.2 BE wormhole networks and recursive methods           | 29              |

|   | 3.2 | Contention-aware mapping                                   | 31              |

|   |     | 3.2.1 Task mapping                                         | 32              |

|   |     | 3.2.2 Application mapping                                  | 34              |

|   | 3.3 | WCTT and mapping baseline references                       | 37              |

| 4 | Ma  | naging $I/O$ in many-cores: problems and approach          | 39              |

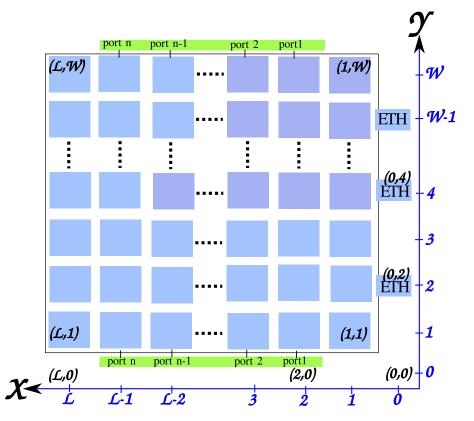

|   | 4.1 | System architecture and assumptions                        | 40              |

|   |     | 4.1.1 Description of I/O in Tilera                         | 40              |

|   |     | 4.1.2 Model of NoC architecture and assumptions            | 43              |

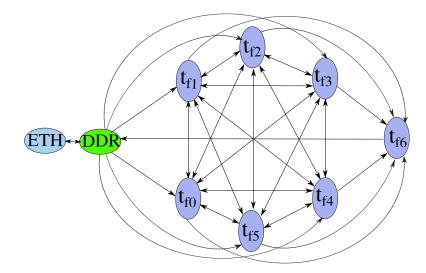

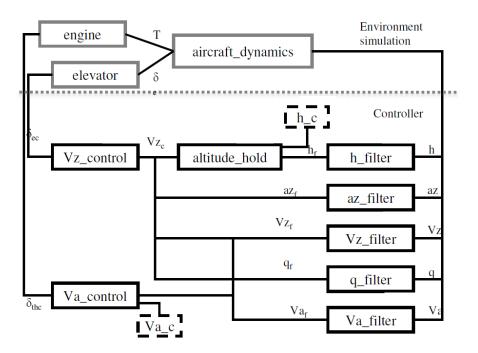

|   | 4.2 | An avionic case study                                      | 46              |

|   | 4.3 | Problem illustration                                       | 51              |

|   |     | 4.3.1 Is improving the computation of the WCTT sufficient? | 53              |

|   |     | 4.3.2 Is a contention-aware mapping strategy the solution? | 56              |

|   |     |                                                            |                 |

|   | 4.4 | Proposal                                                   | 58              |

| 5 |     | Proposal                                                   | 58<br><b>61</b> |

|   | 5.2 | Wormhole network properties                                     | 64  |

|---|-----|-----------------------------------------------------------------|-----|

|   |     | 5.2.1 Local worst-case scenario                                 | 64  |

|   |     | 5.2.2 Direct and indirect contentions                           | 69  |

|   | 5.3 | Description of the proposed pipeline-based algorithm            | 76  |

|   |     | 5.3.1 An illustrating example                                   | 77  |

|   |     | 5.3.2 Identifying the global worst-case scenario                | 80  |

|   |     | 5.3.3 Implementation of direct and indirect contention analysis | 83  |

|   | 5.4 | Unitary evaluation of the properties                            | 89  |

|   | 5.5 | Conclusion                                                      | 93  |

| 6 | Maţ | $p_{IO}$ : an I/O contention-aware mapping technique            | 95  |

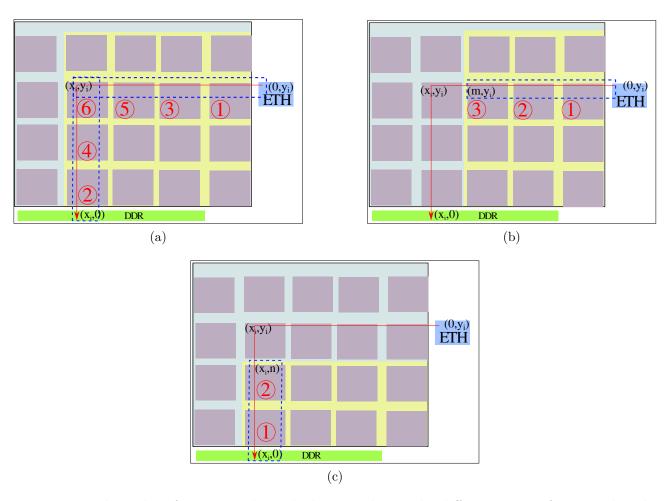

|   | 6.1 | How can the WCTT of core-to-I/O flows be reduced?               | 96  |

|   | 6.2 | Overview of our strategy of mapping: $Map_{IO}$                 | 97  |

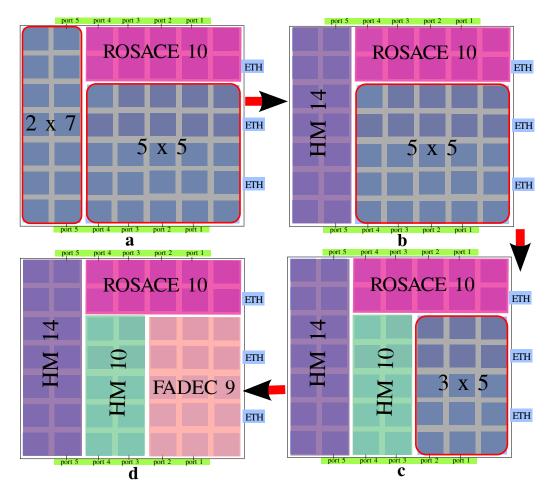

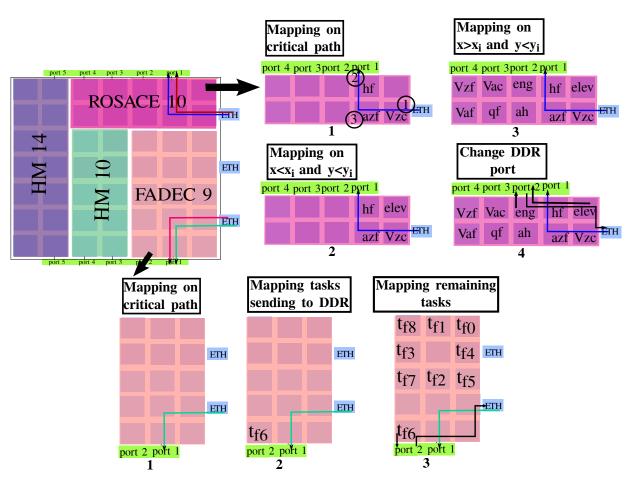

|   | 6.3 | Phase 1: Core-to-I/O flows distance minimization                | 99  |

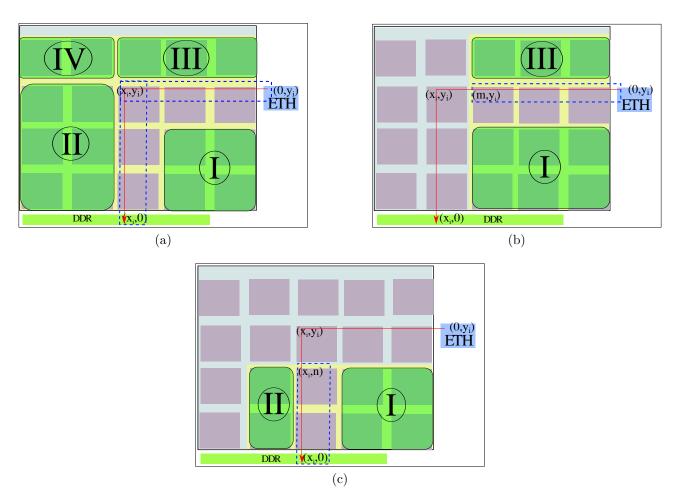

|   |     | 6.3.1 Filling NoC regions with applications                     | 100 |

|   |     | 6.3.2 Application shape and its assignment to regions           | 103 |

|   |     | 6.3.3 Reclaiming unused cores within shapes                     | 106 |

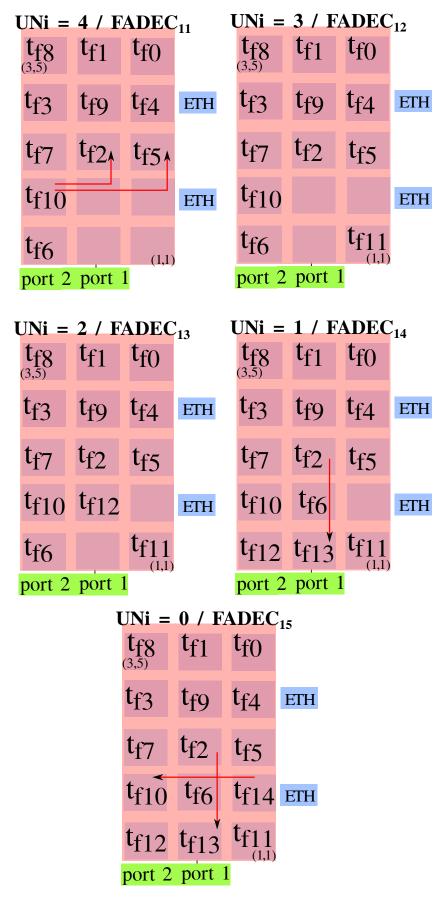

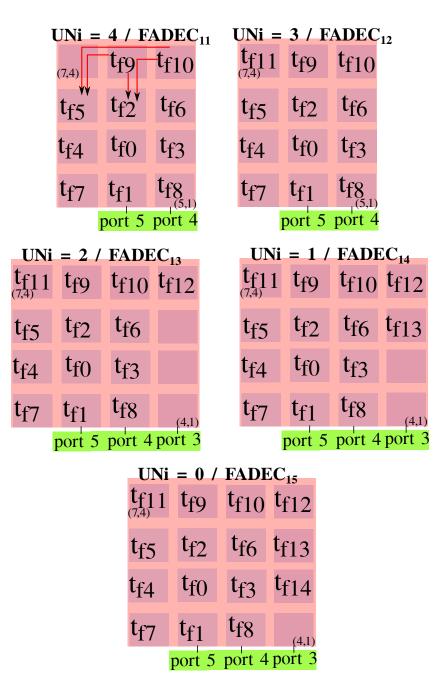

|   | 6.4 | Phase 2: Core-to-I/O flows contention minimization              | 109 |

|   |     | 6.4.1 I/O critical paths within applications                    | 109 |

|   |     | 6.4.2 Mapping tasks on the critical paths                       | 112 |

|   |     | 6.4.3 Mapping tasks around the critical path                    | 117 |

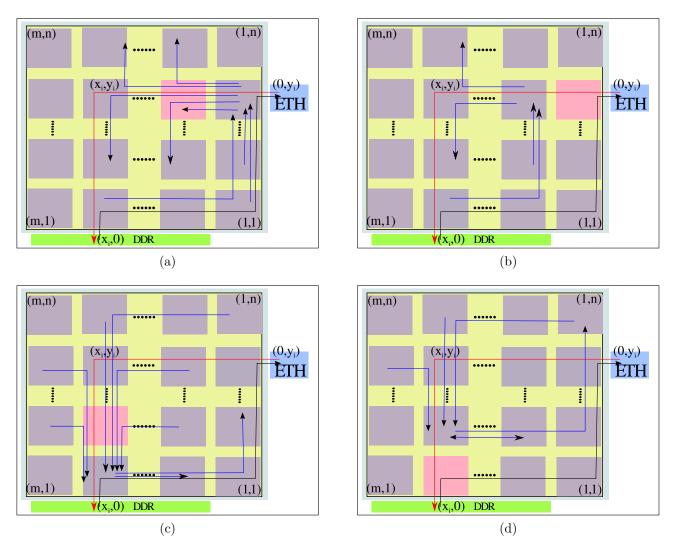

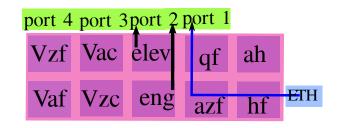

|   |     | 6.4.4 Minimizing the contention of outgoing flows               | 120 |

|    | 6.5   | Conclusion                                                                                                                          | 124 |

|----|-------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7  | Eva   | luation of $RC_{NoC}$ and $Map_{IO}$ on case studies                                                                                | 125 |

|    | 7.1   | Impact of $RC_{NoC}$ on the core-to-I/O flows $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$        | 128 |

|    | 7.2   | Impact of $Map_{IO}$ on the core-to-I/O flows $\ldots \ldots \ldots$ | 129 |

|    | 7.3   | Combining our $Map_{IO}$ and $RC_{NoC}$ is necessary $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                             | 132 |

|    | 7.4   | Impact of $Map_{IO}$ on both core-to-I/O and core-to-core flows $\ldots \ldots \ldots \ldots$                                       | 133 |

|    |       | 7.4.1 Impact of $Map_{IO}$ rules                                                                                                    | 134 |

|    |       | 7.4.2 Impact of unused cores                                                                                                        | 137 |

|    |       | 7.4.3 Discussion                                                                                                                    | 145 |

|    | 7.5   | Conclusion                                                                                                                          | 145 |

| 8  | Con   | clusion                                                                                                                             | 147 |

|    | 8.1   | Summary of Thesis Contributions                                                                                                     | 147 |

|    | 8.2   | Future Work                                                                                                                         | 149 |

| Bi | bliog | graphy                                                                                                                              | 152 |

| Bi | bliog | graphy                                                                                                                              | 153 |

# List of Tables

| 2.1 | Table reporting some examples of NoC architectures.    22                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1 | Different shapes and their free cores for each application                                                                                                                        |

| 7.1 | Table illustrating the WCTT of the core-to-I/O flows, of the case study A, sharing the Ethernet $(0,6)$ and $(0,2)$ using $Map_{IO}$ and SHiC approach 130                        |

| 7.2 | Table illustrating the WCTT of the core-to-I/O flows, of the case study B, sharing the Ethernet (0,6) and (0,2) using $Map_{IO}$ and SHiC approach                                |

| 7.3 | Table illustrating the WCTT of $HM_{12}$ blocking $HM_{16}$ of the case study C and<br>sharing the Ethernet (0,6) using the different mapping strategies and computing<br>methods |

| 7.4 | Table illustrating the different results for applications, of case study A, sharing the Ethernet $(0,6)$ using $Map_{IO}$ and SHiC approach                                       |

| 7.5 | Table illustrating the different results for HM and FADEC in both case studies<br>A and B using $Map_{IO}$ and SHiC approach                                                      |

| 7.6 | Table reporting the WCTT of core-to-I/O flows for the applications of the case study D using $Map_{IO}$ and the SHiC method                                                       |

| 7.7 | Table reporting the WCTT of the core-to-I/O flow of $HM$ when varying the number of unused cores $(U_i)$ by $FADEC_9$                                                             |

# List of Figures

| 2.1 | The NoC components.                                                                           | 8  |

|-----|-----------------------------------------------------------------------------------------------|----|

| 2.2 | The different buffering strategies                                                            | 15 |

| 2.3 | Example of topologies that are most used in NoCs.                                             | 19 |

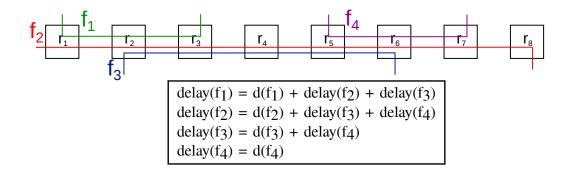

| 3.1 | An example illustrating Recursive Calculus method                                             | 30 |

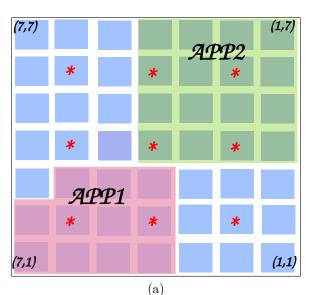

| 3.2 | Allocating $App_3$ using the mapping strategies presented in [dSCCM10], [FRD <sup>+</sup> 12] |    |

|     | and [COM08]                                                                                   | 35 |

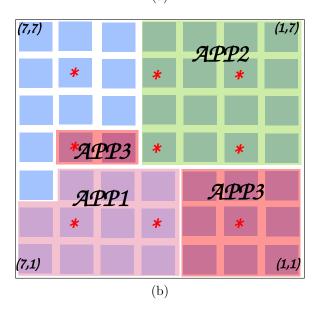

| 3.3 | Allocating $App_3$ using SHiC method presented in [FDLP13]                                    | 37 |

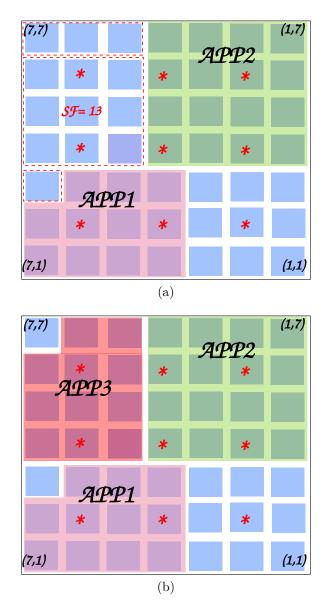

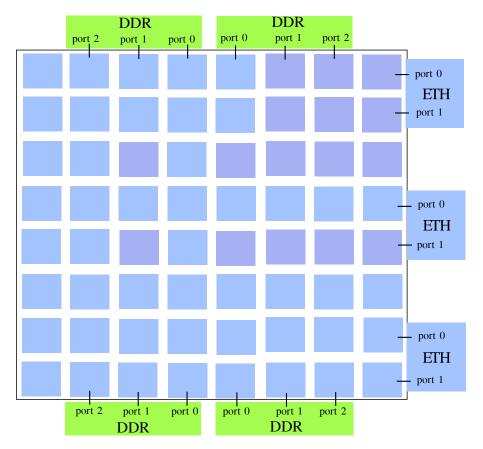

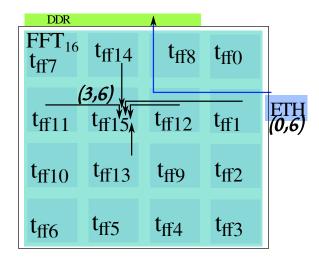

| 4.1 | An overview of a Tilera architecture.                                                         | 41 |

| 4.2 | The different steps of the ingress data flows.                                                | 42 |

| 4.3 | A Tilera-like NoC architecture.                                                               | 44 |

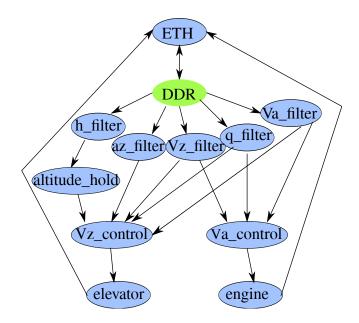

| 4.4 | Task graph of core-to-core and core-to-I/O communications of the FADEC ap-                    |    |

|     | plication assuming 7 tasks                                                                    | 47 |

| 4.5 | ROSACE case study, extracted from [PSG <sup>+</sup> 14].                                      | 48 |

| 4.6 | Task graph illustrating ROSACE case study                                                     | 49 |

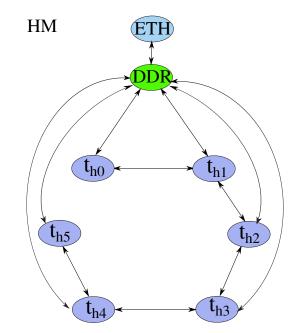

| 4.7 | Task graph illustrating HM application assuming 5 tasks                                       | 49 |

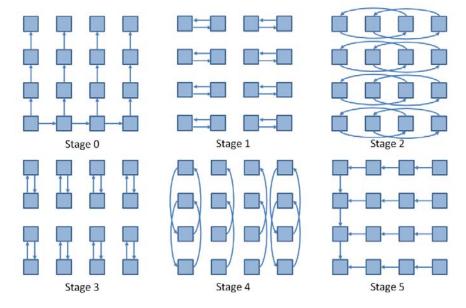

| 4.8  | The 6 FFT communication stages                                                                                                                                                    | 50 |

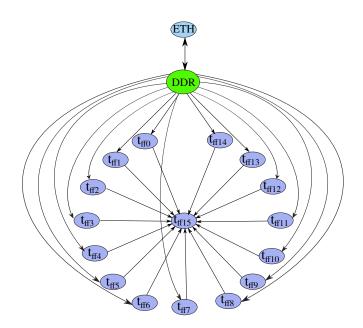

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | Task graph illustaring FFT application assuming 16 tasks                                                                                                                          | 51 |

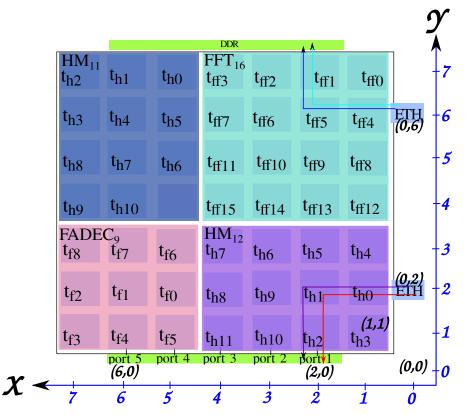

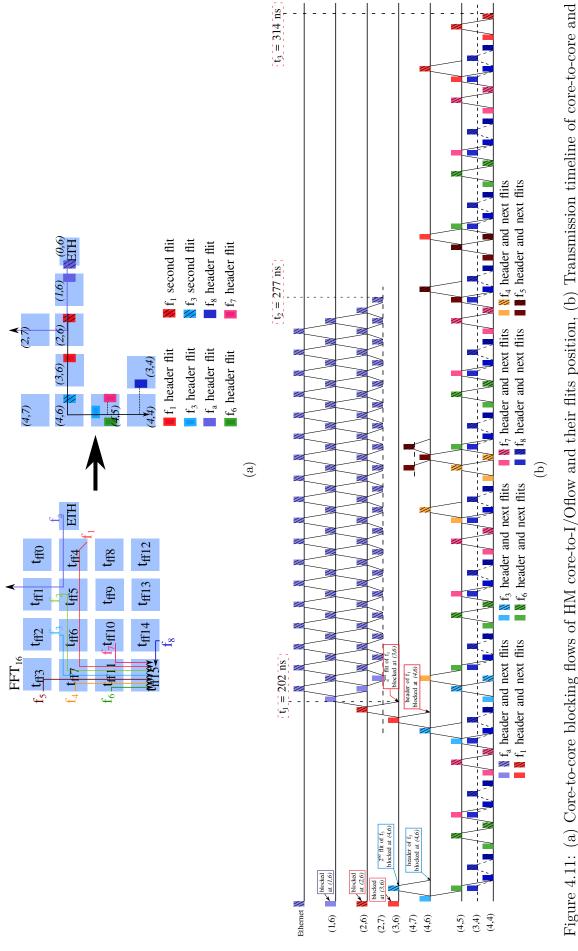

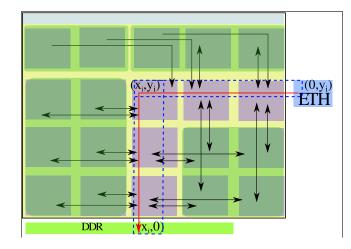

| 4.10 | Arbitrary mapping of a case study made of one FADEC, one FFT and two HM applications                                                                                              | 52 |

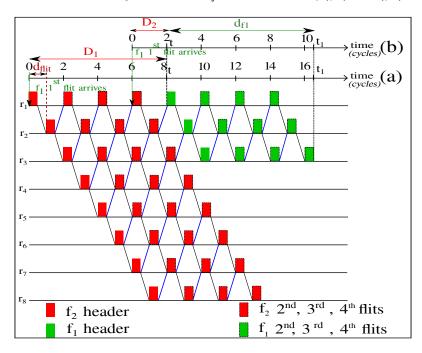

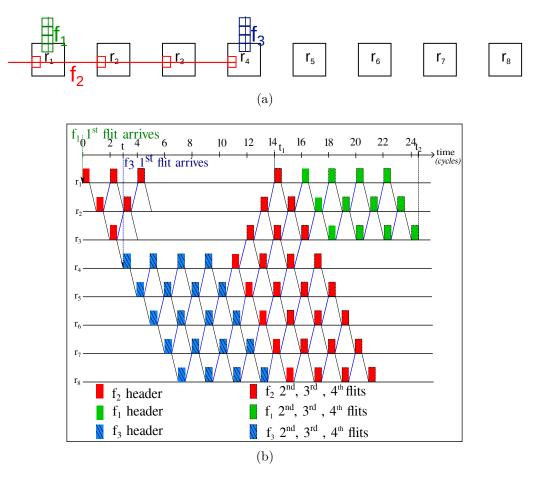

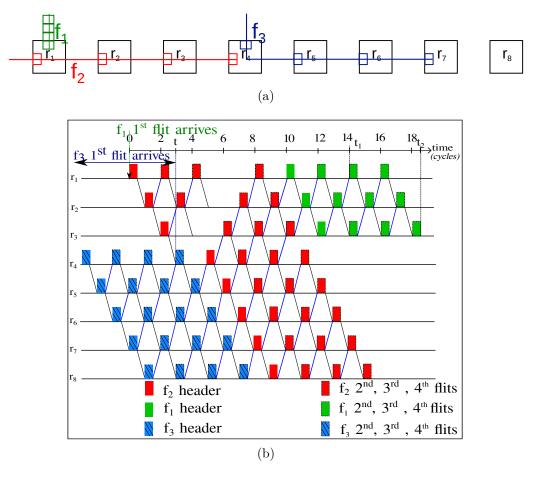

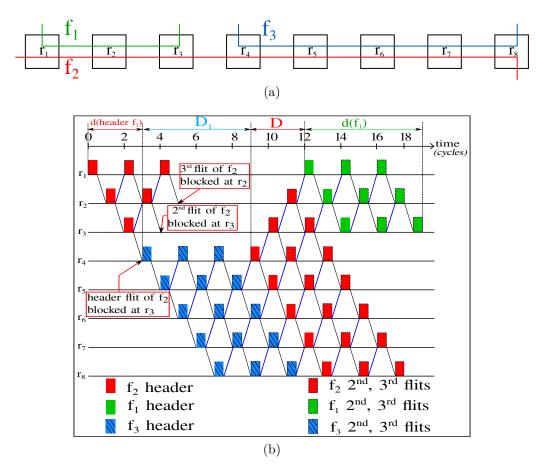

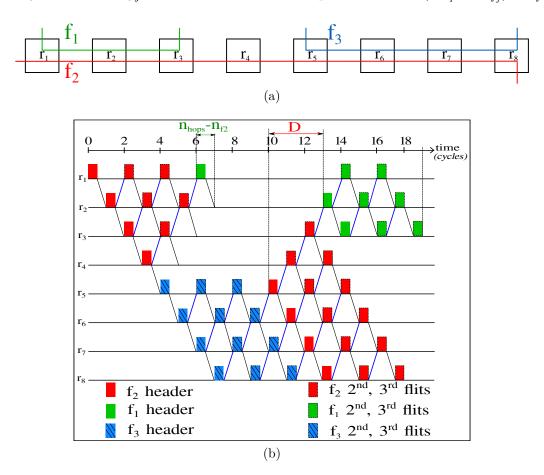

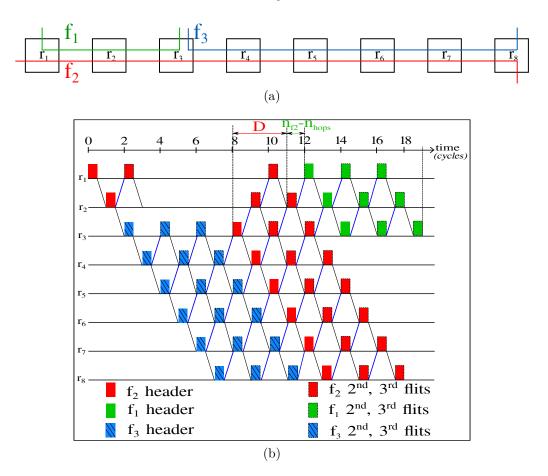

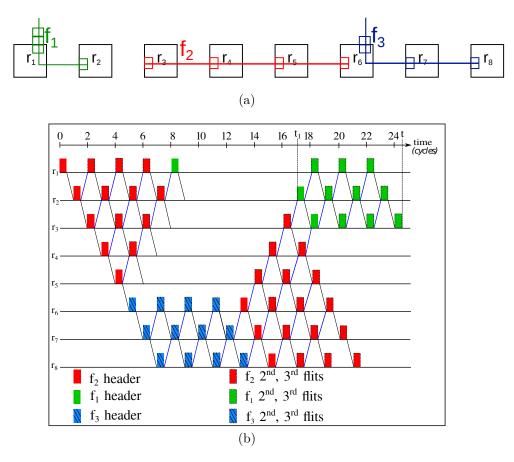

| 4.11 | <ul><li>(a) Core-to-core blocking flows of HM core-to-I/Oflow and their flits position,</li><li>(b) Transmission timeline of core-to-core and core-to-I/Ocommunications</li></ul> | 55 |

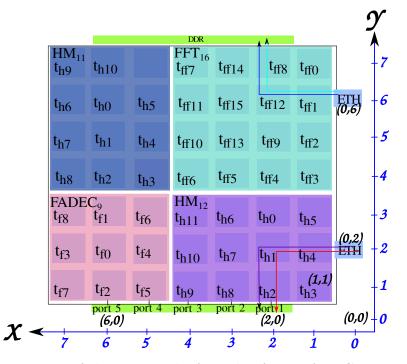

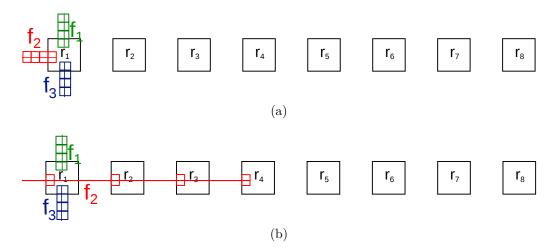

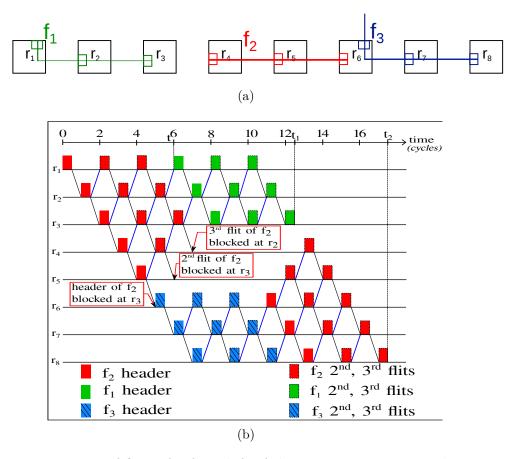

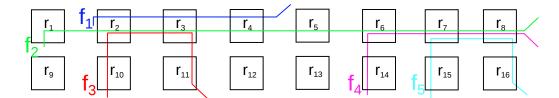

| 4.12 | SHiC mapping of the case study A made of one FADEC, one FFT and two HM applications.                                                                                              | 56 |

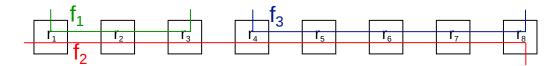

| 4.13 | FFT flows blocking the HM core-to-I/O<br>flow by considering SHiC mapping                                                                                                         | 58 |

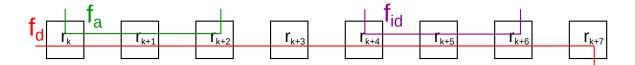

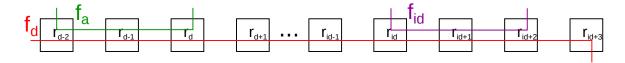

| 5.1  | Example illustrating the number of routers separating an analyzed flow $f_a$ from its indirect flow $f_{id}$ .                                                                    | 63 |

| 5.2  | Example illustrating the second condition of Property 1                                                                                                                           | 65 |

| 5.3  | Different scenarios to illustrate the second condition of property 1                                                                                                              | 65 |

| 5.4  | Timeline of the transmission of flows for the two different scenarios of the example shown in Figure 5.3.                                                                         | 66 |

| 5.5  | Different scenarios illustrating the third condition of property 1                                                                                                                | 67 |

| 5.6  | Timeline of the transmission of flows of the example shown in Figure 5.5                                                                                                          | 68 |

| 5.7  | Example illustrating that Property 1 should be applied recursively                                                                                                                | 68 |

| 5.8  | A worst-case scenario of the example in Figure 5.7 illustrating the recursion of Property 1.                                                                                      | 69 |

| 5.9  | A second configuration of the example in Figure 5.7 which does not lead to a                                                                                                      | 70 |

|      | worst-case scenario.                                                                                                                                                              | 70 |

| 5.10 | An example illustrating the case where $n_{hops} = n_{f_j}$                                                                                                                       | 72 |

| 5.11 | An example illustrating the case where $n_{hops} > n_{f_j} \dots \dots \dots \dots \dots \dots$                                                              | 73  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.12 | An example illustrating the case where $n_{hops} < n_{f_j}$                                                                                                  | 74  |

| 5.13 | Example illustrating the analyzed flow $f_a$ , the direct flow $f_d$ and the indirect flow $f_{id}$ .                                                        | 75  |

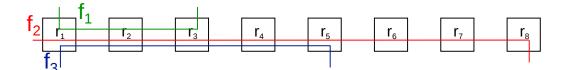

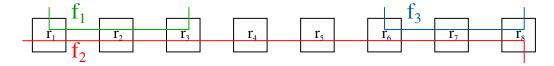

| 5.14 | Example illustrating Property 3                                                                                                                              | 75  |

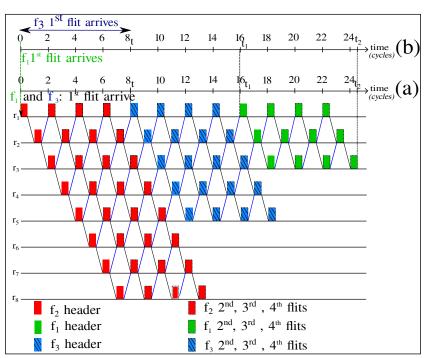

| 5.15 | Transmission of flows $f_1$ , $f_2$ and $f_3$ of the case in Figure 5.14 where we consider<br>a size of 3 flits for each packet                              | 76  |

| 5.16 | Timelines of transmission of flows $f_1$ , $f_2$ and $f_3$ of the case in Figure 5.14 where<br>we consider a size of 4 flits for each packet                 | 77  |

| 5.17 | Example illustrating the method of computation.                                                                                                              | 77  |

| 5.18 | Timeline illustrating the transmission of flows of the example in Figure 5.17 and considering the first scenario.                                            | 79  |

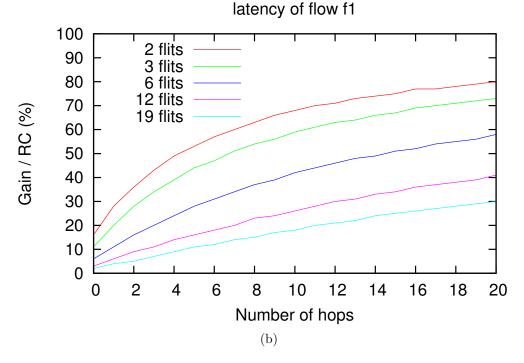

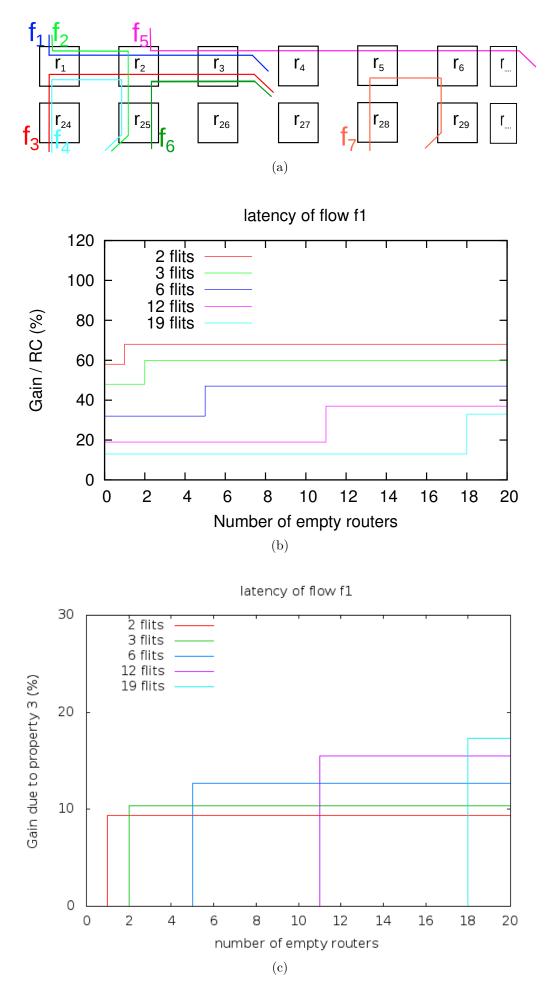

| 5.19 | Mapping of flows in the first configuration and normalized gain compared to the RC method                                                                    | 90  |

| 5.20 | Mapping of flows in the second configuration and normalized gain compared to the RC method                                                                   | 92  |

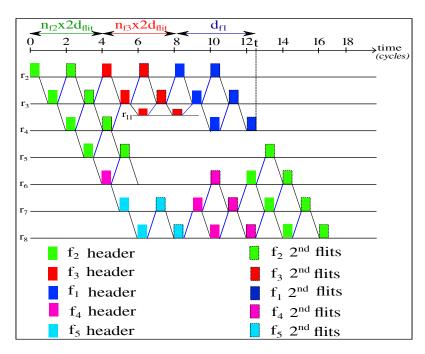

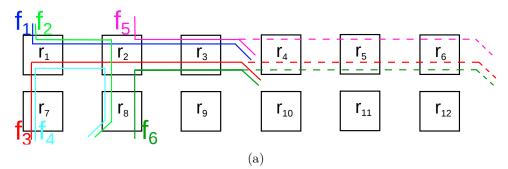

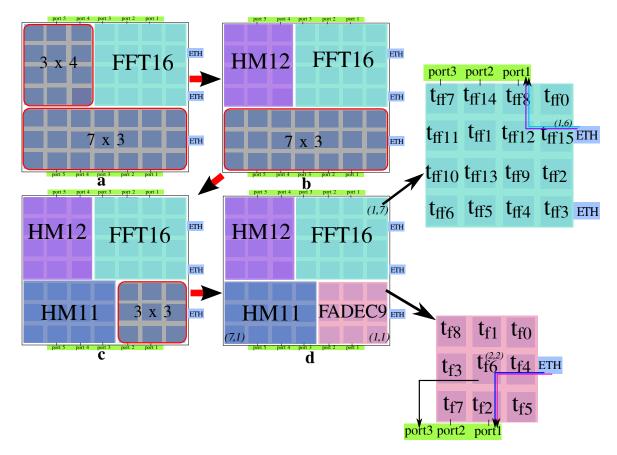

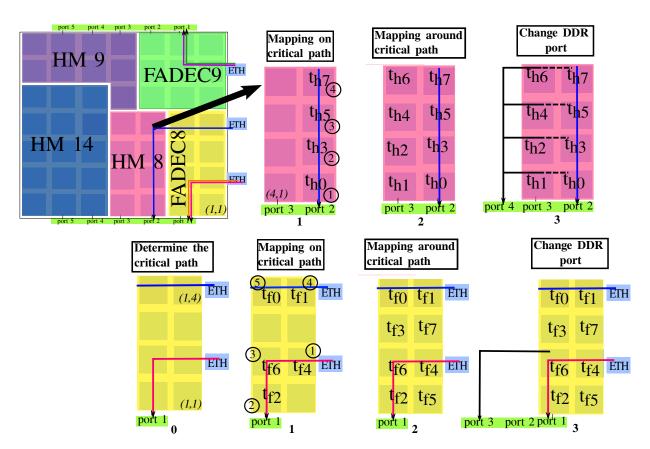

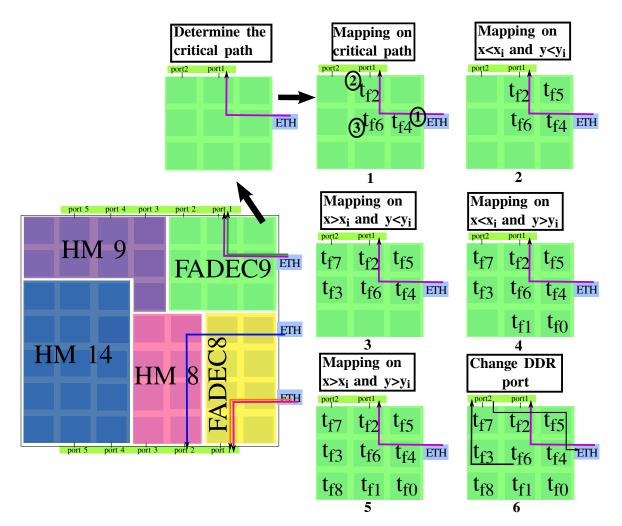

| 6.1  | The different steps of our approach $Map_{IO}$ for mapping FADEC, HM and FFT applications of case study A                                                    | 98  |

| 6.2  | Mapping of FADEC and HM applications of the case study B using our approach $Map_{IO}$ .                                                                     | 105 |

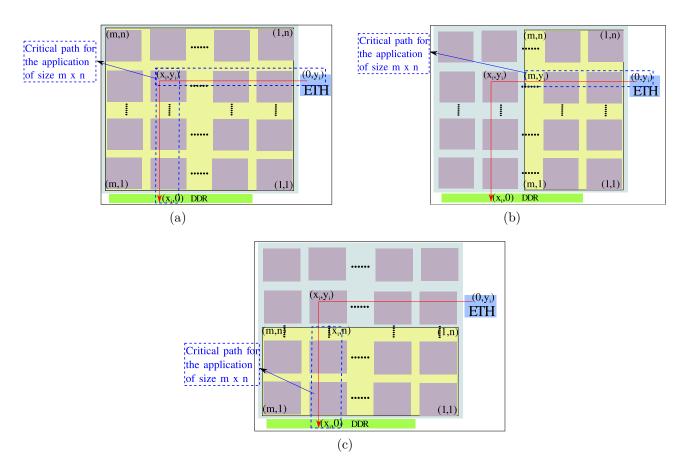

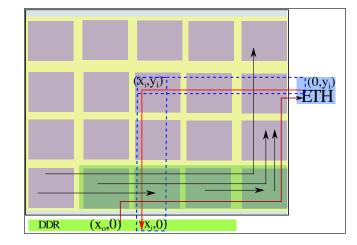

| 6.3  | Different cases of a possible critical path, shown in blue, for a core-to-I/O flow (path shown in red) of an application (whose mapping is shown in yellow). | 110 |

| 6.4  | The different steps of internal mapping for $FADEC_8$ and $HM_8$                                                                                             | 111 |

| 6.5                                           | The order of mapping the tasks by considering the different cases of a critical path                                                                                                                                                                                                                  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.6                                           | The different communications that could block the X and Y part of a critical                                                                                                                                                                                                                          |

|                                               | path depending on where free cores are localized                                                                                                                                                                                                                                                      |

| 6.7                                           | Perpendicular communications with the critical path avoids the contention with the core-to-I/O flow                                                                                                                                                                                                   |

| 6.8                                           | For each possible configuration of a critical path, the defined areas and their order in the tasks mapping                                                                                                                                                                                            |

| 6.9                                           | Flows blocking directly the path of the outgoing flow                                                                                                                                                                                                                                                 |

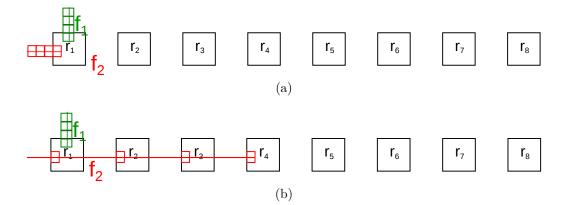

| 6.10                                          | The configuration in (a) shows how the communications with DDR interfere the critical path while this interference is avoided by our mapping as shown in (b). 122                                                                                                                                     |

| 6.11                                          | Mapping of $FADEC_9$ of the case study B                                                                                                                                                                                                                                                              |

|                                               |                                                                                                                                                                                                                                                                                                       |

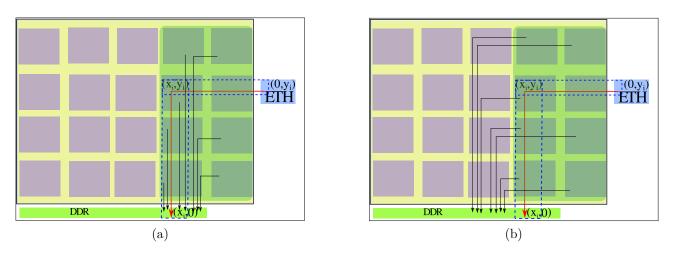

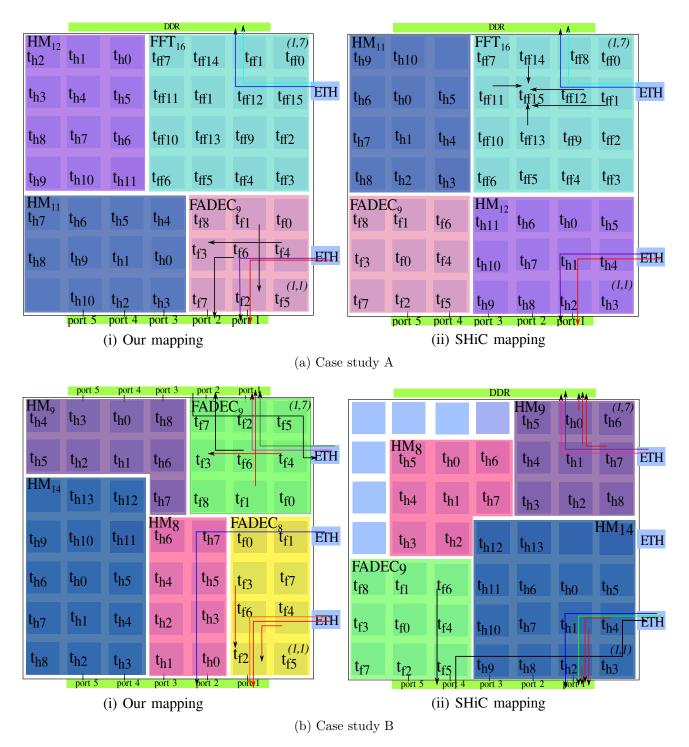

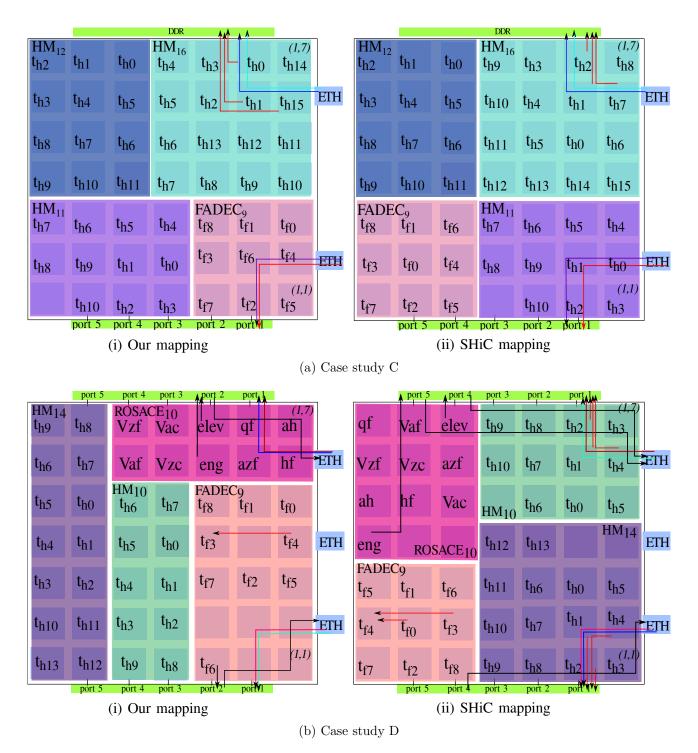

| 7.1                                           | mapping of flows of case studies A and B by applying $Map_{IO}$ mapping and SHiC mapping.                                                                                                                                                                                                             |

| 7.1<br>7.2                                    |                                                                                                                                                                                                                                                                                                       |

|                                               | mapping                                                                                                                                                                                                                                                                                               |

| 7.2                                           | mapping                                                                                                                                                                                                                                                                                               |

| 7.2<br>7.3                                    | mapping                                                                                                                                                                                                                                                                                               |

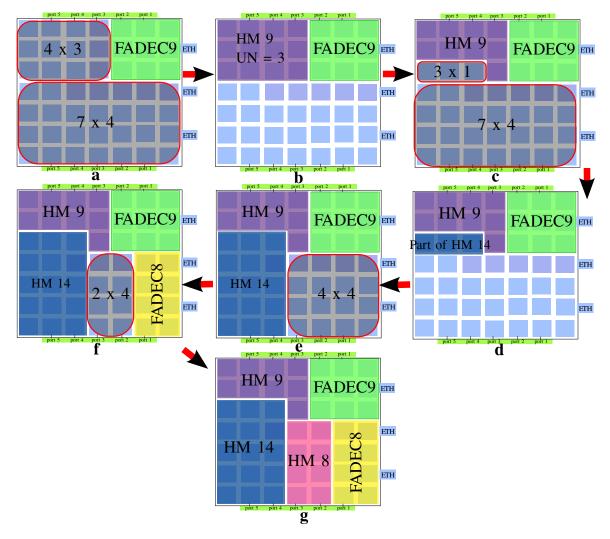

| <ul><li>7.2</li><li>7.3</li><li>7.4</li></ul> | mapping.126mapping of flows of case studies C and D by applying $Map_{IO}$ mapping and SHiCmapping.127The different steps for mapping the applications of the case study D using $Map_{IO}$ .The different steps of $Map_{IO}$ task mapping for ROSACE and FADEC applications of the case study D.138 |

# Chapter 1

# Introduction

### Contents

| 1.1 | Motivation    | 1        |

|-----|---------------|----------|

| 1.2 | Contributions | 4        |

| 1.3 | Publications  | <b>5</b> |

### 1.1 Motivation

The use of real-time systems continues to spread in many diverse application areas including, engine management, process control, medical electronics, telecommunications, robotics, multimedia and avionics. The underlying idea of real-time systems is not the speed concept but the reactivity: a real-time system operates in a dynamic environment and must constantly adapt to the changes in this environment. This implicates that the response to these changes must be adapted (functional correction), but must also respect the time constraints (time correction). These time constraints vary considerably in their degree of severity. In soft real-time systems, the late response may be tolerated. In contrast, in hard real-time systems, a failure to respond within the time constraints may constitute a catastrophic failure of the system.

#### In this thesis, we focus on hard real-time systems.

Real-time systems range in complexity from simple controllers implementing a single function, to complex sets of communicating sub-systems, each of which is responsible for performing a number of critical functions. These systems are becoming increasingly complex with the complexity of applications, whether in architectures (number of processors, the presence of networks), or in requirements (criticality of tasks, computing power, energy consumption, etc..). The need to meet these requirements lead to computer systems that comprised millions of transistors on a single chip, commonly called Systems on Chip or SoC. The most common communication backbone used in SoCs is the shared medium arbitrated bus. However, a bus based SoC does not scale with the number of cores attached, and so the performance is reduced. Thus, a search for the communication backbone of next generation many-core based SoCs supporting new inter-core communication demands started, and lead to the design of what is called Network on Chip (NoC). NoC has emerged as a viable alternative as it consists of various cores connected to a router-based network. Such communication architecture is described as modular and scalable [BDM02b, DT01, KJS<sup>+</sup>02].

### In this thesis, we focus on the NoC-based many-core architectures.

Many-core architectures are indeed promising hardware to support the design of hard real-time systems [NYP<sup>+</sup>14a]. They are based on simpler cores, without complex hardware mechanisms that can be found in multi-core architectures. The timing predictability of cores within manycore architectures are thus easier to analyze. In order to support hard real-time traffic, the guarantees in the worst-case scenarios must be established. Then, the Worst-Case Traversal Time (WCTT) of all the packets generated by a flow must be lower than a predetermined deadline. A deadline marks the latest time that a packet should arrive to its destination. Thus, Quality-of-Service (QoS) has been a major concern for NoC [BM06]. In fact, packets are routed in a network where resources are shared, thus bringing unpredictable performance. NoCs can thus be used in hard real-time systems using two approaches. A first approach is to use analytic methods to analyze the WCTTs of flows on existing many-cores. A second one is to modify the hardware architecture in such a way no contentions can occur by design, leading to straightforward WCTT for flows. However, the problem in the second approach is that it does not exist a commercial NoC architecture implementing it.

## In this thesis, we focus on the use of NoC architectures in hard real-time systems using the first approach.

In embedded real-time systems, a number of applications of different level of criticalities could be allocated on a NoC and required to communicate with sensors and actuators. As manycores architectures present an important number of Ethernet interfaces, thus, it could be used as processing elements within a backbone Ethernet network. The challenge is then to analyze the worst-case behavior of the underlying NoC [BDM02a] used for both inter-core and core to external memories or peripherals communications. Such real-time packet schedulability analysis have been done for various types of networks by taking into account the type of contentions that can occur between flows. However, none of these works consider in addition the core-to-I/O communications.

# In this thesis, we focus on the integration of I/O constraints within NoC communications.

A core-to-I/O flow experiences a change in its speed as it crosses two networks of different types (NoC and Ethernet). However, in NoCs, the congestion is possible especially when using a wormhole switching. A NoC congestion delays the core-to-I/O flow leading to an overflow of the buffer of the Ethernet interface which is of limited capacity. Therefore, incoming Ethernet frames holding critical data could be dropped. Real-time packet schedulability analysis must then be done by taking into account all types of contentions that can occur between all types of flows, which severely complicate its timing analysis.

The objective of this thesis is to analyze the WCTT of all flows on the NoC and to reduce the WCTT of the core-to-I/O flow in order to avoid the loss of critical payloads.

### 1.2 Contributions

In the aim to reach the objectives mentioned in the previous section, this thesis presents three main contributions:

- An analysis showing that existing computing methods and congestion-aware mapping strategies are not sufficient to integrate the I/O constraints within the NoC communications. Besides, an explanation of the I/O interfaces and an illustration of the communications between cores and I/O interfaces are presented. To the best of our knowledge, this is the first work that integrates I/O communications within the NoC communications.

- An analytical method to compute the WCTT by including three properties of the wormhole switching when analyzing contentions between flows. This method reduces the pessimism of the existing methods, thus tightest bounds of the delay can be obtained.

- A congestion-aware mapping strategy of critical and non-critical applications that consider not only the core-to-core communications, but also the core-to-I/O communications. This strategy aims to reduce the contention on the core-to-I/O flows and then their WCTTs.

The thesis is organized as follows:

- Chapter 2 presents the main NoC concepts that impact the WCTT of flows over different architectures. Besides, we present some of the existing NoC architectures in order to argue the architecture we assume in this work

- Chapter 3 describes the existing methods to compute the WCTT of the flows on the wormhole networks. It illustrates also the existing mapping strategies that reduce the congestion on the NoC and thus the WCTT of these flows.

- Chapter 4 presents our first contribution: an illustration of the the problems when using NoCs in real-time systems interconnected to sensors and actuators via Ethernet. Thus, first, we present the model of our NoC architecture and the I/O model. Then, we show

in a motivating case study made of real-time applications what are the limitations of the existing WCTT analysis and mapping methods that lead to these problems.

- Chapter 5 explains our second contribution: an analysis method that reduces the pessimism when computing WCTT of flows. This chapter shows the improvements of our method compared to the existing methods.

- Chapter 6 describes our third contribution: a mapping algorithm that takes into account the core-to-I/O flows and that aims to reduce the contention on these flows.

- Chapter 7 presents an evaluation of our contributions compared to the current state-ofthe-art methods on several case studies. The objective of this chapter is to illustrate the impacts of our proposed approaches on the WCTT of the core-to-I/O and core-to-core flows.

- Chapter 8 concludes the manuscript by summarizing the major contributions of the thesis and proposing interesting research directions as future work.

### 1.3 Publications

This is a list of papers and publications that reflects the results achieved during the developement of the research work presented in this dissertation. A significant part of this thesis is compiled from these papers and publications.

- Laure Abdallah, Mathieu Jan, Jérôme Ermont and Christian Fraboul. "Reducing the contention experienced by real-time core-to-I/O flows over a Network on Chip", In 28th Euromicro Conference on Real-Time Systems (ECRTS), Toulouse, France, July 2016.

- Laure Abdallah, Mathieu Jan, Jérôme Ermont and Christian Fraboul. "Wormhole networks properties and their use for optimizing worst case delay analysis of many-cores", In 10th IEEE International Symposium on Industrial Embedded Systems (SIES 2015), pages 59–68, Siegen, Germany, June 2015.

- Laure Abdallah, Mathieu Jan, Jérôme Ermont and Christian Fraboul. "I/O contention aware mapping of multi-crticalities real-time applications over many-core architectures", In Proc. of the 22nd IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), Session Work-In-Progress, Vienna, Austria, April 2016.

- Laure Abdallah, Mathieu Jan, Jérôme Ermont and Christian Fraboul. "Optimizing worst case delay analysis on wormhole networks by modeling the pipeline behavior", In Proc. of the 13th International Workshop on Real-Time Networks (RTN), Madrid, Spain, July 2014.

- Laure Abdallah, Mathieu Jan, Jérôme Ermont and Christian Fraboul. "Why and how to map real-time core-to-I/O flows over a Tilera-like Network on Chip?", In *FNRS Seminar-Real-time networks*, Brussels, Belgium, May 2016.

- Laure Abdallah, Mathieu Jan, Jérôme Ermont and Christian Fraboul. "Propriétés des réseaux wormhole pour optimiser l'analyse de délai pire cas dans les many-coeurs", In *Real-time summer school*, Rennes, France, August 2016.

# Chapter 2

# Network-on-Chip for real-time service

### Contents

| 2.1 NoC components                                  |

|-----------------------------------------------------|

| 2.2 Real-time systems                               |

| 2.3 NoC concepts and real-time requirements         |

| 2.3.1 Latency and Quality-of-Service                |

| 2.3.2 Main concepts impacting the latency           |

| 2.3.3 Main concepts impacting the design complexity |

| 2.4 Assumed NoC architecture                        |

Network-on-chip has been a very active research field since their emergence in the early 2000s, as it offers various opportunities in terms of performance and computing capabilities. At the same time, they pose many challenges to be used in real-time systems and ensure the temporal predictability of flows. Indeed, the flows on a NoC are routed in a network where resources are shared, thus bringing unpredictable performance. Different parameters impact the upper bounds delay of a flow on a NoC. This chapter aims to analyze the different implementations of the NoC concepts and their impact on delivering real-time requirements. In this chapter, we first present the NoC components and we define the real-time systems. Then, we show how the

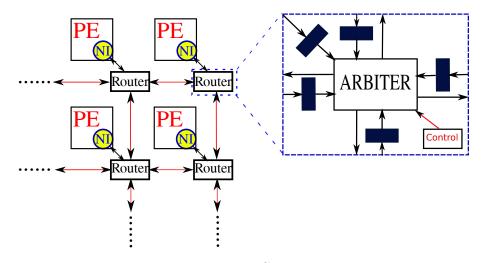

Figure 2.1: The NoC components.

implementation of NoC concepts impacts the needed Quality-of-Service (QoS) and the design complexity of the NoC. Finally, this chapter shows the NoC architecture on which our work is based.

### 2.1 NoC components

NoC was introduced in [DT01] as a better alternative to global wiring structures, used to interconnect different Intellectual Property (IP) cores, which are also called Processing Elements (PE). A NoC, being on a single chip, is composed of a number of interconnected tiles. A tile, which is also called a node, contains one or many IP cores and a network router. A NoC also interconnects the tiles to the I/O interfaces such as the external memory, the Ethernet interfaces, etc. Figure 2.1 illustrates the structure of a NoC which is composed of routers, network interfaces and links.

### Router

A router is used to send messages from one tile to another. It consists of a set-up of input and output ports that can (or not) contain buffers, an interconnection matrix, and an arbiter. Routers can have buffers either at input port or at output port [DT04]. Figure 2.1 illustrates an example of a router with input buffers. These inputs and outputs ports are connected to each other via the interconnection matrix which is controlled by the arbiter [DMB06].

### Links

Routers communicate to each other by one or more physical channels, i.e. a link [DMB06, LRV06]. This connection could be uni- or bi-directional.

#### Network interface

Network Interface (NI) provides an interface between the core and the network. It makes NoC transparent for the PEs. It is used by PEs to access the interconnect medium. The data produced by the core have to be encapsulated by the source NI and decapsulated by the destination NI. NI converts the messages into packets for the transmission of the NoC.

A packet is divided into flow control units (flits). A flit is the minimum unit of information that can be transferred across a link [CSG99]. The first flit is called the header. The packet header contains informations about the destination NoC node. These informations are needed by NI to determine the path of the packet. The header is followed by one or several flits which compose the data payload. The data payload is the data transmitted by the IP core across the NoC.

### 2.2 Real-time systems

In a real-time system, the accuracy of the application depends not only on the result but also on the time at which this result is produced. A data packet received by a destination too late could be useless or even cause a severe consequence. Typical examples of real-time systems include control systems for cars, aircraft and space vehicles. In an Antilock Braking System (ABS), not only the breaking pressure must be calculated, but also the time of application is critical to gain a functioning ABS. ABS braking system should not put more than 150ms to receive the information and 1s to react.

Thus, time is an important characteristic for real-time systems. This characteristic distinguishes

these systems from other types of computing systems. For on-chip communications, the packet transmission duration is the time which interests us. Assigning a deadline to each packet distinguishes a real-time communication from a non real-time one. A deadline marks the latest time that a packet should arrive to its destination. Thus, a real-time communication means meeting the deadlines, i.e. satisfying the timing constraints. For hard real-time systems, a missed deadline is not tolerated. Thus, communications in these systems must imperatively meet deadlines, otherwise the system might fail and the penalty incurred is catastrophic. It could lead to loss of life, serious damage to the environment or threats to business interests. As an example of hard real-time applications, Full Authority Digital Engine Controller (FADEC) that controls the activities of an aircraft jet engine. The FADEC design requires particular timing requirements. For example, if the FADEC senses that a turbine drive shaft has broken, then the FADEC must respond with a damage mitigating action in a predetermined time. In this thesis, we are interested in such hard-real time communications, where we focus on the response time communications. Now, let us see how the implementation of NoC concepts impact the delivery of such real-time requirements.

### 2.3 NoC concepts and real-time requirements

A number of metrics are needed to measure and quantifying the performance of a NoC [KPN<sup>+</sup>05, DYN03]. In general, it is desirable that a NoC architecture exhibits low latency, high throughput, energy efficiency, low cost, low area overhead and high scalability. In hard real-time systems, the delay bounds of each packet must be guaranteed. As we deal with these systems, we focus on the latency metric where the maximal latency, called Worst-case Traversal Time (WCTT), of each packet must be lower than its deadline. The goal of this section is to introduce a number of NoC concepts that impact the latency and the design complexity. First, let us see what is the latency metric?

### 2.3.1 Latency and Quality-of-Service

The measurement of the end-to-end network latency is either at the packet or the message level. Thus, the latency of a packet is the time between sending the first flit at the source and receiving the last flit of this packet at the destination. Similarly, the latency of a message is the time between the transmission of the first packet and the reception of the last one.

However, the latency of a packet is the sum of two components [LRV06]:

- 1. The conflict-free delay;

- 2. The blocking delay.

The conflict-free delay includes the router delay, the wire delay and the distance between the source and the destination. The blocking delay results from the possible contention between packets transmitted on the NoC. However, these delays depend on the choices made when designing the elements of a NoC. But, the degree of freedom is large. For this reason, the key NoCs concepts have to be carefully considered by the designer as they affect all the performance metrics. The latency is an important performance metric as it is often associated with a need for Quality-of-Service (QoS). Actually, a QoS defines a certain level of guarantees that is given for packet transfers. [GDvM<sup>+</sup>03] identifies two basic QoS classes:

#### 1. Best-Effort (BE):

BE services do not reserve any resources, and hence, provide no guarantees on latency and throughput. Thus, it optimizes the average network resources usage.

#### 2. Guaranteed services (GS):

In this service, a number of mechanisms are used to allocate the network resources to ensure fixed throughput and/or latency, regardless of network load.

In the context of real-time systems over NoC, the WCTT must be computed. Thus, in this context, either we use different analytic methods to compute the WCTTs of packets in BE NoCs,

or we use GS NoCs where the analysis of WCTT is more simpler as it leads to straightforward WCTT values.

The way in which a NoC concept is implemented can determine the QoS class offered for the applications on the NoC. Besides, it impacts the performance of a NoC on several metrics, such as the latency, the throughput, the area, etc.

### 2.3.2 Main concepts impacting the latency

The need for a QoS affects the way in which NoC concepts are implemented. Let us first see what are the essential NoC concepts that are used to provide a QoS class.

#### Switching techniques

The switching strategy defines how the flits are transmitted and stored by the routers. There are some points that affect the choice of the strategy, such as the cost, the granularity of data to be transmitted, the complexity of the router and the need of the Quality-of-Service (QoS). The switching techniques are divided into two categories: the circuit-switching and the packet switching [MMM<sup>+</sup>03].

1. Circuit switching: this strategy is usually used to provide guaranteed services, i.e. guaranteed latency, as it reduces the blocking delays. In fact, in this strategy, the connection between two communicating nodes is reserved before the message is sent by the source node. This reservation is only released when the transfer of data is complete and so received by the destination. Thus, the resources (links, buffers) are only used by this communication and could not be used by another pair of nodes willing to communicate via the same path. This strategy is more adapted to transfer large payload in order to compensate the negotiation time to establish the connexion. Here, we can mention SoCBus [WL03] that aims to achieve the real-time guarantees by implementing the circuit switching.

The advantages of this strategy is that the available bandwidth and the latency of the

message are known. However, one of the disadvantages of circuit switching is the inefficient bandwidth usage.

2. Packet switching: In this strategy, packets are injected into the network as soon as the network can accept them, i.e. based on local availability information, without waiting for path setting before sending packets. Thus, in this case there is no guarantee that the path will be entirely available from the source to the destination. Each router takes the decision if a packet should be forwarded to the corresponding output port or whether it should wait in case of unavailability of the port. Thus, a control flow mechanism is required. In case of the unavailability of the port, packets are stored in buffers at intermediate routers.

An advantage of this strategy is the shared network between the communications compared to the circuit-switching where a communication is blocked until the release of the active connexion. Besides, there is no delay to establish a connexion as opposed to circuit-switching. However, this strategy leads to greater delays than on the circuitswitching due to the possible contentions between packets sharing the same resources. Therefore, the packet switching is rather suitable for traffic with low requirements of QoS, i.e. BE. However, it could provide different QoS classes by implementing with specific arbitration mechanisms as we explain later. There are three basic packet switching schemes for forwarding data: store-and-forward (SF), virtual-cut through (VCT) and wormhole [DYN03]. These schemes are differentiated by their packet transmission granularity, i.e. at the flit level or packet level. SF and VCT schemes are not widely used in NoC architectures as they induce a high area cost of a router. Actually, a router should include at each input port a buffer able to store entire packets. Wormhole scheme is the most widely used scheme by NoC [SKH08] and especially to provide a BE service. For this purpose, we are interested by this scheme of packet switching. Let us see the functionality of wormhole switching.

#### Wormhole switching:

Wormhole switching [Moh98] reduces the buffer requirement at the flit level. Thus, the

buffer capacity of the router is a multiple of flits, and so their size is smaller. The packets are transmitted between routers in units of flits, where a flit is transmitted as soon as there is space for one flit in the buffer of the next router. The header flit contains the routing information and the next flits containing data follow contiguously this header in a pipeline fashion. If a packet is blocked, flits of the packet may be stalled on a sequence of routers.

This technique provides a low router latency because they do not have to store the full packets. In addition, the area cost is reduced because the queues are much smaller. However, a packet may occupy several routers at the same time. In this case, it is possible to block the transmission of other packets, leading to a high level of congestion and inefficient use of channel bandwidth due to chained blocking. This chained blocking could lead to deadlock where messages wait for each other and no one can advance any further. To avoid deadlock, specific buffering and/or routing schemes are combined with the wormhole switching. Wormhole switching can provide more efficient network channel utilization. For instance, Tilera [Til11], Mango [BS05], Teraflops [HVS<sup>+</sup>07], Aethereal [GDR05] and Kalray [dDvAPL14] NoCs implement this mode.

### Buffering

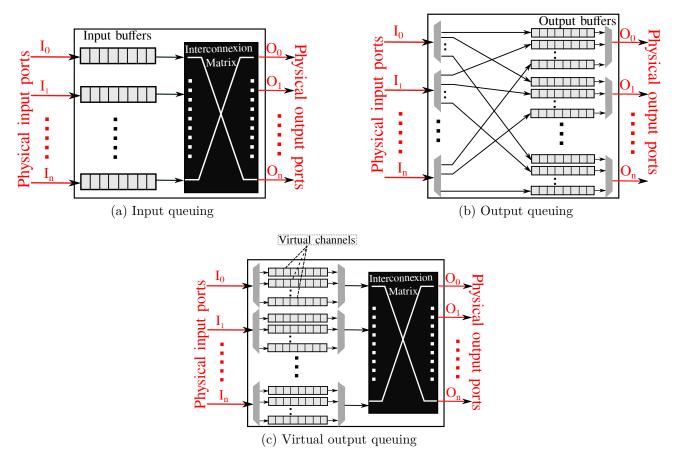

The buffering determines the capacity of storage at the input or output ports of a router. Increasing buffering capacities can improve the latency and the throughput at the price of the cost of area and power. The relative positioning of the buffers at input and output ports of the router is performed using various strategies. In this section, we distinguish three main strategies used in NoC design: input queuing, output queuing and virtual output queuing which are also called by virtual channels [RGR+03].

1. **Input queuing:** In this strategy, N queues are placed at the input ports of the router as illustrated in Figure 2.2a. We note that the router presents N input and N output ports. An arbiter determines when an input queue is connected to an output port so that no conflict occurs. Although this technique is the least expensive on the surface, it

Figure 2.2: The different buffering strategies.

can induce to the Head-of-line blocking problem [KHM87]. This happens when a given data in the head of queue cannot access the associated output port, thus blocking other packets in the queue, even though their output ports are free.

2. Output queuing: When the queues are placed at the output of the router as shown in Figure 2.2b, each output port has a number of output queues equals to the number of input ports. This technique presents higher performance than input queuing but it increases the area cost: for a router of N input ports and N output ports, we need  $N^2$ queues.

These two previous schemes are usually used to provide BE services. However, in order to reduce the waiting delay from which a flow can suffer by waiting a place in the next queues, virtual channels are used.

3. Virtual output queuing or virtual channels: Figure 2.2c illustrates this strategy which combines the advantages of the input and output queuing. Thus, for each input port, there are a number of input queues that help to buffer the incoming packets in function of their destination or of a level of priority. This strategy is also called virtual channels (VCs) [Dal90, MTCM05] as for each physical channel, i.e. the link between two nodes, there are a number of VCs that share the bandwidth of the link. Thus, in this way, a blocked packet can be doubled by another packet sharing the same physical channel, but stored in another VC. It is used to solve the Head-of-Line blocking problem and to increase the router throughput. Although it implies an increase of the area, VCs have several advantages. They are deadlock free and support guaranteed traffic. Thus, this buffering is either coupled with circuit-switching to provide guaranteed latency, as in MANGO NoC, or with the packet switching. However, in the latter case, it should be implemented with the priority arbitration (which is explained in the next paragraph) by using a priority level for each VC to ensure a low latency for the high priority traffic.

#### Arbitration mechanisms

An arbitration mechanism is a way to address the contention problem. At each router, when more than one packet on different input ports, compete for the same output port, the arbitre chooses which input port will transfer the packet. Besides, the arbitration mechanisms are required when VCs are implemented in order to select which VC transfers a flit on a link. In the following, we describe the arbitration mechanisms used in NoCs.

- 1. Time Division Multiple Access (TDMA): This policy is usually coupled with the circuit-switching mode in order to ensure a guaranteed latency (GS) where it leads to straightforward WCTT. This policy divides the time into time-slots. Each time-slot is assigned to a connexion between an input and an output port. Thus, during a time-slot, an input port can have the full access to an output port. However, when these time slots are not carefully aligned, higher latencies cannot be avoided [LRV06]. The Aethereal NoC uses the TDMA with the circuit-switching to ensure guaranteed services.

- 2. **Priority-based:** This policy assigns to each packet an individual priority during its transmission from the source to the destination. Thus, when multiple packets on different input ports contend to the same output port, the packet with the highest priority is granted first. This technique is usually used in real time NoCs where the packets with the highest priority must meet their deadlines. It is especially used with virtual channels where to each VC is assigned a priority level. For example, QNOC [BCGK04] chooses this strategy with virtual channels to provide real-time requirements. However, this policy could lead to a starvation for low priority packets.

- 3. Round-Robin (RR): The RR policy assigns priorities to each input port. In each round of arbitration, the requested input port with the highest priority is served first. But, the request that is served has then the lowest priority in the next round of arbitration [SRM13]. In this way, this policy ensures a fairness between the requested communication from input ports and gives equal chance to the competitors. Besides, it ensures a faster access to an output port than the TDMA policy. Actually, a source port

has to wait its time slot to send packets even when there are any competitors to this output port. The drawback of this policy is that does not differentiate the quality of services demanded by the different packets. Thus, it is usually used in BE NoCs. However, the RR policy is widely used in NoC architectures [TSSJ14] because it is fair and prevents starvation. For example Teraflops [HVS<sup>+</sup>07], Aetheral [GDR05], Tilera [Til11], Kalray [dDvAPL14] and Mango [BS05] NoCs use this strategy.

To summarize, a GS is provided either by the use of a circuit-switching usually coupled with TDMA arbitration and VCs or the implementation of wormhole switching coupled with a priority arbitration and VCs. A BE NoC usually uses the wormhole routing, the RR arbitration and input buffering.

### 2.3.3 Main concepts impacting the design complexity

There are other concepts that have an impact on the design complexity of the NoC, such as the topology, the routing algorithms and the flow control. However, The choice of an implementation of these concepts is not inclusive to a certain QoS class. Let us see what are the different possibilities of these concepts implementations and which one is the most used in the NoCs architecture.

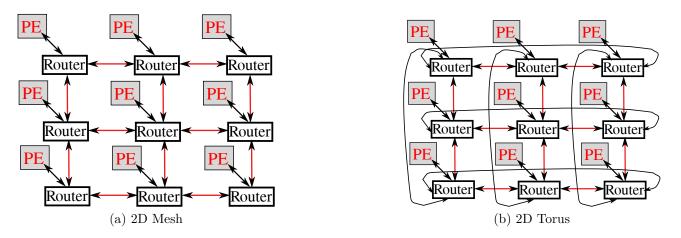

### Topology

The Topology of a network defines how the routers are interconnected using network links. The choice of the topology directly impacts the timing performance and the area. It is the first step in the design of the network as it defines the routing strategy used [BC06].

There are a wide variety of network topologies [DMB06] that are used in NoCs. 2-D mesh and torus topologies, illustrated in 2.3, constitute over 60% of the NoC architectures [SKH08]. They indeed allow to define simple routing rules and provide good electrical properties. However, the most common topology is the 2D-Mesh [IG13], because of the following reasons:

Figure 2.3: Example of topologies that are most used in NoCs.

- 1. It has an acceptable wire cost;

- 2. It presents a reasonably high bandwidth;

- 3. It is easy to group IPs that communicate a lot so that they do not consume any unnecessary high amount of resources in the network.

### **Routing algorithms**

The routing algorithm, implemented at each router, determines which path the packet should take through the network, i.e. the output port from which the packet should be delivered. The selection of the routing algorithm depends on several factors such as the implementation complexity and the performance requirements [OHM05]. Thus, a compromise is needed between an optimal use of the network communication channels and a simple implementation of an algorithm that does not require excessive hardware resources.

A deterministic routing is preferred by NoC designers: according to [SKH08], it is used by more than 70% of the NoCs. It is indeed a simple routing algorithm where the path taken by the packet is completely known in advance for a given source/destination pair [DA93]. Then, it is simple to implement and it is inexpensive. Besides, it presents a low latency when the network is not congested. It is deadlock free when wormhole switching is used. As an example of deterministic routing is the XY routing, which is the popular routing algorithm considered on 2D mesh or torus NoCs [NM93]. An adaptive routing is more complicated to implement [BDM02b] as it provides multiple paths to route a packet from its source to its destination. It may lead to network deadlock or livelock or both. Livelock occurs when a packet does not arrive at its destination and rotates round in the network.

These algorithms can also be determined either at the source (source routing) or constructed sequentially in routers (distributed routing). In the source routing, the source determines the whole path of the packet which will be indicated in the header. In the distributed routing, each router chooses the next destination in function of the final destination. The source routing is simpler than distributed routing but cannot adapt paths in case of traffic congestion as the paths are pre-computed offline. As an example of NoCs that uses the source deterministic routing, we can cite Tilera [Til11] and Mango [BS05] NoCs.

#### Flow control

The choice of the flow control strategy depends on which switching and buffering schemes/strategies are used. Because of the limited capacity of buffers, a flow control is necessary to avoid buffers to overflow and thus to reject some data. Thus, flow control ensures that a router cannot send any data to the next router if there is not enough space available to buffer it. The common control flow mechanisms proposed in the literature are the followings: ON/OFF [CPC08], credit-based protocol [BS04, DRGR03, RDG<sup>+</sup>04] and ACK/NACK [PABB05]. The ON/OFF strategy minimizes the amount of the backpressure signaling by sending only a single control bit that indicates to the upstream router whether it is allowed to send (on) or not (off). In the credit-based mechanism, there is a counter in each upstream router to keep track of the number of free flits within the downstream router. Thus, a router can send a number of flits corresponding to the number of credits. Finally, in the ACK/NACK protocol, the logic flow control must acknowledge each flit received by the receiver port.

In the literature, the credit-based scheme is the most widely used in NoCs because of its high performance with limited buffering [Gai15].

# 2.4 Assumed NoC architecture

This chapter has introduced the different concepts of NoCs and how they can be implemented to provide different classes of QoS. Thus, designing a NoC is difficult as it depends on a large number of parameters. This design is affected by the QoS needed and by a trade-off between the complexity/cost and ensuring a minimum throughput/latency. In order to give a general view on the state-of-the-art on the NoCs, we present a table summarizing a set of NoCs architectures (Table 2.1). For a more exhaustive list, [SKH08] lists sixty architectures of NoCs. We classify these works into the following types: BE (Best-Effort) NoCs providing a good average performance, GS (Gauaranteed-Services) NoCs providing hard real-time requirements or GS and BE NoCs where the routers are more complex as they include two switching mode.

The majority of NoCs uses the mesh topology which is explained by the fact that it is the simplest and most flexible solution to implement. Some NoCs rely on torus topology in the aim to reduce the network diameter which could reduce the latency. Also, we can identify that the round-robin scheme is predominating other arbitration policies. Mostly about 70% of NoCs [SKH08] use the deterministic routing due to its advantages over the adaptive routing as mentioned before. Besides, in order to reduce the cost area of routers and especially buffers, virtual channels and output queuing are avoided.

However, the parameters that are directly related to the QoS are the switching mode and the arbitration mechanism. We can notice that wormhole switching with the round-robin arbitration are the most common mechanisms used in BE NoCs, as it provides lower latency, smaller and faster routers than other techniques [LRV06]. In GS NoCs, the virtual or pure circuit switching is more used and it is coupled with TDMA to ensure a higher predictability for the network as Aethereal [GDR05] and Nostrum [PJ06, MNTJ04]. Other NoCs use the packet switching mode with the priority-based arbitration to ensure guaranteed services such as QNoC [BCGK04] and Faust [DBL05] NoCs. Thus, in order to provide guarantees to hard real-time traffic, GS NoCs present a complex hardware architecture. Thus, no contentions can occur by design, leading to straightforward WCTT for packets but with penalizing the average performance. Besides, none of these NoCs targeting hard real-time constraints are available in commercially existing

|               | SCC [HDV+11]                     | <b>Topology</b><br>Mesh | Switching mode<br>Virtual-cut through   | Buffering<br>VOQ (8 VCs | Buffering<br>OQ (8 VCs) | eringRouting8 VCs)Source deterministic |                                                      |

|---------------|----------------------------------|-------------------------|-----------------------------------------|-------------------------|-------------------------|----------------------------------------|------------------------------------------------------|

| $\mathbf{BE}$ | Teraflops[HVS+07]                | Mesh                    | Wormhole                                | VOQ (2 VCs)             | d                       | deterministic adaptive                 | eterministic adaptive On/OFF                         |

|               | Tilera [Til11]                   | Mesh                    | Wormhole                                | Input                   |                         | Source deterministic                   | Source deterministic Credit-based                    |

|               | Kalray [dDvAPL14] Torus modified | Torus modified          | Wormhole                                | Output                  |                         | Source deterministic                   | Source deterministic source-based                    |

|               | Proteo [STAN04]                  | Ring                    | virtual cut-through                     | I                       |                         | Source deterministic                   | Source deterministic -                               |

|               | Xpipes [BB04]                    | ı                       | wormhole                                | ı                       |                         | Source deterministic                   | Source deterministic -                               |

|               | Spin [AG03]                      | Tree                    | wormhole                                | I                       |                         | Distributed adaptive                   | Distributed adaptive -                               |

|               | Octagon [KND02]                  | Ring                    | wormhole                                | I                       |                         | Source deterministic                   | Source deterministic -                               |

|               | SoCBUS [WL03]                    | Mesh                    | Circuit                                 | Input                   | $\square$               | idtributed Deterministic               | idtributed Deterministic ACK/NACK                    |

| $\mathbf{GS}$ | Faust [DBL05]                    | Mesh                    | wormhole                                | VOQ (2 VCs)             |                         | source deterministic                   | source deterministic ACK/NACK Priority-based         |

|               | QNoC [BCGK04]                    | Mesh                    | wormhole                                | VOQ                     |                         | Source deterministic                   | Source deterministic   credit-based   Priority-based |

|               | Aethereal [GDR05]                | Mesh                    | Wormhole + Circuit                      | Input                   |                         | Source deterministic                   | Source deterministic Credit-based RRA + TDM          |

| GS + BE       | MANGO [BS05]                     | Mesh                    | Wormhole + Circuit                      | VOQ (8 VCs)             |                         | Source deterministic                   | Source deterministic Credit-based                    |

|               | Nostrum [PJ06]                   | Mesh                    | Store&forward + Circuit $ $ VOQ (8 VCs) | t VOQ (8 VCs)           |                         | Adaptive                               | Adaptive -                                           |

Table 2.1: Table reporting some examples of NoC architectures.

many-core architectures.

In hard real-time systems, analytic methods are used to compute the WCTT in BE NoCs. For instance, Tilera [Til11] and Kalray [dDvAPL14] are commercially BE NoCs. Besides, this class of QoS optimizes the average network resources usage. For this reason, we base our work on an existing commercial NoC architecture and we choose a Tilera like NoC. Tilera is a commercial BE NoC implementing the most common used options (Mesh topology, Wormhole switching, Round-Robin arbitration, input buffers). Besides, the documentation on this architecture was available when this study was made.

In this work, we are interested in real-time packet schedulability analysis for many-cores networks. Thus, we need to analyze the worst-case behavior for both inter-core and core to external memories or peripherals communications by taking into account the different contentions that could occur between packets. The next chapter presents a state-of-the-art of the existing methods that are used to analyze, compute and reduce the WCTT.

# Chapter 3

# Related works around Worst Case Traversal Time (WCTT)

## Contents

| 3.1 WCTT over wormhole networks                  | 26 |

|--------------------------------------------------|----|

| 3.1.1 Priority-based wormhole networks           | 26 |

| 3.1.2 BE wormhole networks and recursive methods | 29 |

| 3.2 Contention-aware mapping                     | 31 |

| 3.2.1 Task mapping                               | 32 |

| 3.2.2 Application mapping                        | 34 |

| 3.3 WCTT and mapping baseline references         | 37 |

Chapter 2 has shown different NoCs architectures that provide different classes of QoS. Regardless of the NoC architecture, in distributed hard real-time systems, the WCTT of all the packets generated by a flow must be lower than a predetermined deadline. Such real-time packet schedulability analysis have been done for various types of networks by taking into account the type of contentions that can occur between flows. The challenge lies in the ability to define analysis techniques that have a limited complexity, in order to give results in a reasonable amount of time, and at the same time compute WCTT values that are not too pessimistic. The complexity of the analysis depends on the NoC concepts implemented. Virtual circuit switching relying on a TDMA leads to WCTT that can be easily computed. In fact, no contention can therefore occur. However, in wormhole networks, the analysis of the system behavior becomes more complex due to different types of interferences. Thus, in this chapter, we focus on approaches used to compute the WCTT over wormhole networks. Even we have assumed a BE NoC architecture in the remainder of the work, we focus in this chapter not only on BE wormhole networks but also on priority-based wormhole networks. Actually, we are interested to present how the existing approaches model the behavior of the wormhole switching. Besides, we show how they consider the different types of interferences in the computation of the WCTT. On the other hand, the WCTT depends on the mapping of the application. Thus, another challenge lies in the ability to reduce the congestion incurred by the flows, whether belonging to the same application or not. At the end of the chapter, we present a state-of-the-art on the mapping strategies used to reduce the contentions between flows and thus their WCTT.

# 3.1 WCTT over wormhole networks

In this section, we present a state-of-the art on the approaches used to analyze the WCTT on priority-based wormhole networks and BE wormhole networks.

# 3.1.1 Priority-based wormhole networks

Real-time communication over wormhole networks were studied before NoCs were introduced. The most important mechanism in a wormhole real-time network is the use of virtual channels. Moreover, coupled with a mechanism for preemptive priorities, it allows a message to temporarily stop the transmission of another lower priority message.