En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ FÉDÉRALE TOULOUSE MIDI-PYRÉNÉES

#### Délivré par :

l'Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

#### Présentée et soutenue le 05/12/2016 par :

#### ALI ALHAMWI

Co-design Hardware/Software of Real time Vision System on FPGA for Obstacle Detection

#### **JURY**

MICHEL DEVY

HICHEM SNOUSSI

JULIEN DUBOIS

JEAN FRANÇOIS NEZAN

BERTRAND VANDEPORTAELE

Président du Jury Rapporteur Rapporteur Examinateur Examinateur

## École doctorale et spécialité:

EDSYS: Systèmes embarqués 4200046

Unité de Recherche:

Laboratoire d'analyse et d'architecture des systèmes

Directeur(s) de Thèse :

$Jonathan\ PIAT$

Rapporteurs:

Hichem Snoussi et Julien Dubois

#### Remerciements

Ce travail est le fruit d'une thèse effectuée au laboratoire LAAS-CNRS Toulouse, les travaux de cette thèse n'auront jamais pu voir le jour sans le soutien de nombreuses personnes auxquelles je voudrais exprimer ma profonde reconnaissance.

Tout d'abord je tiens à remercier mon directeur de thèse, Jonathan Piat qui m'a soutenu constamment durant la préparation de ce doctorat. Un grand merci à Bertrand Vandeportaele pour les discussions fréquentes sur les travaux, sur les blocages, sur les outils disponibles, et pour les nombreuses corrections faites sur le manuscrit.

Je remercie chaleureusement Monsieur Julien Dubois, Maître de Conférences à l'Université de Bourgogne, et Monsieur Hichem Snoussi, Professeur à l'université de technologie de Troyes pour l'intérêt qu'ils ont bien voulu porter à ces travaux et pour les précieuses remarques qu'ils ont apportées.

Ensuite je tiens à remercier Monsieur Michel Devy, pour l'honneur qu'il me fait en acceptant de présider le jury de cette thèse. Je remercie également Monsieur Jean François Nézan, Professeur à l'université de Renne, pour l'intérêt qu'il a porté à ce travail en acceptant d'en être un examinateur.

Je tiens à remercier toutes les personnes que j'ai pu côtoyer au LAAS ainsi que tous mes collègues et amis. J'adresse un grand merci à mes chers parents, mes frères et sœurs, Nadine, Sabrine, et Rabee qui illuminent ma vie. Ils ont accepté ma mauvaise humeur sans savoir les raisons et ont toujours été présents quand j'avais besoin.

#### Abstract

Obstacle detection, localization and occupancy map reconstruction are essential abilities for a mobile robot to navigate in an environment.

Solutions based on passive monocular vision such as Simultaneous Localization And Mapping (SLAM) or Optical Flow (OF) require intensive computation. Systems based on these methods often rely on over-sized computation resources to meet real-time constraints. Inverse Perspective Mapping allows for obstacles detection at a low computational cost under the hypothesis of a flat ground observed during motion. It is thus possible to build an occupancy grid map by integrating obstacle detection over the course of the sensor.

In this work we propose hardware/software system for obstacle detection, localization and 2D occupancy map reconstruction in real-time. The proposed system uses a FPGA-based design for vision and proprioceptive sensors for localization. Fusing this information allows for the construction of a simple environment model of the sensor surrounding. The resulting architecture is a low-cost, low-latency, high-throughput and low-power system.

# Contents

| 1  | Inti                  | roduction 1                                                     |    |  |  |  |

|----|-----------------------|-----------------------------------------------------------------|----|--|--|--|

| In | $\operatorname{trod}$ | uction                                                          | 1  |  |  |  |

|    | 1.1                   | Thesis Context                                                  | 3  |  |  |  |

|    | 1.2                   | Thesis Objectives                                               | 5  |  |  |  |

|    | 1.3                   | Document Organisation                                           | 6  |  |  |  |

| 2  | Obs                   | stacles Detection Methods                                       | 7  |  |  |  |

|    | 2.1                   | Introduction                                                    | 7  |  |  |  |

|    | 2.2                   | Obstacle Detection based on Sonar and Radar sensors             | 8  |  |  |  |

|    | 2.3                   | Obstacle Detection based on Lidar sensors                       | 9  |  |  |  |

|    | 2.4                   | Obstacle Detection based on vision sensors                      | 10 |  |  |  |

|    |                       | 2.4.1 Methods based on Optical Flow                             | 10 |  |  |  |

|    |                       | 2.4.2 Methods based on Stereo vision                            | 12 |  |  |  |

|    |                       | 2.4.3 Methods based on Pattern Recognition                      | 15 |  |  |  |

|    |                       | 2.4.4 Methods based on Inverse Perspective Mapping              | 16 |  |  |  |

|    |                       | 2.4.5 Methods based on active vision sensors                    | 17 |  |  |  |

|    | 2.5                   | Conclusion                                                      | 18 |  |  |  |

| 3  | The                   | eoretical Background                                            | 21 |  |  |  |

|    | 3.1                   | Introduction                                                    | 21 |  |  |  |

|    | 3.2                   | Pinhole camera model                                            | 22 |  |  |  |

|    |                       | 3.2.1 Intrinsic parameters                                      | 23 |  |  |  |

|    |                       | 3.2.2 Extrinsic parameters                                      | 23 |  |  |  |

|    |                       | 3.2.3 Radial Distortion                                         | 24 |  |  |  |

|    | 3.3                   | Inverse Perspective Mapping                                     | 26 |  |  |  |

|    | 3.4                   | Obstacle segmentation                                           | 29 |  |  |  |

|    |                       | 3.4.1 Gaussian filter                                           | 29 |  |  |  |

|    |                       | 3.4.2 Otsu's binarization                                       | 30 |  |  |  |

|    |                       | 3.4.3 Morphological operators                                   | 32 |  |  |  |

|    | 3.5                   | Bird's eye transformation                                       | 32 |  |  |  |

|    | 3.6                   | Obstacle localization                                           | 35 |  |  |  |

|    | 3.7                   | Free space detection                                            | 35 |  |  |  |

|    | 3.8                   | Obstacle distance                                               | 37 |  |  |  |

|    | 3.9                   | Conclusion                                                      | 37 |  |  |  |

| 4  | Em                    | bedded Systems Platforms and Design                             | 39 |  |  |  |

|    | 4.1                   | Introduction                                                    | 39 |  |  |  |

|    | 4.2                   | General purpose Processing on Graphical Processing Unit (GPGPU) | 40 |  |  |  |

|    | 4.3                   | Multi-Core CPUs                                                 | 41 |  |  |  |

vi Contents

|   | 4.4 |                  | cation-Specific Integrated Circuit 4                                                                                      |

|---|-----|------------------|---------------------------------------------------------------------------------------------------------------------------|

|   | 4.5 |                  | Programmable Gate Array (FPGA) 4                                                                                          |

|   | 4.6 | FPGA             | A Designs Properties                                                                                                      |

|   |     | 4.6.1            | Pipelined Designs                                                                                                         |

|   |     | 4.6.2            | Designs with reduced latency                                                                                              |

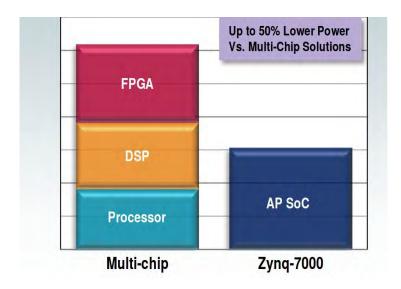

|   |     | 4.6.3            | Power consumption consideration 4                                                                                         |

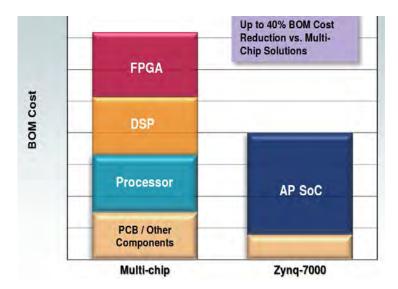

|   |     | 4.6.4            | Cost and Size Requirements                                                                                                |

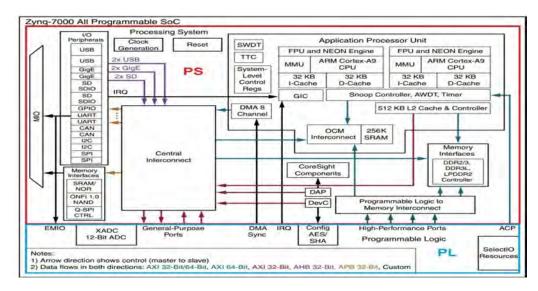

|   | 4.7 | Zynq-            | 7000 all programmable SoC                                                                                                 |

|   | 4.8 | Xillyb           | us IP Core                                                                                                                |

|   | 4.9 | Concl            | usion $\dots \dots \dots$ |

| 5 | Pro | $\mathbf{posed}$ | Optimizations to System Methodology 5                                                                                     |

|   | 5.1 | Introd           | luction                                                                                                                   |

|   | 5.2 | Obsta            | cle bearings based on polar histogram 5                                                                                   |

|   | 5.3 | Obsta            | cles localization in the ground plane                                                                                     |

|   | 5.4 | 2D O             | ccupancy Grid Map Reconstruction 6                                                                                        |

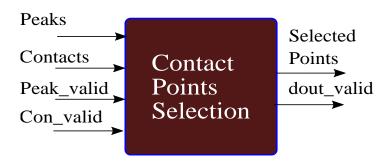

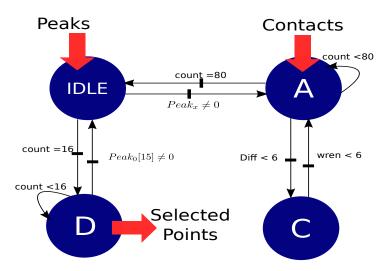

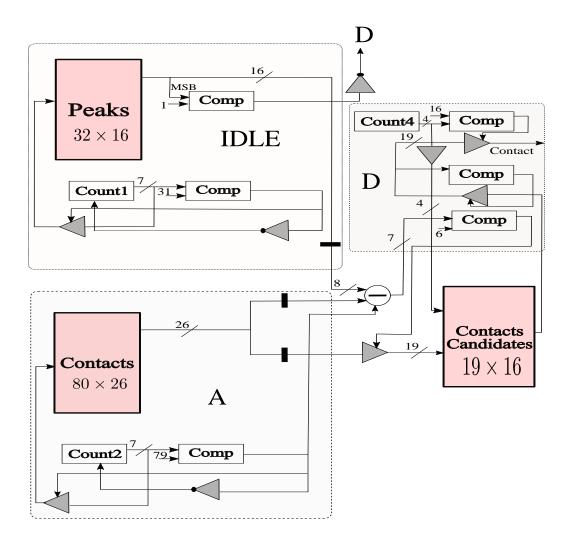

|   |     | 5.4.1            | Contact Points Selection                                                                                                  |

|   |     | 5.4.2            | Map Reconstruction                                                                                                        |

| 6 | Har | dware            | IP Cores 6                                                                                                                |

| • | 6.1 |                  | luction                                                                                                                   |

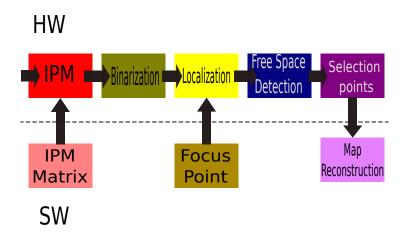

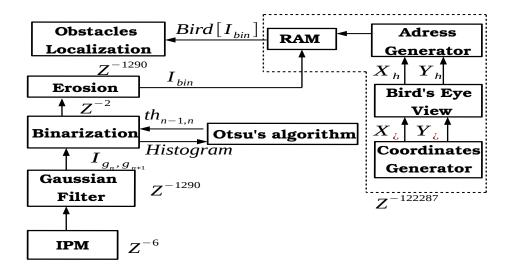

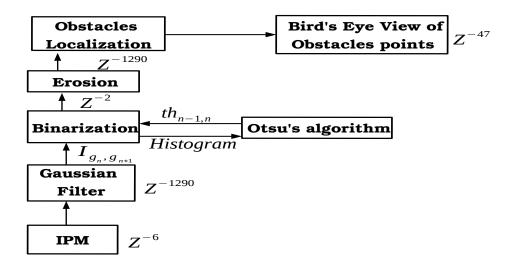

|   | 0.1 | 6.1.1            | Obstacle Detection and Localization Systems 6                                                                             |

|   |     | 6.1.2            | 2D occupancy Grid Map System 6                                                                                            |

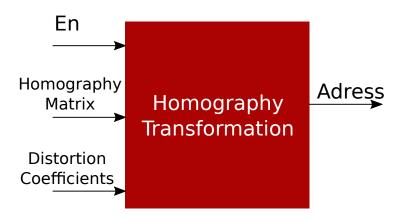

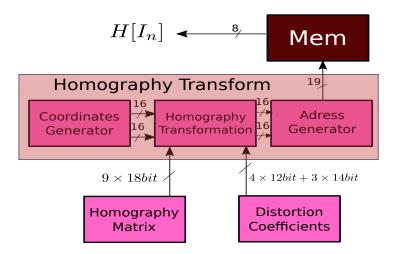

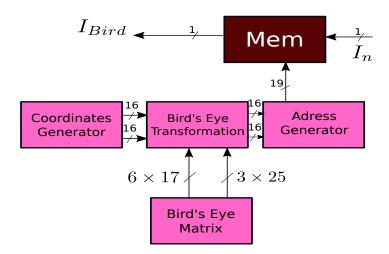

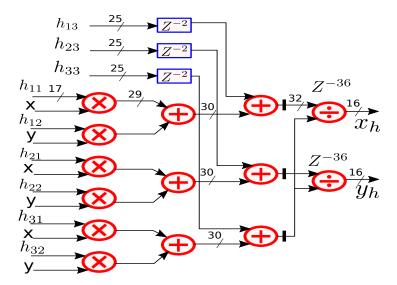

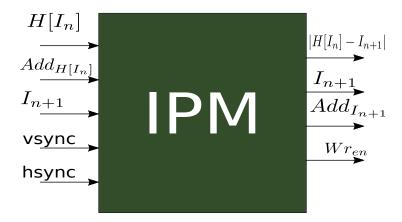

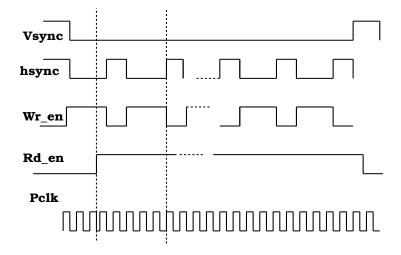

|   | 6.2 |                  | graphy transformation                                                                                                     |

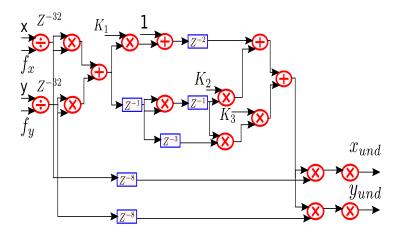

|   | 0.2 | 6.2.1            | Coordinates Generator                                                                                                     |

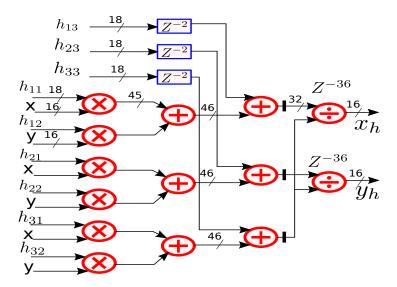

|   |     | 6.2.2            | Distortion correction and Homography transformation 7                                                                     |

|   |     | 6.2.3            | Address Generator                                                                                                         |

|   |     | 6.2.4            | Software part of Homography transformation                                                                                |

|   |     | 6.2.5            | Performance and Comparison with homography module in                                                                      |

|   |     | 0.2.0            | [Botero 2012]                                                                                                             |

|   | 6.3 | Bird's           | s eye transformation                                                                                                      |

|   | 0.0 | 6.3.1            | Resource Utilization and Latency                                                                                          |

|   | 6.4 |                  | and Subtraction                                                                                                           |

|   | 0.1 | 6.4.1            | Resource Utilization and Latency                                                                                          |

|   | 6.5 |                  | ian Filter                                                                                                                |

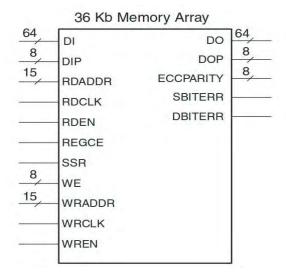

|   | 0.0 | 6.5.1            | Memory organization                                                                                                       |

|   |     | 6.5.2            | Convolution and Delay                                                                                                     |

|   | 6.6 |                  | zation                                                                                                                    |

|   | 0.0 | 6.6.1            | Hardware implementation of Otsu's method 8                                                                                |

|   |     | 6.6.2            | Resource Utilization and Latency                                                                                          |

|   | 6.7 |                  | on operator                                                                                                               |

|   | 6.8 |                  | acles localization                                                                                                        |

|   | 0.0 | 6.8.1            | Left and Right Scan                                                                                                       |

|   |     | 6.8.2            | Resource Utilization and Latency                                                                                          |

|   |     | 0.0.4            | Tresource Offication and Datelley                                                                                         |

Contents

|              | 6.9    | Free s                                        | pace detection module                                                                 | 99  |

|--------------|--------|-----------------------------------------------|---------------------------------------------------------------------------------------|-----|

|              |        | 6.9.1                                         | Resource Utilization and Latency                                                      | 104 |

|              | 6.10   | 2D Oc                                         | cupancy Map Reconstruction                                                            | 104 |

|              |        | 6.10.1                                        | Contact Points selection Module                                                       | 104 |

|              |        | 6.10.2                                        | Map Reconstruction                                                                    | 106 |

| 7            | Res    | ults an                                       | d Experiments                                                                         | 109 |

|              | 7.1    | Introd                                        | $\operatorname{uction}$                                                               | 109 |

|              | 7.2    | Obstac                                        | cle Detection and Localization System Experiment                                      | 110 |

|              |        | 7.2.1                                         | Comparison of the results between hardware and software                               | 111 |

|              |        | 7.2.2                                         | implementation                                                                        |     |

|              | 7.3    | -                                             | •                                                                                     |     |

|              | 1.5    | 7.3.1                                         | cupancy Grid Map Reconstruction Experiment                                            |     |

|              | 7.4    |                                               | Comparison to the state of art                                                        |     |

|              | 1.4    | 7.4.1                                         | Hardware Level                                                                        |     |

|              |        | 7.4.1 $7.4.2$                                 | Firmware Level                                                                        |     |

|              | 7.5    | Conclu                                        |                                                                                       |     |

|              | 7.5    | Concie                                        |                                                                                       | 132 |

| 8            | Con    | onclusion                                     |                                                                                       | 137 |

| $\mathbf{C}$ | onclu  | sion                                          |                                                                                       | 137 |

|              | 8.1    | Propos                                        | sed System Methodology                                                                | 137 |

|              | 8.2    | 2 Proposed Hardware Architectures and Designs |                                                                                       |     |

|              |        | 8.2.1                                         | Obstacles detection and localization architecture with bird's eye view transformation | 140 |

|              |        | 8.2.2                                         | Obstacles detection and localization architecture with our lo-                        |     |

|              |        |                                               | calization method                                                                     |     |

|              |        | 8.2.3                                         | 2D occupancy grid map reconstruction architecture                                     |     |

|              | 8.3    | Future                                        | Works                                                                                 | 141 |

| B            | ibliog | raphy                                         |                                                                                       | 143 |

viii Contents

# Introduction

Making a robot see was something in higher difficulty levels at the mid-twentieth century. After fifty years, researchers have achieved outstanding theoretical and practical successes. A broad field, called Computer Vision, has emerged as a discipline strongly affiliated to mathematics and computer science. Great progress has been achieved in the description of the way the appearance of objects changes when viewed from different viewpoints, and the expression of these changes as functions of objects shape and camera parameters. In the field of geometric computer vision, good math methods were introduced to explain the relations between objects in images and objects in world. On the practical side, we can cite the possibility of guiding a car through regular roads, recognition of road signs, pedestrian detection, forward collision warnings, vision guided robots (VGR) system, and many other applications demonstrated around the world. These achievements wouldn't be realized without sophisticated mathematical methods.

Not only are computer vision realizations grateful to mathematical algorithms, but also to the emergence of powerful, low-cost, and energy-efficient electronics. Every day we interact with many tiny computers. These small chips are the infrastructure of our modern world. An embedded system merges different kinds of devices (mechanical, electrical, chemical, ...etc) into one small computer in order to perform dedicated functions. Embedded systems are every where, in our homes, our phones, our cars, our cities, and even embedded in our bodies [Harris 2015]. Hence, these small devices are shaping our world today. Nowadays, embedded systems solutions become more useful and cost effective, and growing consumer interest in robotics.

With these tiny chips, it has become possible to integrate practical computer vision capabilities into embedded systems. The term "Embedded vision" refers to the use of computer vision in embedded systems [Dipert 2014b]. This topic is the subject of intensive ongoing research and development. The main purpose of embedded vision research is to adequate between desktop prototyping of vision algorithms and operational embedded systems environments.

Today, embedded vision creates a lot of opportunities in the markets in which it is used [Bier 2013], [Alliance 2016]. For example, Kinect video game controller is considered one of the fastest-selling electronic products. This product takes advantage of embedded vision to track users movements without the need for

hand-held controllers, makes video games accessible to all people [Bier 2013], [Bier 2011]. Another interesting application of embedded vision is video content analysis which can generate and organize video contents.

In robotics, the most of successful applications are based on embedded vision technology. It is commonly used to guide robots during navigation tasks, perform quality control, assemble automotive, to name a few [Quevedo 2012], [Dopplinger 2012]. Another interesting application is the use of embedded vision in surgery and healthcare [Hartford 2013]. Through mobile phone applications, functions like monitoring skin lesions for danger signs can be successfully performed.

Embedded vision based security applications is considered as a promising technology in the security market [Dipert 2014b], [Fularz 2015]. Vision systems are deployed in airports for surveillance tasks. The improvements in hardware platforms (processors, sensors) and algorithms allow to perform sophisticated surveillance applications, such as alert generation when an object is leaved or removed, reading vehicle license plate, .....etc.

In automotive area, automotive safety becomes one of the most exciting topic today. ADAS (Advanced driver assistance systems) systems based on embedded vision are mainly used to provide different technologies, including objects (pedestrian and vehicle) detection, lane detection and traffic sign recognition [Dipert 2014a], [Toyota 2016]. One of the promising implementations of embedded vision is the driver monitoring. The purpose of this technology is to monitor the driver's condition to ensure alerts while driving, by analyzing head, eye, and body movements [Dipert 2014c], [Routray 2011]. Parking assistance is another embedded vision application which is widely deployed in modern vehicles.

Let's cite Augmented reality which uses embedded vision technology to view computer-generated graphics in physical real world [Meier 2014], [Wilson 2014]. Due to the emergence of powerful embedded platforms, complex vision algorithms can be performed by mobile devices providing a sufficient processing performance at low cost and power consumption.

Embedded vision technology can touch every aspect of daily lives. The integration of vision capabilities (incorporating gesture recognition, face detection, facial recognition and eye tracking, ....etc) into existing products will make these products more responsive and easier to use. The market research of embedded vision is highly grown during last years. Research departments of large companies predict a good annual revenue growth due to embedded vision applications.

Figure 1.1: A typical transport robot, and an indoor environment model taken from [Neobotix 2016]

## 1.1 Thesis Context

The general context of this thesis is autonomous visual navigation of mobile robots in indoor environments. Intended applications are transport robots in factories or logistics centres. In research, the focus is in the exploration of unknown areas of buildings, and static environments modeling. For this purpose, different methods have been developed to achieve time-efficient exploration [Wettach 2016], [Arndt 2016]. For example, large ground floors in an office building can be detected and mapped, thus making easy to accomplish transport or monitoring tasks automatically. Autonomous robots navigating in such environments can be used to produce reliable exploration systems with reduced total cost, providing a complete description of the environment. Figure 1.1 shows a robot kit mainly used as a transport system for different scenarios in indoor environments. Such robots could react to the changes of its surrounding without danger of collision. Additionally, they are capable to autonomously explore unknown areas and build an occupation map. This latter serves as a reference for transport tasks.

Another important application is the use of indoor mobile robots for the care of elderly. For example, when an emergency situation is detected, a fast navigation (reduced latency, high throughput) in a typical apartment environment is required to perform emergency procedures or to support specific household tasks. Hence, the response time of a robot in such situations is a an important problem. With the help of visual navigation methods, the implementation of service tasks can be more efficient.

LAAS has participated to several projects devoted for indoor navigation.

Figure 1.2: On the left, Robot's and eldercare's future taken from [Smith 2013]. On the right taken from [Aging 2015]

Different hardware-software designs and implementations of well-known vision-based obstacle detection and identification have been developed. For example, an obstacle detection system was developed in the PhD of M.Ibarra Manzano [MANZANO 2011]. The system is performed using a belt of micro-cameras mounted on a robot. Obstacle detection task is accomplished by a method based on pixel classification from color and texture descriptors.

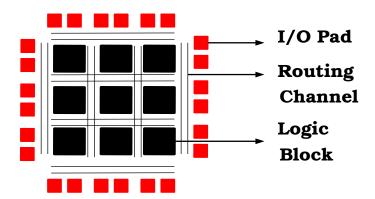

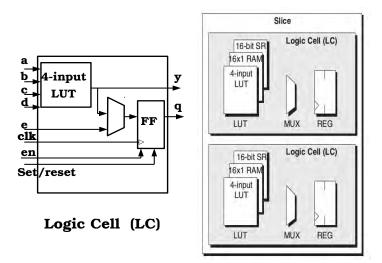

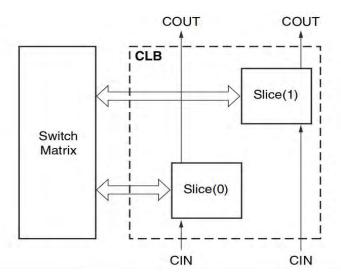

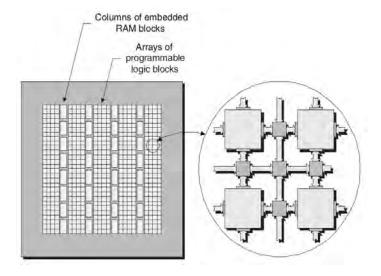

One of the key aspects of development is hardware prototyping on FPGAs (Field Programmable Gate Arrays) for which the algorithm-level and hardware-level optimizations are prevalent. As throughput and latency are regarded as limiting factors for the reactivity of robots, hardware prototyping on FPGAs is used to produce high throughput and low latency architectures. Different algorithms and architectures based on FPGA were developed in the PhD of D.Botero Galeano [Botero-Galeano 2012] for obstacle detection, and to perform localization using multi-spectral cameras.

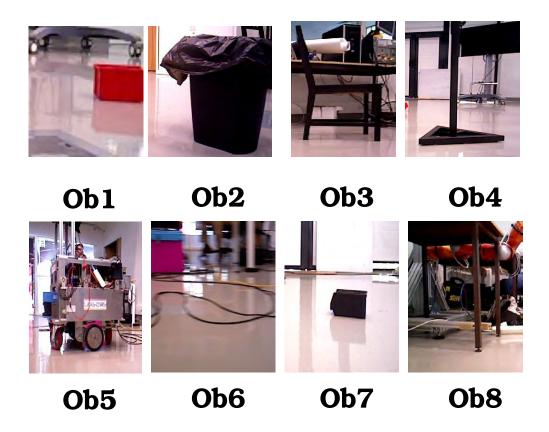

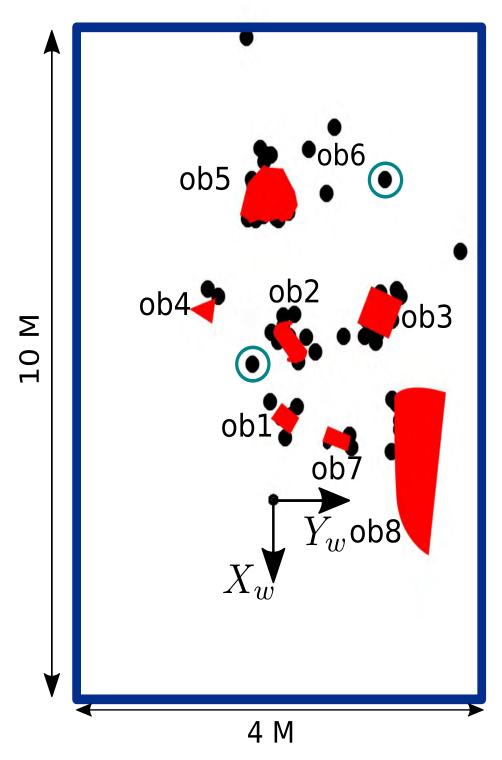

This thesis is developed in the context of CAMERA BELT project. The project aims to build an embedded vision system multi-camera for obstacle detection and localization of a robot navigating in indoor environments. In this project, the hardware architecture will include 8 camera sensors mounted on a robot and connected to FPGAs. The 8 images acquired from different viewpoints allow to build a 2D occupancy map, thus making easy to accomplish navigation task in indoor environments. The complexity resulting from the use of an FPGA target to process multiple images acquired at the same instant imposes different constraints about the choice of obstacle detection method. This latter must be simple and reliable when it is implemented in a hardware architecture.

## 1.2 Thesis Objectives

The objective of this thesis is to design a real time vision system for a robot navigating in indoor environments. The proposed system is devoted to the obstacle detection and localization problems. Additionally, the designed system must facilitate navigation task by building a 2D occupancy map that represents obstacles localization in the ground plane.

In this thesis, we will propose the system parts, and design a hardware module for each part of the system (for image acquisition, distortion correction, homography transformation, Inverse Perspective Mapping, obstacles segmentation, obstacles localization and 2D occupancy map reconstruction).

In order to perform our system, we set the following objectives:

- Development and validation of an obstacle detection method based on visual information. A hardware module is then designed and implemented on FPGA.

- Development and validation of a method for obstacles segmentation. The method is then modelled in a hardware design and implemented on FPGA.

- Proposing a method for obstacles localization in the ground plane.

- Development and validation of the proposed method. A hardware module is then designed to accomplish the localization task.

- Development and validation of a method for free space detection based on localization module results. A hardware module is then deigned and implemented on FPGA.

- Development and validation of a method to build a 2D occupancy map that represents obstacles localization in the ground plane.

So, Our contributions are as follows:

In methodology level:

- Proposing a method for obstacles localization in the ground plane.

- Building a 2D occupancy grid map based on obstacles localization module results.

In hardware level:

- the hardware design of homography transformation is optimized, distortion correction and homography transformation are merged in one hardware module.

- A hardware architecture is designed for obstacles segmentation task. Different hardware modules are developed to perform Gaussian filter, binarization based on Otsu's algorithm, and morphological operations.

- Two hardware modules are proposed for obstacles localization in the ground plane. The first module is an implementation of a method proposed in the state of art while the second module is an implementation of our proposed method.

- A hardware architecture is designed for free space detection based on a method that exists in the state of art.

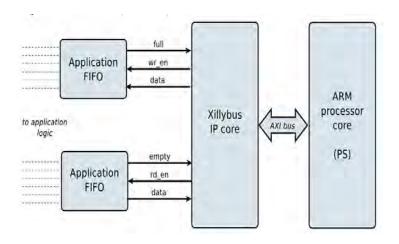

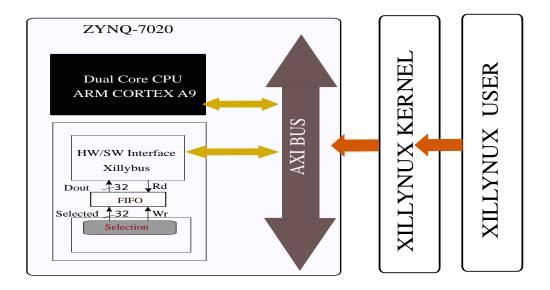

- For rapid system prototyping, a co-design hardware/software is developed using Xillybus core for 2D occupancy grid map reconstruction.

# 1.3 Document Organisation

The thesis is composed of six main chapters introduced as follows:

- Chapter 2 introduces a brief presentation of obstacle detection methods that exist in the state of art. We present sensor types which can support obstacle detection methods. We then present a summary of obstacle detection methods based on visual informations.

- Chapter 3 presents the theoretical background for the different algorithms evaluated during this thesis.

- Chapter 4 explains, by and large, different embedded systems types. A brief presentation is introduced for different embedded systems platforms. Then, we explain in detail the embedded systems based on FPGAs architecture as our proposed architectures are based on FPGAs targets.

- Chapter 5 introduces our contribution to the system methodology. Obstacles localization method, and 2D occupancy grid map reconstruction are described.

- Chapter 6 presents the three proposed architectures and the hardware modules of each proposed system. We describe the design properties for each hardware module coded in VHDL, and the modules integration in the FPGA architecture.

- Chapter 7 presents the results of the proposed architectures. Comparison to the state of art and the software implementation of the methodology are included in this chapter.

Finally, we present a conclusion and the perspective of thesis work.

# Obstacles Detection Methods

| Contents | 8     |                                                     |   |

|----------|-------|-----------------------------------------------------|---|

| 2.1      | Intro | roduction                                           | , |

| 2.2      | Obst  | stacle Detection based on Sonar and Radar sensors 8 | ; |

| 2.3      | Obst  | stacle Detection based on Lidar sensors 9           | ) |

| 2.4      | Obst  | stacle Detection based on vision sensors 10         | ) |

|          | 2.4.1 | Methods based on Optical Flow                       | ) |

|          | 2.4.2 | Methods based on Stereo vision                      | ) |

|          | 2.4.3 | Methods based on Pattern Recognition                | , |

|          | 2.4.4 | Methods based on Inverse Perspective Mapping        | ; |

|          | 2.4.5 | Methods based on active vision sensors              | , |

| 2.5      | Con   | nclusion                                            | ; |

#### 2.1 Introduction

Obstacle detection is a fundamental ability for a mobile robot to operate in a cluttered indoor environment and is essential to perform basic functions like obstacle avoidance and navigation. Traditionally, autonomous navigation systems are equipped with a set of sensors. By interpreting sensors readings, the required informations about obstacles distances in the environment around the robot are extracted. This allows to build a map that represents the occupied and free space of the environment around robot. This is a long studied problem in robotics and a lot of different methods are used to perform this task.

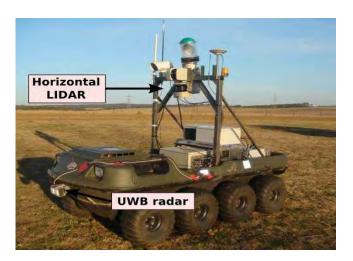

In this chapter, the existing architectures used for obstacle detection and 2D occupancy grid maps reconstruction are introduced. The first part presents obstacle detection systems based on SONAR (SOund Navigation And Ranging), RADAR (RAdio Detection And Ranging), and LIDAR (LIght Detection And Ranging) sensors. The second part will introduce obstacle detection methods based on vision sensors.

Figure 2.1: Detecting parking space using a system based on Radar sensors (taken from [Schmid 2011]).

# 2.2 Obstacle Detection based on Sonar and Radar sensors

Sonar based methods were used in very early research. Thanks to the low cost of ultrasonic sensors, and their good sensing range they have been widely used for obstacle detection and avoidance systems. Sonar methods are based on the computation of time differences between the emission and reception of a ultrasonic signal to compute the distance to a reflective surface. However, data measurements based on ultrasonic sensors are affected by air temperature and humidity. In addition, spatial position detection for obstacles edges is limited by obstacle distances and the angle between obstacle surface and the acoustic axis. Therefore, they prove to be unreliable and give imprecise depth information with low spatial resolution.

Radar based systems works by measuring properties of the reflected radio signals. In [Schmid 2011], a system based on three standard short range radar sensors is used in order to determine parking space in an indoor environment as pictured in 2.1. The drawbacks of Radar systems are that they provide noisy data with low-accuracy. In addition, the high angular uncertainty of radar sensors leads to decrease the accuracy in produced maps. So, Radar systems alone are insufficient to produce accurate terrain traversability maps. Recently, many researches focus in the fusion between these sensors and other active sensors in order to produce 2D occupancy grid maps with high resolution as depicted in [Ahtiainen 2015].

Figure 2.2: Argo robotic platform equipped with Radar and Lidar sensors in [Ahtiainen 2015].

### 2.3 Obstacle Detection based on Lidar sensors

Using Lidar devices for obstacle detection and reconstruction of 2D free space maps has been a standard in robotics for many years. LiDAR works by analyzing the reflected light when objects are illuminated by a laser beam. LiDAR sensors compute the distance from an obstacle by measuring the round-trip time of flight of an emitted pulse (or modulated wave) of light.

LiDAR sensors provide an accurate information, works independent of the ambient light, and offer detailed high rate data of the sensor proximity. This type of sensor gives a 2D information when used in planar or can be used to generate a 3D cloud in scanning mode. Compared to data received from vision sensors, data received from LiDAR scanners is less noisy, more accurate, long range, and precisely show the free space of a robot's environment. However, LiDAR scanners are generally expensive which makes them not suitable for low-cost robotic.

These sensors are also prone to mechanical damages because of their mirror assembly, and provide a performance with low level of vertical resolution. LiDAR may also generate a wrong estimate for black and shiny surfaces [Boehler 2003], and can't be compared to photogrammetric data when a high level of accuracy is required.

Beside, LiDAR measurements suffer from the lack of a rich information about an obstacle due to the sparse nature of data. Compared to vision sensors, LiDAR grids are less informative and more ambiguous.

A simple and practical system based on the 2-D LIDAR LMS511 from SICK is

Figure 2.3: 2D LiDAR SICK LMS511 taken from [Peng 2015].

introduced in [Peng 2015] and shown in figure 2.3. The proposed system uses an algorithm designed for obstacle detection and avoidance.

3D LIDAR scanners allow to build 3D maps of a robots environment. In [Shinzato 2014], a sensor fusion-based solution is proposed for obstacle detection. The proposed approach is based on perspective images acquired from a single camera and a 3D LIDAR.

#### 2.4 Obstacle Detection based on vision sensors

Vision-based methods are becoming increasingly popular due to the dramatic cost reduction of cameras and associated computing architecture. Camera sensors also provide a rich information that can be used for a variety of heterogeneous tasks (obstacle identification, localization, tracking ...). A good vision-based obstacle detection system must be capable of detecting and localizing obstacles at high speed and low latency, avoiding false positive, and minimizing impact on overall system performance (system speed and power consumption).

Vision based algorithms like Optical Flow or SLAM have been widely adopted in robotic applications for obstacle detection task. However, these aforementioned algorithms are regarded as computational intensive methods. The low-cost and richness of the sensor comes with the needs of complex algorithms to extract information from the scene which can make them impractical.

In this section, a brief summary is given for obstacle detection techniques based on optical flow, stereo vision, pattern recognition, and inverse perspective mapping (IPM). These methods are performed using passive vision sensors. Then, techniques based on active vision sensors are introduced.

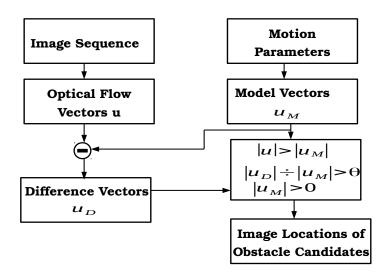

#### 2.4.1 Methods based on Optical Flow

Optical Flow (OF) is a popular technique which is used in many areas [Beauchemin 1995] such as: object detection and tracking, image dominant

Figure 2.4: Obstacle detection approach based on optical flow method (taken from [Enkelmann 1991]).

plane extraction, motion detection, robot navigation and visual odometry. OF is based on the local motion of image elements in image sequences. It aims at computing the motion between two sequential frames. The estimation of optical flow vectors can be done using different approaches divided in two classes: features based methods [Horn 1980], [Smith 1997], [Hildreth 2003], [Castelow 1988] and analytical methods [Enkelmann 1991], [Nagel 1987], [Nagel 1983], [J.Heeger 1988].

The figure 2.4 illustrates the obstacle detection procedure based on the estimation of optical flow vectors. This approach consists of three steps [Enkelmann 1991].

- 1. The local motions (OF vectors) for each pixel of a given grid are measured from the image sequence.

- 2. The prediction of the optical flow model from the measured camera motion is performed.

- 3. The detection of the obstacles is then performed by comparing the optical flow vectors extracted from the images and the optical flow vectors estimated from the motion.

The obstacle detection based on optical flow requires a great computational effort because of the dense sampling it assumes. There is a large work in the literature presenting new solutions for efficient computation and high accuracy. The presented methods are compared to other approaches in terms of computing complexity and accuracy [Silar 2013]. As these methods aim at solving accuracy and computation complexity, the overall performance of a system based on such approaches tends to be lower in terms of real time requirements (frame-rate, latencies). In most cases, OF is a primary phase in more complex vision algorithms.

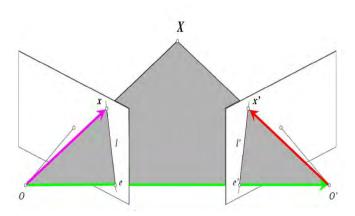

Figure 2.5: Epipolar Geometry [Hartley 2004] [Hoiem 2012]

Many considerations must be taken into account for the available computing resources.

Recent improvements of the computation efficiency have been proposed for optical flow methods by using newly available powerful computing platforms. Because software implementations of this kind of algorithms are not effective enough, some studies have proposed solutions based on dedicated hardware architectures. In [Bako 2015], a real time hardware implementation of the optical flow computation is proposed using an embedded FPGA based platform.

#### 2.4.2 Methods based on Stereo vision

Thanks to the low cost of passive vision sensors, it is possible to integrate two camera to produce stereo vision systems. A system based on stereo vision sensors can extract 3D features from the perceived scene given some requirements on its texture and lighting.

Each camera provides a 2D representation of the environment. By processing two 2D images, one can map each 2D point represented in image coordinate systems to its correspondence in the 3D world coordinate system. The epipolar geometry provides some constraints on the 2D observations given the two camera poses.

Let us introduce some basic notations used in epipolar geometry as shown in figure 2.5.

- The baseline is a line connecting the two camera centers O and  $\grave{O}$ .

- The epipoles are the intersections of the baseline with the image planes in (e) and  $(\grave{e})$ .

- An epipolar plane is a plane containing the baseline OO and a given 3D point X.

- The epipolar lines are the intersections of a given epipolar plane with the image planes in (l) and  $(\dot{l})$ .

The camera matrices containing the intrinsic parameters of the two cameras are supposed known  $(K \text{ and } \hat{K})$ . A 3D scene point (expressed in camera coordinate systems) X (resp.  $\hat{X}$ ) is projected to the first (resp. second) camera to 2D pixel coordinates x (resp.  $\hat{x}$ ) as follows:

$$x = K.X ; \dot{x} = K.\dot{X} (2.1)$$

The first camera's coordinate system is chosen as the world coordinate system. R and T being the rotation and translation between the two camera frames, the 3D scene point X represented in the first camera coordinate system is related to  $\hat{X}$  in the second camera system as follows:

$$X = R\dot{X} + t \tag{2.2}$$

The epipolar constraint enforces that the points X,  $\dot{X}$  and the camera optical centers O and  $\dot{O}$  lie in the same plane:

$$X.[t \times (R\dot{X})] = 0 \tag{2.3}$$

This is rewrote in Eq. 2.4 introducing the Essential matrix E [Hoiem 2012]:

$$X^T E \dot{X} = 0 (2.4)$$

This relation can then be expressed in terms of image coordinates using the Fundamental matrix F:

$$F = K^{-T}E\dot{K}^{-1} \tag{2.5}$$

$$x^T F \grave{x} = 0 \tag{2.6}$$

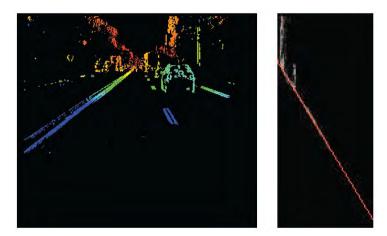

Figure 2.6: Results of the obstacle detection system based on V-disparity in [Labayrade 2002]. The disparity (resp. V-disparity) map is shown on the left (resp. right). The 3D points on the ground lie in a line in the V-disparity map whereas the 3D points on the obstacle (car) do not.

The stereovision configuration allows to constraint possibly matching points between the two images. It reduces the correspondence problem from two dimensions to one. The images from the two cameras can be rectified to obtain synthetic images that would have been acquired in a particular configuration where the epipolar lines are aligned with the horizontal lines of the image planes. In theese rectified images, the matching between pixel can be achieved individually on each line and a single value for each pixel indicates the matching pixel on the same lie in the other image. This value d is named disparity and is related to the depth of the corresponding 3D points in the scene[Miled 2007]. A disparity map is an image where each pixel encodes the corresponding disparity value.

The obstacle detection based on stereo vision has been studied in recent years. In this class of methods, one can cite "The V-disparity" approach in [Labayrade 2002] (see figure 2.6). A detection based on disparity map is performed to extract vertical objects on the scene. In [Ganoun 2009] (see figure 2.7), the authors propose to segment the ground plane and remove it from the disparity map. In [Tarel 2007], the ground is segmented using 3D reconstruction methods.

Different obstacle detection systems were developed in occupancy grid maps framework. In [Badino 2007], three models for occupancy grid map representation based on stereo measurements are presented.

In[Oniga 2010], Digital Elevation Map (DEM), a height based representation, is performed by transforming 3D stereo data measurements into a rectangular digital grid. The authors make use of two classifiers in order to mark DEM cells as road or obstacles. The proposed system is supposed to allow for real time execution due to specific optimizations applied to the software implementation.

Figure 2.7: Tracking multiple targets using a system based on stereo vision (taken from [Ganoun 2009]).

In [Oniga 2015], a method based on a fusion between laser range finder and stereo vision is introduced. The authors claim that the proposed approach is simple and efficient in terms of computational resources, but the performance is limited by the accuracy of the intra-sensor calibration.

# 2.4.3 Methods based on Pattern Recognition

In the field of computer vision, the problem of linking semantics between high level concepts and low level features has been studied. Pattern recognition is a branch of machine learning that focuses on the recognition of patterns and regularities in data [Bishop 2006]. Classification methods used in computer vision are often based on the extraction of features that may include color, texture, shape, or spatial relation informations. Recently, different sophisticated feature extraction techniques have been proposed. An obstacle detection system based on color and/or texture feature algorithms requires an important amount of calculations. Some optimizations have been proposed in [Cervantes 2008] in order to reduce computation time by performing a color-based segmentation before applying a region based classification. The proposed approach is however not suitable for all applications. In [Manzano 2010], a hardware based architecture based on texture-color classification is proposed in order to detect specific objects on the scene. Classifier parameters are learnt offline from ground examples. Hence, the proposed system is able to detect obstacles on indoor environment as shown in figure 2.8.

Image features based on HOG (Histogram of Oriented Gradient) [Dalal 2005] and SIFT (Scale Invariant Feature Transform) [Lindeberg 2012], [Lowe 1999] have been

Figure 2.8: Obstacle detection based on terrain classification (taken from [Manzano 2010]).

widely used. Support vector machine (SVM) classifier [Shawe-Taylor 2000] with these features becomes one of the popular techniques used for obstacle detection. In [Lee 2015] an approach is introduced in order to reduce computing time of (SVM) by reducing the dimension of HOG feature. Authors claim that they can speed-up SVM classifier for vehicle detection by about three times while maintaining the original detection performance [Lee 2015].

#### 2.4.4 Methods based on Inverse Perspective Mapping

Inverse perspective mapping IPM is a geometrical transformation where an initial image is used in order to produce a new image for the same scene from a different position. This method is essentially based on the angle of view of the objects in the scene and their distances from camera due to the perspective effect.

IPM transformation is influenced by the camera extrinsic parameters (position and orientation) and intrinsic parameters (focal, principal point and optical distortions). This transformation is computed for the ground plane in the scene. A subtraction is performed for each pixel between the transformed previous and current (acquired at the new position) images.

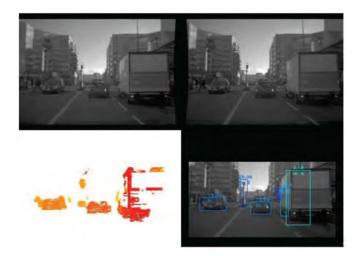

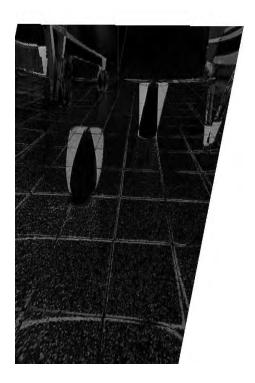

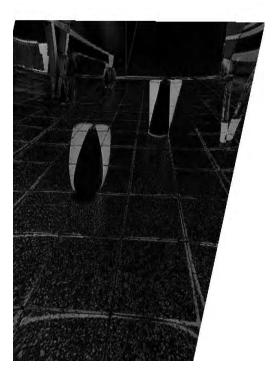

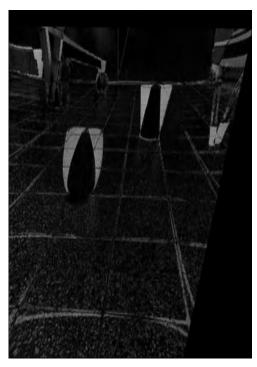

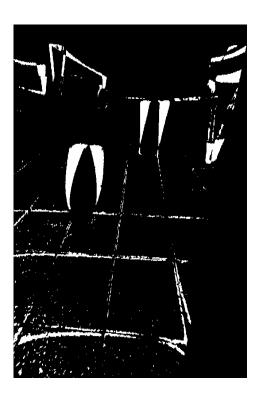

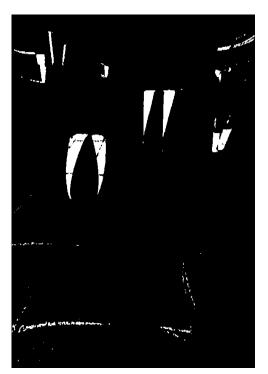

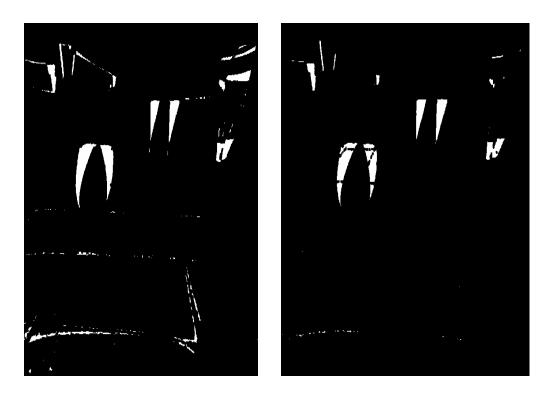

The obstacle detection based on IPM approach is proposed by [Bertozzi 1998b]. This method can be performed either by two cameras (Stereo IPM: SIPM) or one camera (Mono IPM: MIPM). The figure 2.9 shows results of obstacle detection based on IPM in [Bertozzi 1998b] where SIPM is performed. The two acquired images (a), (b) are transformed to remapped views of the scene (c), (d). Subtraction and threshold segmentation are performed between remapped images in (e) and

Figure 2.9: IPM method for obstacle detection in [Bertozzi 1998b]. The two acquired images (a), (b) are transformed to remapped views of the scene (c), (d). Subtraction and threshold segmentation are performed between remapped images in (e) and detected obstacle are shown in (f) (taken from [Bertozzi 1998b]).

detected obstacle are shown in (f).

#### 2.4.5 Methods based on active vision sensors

Systems based on 3D active sensors have been adopted to solve traditional problems in vision systems such as tracking, recognition and feature extraction. An RGB-D sensor like Kinect produces synchronized color images and depth images [Totilo 2010]. Kinect makes use of an infrared (IR) projector which emits a textured light pattern. The disparities measured between expected and observed patterns acquired by a monochrome IR camera permit the estimation of the depth value for each pixel.

Another way of obtaining the depth image is to use Time-of-Flight (TOF) sensors [Castaneda 2011]. Their principle is to measure directly the distance from the camera to the scene for each pixel through the duration of the light round trip travel, the light being emitted by a source located on the camera.

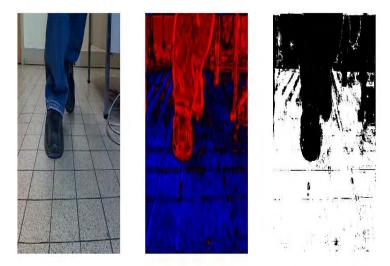

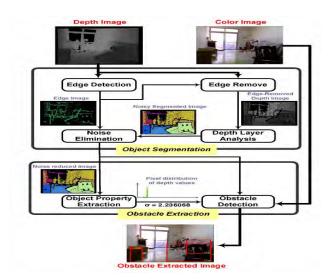

In [Lee 2012], an obstacle detection system based on 3D-sensor includes two stages pictured in figure 2.10:

- Edge detection is firstly performed in the depth image in order to distinguish different objects. This process allows to segment objects in the scene as similar values of intensities in depth image may belong to the same object.

- The detection of the obstacles is performed by using the properties of the

Figure 2.10: Obstacle detection system based on active vision sensor in [Lee 2012]. The system is composed of two stages. The first stage is object segmentation (Edge detection and depth layers analyzation). The next stage is obstacle extraction (taken from [Lee 2012]).

detected objects. The mean and standard deviation of depth values is computed for each object. As the distribution of pixels corresponding to floor in the depth map is scattered, its standard deviation is larger than those of the other objects, hence the floor object can be removed from the other detected objects.

#### 2.5 Conclusion

In this chapter, different methods for obstacle detection were presented. A robot that uses optical flow based methods can find features (corners and edges) of obstacles. However, the algorithms that use optical flow encounter difficulties in large non-textured areas and for edges that suffer from the aperture problem. Obstacle detection based on stereo vision methods is widely used in robotics. However, stereo vision methods suffer from the long computation time required to compute stereo correspondences. In addition, the 3D reconstruction is also computationally prohibitive. Classification methods become increasingly popular. However, these methods need a prior knowledge about the environment. In addition, obstacle detection based on classification methods require a great computational load. Vision approaches based on IPM allow the detection of obstacles under the hypothesis of flat ground, this method is based on the perspective effect perceived from a scene when observed from two different points of view. This method is simpler in terms of computation load when it is compared to other methods. IPM method does not

2.5. Conclusion 19

require textured areas when it is compared to optical flow. IPM method doesn't need the computation correspondences between two sequential images for detecting obstacles. In addition, it doesn't require a prior knowledge about the environment when it is compared to classification methods. However, IPM method requires an accurate camera calibration. Additionally, the method could encounter problems with shiny surfaces and objects shadows.

# Theoretical Background

| Contents | 8                         |                          |  |  |

|----------|---------------------------|--------------------------|--|--|

| 3.1      | 3.1 Introduction          |                          |  |  |

| 3.2      | 2 Pinhole camera model    |                          |  |  |

|          | 3.2.1                     | Intrinsic parameters     |  |  |

|          | 3.2.2                     | Extrinsic parameters     |  |  |

|          | 3.2.3                     | Radial Distortion        |  |  |

| 3.3      | Inve                      | erse Perspective Mapping |  |  |

| 3.4      | Obs                       | tacle segmentation       |  |  |

|          | 3.4.1                     | Gaussian filter          |  |  |

|          | 3.4.2                     | Otsu's binarization      |  |  |

|          | 3.4.3                     | Morphological operators  |  |  |

| 3.5      | Bird's eye transformation |                          |  |  |

| 3.6      | Obstacle localization     |                          |  |  |

| 3.7      | Free space detection      |                          |  |  |

| 3.8      | Obstacle distance         |                          |  |  |

| 3.9      | Con                       | clusion                  |  |  |

#### 3.1 Introduction

In this chapter, the concepts and operators to define a vision-based obstacle detection method are introduced.

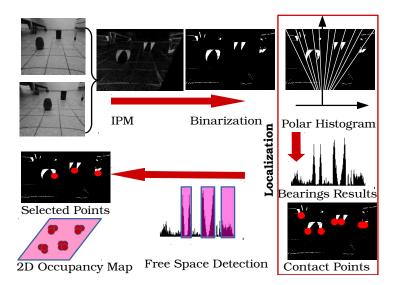

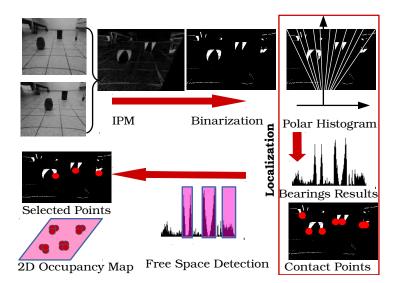

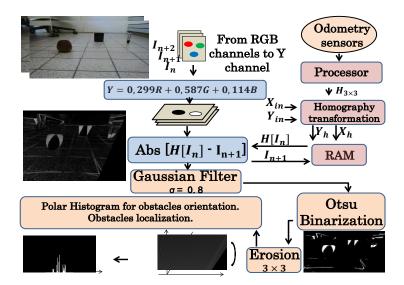

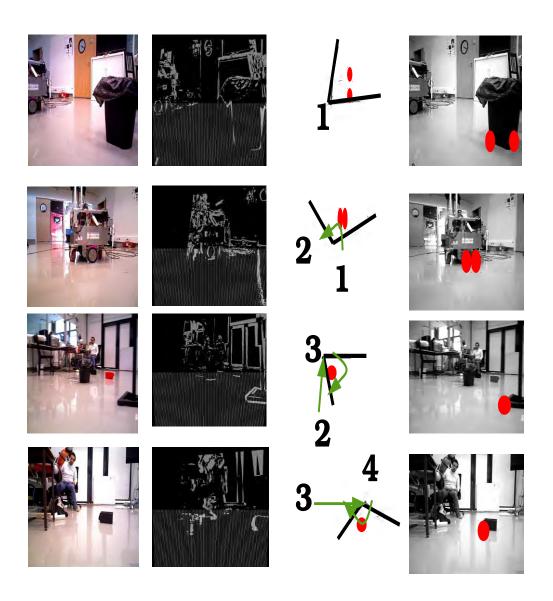

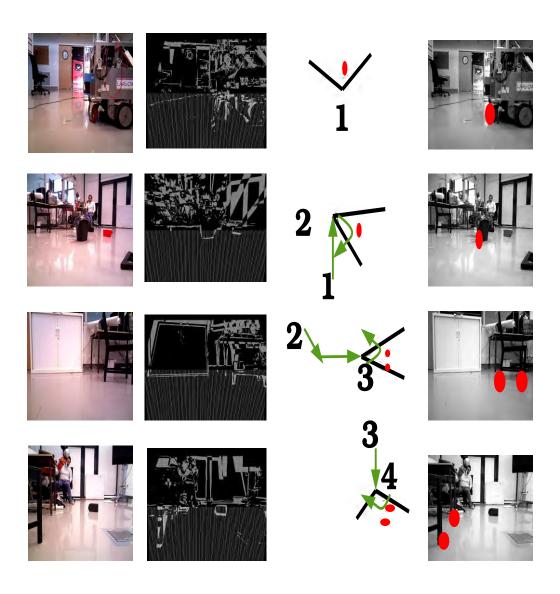

The proposed system is based on inverse perspective mapping for obstacle detection proposed in [Bertozzi 1998b] (see Figure 3.1). Since this method is based on a geometric transformation for the ground plane, the pinhole camera model is firstly introduced. Then a brief overview of the theory behind IPM is given. IPM only allows to compute a pixel-level classification of the image, hence a method for obstacle segmentation and post-processing operators are then presented. An obstacle localization method proposed by the authors of IPM method [Bertozzi 1998b] is finally described in this chapter.

Figure 3.1: General overview of the proposed approach.

## 3.2 Pinhole camera model

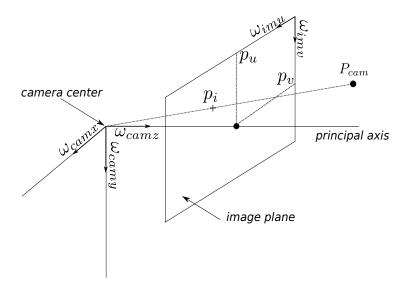

A camera projects a 3-D environment to a 2-D image. The pinhole camera model achieves a central projection to a 2-D plane through an optical center (pinhole aperture). This model is widely used in computer vision due to its simplicity as discussed below. Some definitions of the different coordinate frames follows:

Let  $\omega_{im}$  be a 2D Euclidean coordinate frame attached to the image plane of the camera with the culumn and line axes respectively denoted  $\omega_{imu}$  and  $\omega_{imv}$ .

Let  $\omega_{cam}$  be a 3D Euclidean coordinate frame whose origin is the center of projection of the pinhole camera. Let  $\omega_{camx}$  and  $\omega_{camy}$  be the first 2 axes of this coordinate frame respectively parallel to the  $\omega_{imu}$  and  $\omega_{imv}$  axes of the image plane. The  $\omega_{camz}$  axis is thus orthogonal to the image plane.

Let  $\tilde{p_i} = \begin{bmatrix} p_u & p_v & p_w \end{bmatrix}^T$  be a projective point in projective space  $P^2$ . In that projective space, points can either represent positions or directions in the euclidian space  $R^2$  using the coordinate frame  $\omega_{im}$ , depending on the value of its last component  $p_w$ . If  $p_w$  is equal to 0,  $\tilde{p_i}$  represents a direction  $\begin{bmatrix} p_x & p_y \end{bmatrix}$ . Oppositely, if  $p_w$  is not equal to 0,  $\tilde{p_i}$  represents a position  $\begin{bmatrix} p_u/p_w & p_v/p_w \end{bmatrix}$ . Considering that  $\tilde{p_i}$  defines a position  $\begin{bmatrix} u & v \end{bmatrix}$ , it is possible to express it up to a scale factor as:

$$\tilde{p_i} = \begin{bmatrix} s.u \\ s.v \\ s \end{bmatrix} \tag{3.1}$$

Let  $P_{cam} = \begin{bmatrix} P_{camx} & P_{camy} & P_{camz} & 1 \end{bmatrix}^T$  be a point in projective space  $P^3$  corresponding to the position  $\begin{bmatrix} P_{camx} & P_{camy} & P_{camz} \end{bmatrix}$  in euclidian space  $R^3$  using the coordinate frame  $\omega_{cam}$ .

#### 3.2.1 Intrinsic parameters

As pictured in figure 3.2, the center of projection is known as the camera or optical center. The line from the camera center perpendicular to the image plane is known as the principal axis or principal ray of the camera. The point where the principal axis meets the image plane is known as the principal point. Let K be the camera calibration matrix as defined in equation 3.2. This matrix contains the different intrinsic parameters:  $f_u$  and  $f_v$  are the focals in pixel unit and  $p_u$  and  $p_v$  are the principal point coordinates in the image plane in pixel unit.

$$K = \begin{bmatrix} f_u & 0 & p_u \\ 0 & f_v & p_v \\ 0 & 0 & 1 \end{bmatrix}$$

(3.2)

The focal parameters in pixel unit are obtained from the focal f (in metric unit) and the dimensions of the pixel in u and v directions  $e_u$  and  $e_v$  (in metric unit per pixel), thus  $f_u$  and  $f_v$  differ if the pixels are not square:

$$f_u = f.e_u^{-1}$$

$f_v = f.e_v^{-1}$  (3.3)

The projection of a 3D point  $P_{cam}^{\tilde{}}$  to the image plane of the camera is obtained by the equation 3.4. The  $3\times 4$  matrix [I|0] is used to ensure size consistency between K and  $P_{cam}^{\tilde{}}$  and its effect is to omit the last component of  $P_{cam}^{\tilde{}}$ . This omission renders the fact that all the 3D points along a line passing through the optical center (even at infinity) are projected to the same location in the image plane. Thanks to the homogeneous parametrization of the points, the central projection is expressed as a linear mapping between the homogeneous coordinates. This simplicity is the main cause of the wide use of the pinhole camera model.

$$\tilde{p_i} = K.[I|0].\tilde{P_{cam}} \tag{3.4}$$

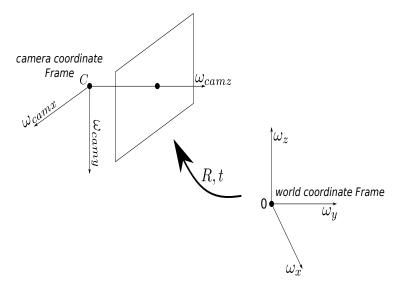

#### 3.2.2 Extrinsic parameters

In practice, the 3D points in space are often expressed in a different Euclidian coordinate frame known as the world coordinate frame  $\omega_{\omega}$ . These two coordinate frames are related via a rigid transform composed of a rotation and a translation as pictured in figure 3.3.

Let  $P_{\omega}$  be the coordinates of a 3D point in the world coordinate frame, and  $P_{cam}$  denotes the same point in the camera coordinate frame. C being the coordinates of the camera center in the world coordinate frame, and R being a 3 × 3 rotation

Figure 3.2: Pinhole camera model.

matrix which denotes the orientation of the camera coordinate frame. The equation 3.5 relates  $P_{\omega}$  and  $P_{cam}$ :

$$P_{cam} = R.(P_{\omega} - C) \tag{3.5}$$

Considering homogeneous coordinates, the equation 3.5 can be rewritten as:

$$\tilde{P_{cam}} = \begin{bmatrix} R & -R.C \\ 0 & 1 \end{bmatrix} .\tilde{P_{\omega}} \tag{3.6}$$

The Eq. 3.4 and Eq. 3.6 can be combined to obtain directly the projection of a 3D point expressed in the world coordinate frame:

$$\tilde{p_i} = K.R.[I|-C].\tilde{P_\omega} \tag{3.7}$$

The projection matrix  $\tilde{P}$  is used to express the projection of  $\tilde{P}_{\omega}$  to  $\tilde{p}_{i}$ :

$$\tilde{p}_i = \tilde{P}.\tilde{P}_{\omega} \tag{3.8}$$

If one writes t = -R.C, the projection matrix expression is:

$$\tilde{P} = K.[I|0]. \begin{bmatrix} R & t \\ 0 & 1 \end{bmatrix} = K.[R|t]$$

(3.9)

#### 3.2.3 Radial Distortion

The pinhole camera model assumes that a world point, its image and the optical center are collinear. Also, the world lines are mapped to lines in the images [Hartley 2004]. For real cameras made of lenses, this linear model may not hold.

Figure 3.3: Extrinsic transformation.

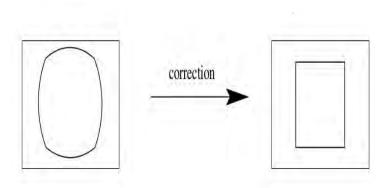

The most important deviation is induced by radial distortions. They can induce "barrel" or "pincushion" distortion as pictured in figure 3.4. The modeling of the distortions aims at being able to correct the images in order to obtain images that would have been acquired without distortions, ie. where straight lines of the scene are imaged to straight lines.

Different models exist to model the distortions. A sixth order model is used in the next equations. This model is the one used in camera calibration with OpenCV [OpenCV 2014].

This model applies in the normalized image plane, which is a plane located at  $\omega_{camz} = 1$  using metric unit for its axes  $\omega_{nx}$  and  $\omega_{ny}$ .

A point location  $\begin{bmatrix} x_{distorted} & y_{distorted} \end{bmatrix}$  is mapped to  $\begin{bmatrix} x_{corrected} & y_{corrected} \end{bmatrix}$  using the following equations:

$$x_{distorted} = x_{corrected}(1 + k_1r^2 + k_2r^4 + k_3r^6)$$

(3.10)

$$y_{distorted} = y_{corrected}(1 + k_1r^2 + k_2r^4 + k_3r^6)$$

(3.11)

$$r^2 = x_{corrected}^2 + y_{corrected}^2 (3.12)$$

$k_1$ ,  $k_2$ ,  $k_3$  are the radial distortion coefficients. Higher-order coefficients are not considered in the implementation of the proposed hardware architectures because the added computational complexity is not justified.

In order to apply the radial distortion correction to the image, it is necessary to:

• Sample each pixel location of the corrected image to generate  $\begin{bmatrix} u_{corrected} & v_{corrected} & 1 \end{bmatrix}^T$ .

Figure 3.4: Example of the "barrel" distortion correction.

• Get the corresponding location in the normalized image plane by multiplying by the inverse of the K matrix (see Eq. 3.13).

$$\begin{bmatrix} x_{corrected} \\ y_{corrected} \\ 1 \end{bmatrix} = K^{-1}. \begin{bmatrix} u_{corrected} \\ v_{corrected} \\ 1 \end{bmatrix}$$

(3.13)

- Apply Eq. 3.10 and 3.11 to obtain the location of the corresponding point with distortion.

- Get the corresponding location in the image plane by multiplying by the K matrix (see Eq. 3.14).

$$\begin{bmatrix} u_{distorted} \\ v_{distorted} \\ 1 \end{bmatrix} = K. \begin{bmatrix} x_{distorted} \\ y_{distorted} \\ 1 \end{bmatrix}$$

(3.14)

• To determine the pixel value associated to the non integer position  $\begin{bmatrix} u_{distorted} & v_{distorted} \end{bmatrix}^T$ , one can achieve different kind of interpolation (nearest neighbor, bilinear...).

# 3.3 Inverse Perspective Mapping

The Inverse Perspective Mapping is a technique based on a geometric transformation applied on frames acquired with different point of view (either using multiple camera, or frames acquired at different time). This method belongs to the resampling effect family; an initial image is transformed to generate a view from a

Figure 3.5: IPM method applied to robot.

different position.

Taking advantage of the perspective effect, this generated image is compared to a real image acquired from the new position, this comparison generates high differences for object sticking out of the ground plane. Detecting and localizing these differences in the ground plane allows to compute the object position relative to the camera.

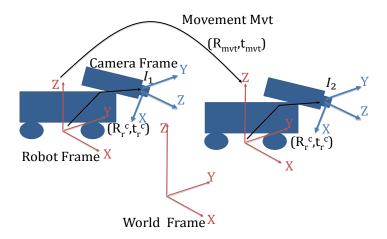

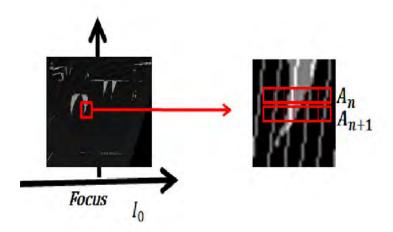

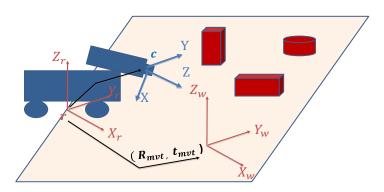

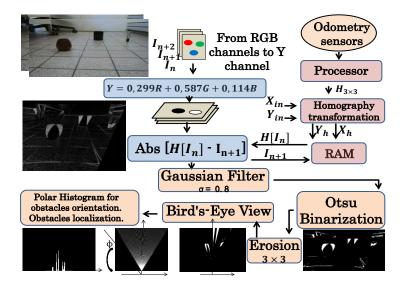

In Mono Inverse perspective mapping [Botero 2012], a single camera is used, two frames are acquired at distinct instants  $t_n$  and  $t_{n+1}$ , as the robot moves. Odometry sensors are used as input to compute the homography matrix.

Homography matrix encodes the effect on the images of the relative motion of the robot between the two positions for a given plane in the scene which is the ground plane in our case. The camera is considered already calibrated; i.e., it's intrinsic parameters (focal, principal point and distortion coefficients) have been determined off line. Thanks to this knowledge, optical distortions can be removed and it is possible to consider the simple Pinhole camera model to perform IPM. A 3D point of the scene ( $P_{camx}$ ,  $P_{camy}$ ,  $P_{camz}$ ) in the world frame is projected to pixel coordinates (u ,v) in the pinhole image as already shown in the equation 3.9. It can be rearranged as follow:

$$\begin{bmatrix} su \\ sv \\ s \end{bmatrix} = KR \begin{bmatrix} P_{camx} \\ P_{camy} \\ P_{camz} \end{bmatrix} + Kt$$

(3.15)

K is camera intrinsic matrix and (R,t) encodes the rotation and translation from the world frame to the camera frame. These former are named the camera extrinsic parameters. As IPM is intended to detect the ground pixels, the world frame which is the robot frame (see figure 3.5) is chosen such as the  $P_{camx}P_{camy}$  plane is the ground plane. Therefore, for 3D points in the world frame laying in the ground plane,  $P_{camz} = 0$  is applied to Eq. 3.15:

$$\begin{bmatrix} su \\ sv \\ s \end{bmatrix} = K(R \begin{bmatrix} P_{camx} \\ P_{camy} \\ 0 \end{bmatrix} + t)$$

(3.16)

Applying Algebraic properties to Eq. 3.16:

$$\begin{bmatrix} su \\ sv \\ s \end{bmatrix} = K \begin{bmatrix} r_1 & r_2 & t \end{bmatrix} \begin{bmatrix} P_{camx} \\ P_{camy} \\ 1 \end{bmatrix}$$

(3.17)

In the first acquisition, the robot frame is considered as the world frame. Therefore, each pixel coordinates are represented Eq. 3.18:

$$\begin{bmatrix} s_1 u_1 \\ s_1 v_1 \\ s_1 \end{bmatrix} = K \begin{bmatrix} r_{r1}^c & r_{r2}^c & t_r^c \end{bmatrix} \begin{bmatrix} P_{camx} \\ P_{camy} \\ 1 \end{bmatrix} = H_1 \begin{bmatrix} P_{camx} \\ P_{camy} \\ 1 \end{bmatrix}$$

(3.18)

In the second acquisition, the position of the robot frame origin in the second acquisition is represented in the robot frame of the first acquisition Eq 3.19:

$$\begin{bmatrix} s_2 u_2 \\ s_2 v_2 \\ s_2 \end{bmatrix} = K \begin{bmatrix} r_{w1}^c & r_{w2}^c & t_w^c \end{bmatrix} \begin{bmatrix} P_{camx} \\ P_{camy} \\ 1 \end{bmatrix} = H_2 \begin{bmatrix} P_{camx} \\ P_{camy} \\ 1 \end{bmatrix}$$

(3.19)

The transformation  $(R_w^c, t_w^c)$  is computed from Eq. 3.20 as shown in the figure 3.5:

$$\begin{bmatrix} R_w^c & t_w^c \\ 0 & 1 \end{bmatrix} = \begin{bmatrix} R_r^c & t_r^c \\ 0 & 1 \end{bmatrix} \begin{bmatrix} R_{mvt} & t_{mvt} \\ 0 & 1 \end{bmatrix}$$

(3.20)

From Eq. 3.18 and Eq. 3.19:

$$\begin{bmatrix} s_2 u_2 \\ s_2 v_2 \\ s_2 \end{bmatrix} = H_2 H_1^{-1} \begin{bmatrix} s_1 u_1 \\ s_1 v_1 \\ s_1 \end{bmatrix} = T_{ipm} \begin{bmatrix} s_1 u_1 \\ s_1 v_1 \\ s_1 \end{bmatrix}$$

(3.21)

$$\begin{bmatrix} s_2 u_2 \\ s_2 v_2 \\ s_2 \end{bmatrix} = K \begin{bmatrix} r_{w1}^c & r_{w2}^c & t_w^c \end{bmatrix} \begin{bmatrix} r_{r1}^c & r_{r2}^c & t_r^c \end{bmatrix}^{-1} K^{-1} \begin{bmatrix} s_1 u_1 \\ s_1 v_1 \\ s_1 \end{bmatrix}$$

(3.22)

Therefore, each ground point represented in the camera frame  $I_1$  and represented with the coordinates  $(u_1, v_1)$  in the image frame will be presented in the camera frame  $I_2$  with the coordinates  $(u_2, v_2)$  in the image frame. From Eq. 3.22:

$$H = T_{ipm} = K \begin{bmatrix} r_{w1}^c & r_{w2}^c & t_w^c \end{bmatrix} \begin{bmatrix} r_{r1}^c & r_{r2}^c & t_r^c \end{bmatrix}^{-1} K^{-1}$$

(3.23)

The transformation Eq. 3.23 is only correct for ground points. Therefore, the subtraction between  $T_{ipm}[I_1]$  and  $I_2$  will remove the ground points.

# 3.4 Obstacle segmentation

### 3.4.1 Gaussian filter

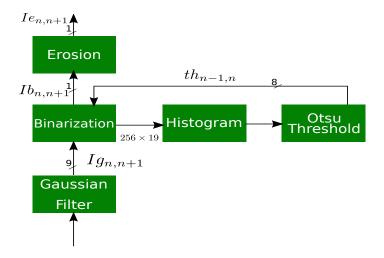

In the resulting image after IPM transformation, pixels of the ground plane have low absolute intensity values while pixels of objects sticking out of the ground plane have high intensity absolute values. Such image has a bimodal histogram; pixels intensities will be clustered around two well-separated values(peaks). Hence, a good threshold for separating these two groups can be found somewhere in between the two peaks in the histogram. Thanks to Otsu's algorithm which computes threshold value from a histogram of bimodal image.

Before Otsu's binarization is performed, Gaussian filter is applied to the resulting image after IPM transformation in order to remove noise. As segmentation methods are sensitive to noise, applying Gaussian Blur filter before Otsu's binarization aims to reduce noise and improve the results of Otsu's algorithm.

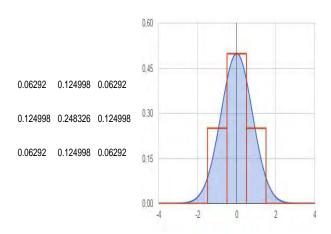

Gaussian Blur is a type of image-blurring filter that uses a Gaussian function. The equation of a Gaussian function in two dimensions is:

$$G(x,y) = \frac{1}{2\pi\sigma^2} e^{-\frac{x^2+y^2}{2\sigma^2}}$$

(3.24)

Figure 3.6: Gaussian kernel coefficients. Reprinted from Gaussian kernel calculator. Retrieved November 2015, from http://dev.theomader.com/gaussian-kernel-calculator/.

x denotes the distance from the origin in the horizontal axis, y denotes the distance from the origin in the vertical axis.  $\sigma$  being the standard deviation of the Gaussian distribution. This equation produces a surface whose contours are co-centric circles representing the Gaussian distribution from the center point.

Gaussian smoothing is done by convolution. Since the image is stored as a collection of discrete pixels, a discrete approximation kernel to the Gaussian function is produced before executing the convolution. The kernel weights are renormalized. Thus, the sum of all weights is one. The heaviest weight having the highest Gaussian value is given to the original pixel while smaller weights are given to neighbouring pixels.

The kernel used in the proposed system is a  $3 \times 3$  kernel whose standard deviation is  $\sigma = 0.8$ . Figure 3.6 shows the weights of such kernel.

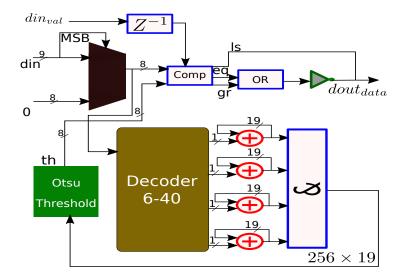

#### 3.4.2 Otsu's binarization

In obstacle detection system, one of the important steps to extract obstacle pixels is the segmentation of binary image and thresholding is a fundamental tool for segmentation. Otsu's thresholding [Otsu 1979] is known as a good method, this method finds the optimal threshold by minimizing the mean square errors between original image and the resultant binary image. In order to segment obstacle points,

the image resultant from the Gaussian smoothing is segmented into two regions: obstacle objects and background region. In general, the gray-level histogram is normalized and regarded as probability distribution Eq. 3.25:

$$p_i = \frac{n_i}{N} \tag{3.25}$$

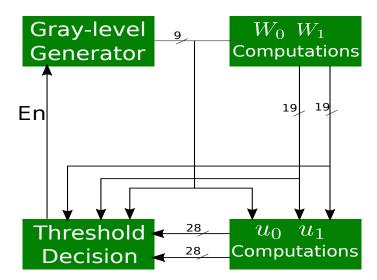

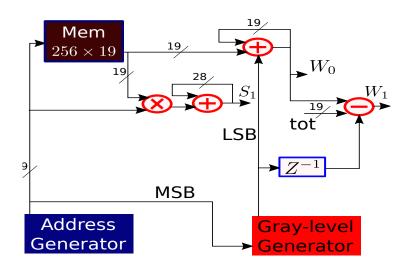

where N is the total number of pixels and  $n_i$  is the number of pixels at level i, the total number of gray levels is L. Pixels are classified into two classes background and obstacle objects by a threshold at level k. The class probability  $\omega_{0,1}$  is computed as follows:

$$\omega_0 = \sum_{i=1}^k p_i, \qquad \omega_1 = \sum_{i=k+1}^L p_i$$

(3.26)

The class mean  $\mu_{0,1}$  is then expressed as follows:

$$\mu_0 = \sum_{i=1}^k \frac{ip_i}{\omega_0}, \qquad \mu_1 = \sum_{i=k+1}^L \frac{ip_i}{\omega_1}$$

(3.27)

A threshold based on Otsu's algorithm is computed from Eq. 3.26 and Eq. 3.27:

$$\sigma_0^2(t) = \sum_{i=1}^k [i - \mu_0(t)]^2 \frac{p_i}{\omega_0}$$

(3.28)

$$\sigma_1^2(t) = \sum_{i=k+1}^{L} [i - \mu_1(t)]^2 \frac{p_i}{\omega_1}$$

(3.29)

The desired threshold corresponds to the minimum value of the weighted within class variance produced by Eq. 3.28, and Eq. 3.29. In practice, this problem of searching the optimal threshold can be reduced to search a threshold that maximizes the between-class variance which is computed as follows:

$$\sigma_B^2 = \omega_0 \omega_1 (\mu_1 - \mu_0)^2 \tag{3.30}$$

For quicker calculation and optimal performance in hardware implementation the equation 3.30 is used to find Otsu's threshold from the histogram extracted from gray-level image.

### 3.4.3 Morphological operators

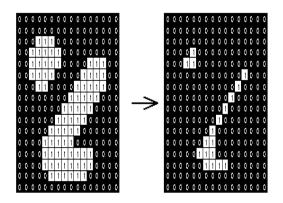

In morphological image processing, erosion is one of two basic operators which are typically applied to binary images. When erosion operator is applied to a binary image, the boundaries of regions of foreground pixels (i.e. white pixels) are eroded away. Hence, areas of foreground pixels shrink in size, and holes within those areas become larger. Erosion operation is mathematically defined as follows [Fisher 2000]:

"Suppose that X is the set of Euclidean coordinates corresponding to the input binary image, and that K is the set of coordinates for the structuring element. Let Kx denote the translation of K so that its origin is at x. Then the erosion of X by K is simply the set of all points x such that Kx is a subset of X".

The erosion operator takes two inputs. The first input is the image which is to be eroded. The second input is a set of coordinate points known as a structuring element. The precise effect of the erosion on the input image is mainly determined by the structuring element.

Let the structuring element to be a  $3 \times 3$  square with the origin at its center. Foreground pixels are represented by 1, and background pixels by 0.

To compute the output image by this structuring element, the structuring element is superimposed on top of the input image for each foreground pixel so that the origin of the structuring element corresponds to the input pixel coordinates. For every pixel in the structuring element, if the corresponding pixel in the image underneath is a foreground pixel, then no change is applied to the input pixel. On the other hand, if any of the corresponding pixels in the image is background, the input pixel is set to background value.

In our system, erosion is applied to the binarized image resulting from Otsu's algorithm. it uses a kernel of  $3 \times 3$ . Figure 3.7 shows the erosion operator impact using the  $3 \times 3$  structure element [Fisher 2000].

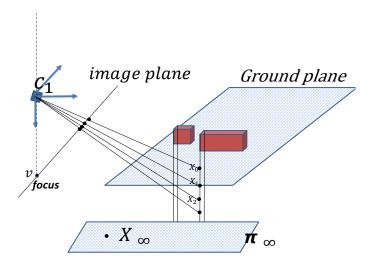

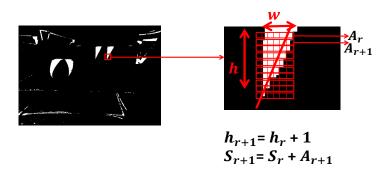

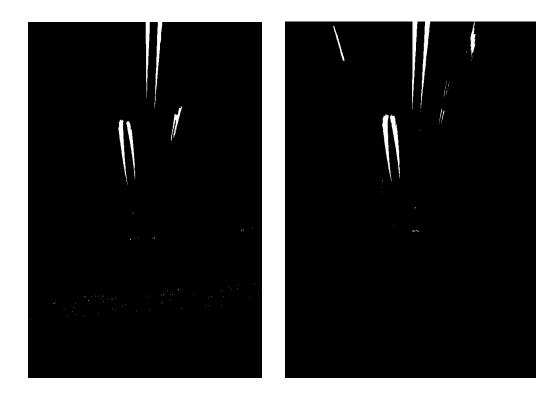

# 3.5 Bird's eye transformation

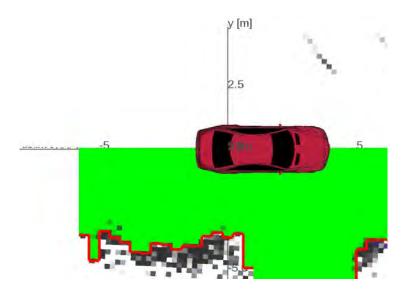

This transformation is used in the state of art of IPM method for obstacle detection [Bertozzi 1998b]. Bird's eye transformation allows the distribution of obstacle information in all pixels and leads to an efficient implementation of polar histogram in order to localize obstacles.

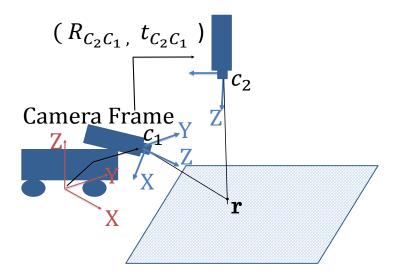

The binarized image is projected on the ground plane in the robot frame as depicted in figure 3.8, up to a rotation around the vertical axis and a translation in XY.  $C_1$  and  $C_2$  represent camera frame as shown in figure 3.8. Any point on the ground plane P has a 3D position represented with respect to the camera  $C_1$  is  $r_{C_1}$  [Hartley 2004] Eq. 3.31:

Figure 3.7: Erosion effect using a kernel of  $3 \times 3$ . Reprinted from [Fisher 2000].

Figure 3.8: Bird's eye view transformation.

(a) Perspective view.

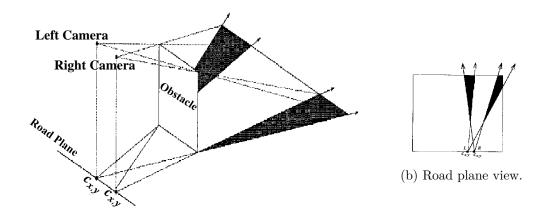

Figure 3.9: Relationships between obstacle and cameras position. Reprinted from "GOLD: Real time Stereo vision system for generic obstacle and lane detection" [Bertozzi 1998a]

$$\frac{n_{C_1}^T \cdot r_{C_1}}{d_{C_1}} = 0 (3.31)$$

$n_{C_1}$  is the ground plane normal represented in camera  $C_1$  coordinates and  $d_{C_1}$  is the distance of the ground plane from the origin of camera  $C_1$ , the position vector  $r_{C_2}$  of the same point represented in camera  $C_2$  Eq. 3.32:

$$r_{C_2} = R_{C_2C_1}(r_{C_1} - t_{C_1}^{C_2C_1}) (3.32)$$

where  $R_{C_2C_1}$  is the rotation matrix from  $C_1$  to  $C_2$  and  $t_{C_1}^{C_2C_1}$  is the translation from  $C_1$  to  $C_2$  presented in  $C_1$  coordinates.

The required transformation from the original Camera  $C_1$  to the virtual camera  $C_2$  presenting bird's-eye view is Eq. 3.33:

$$r_{C_2} = H_{C_2C_1} \ r_{C_1} \tag{3.33}$$

$$H_{C_2C_1} = R_{C_2C_1} - \frac{1}{d_{C_1}} t_{C_2}^{C_2C_1} . n_{C_1}^T$$

(3.34)

By using Eq. 3.34, the homography matrix of bird's-eye view for the cameras is calculated. To use this matrix in image coordinates(pixels), camera intrinsic matrix K is required as shown in the equation (15):

$$H_{bird} = K(R_{C_2C_1} - \frac{1}{d_{C_1}} t_{C_2}^{C_2C_1} . n_{C_1}^T) K^{-1}$$

(3.35)

and the bird's eye image of the ground plane is generated.

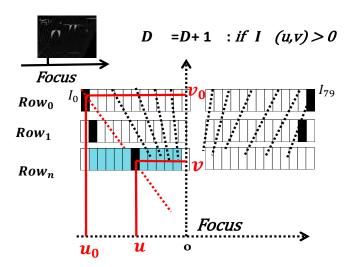

## 3.6 Obstacle localization

Obstacles localization using stereo IPM is introduced in [Bertozzi 1998b]. The goal of this process is to determine the free space around robot without a complete recognition of obstacles. As depicted in figure 3.9, bird's eye operation transforms vertical edges of obstacles to lines passing through the projection  $C_{x,y} = (l, d, 0)$  of the camera center on the road plane z = 0.

As the system used in [Bertozzi 1998b] is based on stereo IPM, two projection centers are obtained in the plane z=0. The resulting image after IPM transformation in [Bertozzi 1998b] produces two triangle shapes of obstacle projected on the ground plane as depicted in figure 3.9. The triangle prolongation edges intersect at the projections  $C_{x,y}^L$ ,  $C_{x,y}^R$ .

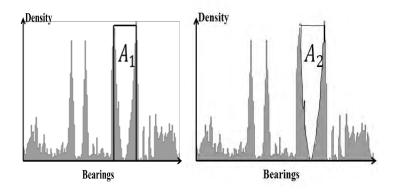

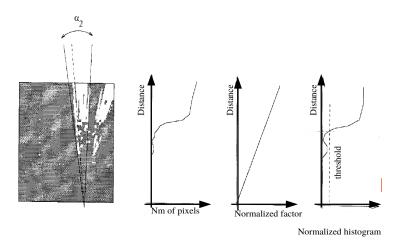

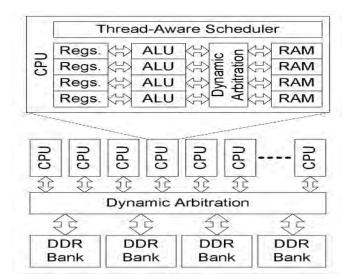

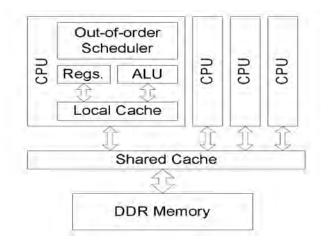

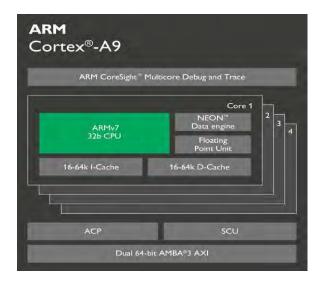

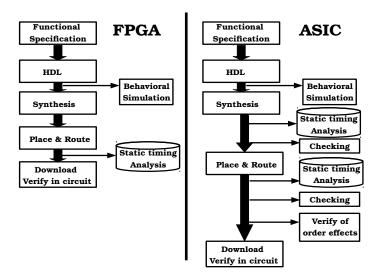

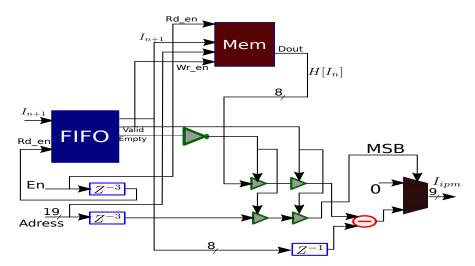

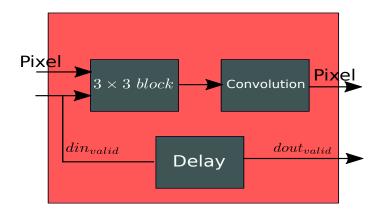

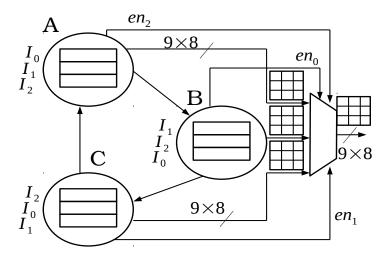

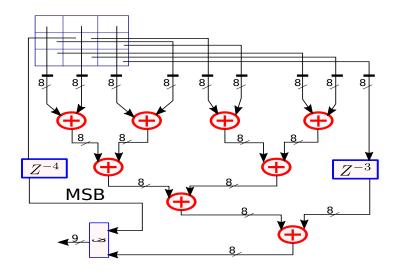

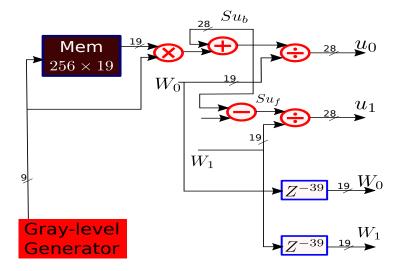

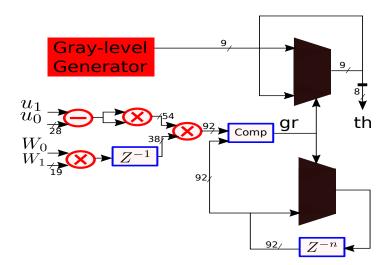

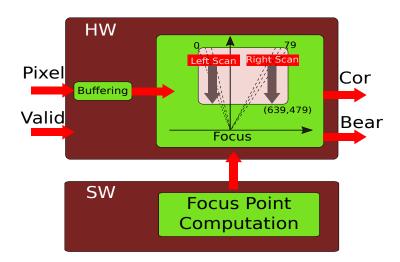

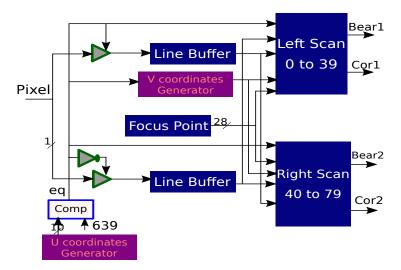

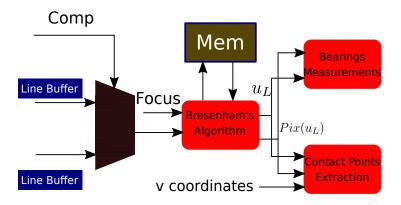

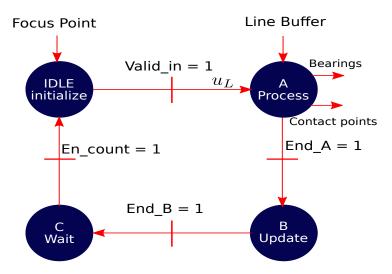

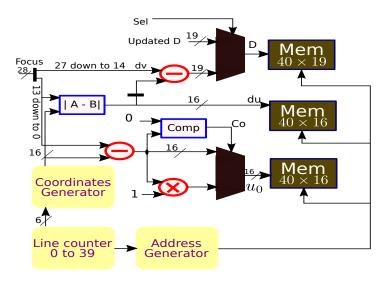

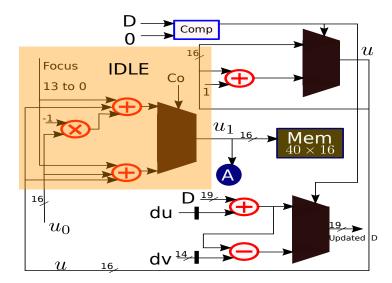

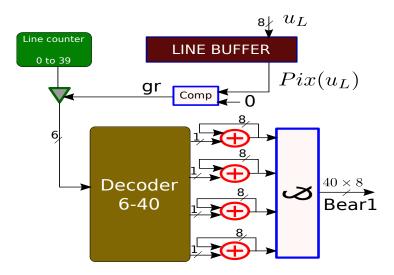

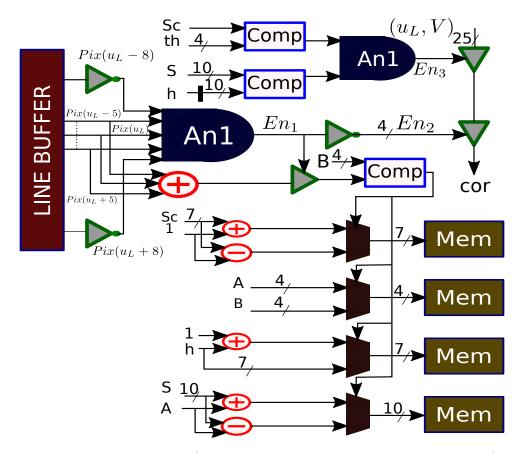

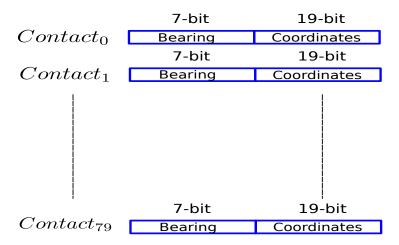

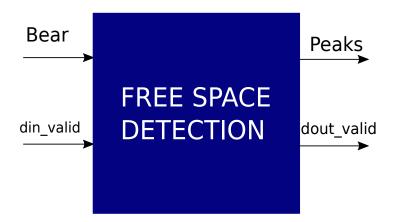

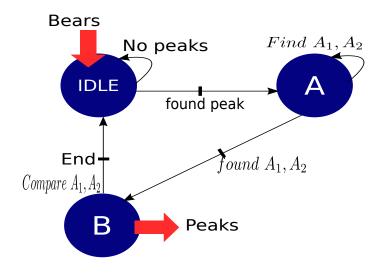

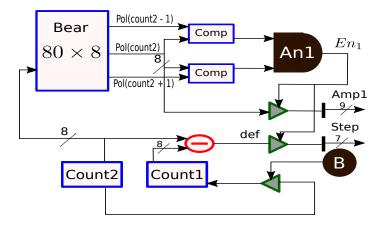

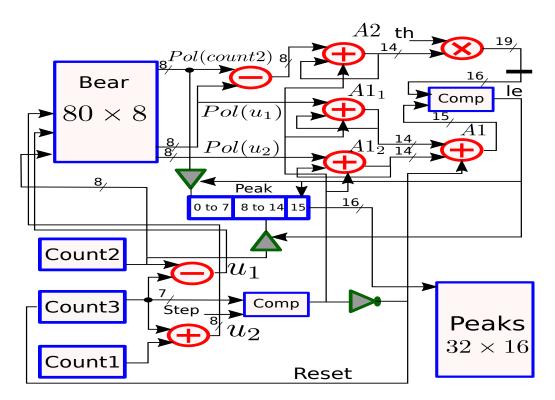

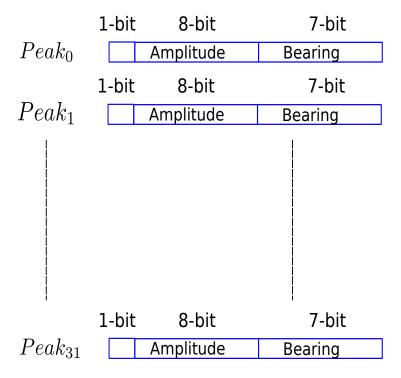

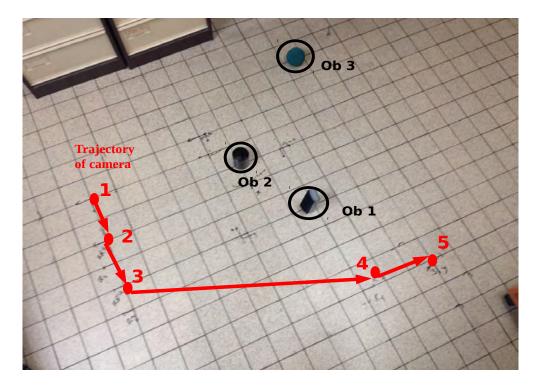

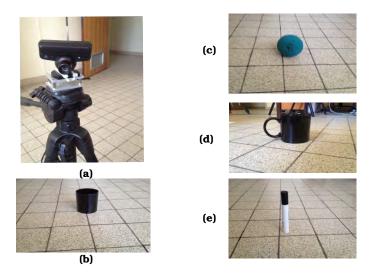

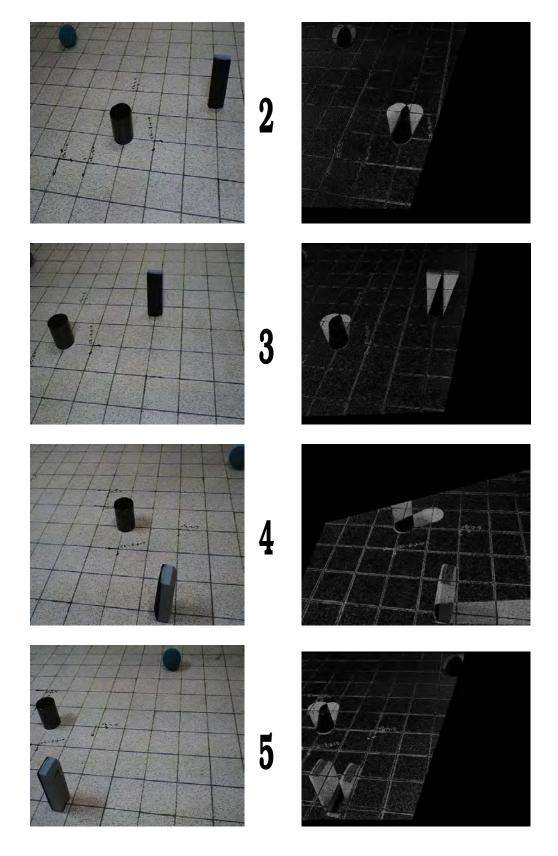

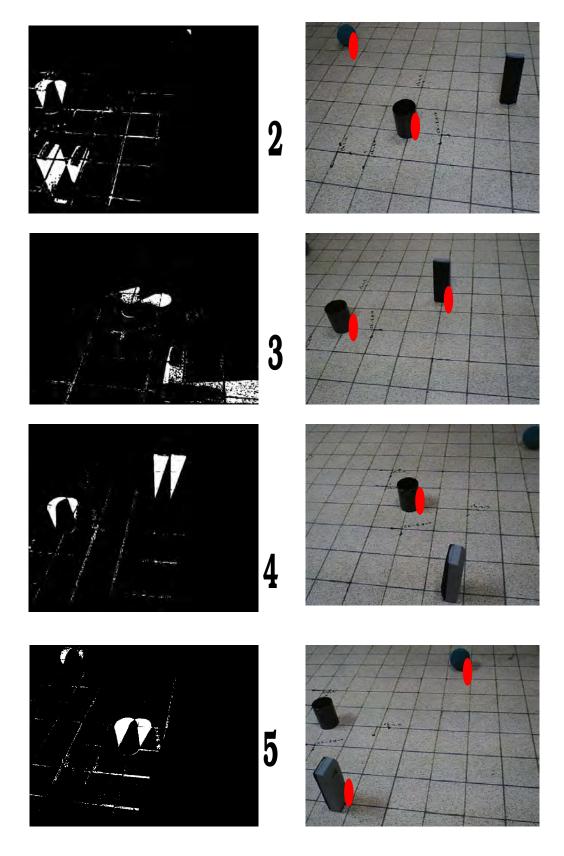

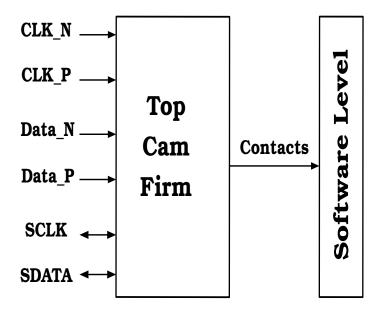

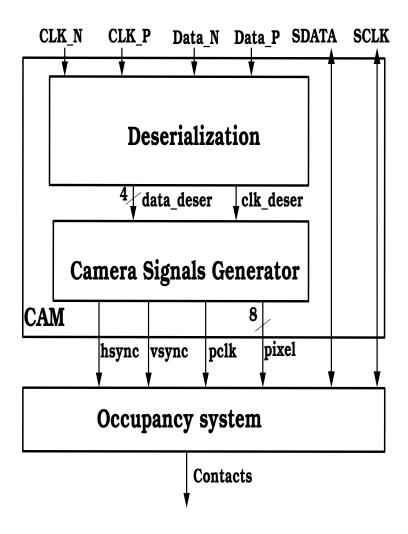

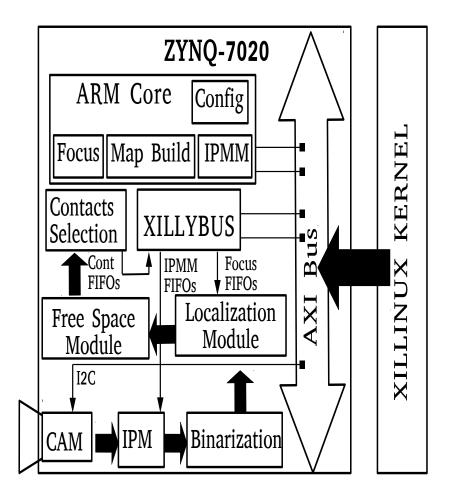

The midpoint point namely focus is halfway between the two projections  $C_{x,y}^L$ ,  $C_{x,y}^R$ . As polar histogram is used to detect the triangles in the produced image after applying IPM method in [Bertozzi 1998b], focus point is used as the origin of polar histogram beam. The polar histogram is performed by a beam of lines originating from focus and counting the number of over-threshold pixels per line.