## GPU PERFORMANCE MODELING AND OPTIMIZATION

#### **ANG LI**

# A THESIS SUBMITTED FOR THE JOINT DEGREE OF DOCTOR OF PHILOSOPHY BETWEEN

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

AND

DEPARTMENT OF ELECTRICAL ENGINEERING EINDHOVEN UNIVERSITY OF TECHNOLOGY

#### Doctorate committee:

prof.dr.ir. B. Smolders Eindhoven University of Technology Eindhoven University of Technology prof.dr. H. Corporaal Technische Universität Dresden prof.dr. A. Kumar Eindhoven University of Technology prof.dr. K. Goossens prof.dr.ir. P.H.N. de With Eindhoven University of Technology prof.dr. Y. Ha National University of Singapore prof.dr. W.F. Wong National University of Singapore prof.dr. V. Bharadwaj National University of Singapore dr.ir. C. Nugteren Blippar Layar

This work is supported by the Research Scholarship from National University of Singapore.

#### © Copyright 2016, Ang Li

All rights reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Cover designed by Yanfei Li.

Printed by CPI-Koninklijke Wöhrmann B.V., The Netherlands.

A catologue record is available from the Eindhoven University of Technology Library.

ISBN: 978-90-386-4155-3

## **GPU Performance Modeling and Optimization**

## **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de

Technische Universiteit Eindhoven, op gezag van de

rector magnificus, prof.dr.ir. F.P.T. Baaijens, voor een

commissie aangewezen door het College voor

Promoties in het openbaar te verdedigen

op dinsdag 18 oktober 2016 om 14.00 uur

door

Ang Li

geboren te Shanxi, China

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

voorzitter: prof.dr.ir. B. Smolders

promotor: prof.dr. H. Corporaal

promoter: prof.dr. A. Kumar (Technische Universität Dresden)

leden: prof.dr. K. Goossens

prof.dr.ir. P.H.N. de With

prof.dr. Y. Ha (National University of Singapore)

prof.dr. W.F. Wong (National University of Singapore)

prof.dr. V. Bharadwaj (National University of Singapore)

dr.ir. C. Nugteren

Het onderzoek dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

## **Declaration**

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

\_\_\_\_

Ang Li Sep 2016

## Acknowledgments

First I would be greatly thankful to my wife, my parents and my brother for their continuous support in my life. I would like to thank my supervisor Prof. Henk Corporaal who offered me the great opportunity to enroll in the joint-PhD program so that I had the chance to join the ES group and Eindhoven University of Technology (TU/e). His insightful comments and sharp questions always motivate me a lot and make me realize that there is always a better approach. I would thank my supervisor Prof. Akash Kumar. Without him, I could not have the chance to pursue the PhD degree in National University of Singapore (NUS). His smartness, patience and the extremely effectiveness in all research, teaching and life always remain the objective for me to follow. He has helped me resolve quite a lot of troubles I feel so frustrated and incapable to deal with. I would also like to thank my co-supervisor Prof. Yajun Ha, for his great support during my stay in NUS and offered me the high-quality journal articles for review.

I would like to thank Prof. Bart Smolders, Prof. Veeravalli Bharadwaj, Prof. Weng-Fai Wong, Prof. Peter de With, Prof. Kees Goossens, Prof. Ana Lucia Varbanescu and and Dr. Cedric Nugteren for serving on my dissertation committee for both sides. Their valuable feedback significantly improved the thesis.

I would like to thank Prof. Y.C. Tay for getting me in the module about performance modeling for compute systems, which was the most excellent class I ever took. The great theory I learnt in the module about closed queuing-network and transit analysis are the most initial sources for me to derive the idea about X-model presented in this thesis. I would like to thank Dr. Leon Shuaiwen Song for guiding and working with me on the latest several papers. Without him, I could not be so efficient in the past year and completed my PhD on time. I would like to thank to Dr. Weifeng Liu for his great help in the experiments of the SC-15 paper and the collaboration in the EuroPar-16 paper.

I would like to thank all the members in the PARsE group: Gert-Jan van den Braak, Maurice Peemen, Mark Wijtvliet, Luc Waeijen, Roel Jordans, Sohan Walimbe for their comments and suggestions on my presentations during the biweekly PARsE meetings. Special thanks to Gert-Jan for his assistance in the ICS-15 paper and SC-15 paper. Special thanks to Mark for his help in designing and setting up the environment to measure the power of the Jetson-TX1 board for the ICS-16 paper.

Sincerely thank to my great friends Li Yonghui, Tang Qi, Chen Xin, Geng Tong, Li Zechuan, Shi Runbin, Jiao Hailong, Wang Wenjin, Chita, Wang Wenfeng, He Yifan, Wang Qing and She Dongrui. Thanks to Yonghui for the great help that I can never count up. Thanks to Tang Qi for sharing the wonderful wine with me, the sharp and interesting conversation about politics, education and life in Austria. Thanks to Chen Xin, Geng Tong and Li Zechuan for shopping together every Saturday morning, which are my most relaxing time for me in a week. Thanks to Runbin for the happy cooking and the comfortable conversation together in my early days in TU/e. Thanks to Hailong for being the host to organize our parties and driving me in the early morning to Schiphol Airport for the conferences in US. Thanks to Wenjin for his Philip member card. Thanks to Chita for being my neighbor and sharing me with the delicious Indian curry and Chinese tofu. Thanks

to Wenfeng for passing me the form for applying to work in Flux during weekends. Thanks to Yifan for leaving me the userful hair-cutting tools. Thanks to Dongrui for transferring his seat/desk in the old Potential building and inviting me to his defense dinner. Thanks to everybody, without you all, my life in TU/e would fade and lost its color.

Thanks to my old friends during my first two years in Singapore: Zhao Wenfeng, Chen Yongzhen, Lin Longyang, Zhao Jian, Zhao Yang, Wang Xi, Wu Qiang, Anup Das, Amit Kumar Singh, Nam Khanh Pham, Mohammad Shihabul Haque, Tuan Nguyen, Hoo Chin Hau, Luo Shaobo, Wang Yi, Jin Jing, Li Weimin, Tang Liang, Wu Tong, Fang Fan, Hu Qikai, Zhong Guanwen, Tan Cheng, Wan Xuejun, Wang Zi, An Jianfeng and others.

Many thanks to everyone in the ES-group, who made working in the Lab a great and enjoyable experience. Special thanks to the head of the group Prof. Twan Basten for letting me attend the conferences to present my papers. Special thanks to our secretary Marja, for all the patience and substantial supporting in the involved paper-work.

Finally, thanks to my coming daughter, although you have not yet come to the world, you already bring me the great courage and the enthusiasm for the future life. Looking forward to see you after the PhD oral defense.

#### **Abstract**

The last decade has witnessed the blooming emergence of generalpurpose Graphic-Processing-Unit computing (GPGPU). With the exponential growth of cores and threads in a modern GPU processor, how to analyze and optimize its performance becomes a grand challenge. In this thesis, as the modeling part, we propose an analytic model for throughput-oriented parallel processors. The model is visualizable, traceable and portable, while providing a good abstraction for both application designers and hardware architects to understand the performance and motivate potential optimization approaches. As the optimization part, we focus on each crucial component of a GPU streaming-multiprocessor, in particular registers-files, compute-units (SPU, DPU, SFU), caches (L1, L2, read-only, texture, constant) and scratchpad memory alternatively, clarify its underlying performance tradeoffs, and propose effective solutions to handle the tradeoffs in the design space. All the proposed optimization approaches are purely software-based. They are adaptive, transparent, traceable and portable, which leads to achievable and immediate performance gains for various existing GPU devices, especially for GPU integrated high-performancecomputers (HPC).

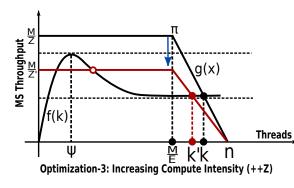

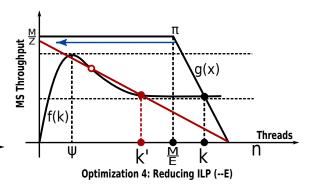

Particularly, the first contribution in Chapter 3 is a novel visualizable analytic model called "X" that is specially for today's highly parallel machines. It comprehensively analyzes the interaction between the four types of parallelism (TLP, ILP, DLP and MLP) and two types of memory effects (local on-chip cache effect and re-

mote off-chip memory effect), in terms of system throughput. The X-model acts as the theoretical basis of this thesis.

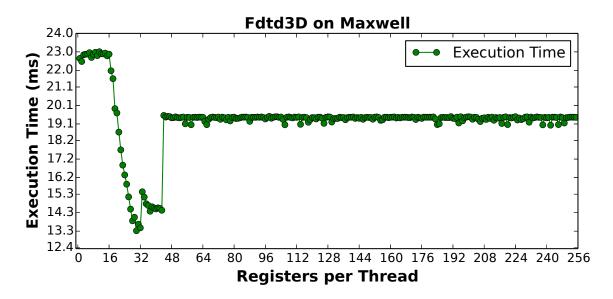

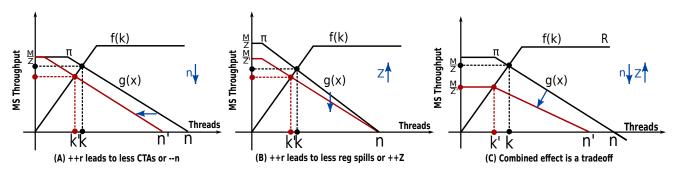

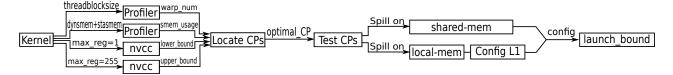

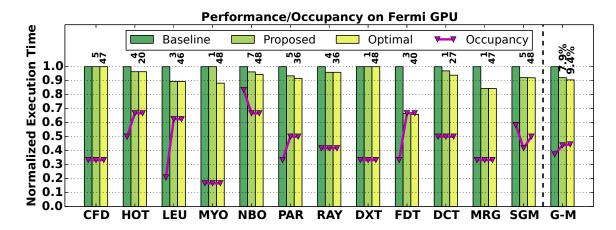

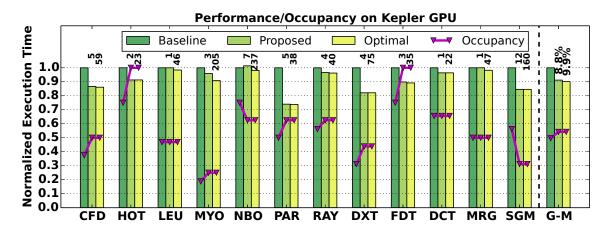

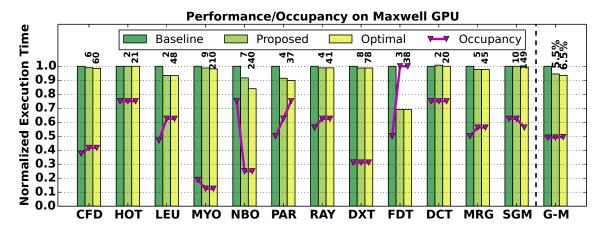

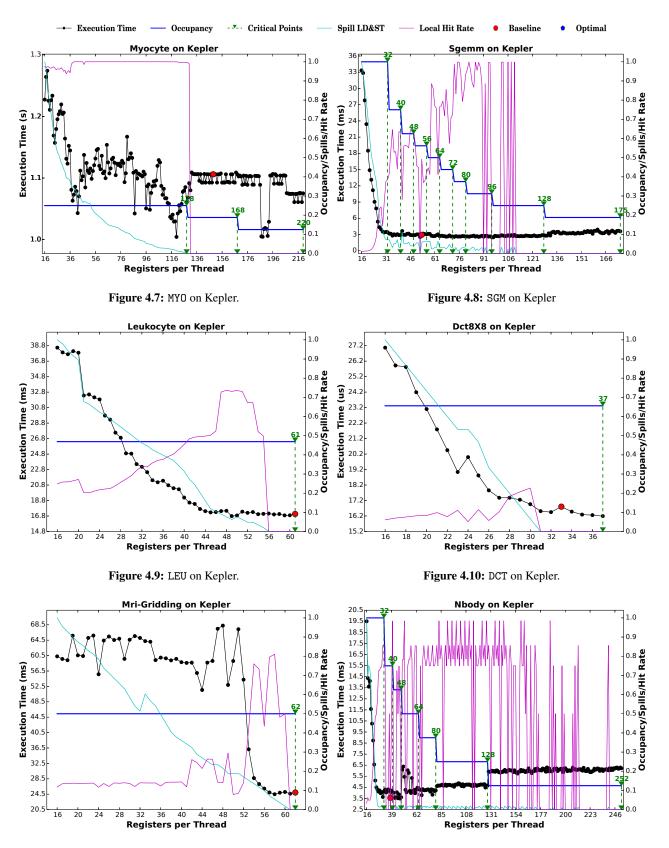

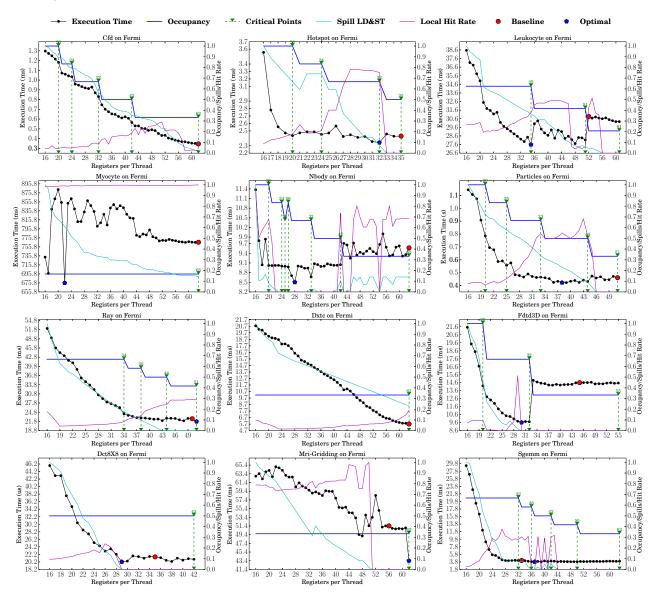

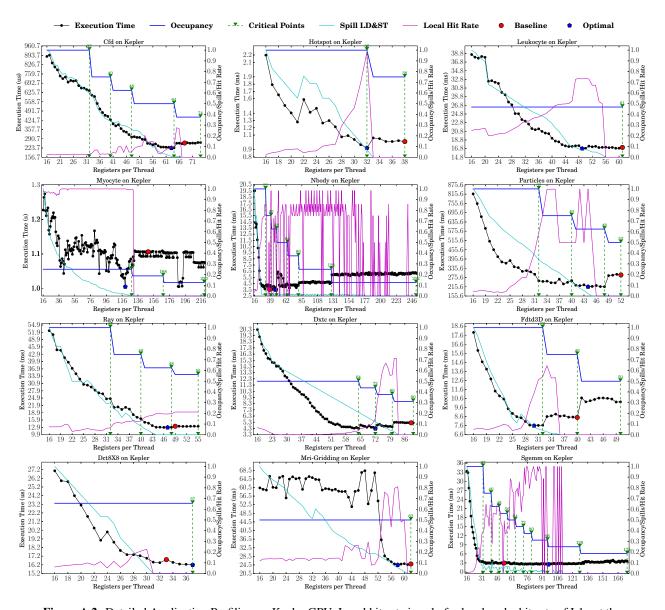

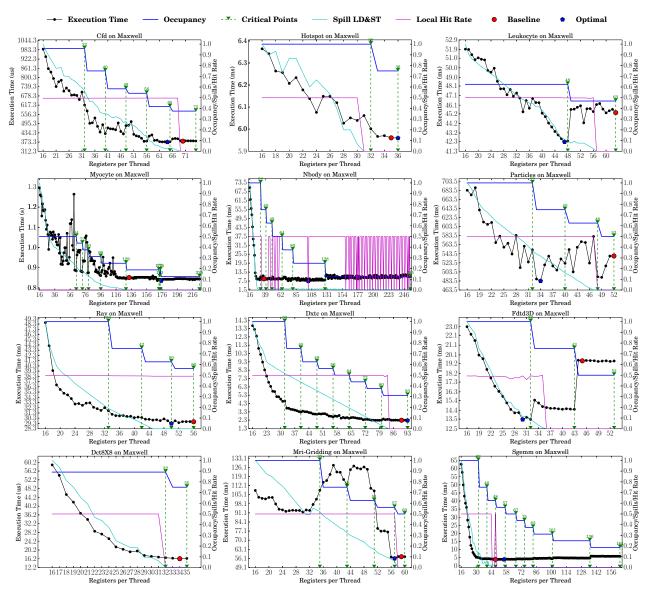

The second contribution in Chapter 4 is an effective auto-tuning framework to resolve the conflict between overall thread concurrency and per-thread register usage for GPUs. We discover that the performance impact from register usage is continuous, but from concurrency is discrete. Their joint-effects form a special relationship such that a series of critical-points can be pre-computed. These critical-points denote the best performance for each concurrency level. Therefore, the global optimum, which refers to the optimal number of registers per-thread, can be quickly and efficiently selected to deliver the best GPU performance.

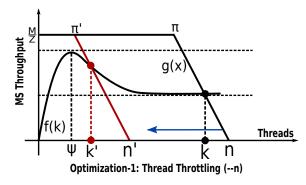

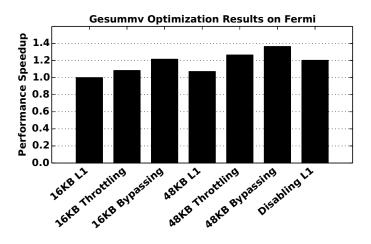

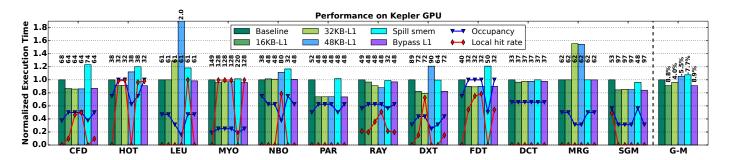

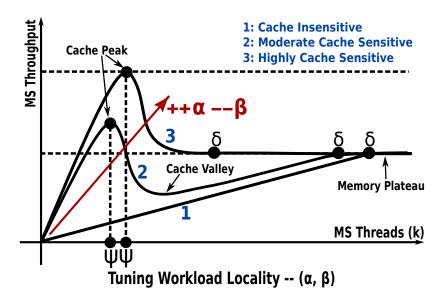

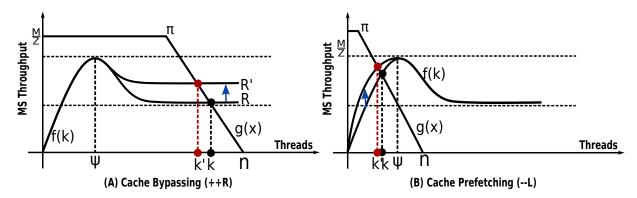

The third contribution in Chapter 5 is an adaptive cache bypassing framework for GPUs. It uses a simple but effective approach to throttle the number of threads that could access the three types of GPU caches –L1, L2 and read-only caches, thereby avoiding the fierce cache thrashing of GPUs, and significantly improving the performance for cache-sensitive applications.

In Chapter 6, we focus on a crucial GPU component that has long been ignored – the Special Function Units (SFUs) and show its outstanding role in performance acceleration and approximate computing for GPU applications. We exhaustively evaluate the numeric transcendental functions that are accelerated by SFUs and propose a transparent, tractable and portable design framework for SFU-driven approximate acceleration on GPUs. It partitions the active threads into a PE-based slower but accurate path, and a SFU-based faster but approximated path, and tunes the relative partition ratio among two paths to control the tradeoffs between the performance and accuracy of the GPU kernels. In this way, a fine-

grained and almost linear tuning space for the tradeoff between performance and accuracy can be created.

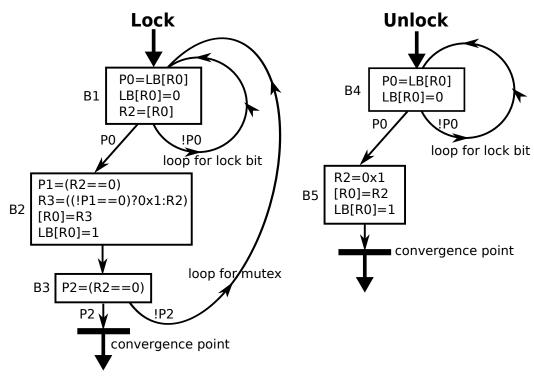

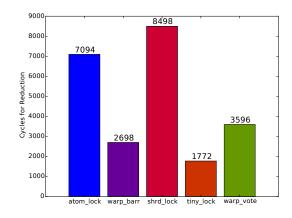

Finally, the last contribution in Chapter 7 is a novel approach for fine-grained inter-thread synchronizations on the shared memory of modern GPUs. By reassembling the low-level assembly-based micro-operations that comprise an atomic instruction, we develop a highly efficient, low-cost lock approach that can be leveraged to set up a fine-grained producer-consumer synchronization channel between cooperative threads in a thread block. Additionally, we show how to implement a dataflow algorithm on GPUs using a real 2D-wavefront application.

| 1 | Inti | roduction                                                  | 1  |

|---|------|------------------------------------------------------------|----|

|   | 1.1  | Traditional GPUs                                           | 2  |

|   |      | 1.1.1 GPU History                                          | 2  |

|   |      | 1.1.2 GPU Graphics Pipeline                                | 3  |

|   | 1.2  | GPGPU                                                      | 4  |

|   |      | 1.2.1 CUDA and OpenCL make GPGPU Popular                   | 4  |

|   |      | 1.2.2 GPGPU Performance Scaling                            | 5  |

|   |      | 1.2.3 GPGPU Research Trends                                | 7  |

|   | 1.3  | Research Problems                                          | 9  |

|   | 1.4  | Thesis Contributions                                       | 11 |

|   | 1.5  | Thesis Structure                                           | 13 |

| 2 | Bac  | ekground                                                   | 15 |

|   | 2.1  | GPU Machine Model – The SM-Centric Architecture            | 15 |

|   |      | 2.1.1 Function-Units                                       | 15 |

|   |      | 2.1.2 Device Memories                                      | 16 |

|   |      | 2.1.3 Device Caches                                        | 18 |

|   |      | 2.1.4 NC and ROP                                           | 19 |

|   | 2.2  | GPU Execution Model – Massive SIMT and Thread Mapping      | 20 |

|   |      | 2.2.1 SIMT Execution Model                                 | 20 |

|   |      | 2.2.2 Thread Hierarchy Mapping                             | 21 |

|   | 2.3  | GPU Programming Model: Configuration and Compilation       | 21 |

|   |      | 2.3.1 Kernel Configuration                                 | 21 |

|   |      | 2.3.2 Compilation Trajectory                               | 22 |

|   | 2.4  | GPU Evaluation Model: Simulators, Benchmarks and Profiling | 24 |

|   |      | 2.4.1 Simulators                                           | 24 |

|   |     | 2.4.2 Benchmarks                                              | 24     |

|---|-----|---------------------------------------------------------------|--------|

|   |     | 2.4.3 Profiling-Tools                                         | 27     |

|   | 2.5 | Summary                                                       | 27     |

| 3 | X-N | Model for Parallel Machines                                   | 29     |

|   | 3.1 | Introduction                                                  | 29     |

|   | 3.2 | Basic Transit Model                                           | 31     |

|   |     | 3.2.1 Bounding Analysis                                       | 31     |

|   |     | 3.2.2 Transit Model Construction                              | 32     |

|   | 3.3 | X-Model                                                       | 36     |

|   |     | 3.3.1 X-Model Input Parameters                                | 36     |

|   |     | 3.3.2 X-Model For Parallelism                                 | 37     |

|   |     | 3.3.3 X-Model with Cache Effects                              | 39     |

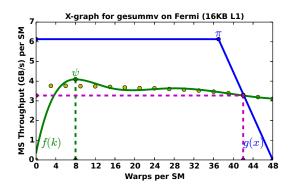

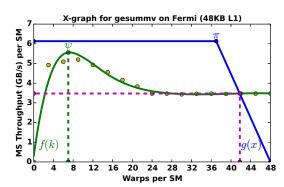

|   |     | 3.3.4 X-graphs Reflecting Cache Effects                       | 42     |

|   |     | 3.3.5 Interesting Insights Gained From the X-graph            | 42     |

|   | 3.4 | Guidelines For Plotting X-Graph                               | 44     |

|   | 3.5 | Validation                                                    | 46     |

|   | 3.6 | Case Study                                                    | 48     |

|   | 3.7 | Related Work                                                  | 52     |

|   | 3.8 | Summary                                                       | 53     |

| 4 | GP  | U Register Optimization: Critical-Points Based Register-Concu | rrency |

|   | Aut | otuning                                                       | 55     |

|   | 4.1 | Introduction                                                  | 55     |

|   | 4.2 | GPU Thread Organization and Local Memory Access               | 57     |

|   | 4.3 | CP-based Autotuning Method                                    | 57     |

|   | 4.4 | Validation                                                    | 61     |

|   | 4.5 | Discussion                                                    | 65     |

|   | 4.6 | Related Work                                                  | 66     |

|   | 4.7 | Summary                                                       | 66     |

| 5 | GP  | U Cache Optimization: Adaptive and Transparent Cache By-   |    |

|---|-----|------------------------------------------------------------|----|

|   | pas | sing                                                       | 69 |

|   | 5.1 | Introduction                                               | 69 |

|   | 5.2 | GPU Memory Access Datapaths                                | 71 |

|   | 5.3 | X-Model Analysis                                           | 72 |

|   | 5.4 | Cache Bypassing                                            | 74 |

|   |     | 5.4.1 Cache Operators                                      | 74 |

|   |     | 5.4.2 Horizontal Cache Bypassing                           | 75 |

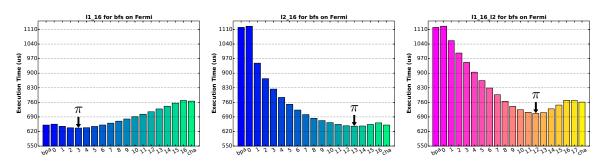

|   |     | 5.4.3 BFS Case Study                                       | 77 |

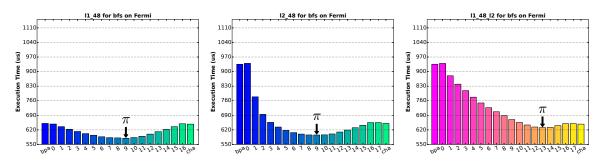

|   |     | 5.4.4 Acquire Ideal Bypassing Threshold                    | 79 |

|   | 5.5 | Evaluation                                                 | 80 |

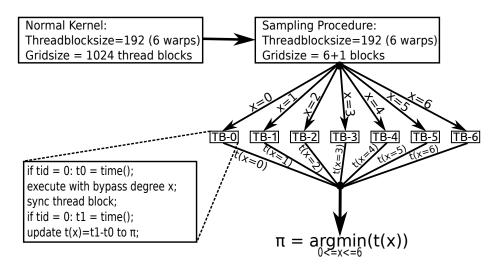

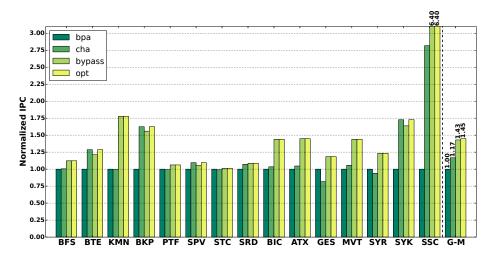

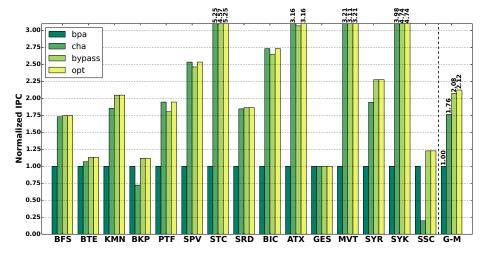

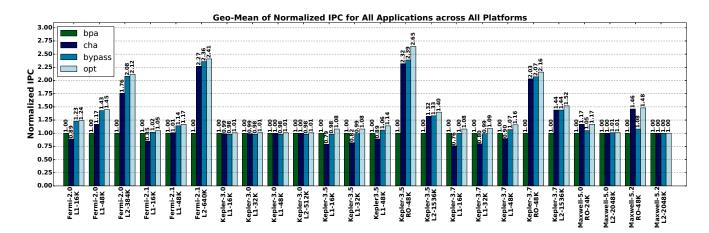

|   |     | 5.5.1 Performance Analysis Across Platforms                | 84 |

|   |     | 5.5.2 Performance Analysis Across Applications             | 84 |

|   |     | 5.5.3 Optimization Suggestions                             | 85 |

|   | 5.6 | Discussion                                                 | 85 |

|   |     | 5.6.1 Software Approach                                    | 85 |

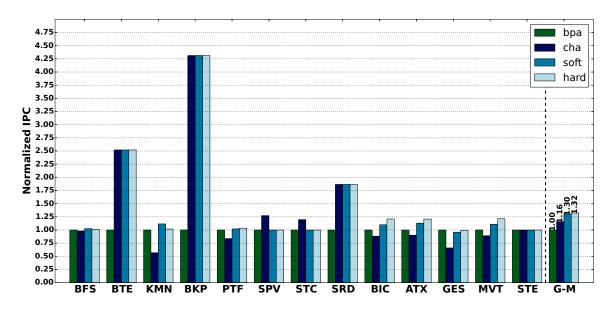

|   |     | 5.6.2 Hardware Approach                                    | 86 |

|   |     | 5.6.3 Application Bypass Patterns                          | 86 |

|   | 5.7 | Related Work                                               | 88 |

|   | 5.8 | Summary                                                    | 90 |

| 6 | GP  | U Compute Units Optimization: SFU-Driven Transparent       |    |

|   | App | proximation Acceleration                                   | 91 |

|   | 6.1 | Introduction                                               | 91 |

|   | 6.2 | SFU Design and Implementation                              | 93 |

|   |     | 6.2.1 SFU Design                                           | 93 |

|   |     | 6.2.2 SFU Implementation                                   | 94 |

|   | 6.3 | Measurement and Observation: Exploration of SPU, DPU and   |    |

|   |     | SFU                                                        | 95 |

|   | 6.4 | SFU-Driven Approximation Acceleration: A Software Approach | 98 |

|   |     | 6.4.1 Flexible SPU/DPU/SFU APIs Invocation                 | 99 |

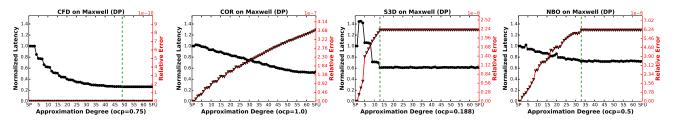

|   | 6.4.2 Controlling Approximation Degree Horizontally              | 100 |

|---|------------------------------------------------------------------|-----|

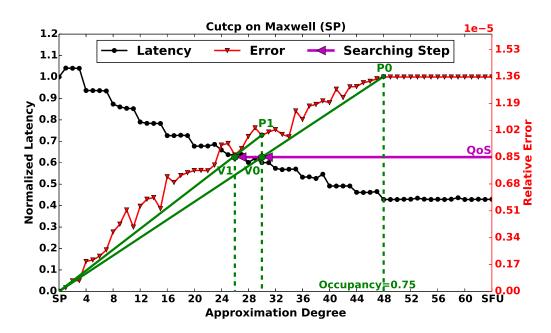

|   | 6.4.3 Exploring the Performance-Accuracy Trade-off               | 102 |

|   | 6.4.4 Finding the Optimal Approximation Degree                   | 105 |

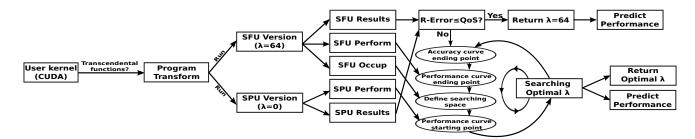

|   | 6.5 Overall Framework                                            | 107 |

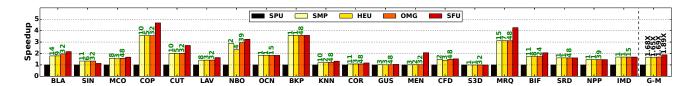

|   | 6.6 Validation                                                   | 108 |

|   | 6.7 Related Work                                                 | 110 |

|   | 6.8 Summary                                                      | 111 |

| 7 | <b>GPU Shared Memory Optimization:</b> Fine-Grained Synchroniza- |     |

|   | tion and Dataflow Programming                                    | 113 |

|   | 7.1 Introduction                                                 | 113 |

|   | 7.2 Lock Unit on GPU Shared Memory                               | 115 |

|   | 7.2.1 Shared Memory Lock Unit                                    | 115 |

|   | 7.2.2 Shared Memory Atomic Operations                            | 116 |

|   | 7.3 Fine-Grained Synchronization                                 | 117 |

|   | 7.3.1 Motivation                                                 | 117 |

|   | 7.3.2 Tiny-Lock                                                  | 117 |

|   | 7.3.3 Fine-Grained Synchronization                               | 120 |

|   | 7.3.4 Deadlock                                                   | 121 |

|   | 7.3.5 Warp-Shared Lock Bit                                       | 123 |

|   | 7.4 Validation                                                   | 124 |

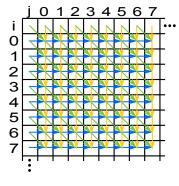

|   | 7.5 Wavefront Application                                        | 127 |

|   | 7.6 Related Work                                                 | 130 |

|   | 7.7 Limitations                                                  | 131 |

|   | 7.8 Summary                                                      | 131 |

| 8 | Conclusion and Future Work                                       | 133 |

|   | 8.1 Conclusion                                                   | 133 |

|   | 8.2 Future Work                                                  | 136 |

|   | 8.2.1 X-model                                                    | 136 |

|   | 8.2.2 Register-Parallelism Tradeoff                              | 136 |

| 8.2.3 Cache Bypassing               | 137 |

|-------------------------------------|-----|

| 8.2.4 Performance-Accuracy Tradeoff | 137 |

| 8.2.5 Fine-grained Synchronization  | 138 |

| References                          | 139 |

| Appendix A                          | 158 |

| Appendix B                          | 161 |

| Abbreviations                       | 165 |

| Curriculum Vitae                    | 167 |

| List of Publications                | 168 |

## Introduction

High computing capability is always in high demand, especially for modern emerging applications, such as physical, chemical and biological simulations, data mining, computational financing, high-quality video processing, machine learning, big-data processing, virtual reality, etc. Traditionally, all applications are executed in Central-Processing Units (CPUs). However, the ever increasing compute demand substantially outstrips the scaling of CPU performance. Therefore, various compute accelerators are introduced, including Graphics Processing Units (GPUs) [1], Xeon Phi [2], Field-Programmable Gate Arrays (FPGAs) [3] and the recently shipped Micron Automata Processors [4]. Within all these accelerators, GPUs are most popular due to their easier accessibility, since a GPU, no matter integrated or independent, is the default component for displaying in a modern computer system.

Traditionally, GPUs are utilized for graphics purposes only. However, with the high demand of computing capability and the increased programmability of GPUs, people are seeking to apply GPUs also for (**G**)eneral-(**P**)urpose applications, known as **GPGPU** [1]. For some applications, GPUs are reported to achieve hundreds of times speedup over CPUs [5, 6, 7, 8, 9].

Although GPUs obtain great success and demonstrate much faster performance scaling [10], the ever-growing compute demand still enforces great pressure over the performance scaling of GPUs. On the other hand, with a completely divergent design principle, the throughput-oriented GPUs incorporate much larger volume of light-weighted cores and threads than the latency-oriented CPUs, which devote a large portion of their on-chip areas for caches. Therefore, conventional CPU-targeted optimizations strategies, especially for reducing latency, are no longer applicable for GPUs; the community requires new optimization approaches specially for GPUs. Even worse, when a GPGPU application shows certain performance on a GPU device, it is hard for the CPU developers to locate the GPU performance bottlenecks, since the latency bottlenecks are not necessarily the throughput bottlenecks, either in software or hardware.

This thesis attempts to answer the two fundamental questions about GPGPU performance: "how to explain and improve GPGPU performance", via *performance modeling* and *software-based optimization* approaches. We propose a high-level, visualizable analytic model for analyzing the performance of throughput-oriented parallel machines, with GPUs being the best representative. Meanwhile, we target various design tradeoffs for general GPGPU programs and present four primary

#### **Chapter 1. Introduction**

software-based optimization strategies. The four strategies, focusing on GPU registers, caches, function units and scratchpad memory respectively, are validated on multiple GPU platforms in different generations to show their portability and great benefits.

The remaining part of this chapter is organized as follows. In Section 1.1 we briefly review GPU's history and the conventional graphic rendering pipeline. In Section 1.2, we summarize the development, the performance scaling and the research trends of GPGPU. In Section 1.3, we propose the research problems of this thesis. In Section 1.4, we list the contributions of this thesis. Finally, in Section 1.5, we draw an outline of the remaining chapters.

## 1.1 Traditional GPUs

According to Wikipedia, GPU is traditionally defined as a specialized electronic circuit to rapidly manipulate and alter memory to accelerate the creation of images in a frame buffer intended for output to a display. In this section, we briefly describe the origin of GPU and the conventional design purpose of GPU — to process graphics via the graphics rendering pipeline.

#### 1.1.1 GPU History

Each commodity hardware is designed with specific customer requirements from certain markets. GPU, as an indispensable component for modern computer systems, was born and grown with the demand of high-quality graphic display from video-game players. Early to 1970s, chips specialized for graphic utilizations had been implemented in the arcade system boards (Figure 1.1). The major reason is that the random-access memory (RAM) utilized as the frame buffers for the display of these video games were too expensive at that time. A good example for such specialized chips was *Fujitsu's MB14241 video shifter* (Figure 1.2), which was designed to accelerate the drawing of sprite graphics for various arcade games, e.g., *Gun Fight* (1975), *Sea Wolf* (1976) and *Space Invaders* (1978). In 1982, the system boards for arcade games such as "*Robotron:2084*", "*Joust*" and "*Bubbles*" all included custom coprocessors for operating 16-color bitmaps [11]. In 1988, the *CPS-1* arcade system board developed by *Capcom* contained a graphics chipset that offered a 65,536 color palette and hardware support for sprites, scrolling and multiple playfields. From early 1990, CPU-assisted real-time 3D graphics became increasingly popular in arcade, computer and console games, which led to the high demand for hardware-accelerated 3D graphics, e.g., *Sega Model, Namco System-22* arcade system boards and *Saturn, PlayStation* video game consoles.

At the same time, *OpenGL* [12] appeared as a professional graphics API. Early implementations of OpenGL were based on software, but soon hardware implementation became the trend. Meanwhile, *DirectX* [13] appeared as the popular graphics API for Windows game developers. To be compatible with these fast developed graphics APIs, 3D accelerator cards started to add substantial hardware stages beyond the conventional 3D rendering pipeline, which led to the release of the world's first

Figure 1.1: Arcade Machine

Figure 1.2: Fujitsu MB14241

Figure 1.3: NVIDIA GeForce 256 GPU

genuine GPU product – the NVIDIA GeForce 256 [14] (Figure 1.3). By "genuine", NVIDIA's official website technically describes a GPU as "A single chip processor with integrated transform, lighting, triangle setup/clipping, and rendering engines that is capable of processing a minimum of 10 million polygons per second.". Later in 2001, NVIDIA announced the first GPU that supported programmable shading<sup>1</sup>, known as GeForce 3, which was adopted in the Microsoft Xbox console. In 2002, ATI introduced Radeon 9700, which was the world's first Direct3D 9.0 GPU, and in which pixel and vertex shaders were capable to implement floating-point operations and loops. With these features, GPUs became much more flexible and offered orders of magnitude performance speedup for operations upon image-like arrays than their CPU counterparts. The introduction of NVIDIA GeForce 8800 further improved the flexibility of GPUs by integrating generic streaming processing units. Such increased flexibility, together with the tremendous potential performance benefit, led to the tendency of GPGPUs.

#### 1.1.2 GPU Graphics Pipeline

GPU was originally designed to process graphics via the so-called *graphics rendering pipeline*. Rendering refers to the process of generating image on the display (e.g., a monitor) from the model descriptions. Figure 1.4 shows a 3D graphics rendering pipeline, which reads in the descriptions of 3D objects in terms of vertices and primitives. Primitives here refer to the shapes or connected vertices, such as triangle, point, line and quad. The pipeline outputs the color values for all the pixels on the display. The graphics rendering pipeline is composed by the following stages:

Figure 1.4: The 3D Graphics Rendering Pipeline

• **Vertex Processing.** It is performed by vertex processors, which transform individual vertices into a common coordinate system (e.g., via rotation, translation and scaling).

<sup>&</sup>lt;sup>1</sup>Shaders are the short programs that describe the properties of a vertex or a pixel before being projected onto the screen.

#### **Chapter 1. Introduction**

- **Rasterization.** It is performed by rasterizers, which convert primitives into fragments<sup>2</sup>.

- **Fragment Processing.** It is performed by fragment processors, which process individual fragments (e.g., binding texture).

- Merging. It is to combine all the processed fragments of primitives (in 3D space) into a 2D array of pixels for displaying.

For old GPUs, the four stages in the rendering pipeline were fixed. But soon (e.g., in GeForce 3), the vertex processing and fragment processing stages became programmable. People can write vertex shaders and fragment shaders to do custom transformations of vertices and fragments. The shader programs are in C-like style. Typical shading languages are *GLSL* (OpenGL Shading Language) [15], *HLSL* (High-Level Shading Language for Microsoft Direct3D) [16] and *Cg* (C for Graphics used by NVIDIA) [17].

#### 1.2 GPGPU

With the enhanced programmability of GPUs (e.g., the vertex processors and fragment processors), GPGPU becomes possible. However, the real prosperity of GPGPUs could not appear without the existence of generic programming models, such as *Compute-Unified-Device-Architecture* (CUDA) [10] and *Open-Computing-Language* (OpenCL) [18]. In this section, we introduce these models and the recent development of GPGPUs, attempting to answer the questions about *why GPGPUs become so popular? What are the utilizations of GPUs in different domains? What is the performance scaling of GPUs? What are the current popular GPGPU research topics?*

#### 1.2.1 CUDA and OpenCL make GPGPU Popular

Prior to the introduction of CUDA and OpenCL, programming non-graphics applications on GPUs was extremely complicated and difficult, which required deep understanding on both the graphic rendering pipelines [19], the graphic programming interface (e.g., DirectX [13] and OpenGL [12]) and possibly the shader languages (e.g., Sh [20] and Brook [21]). Most of the GPGPU applications at that time were linear-algebra programs performing intensive mathematic operations on image-like arrays in a streaming fashion [22, 23, 19, 24, 25].

These programming difficulties had been greatly mitigated since CUDA was published in 2007. CUDA, as the world's first and probably the most widely accepted GPGPU programming framework, was designed to work with popular programming languages such as C, C++, Fortran, Matlab and Python. Under the persistent promotion by NVIDIA, both CUDA and GPGPU gained great success and had been utilized in various domains. As a direct response, the other major GPU vendor –

$<sup>^2</sup>$  Fragments are the pixels in 2D or 3D space that are aligned with the pixel grid, with attributes such as position and color.

#### Chapter 1. Introduction

**Table 1.1:** NVIDIA GPU Architecture Generations. Compute Capability (X.Y) is to describe the hardware version of a GPU: X is the major architecture generation (e.g., Kepler is 3, Maxwell is 5, etc.); Y is the minor architecture version in the same generation (therefore sharing the same ISA.

| Arch.   | Release Year | <b>Compute Capability</b> | Process  | Most highlighted Features    | Flagship GTX/Tesla/Jetson GPUs                                                   | Ref.     |

|---------|--------------|---------------------------|----------|------------------------------|----------------------------------------------------------------------------------|----------|

| Tesla   | 2008         | 1.0, 1.1, 1.2, 1.3        | 65 nm    | GPU baseline architecture    | GTX8800, GTX9800, GTX280,<br>Tesla1060                                           | [45]     |

| Fermi   | 2010         | 2.0, 2.1                  | 40 nm    | L1/L2 caches, dual scheduler | GTX480, GTX460, GTX580,<br>Tesla2070                                             | [46][47] |

| Kepler  | 2012         | 3.0, 3.2, 3.5, 3.7        | 40/28 nm | Floating-point performance   | GTX680, GTX-TitanZ, Tesla-K10,<br>Tesla-K20, Tesla-K40, Tesla-K80,<br>Jetson-TK1 |          |

| Maxwell | 2014         | 5.0, 5.2, 5.3             | 28 nm    | Power efficiency             | GTX750Ti, GTX980, GTX-TitanX,<br>Tesla-M40, Tesla-M60, Jetson-TX1                | [50][51] |

| Pascal  | 2016         | 6.0                       | 16 nm    | 3D Memory, numeric SMs       | Tesla-GP100, GTX1080                                                             | [52]     |

AMD, together with Apple, IBM and Intel, published a unified programming standard, known as OpenCL [26] for heterogeneous platforms, including GPUs [18], CPUs [27] and FPGAs [3]. NVIDIA also announced the support of OpenCL thereafter [28].

Although OpenCL is more general and vendor-independent, CUDA is more widely-adopted for GPGPU developers. It offers much stronger lower-level controllability over the GPU hardware (e.g., cache prefetching and bypassing, register throttling, low-level synchronization, etc), which substantially facilitates the extraction of the remarkable computing power of modern GPGPUs. Moreover, the great portability of OpenCL comes at a cost — to migrate an OpenCL program written for GPUs to CPUs or FPGAs, significant efforts are always necessary to attain the expected performance. That is why in this thesis, CUDA, rather than OpenCL, is utilized as the GPU programming language. Besides, all the GPU platforms for evaluation in this thesis are NVIDIA GPUs. For that reason, we also use CUDA terminology in this thesis.

Thanks to CUDA and OpenCL, today, GPGPUs are widely adopted for various application domains, including Linear Algebra [29], Image & Video Processing [30], Searching [31], Physical & Biological Simulations [32], Data Mining [33], Bioinformatics [34], Machine Learning [35], Computational Finance [36], etc. Most of the example applications for these domains can be found in the open-source GPGPU benchmarks, such as Rodinia [37], Parboi [38], Shoc [39], Polybench [40], Mars [33], LonestarGPU [41], CUDA-SDK [42] and GPGPU-sim [43]. Their characteristics are summarized in Chapter 2. In addition, the book GPU Computing-Gems [44] provides thorough descriptions about a broad domain of GPGPU applications.

#### 1.2.2 GPGPU Performance Scaling

For NVIDIA GPUs, during the past decade, there are in total five major architecture generations: **Tesla, Fermi, Kepler, Maxwell** and **Pascal**. (see Table.1.1). The Tesla architecture [45] is the first CUDA-enabled GPU architecture and is already out of date now. It does not even appear in the recent official CUDA programming guide [53]. Fermi, as a direct response to the criticism from its competitor [54], introduced the two-level cache hierarchy and the functionality of multi-issuing. The Kepler GPUs are most high-lighted for their enormous compute capability, as they contained

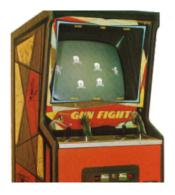

Figure 1.5: The Scaling of NVIDIA GTX Products for Desktop Utilizations

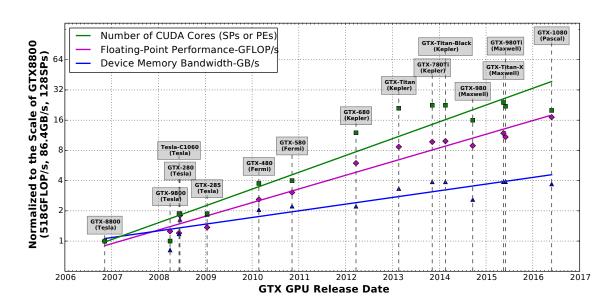

Figure 1.6: The Scaling of NVIDIA Tesla Products for Supercomputer Utilizations

the most number of CUDA cores per streaming-multiprocessor. From Maxwell, GPU started to put power-efficiency, in addition to performance, as its primary design principle. Finally, the latest Pascal architecture [52], which was announced early this year (2016), is known for introducing the 3D stacked memory and the ability to quickly process half-precision (16 bits) calculations. Note, the *GTX product-line* is for desktop utilizations; the *Tesla product-line*<sup>3</sup> is for high-performance-computing (HPC) utilizations; the *Jetson TK1* and *TX1* are for embedded system (ES) utilizations.

Figure 1.5 illustrates the performance scaling of NVIDIA GTX and Tesla flagship GPU products in terms of CUDA cores, single-precision floating-point performance (GFLOP/s) and global memory

<sup>&</sup>lt;sup>3</sup>The name "Tesla" is used by NVIDIA for both a GPU product line and a GPU architecture generation.

#### **Chapter 1. Introduction**

throughput (GB/s), normalized to the first CUDA-capable GPU — GTX8800 during the past decade. Specially, Figure 1.6 illustrates the performance scaling for NVIDIA Tesla Product GPUs, which represent the most advanced GPUs in each generation for HPC. The metrics are normalized to the first Tesla product – Tesla-C870.

As can be seen, the scaling of the three important performance metrics roughly comply with *Moore's Law* (i.e., performance doubles each two years, thus about 32 times in a decade). Additionally, we have the following observations:

- From GTX-Titan and Tesla-K10 onwards, the number of CUDA cores in a GPU does not increase much. This is due to the fall of CUDA cores per streaming-multiprocessors (SM) since Kepler the number of CUDA cores per SM evolved from 32 in Tesla, to 48 in Fermi, to 192 in Kepler, to 128 in Maxwell and finally 64 in Pascal. Despite the stagnant core scaling, the deliverable floating-point performance has continuously increased in an exponential speed (red lines in Figure 1.5 and 1.6).

- The scaling of memory bandwidth remains far behind the scaling of cores or floating-point performance, which indicates that the memory-wall continuously remains the major challenge for harvesting GPU performance. In fact, also from Tesla-K10, the memory bandwidth scaling has slowed down significantly. However, such a big performance-scaling gap has substantially mitigated in the latest Pascal GPUs, which adopt the so-called High-Bandwidth-Memory 2 (HBM2) 3D-stacked memory technology [52]. This technology packs the memory dies in 3D and links them vertically via the through-silicon-vias (TSVs), which significantly reduces the wire length and the memory accessing latency while enhancing the accessing bandwidth.

#### 1.2.3 GPGPU Research Trends

To further improve GPGPU performance and broaden the utilization of GPGPUs, contemporary GPGPU research mainly focuses on the following four topics:

**Performance Scaling**: As heterogeneous accelerators such as GPUs play a crucial role in the performance scaling towards exascale computing [55, 56, 57], continuously enhancing performance for these accelerators always remains a major research topic, from both software and hardware perspectives. This is also the focus of this thesis.

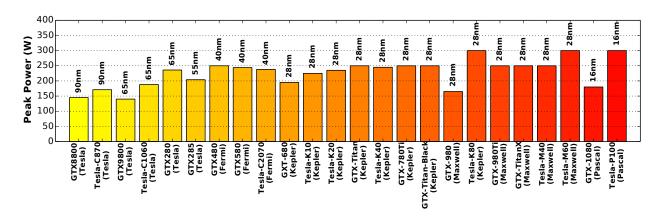

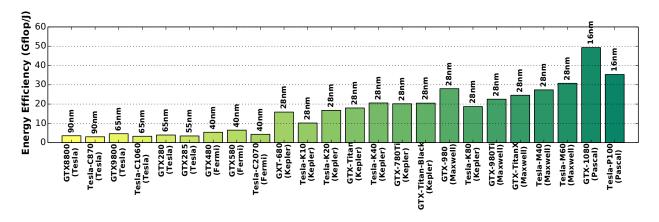

**Energy Reduction**: GPU is heavily criticized for its considerable power consumption. Therefore, efficiently reducing power while continuing the performance scaling is an important research topic for GPUs. Typical methods including clock-gating [58, 59], power-gating [60, 61, 62] and DVFS [63, 64]. Figure 1.7 summarizes the power consumption for the aforementioned GTX and Tesla GPUs with the evolving of CMOS manufacturing process. Figure 1.8 shows their energy efficiency (Gflop/joule or flop/s per watt). As can be seen, the energy efficiency of GPUs continuously scales with improved architectures and manufacturing processes.

Figure 1.7: The Manufacturing Process and Peak Power Consumption for NVIDIA GTX and Tesla Flagship GPUs.

**Figure 1.8:** The Manufacturing Process and Energy Efficiency (with peak power consumption) for NVIDIA GTX and Tesla Flagship GPUs.

Emerging Applications: Today, the increased programmability of GPGPUs makes most contemporary applications relatively easy to migrate on GPUs. However, efficiently implementing irregular applications, especially the graph-related algorithms from big-data applications, still remains a difficult task. Therefore, the strategies to efficiently implement irregular algorithms on GPUs and the hardware designs to optimize GPU architectures for irregular routines/data-structures persistently remain hot research topics for GPGPU [65, 66, 67, 68]. Another type of emerging application domain is machine learning, especially the deep-learning [69, 70, 71]. In fact, the latest Pascal GPU P100 is specially designed for deep-learning utilizations (FP16 support, HBM2 memory, NVLink, large register file, large L2 cache as well as the specially-designed DGX-1 system for deep-learning [52]).

**Resilience Related**: There are three topics about resilience-related issues on GPUs: *approximate computing*, *fault-tolerance* [72, 73, 74] and *reliability* [75, 76, 77]. Specially, under the pressure of continuous performance scaling and power control, and given the inherent fault-tolerant properties of the emerging applications (e.g., big-data, multimedia and machine-learning), approximate computing quickly becomes an emerging and promising technique for GPGPU. This is one of the most rapidly developing areas for GPU research [78, 79, 80, 81, 82, 83].

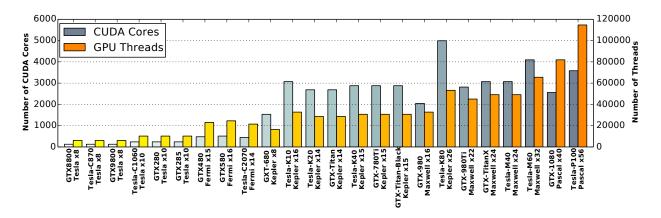

#### 1.3 Research Problems

Moore's Law has continued to show promise, but the end of clock-frequency scaling for uniprocessors has driven mainstream computation towards the multi-core era [84]. Multi-core processors offer enormous computing power, but insufficient exploitable parallelism and long-latency remote communication, typically off-chip memory access, restrict the attainable performance [85]. Consequently, *multithreading* [86] [87] has been proposed as an effective solution. It raises processor utilization through thread-level parallelism (TLP) and hides memory delay via fast context switching. Multithreading was later evolved to be applied on wide-issue superscalar processor, known as *simultaneous multithreading* [88] [89], vector processor, known as *vector multithreading* [90] [91] and chip multiprocessor, known as *chip multiprocessing* [92] [93]. The last decade has seen the blooming emergence of *massively fine-grained multithreaded architectures*, such as GPGPUs [45] [47]. In this evolution process, both the number of cores and threads have increased dramatically. Nowadays, a single GPU chip encapsulates up to 5,000 scalar cores and accommodate over 110,000 active threads simultaneously. The scaling of GPU cores and threads are shown in Figure 1.9.

Obviously, analyzing and tuning performance for such massively multithreaded-multicore platforms becomes a big challenge. Although modest speedup could be attained through basic functional porting, programmers have to spend significant time and effort to identify and alleviate the system bottleneck before fully extracting the hardware potential. This is especially the case when little is known about the underlying implementation of the target machine, such as GPUs. Therefore, many programmers and designers have to search exhaustively in a huge design space or rely entirely on former experience obtained from CPUs.

Profilers and simulators can be helpful for performance learning and tuning. However, most profilers only display dozens of raw measurements of the profiling counters, and it is often daunting for programmers to integrate these metrics coherently to address the true causes of slowdowns, much less identify what optimization step to take next so that bottlenecks could be mitigated or eliminated [94]. Further, the kinds of information tracked by profilers are severely limited by the diversity of the hardware performance counters, which are "historically cavaliered" by architects [95]. Simulators are more flexible and accurate, but often hindered by expense, since both developing and using a simulator for a detailed simulation is quite time-consuming. More importantly, the simulator itself does not provide any insights about why certain designs are adopted by architects and how programmers could refine their code accordingly. In one word, the profiler and simulator do not help to *understand the performance*.

Analytical model provides an alternative approach. In general, an analytical model falls into one of two categories: it either models a particular architecture that requires numerous parameters to grasp the detailed machine features, so as to predict performance precisely, e.g. [96, 97], or it models a general machine that is easy to understand and manipulate, in order to highlight new behaviors, explain observed phenomena, and derive intuition, e.g. [98, 99]. Models in the second category are of more interest, as they offer insights about general machines at a higher level.

**Figure 1.9:** The Number of Cores and Maximum Number of Active Threads for NVIDIA GTX and Tesla Flagship GPU Products in the past decade. Note, the core number uses the left Y-axis while the thread number uses the right Y-axis. As can be seen, after ten years exponential scaling, today the number of cores has reached as many as 5,000 while the volume of resident threads is nearly 120,000 in a single GPU card! Such a "thousands-of-cores while hundreds of thousands of threads in a card" situation is never imaginable in any conventional CPU contexts.

Various analytical models have been proposed for multithreaded machines, such as [100, 101, 102, 99, 103, 104] for traditional multithreaded processors and [105, 97, 106, 94] specially for GPUs. All of these models, however, predominately focus on the temporal behavior of a "typical thread" or "average thread", without considering the thread parallelism and thread interaction. In addition, most of the these models belong to the first category and are aimed at time prediction, so they are devoted to the precise modeling of low-level details. Such an effort requires large amount of parameters and the model itself can be time consuming to understand and implement. Furthermore, most of these existing models are based on symbolic analysis and are not visualizable.

The Roofline model [98, 85] falls into the second category. It draws a simple roofline-like figure to show the variation of machine throughput with respect to the arithmetic intensity of the workload, so as to derive intuition [98]. However, the roofline model is essentially for sequential machines, as no concept of parallelism is involved or addressed in the model. In addition, it only models the influence of arithmetic intensity, which is too optimistic and simplified in many conditions, e.g., evaluating a shared cache. Furthermore, the roofline model is static. It cannot suggest potential optimizations; nor it can tell whether a particular optimization is effective or not — all application-related features are attributed to a single parameter, the arithmetic intensity.

Therefore, for multithreaded multicore machines such as GPUs, is there an analytic model that is similar to the roofline model (i.e., simple, visualizable and intuitive) but is parallel, dynamic and comprehensive? In particular, an analytic model that can answer the following questions is desired:

- How to understand the impact from various types of parallelism in modern parallel machines, from both hardware and software perspectives?

- Given a specific application on a specific platform, what are the possible performance bottlenecks? Why a bottleneck appears there?

#### **Chapter 1. Introduction**

• What kind of optimizations can be applied to mitigate or even eliminate the bottlenecks? How much performance gain can be anticipated if a specific hardware or software optimization is adopted?

Having an analytic model to understand the performance bottlenecks, the next step is to actually optimize performance. Although huge amount of works have been proposed regarding GPU performance optimizations, the following general observations about them are derived:

- Most of the existing optimization techniques are migrated from CPU-based design schemes, thus a majority of them still follow the conventional sequential-design paradigm (e.g., latency-oriented, cache-enforced). However, modern highly parallel computation platforms such as GPUs, follow a completely distinct parallel-design paradigm (e.g., throughput-oriented, off-chip bandwidth enforced). Thus, these optimization techniques may not obtain expected performance (e.g., cache prefetching is not that effective for GPUs due to good latency hiding).

- Most of the existing optimizations are hardware-based and validated using high-level simulators. These designs may suffer from usability, realiability and timing concerns: (i) Usability: while some designs show promising and sufficiently demonstrated in a simulator written in high-level language (e.g. C++, Java), they are extremely difficult or too costly to be implemented in low-level hardware. (ii) Reliability: as few hardware implementation details about GPUs are public available, the simulator utilized for validation may not be sufficiently accurate, as will be seen in Chapter 5. (iii) Timing: although some of the hardware designs appear to be reasonable, they can only benefit future hardware products; existing hardware cannot gain from a hardware design or modification.

- Most of the exisiting optimizations are architecture-specific and only validated on a single platform (e.g., the Fermi-based GPGPU-Sim or a single GPU card). As GPU architecture is evolving quite fast, these techniques may suffer from portability concern.

Therefore, regarding performance tuning, are there any optimization techniques that are specially designed for GPUs, purely software-based, and portable among various GPU architectures?

#### 1.4 Thesis Contributions

Targeting on the research problems proposed, this thesis makes the following contributions:

The first contribution is a novel analytic model for throughput-oriented parallel machines presented in Chapter 3, called X [107, 108]. It is visualizable and is specially designed for parallel machines. It can be used to comprehensively analyze the interaction/tradeoffs between four major types of parallelism (i.e., thread-level parallelism, instruction-level parallelism, data-level parallelism and memory-level parallelism) and two types of memory effects (local on-chip cache effect and remote off-chip memory effect), in terms of system throughput. The X-model acts as the theoretical basis

#### **Chapter 1. Introduction**

of this thesis. It is used to analyze the underlying tradeoffs between concurrency and registers in Chapter 4, and between memory-level parallelism and cache-performance in Chapter 5.

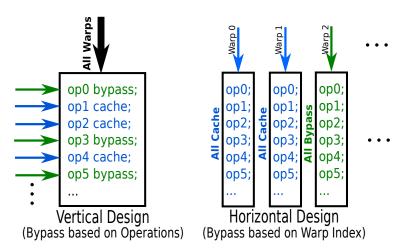

The second contribution is a new design paradigm specially for GPUs, called **bico-scheduling**. It is based on the unique single-instruction-multiple-threads (SIMT) execution model of GPUs. SIMT has two typical features: single instruction-stream (SI) and multiple-threads (MT), which enables a general design technique for GPU architecture modification and performance tuning, labeled as binary co-scheduling, or bico-scheduling for short. It is motivated from the observation that when a new function module is integrated into GPUs for acceleration purposes (e.g., an on-chip cache, a special-function-unit), the excessive GPU threads often flood the module and lead to fierce resource contention, which limits the performance. The bico-scheduling here introduces a fine-grained performance tuning space, so that the large amount of GPU threads are separated into dual groups targeting two paths: one for the accelerator module as a fast path, and the other for the original path as a slow path (e.g., one thread-group buffers in the on-chip cache, the other thread-group bypasses the cache). In addition, a runtime-tunable threshold is introduced to control the partition degree for the two groups, so as to reach a good balance between parallelism and the utilization of the accelerator module (i.e., bico-scheduling among fast path and slow path). Such a design paradigm is only for GPU as the feature of SI creates a monotonic tuning space (threads are identical) while the MT feature enables a very fine-grained, incrementally changed tuning space, both are non-existent in conventional processors. It thus leads to many novel optimization opportunities for GPUs, such as the one for caches in Chapter 5 and the one for SFUs in Chapter 6. It is also possible to apply this paradigm upon other on-chip modules, such as NoC, lock-bit, registers, etc.

The third contribution is the four GPU-specific, software-based and architecture-independent optimization approaches that cover most of the function modules inside a GPU streaming processor: register-files (Chapter 4), caches (Chapter 5), compute units (Chapter 6) and shared memory (Chapter 7). They differentiate each other by targeting different design tradeoffs: per-thread performance vs. parallelism for register files in Chapter 4, per-thread cache performance vs. overall cache performance for caches in Chapter 5, compute performance vs. compute accuracy for compute units in Chapter 6 and shared memory performance vs. programmability for scratchpad memory in Chapter 7.

#### Particularly,

- In Chapter 4, we propose an effective autotuning approach to resolve the conflict between overall thread concurrency and per-thread register usage for GPUs. We discover that the performance impact from register usage is almost continuous, but from concurrency is discrete. Their joint-effects form a special relationship such that a series of critical-points can be precomputed. These critical-points denote the best performance for each concurrency level. Therefore, the global optimum, which refers to the optimal number of registers per-thread, can be quickly and efficiently selected to deliver the best GPU performance [109].

- In Chapter 5, we propose an adaptive cache bypassing framework for GPUs. It uses a simple but effective approach to throttle the number of threads that could access the three types of

GPU caches – L1, L2 and read-only caches, thereby avoiding the fierce cache thrashing of GPUs, and significantly improving the performance for cache-sensitive applications [110].

- In Chapter 6, we focus on a crucial GPU component that has long been ignored the Special Function Units (SFUs) and show its outstanding role in performance acceleration and approximate computing for GPU applications. We exhaustively evaluate the numeric transcendental functions that are accelerated by SFUs and propose a transparent, tractable and portable design framework for SFU-driven approximate acceleration on GPUs. It partitions the active threads into a PE-based slower but accurate path, and a SFU-based faster but approximated path, and tunes the relative partition ratio among two paths to control the tradeoffs between the performance and accuracy of the GPU kernels. In this way, a fine-grained and almost linear tuning space for the tradeoff between performance and accuracy can be created [82].

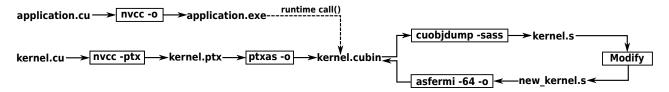

- In Chapter 7, we propose a novel approach for fine-grained inter-thread synchronization on the shared memory of modern GPUs. By reassembling the low-level assembly-based micro-operations that comprise an atomic instruction, we develop a highly efficient, low-cost lock approach that can be leveraged to set up a fine-grained producer-consumer synchronization channel between cooperative threads in a thread block. Additionally, we show how to implement a dataflow algorithm on GPUs using a real 2D-wavefront application [111].

#### 1.5 Thesis Structure

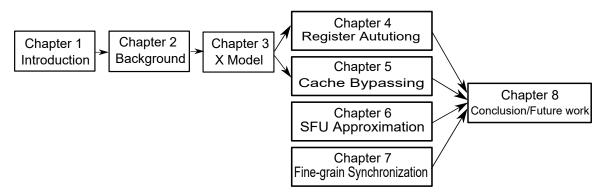

Figure 1.10: Thesis Structure

As shown in Figure 1.10, the thesis is organized as follows: Chapter 1 makes the introduction. Chapter 2 discusses the background knowledge about GPUs — the machine model, the execution model, the programming model and the evaluation model. Chapter 3 presents the X-Model for parallel machines, which is later applied in Chapter 4 and 5. Chapter 4 discusses the register file optimization technique for GPUs. Chapter 5 talks about the cache optimization technique for GPUs. Chapter 6 describes the compute units optimization technique. Chapter 7 shows the shared memory optimization technique. Finally, Chapter 8 summarizes the thesis and discusses future work.

## **Background**

To make an easier description of the GPGPU analytic model and optimization techniques in the next several chapters, we describe some background knowledge about modern GPGPUs in this chapter. To show readers a complete and comprehensive view about GPGPU, we describe it from four aspects: *GPU Machine Model* (i.e., architecture), *GPU Execution Model* (i.e., thread hierarchy and mapping to hardware), *GPU Programming Model* (i.e., kernel configuration and compilation) and *GPU Evaluation Model* (i.e., simulators, benchmarks and profiling tools).

#### 2.1 GPU Machine Model – The SM-Centric Architecture

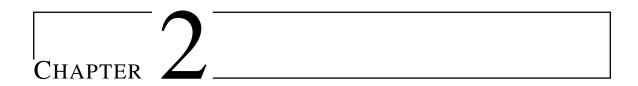

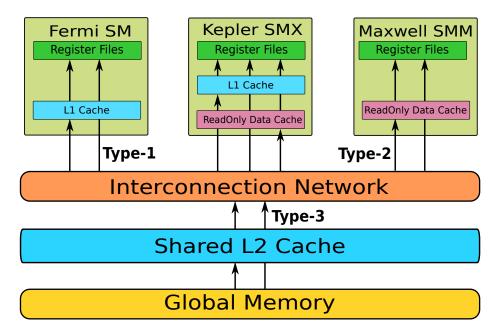

A GPU is composed of multiple *streaming-multiprocessors* (SMs), sharing an L2 cache and DRAM controllers via a crossbar interconnection network (NC). The SMs are the central parts of the GPU architecture, which perform all the vertex/geometry/pixel-fragment shader-programs and GPGPU-programs. As shown in Figure 2.1, an SM features a number of *scalar processor* cores (SPs) and two other types of function-units — the *Double-Precision Units* (DPUs) for double-precision (DP) floating-point calculations and the *Special-Function Units* (SFUs) for processing transcendental functions and texture-fetching interpolations. Other components, such as the *register files* (RFs), *load-store units* (LSUs), *scratchpad memory* (i.e., shared memory), and various caches (i.e., *instruction cache, constant cache, texture/read-only cache, L1 cache*) for on-chip data caching also reside in the SMs.

#### 2.1.1 Function-Units

This subsection introduces the four function-units inside an SM: SP, SFU, DPU and LSU.

**Scalar-Processor** (**SP**): The scalar-processors, known as the CUDA cores, are the primary basic processors in an SM, performing the fundamental integer, floating-point, comparison and type-conversion operations. Each SP contains a single-precision floating-point unit (FPU) and an integer arithmetic/logic unit (ALU) — both units are fully pipelined.

Figure 2.1: General Architecture for Modern GPUs.

**Special-Function-Unit (SFU):** The SFUs are integrated for fast transcendental function calculations (e.g., sine, cosine, reciprocal, square-root, etc.) and planar attribute interpolations. Each SFU also features four floating-point multipliers that can offer extra FP throughput in addition to SPs. The SFU pipelines are independent from the SP pipelines. We thoroughly evaluate the characteristics of SFUs in Chapter 6.

**Double-Precision-Unit (DPU):** The DPUs are the units specially for double-precision (DP) computations. They perform fused multiply-add (FMA) DP operations in highly efficient deep pipelines. The number of DPUs in an SM dictates the DP performance of a GPU device, e.g., the Maxwell GPUs have only 4 DPUs in the SMs, delivering only 1/32 DP performance compared to their SP performance. We exploit DPUs in Chapter 6.

**Load-Store-Unit** (**LSU**): As indicated by the name, the load-store units are used to fetch and save data to memory. They contain dedicated computing units to rapidly calculate the source and destination addresses for the initiated memory requests.

#### 2.1.2 Device Memories

We discuss the various types of memories in a GPU, including *register files, shared-memory, local-memory, global-memory, constant memory* and *texture memory* in this subsection. Their basic features are summarized in Table 2.1.

Register Files: GPUs overall have very large volume of registers. Due to the large size, GPU

On/Off Chip Lifetime Memory Cached Access Scope **Register Files** On N/A Read/Write Per-thread Thread **Local Memory** Off L1/L2 Read/Write Per-thread Thread **Shared Memory** On N/A Read/Write Thread Block (CTA) Thread Block (CTA) **Global Memory** Off L1/L2 Read/Write GPU+CPU Host Allocation **Constant Memory** Off Constant cache Read Only GPU+CPU Host Allocation **Texture Memory** Off Texture cache Read Only GPU+CPU Host Allocation

**Table 2.1:** GPU Device Memory Features

registers are implemented by SRAMs, which are partitioned into banks for throughput concern. Therefore, compared to CPU registers, the GPU registers experience long access latency and may suffer from potential bank conflicts [112]. We discuss how to exploit GPU registers in Chapter 4.

**Local Memory:** The local memory is not a physical memory space but rather a portion of the global memory (see below). Its scope is thread-private, the same as RFs (see Table 2.1). It is generally used for temporal spilling when there are insufficient registers to hold all the required variables (i.e., register spilling), or when the arrays are declared in the kernel but the compiler cannot decide the exact indexing to reference them. The local memory is cached by L1 and L2 in Fermi and Kepler, but is only cached by L2 in Maxwell and Pascal. Register spilling in local memory hurts the performance as it introduces extra instructions and memory traffic, especially when there is a cache miss (so the register value has to be fetched from off-chip global memory). We evaluate the impact of local cache in Chapter 4.

**Shared Memory:** The shared memory or *scratchpad memory* is an on-chip storage shared among all units inside an SM. It serves as a communication interface for fast data exchanging between different threads of a thread block (i.e., Cooperative-Thread-Array or CTA, see Section 2.2.1). Being on-chip, the shared memory has much higher bandwidth and shorter accessing latency compared to the local memory or global memory. Therefore, optimizations which can shift global/local memory access to shared memory are highly recommended by the CUDA programming guide [53]. To achieve higher bandwidth, the shared memory is partitioned into banks, thus can be accessed in parallel (similar to register files and L2 cache). However, in case two addresses from the same memory request fall in the same bank, a *bank conflict* occurs and the accesses have to be serialized, which seriously degrades the performance of the shared memory. We discuss optimization techniques regarding shared memory in Chapter 7.

Global Memory: The global memory is the *device memory*, also known as GPU off-chip memory or GPU main-memory. It is the most frequently-used memory for GPUs such that its throughput in many conditions (i.e., memory-bound applications) determines the final achievable performance of GPUs. The attainable global memory throughput, or sustainable throughput [113], is mainly constrained by two factors: *raw memory bandwidth* and *coalescing degree*. (1) The raw memory bandwidth is limited by the pin number, wire length and the physical property of DRAM; therefore it is increasing slowly since Kepler (see Figure 1.5 in Chapter 1). However, such a stagnant situation is completely changed by the 3D-stack memory technique recently applied in Pascal [52]. (2) To gain from transmitting large data blocks at a time, a technique known as *memory access coalescing*

#### Chapter 2. Background

is applied. The LSUs initially calculate the target addresses of each warp lane individually. Before memory fetching, a special Address-Coalescing hardware [114] will check whether the addresses from the same warp are continuously distributed (which is the common case for global memory access). It then notifies the Memory-Interface-Units for one or multiple aggregated block transfers from the cache or global memory [114]. The CUDA programming guide provides detailed discussion about the identification of memory coalescing [10].

Constant Memory / Constant Cache: The constant memory is used to store data that does not change during the kernel execution. It is 64 KB for all GPU generations and is off-chip. Similar to local memory, it is a special part of the global memory. However, the constant memory is not cached by L1/L2 but an individual cache known as constant cache. The 8/10 KB constant cache in each SM is specially designed so that the data of a single memory address can be broadcast to all threads across the warp at a time. However, when different addresses are requested from a warp, the accessing request has to be split into as many requests as the number of different addresses.

**Texture Memory / Texture Cache:** The texture memory or *surface memory* also resides in the global memory. It is buffered by a texture cache so that texture fetches or surface read are performed only when there is a cache miss. The texture cache is specially optimized for 2D spatial locality. Therefore, threads from a warp can gain extra performance when they access nearby addresses in 2D space [115]. Besides, the addresses of texture memory are calculated by dedicated units outside the kernel [116], thus gaining extra compute capacity. In addition, the packed (image) data (if applicable) can be unpacked and broadcast to multiple variables in a single operation [116]. As the texture cache is designed for streaming fetches with fixed latency, a cache hit reduces off-chip memory throughput demand but not the fetching latency [53].

Prior to Maxwell, the texture cache was only utilized for texture memory. However, from Maxwell onwards, the previous L1 cache, which shared the same physical storage with the on-chip shared memory in an SM, has been discarded. On the other hand, the texture cache was firstly marked as *read-only* (or non-coherent) cache [49] and later labeled as the L1 cache in the CUDA official documents [50, 51, 52]. It is claimed that the texture cache (i.e., read-only cache) has higher tag bandwidth thus supporting full speed unaligned memory access patterns [49].

#### 2.1.3 Device Caches

We have already discussed constant cache and texture cache. Nw we introduce the *L1 Instruction Cache*, *L1 data cache* and *L2 data cache*.

**L1 Instruction-Cache:** There are very few documents or literature available discussing about GPU instruction cache, specially for new GPU architectures. One may refer to [112] for analysis on the old Tesla architecture GT200 GPUs. In addition, [117] discussed instruction cache thrashing when implementing warp-based synchronization schemes on Fermi GPUs.

**L1 Data-Cache:** The L1 data cache <sup>1</sup> for GPU was firstly introduced in Fermi. The SM-private L1 cache shares the same on-chip storage with the shared memory of an SM. Their relative sizes are reconfigurable (16/48 or 48/16 KB in Fermi and 16/48, 32/32 or 48/16 KB in Kepler). The L1 cache-line is 128 B. It caches both global memory read and local memory access (read and write) and is non-coherent [46]. The local memory is generally utilized for register spilling, function calls and automatic variables [53]. The L1 cache is read-only when caching access to global memory, but is writable when caching access to local memory. As discussed, from Maxwell, the traditional L1 cache is unified with texture cache.

**L2 Cache:** The unified L2 cache is also firstly introduced in Fermi. It services all types of memory access (i.e., global, local, constant and texture) and is coherent with the host CPU memory. The L2 cache is read/writable and adopts write-back replacement policy [46]. It is the primary point for data unification [49] and is a good place for data sharing across SMs. The L2 cache is generally partitioned into banks, each of them acting as a buffer for a way of off-chip memory channel (GDDR or HBM2-DRAM), so as to significantly reduce the ultimate memory bandwidth demand.

#### **2.1.4** NC and ROP

We briefly discuss the NC and ROP in this subsection to make the description complete, although they are not relevant to the main topics of this thesis.

Interconnection Network (NC): The interconnection network among SMs and L2 banks is a crossbar network. It allows simultaneous communication between multiple SMs and L2 banks, thus offering considerable NC throughput. As introduced in [118], a typical crossbar NC encapsulates an address bus and two data buses. The address bus is unidirectional from SMs to L2 banks; whereas the two data buses form a bidirectional channel between SMs and L2 banks. Here, the communication are point-to-point [119]. A memory-request queue (MRQ) and a a bank load queue (BLQ) is attached to each SM and L2 bank, respectively. When a load request is generated from the LSUs inside an SM, it will first cache in the local MRQ and then be delivered to the destination BLQ through the crossbar NC. After some waiting time in BLQ, the request will be processed by the L2 banks. It is already known that the crossbar network comes at a high switching cost for the simultaneously connections. Particularly, when the accessing requests are random and messy, interference will appear, which leads to the reduction of effective bandwidth [120].

**Raster Operation Processor (ROP):** The fixed-function ROP is to perform color and depth frame buffer operations directly on memory. It also services the external memory load, store and atomic accesses.

Finally, we have summarized the architecture configurations for each generation of NVIDIA GPUs, as shown in Table 2.2. This is done for the ease of future references.

<sup>&</sup>lt;sup>1</sup>In this thesis, without special indication, instruction cache specially refers to L1 instruction cache while L1 means L1 data cache.

|         | 00  | n                  | C7. F |        | -   |     | -   | T 077 | G1 137      | Α .   | m .     | • 4         |         |

|---------|-----|--------------------|-------|--------|-----|-----|-----|-------|-------------|-------|---------|-------------|---------|

| Arch.   | CC. | Representative GPU | SMs   | RF     | SP  | SFU | DPU | LSU   | Shared Mem  | Const | Texture | L1          | L2      |

| Tesla   | 1.0 | Tesla-C870         | 8     | 8 KB   | 8   | 2   | N/A | N/A   | 16 KB       | 8 KB  | 12 KB   | N/A         | N/A     |

| Tesla   | 1.3 | Tesla-C1060        | 10    | 16 KB  | 8   | 2   | N/A | N/A   | 16 KB       | 8 KB  | 12 KB   | N/A         | N/A     |

| Fermi   | 2.0 | Tesla-C2070        | 16    | 32 KB  | 32  | 4   | 16  | 16    | 16/48 KB    | 8 KB  | 12 KB   | 48/16 KB    | 768 KB  |

| Fermi   | 2.1 | GTX-460            | 16    | 32 KB  | 48  | 8   | 4   | 16    | 16/48 KB    | 8 KB  | 12 KB   | 48/16 KB    | 512 KB  |

| Kepler  | 3.0 | Tesla-K10          | 8     | 64 KB  | 192 | 32  | 8   | 32    | 16/32/48 KB | 8 KB  | 48 KB   | 48/32/16 KB | 512 KB  |

| Kepler  | 3.5 | Tesla-K40          | 15    | 64 KB  | 192 | 32  | 64  | 32    | 16/32/48 KB | 8 KB  | 48 KB   | 48/32/16 KB | 1536 KB |

| Kepler  | 3.7 | Tesla-K80(x2)      | 13x2  | 128 KB | 192 | 32  | 64  | 32    | 112 KB      | 8 KB  | 48 KB   | 16 KB       | 1536 KB |

| Maxwell | 5.0 | GTX-750Ti          | 5     | 64 KB  | 128 | 32  | 4   | 32    | 64 KB       | 10 KB | 24 KB   | N/A         | 2048 KB |

| Maxwell | 5.2 | Tesla-M40          | 24    | 64 KB  | 128 | 32  | 4   | 32    | 96 KB       | 10 KB | 48 KB   | N/A         | 2048 KB |

| Pascal  | 6.0 | Tesla-P100         | 60    | 64 KB  | 64  | 16  | 32  | 16    | 64 KB       | 10 KB | 48 KB   | N/A         | 4096 KB |

Table 2.2: GPU SM Architecture. "CC." stands for Compute Capability [53].

## 2.2 GPU Execution Model – Massive SIMT and Thread Mapping

We introduce the SIMT execution model and the thread hierarchy mapping of GPUs in this subsection. These are basements for further discussions of this thesis.

#### 2.2.1 SIMT Execution Model

Evolved from SIMD, the execution model of GPUs is known as *single-instruction-multiple-threads* or **SIMT** [45, 53]. A kernel, which is a function that runs on the GPU part of the processing system (CPU+GPU), includes thousands of simultaneous lightweighted GPU threads that are primarily grouped into multiple *thread blocks* or *Cooperative-Thread-Arrays* (**CTAs**). When a kernel is launched, its CTAs are dispatched to the SMs. It is possible that several CTAs are dispatched to the same SM, depending on the available SM on-chip resources, such as the registers and shared memory. These resources are evenly divided among the concurrent CTAs of an SM.

Threads inside a CTA are further organized as a number of execution groups that perform the same operations on different data in a lockstep manner. Such execution groups are called **warps**. In an SM, a warp is the basic unit in terms of scheduling, executing and accessing cache/memory. If threads in a warp diverge at a point (e.g., upon *if-else*), all the branches will be executed alternatively and sequentially, with threads not belonging to the present branch being masked off, until divergent threads consolidate at a convergent point and continue the lockstep execution. Such a divergence (called *warp divergence*) incurs enormous overhead [121]. We deeply discuss such overhead and warp divergence issue in Chapter 7. Meanwhile, if a warp is obstructed by a long latency operation, e.g., off-chip global memory read, the warp scheduler will fetch-in another ready warp instantly with little cost [53]. How to establish an orchestrated warp scheduling for good execution overlapping or latency hiding, especially considering the positive/negative impact on the memory system, has recently become a hot research topic [122, 123, 124, 125].

GPUs support multi-issuing and multi-dispatching. During execution, the dual- or quad-warp schedulers select two or four ready warps (with up-to two independent instructions per warp [49]) to dispatch onto the different function units (e.g., SPs, SFUs). Although most instructions are accomplished by SPs, the DPUs and SFUs offer extra processing bandwidth when processing special

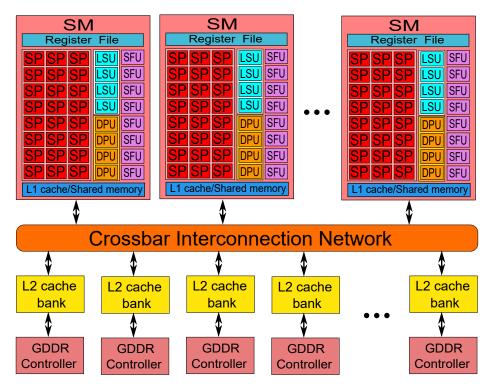

Figure 2.2: GPU Thread Hierarchy Mapping to Architecture

functions (e.g., transcendental functions) or double precision data. These special units are useful, but it is often challenging to leverage them in a balanced way. This is the reason why multi-issuing/dispatching mixed instructions to these function units remains critical for GPU performance delivery [126, 127].

# 2.2.2 Thread Hierarchy Mapping

Figure 2.2 summarizes the mapping from CUDA thread hierarchy to GPU architecture discussed in Section 2.1. As can be seen, (1) the thread instruction is mapped to a SP or SFU or DPU (in a unit of warp); (2) the thread blocks or CTAs are mapped to the SMs; (3) the thread grid is mapped to the GPU device. We also show the scope of memory introduced in Section 2.1 in the figure. The global memory, constant memory and texture memory are shared among all threads in a grid, while accessing the shared memory is only possible for threads within the same CTA. The register files and local memory are private to a thread.

# 2.3 GPU Programming Model: Configuration and Compilation

We introduce the GPU programming model, particularly how to configure a kernel function and how it is compiled in this subsection.

# 2.3.1 Kernel Configuration

CUDA extends C/C++ by allowing programmers to define *kernel functions*. As already discussed, the kernel is the function that runs on the GPU side by massive parallel GPU threads. The way to specify the number of threads to execute the kernel is via the <<<...>>> configuration syntax. As shown in Listing 2.2 which is a simple element-to-element multiplication for 2D matrices, <<<*Grid\_config*, *CTA\_config* >>> implies that a kernel has a grid configuration defined by *Grid\_config* and a CTA

Maxwell

Pascal

5.3

6.0

16

32

```

//2D vector multiplication

for (i=0; i<n; i++)

for (j=0; j<n; j++)

C[i][j]+= A[i][j]*B[i][j];

Listing 2.1: CPU Loop Nest

-_global__ void VM2D(A,B,C){

int x=blockldx.x*blockDim.x+threadIdx.x;

int y=blockldx.y*blockDim.y+threadIdx.y;

C[x][y]+=A[x][y]*B[x][y];

VM2D <<<Grid_config, CTA_config>>>(A,B,C);

```

Listing 2.2: GPU Kernel and CTA

| Arch.   | CC. | Grids/GPU | CTAs/Grid                  | Thds/CTA | CTAs/SM | Thds/SM | Thds/Warp | Warps/CTA | Warps/SM |

|---------|-----|-----------|----------------------------|----------|---------|---------|-----------|-----------|----------|

| Tesla   | 1.0 | 1         | (512,512,64)               | 512      | 8       | 768     | 32        | 16        | 24       |

| Tesla   | 1.1 | 1         | (512,512,64)               | 512      | 8       | 768     | 32        | 16        | 24       |

| Tesla   | 1.2 | 1         | (512,512,64)               | 512      | 8       | 1,024   | 32        | 16        | 32       |

| Tesla   | 1.3 | 1         | (512,512,64)               | 512      | 8       | 1,024   | 32        | 16        | 32       |

| Fermi   | 2.0 | 16        | $(2^{16}, 2^{16}, 2^{16})$ | 1,024    | 8       | 1,536   | 32        | 32        | 48       |

| Fermi   | 2.1 | 16        | $(2^{16}, 2^{16}, 2^{16})$ | 1,024    | 8       | 1,536   | 32        | 32        | 48       |

| Kepler  | 3.0 | 16        | $(2^{31}-1,2^{16},2^{16})$ | 1,024    | 16      | 2,048   | 32        | 32        | 64       |

| Kepler  | 3.2 | 4         | $(2^{31}-1,2^{16},2^{16})$ | 1,024    | 16      | 2,048   | 32        | 32        | 64       |

| Kepler  | 3.5 | 32        | $(2^{31}-1,2^{16},2^{16})$ | 1,024    | 16      | 2,048   | 32        | 32        | 64       |

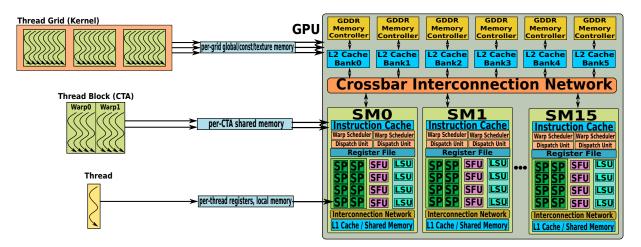

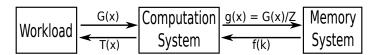

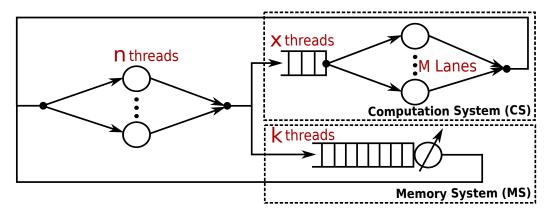

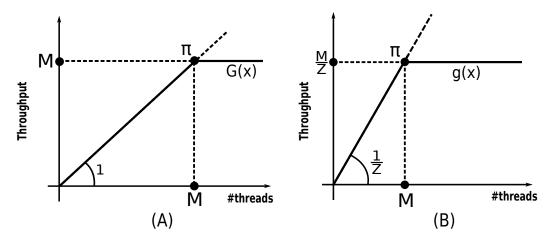

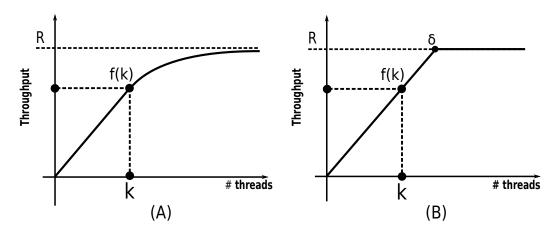

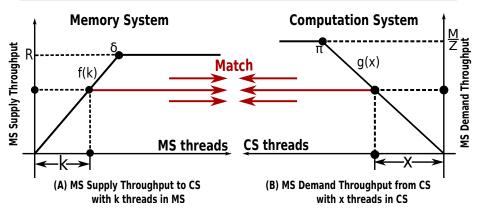

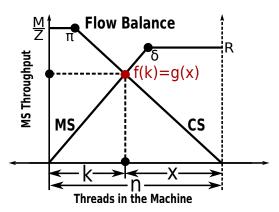

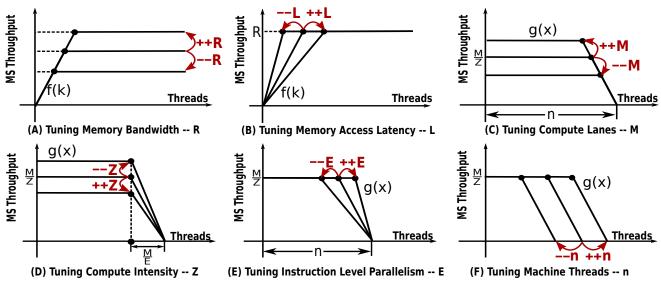

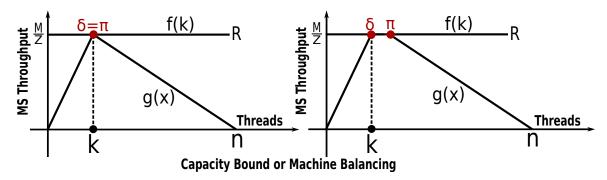

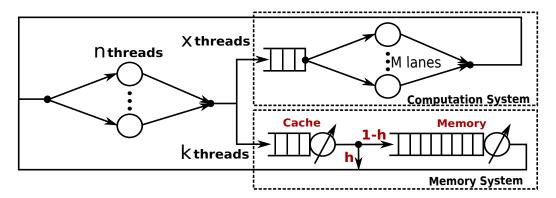

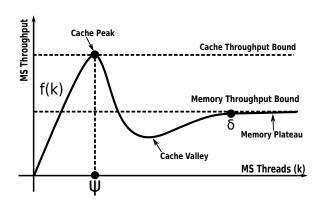

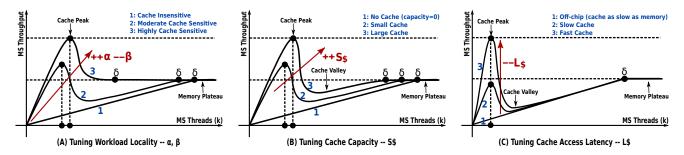

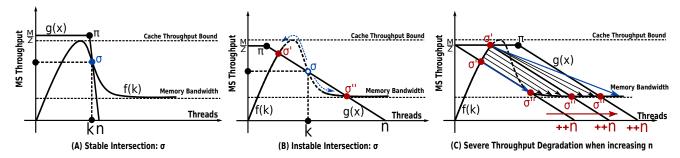

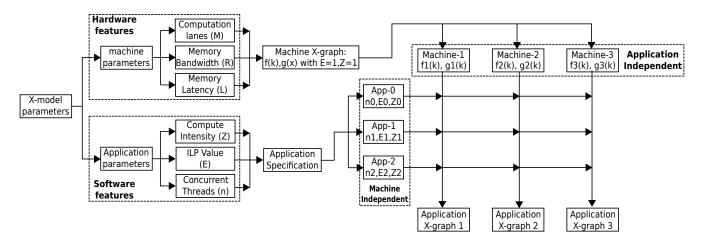

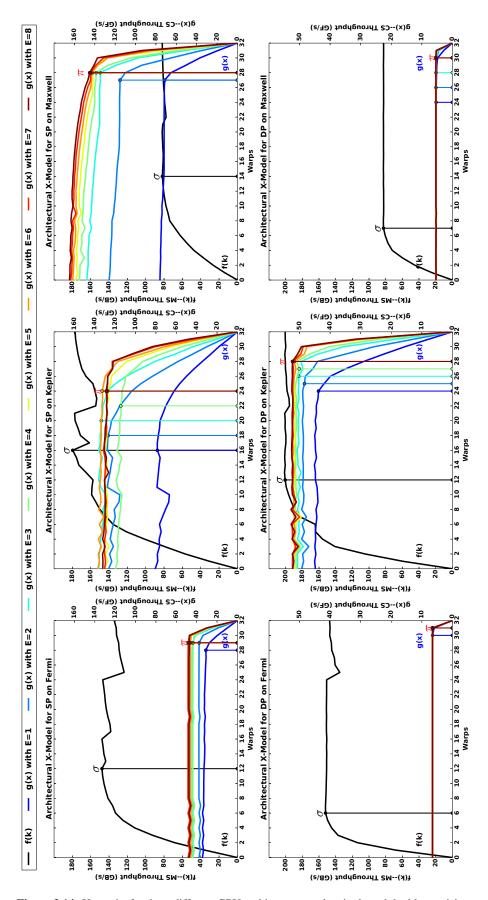

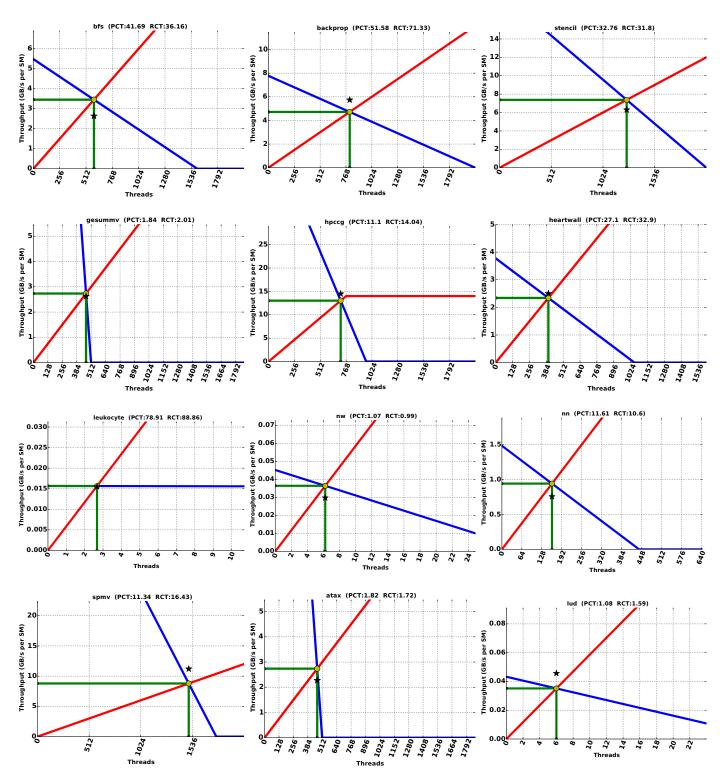

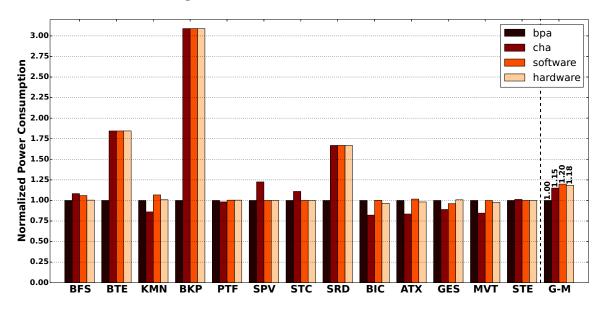

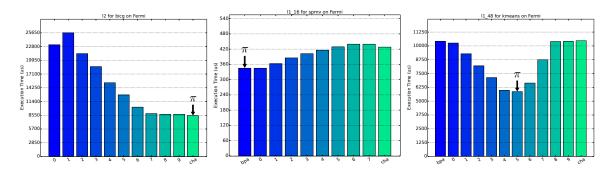

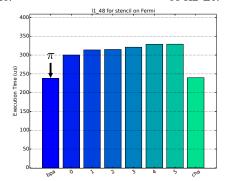

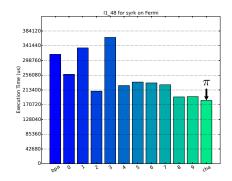

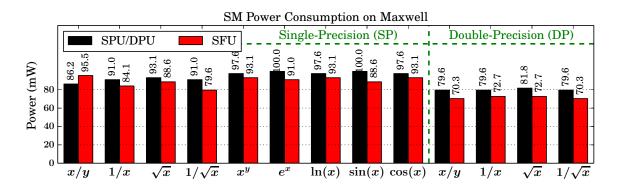

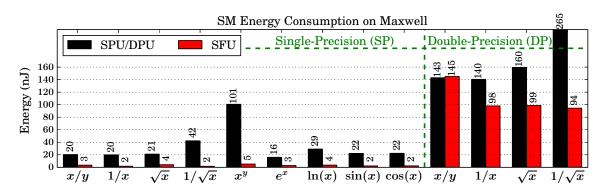

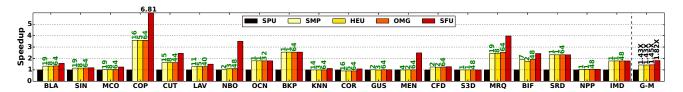

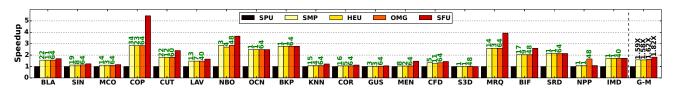

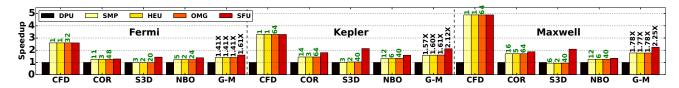

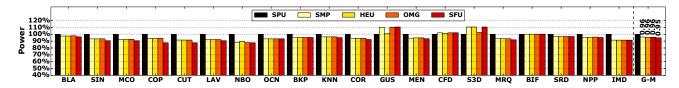

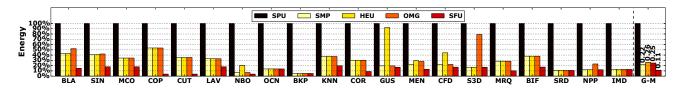

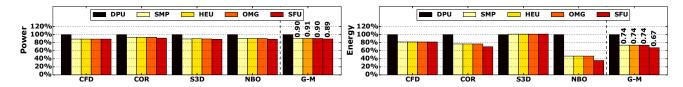

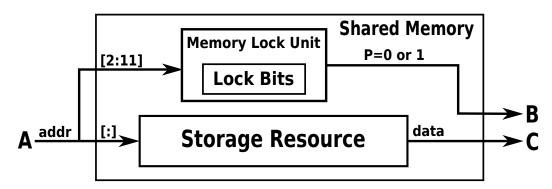

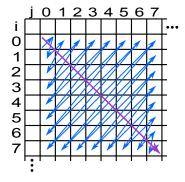

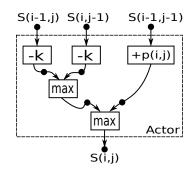

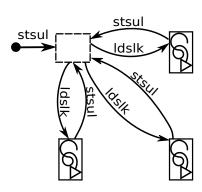

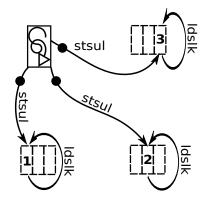

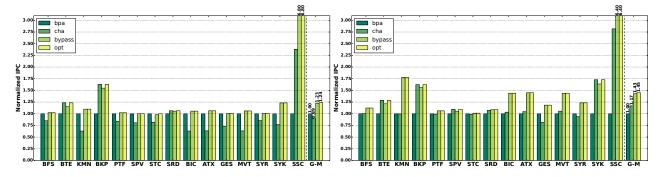

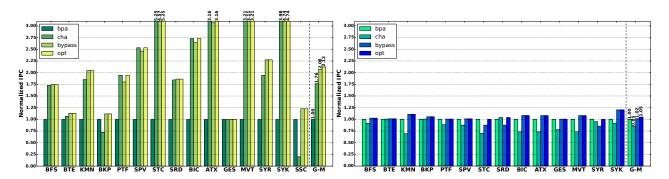

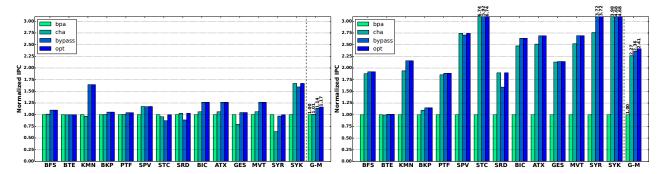

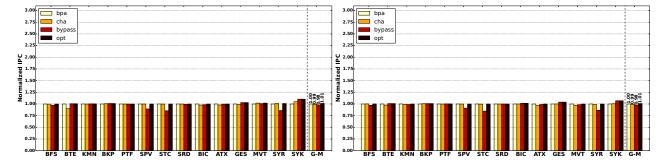

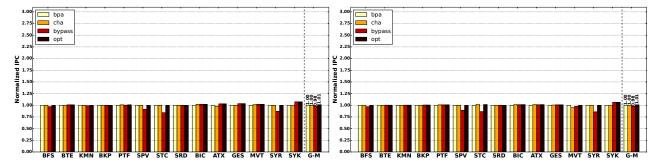

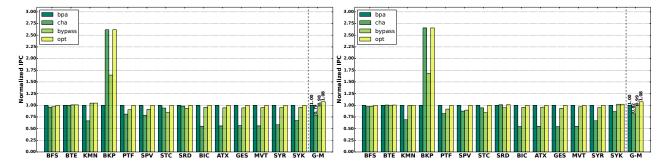

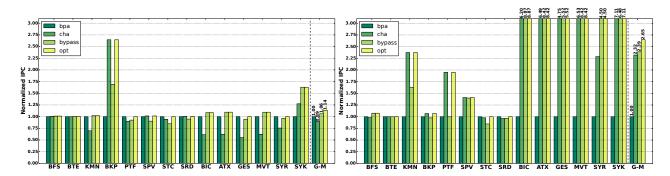

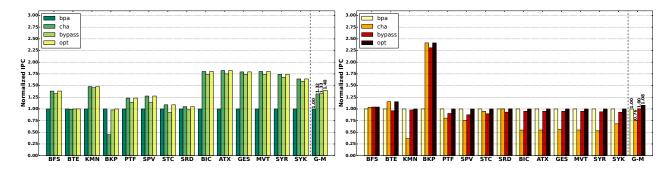

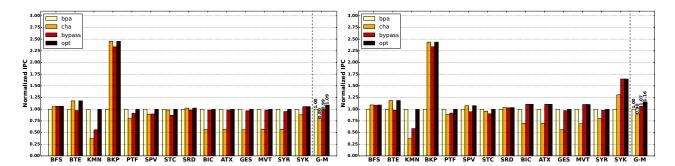

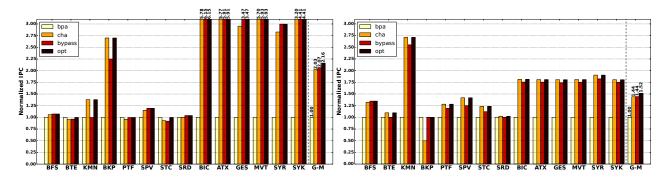

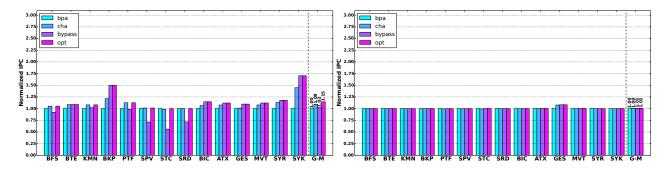

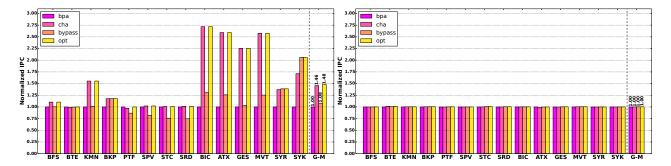

| Kepler  | 3.7 | 32        | $(2^{31}-1,2^{16},2^{16})$ | 1,024    | 16      | 2,048   | 32        | 32        | 64       |