Todri-Sanial, A. et al. (2017) A survey of carbon nanotube interconnects for energy efficient integrated circuits. IEEE Circuits and Systems Magazine, 17(2), pp. 47-62.

There may be differences between this version and the published version. You are advised to consult the publisher's version if you wish to cite from it.

http://eprints.gla.ac.uk/141434/

Deposited on: 31 May 2017

Enlighten – Research publications by members of the University of Glasgow http://eprints.gla.ac.uk

# A Survey of Carbon Nanotube Interconnects for Energy Efficient Integrated Circuits

Aida Todri-Sanial, Raphael Ramos, Hanako Okuno, Jean Dijon, Abitha Dhavamani, Marcus Wislicenus, Katharina Lilienthal, Benjamin Uhlig, Toufik Sadi, Vihar Georgiev, Asen Asenov, Salvatore Amoroso, Andrew Pender, Andrew Brown, Campbell Millar, Fabian Motzfeld, Bernd Gotsmann, Jie Liang, Gonçalo Gonçalves, Nalin Rupesinghe, Ken Teo

Abstract—This article is a review of the state-of-art carbon nanotube interconnects for Silicon application with respect to the recent literature. Amongst all the research on carbon nanotube interconnects, those discussed here cover 1) challenges with current copper interconnects, 2) process & growth of carbon nanotube interconnects compatible with back-end-of-line integration, and 3) modeling and simulation for circuit-level benchmarking and performance prediction. The focus is on the evolution of carbon nanotube interconnects from the process, theoretical modeling, and experimental characterization to onchip interconnect applications. We provide an overview of the current advancements on carbon nanotube interconnects and also regarding the prospects for designing energy efficient integrated circuits. Each selected category is presented in an accessible manner aiming to serve as a survey and informative cornerstone on carbon nanotube interconnects relevant to students and scientists belonging to a range of fields from physics, processing to circuit design.

Index Terms—carbon nanotubes, interconnects, energy efficiency.

# I. INTRODUCTION

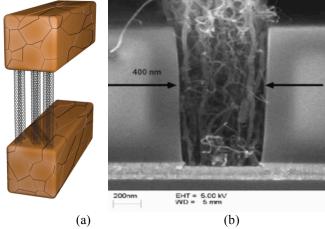

It was in early 2000 that the team lead by F. Kreupl filed the very first patent on the use of carbon nanotubes (CNTs) as vertical interconnects for nanoelectronic components on semiconductor chips [1] (see Fig. 1). The team emphasized that CNTs would be particularly beneficial for interconnect application due to quasi-ballistic current transport in CNTs that would allow very low resistance interconnects. They also explored how CNTs could be processed to be compatible with the on-chip interconnect fabrication. Since then, CNTs for

Manuscript submitted on Day, Month, Year. Revised on Day, Month, Year. A. Todri-Sanial and J. Liang are with Microelectronics Department at CNRS-LIRMM, Montpellier, France.

R. Ramos, H. Okuno, and J. Dijon are with the University of Grenoble, Alpes and the Nanomaterials Department at the CEA-LITEN, Grenoble, France.

A. Dhavamani, M. Wislicenus, K. Lilienthal and B. Uhlig are with the Center Nanoelectronic Technologies Department at the Fraunhofer IPMS, Dresden, Germany.

T. Sadi, V. Georgiev, and A. Asenov are with the Electrical Engineering Department at the University of Glasgow, UK.

S. M. Amoroso, A. Pender, A. Brown and C. Millar are with the R&D Department of Synopsys, Inc. UK.

F. Motzfeld and B. Gotsmann are with the Science & Technology Department at the IBM Research Zurich, Switzerland.

G. Gonçalves, N. Rupesinghe, and K.Teo are with the Nanoinstruments Department at the Aixtron Ltd., UK.

Corresponding author email: aida.todri@lirmm.fr

Figure 1. a) Illustration of carbon nanotube as the vertical connection between two copper wires, and b) SEM image of a cross-section of a carbon nanotube via [Kreupl, IEDM2004].

interconnect application have attracted a lot of research interest.

Before we delve deeper into CNTs properties and advancements, it is important to understand the flaws of current interconnect technologies and the imminent interconnect problems that the industry is currently facing.

Continued aggressive scaling into the deep nanometer regime has been an essential strategy to improve transistor performance—however, the reverse is happening Such scaling interconnects. continually semiconductor industry to search for new material combinations and innovative technological solutions to meet the demands set for future generations. The fabrication of interconnects is no exception to this trend. It was this driving force that forced the transition from Aluminium (Al) interconnects to dual Damascene Copper (Cu) interconnects a few decades ago, that proved to be a groundbreaking accomplishment in the field deep nanometer scale VLSI (Very Large Scale Integration) technology. Copper interconnects were introduced in 1998 and since 2001, the International Technology Roadmap for Semiconductors (ITRS [2]) highlighted problems with the resistivity increase as line widths approached electron mean free path. For example, Cu interconnects with dimensions in the order of the mean free

path of electrons (~40 nm in Cu at room temperature) undergo resistance increase rapidly. This is due to the combined effects of enhanced grain boundary scattering, surface scattering and the presence of a highly resistive diffusion barrier layer surrounding the copper line [3,4]. Moreover, at nano-scale dimensions, the increase of Cu interconnect resistivity, in addition to the increasing current density (J), results in higher self-heating of interconnects.

By 2003, low-K insulator dielectrics were introduced to slow this pace. However, Cu resistivity continued to rise due to electron scattering. Additionally, yield issues associated with the integration of low-K materials with copper proved to be more challenging than expected. Also, low-K dielectrics with inherently lower thermal conductivity (i.e. K<sub>th, ILD</sub><0.4 W/mK) hinder heat conduction from interconnect layers to the heat sink. Vias and interconnects have a thermal conductivity in the range of  $K_{th}$  Cu=385 W/mK. Nevertheless, thermal conductivity worsens when the back-end metal temperature (T<sub>m</sub>) rises above the junction temperature [3]. Elevated temperatures along with scaling introduce reliability concerns on Cu lines with low-K dielectric also known as time dependent dielectric breakdown (TDDB). All these factors adversely affect electromigration (EM) lifetime of Cu interconnects which depends quadratically on J and exponentially on T<sub>m</sub> [3]. ITRS [2] reports that current density limits for copper will be exceeded by 2017.

While some solutions have been found for the logic and memory applications up to 14nm node, there is an on-going race on contenders for replacing copper interconnects. Thinner barrier and adhesion layers, doping of metals to enhance the grain boundary conductance, and selective capping are some of the adopted solutions improving copper interconnects. Other short-term solutions to address the scaling challenges faced by Cu include load-aware redundant double vias to avoid EM issues [6], via prefill with alternate materials (like Cobalt) with higher current migration resistance and better fill [7], ultra-thin self-forming barriers (metal oxide barriers like MnO<sub>x</sub>) to optimize the utilizable cross-section for Cu, alternative materials for better EM [8], reflow seed layers for defect reduction [9], etc. Nevertheless, these short-term steps aim to solve one or few of the Cu-foreseen issues at once and to combine them might prove to be impractical or just economically unfeasible. As we go beyond 10nm and 7nm nodes, novel interconnect materials and integration approaches are needed and are under investigation.

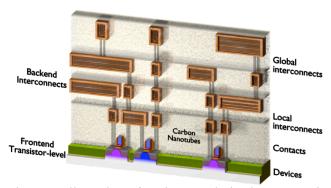

In digital logic design, local interconnects (interconnects closer to the device level, see Fig. 2) and intermediate interconnects tend to shrink with scaling. Thus, the impact of their delay is minor. Global interconnects (usually used for power/ground and clock) have the greatest wire lengths and widths, and are the most impacted by scaling. The problem is even more severe for memories. Metal bit lines (local metal layer) in memory cells have the most aggressive metal pitch, and their contact layer has the highest aspect ratio in all semiconductor devices. Therefore, they face the largest delay due to electron scattering. To date, potential solutions have been identified to solve these problems. Hence, the

Figure 2. Illustration of an integrated circuit cross-section depicting devices and interconnects made with carbon nanotubes.

interconnect problem is acute, and the limits of copper interconnects are approaching fast.

Comparable to the paradigm shifting transition from Al to Cu dual damascene process in the late 1990s, new potential pathways of advanced metallization in the back end of line, addressing the aforementioned issues, need to be explored for future technology nodes. This very necessity has yielded a great number of ambitious concepts involving graphene-based interconnects [10], optical interconnects [11], organic interconnects, spintronic switches [12], alternative metals as well as alloys and composites.

Carbon nanotubes (CNTs) have aroused a lot of interest in their applicability as VLSI interconnects of the future because of their extremely desirable properties of high mechanical and thermal stability, high thermal conductivity and large current carrying capacity [13,14,15,16]. Due to strong sp2 bonding between carbon atoms, CNTs are much less susceptible to EM problems than copper interconnects and can carry high current densities [13]. Ballistic electronic transport can go over long nanotube lengths, 1 µm, enabling CNTs to carry very high currents with virtually no heating due to nearly 1D electronic structure. Metallic single-walled CNT bundles have been shown to be able to carry extremely high current densities of the order of 10<sup>9</sup> A/cm<sup>2</sup> [17]. In contrast, EM limits the current carrying capacity of Cu interconnects to ~10<sup>6</sup> A/cm<sup>2</sup> [18]. Copper interconnect with cross-section 100 nm x 50 nm can carry currents up to 50 µA, whereas a 1 nm diameter CNT can carry up to 20-25 µA current [19]. Hence, from a reliability perspective, a few CNTs are enough to match the current carrying capacity of a typical Cu interconnect. Although it should be noted, that the need to reduce interconnect resistance (and hence delay) makes it necessary to have CNTs with a minimum density of 0.096 per nm<sup>2</sup> [2], if pure CNT interconnects are used. Additionally, estimations based on measured thermal conductivity (K<sub>th</sub>) on films of SWCNT bundles, combined with observations from electrical conductivity experiments, predict K<sub>th</sub> in the range 3000-10000 W/mK [20] at room temperature, while  $K_{th, Cu}=385$  W/mK. Hence, heat diffuses more efficiently through CNT vias than Cu vias and can reduce the on-chip temperature. Such properties also make CNTs desirable as vertical throughsilicon via for three-dimensional (3D) integration. There is also progress on the commercial wafer-level scaling of CNTs.

Current state-of-the-art on CNT deposition is developed using equipment such as AIXTRON BM300T [116]. CNT growth occurs in a vertical flow reactor where gasses (ammonia, argon, acetylene, hydrogen, methane) can be injected to control the CNT growth and alignment. The growth chambers can be assembled into a cluster for high-volume production capacities.

In this paper, we overview the recent advancements of carbon nanotubes as interconnect material for nanoelectronics. The rest of the paper is organized as follows. CNT transport properties and modeling are described in Section II. Section III presents some of the research work related to CNT on-chip interconnects covering aspects on doping and composite CNTs for enhancing current density and lowering resistance. Section IV provides an overview on CNT-based through-silicon vias. Section V includes some of the on-going efforts on the chip design with CNT devices and interconnects for energy efficiency. Section VI provides an overview of the CNT characterization methods. Section VII describes the prospective research problems related to CNT interconnects and Section VIII concludes the paper.

#### II. TRANSPORT PROPERTIES OF CNTS

In this section, we provide a brief description of CNT modeling. CNT properties such as band structure, electronic transport, and tunneling currents are now well understood and predicted by atomistic-level modeling. The modeling of CNT structures consists of two closely interlinked models: physical 'microscopic' modeling and compact/analytical 'macroscopic' modeling for circuit-level simulations. The modeling cycle starts from the development of an efficient physical simulation framework, based on first-principle methods such as density functional theory (DFT) combined with transport simulation models such as non-equilibrium Green's functions (NEGF) or Monte Carlo methods. Robust physics-based models allow a comprehensive theoretical study of CNTs and facilitate the design of high-performance systems. Physical models need continuous calibration with measured data to increase model accuracy and the predictive capabilities of simulation tools. Compact models are the interface between physical simulations and measurements. Compact models are based on extensive physical simulations and suitable for circuit simulations using standard SPICE-like circuit simulators [22]. Below is a brief survey of available macroscopic and microscopic models.

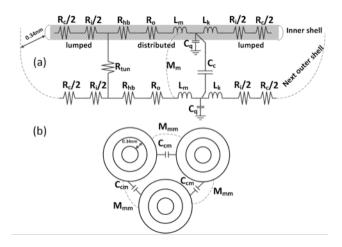

Macroscopic level modeling – compact models: From a circuit-simulation perspective, a generalized compact RLC model for CNT interconnects can be depicted as in Fig. 3 [23]. The model is also applicable to SWCNTs with a single shell. The model represents conductance, inductance, and capacitance. Each shell has a lumped ballistic resistance ( $R_i$ ) and lumped contact resistance ( $R_i$ ) due to imperfect metal nanotube contacts. These contacts are typically constructed of Gold, Palladium, or Rhodium [23]. The nanotubes also have a distributed ohmic resistance ( $R_o$ ), which is dependent on length,  $l_b$ , and mean free path of acoustic phonon scattering ( $\lambda_{ap}$ ). CNT resistance also depends on the applied bias voltage,  $R_{hb} = V_{bias}/I_o$ , where  $I_o$  is the maximum saturation current ( $I_o$  values 15 to 30 μA [24]). Between shells in MWCNTs, there

Figure 3. Illustration of compact RLC model for CNT interconnect.

is also an intershell tunneling resistance ( $R_{\scriptscriptstyle lum}$ ). As the applied bias voltage to each shell is the same, the impact of  $R_{\scriptscriptstyle lum}$  is relatively small. All the aforementioned ballistic, ohmic and contact resistance depend on the number of 1-D conducting channels,  $N_c$ . For metallic SWCNTs, the number of conducting channels is always  $N_c$ =2 due to lattice degeneracy [25]. Carbon nanotubes have quantum,  $C_q$  (i.e. 193 aF/ $\mu$ m per conducting channel) and electrostatic capacitance,  $C_c$ . Additionally, there is coupling capacitance between 1) conducting shells inside MWCNTs,  $C_c$  and 2) one nanotube to another depending on their distance,  $C_{cm}$ . As for inductance, CNTs have kinetic  $L_k$  (i.e. 8 nH/ $\mu$ m per conducting shell) and magnetic inductance,  $L_m$ . There is also mutual inductance between shells and among CNT bundles.

The macroscopic circuit simulation addresses just the interconnect performance neglecting other important aspects like reliability and variability of CNTs, which can be adequately treated only at the mesoscopic level by employing fully three-dimensional (3D) Technology Computer Aided Design (TCAD) modeling approaches. Recently, industrial and scientific communities are investing considerable efforts to investigate the modeling of CNT variability and reliability utilizing 3D TCAD approaches for advanced technologies.

Microscopic level modeling: Besides macroscopic (circuitlevel) and mesoscopic (TCAD level) modeling of CNT interconnects, it is also important to consider microscopic (Ab Initio level) modeling to understand the underlying physics. Significant work has been carried out on the electrical, [24-27] and thermal [28], [29] modeling of CNTs. Simulation tools on band structure and molecular level simulation tools can be found in [30]. For the modeling of the electronic and thermal properties of CNT structures, several methods have been successfully applied—models based DFT, the extended Hückel [31] or Slater-Koster [32] formalisms. Classical models have also been incorporated into commercial tools such as ATK-QuantumWise [33] allowing in-depth insight into the physical behavior of CNTs. Transport models such as NEGF and molecular dynamics are also widely available as part of commercial and open-source software packages such as LAMMPS [34] and GPAW [35].

|                                         | Cu                    | SWCNT                      | MWCNT                      | Cu-CNT                              |

|-----------------------------------------|-----------------------|----------------------------|----------------------------|-------------------------------------|

| Maximum current density (A/cm²)         | < 1 x 10 <sup>7</sup> | > 1 x 10 <sup>9</sup> [55] | > 1 x 10 <sup>9</sup> [56] | 6 x 10 <sup>8</sup> [53]            |

| Thermal conductivity @ 300 K<br>(W/mK)  | 385                   | 3000-10000<br>[52]         | 3000 [52]                  | ~800 [54]                           |

| Electron mean free path @ 300 K<br>(nm) | 40                    | > 1000 [58]                | > 25000 [57]               |                                     |

| Conductivity (S/cm)                     | 5.8 x 10 <sup>5</sup> | 7 x 10 <sup>5</sup> [59]   | 2.7 x 10 <sup>5</sup> [60] | 2.3 - 4.7 x 10 <sup>5</sup><br>[53] |

Table I: Comparison of properties of Cu, SWCNT, MWCNT and Cu-CNT composites.

#### III. CNTs for On-Chip Interconnects

CNTs can be either single-wall (SWCNT) or multi-wall (MWCNT). Research papers on CNT interconnect date as early as 2002 [36]. It has been reported that SWCNT bundles with same dimensions as Cu/low-K interconnects can provide significant improvements [37], [38]. An arrangement of several SWCNTs has shown to reduce the resistance by as much as 50% and to help reduce the delay and power consumption, which can be particularly interesting for local interconnects [39]. As for MWCNTs, it was proven both theoretically and experimentally that all inner shells can conduct if properly connected [40], [41], [42], [43] and can potentially outperform Cu and SWCNTs. MWCNTs interconnects operating in the gigahertz frequency range, have been demonstrated. However their conductivity considerably lower than the theoretical models predict, due to large defect density [44], [45]. More recently, researchers have designed and fabricated the first carbon nanotube computer [46], which operates on only 1-bit of information and uses a single instruction. Additionally, [47] and [48] have demonstrated 1GHz operation of carbon nanotube interconnects with silicon transistors. While these resemble a rudimentary computer design, they are significant advances to fabricate a circuit using only CNT field effect transistors and interconnects.

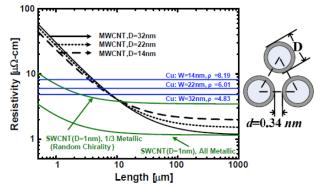

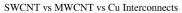

Thus, the enhanced properties of CNTs address most of the challenges faced by the current Cu-interconnect technology, especially the issues that rise due to its parasitic resistance and insufficient current carrying capacity. Table 1 shows the comparison between Cu, single-walled (SWCNT) and multiwalled CNTs (MWCNT). Specifically, Fig. 4 shows the theoretical resistivity comparison among Cu wire and MWCNTs for different lengths and diameters up to 32nm [49]. For a larger diameter of MWCNTs, resistivity values are shown in Fig. 5. They show that for long lengths (>10um), the theoretical resistivity of MWCNTs is several times lower that Cu wires and become comparable to that of SWCNTs. These characteristics highlight the potential of CNTs for interconnects that drive the enormous technological efforts realized in the past 15 years to integrate CNTs in back-end-of-

line semiconductor device fabrication.

From a processing point of view, the most widespread and most studied approach to integrating CNTs in interconnects is to directly grow CNTs in the desired structures by catalytic chemical vapor deposition (CCVD). Most efforts so far were devoted to the fabrication of vertical *via* interconnects, and a number of integration process flows were developed to selectively grow densely packed bundles of CNTs on the metallic bottom electrode and to contact the other end of the CNTs with a top metal [61]. Recently, an original integration approach relying on the report of CNT plugs in via holes was also introduced [62]. As for horizontal interconnects, fewer reports exist and mostly rely either on the direct horizontal growth of CNTs on dedicated vertical structures [63]; or on

Figure 4. Comparison of resistivity of MWCNT bundles with Cu wires. The dimension of Cu wires are adopted from ITRS [49].

Figure 5. Comparison of resistivity of MWCNTs with Cu wires using analytical models for Cu and CNT materials [50-51].

the vertical growth of CNTs followed by subsequent horizontal alignment [64, 65]. It should be noted that alternative processes based on the assembly of CNTs from solutions were also considered [66]. Despite the significant improvements realized regarding CNT integration, there are still several processes and reliability related challenges that need to be addressed before CNTs can enter as mainstream VLSI interconnects. Presently, the realization of good electrical contacts with metallic electrodes remains a challenge. This is particularly problematic for vertical interconnects where the bottom electrode acts both as a support for the catalytic growth of CNTs and as an electrical contact [67,119]. Another major roadblock comes from the fact than one ideally desires to inject current alongside the axis of the CNT to create a so-called end-bonded contact to the CNTs, which requires a perfect control over the quality of the interface between open-ended CNTs and metal [68].

In addition to contact issues, the electrical performances of CNTs integrated as interconnects are systematically lower than those of copper or the prediction of theoretical models, regardless of the process flow for vertical or horizontal alignment. Regarding resistivity, the lowest values reported fall in the range of 0.5 to 1 m $\Omega$ .cm, i.e. at least two orders of magnitude higher than the resistivity of aggressively scaled Cu interconnects [65, 67, 69-71]. These reduced performances can be explained by two main factors: (1) the quality of the CNTs produced by CCVD, which is a relatively lowtemperature process compared to arc-based processes; and (2) the non-ideal packing density of CNTs in integrated interconnects. The latter was much improved by increasing the CNT growth density in the 10<sup>13</sup> cm<sup>-2</sup> range [67, 119], but it is however inherently limited by the tortuosity of the CNTs produced by CCVD. Even after liquid-induced compaction of the CNT bundles, the packing density of CNTs in interconnect structures is still rather low. Due to current technological challenges, CNT interconnects are unlikely to replace all copper interconnects at once but rather gradually—introducing hybrid structures such as doped and metal composite CNTs.

## A. Doped CNTs

As already mentioned above, over the recent years there have been many advancements in process and growth of CNTs interconnects and more specifically for vertical lines. Currently, several growth techniques have been established to synthesize carbon nanotubes at workable temperature levels for microelectronics process (i.e. below 450°C) with the ability to control nanotube dimensions, density (i.e. up to 10<sup>13</sup> CNTs cm<sup>-2</sup>) and patterning at specific locations [72], [73], [74], [75], [67], [119]. However, the design of catalyst to control nanotube chirality and especially for metallic nanotubes is very challenging [75], [76]. It is one of the main challenges for CNT interconnects to design catalyst and process conditions that simultaneously give ultra-high area densities, chiral selectivity, and growth on conductive support layers [77].

However, doping carbon nanotubes is an alternative to reducing resistivity without the need for chirality control since all doped tubes behave as metals irrespective of their semiconducting or metallic character in the neutral state [118]. Indeed, whichever approach is used to dope the CNTs, i.e. substitutional doping, internal (endohedral) doping, or external doping, the transport properties are affected by shifting the Fermi level and thus changing the number of conduction channels per CNT. Two- to four-fold improvement in the conductivity of horizontal CNT interconnects was already demonstrated using external doping by platinum salts [66] or iodine vapor [78, 79]. The temporal and thermal stability of such charge transfer based doping process, however, needs to be carefully studied. In this respect, substitutional or internal doping may be more robust.

Recently, an interesting alternative relying on the coating of CNTs by a thin film of evaporated MoO<sub>3</sub> was reported [77]. Significant decreases in resistivity were obtained up to 50  $\mu\Omega$ cm, which is the lowest resistivity value measured to date on nanotube bundles while maintaining a highly ordered alignment [77]. The improved electrical resistivity was attributed both to the shift of the Fermi energy of semiconducting nanotubes (i.e. doping by charge transfer) and to the conversion of the MoO<sub>3</sub> oxide into a layer of metallic character [77].

Doped CNTs might be potential candidates for replacing on-chip local interconnects due to lower resistivity for short interconnect lengths typically used for local interconnects. For small dimension interconnects (< 10 nm diameter), which would be made of only a few carbon shells in parallel and would thus exhibit large performance variability due to the random distribution of semiconducting and metallic shells, one can also expect doping to reduce this variability by causing all shells to conduct.

## B. Composite CNTs

Cu-CNT composite interconnects can be potential replacements of global copper interconnects. Global interconnects for supply voltage delivery are susceptible to electromigration issues due to a large amount of unidirectional current flowing for an extended period of times, which ultimately cause atoms to migrate by creating voids and hillocks. To circumvent this issue, combinations of CNTs with copper were envisioned soon after the pioneering studies about CNT interconnects [80]. In [81,82,83], initial experiments were conducted on "bulk" approach where a mixture of CNTs and Cu is deposited from a solution to target substrate. This approach demonstrated a mitigated performance for interconnects such that the focus now is exclusively on composite materials where CNT alignment is controlled by current flow (referred to as aligned CNT-Cu composite).

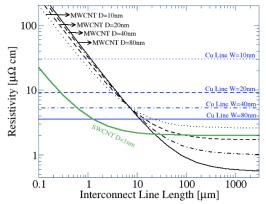

Chai et al. [85-87] first demonstrated the fabrication of vertical interconnects using aligned CNT-Cu composite materials in 2007 where vertically aligned CNTs were grown before electroplating was used to fill the voids between CNTs with Cu. They demonstrated that the composite material could reach low, Cu-like, resistivity, however, more resistant to electromigration than copper. More recently, a renewed interest for composite CNTs was generated by [84] claiming a

100 fold increase in current carrying capacity of aligned CNT-Cu material compared to pure Cu while maintaining Cu-like conductivity (see Fig. 6). The integration of aligned CNT-Cu composite materials in interconnect structures is now actively studied [88-92] and can lead to significant performance gain and reliability enhancement of integrated circuits.

The benefits such as robustness, fabrication and economic feasibility of introducing aligned CNT-Cu composites in the semiconductor interconnects technology are immense. This might prove to be one of the most promising short-term solutions to pave the way for a paradigm shift of on-chip interconnects.

Figure 6. Properties of Cu-CNT composite. a) improvement of current density vs. conductivity. b) Cu-CNT resistivity comparison with copper [84].

## IV. CNTs Through-Silicon Vias

An important application of CNTs is also their use as vertical via interconnect. As future high-performance systems will demand large memory bandwidth, the state of the art of off-chip interconnects (i.e. 25pJ/bit) needs to be further improved to allow for low power, fast and high bandwidth interconnects. Three-Dimensional (3D) integration is one of the most promising technologies for System-on-Chip (SoC) developments and a viable solution for heterogeneous integration (i.e. processors, memory, digital, analog, mems, sensors, harvesters, etc.). Through-Silicon-Vias (TSVs) are the key enablers of 3D integration by providing continuous connections between different stacked dies. TSVs are etched in the silicon substrate and filled either with copper or Tungsten (W). However, these materials have limitations due to the highly demanding fabrication process, reliability, manufacturability, and performance. In the recent years, a lot of research efforts have been dedicated to the development of carbon nanotube-based TSVs for 3D integration. CNT TSVs present an opportunity to further progress packaging technology and enable high-density interconnects.

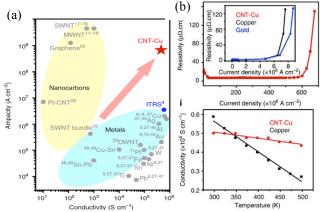

CNT TSVs are extensively investigated, and several research groups have successfully implemented growth and realized functional integration of multi-wall CNT bundles as high aspect ratio TSVs. In [93], CNT TSV bundles were

grown in sub-5µm diameter on top of metal lines in a bottom-up approach, which is compatible with CMOS process temperatures (see Fig. 7). In [95], integration scheme for CNT-based TSVs are demonstrated for two scenarios 1) connecting two TSVs and 2) connecting a TSV to a metal pad. Authors reported on integration scheme for vias 100 µm in diameter and 132 µm deep and resistance values of 46  $\Omega$  and 9.8  $\Omega$  were obtained for via and contact, respectively. In [94], CNT TSV bundles with 50 µm length and aspect ratio 5 or 10 were demonstrated. CNT bundle resistance of 69.7  $\Omega$  was reported. Further improvement on integration scheme and

Figure 7. Scanning electron microscopy images of through-silicon vias filled with carbon nanotubes for 3D stacking of logic with memory [95].

lowering contact resistance of vias are required for enabling seamless integration of CNT TSVs as off-chip interconnects.

## V. CNT-AWARE VLSI DESIGN METHODS

To overcome the challenges of processing highly aligned CNTs (i.e. either for devices or interconnect), there is a lot of on-going research on circuit design methods that take into account misalignment and mispositioned CNTs to design functionally correct and reliable circuits. Thus, circuit designers are looking into efficient methods to design reliable, energy efficient and high-performance circuits despite the fact that CNTs might have defects. One effective method that has been applied by [96] is that after transferring CNT-based field effect transistors (CNTFETs) or CNT interconnects, regions of misalignments are identified and are etched away by using lithography. These techniques are known as CNT removal after CNT growth by electrical burning [97] or selective etching [98].

A strong motivation for this work is that disregarding defective chips (i.e. misaligned, mispositioned CNTs) or reconfiguring around defective devices and interconnects may be very expensive and simply not feasible due to complexity in processing methods. Moreover, traditional fault-tolerance techniques (i.e. redundancy) might not be applicable due to a large area and power overhead. Hence, many research efforts are focused on defective CNT-immune design techniques while having a minimal impact on existing design flows.

Additionally, considerable progress has been made towards full wafer-level CNT-based digital systems. Recently, researchers [46] have demonstrated the first processor design with CNT field effect transistors and developed VLSI-compatible design techniques to overcome the challenges of CNT imperfections [99].

To explore energy efficiency of carbon nanotube-based circuits and recent advancements on nano-engineering, researchers have presented a design approach that capitalizes on several recent nanotechnology breakthroughs called N3XT [99]. The main thrust of N3XT is to include high performance and energy efficient devices based on CNTs, combined with large amount of nonvolatile memory (such as low-voltage resistive RAM and magnetoresistive memories as spin-transfer STT-MRAM) magnetic RAM, and microarchitectures for scalable computing that are all implemented in fine-grained (monolithic) 3D integration with ultra dense CNT interconnects between logic and memory layers. Exploiting the progress on each technology enables new system integration that promises high energy-efficiency and high-performance.

#### VI. CNT CHARACTERIZATION

Suitable characterization techniques are essential for the successful integration of CNT interconnects and evaluation of development prototypes.

For a CNT-based interconnect technology, electrical measurements are necessary for verifying the expected high conductivities and are required for optimization of doping and contact technology. The main challenge of electrical characterization is the formation of suitable contacts. The first successful attempts at defining metal contacts on single CNTs have already been reported in the late 1990s, along with the first experimental studies of their electrical properties [100-102]. Today, even though the contacting of single CNTs was demonstrated and nanoscale devices based on CNTs can be built and characterized [103] – the realization of transparent ohmic electrical contacts is still challenging [68].

CNT interconnect technology promises improved thermal properties with reduced self-heating and improved thermal coupling to the heat sink. To maximize the potential benefits, thermal characterization techniques are crucial. One approach to studying the thermal properties of single, metallic CNTs is deriving them from their current-voltage (I-V) characteristics under bias conditions where Joule heating leads to non-ohmic behavior [104]. This approach can yield the global thermal conductivity of a single CNT line, but a valid electro-thermal model is needed to extract the data. Moreover, the approach cannot resolve non-homogeneous thermal conductivity distributions or the formation of hot spots.

Optical approaches are fast and contact-less, but diffraction limits their spatial resolution. The temperature-induced shift of the **G** bands in CNTs can be measured using Raman spectroscopy [105-107]. This way, the local temperature and thermal conductivity along the axis of self-heated CNT lines can be obtained with sub-micron lateral resolution. A second laser source can be used for rapid local heating of the CNT [108]. Infrared thermometry was also successfully applied to

image local heat dissipation in carbon nanotube network (CNN) transistors. The technology might be applicable for interconnect structures made from bundled CNTs.

Scanning probe-based thermometry techniques are not diffraction-limited and therefore achieve the highest reported spatial resolutions. Scanning Joule Expansion Microscopy (SJEM) has been applied to study the thermal properties of an array of parallel, single CNT lines embedded in PMMA [109]. By measuring the thermal expansion of the CNTs and the surrounding PMMA - metallic and semiconducting CNTs could be distinguished, the local temperature could be obtained with a lateral resolution of 100 nm and local hot-spot formation could be observed. Moreover, the point where the thermal breakdown would occur can be accurately predicted. To reach even higher performances, specialized tips can be used in so-called scanning thermal microscopy (SThM).

One such approach, in which the passive atomic force microscope (AFM) tip is replaced with a nanoscale thermocouple [110], has been applied to single CNTs [109]. Self-heating of a single CNT could be resolved with a lateral resolution of 50 nm. A novel SThM approach, relying on a cantilevered tip with integrated heater, recently demonstrated a lateral resolution of 10 nm [111]. This approach has also been used to study the thermal transport into graphene [112] and is a promising candidate for high-resolution thermometry of single CNTs. Thermal and electrical properties of CNTs strongly depend on their morphology and structure. The properties of SWCNTs are to a large extent determined by their chirality. Defects in the honeycomb lattice can affect the properties of both SWCNTs and MWCNTs. Impurities in the lattice—such as doping atoms—can have a strong impact as well. It is thus important to characterize morphology and structure of CNT interconnects alongside their thermal and electrical properties.

For morphological and structural characterization of CNTs on an individual level, only a few technologies are suitable. Among them are scanning tunneling microscopy (STM) and transmission electron microscopy (TEM) [113]. While STM can also yield information on the electronic density of states, a conductive substrate is necessary, which makes the approach rather suited for primary CNT research. TEM, on the other hand, can be applied to suspended CNTs, to allow in-situ investigations with atomic resolution imaging. Today, using low-voltage aberration corrected TEM technologies, dopant atoms and nanostructures that have been filled inside CNTs can be visualized [114] while imaging morphology and potential defects at the atomic scale simultaneously. It is possible to identify in a precise manner the location and type of defects and contaminations on a CNTs surface. Damage introduced by electron irradiation may nowadays be kept at a minimum. Moreover, the position and atomic structure of dopant atoms can be characterized [115] The information gained from in-situ TEM measurements can be expected to enable a more direct comparison of theory and experimental data and might provide insights into the mechanisms that shape the electrical and thermal properties of CNT interconnects.

#### VII. RESEARCH PROSPECTS

Carbon nanotubes present viable solutions to overcome the current challenges with copper interconnect technology. The challenge of introducing CNTs in integrated circuits is not just in the processing technology. The scientific community still lacks the know-how to exploit CNTs both as devices and interconnects. Understandings such as to what extent CNTs can be exploited for reliable and efficient interconnect architectures; are certain device technologies more suitable to be integrated with CNTs and give best performance; and how to design optimal circuits despite of having non-perfect CNTs are significant challenges to be addressed if we are to truly find a replacement material for copper.

Research efforts related to physical modeling, physical design, design space exploration, CNT processing and characterization are gaining momentum and will provide a clearer picture of the costs and benefits of integrating CNTs as on-chip interconnects [117]. With respect to modeling, electro-thermal modeling and simulation tools are needed to evaluate the performance, reliability and variability of CNTs and composite Cu-CNT interconnects. It can also help to assess the impact of CNT-metal contacts. In this context, a multi-scale physics-based simulation platform (from ab-initio material simulation to circuit-level) that considers all aspects of VLSI interconnects (i.e. performance, power, and reliability) is desirable to explore and evaluate the potential of CNT technology. Regarding circuit design, novel VLSI design methods are needed to take into account the peculiarities of CNT process and its variability issues. Such design methods will enable design space exploration of carbon nanotube circuits. On the processing side, continued efforts are needed on the CCVD growth of CNTs both to produce high-quality CNTs at a reasonable temperature, but also to reduce the CNT tortuosity and increase their packing density in interconnects. There is also a large effort, which is necessary, to integrate CNTs into the back-end-of-line fabrication process. Challenges arise from high planarity CMP processes, temperature budget (i.e. 350°C) and contamination management. Stable doping of CNTs at the operating temperature of circuits still needs to be developed and integrated into back-end-of-line processing. The fabrication of aligned CNT-Cu composite material requires specific developments, and the corresponding electrical conduction mechanism needs to be carefully studied. On characterization, there is a need for structural and morphological CNT-level electrical and thermal characterization. In summary, there are a lot of research efforts required into enabling CNTs to be embedded on-chip and become widely deployed in the semiconductor industry.

## VIII. CONCLUSIONS

In this paper, we provide an overview of the advancements of carbon nanotube based interconnects. There is a lot of ongoing research focused on the processing and growth of carbon nanotube interconnects for achieving high density, directional growth, and well-aligned carbon nanotubes. To allow integration of CNT interconnects as on-chip interconnects, there are two short-term solutions being explored by the community. Doped CNTs present interesting

properties to be used as local interconnects by reducing their resistance. Metal-CNT composite materials are also being investigated as a potential replacement for global copper interconnects to allow high current densities. To further increase package density and bandwidth, carbon nanotube based through-silicon-vias allow faster, denser and reliable off-chip interconnects and can thus be expected to lead to advancements in other fields of nanoelectronics, such as CNT-based-devices, non-volatile memories, and 3D integration. CNTs present new opportunities for designing energy efficient, high-bandwidth and high-performance circuits and systems.

#### ACKNOWLEDGMENT

This work is supported by EU H2020 CONNECT project under grant agreement No. 688612, <a href="http://www.connect-h2020.eu/">http://www.connect-h2020.eu/</a>.

### REFERENCES

- [1] M. Engelhard, W. Hönlein and F. Kreupl, Electronic component comprising an electrically conductive connection consisting of carbon nanotubes and a method for producing the same, US Patent 7,321,097 B2, 16 Feb 2000.

- [2] ITRS 2.0. http://www.itrs2.net.

- [3] S. Im, et al., "Scaling Analysis of Multilevel Interconnect Temperatures for High-Performance ICs," IEEE TED, Vol. 52, No. 12, pp. 2710-2719, 2005.

- [4] W. Steinhogl, et al., "Comprehensive Study of the Resistivity of Copper Wires With Lateral Dimensions of 100 nm and Smaller," J. of Applied Physics, Vol. 97, No. 2, 023706-1-023706-7, 2005.

- [5] N. Srivastava, et al., "A Comparative Scaling Analysis of Metallic and Carbon Nanotube Interconnections for Nanometer Scale VLSI Technologies," Proc. VMIC, pp. 393-398, Sept. 2004.

- [6] Biagalke, et al., "Load-aware redundant via insertion for electromigration avoidance," In Proc. of the 2016 ACM International Symposium on Physical Design (ISPD), pages 99—106, DOI: 10.1145/2872334.2872355, 2016

- [7] Veen, et al., "Cobalt Bottom-Up Contact and Via Prefill enabling Advanced Logic and DRAM Technologies," IEEE International, DOI: 10.1109/IITC-MAM.2015.7325605, 2015

- [8] Majumder M. K., et al., "Analysis of MWNT and bundled SWNT interconnects: impact on crosstalk and area," IEEE Electron Device Lett 33(8):1180–1182, 2012

- [9] Motoyama, et al., "PVD Cu Reflow Seed Process Optimization for Defect Reduction in Nanoscale Cu/Low-k Dual Damascene Interconnects," DOI: 10.1149/2.035312jes, J. Electrochem. Soc., Volume 160, Issue 12, D3211-D3215, 2013

- [10] Adelman, et al., "Alternative Metals for Advanced Interconnects," IEEE International, DOI: 10.1109/IITC.2014.6831863, 2014

- [11] B. K. Kaushik et. al., "Future VLSI interconnects: optical fiber or carbon nanotube a review," Microelectron. Int., 24(2):53–63, 2007

- [12] Sharad, et al., "Spintronic Switches for Ultra Low Energy On-Chip and Inter-Chip Current-Mode Interconnects," IEEE Electron Device Letters, Vol. 34, No. 8, 2013

- [13] B. Q. Wei, et al., "Reliability and Current Carrying Capacity of Carbon Nanotubes," Appl. Phys. Lett., Vol. 79, No. 8, pp. 1172-1174, 2001.

- [14] P. G. Collins, et al., "Current Saturation and Electrical Breakdown in Multiwalled Carbon Nanotubes," PRL, Vol. 86, No. 14, pp. 3128-3131, 2001.

- [15] S. Berber, et al., "Unusually High Thermal Conductivity of Carbon Nanotubes," PRL, Vol. 84, No. 20, pp. 4613-4616, 2000.

- [16] K. M. Liew, et al., "Thermal Stability of Single and Multi-walled Carbon Nanotubes," Physical Review B, Vol. 71, 075424, 2005.

- [17] M. Radosavljevic, et al., "High-field Electrical Transport and Breakdown in Bundles of Single-wall Carbon Nanotubes," Physical Review B, Vol. 64, 241307, 2001.

- [18] K. Banerjee, et al., "Global (Interconnect) Warming," IEEE Circuits & Devices Magazine, Vol. 17, Issue 5, pp. 16-32, 2001.

- [19] J. Y. Park, et al., "Electron-Phonon Scattering in Metallic Single-Walled Carbon Nanotubes," Nano Letters, Vol. 4, No. 3, pp. 517-520, 2004.

- [20] J. Hone, et al., "Thermal Conductivity of Single-Walled Carbon Nanotubes," Physical Review B, Vol. 59, No. 4, R2514, 1999.

- [21] J. Hone, et al., "Electrical and Thermal Transport Properties of Magnetically Aligned Single-Wall Carbon Nanotube Films," App. Phy. Lett., Vol. 77, No. 5, pp. 666-668, 2000.

- [22] http://bwrcs.eecs.berkeley.edu/Classes/IcBook/SPICE/

- [23] A. Todri-Sanial, "Investigation of horizontally aligned carbon nanotubes for efficient power delivery in 3D ICs," IEEE 18th Workshop on Signal and Power Integrity (SPI), pp.1-4, 2014.

- [24] Y. Takada and T. Yamamoto, Japanese Journal of Applied Physics, vol. 52, p. 06GD07, 2013

- [25] K. Thiagarajan and U. Lindefelt, Nanotechnology, vol. 23 p. 265703, 2012

- [26] A. Zienert, J. Schuster, and T. Gessner, Nanotechnology, vol. 25, p. 425203, 2014

- [27] C. Adessi et al., C. R. Physique, vol. 10, p. 305, 2009.

- [28] T. Yamamoto and K. Watanabe, Phys. Rev. Lett, vol. 96, p. 255503, 2006.

- [29] L. Lindsay, D. A. Broido, and N. Mingo, Phys. Rev. B, vol. 80, 125407, 2009.

- [30] https://nanohub.org

- [31] D. Kienle, J. I. Cerda, and A. W. Ghosh, "Extended Hückel theory for band structure, chemistry, and transport. i. carbon nanotubes," J. Appl. Phys., vol. 100, p. 043714, 2006.

- [32] J. C. Slater and G. F. Koster, Phys. Rev., vol. 94, p. 1498, 1954

- [33] http://quantumwise.com/

- [34] http://lammps.sandia.gov/

- [35] https://wiki.fysik.dtu.dk/gpaw/

- [36] F. Kreupl and et al. Carbon nanotubes in interconnect applications. Microelectronic Engineering, 2002.

- [37] A. Naeemi and et al. Design and performance modeling for single-walled carbon nanotubes as local, semi-global, and global interconnects in Giga-scale integrated systems, 2007.

- [38] A. Nieuwoudt and et al. Evaluating the impact of resistance in carbon nanotube bundles for VLSI interconnect using diameter-dependent modeling techniques. IEEE Transaction on Electron Devices.

- [39] H. Li and al. Low-resistivity long-length horizontal CNT bundles for interconnect applications. IEEE Transactions on Electron Devices, 2013.

- [40] H. J. Li and et al. Multichannel ballistic transport in multiwall carbon nanotubes. Physical Review Letters, 95, 2005

- [41] J. Y. Huang and et al. Atomic-scale imaging of wall-bywall breakdown and concurrent transport measurements in multiwall carbon nanotubes. Physical Review Letters, 94, 2005.

- [42] C. Berger and et al. Multiwalled carbon nanotubes are ballistic conductors at room temperature. Applied Physics A: Materials Science and Processing, 74, 2002.

- [43] A. Naeemi and et al. Compact physical models for multiwall carbon nanotube interconnects. IEEE Electron Device Letters, 27, 2006

- [44] P.G. Collins, M.S. Arnold, and P. Avouris. Engineering carbon nanotubes and nanotube circuits using electrical breakdown. Science, 292(5517):706–709, 2001.

- [45] D. Yokoyama, T. Iwasaki, K. Ishimaru, S. Sato, T. Hyakushima, M. Nihei, Y. Awano and H. Kawarada Electrical properties of carbon nanotubes grown at a low temperature for use as interconnects. Jpn. J. Appl. Phys., 47:1985, 2008.

- [46] M. Shulaker and et al., Carbon nanotube computer. Nature, 501.

- [47] X. Chen and et al. Fully integrated graphene and carbon nanotube interconnects for gigahertz high-speed CMOS electronics. IEEE Trans. on Electron Devices, 57(11), 2010

- [48] G. F. Close and et al. A 1 GHz integrated circuit with carbon nanotube interconnects and silicon transistors. Nano Lett., 8, 2008.

- [49] K. Banerjee and et al., "Current Status and Future Perspectives of Carbon Nanotube Interconnects," DOI: 10.1109/NANO.2008.132, Conference: Nanotechnology, 2008

- [50] J. S. Clarke et al., "Process Technology Scaling in an Increasingly Interconnect Dominated World," VLSI Symposium 2014, pp.142-143.

- [51] A. Naeemi and J. D. Meindl, EDL, Vol. 27, no. 5, pp.338-340, 2006.

- [52] A. M. Marconnet, M. A. Panzer, K. E. Goodson, Thermal conduction phenomena in carbon nanotubes and related nanostructured materials, Reviews of modern physics 85, 1295 (2013)

- [53] C. Subramaniam, A. Sekiguchi, T. Yamada, D. N. Futaba, K. Hata, Nano-scale, planar and multi-tiered current pathways from a carbon nanotube-copper composite with high conductivity, ampacity and stability Nanoscale, 8, 3888 (2016).

- [54] C. Subramaniam, T. Yamada, K. Kobashi, A. Sekiguchi, D. N. Futaba, M. Yumura, K. Hata, One hundred fold increase in current carrying capacity in a carbon nanotube-copper composite, Nat. Commun. 4, 1 (2013).

- [55] Z. Yao, C. L. Kane, C. Dekker, High-Field Electrical Transport in Single-Wall Carbon Nanotubes, Phys. Rev. Lett. 84, 2941 (2000).

- [56] B. Q. Wei, R. Vajtai, P. M. Ajayan, Reliability and current carrying capacity of carbon nanotubes, Appl. Phys. Lett. 79, 1172 (2001).

- [57] C. Berger, Y. Yi, Z.L. Wang, W.A. de Heer, Multiwalled carbon nanotubes are ballistic conductors at room temperature, Appl. Phys. A 74, 363 (2002).

- [58] M. Purewal, B. H. Hong, A. Ravi, B. Chandra, J. Hone, P. Kim, Scaling of Resistance and Electron Mean Free Path of Single-Walled Carbon Nanotubes Phys. Rev. Lett. 98, 186808 (2007).

- [59] S. Li, Z. Yu, S.-F. Yen, W. C. Tang, P. J. Burke, Carbon Nanotube Transistor Operation at 2.6 GHz, Nano Lett. 4, 753 (2004).

- [60] S. Kim, D. D. Kulkarni, K. Rykaczewski, M. Henry, V. V. Tsukruk, A. G. Fedorov, Fabrication of an UltraLow-Resistance Ohmic Contact to MWCNT-Metal Interconnect Using Graphitic Carbon by Electron Beam-Induced Deposition (EBID) IEEE Trans Nanotechnol 11, 1223 (2012).

- [61] S. Vollebregt, R. Ishihara. Carbon Nanotubes as Vertical Interconnects for 3D Integrated Circuits in Carbon Nanotubes for Interconnects: Process, Design, and Applications. A. Todri-Sanial, J. Dijon, A. Maffucci (Springer 2017 - ISBN 978-3-319-29746-0).

- [62] M. Sato, M. Takahashi, M. Nihei, S. Sato, N. Yokoyama. Novel Implantation Process of Carbon Nanotubes for Plugs and Vias, and their Integration with Transferred Multilayer Graphene Wires. IEEE IEDM 2013 (DOI: 10.1109/IEDM.2013.6724716).

- [63] J. Lu, J. Miao, T. Xu, B. Yan, T. Yu, Z. Shen. Growth of horizontally aligned dense carbon nanotubes from trench sidewalls. Nanotechnology 22, 265614 (2011).

- [64] S. Tawfick, K. O'Brien, A. J. Hart. Flexible High-Conductivity Carbon-Nanotube Interconnects Made by Rolling and Printing. Small 5, 2467 (2009).

- [65] N. Chiodarelli, A. Fournier, H. Okuno, J. Dijon. Carbon nanotubes horizontal interconnects with end-bonded contacts, diameters down to 50 nm and lengths up to 20 µm. Carbon 60, 139 (2013).

- [66] Y. L. Kim, B. Li, X. An, M. G. Hahm, L. Chen, M. Washington, P. M. Ajayan, S. K. Nayak, A. Busnaina, S. Kar, Y. J. Jung. Highly Aligned Scalable Platinum-Decorated Single-Wall Carbon Nanotube Arrays for Nanoscale Electrical Interconnects. ACS Nano 3, 2818 (2009).

- [67] R. Ramos, A. Fournier, M. Fayolle, J. Dijon, C.P. Murray, J. McKenna. Nanocarbon interconnects combining vertical CNT interconnects and horizontal graphene lines. IEEE IITC 2016 (DOI: 10.1109/IITC-AMC.2016.7507676).

- [68] Q. Cao, S.-J. Han, J. Tersoff, A. D. Franklin, Y. Zhu, Z. Zhang, G. S. Tulevski, J. Tang, W. Haensch. End-bonded

- contacts for carbon nanotube transistors with low, size-independent resistance. Science 350, 68 (2015).

- [69] Robertson J., Zhong G., Hofmann S., Bayer B. C., Esconjauregui C. S., Telg H., and Thomsen C. Use of carbon nanotubes for VLSI interconnects. Diamond Relat. Mater., 18:957, 2009.

- [70] Yokoyama D., Iwasaki T., Ishimaru K., Sato S., Hyakushima T., Nihei M., Awano Y., and Kawarada H. Electrical properties of carbon nanotubes grown at a low temperature for use as interconnects. Jpn. J. Appl. Phys., 47:1985, 2008.

- [71] Chiodarelli N., Masahito S., Kashiwagi Y., Li Y., Arstila K., Richard O., Cott D. J., Heyns M., Gendt S. D., and Groeseneken G. Measuring the electrical resistivity and contact resistance of vertical carbon nanotube bundles for application as interconnects. Nanotechnology, 22:085302, 2011.

- [72] Hata K., Futaba D. N., Mizuno K., Namai T., Yumura M., and Iijima S. Water-assisted highly efficient synthesis of impurity-free single-walled carbon nanotubes. Science, 306:1362, 2004.

- [73] Yamada T., Maigne A., Yudasaka M., Mizuno K., Futaba D. N., Yumura M., Iijima S., and Hata K. Revealing the secret of water-assisted carbon nanotube synthesis by microscopic observation of the interaction of water on the catalysts. Nano Lett., 8:4288, 2008.

- [74] Zhong G., Warner J. H., Fouquet M., Robertson A. W., Chen B., and Robertson J. Growth of ultrahigh density single-walled carbon nanotube forests by improved catalyst design. ACS Nano, 6:2893, 2012.

- [75] Harutyunyan A. R., Chen G., Paronyan T. M., Pigos E. M., Kuznetsov O. A., Hewaparakrama K., Kim S. M., Zakharov D., Stach E. A., and Sumanasekera G. U. Preferential growth of single-walled carbon nanotubes with metallic conductivity. Science, 326:116, 2009.

- [76] Koziol K. K. K., Ducati C., and Windle A. H. Carbon nanotubes with catalyst controlled chiral angle. Chem. Mater., 22:4904, 2010.

- [77] Santiago Esconjauregui, Lorenzo D Arsie, Yuzheng Guo, Junwei Yang, Hisashi Sugime, Sabina Caneva, Cinzia Cepek, and John Robertson. Efficient transfer doping of carbon nanotube forests by moo3. ACS Nano, 9(10):10422–10430, 2015. PMID: 26375167.

- [78] Y. Zhao, J. Wei, R. Vajtai, P. M. Ajayan, E. V. Barrera. Iodine doped carbon nanotube cables exceeding specific electrical conductivity of metals. SCIENTIFIC REPORTS 1, 83 (2011).

- [79] J. Dijon, R. Ramos, A. Fournier, H. Le Poche, H. Fournier, H. Okuno, J.P. Simonato. Record resistivity of in-situ grown horizontal carbon nanotube interconnect. Technical Proceedings of the 2014 NTSI-Nanotech conference, 3, 17 (2014).

- [80] V. M. Dubin. Integrated circuit with metal layer having carbon nanotubes and methods of making same. Intel US patent 7,300,860, 2004.

- [81] P. Liu, D. Xu, Z. Li, B. Zhao, E. Siu-Wai Kong, Y. Zhang. Fabrication of CNTs/Cu composite thin films for interconnects application. Microelectronic Engineering 85, 1984 (2008)

- [82] J. J. Yoo, J. Y. Song, J. Yu, H. K. Lyeo, S. Lee, J. H. Hahn. Multi-Walled Carbon Nanotube/Nanocrystalline Copper Nanocomposite Film as an Interconnect Material. IEEE ECTC p. 1282 (2008) DOI: 10.1109/ECTC.2008.4550140.

- [83] L. Aryasomayajula, R. Rieske, K.-J. Wolter. Application of Copper-Carbon Nanotubes Composite in Packaging Interconnects. IEEE ISSE p. 531 (2011) DOI: 10.1109/ISSE.2011.6053943.

- [84] C. Subramaniam, T. Yamada, K. Kobashi, A. Sekiguchi, D. N. Futaba, M. Yumura, K. Hata. One hundred fold increase in current carrying capacity in a carbon nanotube-copper composite. Nat. Commun. 4, 1 (2013).

- [85] Y. Chai, K. Zhang, M. Zhang, P. C. H. Chan, M. M. F. Yuen. Carbon Nanotube/Copper Composites for Via Filling and Thermal Management. IEEE ECTC p. 1224 (2007) DOI: 10.1109/ECTC.2007.373950.

- [86] Y. Chai, P. C. H. Chan. High Electromigration-Resistant Copper/Carbon Nanotube Composite for Interconnect Application. IEEE IEDM p. 607 (2008) DOI: 10.1109/IEDM.2008.4796764.

- [87] Y. Chai, P. C. H. Chan, Y. Fu, Y. C. Chuang, C. Y. Liu. Copper/Carbon Nanotube Composite Interconnect for Enhanced Electromigration Resistance. IEEE ECTC p. 412 (2008) DOI: 10.1109/ECTC.2008.4550004.

- [88] M. Melzer, T. Waechtler, S. Müller, H. Fiedler, S. Hermann, R. D. Rodriguez, A. Villabona, A. Sendzik, R. Mothes, S. E. Schulz, D. R.T. Zahn, M. Hietschold, H. Lang, T. Gessner. Copper oxide atomic layer deposition on thermally pretreated multi-walled carbon nanotubes for interconnect applications. Microelectronic Engineering 107, 223 (2013)

- [89] Y. Feng, S. L. Burkett. Fabrication and electrical performance of through-silicon via interconnects filled with a copper/carbon nanotube composite. J. Vac. Sci. Technol. B 33, 022004 (2015)

- [90] Y. Feng, S. L. Burkett. Modeling a copper/carbon nanotube composite for applications in electronic packaging. Computational Materials Science 97, 1 (2015)

- [91] M. B. Jordan, Y. Feng, S. L. Burkett. Development of seed layer for electrodeposition of copper on carbon nanotube bundles. J. Vac. Sci. Technol. B 33, 021202 (2015).

- [92] W.-S. Zhao, J. Zheng, Y. Hu, S. Sun, G. Wang, L. Dong, L. Yu, L. Sun, W.-Y. Yin. High-Frequency Analysis of Cu-Carbon Nanotube Composite Through-Silicon Vias. IEEE TRANSACTIONS ON NANOTECHNOLOGY, 15, 506 (2016).

- [93] Ghosh K., Verma K. Y., and Tan Ch. S. Implementation of carbon nanotube bundles in sub-5um diameter through-silicon-via structures for three-dimensionally stacked integrated circuits. Materials Today Communications, 2:e16–e25, 2015.

- [94] R. Xie, C. Zhang, M. H. van der Veen, K. Arstila, T. Hantschel, B. Chen, G. Zhong, and J. Robertson. Carbon nanotube growth for through silicon via application. Nanotechnology, 24(12):125603, 2013.

- [95] Wang T., Chen S., Jiang D., Fu Y., Jeppson K., Ye L., and Liu T. Through-silicon vias filled with densified and

- transferred carbon nanotube forests. IEEE Electron Device Letters, 33(3):420–422, 2012

- [96] N. Patil, J. Deng, A. Lin, H.-S.P. Wong, and S. Mitra. Design methods for misaligned and mispositioned carbon-nanotube immune circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 27(10):1725–1736, 2008.

- [97] P.G. Collins, M.S. Arnold, and P. Avouris. Engineering carbon nanotubes and nanotube circuits using electrical breakdown. Science, 292(5517):706–709, 2001.

- [98] G.Zhang, P.Qi, X.Wang, Y.Lu, X.Li, R.Tu, S.Bangsaruntip, D.Mann, L. Zhang, and H. Dai. Selective etching of metallic carbon nanotubes by gas-phase reaction. Science, 314(5801):974–977, 2006.

- [99] M. Sabry Aly, M. Gao, G. Hills, Ch-Sh. Lee, G. Pitner, M. M. Shulajer, T.F. Wu, M. Asheghi, J. Bokor, F. Franchetti, K.E. Goodson, Ch. Kozyrakis, I.Markov, K.Olukotun, L.Pileggi, E.Pop, J.Rabaey, Ch.Re, H.-S.Ph. Wong, and S. Mitra. Energy efficient abundant data computing: The n3xt 1000x. Rebooting Computing, pp. 24–33, Dec 2015.

- [100] TW Ebbesen, HJ Lezec, H Hiura, JW Bennett, HF Ghaemi, T Thio, et al. Electrical-conductivity of individual carbon nanotubes. Nature, 382(6586):54–56, 1996.

- [101] Sander J Tans, Michel H Devoret, Hongjie Dai, Andreas Thess, Richard E Smalley, LJ Georliga, and Cees Dekker. Individual single wall carbon nanotubes as quantum wires. Nature 386 (6624), 474-477.(1997), 1997.

- [102] Sander J Tans, Alwin RM Verschueren, and Cees Dekker. Room-temperature transistor based on a single carbon nanotube. Nature, 393 (6680):49–52, 1998.

- [103] Aaron D Franklin, Mathieu Luisier, Shu-Jen Han, George Tulevski, Chris M Breslin, Lynne Gignac, Mark S Lundstrom, and Wilfried Haensch. Sub-10 nm carbon nanotube transistor. Nano Letters, 12(2): 758–762, 2012.

- [104] Eric Pop, David Mann, Qian Wang, Kenneth Goodson, and Hongjie Dai. Thermal conductance of an individual single-wall carbon nanotube above room temperature. Nano Letters, 6(1):96–100, 2006.

- [105] Vikram V Deshpande, Scott Hsieh, Adam W Bushmaker, Marc Bockrath, and Stephen B Cronin. Spatially resolved temperature measurements of electrically heated carbon nanotubes. Physical Review Letters, 102(10):105501, 2009.

- [106] Qingwei Li, Changhong Liu, Xueshen Wang, and Shoushan Fan. Measuring the thermal conductivity of individual carbon nanotubes by the Raman shift method. Nanotechnology, 20(14):145702, 2009.

- [107] Cheng-Lin Tsai, Albert Liao, Eric Pop, and Moonsub Shim. Electrical power dissipation in semiconducting carbon nanotubes on single crystal quartz and amorphous sio2. Applied Physics Letters, 99(5):053120, 2011.

- [108] I-Kai Hsu, Michael T Pettes, Mehmet Aykol, Chia-Chi Chang, Wei-Hsuan Hung, Jesse Theiss, Li Shi, and Stephen B Cronin. Direct observation of heat dissipation in individually suspended carbon nanotubes using a twolaser technique. Journal of Applied Physics, 110(4):044328, 2011.

- [109] Xu Xie, Kyle L Grosse, Jizhou Song, Chaofeng Lu, Simon Dunham, Frank Du, Ahmad E Islam, Yuhang Li, Yihui Zhang, Eric Pop, et al. Quantitative thermal imaging of single-walled carbon nanotube devices by scanning Joule expansion microscopy. ACS Nano, 6(11):10267–10275, 2012.

- [110] Li Shi, Sergei Plyasunov, Adrian Bachtold, Paul L McEuen, and Arunava Majumdar. Scanning thermal microscopy of carbon nanotubes using batch-fabricated probes. Applied Physics Letters, 77 (26):4295–4297, 2000.

- [111] Fabian Menges, Philipp Mensch, Heinz Schmid, Heike Riel, Andreas Stemmer, and Bernd Gotsmann. Temperature mapping of operating nanoscale devices by scanning probe thermometry. Nature Communications, 7, 2016.

- [112] Fabian Menges, Heike Riel, Andreas Stemmer, Christos Dimitrakopoulos, and Bernd Gotsmann. Thermal transport into graphene through nanoscopic contacts. Physical review letters, 111(20):205901, 2013.

- [113] Thomas Belin and F Epron. Characterization methods of carbon nanotubes: a review. Materials Science and Engineering: B, 119(2):105–118, 2005.

- [114] Lunhui Guan, Kazu Suenaga, Zujin Shi, Zhennan Gu, and Sumio Iijima. Polymorphic structures of iodine and their phase transition in confined nanospace. Nano Letters, 7 (6):1532–1535, 2007.

- [115] Pedro MFJ Costa, Ujjal K Gautam, Yoshio Bando, and Dmitri Golberg. Direct imaging of Joule heating dynamics and temperature profiling inside a carbon nanotube interconnect. Nature Communications, 2:421, 2011.

- [116] http://www.aixtron.com/en/products/technologies/

- [117] A. Todri-Sanial, J. Dijon, A. Maffucci, Carbon Nanotubes for Interconnects: Process, Design, and Applications, Springer 2017 - ISBN 978-3-319-29746-0.

- [118] A. Pénicaud, P. Petit, J. E. Fischer. Doped Carbon Nanotubes in Carbon Meta-Nanotubes: Synthesis, Properties, and Applications. M. Monthioux (Wiley 2011 - ISBN: 978-0-470-51282-1)

- [119] S. Esconjauregui, M. Fouquet, B. Bayer, C. Ducati, R. Smajda, S. Hofmann and J. Robertson, "Growth of ultrahigh density vertically aligned carbon nanotube forests for interconnects." ACS Nano, 4:7431, 2010.