# Evaluating the Impact of Future Memory Technologies in the Design of Multicore Processors

**Guillem López Paradís**

Thesis supervisor: Prof. Teresa Monreal

Co-Supervisor: Dr. Lluc Alvarez

Internal examiner: Dr. Miquel Moretó

Project Bsc Barcelona Supercomputing Center Centro Nacional de Supercomputación

Specialization in Computer Engineering Polytechnic University of Catalonia

This dissertation is submitted for the degree of Bachelor Degree in Informatics Engineering

Barcelona School of Informatics

January 2017

## Acknowledgements

First of all, I would like to thank all of my advisors: Teresa, Lluc and Miquel. They have been very patient with me and I appreciate this effort for guiding me during the last months. They also have made corrections to this document and I am pleased for this amazing experience.

In addition, I would like to thank all the RoMoL team for the feedback given during the project and its acceptance. Specifically I would like to thank the main developer of TaskSim, Francesc, which has helped me with TaskSim.

Finally, I would like to thank my friends and my family for their loving and support.

### Abstract

### "It's the Memory, Stupid!"

In 1996, Richard Sites, one of the fathers of Computer Architecture and lead designer of the DEC alpha, wrote a paper [36] with the title above. In that paper he realized that the only important design issue for microprocessors in the next decade would be the memory subsystems design.

After more than a decade later, the community of researchers started to digest and internalize this quote. Now, after more than two decades, it can be said that a lot of progress has been done since 1996 but the expectations of the enormous data sets that software is going to handle in the followings years tells that more aggressive designs are needed.

Another reason new memory technologies are needed is because of the multicore architecture which has increased the required memory bandwidth. This architecture completely extended across the main computer sectors was the result of continuing the Moore's law in exchange of adding more difficulties for software and hardware developers.

All of this has promoted this project. First, it has been decided to create a bridge of the state of the art DRAM simulator Ramulator [30] with the micro-architecture simulator TaskSim [34]. Once the bridge has been completed, the second goal of this project has been to make an evaluation of the impact of the current and future memory technologies in multicore architectures.

As a first approach, this new infrastructure has been used to evaluate the behavior of several parallel applications concluding that the execution time of the applications varies significantly across different memory technologies which even increase the differences while simulating different processors. The doubtless winner among all the memory technologies evaluated has been HBM which in some cases has achieved the best expected memory cycle response time.

### **Abstract (Catalan Version)**

### "És la Memòria, Estúpid!"

El 1996, Richard Sites, un dels pares de l'Arquitectura de Computadors i dissenyador principal del DEC Alpha, va escriure un article [36] amb el títol anterior. En aquest article es va adonar que l'única qüestió important per al disseny de microprocessadors en la dècada següent seria el disseny de subsistemes de memòria.

Després de més d'una dècada, la comunitat d'investigadors va començar a digerir i assimilar aquesta cita. Ara, després de més de dues dècades, es pot dir que un gran progrés s'ha fet des de 1996, però les expectatives dels enormes conjunts de dades que el software utilitzarà en els següents anys indica que es necessiten dissenys més agressius.

Una altra raó per el qual es necessiten noves tecnologies de memòria és degut a les arquitectures multinucli que augmenten l'ample de banda de memòria requerit. Aquesta arquitectura completament estesa a través dels sectors principals va ser el resultat de seguir la llei de Moore a canvi d'afegir més dificultats per als desenvolupadors de software i hardware.

Tot això ha promogut aquest projecte. En primer lloc, s'ha decidit crear un pont sobre el capdavanter simulador de DRAM Ramulator [30] amb un de micro-arquitectura TaskSim [34]. Una vegada que s'ha completat el pont, el segon objectiu d'aquest projecte ha estat fer una avaluació de l'impacte de les tecnologies de memòria actuals i futures en les arquitectures multinucli.

Com a primera aproximació, s'ha utilitzat aquesta nova infraestructura per avaluar el comportament de diverses aplicacions paral·leles arribant a la conclusió que el temps d'execució de les aplicacions varia significativament entre diferents tecnologies de memòria, que fins i tot augmenten les diferències amb la simulació de diferents processadors. El guanyador, sens dubte, entre totes les tecnologies de memòria ha estat HBM que en alguns casos ha aconseguit el millor temps de cicle de memòria esperat.

### **Abstract (Spanish Version)**

### "Es la Memoria, Estupido!"

En 1996, Richard Sites, uno de los padres de la Arquitectura de Computadores y diseñador principal del DEC alpha, escribió un artículo [36] con el título anterior. En ese artículo se dio cuenta de que el único problema de diseño importante para los microprocesadores en la próxima década sería el diseño del subsistema de memoria.

Una década más tarde, la comunidad de investigadores comenzó a digerir e interiorizar esta cita. Ahora, después de más de dos décadas, se puede decir que se han hecho muchos progresos desde 1996, pero las expectativas de los enormes conjuntos de datos que el software va a manejar en los próximos años indican que se necesitan diseños más agresivos.

Otra razón por la que se necesitan nuevas tecnologías de memoria es debido a la arquitectura multinúcleo que aumenta el ancho de banda de memoria requerido. Esta arquitectura completamente extendida a través de los principales sectores fue el resultado de continuar la ley de Moore a cambio de añadir más dificultades para los desarrolladores de software y hardware.

Todo esto ha promovido este proyecto. En primer lugar, se ha decidido crear un puente entre el potente simulador de DRAM Ramulator [30] con uno de micro-arquitecura TaskSim [34]. Una vez que el puente se ha completado, el segundo objetivo de este proyecto ha sido hacer una evaluación del impacto de las tecnologías de memoria actuales y futuras en arquitecturas multinúcleo.

Como primera aproximación, se ha utilizado esta nueva infraestructura para evaluar varias aplicaciones paralelas llegando a la conclusión de que el tiempo de ejecución de las aplicaciones varía significativamente entre las diferentes tecnologías de memoria y que incluso aumentan las diferencias al simular diferentes procesadores. El ganador sin duda entre todas las tecnologías de memoria evaluadas ha sido HBM que en algunos casos ha logrado el mejor tiempo de ciclo de memoria de respuesta esperado.

## **Table of contents**

| List of figures xiii |                                                 |                                                              | xiii |  |  |  |

|----------------------|-------------------------------------------------|--------------------------------------------------------------|------|--|--|--|

| Li                   | List of tables xv                               |                                                              |      |  |  |  |

| No                   | omen                                            | clature                                                      | xvii |  |  |  |

| 1                    | Intr                                            | oduction                                                     | 1    |  |  |  |

|                      | 1.1                                             | Project Objectives                                           | 4    |  |  |  |

|                      |                                                 | 1.1.1 Integration of Ramulator in TaskSim                    | 4    |  |  |  |

|                      |                                                 | 1.1.2 Impact of Memory Technologies on Parallel Applications | 4    |  |  |  |

|                      | 1.2                                             | Document Structure                                           | 5    |  |  |  |

| 2                    | Stat                                            | e of the art                                                 | 7    |  |  |  |

| 3 Simulators         |                                                 | 11                                                           |      |  |  |  |

|                      | 3.1                                             | TaskSim                                                      | 11   |  |  |  |

|                      | 3.2                                             | Ramulator                                                    | 13   |  |  |  |

| 4                    | Bridge                                          |                                                              |      |  |  |  |

|                      | 4.1                                             | First use of Simulators                                      | 17   |  |  |  |

|                      |                                                 | 4.1.1 Ramulator                                              | 17   |  |  |  |

|                      |                                                 | 4.1.2 TaskSim                                                | 18   |  |  |  |

|                      | 4.2                                             | Other Bridges                                                | 19   |  |  |  |

|                      | 4.3                                             | Bridge TaskSim-Ramulator                                     | 22   |  |  |  |

|                      | 4.4                                             | Debug and firsts tests                                       | 24   |  |  |  |

|                      | 4.5                                             | Bugs found                                                   | 24   |  |  |  |

| 5                    | Experimental Setup and Validation of the Bridge |                                                              |      |  |  |  |

|                      | 5.1                                             | Hardware and Software                                        | 27   |  |  |  |

|                      | 5.2                                             | Applications                                                 | 28   |  |  |  |

|                                         |                                             | 5.2.1        | PARSEC Benchmarks and SpecFem3D | 29 |

|-----------------------------------------|---------------------------------------------|--------------|---------------------------------|----|

|                                         |                                             | 5.2.2        | Synthetic Benchmarks            | 29 |

|                                         | 5.3                                         | -            |                                 |    |

|                                         |                                             | 5.3.1        | CPU configuration               | 30 |

|                                         |                                             | 5.3.2        | DRAM configuration              | 31 |

|                                         | 5.4                                         | 4 Validation |                                 |    |

|                                         |                                             | 5.4.1        | Verification of the requests    | 33 |

|                                         |                                             | 5.4.2        | Time overhead analysis          | 34 |

| 6                                       | Ana                                         | lysis        |                                 | 37 |

|                                         | 6.1                                         | MPKI         |                                 | 37 |

|                                         | 6.2                                         | Execut       | ion cycles                      | 38 |

|                                         | 6.3                                         | Row H        | its, Misses and Conflicts       | 41 |

|                                         | 6.4                                         | Distrib      | ution of Commands Across Banks  | 44 |

| 7                                       | Con                                         | clusions     | 3                               | 47 |

|                                         | 7.1                                         |              | outions                         | 48 |

|                                         | 7.2                                         |              | Work                            | 48 |

| 8 Project Management                    |                                             | nagement     | 51                              |    |

| Ū                                       | 8.1 Stakeholders, Obstacles and Methodology |              | 51                              |    |

|                                         |                                             | 8.1.1        | Stakeholders                    | 51 |

|                                         |                                             | 8.1.2        | Obstacles                       | 52 |

|                                         |                                             | 8.1.3        | Methodology                     | 53 |

|                                         | 8.2                                         | Project      | Planning                        | 54 |

|                                         |                                             | 8.2.1        | Project Tasks                   | 54 |

|                                         |                                             | 8.2.2        | Time Table                      | 56 |

|                                         |                                             | 8.2.3        | Planning                        | 57 |

|                                         |                                             | 8.2.4        | Alternatives and Action Plan    | 57 |

|                                         | 8.3                                         | Budget       | and sustainability              | 58 |

|                                         |                                             | 8.3.1        | Cost Evaluation                 | 58 |

|                                         |                                             | 8.3.2        | Budget Monitoring               | 60 |

|                                         |                                             | 8.3.3        | Sustainability and Viability    | 61 |

| Re                                      | feren                                       | ces          |                                 | 63 |

| Appendix A Configuration File TaskSim 6 |                                             |              |                                 | 67 |

### Appendix B Configuration File Ramulator

71

# List of figures

| 1.1  | Memory Wall and Moore's Law. Figure taken from [7]                                | 2  |

|------|-----------------------------------------------------------------------------------|----|

| 2.1  | AMD's HBM implementation. Figure taken from [1]                                   | 7  |

| 3.1  | Internal Memory Organization in tree.                                             | 15 |

| 4.1  | Gem5 bridge with Ramulator                                                        | 20 |

| 4.2  | TaskSim bridge with Ramulator.                                                    | 22 |

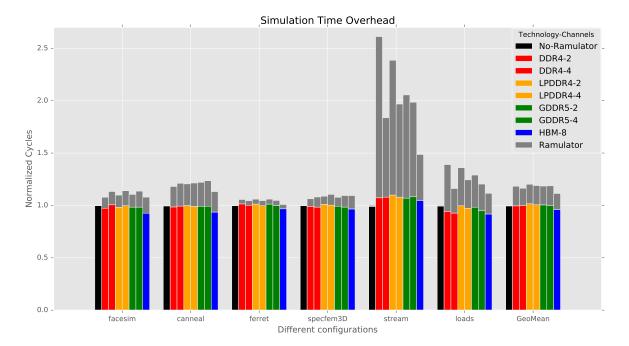

| 5.1  | Simulation time overhead measured as normalized time in cycles                    | 35 |

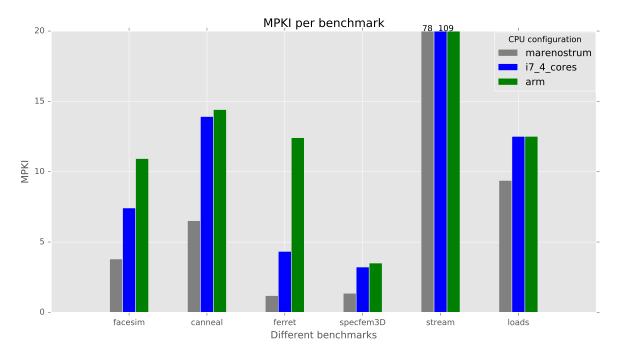

| 6.1  | Misses per Kilo Instruction per benchmark.                                        | 38 |

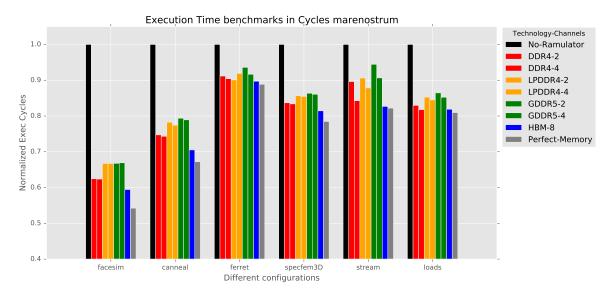

| 6.2  | Execution time of benchmarks on <b>marenostrum</b> configuration with different   |    |

|      | memory technologies                                                               | 39 |

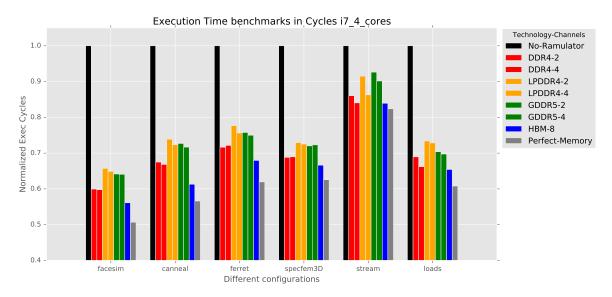

| 6.3  | Execution time of benchmarks on i7 configuration with different memory            |    |

|      | technologies.                                                                     | 39 |

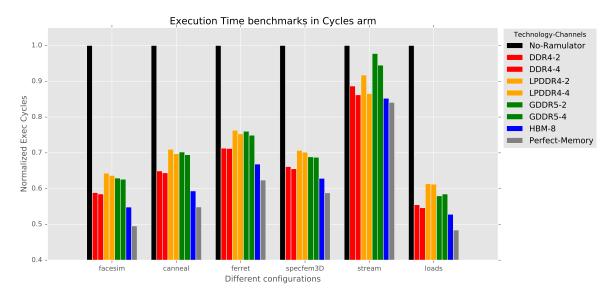

| 6.4  | Execution time of benchmarks on <b>arm</b> configuration with different memory    |    |

|      | technologies.                                                                     | 40 |

| 6.5  | Simplified address mapping. Figure taken from [6].                                | 41 |

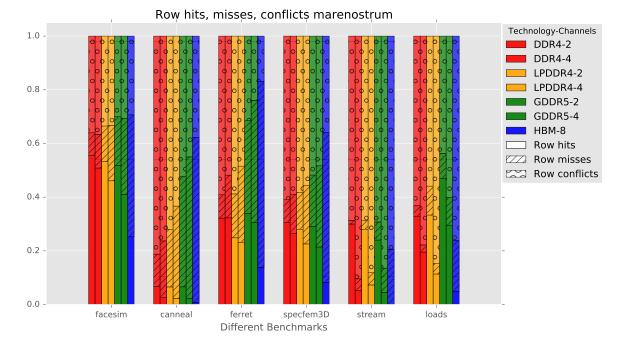

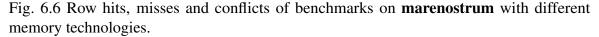

| 6.6  | Row hits, misses and conflicts of benchmarks on marenostrum with differ-          |    |

|      | ent memory technologies.                                                          | 42 |

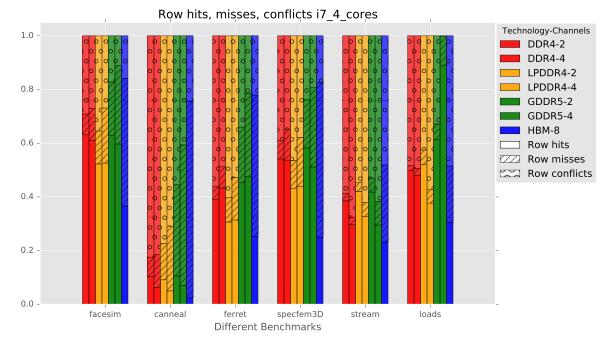

| 6.7  | Row hits, misses and conflicts of benchmarks on i7 with different memory          |    |

|      | technologies.                                                                     | 43 |

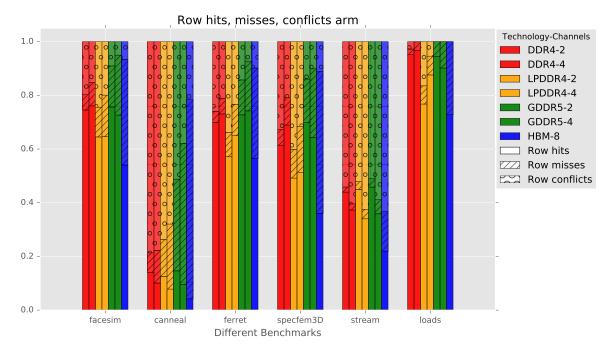

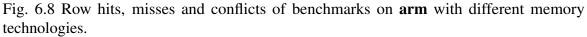

| 6.8  | Row hits, misses and conflicts of benchmarks on <b>arm</b> with different memory  |    |

|      | technologies.                                                                     | 43 |

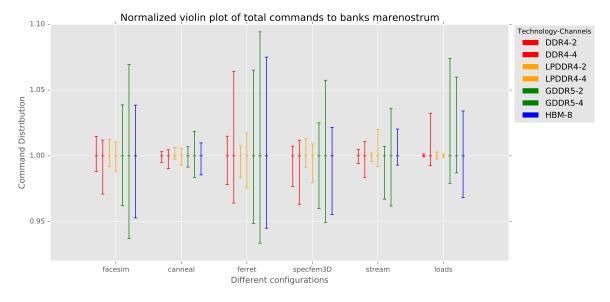

| 6.9  | Command distribution violin plot of benchmarks on marenostrum with                |    |

|      | different memory technologies.                                                    | 45 |

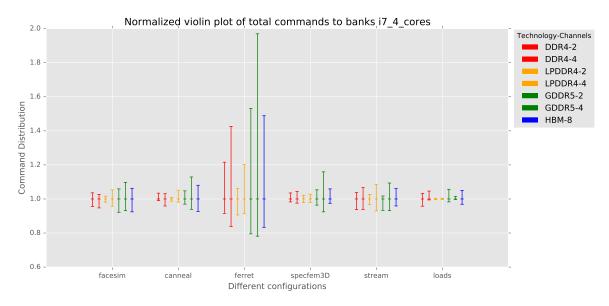

| 6.10 | Command distribution violin plot of benchmarks on <b>i7</b> with different memory |    |

|      | technologies.                                                                     | 45 |

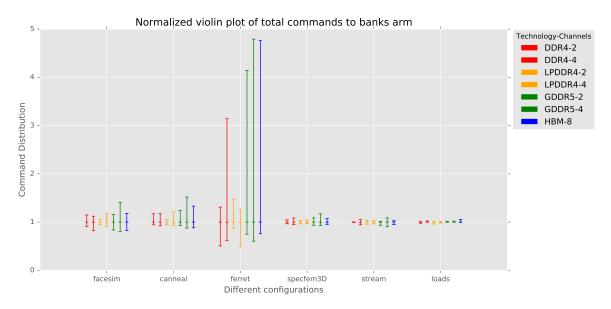

| 6.11 | 11 Command distribution violin plot of benchmarks on <b>arm</b> with different |    |

|------|--------------------------------------------------------------------------------|----|

|      | memory technologies.                                                           | 46 |

| 8.1  | Example of my Scrum board in Trello                                            | 53 |

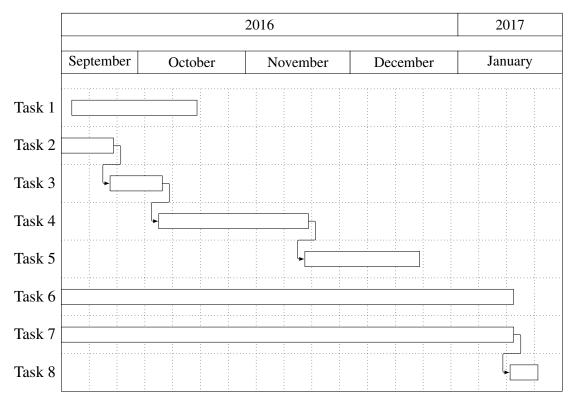

| 8.2  | Gantt chart.                                                                   | 57 |

## List of tables

| 4.1 | Default configuration.                                 | 24 |

|-----|--------------------------------------------------------|----|

| 5.1 | CPU configurations.                                    | 30 |

| 5.2 | DRAM relevant characteristics                          | 31 |

| 5.3 | DRAM technical characteristics.                        | 32 |

| 5.4 | Misses tables comparing theoretical and in simulation. | 34 |

| 8.1 | Hours per task.                                        | 56 |

| 8.2 | Global Cost                                            | 58 |

| 8.3 | Human Resources price.                                 | 58 |

| 8.4 | Hardware resources                                     | 59 |

| 8.5 | Cost per task.                                         | 60 |

## Nomenclature

#### **Acronyms / Abbreviations**

- ACM Association for Computer Machinery

- BSC Barcelona Supercomputing Center

- CPU Computer Processing Unit

- DAC Departament d'Arquitectura de Computadors(Computer Archirtecture Department)

- DDR Double Data Rate

- DRAM Dynamic Random Access Memory

- GDDR Graphics Double Data Rate

- HBM High Bandwidth Memory

HMC Hybrid Memory Cub

- ISA Instruction Set Architecture

- JEDEC Joint Electron Device Engineering Council

- LPDDR Low Power Double Data Rate

- RoMoL Riding on the Moore's Law Project

- SDR Single Data Rate

- SDRAM Synchronous Dynamic Random Access Memory

WIO Wide I/O

## Chapter 1

## Introduction

During the last decades, it has been given all the relevance to the Moore's law which has been predicting the decreasing size of transistors every two years. This law was an observation made by Gordon Moore<sup>1</sup> which has completely direct the semiconductor industry until now having every two years a more powerful computer.

Unfortunately, last year was fateful to the Moore's law and finally Intel could not continue shrinking the size of the transistor at the same speed. Intel had to change the manufacturer process to three years. This also confirmed and defensed the bet of going for multicore processors.

Some years ago it was decided to go for processors with multiple cores because it was no longer profitable as before to increase the performance of a single core increasingly complex. This change resulted in not increasing as much the single core performance in exchange of having more cores. However, this change also increased the complexity of the software needed to take full advantage of the new design.

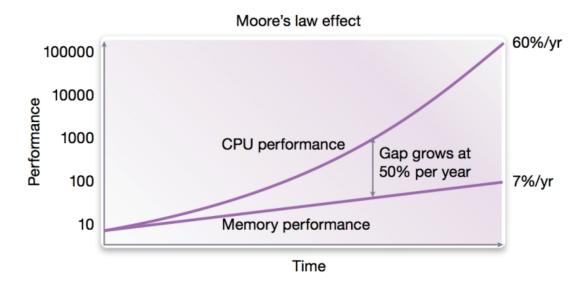

At the same time as the Moore's law was predicting the nearly exponential growth of CPU performance, the memory performance was not growing at that rate. This phenomena commonly known as the memory wall problem, visualized in figure 1.1, has also been very important for computer architects for not being blocked the CPU activity by the memory.

In the search to obtain an ideal performance in the execution of the programs, it has been the memory subsystem that presented the most obstacles. When running multiple applications on a chip multiprocessor it occurs that a large percentage of the execution cycles is waiting the memory.

One of the first approaches to solve this problem was to manage a cache hierarchy inside the CPU chip, in this manner the data access latency was extremely reduced to nearly one cycle in the best case scenario. While the integration technology has advanced, the logical

<sup>&</sup>lt;sup>1</sup>Co-Founder of Intel.

approach has been to put more caches inside the chip until the current three levels of cache. In addition, a simultaneous goal of increasing the with of instruction issue and reducing the average latency of memory access, requires to have a off-chip memory technologies able to support several concurrent accesses and high rates of data transfers (high bandwidth) [26].

Fig. 1.1 Memory Wall and Moore's Law. Figure taken from [7].

In a bigger perspective, this can be viewed as a memory hierarchy where at the top are the faster technologies: all the CPU registers and on-chip caches, but the lower levels are the slowest: off-chip DRAM memory and then the hard drive. This project focuses on the study and evaluation of memory technologies located on the low side of this hierarchy and more specifically off-chip DRAM memories.

On this side, several design decisions have been taken in the aim of shortening the now called bandwidth wall<sup>2</sup> between the CPU and the off-chip memory. One of the first advances was the transition from *Single Data Rate* (SDR) to *Double Data Rate* (DDR) in the firsts designs of SDRAM. Currently, DDR is the most widespread design.

This architecture allows to send in one cycle two words<sup>3</sup> which increased by two the performance. This prolific standard is nowadays in its fourth revision DDR4 (2012) [5] and has also been expanded to different sectors like video cards (GDDR) and low power memories for the mobile sector (LPDDR).

Although this architecture has made enormous achievements, the new era of multicore processors with high frequency and bigger data sets imposed by the future software has aimed

<sup>&</sup>lt;sup>2</sup>Limited communication bandwidth beyond chip boundaries.

<sup>&</sup>lt;sup>3</sup>Particular unit of data for processor typically 32 or 64 bits.

to investigate new technologies able to achieve higher bandwidths. One of the promising technologies is the stacking of memory over the processor chip, reducing drastically the latency of a memory request. For this technology under development has already been made some standards like *High Bandwidth Memory* (HBM) [4] and its rival *Hybrid Memory Cube* (HMC).

On the other hand, advances in both industries (processors and memories) have been taken advantage of simulators in order to fully determine step by step whether one new proposal is useful or not. While CPU simulators are abundant and very powerful, simulating DRAM has not been very easy in the last decades until 2015 when Ramulator [11, 30] was published by a group of researchers at *Carnegie Mellon University* (CMU). This promising simulator has a clear advantage over the others: supporting several standards in contrast to a few offered by the others which could be interesting for furthers research.

Moreover, Ramulator comes with the possibility of being simulated with one of the most extended CPU simulators, Gem5 [18]. These features expand its uses with simulating a full memory hierarchy including the usually forgotten RAM in depth. Gem5 can simulate in different levels of abstraction and detail, which had enabled during the last years prolific research. However, as its main purpose is not simulating a big number of processors, it is slow compared to others simulators.

Another interesting simulator proposed by BSC is TaskSim [16, 34], a simulator not as powerful as Gem5 in terms of simulating at a low level of abstraction in exchange of simulating bigger amounts of processors. This simulator is under development and very used through the researchers at BSC offering great opportunities for evaluating the capability of parallel applications to scale up to high number of processors [24, 37, 27, 31, 32]. However, this kind of simulation needs a better memory simulation detail because of the increased memory bandwidth requirements of future applications.

The first approach taken by TaskSim to simulate the memory in a great level of detail was using DramSim2 [35] only able to simulate old standards like DDR2 (2003) and DDR3 (2007), which makes it obsolete for future memory technologies. This creates an opportunity for this project to integrate a new memory simulator in TaskSim and extend this infrastructure to make further studies.

This is one of the reasons why this project is interesting because making the bridge with Ramulator will add a needed realism to TaskSim in order to permit the evaluation of the impact of future memory technologies on parallel applications. This kind of evaluations are rarely found in the literature, which creates an opportunity for this project to make a study that is useful for the community.

### **1.1 Project Objectives**

The project has two main objectives: integrating Ramulator in TaskSim and using these simulation infrastructure to study the impact of different memory technologies on parallel applications.

#### 1.1.1 Integration of Ramulator in TaskSim

The first objective of this project will be the integration of a memory simulator inside a micro-architecture simulator. This will add a needed realism when simulating the memory in the selected micro-architecture simulator: TaskSim, a trace-driven cycle-accurate simulator that is being developed at BSC.

On the other hand, the memory simulator that will be used is Ramulator, a fast and extensible DRAM simulator that is being developed at the Carnegie Mellon University (CMU).

In order to achieve this objective, first of all, a stand-alone study of each simulator will be necessary. This first study will allow understanding in depth each simulator finding its drawbacks or limitations. This study will consist on reading the documentation provided by each simulator, experimenting with simulations and reading its code to understand how work internally.

Having completed this first study, it will be the time to create the actual bridge of the simulators. This bridge will consist in a piece of software inside TaskSim that will send memory requests to Ramulator and eventually receive messages from Ramulator for the purpose of ending these memories requests.

After the integration is done a validation will be necessary. The validation will determine whether it works as expected or there is something wrong. Although this may not seem very important, it is the key for further uses of this bridge. It has to be verified that the integration simulates the workloads correctly and does not break the execution.

#### 1.1.2 Impact of Memory Technologies on Parallel Applications

Once the integration has been done, researches that use TaskSim will be able to evaluate better the performance of parallel programs with different real standards of memory. It also would allow to analyze the impact of memories on parallel applications.

This second objective is as ambitious as the first and several steps will be needed. First, it will be required a study of different DRAM memory technologies in the interest of finding

their limitations and advantages. This will allow to decide which standards will be used for the analysis in pursuance of a fair competition and for not obtaining a bad comparison.

One of the best features of Ramulator is its diverse range of standards that accepts by default. This feature is ideal for the integration because it will allow to simulate parallel programs with different DRAM standards in furtherance of an interesting and new analysis.

Finally, the study will provide several results conductive to an evaluation of the bottlenecks and advantages of the DRAM standards in parallel programs. Adding to this, using different CPU configurations in TaskSim will add richer results to this study.

### **1.2 Document Structure**

This document presents a logical order through the chapters starting from the introduction and state of the art until an expected conclusion. The first part of this document is the first two chapters which presents the problem and explains the history until nowadays in order to easily entry in the topic of this project.

The second part of the document consists of the detailed explanation of the project from chapter 3 until chapter 7. Within this part it can be divided into three main topics:

- Chapters 3 and 4 explain the simulators and the bridge.

- Chapters 5 explains the experimental setup and the validation process of the bridge.

- Chapter 6 is where the analysis of memory standards in parallel applications is detailed giving several charts to easily see the results.

Having reviewed all these parts, the conclusions are given in chapter 6 and finally some project management considerations are summarized in the last chapter. After this, there are the references of all the chapters numbered in ACM<sup>4</sup> style. Finally, Appendices A and B show two configurations files: one of TaskSim and the other of Ramulator.

<sup>&</sup>lt;sup>4</sup>Association for Computer Machinery.

## Chapter 2

## State of the art

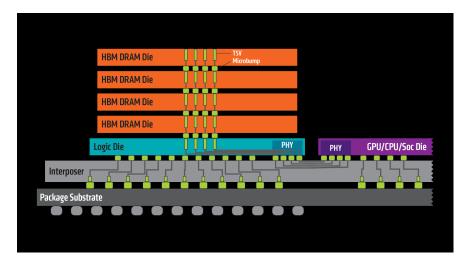

The state of the art of memory technologies is going on the direction of on-chip memories reducing the big latency of off-chip standards and at the same time, increasing the bandwidth. This new memories are possible using an old technique called *Through-Silicon Via* (TSV) which enables to interconnect through the package of the chip. The next figure 2.1 shows how are interconnected.

Fig. 2.1 AMD's HBM implementation. Figure taken from [1].

Following this technique, there are three standards already published by the *Joint Electron Device Engineering Council* (JEDEC) which is the Solid State Technology Association in charge of publishing new memory technologies. The three standards corresponds to different implementations using TSV: the most famous ones are HBM and HMC: HBM intended for video cards and HMC targeting supercomputers. There is also another standard called Wide I/O which aims to be the low power solution for memories requiring high bandwidth.

Moreover, TSV is a good technology for the 3D stacking of the chips, packaging the memory over the processor in order to reduce the latency. Having the memory over the processor has the clear advantage of proximity to the CPU but they also have some temperature problems. Up to date, this kind of packages have already been fabricated in some commercial graphics cards and industry research oriented products.

Furthermore, these new standards are intended to compete with the current established standards like DDR4 [5] for desktops and servers, GDDR5 [3] for video cards and LPDDR4 [2] for the mobile sector. This competition have to be validated and further studies are needed. It will be done in simulation and one of the current best memory simulators is the already mentioned Ramulator, which can simulate all these new standards except HMC.

Ramulator is the state of the art simulator offering a great range of standards to simulate, a fast simulation time and the possibility to be integrated with others simulators or to be altered in order to make studies of new memories. Some studies have already been made modifying Ramulator to simulate two levels of heterogeneous memory composed by HBM and DDR3 and to make an evaluation of reliability versus performance of this heterogeneous computers [25].

Moreover, another study [21] using Ramulator makes for the first time a detailed experimental characterization and analysis of latency variation. Once again it is used a modified Ramulator to do the study confirming its adaptability. One of the best competitors of Ramulator, DramSim2 [35], only accepts DDR2/3, so it is very limited to evaluate new proposals.

Nevertheless, Ramulator also offers an integration with one of the state of the art CPU simulators: Gem5. Gem5 is a modular execution driven architectural simulator that is developed by the community of researchers. A lot of studies have been made with this tool but not focusing in the memory. In contrast to this simulator, there are others simulators that are more lightweight so, even though they lose some accuracy, they are better suited to simulate big machines. For example TaskSim is a computer architecture simulator perfect for analyzing programming models and evaluate architecture with multiple cores.

As being the integration of simulators a must, TaskSim has some bridges and the one which is interesting to this project is with DramSim2. Although having said DramSim2 is obsolete for the one of the purposes of this project, it is very useful to have a related work inside TaskSim allowing a future bridge to be easier.

Nevertheless, related works about memories studies exist, for example a study [38] focused on new memory technologies using TSV defends its use comparing to the off-chip solutions. This study is interesting and related to this project in the manner that for future parallel applications this might be the key for achieving great performance.

Apart from the above paper, there is a good revision of the standards in the most important sectors like desktop, mobile and video cards [23]. From this work it can be obtained several interesting observations of memory technologies like the correlation between the memory performance and the number of *Dual In-line Memory Module* (DIMM)<sup>1</sup> of a channel. More DPC<sup>2</sup> reduce the overall performance of the memory system.

Although, these articles can be very useful they are not exactly the kind of study aimed for this project and no further related work have been found. The evaluation of memory architectures for parallel applications it is kind of new.

Finally, new architectures have been proposed specifically designed for multicore architectures. Udipi et al. [39] proposed a new design and organization of DRAM to improve the performance in multicore architectures.

<sup>&</sup>lt;sup>1</sup>Memory module with both sides of the PCB with DRAM chips. <sup>2</sup>DIMM Per Channel.

## Chapter 3

## **Simulators**

In this section, the simulators used for the project are presented. First, the selected CPU simulator is TaskSim and a brief discussion about this simulator is given as for one of the best alternatives, Gem5. Finally, for the part of Ramulator the same approach is followed.

### 3.1 TaskSim

TaskSim is a trace-driven simulator developed at Barcelona Supercomputing Center (BSC) by the team of Alejandro Rico [34] and nowadays, the RoMoL team. Being trace-driven means that TaskSim requires a trace<sup>1</sup> of the application to be simulated and a configuration file. This configuration file<sup>2</sup> specifies to TaskSim which kind of simulation will be done and the characteristics of the processors and the memory hierarchy. Lastly, TaskSim targets the simulation of parallel applications abstracting the detailed computation of each core for systems with lots of them in order to view the scalability of a large computational system.

TaskSim works at the level of tasks and this allows to model issues of parallel applications like inter-task synchronization, overlapping of data transfer with task computation, cache sizes, coherency protocols and data migration, interconnection bandwidth and topology and memory latencies. It has two main modes of operation, the one that will be used in this project as it offers a great level of detail and a *Burst Mode* which is faster in exchange of not modeling the accesses to the memory hierarchy. The original aim of TaskSim was to scale up to 1000 processors which was very ambitious and it is still under development.

However, there are several kinds of simulators that have its advantages and drawbacks in contrast to trace-driven. In the last years, execution-driven simulators have been made very famous which in exchange of bigger simulation time they can dynamically change the

<sup>&</sup>lt;sup>1</sup>Pre-recorded stream of instructions with a fixed input.

<sup>&</sup>lt;sup>2</sup>An example of the default configuration file can be seen in Appendix A.

instructions to be executed depending on different inputs data. This kind of simulators work at the level of instructions allowing to be very specific in timings of the micro-architecture and see related issues to this kind of abstraction. The drawback with this kind of approach is the scalability for enormous systems.

TaskSim accepts different kind of traces that affects its performance (simulation time). However, since 2014 there is a default configuration which is binary, instead of plain text. This change enabled to decrease the size of the traces. They can also be different depending on the desired type of simulation. The most recent ones are *uop* and *rle*: both stores the memory access and operations separated but in *rle*, the memory addresses are expressed in a relative value to the last memory address reducing the total trace size. Finally, there was also an old type of traces called *mem* in plain text.

Furthermore, traces are generated by an external instrumentation tool called PIN provided by Intel and with the help of Nanos++<sup>3</sup>. PIN enables to record which instructions are executed and the addresses of all memory accesses for a binary program execution at runtime. Moreover, it also detects the Nanos++ library calls and is able to catch the Task creation, deletion, pausing, resuming, etc. Merging all of this information, TaskSim is able to generate a trace.

For the study of scalability of large systems it is not required a detailed level of instruction because it will be inviable in simulation time. The approach that follows TaskSim is the commented above task-execution which scales very good with so many cores. With the help of native execution, off-line simulation and analytical-models it is obtained a burst length for the task not being that detailed. Combining this with the inter-task synchronization and data-transfers allows to model the memory and interconnection systems in cycle-accurate detail.

Although there are several good simulators in the market, one of the most famous is the Gem5 simulation infrastructure. It is the result of the merge between M5 [19] and GEMS [33]. M5 provides a a highly configurable framework, multiple *Instruction Set Architecture's* (ISA) and different CPU models. On the other hand, GEMS complements these features with a detailed and flexible memory system, including support for multiple cache coherence and interconnect protocols.

Gem5 is an execution-driven simulator with an excellent detailed CPU and hierarchy model that permits to simulate in different levels of abstraction easily specifying which level is required. Two of the main features of the simulator are the Python Integration that permits to easily configure the system while being coded in C++ (around 85%) and its Object-Oriented design that allows flexibility for multiple configurations.

<sup>&</sup>lt;sup>3</sup>Run-time library developed in C++ that takes care of dependency management in task-parallel programs.

However, one of the most common problems in the commented simulators is the lack of a good memory simulation. For this reason, TaskSim has a bridge with DramSim2 that enables simulating with a great level of accuracy systems with DDR2/DDR3. This bridge has some drawbacks like high simulation time overhead and a limited number of memory standards.

### 3.2 Ramulator

Memory simulation has received little attention during the last decade compared to CPU simulation. Simulators have been emerging but never been designed to accept differents standards. For example, two of the most famous simulators a few years ago were DramSim2 and USIMM [20] but only support two standards: DDR2/DDR3. This is a big limitation for the rapid changes of DRAM standards. Moreover, in the recent years new academic proposals have been proposed.

One of the newest memory simulators is Ramulator, a fast, extensible and cycle-accurate DRAM simulator developed at CMU that offers a good performance and multiple DRAM industry and academic standards configurations. This allows to evaluate the strengths and the weaknesses of present and future standards. Also, the extensibility of Ramulator is kind of new in the world of DRAM simulators.

Ramulator is an open source simulator with a *MIT* license that enables to the community to modify and help in the development of the project if the authors authorize it. Actually, the project is on Github [11] which enables anybody to view, download and use the simulator.

Having a *MIT* license means that anybody can use, publish, modify, merge, etc with the little restriction of including the copyright. This kind of license created at MIT is one of the most famous one in the free software community. This license also enables to improve the simulator by the community finding new bugs or proposing new features.

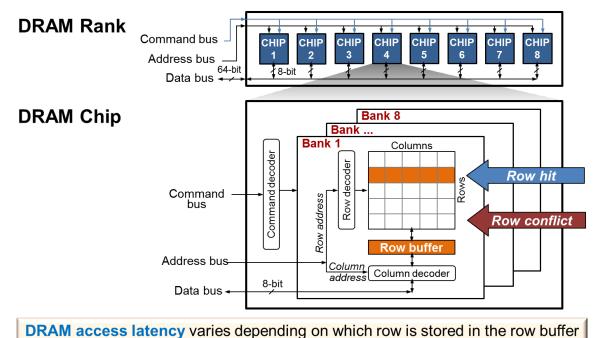

Ramulator is based on an important observation: DRAM can be abstracted as a hierarchy of states-machines where the behavior of each state machine is dictacted by the standard. For this reason, Ramulator offers a standard-agnostic state-machine which is fitted in the class DRAM.h and then all the standards are built from this class. As a result, it offers a wide range of academic and industrial standards: DDR3/4 (desktop), GDDR5 (video cards), LPDDR3/4 (mobile), HBM (server, high bandwidth), WIO1/2 (mobile, high bandwidth), SALP (academic) ...

Any standard class that comes with Ramulator inherits from DRAM.h class. They offer a great level of detail and every timing reference can be checked with the JEDEC standards. Actually, in this project, it will be checked as a validation procedure for ensuring the validity of the standards.

By default, it supports three different types of usage:

- Memory Trace Driven: In this method Ramulator reads memory traces from a regular file and simulates the DRAM behavior. It assumes that the trace files contains at each line an address followed by a 'R' or 'W' that first indicates the address and then the operation. An example could be: 0xFF233245 R which performs a read of the address 0xFF233245.

- **CPU Trace Driven:** There is a simplified model of a "core" that generates memory requests to the DRAM subsystem built in Ramulator. In this manner, Ramulator expects in each line of a trace file a memory request and must have the amount of CPU instructions followed by the address and optionally a writeback<sup>4</sup> request, which is the dirty cache-line<sup>5</sup> that is evicted by the read request. An example could be: <num-cpuinst> <addr-read> <addr-writeback>.

- Gem5 Driven: In this case, Ramulator works as an independent simulator that receives memory requests as they are generated by the Gem5 simulator. This has a lots of possibilities for studying the performance using different configurations.

I order to execute Ramulator, a configuration file must be provided. At appendix B there is an example although the configuration consists in the following key-data:

- **standard** = One of the all standards that supports (Ex: DDR3/4, HBM, etc...)

- **channels** = The number of channels of the configuration. Being a channel the physical connection between a memory controller and DRAMs [28].

- **ranks** = The number of ranks (set of DRAM chips) per channel

- **speed** = The speed regarding the type of organization selected between the standard.

- **org** = The organization selected (standard-size-width of bank: DDR3\_2Gb\_x8). Being a bank the basic unit considered in Ramulator which is a group of several memory arrays of storage cells [28].

This organization will be explained in the analysis chapter where further explanations will be given.

<sup>&</sup>lt;sup>4</sup>A writeback request occurs in caches with a writing policy of write-back where the only copy of the memory even modified is stored in the cache until a request to the same position in the cache force the copy back to the memory.

<sup>&</sup>lt;sup>5</sup>Cacheline is the container of several blocks of memory in a cache and a dirty cacheline is the common way to refer to a modified cacheline in write-back caches.

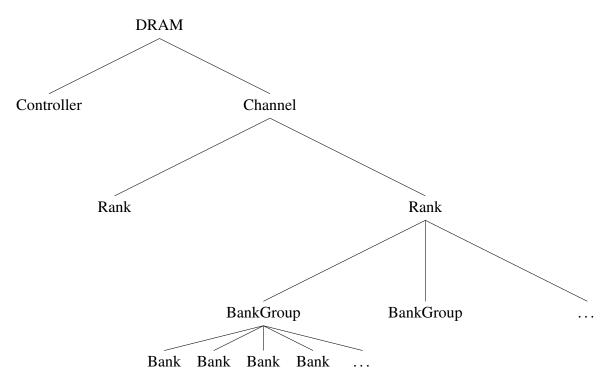

Internally the organization of memories in Ramulator is translated in this manner:

Fig. 3.1 Internal Memory Organization in tree.

It also allows to record all the internal commands and timings from the memory controller to the banks of the simulation in order to see exactly what happens inside. As expected, this feature increases dramatically the simulation time and it is only useful for debug and learning purposes.

| PRE | 90959: |

|-----|--------|

| ACT | 90960: |

| PRE | 90960: |

| RD  | 90961: |

This snippet of the command trace shows the command at the first column and the clock at the second. Ramulator also permits to print more internal parameters but they are not useful for this project. Acronyms *PRE*, *ACT and RD* are some of the commands taking part in the process of accessing the memory (Precharge, Activate, Read) [28].

Comparing to its competitors Ramulator's creators state that Ramulator is 2.5X faster than its best competitor, USIMM. This is due to the fact that it uses look-up tables to store and update the relevant timings of the queries. The look-up table is a two-dimensional array of

lambdas functions<sup>6</sup>, which is indexed using the level in the hierarchy at which the command is being decoded for in this manner store relevant data with a rapid access.

<sup>&</sup>lt;sup>6</sup>A C++11 construct.

## Chapter 4

## Bridge

In this chapter it is explained the process of making the bridge between TaskSim and Ramulator. It starts talking about the first get in touch with both simulators and its tools. Then it is explained the DramSim2 bridge with TaskSim and then the Gem5 with Ramulator. Following the bridges it is explained the bridge with Ramulator and finally, the results and tests.

### 4.1 First use of Simulators

The first simulator that has been used is Ramulator because of its size. It is less complex and for starting in the world of simulators it is a better choice than a more complex one as TaskSim.

### 4.1.1 Ramulator

Its installation is very straight forward and it only requires to download it from the Github page and then follow the instructions explained in the same page. The only requirement for the installation is a C++11 compiler like g++-5 or clang++<sup>1</sup>.

Once it has been downloaded, executing the usual command: "make -j " will install it. By default it will execute clang++, so if the preferred compiler is g++-5 a little change in the Makefile is needed but for the initial execution stand-alone is fine clang++.

However, if the desired usage is the third one with gem5, then it is necessary to follow some others instructions that also requires to apply a patch that Ramulator offers to Gem5. Although it does not seem very difficult, it does not suit into the goal of this TFG so this has not been tried.

<sup>&</sup>lt;sup>1</sup>g++-5 is the fifth version of G++ and clang is an alternative developed by Apple.

For testing purposes and because the simple test provided by Ramulator is very easy, some different tests have been created to observe the performance. Memory trace driven is the perfect candidate for this kind of test, hence both random and sequential memory access traces have been simulated.

These initial sequential and random traces were created using a C++ program. In the sequential trace, the memory positions of a vector traversal were printed. In the case of the random trace, several numbers were generated using a random library.

In addition, it has also been reviewed the different configuration files that Ramulator offers in order to interact a little bit with the standards and its configurations.

The results of this preliminary tests are very promising as running a 10 million memory access do not last more than 20 minutes in a laptop environment, which is incredibly fast.

Furthermore, the second task of this part is more important because for making the bridge it is required a good understanding of how the simulator works. So further reading of the simulator code and tests have been useful to understand better the simulator.

#### 4.1.2 TaskSim

Comparing to Ramulator, TaskSim is a bigger software and has a more complex installation. First, it has a copyright which means that the software is not publicly available and for this reason, a request for permissions is needed. TaskSim is maintained using a tool called RedMine [12], a flexible project management web application that in the case of TaskSim helps to group a wiki and the code repository in the same web.

For the installation of TaskSim there is a fully detailed page that explains step by step what is needed but for the first time, it is very easy to get lost. TaskSim is organized by different modules and each of them has a Makefile and finally a huge Makefile for every part. For this part, the help of the development team of TaskSim, in special mention to Francesc, has been crucial for correctly installing TaskSim.

Furthermore, TaskSim depends on other software for working like: Nanos++ [9], a runtime library designed at BSC, the compiler Mercurium [8], a source-to-source compilation infrastructure also from BSC and finally the Pin Instrumentation tools from Intel for making traces.

Therefore, the first installation is more difficult than Ramulator requiring other software to be installed and multiple configurations to manage. Also, comparing to Ramulator, first the sources are built and finally installed enabling multiple configurations but increasing its complexity.

This last feature is very useful in the usual case of having different versions of TaskSim: one for tracing, one using DramSim2, one for a special kind of trace... In this project,

five different TaskSim's have been installed: two enabling Ramulator or not, two enabling different traces (rle and uop) and finally one for tracing.

For testing purposes, it has been used traces already generated like the parsec benchmark suite [10] ported to Ompss<sup>2</sup> [22]. The first execution was the blackscholes<sup>3</sup> benchmark due to its simulation time which only takes about 45 minutes. This simulation time is much bigger compared to Ramulator and hence the laptop may suffer. For this part is just enough although for further experiments a cluster will be needed.

Executing this test has been very useful to understand how works the configuration file of TaskSim and although very simple modifications have been tested it offers multiple options.

Finally, the classes of the bridge with DramSim2 have been reviewed in order to understand the approach it has been followed and to start thinking how to do the bridge with Ramulator.

# 4.2 Other Bridges

**TaskSim bridge with DramSim2** is done by three classes: Dramsim2Controller.h, Dramsim2-Controller-impl.h and Dramsim2ControllerDefs.h. The code resides in Dramsim2Controller-impl.h file which contains the implementation of the bridge. It is quite straight forward because Dramsim2 offers the possibility to be compiled as a library.

The connection is quite simple although some difficulties may come with the callbacks of the reads and writes which must be initialized properly in order to permit DramSim2 notify when it has finished doing a read or write request. Then it is also important to deal with the types of the variables and not loose accuracy. Finally, the Dramsim2ControllerDefs.h exists in order to have a configuration by default but enabling to modify at the configuration file of TaskSim.

After some time of debugging this bridge, an improvement was made by the development team of TaskSim because some users claimed its simulation time overhead was important. The improvement consisted on making in bursts all the cycles until Dramsim2 was up to date with TaskSim. This enabled to reduce the simulation time overhead significantly.

On the other hand, the **Gem5 bridge with Ramulator** is not that easy and needs further installation steps. To begin with, the bridge with Ramulator needs to apply to Gem5 a special patch<sup>4</sup> that is given with Ramulator code. This may not be the ideal solution due to Gem5

<sup>&</sup>lt;sup>2</sup>Extension of OpenMp by BSC.

<sup>&</sup>lt;sup>3</sup>Program consisting in option pricing with Black-Scholes Partial Differential Equation (PDE).

<sup>&</sup>lt;sup>4</sup>Update of the code using a diff highly efficient.

users tend to modify the code an this patch may break some parts. Another solution could be to insert this patch inside the repository of Gem5 and have Ramulator as module.

Once the patch is applied, as ideally only creates two classes and modifies few lines, actually the size of the patch is 500 lines. Then it can be executed like # Run gem5 with –mem-type=ramulator and –ramulator-config=configs/DDR3-config.cfg. Finally, it can be seen that a configuration file must be specified and a special mem-typed is needed.

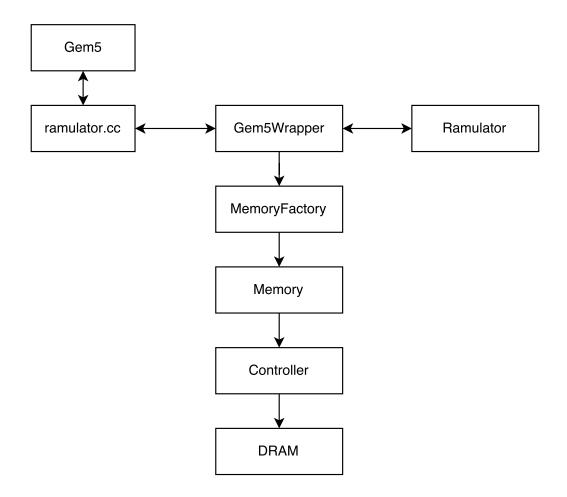

In the following figure 4.1 it is shown the software architecture of this bridge:

Fig. 4.1 Gem5 bridge with Ramulator.

Gem5Wrapper is the class that serves as middleware to use the statistics from Gem5. It also serves as a *application programming interface* (API) to use it in Gem5 in order to

make memory requests. It communicates with Gem5 through a class called *Ramulator* inside Gem5 that its only function is to call Gem5wrapper.

Then, inside the Ramulator code base there is MemoryFactory which helps in the task of further bridges and it is used by Gem5Wrapper to create the Memory. It also checks the parameters of the Ramulator configuration file that passes Gem5 makes sense before proceeding.

MemoryFactory creates an instance of Memory which only needs a configuration file and a vector of Controllers of the selected DRAM already created. This class is incredible useful for the bridge with TaskSim and it will be used because it allows to create automatically the memory.

As it can be seen, this bridge is different than the one of TaskSim with Dramsim2 because Ramulator team has made the bridge but does not participate in the design of Gem5. This is the opposite approach as in TaskSim with DramSim2 although it is very useful as it offers the special class MemoryFactory which facilitates any future bridge.

# 4.3 Bridge TaskSim-Ramulator

The first problem found was the version of g++ needed by Ramulator. The version used in TaskSim by default is 4.7 whereas the minimum needed in Ramulator is at 5.0 which created a conflict. The only possible solution was to fixed the problems that may have TaskSim to compile with the version 5 and hopefully were not much. The only errors found were related to syntax changes of some C++ libraries like String.

Having seen both bridges, the selected software architecture was inspired by both and the next figure 4.2 shows the general idea of the bridge.

Fig. 4.2 TaskSim bridge with Ramulator.

The main difference between the bridge of Ramulator with Gem5 is that although RamulatorController is inside TaskSim it does not use Gem5Wrapper and it uses directly the MemoryFactory class. This is necessary due to the dependencies of Gem5Wrapper and also because it allows to not depend on an API that may change.

Another big difference is the decision of not using a separate configuration file than the one that uses TaskSim. This is for simplicity for the user and because it is not difficult to do.

The main idea is that the user will put inside the TaskSim configuration file a module called RAMULATOR and then specify the standard, channels, ranks that characterize the simulated technology.

The only difference between this configuration and the one that uses Ramulator is that in this case the user must specify the path where Ramulator statistics will be saved because they are not integrated inside TaskSim ones. This is another decision and it is done in this way because depending on the configuration the statistics file from Ramulator can be bigger than 200 lines and it is not viable to print it in the terminal.

#### [RAMULATOR]

```

full-path = / path / to / write / statistics

standard = HBM

channels = 8

ranks = 1

speed = HBM_1Gbps

org = HBM_4Gb

```

On the other hand, this architecture is similar to the bridge with Dramsim2 because some parts can be applied similarly. In the opposite side, the main difference is in the building: Dramsim2 offers a library which facilitates the process of linking and building whereas Ramulator does not have this feature which has made to include all the possible files in the corresponding Makefile of the memory module which ends in a slightly more time of compilation.

Furthermore, some Makefiles have been modified in order to enable some new flags to compile TaskSim with Ramulator. For enable Ramulator, the flag –enable-ramulator must be indicated and the source where is installed Ramulator: –with-ramulator-src-path=path.

Finally the bridge consists in three new classes:

- **RamulatorController.h**: This class contains the headers of the private functions and is mandatory for the connection with TaskSim.

- **RamulatorController-impl.h** : Here is where the code resides and the definition of each function is given. Here is the part that depends on Ramulator code as includes functions of MemoryFactory.h class.

- **RamulatorControllerDefs.h** : This class is a default configuration class in order to have some default in case the user only wants to try if it works.

| Standard | Channels | Ranks | Speed      | Org         |

|----------|----------|-------|------------|-------------|

| DDR4     | 1        | 1     | DDR4_2400R | DDR4_4Gb_x8 |

The selected configuration by default is summarized in the following table 4.1:

| Table 4.1 Default configu | ration. |

|---------------------------|---------|

|---------------------------|---------|

The same improvement done in Dramsim2 to reach a better performance has been preserved in this bridge. When Ramulator is needed, it does not wake up for only one cycle as it tries to do as much as it can in one burst of cycles.

In Dramsim2 some statistics were included in TaskSim but in this case, the decision was not to include them as it did not provide any more information than Ramulator's statistics.

### 4.4 Debug and firsts tests

In order to try for the first time the bridge some synthetics simple tests were required. The first synthetic was a for loop of 10 iterations that traverse a vector for making only reads. This test was rapid enough for making the simulation and see the firsts errors. The configuration was no relevant so the default was good enough.

Moreover, the next logically test was making writes and several approaches were tried. The difficulty came with default configuration of TaskSim which have a last level cache of 20MB and filtered all the memory requests. The intrinsic problem was having a cache with a write-back policy which required to have more request than 20MB. The useful approach was to reduce the capacity of the last level cache which enabled to find a severe bug explained in the next section.

Then, the next step was to increase the number of iterations of both tests to see if any error occurs. It did not happen so we conclude this part in order to continue to the validation of the bridge.

# 4.5 Bugs found

During the development of the bridge some bugs have been found. First of all, in TaskSim documentation there were several little mistakes that were fixed in order to be more friendly for new users or to clarify some miss-interpretations.

TaskSim also had a problem with sending the CPU  $ID^5$  of a request. This CPU ID is very useful for Ramulator statistics. Some changes were done by the development team

<sup>&</sup>lt;sup>5</sup>This ID corresponds to the core in a multicore-processor that issue the memory request.

of TaskSim in order to enable the delivery CPU ID of the issuer of a memory request to Ramulator. However, when the type of Cache is Writeback the actual issuer of a write request to the memory is the cache itself and the solution proposed was to send a -1 in the issuer to mark as write from cache. Then in the statistics one core will be added in order to track these requests.

On the other hand, a major bug was found in Ramulator when the writes were tried. Any write to Ramulator did not send its correct callback although it had finished properly. The little mistake created a middle bottleneck in the development of the project because in the best case scenario it finished in a stack overflow but in the worst case it halted the simulation.

At the time it was found in this project, this bug had already been reported by another person and the solution proposed was indeed similar to the one proposed in this project. In addition to this problem, which affected nearly all the standards of memory, it was noticed that this bug will affect on some academics standards like SALP [29] so it was reported on GitHub.

Finally, the developers respond to both pull requests<sup>6</sup> but no fixing has been made to this date which means that error stills in the public code on GitHub.

<sup>&</sup>lt;sup>6</sup>Request to modify the code on GitHub with the supervision of the authors, very common in open source projects.

# Chapter 5

# **Experimental Setup and Validation of the Bridge**

In this chapter, the hardware and software setup used for the following experiments is explained. Then, the applications that will be used are introduced and finally the configuration of the processors and DRAM used in the simulations.

# 5.1 Hardware and Software

First of all, the experiments will be executed on three different machines: personal laptop, cluster Arvei and MareNostrum, each of them for a purpose explained below.

- A personal laptop will be used for the first testing and validation. It is a Dell XPS 13 (year 2013) sufficiently powerful to execute little tests, code and make charts:

- CPU: Intel(R) Core(TM) i7-4500U 1.80GHz 2 cores

- RAM: DDR3 8 GB 1600 MHz

- Arvei is a cluster of the Department of Computer Architecture (DAC) at UPC focused on research. It is composed of different configurations starting from 2006 until 2016 and the newer server that can be used has:

- CPU: 2x Intel(R) Xeon E5-2630L v3 1.80 GHz 8 cores

- RAM: 128 GB

- MareNostrum is the most powerful supercomputer in Spain and one of the most powerful in Europe. Actually, during 2017 it is planned to have its 4th upgrade and achieve a better position in the TOP 500<sup>1</sup>. The current nodes are composed by:

- CPU: Intel Xeon CPU E5-2670 2.60GHz 8 cores

- RAM: 32 GB

Arvei cluster is specifically oriented to the collaborative work of the research groups at DAC. Hence, the waiting time for running a job at this cluster is not high which permits doing the experiments here. Nonetheless, this cluster does not allow to lock a node for only one user and execute different scripts in furtherance of giving the maximum resources for a simulation.

In the following chapters it will be seen that an interesting metric of the bridge done in the project will be a study of simulation time overhead that is added using the bridge versus not. For this kind of study, it will be required to lock the node for only the simulation to not being affected by others jobs.

Conversely to Arvei, MareNostrum allows to reserve the node for only one user and hence permits the analysis of simulation time overhead. However, this machine is highly used compared to Arvei by a lot of national and international researchers which may add some waiting time to this analysis.

On the other hand, the strictly required software that will be used for the experiments will consist of:

- TaskSim: CPU simulator.

- Ramulator: DRAM simulator.

- G++: v5.1 in personal laptop and MareNostrum but v6.0 in Arvei.

- Matplotlib: library in Python for making charts.

# 5.2 Applications

In order to make an interesting analysis and validate the bridge two different sets of programs (benchmarks) have been used. First of all, a benchmark suit has been used, the PARSEC suite which is ideal for parallel simulations because it has been designed for today's and future real world applications.

<sup>&</sup>lt;sup>1</sup>TOP 500 is the list of 500 most powerful supercomputers in the world.

However, this kind of suites have some limitations like being quite huge and difficult to change, so for this reason it also has been used three synthetics benchmarks for testing some rare cases and for debugging. Finally, it has also been added the benchmark SpecFem3D.

### 5.2.1 PARSEC Benchmarks and SpecFem3D

This suite was created as a reference for parallel simulations because it offers 13 programs from many different areas like computer vision, video encoding, financial analytics, animation physics and image processing.

One of the common features of benchmarks suites is having different inputs sets and Parsec suite offers four inputs for simulation: simdev, simsmall, simmedium and simlarge. It also offers a native input designed for native execution. The selected input used in this project will be simlarge.

Luckily eight out of thirteen applications have already been ported to OmpSs for enabling its simulation in TaskSim by the research group of RoMoL: blackscholes, body-track, canneal, dedup, ferret, fluidanimate, swaptions and x264. For this project, although all applications have been simulated, only three of them are sufficiently memory intensive for being useful for the analysis.

The most interesting applications have been facesim, canneal and ferret. They are quite diverse because while facesim simulates the motions of a human face, canneal simulates cache-aware annealing to optimize routing cost of a chip design and ferret calculates the similarity of generic data specially useful for search servers.

On the other hand, SpecFem3D [14], as they authors state, simulates seismic wave propagation in any type of conforming mesh of hexahedra (structured or not). An example of this could be simulating earthquakes or ocean acoustics. This benchmark has also been ported to OmpSs by the research group of RoMoL.

### 5.2.2 Synthetic Benchmarks

The PARSEC suite has showed some limitations like a big simulation time and low MPKI<sup>2</sup> for the next analysis. Therefore, two synthetics benchmarks were created to debug: stores and loads. As their name show, each program consists on a loop doing loads or stores. This program has been very useful for debugging purposes and the loads benchmark also has been used for the analysis and validation of the bridge.

Furthermore, a well-known memory intensive synthetic benchmark has also been used: the Stream [15]. Stream is a simple synthetic benchmark that measures memory bandwidth

<sup>&</sup>lt;sup>2</sup>Misses per Kilo Instruction, a good metric for memory intensive applications.

(in MB/s) and it is usually used to measure the bandwidth of a system. In order to be included in the study we have ported it to OMPSS. In contrast to the original, it has also been vectorized to increase its MPKI.

# 5.3 Simulation configurations

### **5.3.1** CPU configuration

In furtherance of the realism of the simulations, three different CPU configurations have been used in TaskSim. They fit to the server, the laptop and the mobile sectors showing good variations in the end. These three configurations have resulted in three CPU configurations files for TaskSim similar to the one in appendix A.

The configurations are explained and table  $5.1^3$  summarizes its main characteristics.

- **marenostrum** CPU: similar to an Intel Xeon with three-level cache hierarchy with the last level reduced in order to beneficially get more misses in pursuance of putting more pressure to the DRAM subsystem.

- **i7** CPU: similar to an Intel i7 that can be found in laptops with also a three-level cache hierarchy.

- **arm** CPU: similar to an ARM Cortex-A57 included in the Qualcomm Snapdragon 810 with a two-level cache hierarchy.

|       | marenostrum | i7    | arm  |

|-------|-------------|-------|------|

| Cores | 8           | 4     | 2    |

| L1    | 32KB        | 32KB  | 32KB |

| L2    | 256KB       | 256KB | 1MB  |

| L3    | 10MB        | 8MB   |      |

| Table 5.1 CPU | configurations. |

|---------------|-----------------|

|---------------|-----------------|

The three sectors are investing in multicore architecture and the trend is going to continue in the near future. Moreover, one of the most promising is the mobile sector with its manycore architecture. Manycore architecture helps to reduce the energy consumption providing different cores designed at a different frequency changing dynamically depending on the load.

<sup>&</sup>lt;sup>3</sup>For marenostrum and i7 configurations, L1 and L2 are private for each core and L3 is shared whereas in arm configuration L1 is private to each core and L2 shared.

### 5.3.2 DRAM configuration

This is one of the critical parts of the study. Without properly equally configurations, the results could be misleading. Although the last statement is true, depending on the type of analysis different configurations can be great at the same time. This is why it has selected a basic configuration similar to the one used in the paper of Ramulator [30] which for a start is good enough.

The selected standards for the study are the most used in the industry nowadays: DDR4 [5], LPDDR4 [2] and GDDR5 [3]. It has also been added HBM [4] to the study due to its promising performance.

| Standard | Rate   | Timing      | Channels | Width    | BW     | # Bank width      |  |

|----------|--------|-------------|----------|----------|--------|-------------------|--|

| Stanuaru | (MT/s) | (CL-RCD-RP) | Channels | Channel  | (GB/s) | $\pi$ Dalik width |  |

| DDR4     | 2400   | 16-16-16    | 2/4      | 64 bits  | 38.4   | x16               |  |

| LPDDR4   | 2400   | 22-22-22    | 2/4      | 32 bits  | 19.2   | x16               |  |

| GDDR5    | 6000   | 18-18-18    | 2/4      | 64 bits  | 96.0   | x16               |  |

| HBM      | 1000   | 7-7-7       | 8        | 128 bits | 128.0  | x1024             |  |

Table 5.2 DRAM relevant characteristics.

This table shows the most relevant characteristics that are looked when comparing DRAM's [28]:

- Rate is the usual metric corresponding to the number of operations transferring data per second. In this case, MegaTransfers per second which in DDR memories is the double of the frequency.

- Timing englobes three of the most important DRAM timing parameters:

- CL: It is also referred as CAS and corresponds to the time interval between sending a column address to the memory and the start of data return by the DRAM device.

- RCD: Time interval from the row access until the data is ready at the sense amplifiers before issuing a column delay.

- RP: Time interval of precharging a DRAM array for another row access.

- Despite HBM that only allows 8 channels, the other configurations permit to modify and hence two sets of channels have been tried: 2 and 4.

- Channel width is a characteristic defined by JEDEC and this can not be modified for the selected standards. It represents the amount of bits that are read each from the bank each time.

- Bandwidth (BW) is the maximum theoretical data rate that can be achieved with the selected configuration. Is has been calculated with:

BW(GB/s) = Rate (MT/s)

$$*1 \times 10^6$$

\* channel width \* #channels \*  $\frac{1 \text{ byte}}{8 \text{ bits}}$

• The bank width is also determined by the JEDEC standard and depends on the organization selected.

| Standard | Channels | Ranks | BankGroups | Banks | Rows   | Columns | Page size | Capacity |

|----------|----------|-------|------------|-------|--------|---------|-----------|----------|

| DDR4     | 2        | 1     | 4          | 16    | 65536  | 2^10    | 2 KB      | 8 GB     |

| DDR4     | 4        | 1     | 8          | 32    | 131072 | 2^10    | 2 KB      | 16 GB    |

| LPDDR4   | 2        | 1     | None       | 16    | 32768  | 2^10    | 2 KB      | 4 GB     |

| LPDDR4   | 4        | 1     | None       | 32    | 65536  | 2^10    | 2 KB      | 8 GB     |

| GDDR5    | 2        | 1     | 8          | 32    | 32768  | 2^7     | 2 KB      | 8 GB     |

| GDDR5    | 4        | 1     | 16         | 64    | 65536  | 2^7     | 2 KB      | 16 GB    |

| HBM      | 8        | 1     | 32         | 128   | 131072 | 2^7     | 2 KB      | 4 GB     |

Table 5.3 DRAM technical characteristics.

Conversely, this table 5.3 shows the technical characteristics of each configuration. All of these characteristics can be checked at each corresponding JEDEC and Ramulator uses the same.

Although the ranks could be a great study, for starters it has been set to one. The rest of the characteristics can not be changed without changing the organization.

Eventually we have used a total of nine DRAM configurations: seven of them are used with Ramulator and the last two using a memory model inside TaskSim:

- TaskSim memory by default which has a constant latency of 200 ns for each memory request useful for measuring the actual improvement of realism with Ramulator.

- Perfect memory configuration consisting on the ideal of 1 cycle per request useful for an upper bound of the benefits that memory technologies can provide.

# 5.4 Validation

In this section, the process of validation of the bridge is described. First of all, it is described the initial tests for validating the number of misses that arrived to Ramulator. Finally, a timing overhead analysis of the bridge is done.

### 5.4.1 Verification of the requests

The main fear in a bridge is breaking one of both simulators. This is why it has been payed attention to this case. To start with, a test has been created to check if all the requests sent by TaskSim arrives to Ramulator. This test is a Python script which makes a comparison of two greps<sup>4</sup>: one for the TaskSim statistics file and the other for the Ramulator statistics file.

This script is, on one side, very useful to check if any simulation has not ended correctly which eventually may happen and on the other hand, to check whether the bridge is not working properly.

Furthermore, in order to track all the misses through the memory hierarchy and finally expect a determined amount of memory requests has been impossible in the Parsec benchmark suite. Adding to this, the simulation time of these benchmarks is not acceptable for debugging and validation purposes in early stages.

All of this has encouraged creating special benchmarks for testing little cases. The first and most useful test has been a simple loop that only makes loads which results in a sum of a vector. If the size of the vector is known and can be modified, a study of different sizes can be sufficient to determine if the bridge is obtaining the expected amount of memory requests.

The following code shows the above mentioned loop.

```

#define SIZE 1024*1024*16

....

double *v = malloc(sizeof(double)*SIZE);

for(i=0; i<SIZE; i+=BSIZE) {

suma += v[i+ii];

}</pre>

```

<sup>&</sup>lt;sup>4</sup>Grep is a program in linux environments very useful to find strings in files.

Although by hand we can calculate the amount of misses that should happen, some more misses could be produced on account of run-time behavior. However, TaskSim offers the feature of only simulating the main thread which results in not having a big deviation of the calculated misses with the simulated misses. In the next table 5.4 it can be summarized.

| Vector Elements    | 64K   | 128K  | 256K  | 512K  | 1M     | 2M     | 4M     |