# On the design of high-efficiency RF Doherty power amplifiers

Mehran Yahyavi

Thesis advisor: Dr. Eduard Bertran Alberti

DOCTORATE PROGRAM IN SIGNAL THEORY AND COMMUNICATIONS (TSC) TECHNICAL UNIVERSITY OF CATALONIA (UPC)

BARCELONATECH, CAMPUS NORD

This research was partially supported by the Spanish Ministry of Economy and Competitiveness (MINECO) under project TEC2014-58341-C4-3-R and by the Secretary for Universities and Research of the Government of Catalonia, under grant 014 SGR 1103.

# **Table of Contents**

| List of FiguresV                                          |

|-----------------------------------------------------------|

| List of TablesIX                                          |

| NomenclatureX                                             |

| AbstractXI                                                |

| Chapter 11                                                |

| 1 Introduction                                            |

| 1.1 Motivation and statement of the problem               |

| 1.2 Compromise between linearity and efficiency           |

| 1.2.1 Linearity                                           |

| 1.2.2 Power efficiency11                                  |

| 1.3 Load modulation                                       |

| 1.4 Doherty Power Amplifiers (DPAs)                       |

| 1.4.1 Fundamentals of the DPA                             |

| 1.4.2 Asymmetrical power splitting                        |

| 1.5 An overview of the rest of the thesis                 |

| List of published papers on this research                 |

| Chapter 2                                                 |

| 2 State of the art in DPAs                                |

| 2.1 Introduction                                          |

| 2.2 Technologies and applications related to DPAs         |

| 2.3 Trends on increasing efficiency and linearity of DPAs |

| 2.3.1 Enlarging output back-off (OBO) 46                  |

| 2.3.2 Uneven power driving and asymmetrical devices       |

| 2.3.3 Optimizing output combiner                          |

| 2.3.4 Other techniques                                    |

| 2.4 Broadband techniques 50                               |

| 2.4.1 Optimizing the matching networks                    |

| 2.5    | Lo   | ad modulation in DPAs                               | 55  |

|--------|------|-----------------------------------------------------|-----|

| Chapte | er 3 |                                                     |     |

| 3 De   | sign | of DPAs                                             | 59  |

| 3.1    | Ma   | ain aspects in the design of DPAs                   | 60  |

| 3.     | 1.1  | Load-pull and source-pull                           |     |

| 3.     | 1.2  | Bias network                                        |     |

| 3.     | 1.3  | Stability                                           |     |

| 3.2    | Be   | ginning of the work                                 |     |

| 3.3    | De   | esign and fabricate a DPA with a tapered line       | 69  |

| 3.     | 3.1  | Design rules                                        |     |

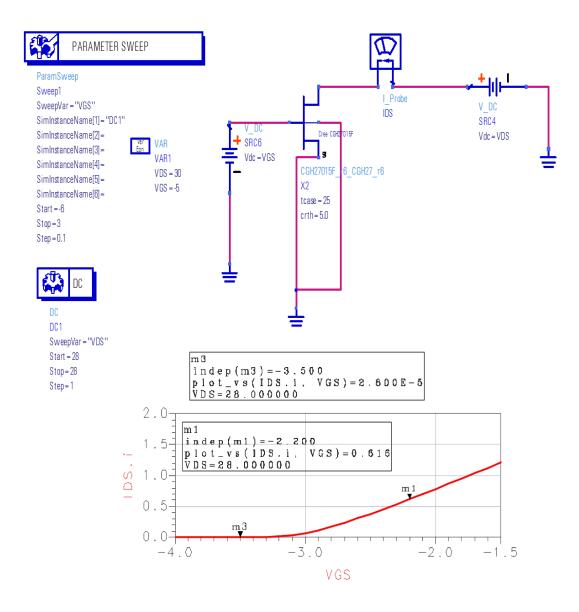

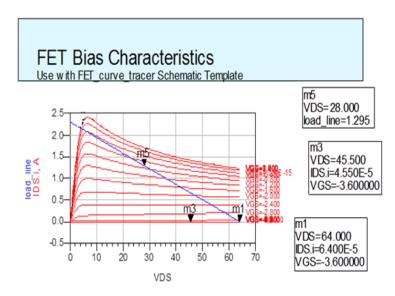

| 3.     | 3.2  | DC analysis                                         | 71  |

| 3.     | 3.3  | Biasing network                                     |     |

| 3.     | 3.4  | Stability of DPA                                    |     |

| 3.     | 3.5  | Matching networks                                   | 77  |

| 3.     | 3.6  | Simulation and experimental results                 |     |

| Cha    | pter | 4                                                   | 89  |

| 4 Do   | hert | y-like architecture using a mixed combining network |     |

| 4.1    | Int  | roduction                                           |     |

| 4.2    | De   | sign approach                                       |     |

| 4.3    | Ex   | perimental results                                  |     |

| 5 Co   | nclu | sions and proposals for the future works            |     |

| 5.1    | Co   | onclusions                                          |     |

| 5.2    | Fu   | ture works                                          |     |

| Refere | nces |                                                     | 110 |

# List of Figures

| Figure 1.1 Basic structure of a classical FB                                                       | . 9 |

|----------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 FF simplified block diagram and principles of operation                                 | 10  |

| Figure 1.3 Schematic diagram of class- E amplifier                                                 | 13  |

| Figure 1.4 Schematic diagram of class-F amplifier [48]                                             | 14  |

| Figure 1.5 EER circuit design                                                                      | 15  |

| Figure 1.6 Challenges in practical implementation of EER systems                                   | 15  |

| Figure 1.7 ET technique                                                                            | 16  |

| Figure 1.8 Chireix technique                                                                       | 17  |

| Figure 1.9 DPA technique                                                                           | 18  |

| Figure 1.10 Ideal dc load line for the calculation of optimum load                                 | 19  |

| Figure 1.11 The performance of load curves in load modulation                                      | 20  |

| Figure 1.12 A simple schematic of load modulation [76]                                             | 22  |

| Figure 1.13 Simplified schematic of the Doherty amplifier [76]                                     | 23  |

| Figure 1.14 Quarter-wave transformer line as impedance inverter                                    | 23  |

| Figure 1.15 Typical Doherty amplifier structure                                                    | 24  |

| Figure 1.16 Evolution of the load curves for both DPA active devices: main (left) and peaking      |     |

| (right) amplifiers [77]                                                                            | 25  |

| Figure 1.17 Typical DPA efficiency behavior versus input power [77]                                | 26  |

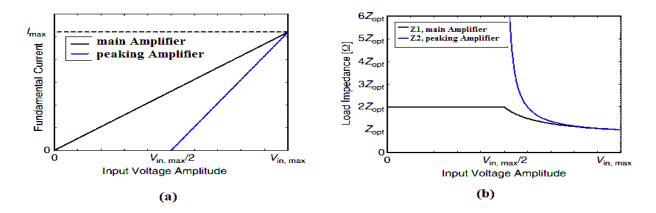

| Figure 1.18 Fundamental currents versus input voltage (a), Load impedances versus input drive      | ;   |

| (b) in DPAs [78]                                                                                   | 27  |

| Figure 1.19 Schematic of DPA performance based on changing the load impedances of the mai          | n   |

| and peaking amplifiers in low (a) and high (b) power region                                        | 28  |

| Figure 1.20 Plot of efficiencies versus the input drive level for the Doherty amplifier and the    |     |

| class AB amplifier [78]                                                                            | 29  |

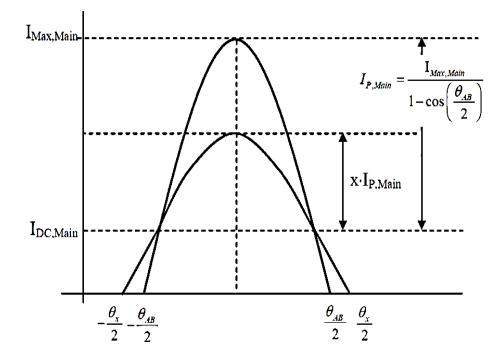

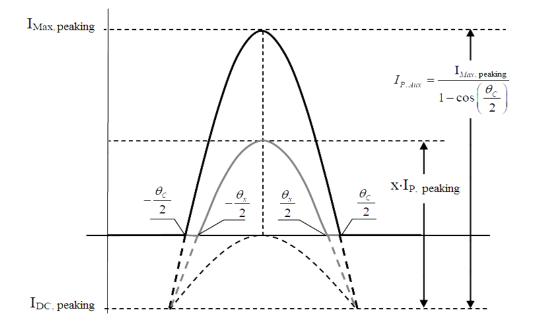

| Figure 1.21 Current waveform in time domain of the main amplifier [79]                             | 32  |

| Figure 1.22 Current waveform in time domain of the Auxiliary amplifier for $x=x_{break}$ and $x=1$ |     |

| [79]                                                                                               | 34  |

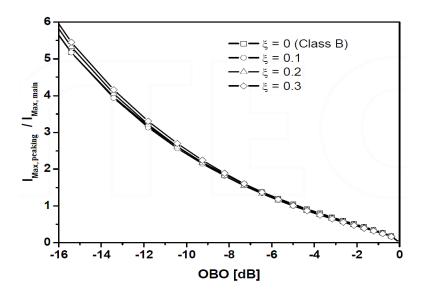

| Figure 1.23 Ratio between Auxiliary and Main maximum currents as function of OBO and $\xi$         |     |

| [80]                                                                                               | 35  |

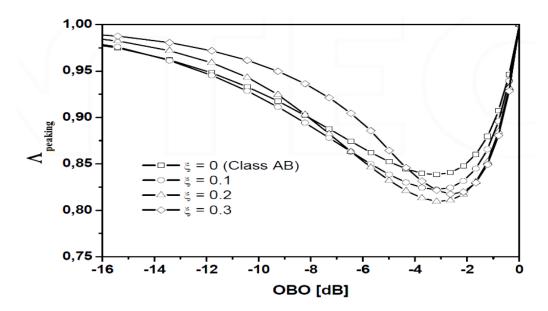

| Figure 1.24 Apeaking behavior as a function of OBO and $\xi$ , assuming for both devices the same  | ne  |

| values for g <sub>m</sub> and R <sub>in</sub> [80]                                                 |     |

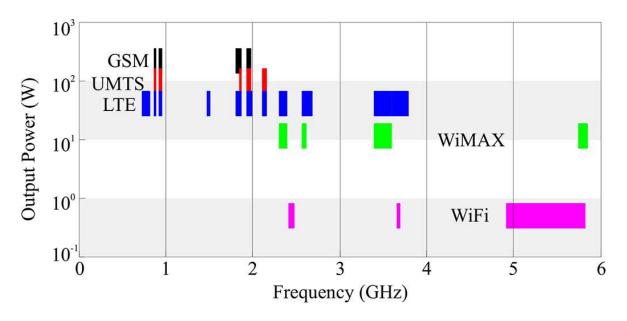

| Figure 2.1 Output power levels besides the used frequency band of wireless services [82]           | 41  |

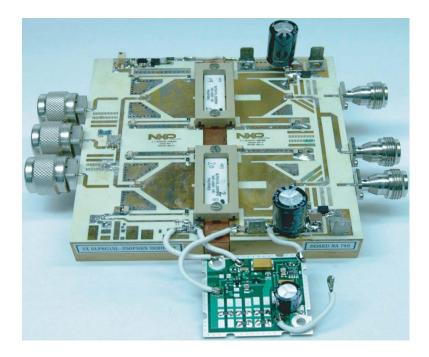

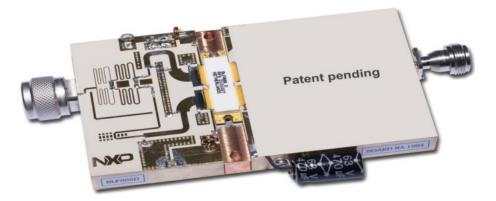

| Figure 2.2 Photograph of the BLF6G15L-250PBRN Doherty power amplifier [85]                         | 43  |

| Figure 2.3 Ultra-Wideband Doherty Amplifier announced in [86]                                      | 43  |

| Figure 2.4 Doherty amplifier designed for 710 MHz [87]                                          | 44    |

|-------------------------------------------------------------------------------------------------|-------|

| Figure 2.5 Cellular power amplifier reference design in [88]                                    | 44    |

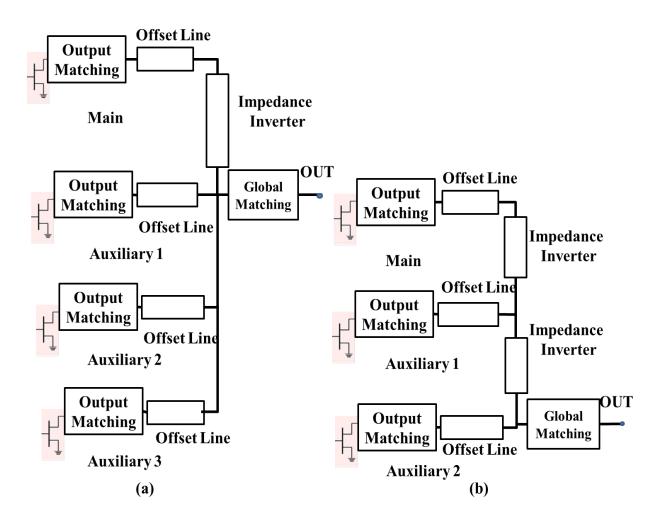

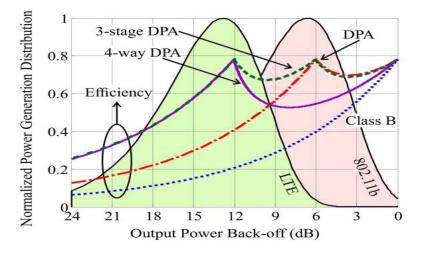

| Figure 2.6 Multiway asymmetrical DPA (a), and multi-stage DPA (b) [82]                          |       |

| Figure 2.7 Normalized efficiency of class B and Doherty PAs (standard, 4-way and 3-stage)       |       |

| versus normalized output power over-imposed to examples of normalized power distributions       |       |

| modulated signals for wireless applications [82]                                                |       |

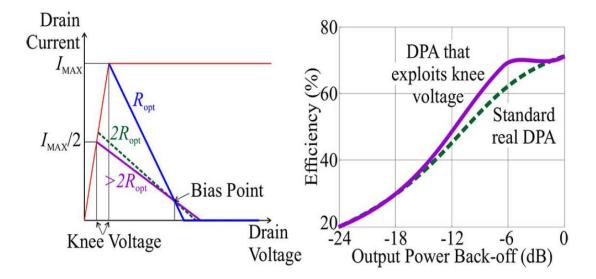

| Figure 2.8 Larger back-off impedance for efficiency maximization [95], [96]. Dynamic load       |       |

| lines of the main device at saturation and back-off (left). Typical efficiency improvement (rig | ,ht). |

|                                                                                                 | 49    |

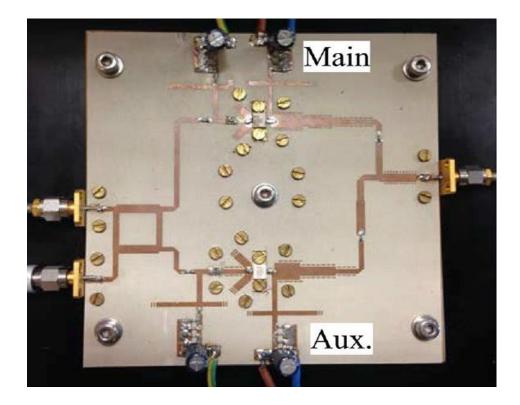

| Figure 2.9 Fabricated DPA using a 20 W GaN-based 3–3.6 GHz [106]                                |       |

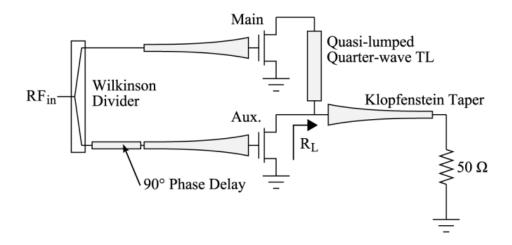

| Figure 2.10 The scheme of the proposed DPA by using quasi-lumped quarter-wave transmiss         | ion   |

| line in load modulation [107]                                                                   |       |

| Figure 2.11 Typical schematic of digital DPAs [82]                                              | 54    |

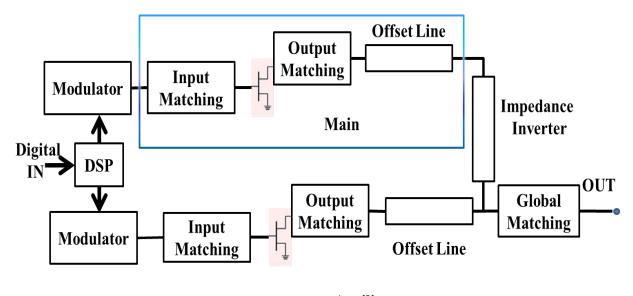

| Figure 2.12 The scheme of the proposed DPA by using the impedance transformer type in loa       |       |

| modulation [113]                                                                                | 56    |

| Figure 2.13 The scheme of the proposed DPA by using the impedance transformer type in loa       | ad    |

| modulation [120]                                                                                | 57    |

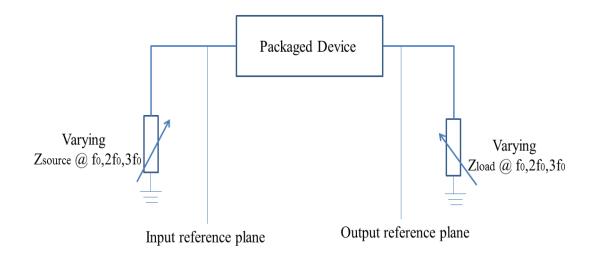

| Figure 3.1 A simplified load and source pull setup                                              | 61    |

| Figure 3.2 The simulated fundamental load-pull contours of a 10 W GaN device at 2 GHz           |       |

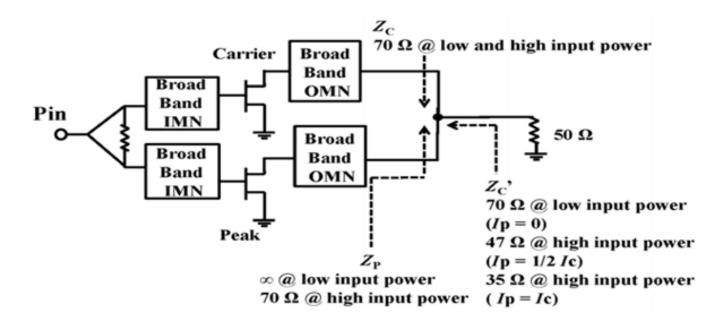

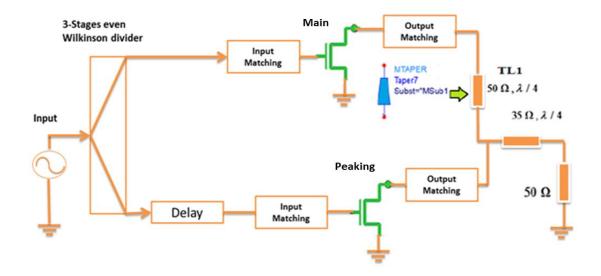

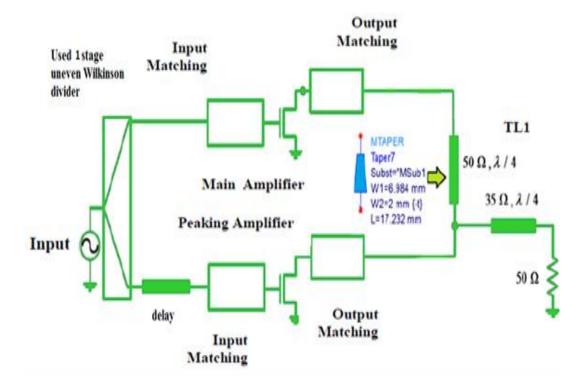

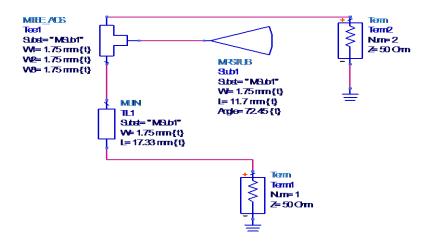

| Figure 3.3 The first proposed DPA by using a tapered line as impedance inverter                 | 64    |

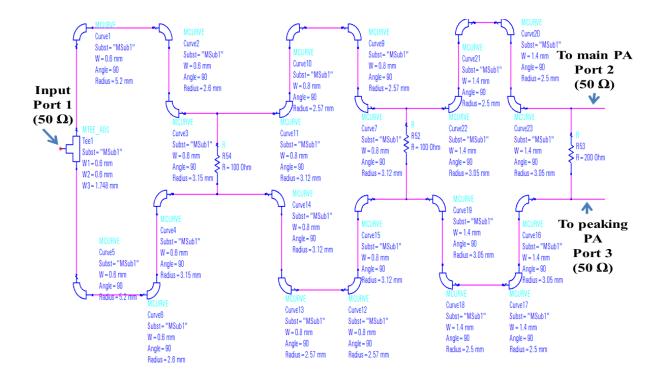

| Figure 3.4 The used 3-stages even Wilkinson divider in designed DPAs (with tapered line (W      |       |

| and without tapered line (WO-T))                                                                | 65    |

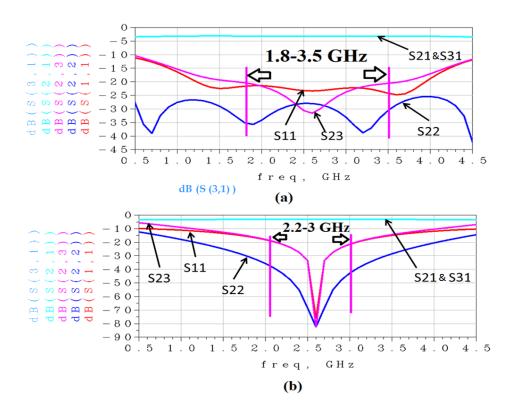

| Figure 3.5 The performance of 3-stages even Wilkinson divider (a) and 1-stage even Wilkins      | on    |

| divider (b)                                                                                     |       |

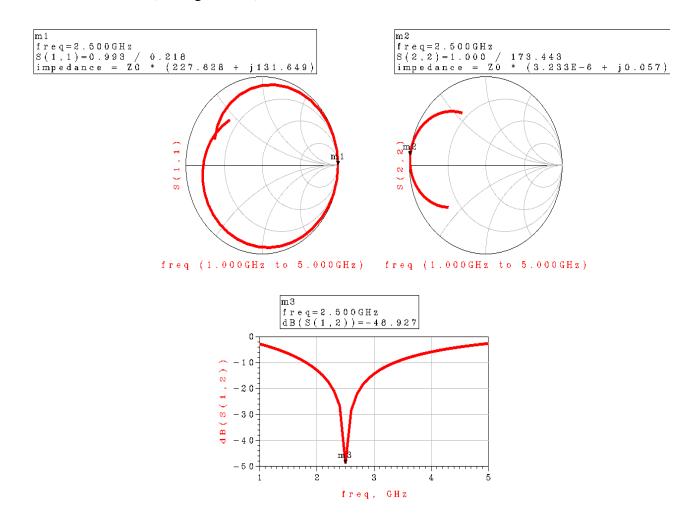

| Figure 3.6 Scattering parameters of DPA: (a) without tapered line and (b) with tapered line at  |       |

| 2.6GHz                                                                                          | 66    |

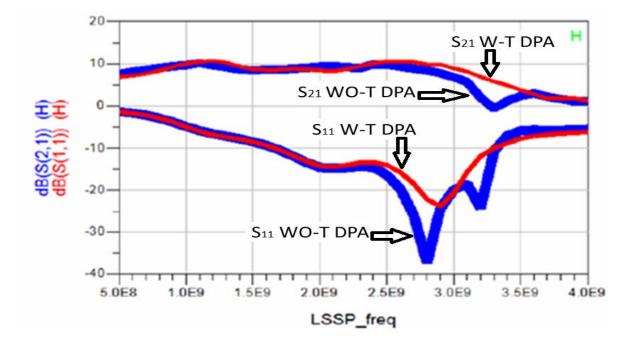

| Figure 3.7 Large-signal S-parameters of DPA: in WO-T and in W-T at 35dBm output power           | 67    |

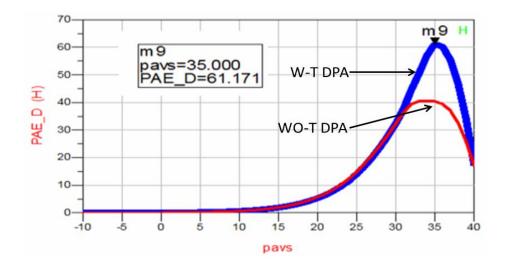

| Figure 3.8 PAE in: WO-T DPA (red line) and W-T DPA (blue line), at 2.6GHz                       | 68    |

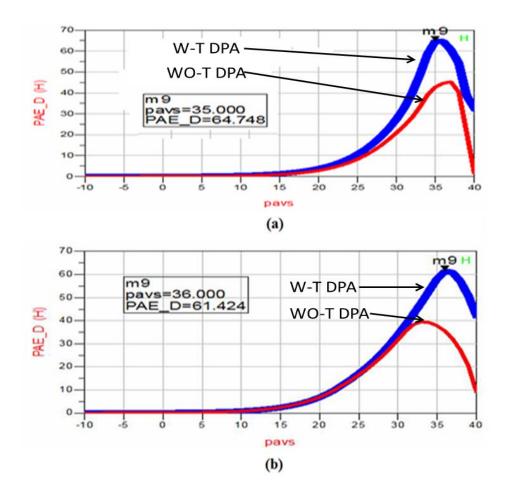

| Figure 3.9 PAE in: (a) WO-T DPA (red line) at 1.6 GHz, (b) W-T DPA (blue line), at 3 GHz        | 68    |

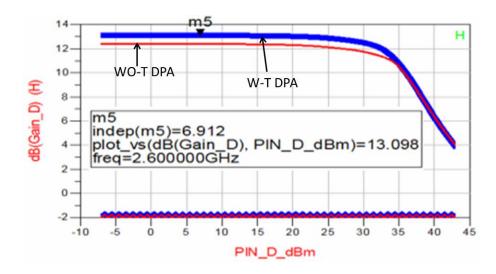

| Figure 3.10 Gain versus input power in: WO-T (red line), W-T DPA (blue line)                    | 69    |

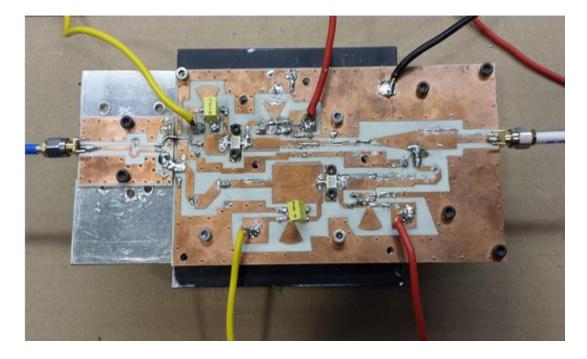

| Figure 3.11 The PCB of proposed DPA with tapered line                                           | 70    |

| Figure 3.12 Proposed DPA by using a tapered line as impedance inverter                          | 71    |

| Figure 3.13 Transfer Characteristics of CGH27015F                                               | 72    |

| Figure 3.14 Output Characteristics of CGH27015F                                                 | 73    |

| Figure 3.15 Biasing network in proposed DPA                                                     | 73    |

| Figure 3.16 Performance of used biasing network                                                 | 74    |

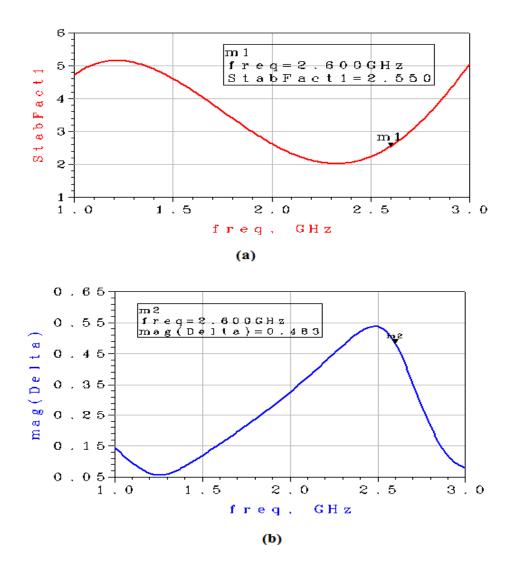

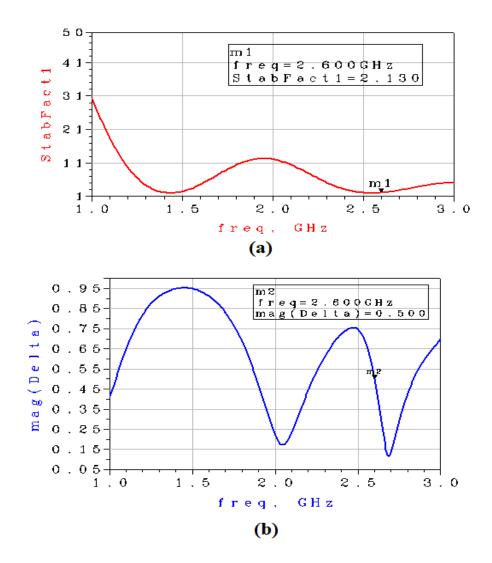

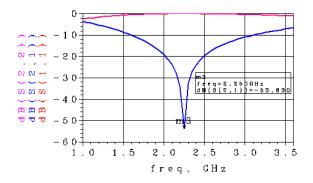

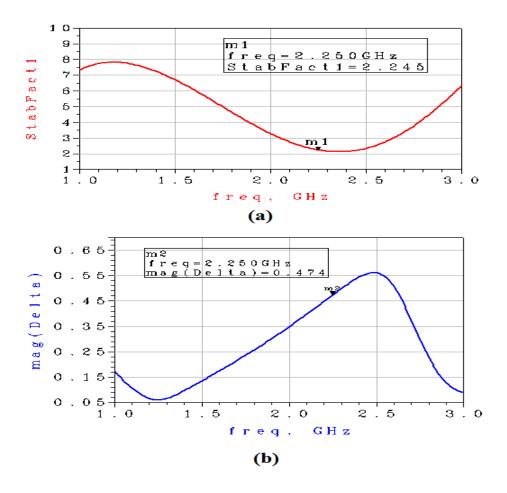

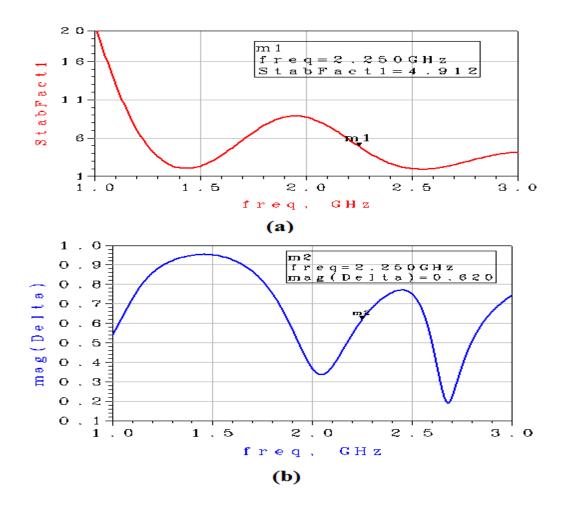

| Figure 3.17 Stability in Circuit of Class AB (Stab factor (a) and Delta (b))                    | 75    |

| Figure 3.18 Stability in Circuit of Class C (Stab factor (a) and Delta (b))                     | 76    |

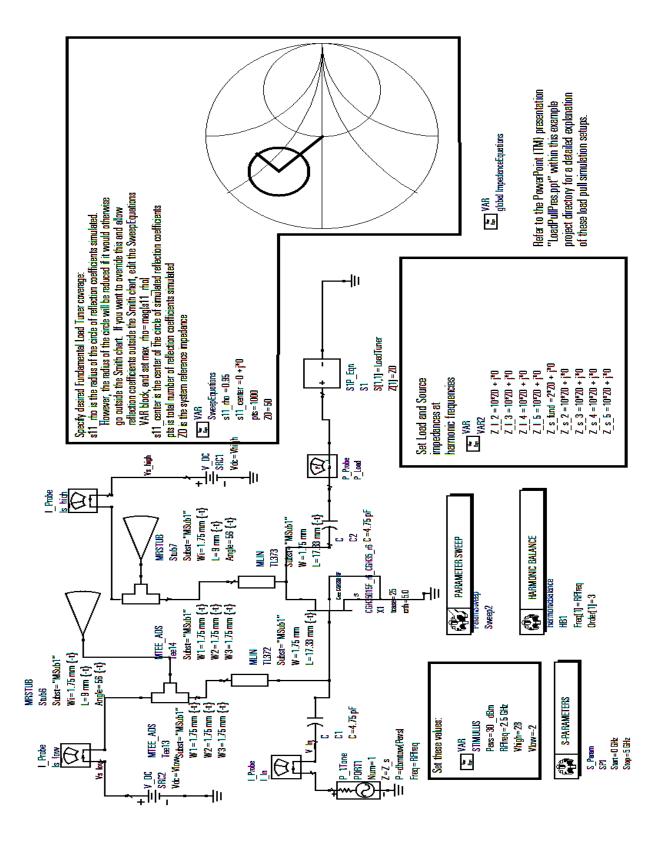

| Figure 3.19 Circuit of design guide HB1Tone_LoadPull for 1-tone analysis in both amplifiers     | 5     |

| with difference biasing voltages                                                                | 78    |

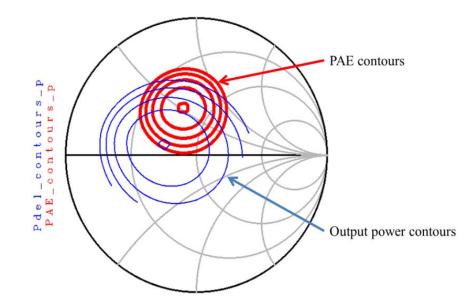

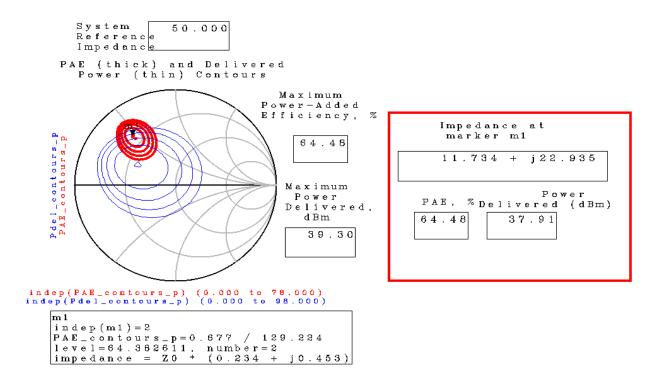

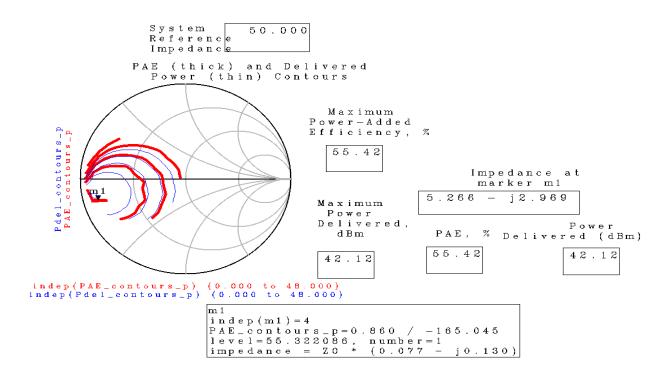

| Figure 3.20 Resulting PAE and delivered power contours drawn in the Smith Chart in main                          |

|------------------------------------------------------------------------------------------------------------------|

| amplifier for load pull analysis                                                                                 |

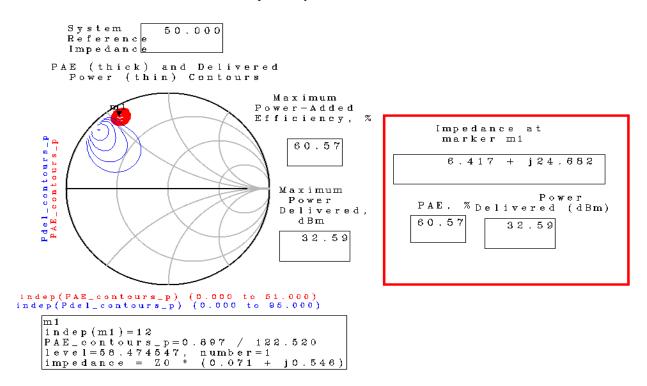

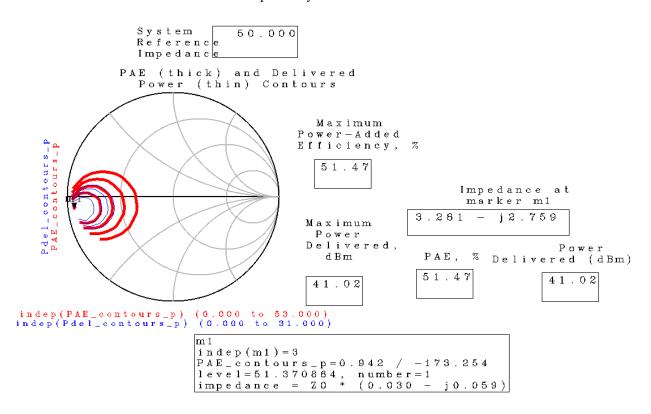

| Figure 3.21 Resulting PAE and delivered power contours drawn in the Smith Chart in peaking                       |

| amplifier for load pull analysis                                                                                 |

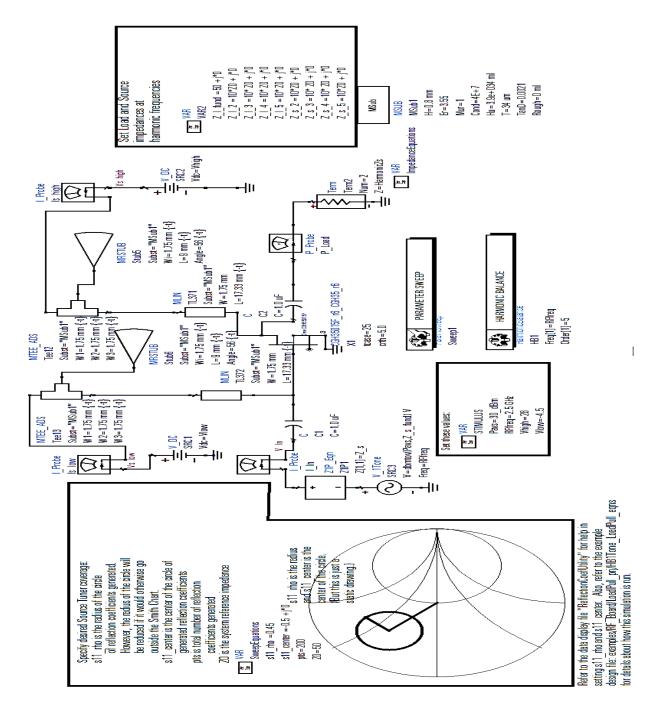

| Figure 3.22 Circuit of design guide HB1Tone_Source Pull for 1-tone analysis in both amplifiers                   |

| with difference biasing voltages                                                                                 |

| Figure 3.23 Resulting PAE and delivered power contours drawn in the Smith Chart in peaking                       |

| amplifier for source pull analysis                                                                               |

| Figure 3.24 Resulting PAE and delivered power contours drawn in the Smith Chart in peaking                       |

| amplifier for source pull analysis                                                                               |

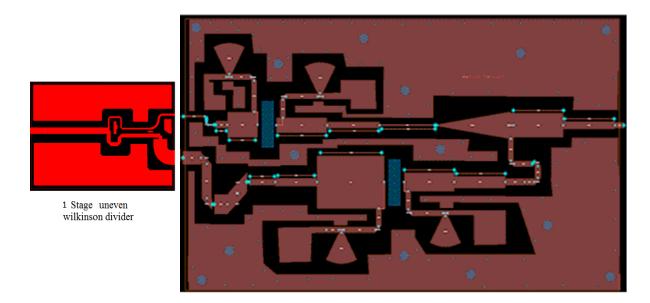

| Figure 3.25 Layout of proposed DPA (two separated PCB layout 1-stage uneven Wilkinson and                        |

| DPA)                                                                                                             |

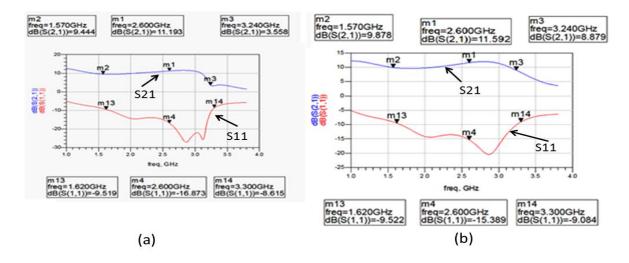

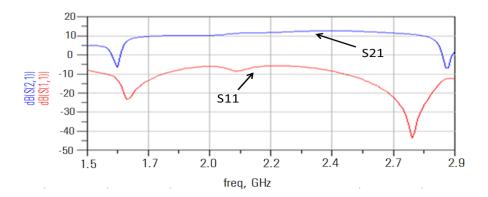

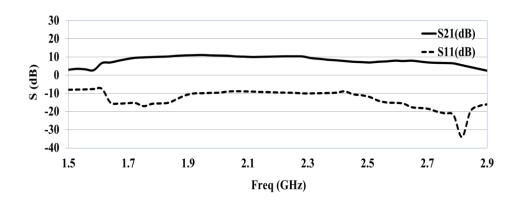

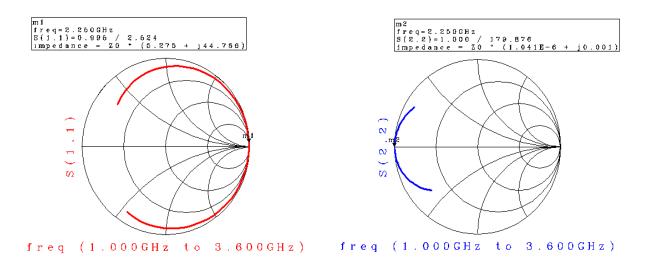

| Figure 3.26 Scattering parameters of proposed DPA with 1- stage uneven Wilkinson divider in                      |

| simulation                                                                                                       |

| Figure 3.27 Scattering parameters of experimental proposed DPA with 1- stage uneven                              |

| Wilkinson divider                                                                                                |

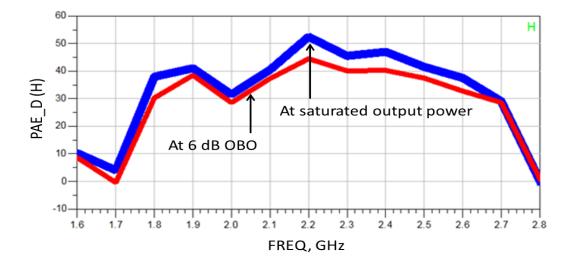

| Figure 3.28 PAE of proposed DPA at: saturated output power (blue line), 6dB OBO (red line) 84                    |

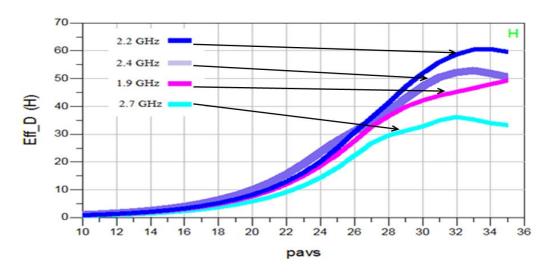

| Figure 3.29 Simulated drain efficiency at 1.9, 2.2, 2.4 and 2.7 GHz as a function of output power                |

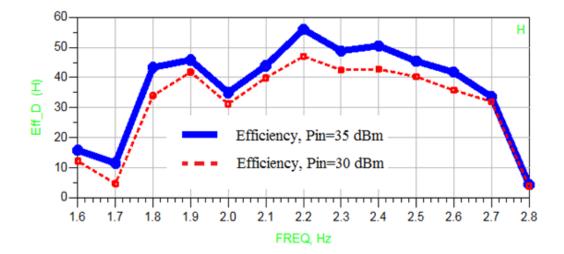

| Figure 3.30 Simulated drain efficiency versus frequency at 35 dBm and 30 dBm (6 dB OBO) . 85                     |

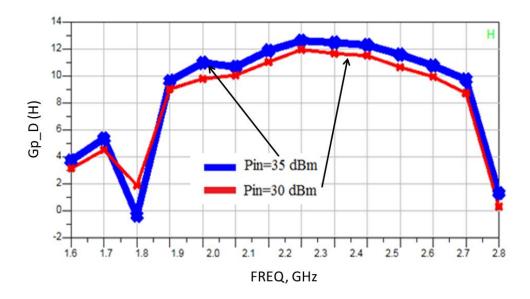

| Figure 3.31 Simulated gain versus frequency at the input power 30 and 35 dBm                                     |

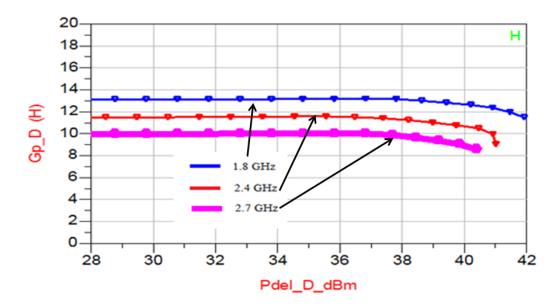

| Figure 3.32 Simulated gain of proposed DPA versus output power at 1.8, 2.4 and 2.7 GHz 86                        |

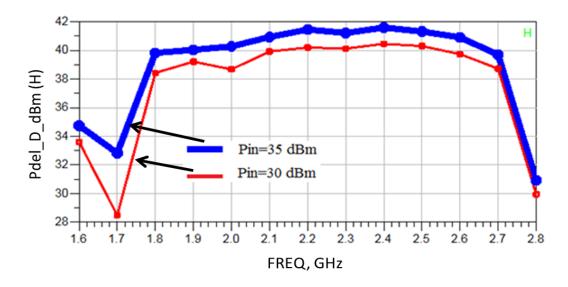

| Figure 3.33 Simulated maximum Power output versus frequency at full power output (35 dBm                         |

| Pin) and 6 dB OBO (30dBm Pin)                                                                                    |

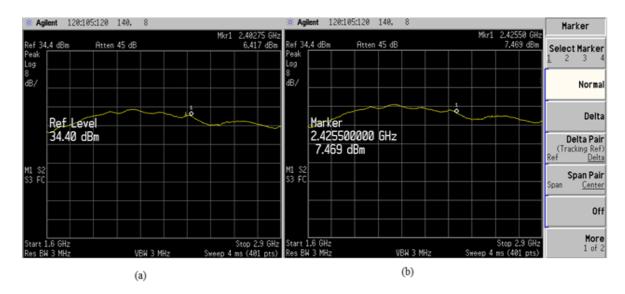

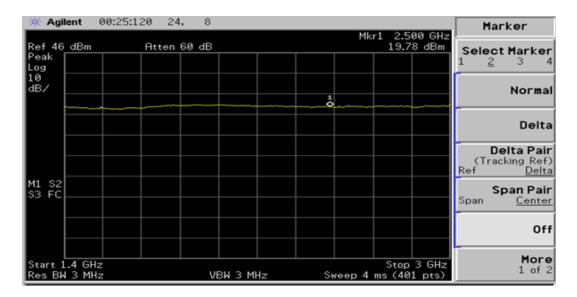

| Figure 3.34 Measured output power by using 33 dB Attenuator at P1dB (a) and saturated power                      |

| of proposed DPA (b)                                                                                              |

| Figure 3.35 Performance of used the linear Pre amplifier to supply proper input power                            |

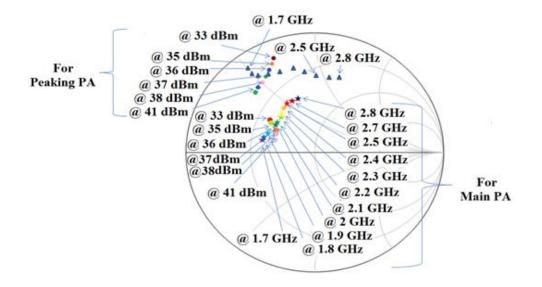

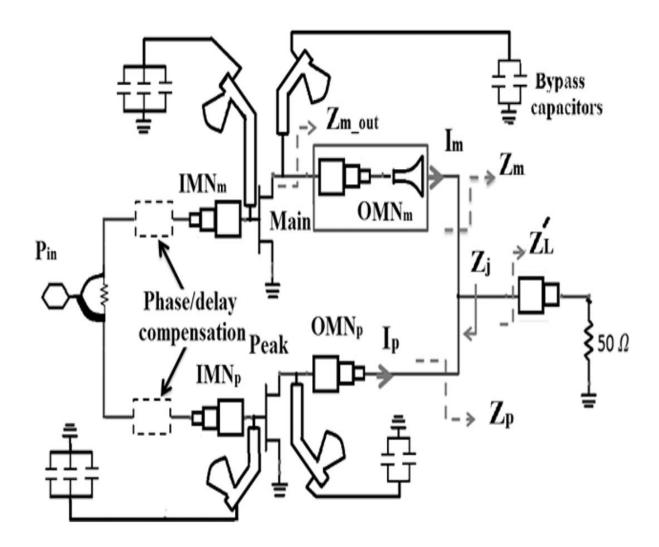

| Figure 4.1 Output impedances of the main PA and peaking PA for maximum                                           |

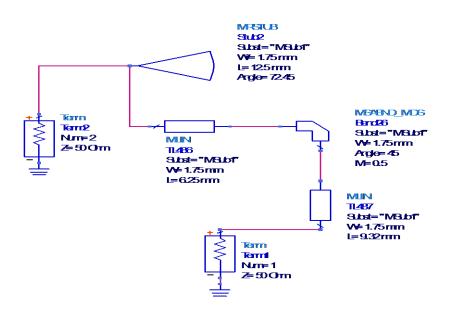

| Figure 4.2 The schematic of the biasing network in implementing Doherty-like                                     |

| Figure 4.3 Results f biasing networks for DPA-like                                                               |

| Figure 4.4 Stability in main stage: (Stab factor (a) and Delta (b))                                              |

| Figure 4.5 Stability in peaking stage :(Stab factor (a) and Delta (b))                                           |

| Figure 4.6 Schematic of the proposed Doherty-like PA                                                             |

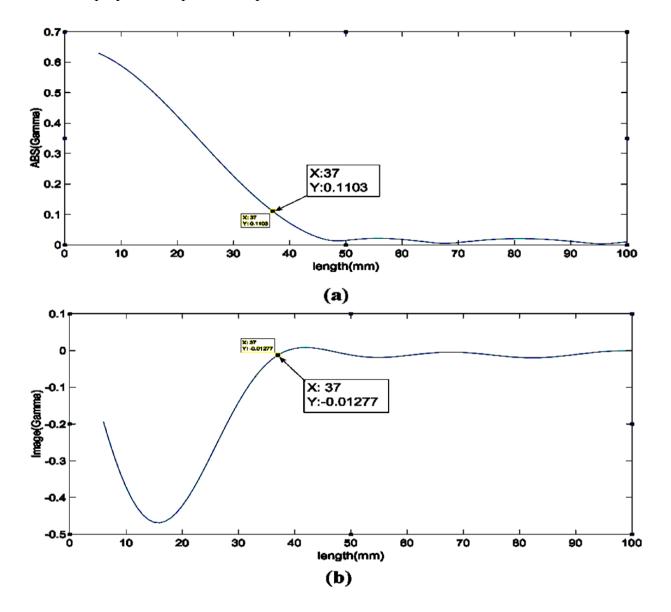

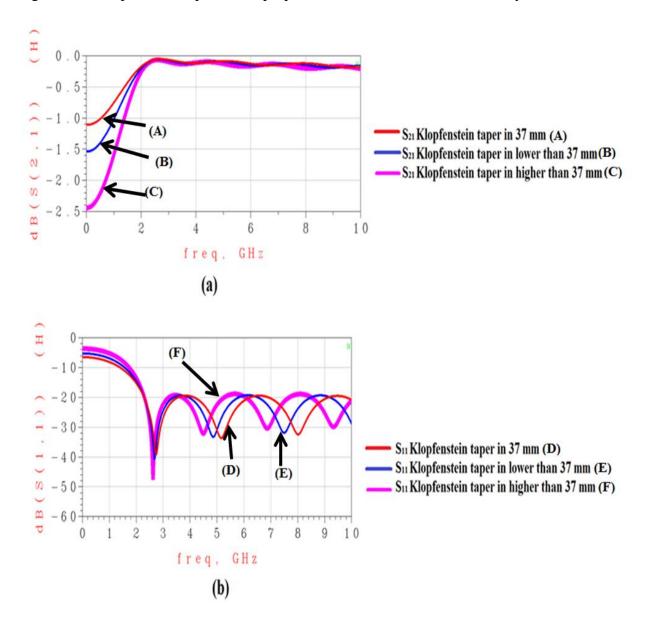

| Figure 4.7 Real (a) and imaginary (b) part of $\Gamma(\theta)$ for used Klopfenstein taper                       |

| Figure 4.8 Comparison the $S_{11}$ and $S_{21}$ of the Klopfenstein taper can be used to transfer 85 $\Omega$ to |

| 25 $\Omega$ in different lengths                                                                                 |

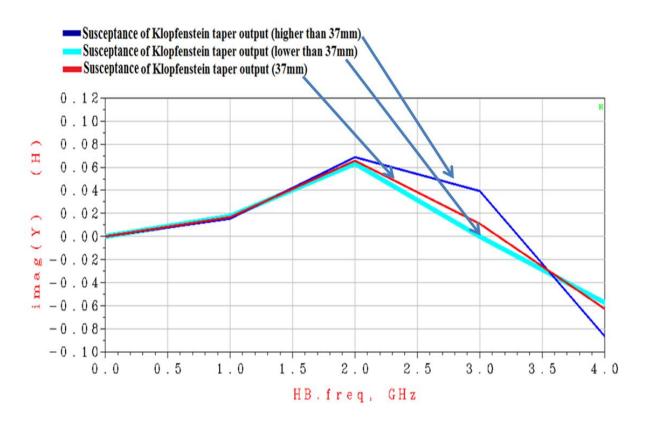

| Figure 4.9 The susceptance of Klopfenstein taper output in different lengths 100                                 |

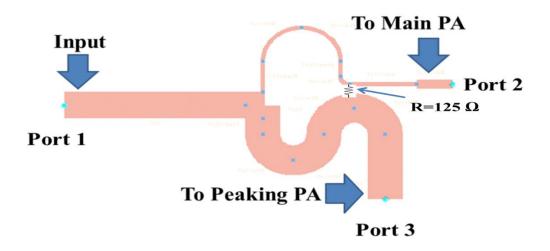

| Figure 4.10 PCB design of uneven Wilkinson splitter (with Wilkinson divider resistance of 125                    |

| Ω)101                                                                                                            |

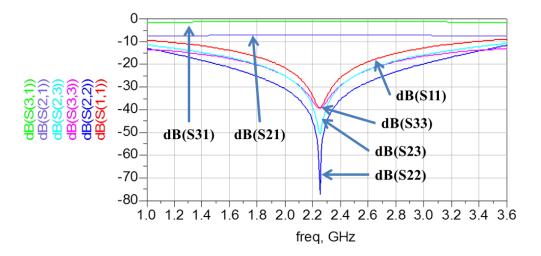

| Figure 4.11 S-parameters of implemented uneven power divider                                                     |

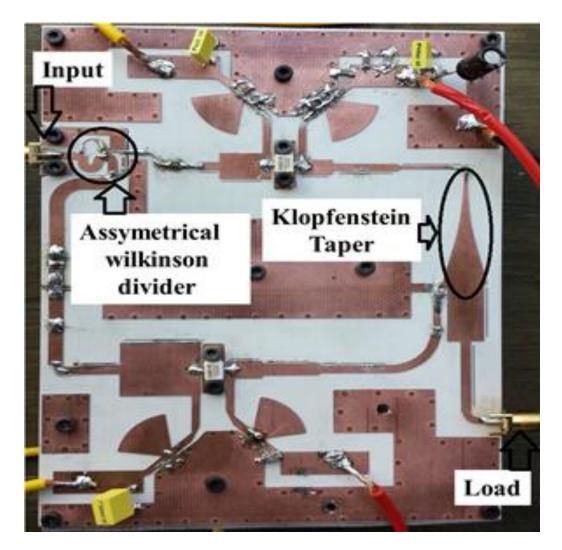

| Figure 4.12 Photograph of the implemented Doherty-like PA                                 | 102 |

|-------------------------------------------------------------------------------------------|-----|

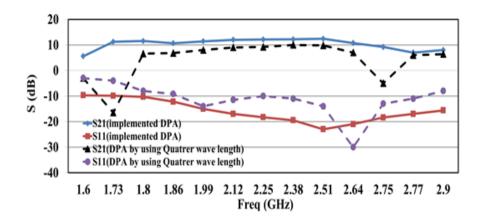

| Figure 4.13 Measured S-parameters of the proposed amplifier, compared with a conventional |     |

| DPA (some schematic, but with the classical $\lambda/4$ transformer)1                     | 103 |

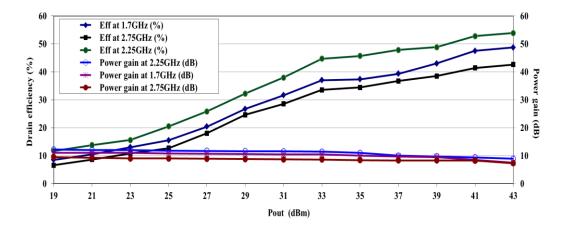

| Figure 4.14 Measured drain efficiency and power gain versus output power (Pout)           | 103 |

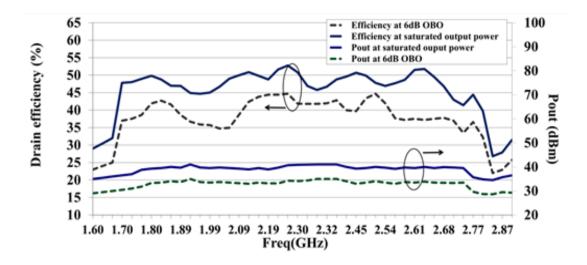

| Figure 4.15 Measured power out and DE (at 6 dB OBO and at saturated power)                | 104 |

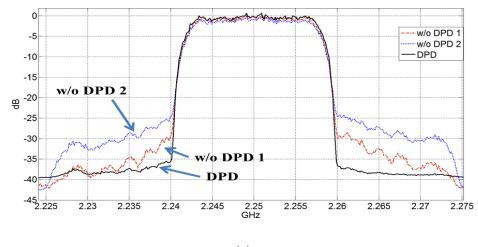

| Figure 4.16 (a) output spectrum with a 20-MHz WCDMA (HSPA+ expanded, release 10)          |     |

| driving signal, at center frequency of 2.25 GHz and average output power of 33 dBm (w/o   |     |

| DPD1) and 36 dBm (w/o DPD2). Common benefits to apply a memory polynomial DPD (ACI        | PR  |

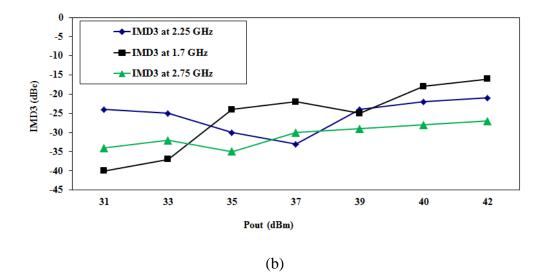

| increased in 10-15 dB) are indicated in the figure and (b) IMD3 measured at 3 different   |     |

| frequencies 1                                                                             | 105 |

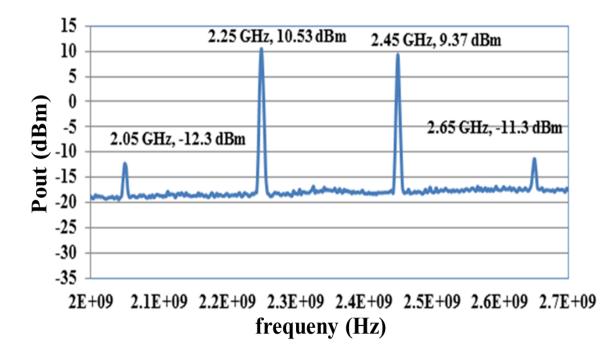

| Figure 4.17 Two-tone test measurements                                                    | 106 |

# **List of Tables**

| Table 1.1 Theoretical efficiency and linearity performance for different PA classes of |     |

|----------------------------------------------------------------------------------------|-----|

| operation                                                                              | 6   |

| Table 1.2 Material properties of common semiconductors devices [45]                    | 12  |

| Table 1.3 Advantages of GaN-HEMT amplifier [45]                                        | 12  |

| Table 1.4 Performance comparison between DPAs in different works [82]                  | 44  |

| Table 1.5 Bandwidth enhancing performance in recent proposed DPAs [82]                 | 50  |

| Table 1.6 Comparison the implemented DPA-like with other wideband DPAs                 | 105 |

# Nomenclature

| ACPR    | adjacent-channel power ratio                    |

|---------|-------------------------------------------------|

| ADS     | advanced design system                          |

| BER     | bit error rate                                  |

| BW      | bandwidth                                       |

| CA      | carrier amplifier                               |

| CCA     | current conduction angle                        |

| CS      | Common Source                                   |

| DPA     | Doherty power amplifier                         |

| DPD     | Digital predistortion                           |

| DSP     | Digital Signal Processor                        |

| EER     | Envelope Elimination and Restoration            |

| ET      | Envelope Tracking                               |

| FB      | Feedback                                        |

| FF      | Feed Forward                                    |

| IBO     | input back-off                                  |

| IIN     | Impedance Inverter Network                      |

| IMD3    | third-order inter-modulation distortion         |

| IMN     | input matching network                          |

| IMP     | Intermodulation Products                        |

| LINC    | Linear Amplification with Non-linear Components |

| LMS     | least mean square                               |

| LNAs    | Low Noise Amplifiers                            |

| MEMS    | micro electro-mechanical switch                 |

| m-HEMTs | metamorphic high electron mobility transistor   |

| NPR     | noise power ratio                               |

| OBO     | output back-off                                 |

| OMN     | output matching network                         |

| PAE     | Power Added Efficiency                          |

| PAPR    | peak-to-average ratio                           |

| PAs     | power amplifiers                                |

| PCN     | Phase Compensation Network                      |

| PD      | Predistortion                                   |

| PkA     | peaking amplifier                               |

| PLL     | phase-locked loop                               |

| PT      | Polar Transmitter                               |

| Q       | quality-factor                                  |

| RF      | radio frequency                                 |

| W-T     | with tapered line                               |

| Wo-T    | without tapered line                            |

|         |                                                 |

# Abstract:

Nowadays, power amplifiers (PAs) are one of the most crucial elements in wireless standards. These elements have been focused on an important issue, which is related to the reduction of power amplifier efficiency at the output back-off (OBO) power level of transmitters so that the resulting signals have a high peak-to-average ratio (PAPR). The lower efficiency of PAs causes the waste of energy as heat. In fact, this lower issue leads to the increment of costs and size (e.g. the cooling requirements). Furthermore, the trade-off between linearity and efficiency in PAs can be considered as another major issue.

To cope with the undesired circumstances offered by efficiency degradation, the Doherty power amplifier (DPA) is one of the useful techniques which provide high efficiency for high PAPR of modern communication signals. Nevertheless, the limited bandwidth(BW) of these kind of PAs (about 10% of fractional bandwidth) and its importance (in modern wireless systems such as LTE, WiMAX, Wi-Fi and satellite systems) have encouraged the researchers to improve this drawback in recent years. Some typical BW limiting factors effect on the performance of DPAs: i) quarter-wave length transformers, ii) phase compensation networks in/output matching circuits, iii) offset lines and device non-idealities; Note that quarter-wave length transformers performs as an inverter impedance in the load modulation technique of DPAs. Concretely, the future objective of designing DPAs is to decrease the impact of these issues.

In this context, this PhD-thesis is focused on improving fractional bandwidth of DPAs using the new methods that are related to impedance transformer in load modulation technique. This study has two fold. First, a novel DPA is presented where a wideband GaN DPA in the 2.5 GHz band with an asymmetrical Wilkinson splitter are employed. Note that the impedance transformer of the proposed architecture is based on a matching network, including a tapered line with multi-section transformer in the main stage. The following results are obtained:

- The bandwidth showed from 1.8 to 2.7 GHz

- The power efficiency is obtained showing more than 33% drain efficiency in the range of 1.8 to 2.7 GHz at both 35 dBm and 30 dBm input power.

Second, based on the benefits of Klopfenstein taper, a promising DPA design is proposed since Klopfenstein taper has been replaced with tapered line. In fact, this substituting results on reducing the reflection coefficient of transformer.

This novel Doherty-like power amplifier has been fabricated using 15 W, 2.7 GHz, GaN HEMT transistors.

From a practical prototype realization, this modification has demonstrated that the resulting DPA BW is increased in comparison with the conventional topology while keeping the efficiency figures. Moreover, this study is shown that the Klopfenstein taper based design allows an easy tuning of the group delay through the output reactance of the taper, resulting in a more straightforward adjustments than other recently published designs where the quarter-wave transformer is replaced by multi-section transmission lines (hybrid or similar). Experimental results have shown 43-54% of drain efficiency at 42 dBm output power, in the range of 1.7 to 2.75 GHz. Concretely, the results presented in this novel Doherty-like power amplifier implies the specific load modulation technique that uses the mixed Klopfenstein tapered line together with a multi-section transformer in order to obtain high bandwidth with the relative efficiency in DPAs.

Keywords: Power amplifiers, OBO, Klopfenstein taper, Doherty power amplifier, wideband, GaN

# Chapter 1 INTRODUCTION

## **1** Introduction

## **1.1** Motivation and statement of the problem

The power amplifiers (PAs) are the most power-consuming components in wireless transmitters. In the design of RF transceivers for modern communication systems, the non-linearity specification of PAs, which plays an important role in the bit error rate (BER) and adjacent-channel power ratio (ACPR) performance of radio frequency (RF) transceivers, has to be especially considered. With the evolution of RF standards, more complex signal modulation schemes have been presented to increase data transmission capacity. Therefore, in order to achieve to the broader bandwidths and higher peak-to-average power ratios (PAPR), RF PA designs will be targeted and get influence of these criteria. Normally, the efficiency of PAs is reduced while the PAPR is increased. These are due to the PAs have to amplify the signals in backed-off regions proportioned to the PAPR figures.

Based on the communication standards, with an increasing demand for higher data-rates, it has forced to use of advanced modulation formats with the information contained in the both amplitude and phase variations. Typically, the modern communication systems such as LTE, WiMAX, Satellite systems and Wi-Fi utilize the modulation schemes like M-QAM, CDMA and OFDM, with the high PAPRs where the PAs operate at an output power back-off. Based on working PAs in the back-off region, the performance of PAs is in the linear region and the efficiency degradation will occur in PAs chain. Hence, considering the linearity besides efficiency of PAs can be of a great importance. To tackle these problems, especially in linearity, some techniques have been proposed, such as Feedback (FB), Feed Forward (FF), and Predistortion (PD). More details about these techniques will be provided in future sections.

Furthermore, in order to enhance the back-off efficiency issue in the amplification, some strategies were suggested such as Kahn Envelope Elimination and Restoration (EER) [1], Envelope Tracking (ET) [2], Polar Transmitter (PT) [3], Linear Amplification with Non-linear Components (LINC) [4] and Load Modulation technique. These techniques are generally applied to enhance efficiency for high PAPR applications. All of these strategies have their own advantages and disadvantages that should be taken into consideration in order to select one. For

example, the EER adopts a saturated high-efficiency PA by using a driven switching current PA. Mentioned switches create constant envelope signal carrying phase information and amplitude information of the input signal. But the voltage supply tracking in the ET adopts by a linear PA. The main drawbacks of these methods are reduction of the efficiency in used modulator, the lack of broadband requirements in the amplitude path and the difficulty to sync the phase and envelop paths in PA. These matters lead to an increment of size and cost. In addition, the performance of PT is similar to the EER with a major advancement in utilizing the Digital Signal Processor (DSP) for modulating of digital signals. The principal drawback of the PT is synchronizing the modulated input signals related to delay matching [5]. Regarding this drawback, the dissipation of power can result in the form of heat. The insufficient bandwidth of the envelope path on the utilized DC-DC converter could be another problem of PT. LINC, based on the Chireix outphasing power amplifier, is a method of separating the signal into two vector summing constant amplitude phase-modulated signals to achieve efficient power amplification. Once the signal has been amplified by highly efficient (switched) amplifiers, both outputs are merged by means of a Chireix power combiner which uses parallel inductance and capacitance compensators for canceling the reactive part of the outputs. The matching of the delays between these two paths can be a problem, an issue that may reduce either efficiency or linearity. The last pointed technique is load modulation. The basic concept of this method is to change the slope of the load line match based on the instant demand of output power. The load impedance may be varied by a varactor based on a tunable matching network or by the Doherty technique. However, another solution can be the supply modulation that is based on controlling the supply voltage by envelope amplifier. More details will be discussed in the future sections.

As mentioned Doherty is a specific kind of load modulation technique which can deliver highly efficient operation at low output power levels, backed-off from maximum output power, without degrading any high power RF performances. Doherty PAs consist of two PAs namely peaking amplifier (PkA) and carrier (or main) amplifier (CA). The CA is typically biased at class AB and the PkA is typically biased at class C. Apart from some issues related to implementation constraints such as delay adjustments, reactance compensation or active devices biasing, the linearity and the insufficient bandwidth (BW) are drawbacks for using the Doherty PAs (DPAs) in broadband applications. The amount of fractional BW in conventional DPA is usually restricted up to 10%. This value is sufficient for a number of RF applications. However, other ones require higher BW for base station configurations [6], [7]. Considering the fact that the biasing level of PkA is lower than CA, this will prevent the maximum PkA input drive to reach the acceptable maximum current level. Hence, the modulated load is not optimal and less power will be generated. Beside that in order to solve these problems, the trade-off among BW, gain, efficiency and linearity shall be considered. According to the mentioned discussion, the contribution of this study deals with the problem of enhancing the power efficiency and BW in DPAs using the proper technique related to impedance transformer in load modulation technique that will be justified later on.

### **1.2** Compromise between linearity and efficiency

Two significant factors in power amplifiers are linearity and efficiency. The trade-off between linearity and efficiency is unavoidable and achieving them is very difficult. Normally, reducing the nonlinearity requirements, which are related to the power efficiency, causes the transmission of signals whose peak amplitudes are below the compression point of the amplifier. So, in order to avoid the PA from these nonlinear effects, it is needed to operate more backed-off (far from the compression point) with the consequent degradation of the overall system efficiency. In other words, power efficiency performance gets influence from the input or output back-off (IBO, OBO respectively). In continue, some other impressment agents on efficiency and linearity will be mentioned in three levels of solution (device level, circuit level and system level) below.

The efficiency of an amplifier is a parameter to show how efficient DC power is converted to RF power, the common definition (drain efficiency) is expressed as:

$$\eta = \frac{P_{out}}{P_{DC}} \qquad [\%, dimensionless] \qquad 1.1$$

Moreover, in order to measure the actual power (previous definition may indicate a good efficiency even at 0 dB gain if  $P_{out} = P_{in}$ ) we need to Power Added Efficiency (PAE) measurement. It is defined as:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \quad [\%, dimensionless]$$

1.2

On the other hand, linearity can be quantified in different ways, for example, in a two-

tone test, by the Third-order Interception Point ( $IP_3$ ) or considering a modulated output signal spectrum by the Adjacent Channel Power Ratio (ACPR), defined in equation (1.3).

$$ACPR_{TOT} = \frac{P_{in-band}}{P_{adjacent-channel}} = \frac{\int_{B} P_{out}(f).df}{\int_{LS} P_{out}(f)df + \int_{US} P_{out}(f).df} [dB]$$

1.3

Furthermore, another way to indicate the performance of PA linearity with many carriers (>10) is using a noise power ratio (NPR) measurement technique. Usually, the NPR test generator consists of a white noise source connected in cascade with a bandpass filter and a notch filter. The notch depth which is the NPR amount can be measured with a Spectrum Analyzer.

#### 1.2.1 Linearity

The linearity solutions can be classified into three different levels. These levels are discussed as follows [8]:

#### 1- At the device level:

The applied semiconductor technologies are a solution at the device level for PAs linearization. A wide variety of semiconductor technologies exist: Si BJT, SiGe HBT, Si LDMOS FET, GaAs MESFET, GaAs HFET, GaAs HBT, SiC MESFET and GaN HEMT, which have been applied in RF power amplifiers. Based on PAs requirements, more specifically regarding the linearity and efficiency, each technology has been used for a particular application. For example, GaAs MESFETs are widely used in the semiconductor industry, due to their simple process and their excellent RF performance. Heterostructure FETs such as HFETs, p-HEMTs, and metamorphic high electron mobility transistors (m-HEMTs) provide a higher  $f_T$  and  $f_{max}$ , and a better noise figure and breakdown voltage compared to other device technologies, which makes them ideal candidates for Low Noise Amplifiers (LNAs) and PAs. Moreover, device technologies such as InP-based devices can be performed a great capacity for the quick and monolithic operation in RF circuit blocks with medium linearity. Nowadays, most of these technologies are nearly out of date, and the high demand for high power devices at higher frequencies made GaN technology important in the major market of the RF and microwave industry. It is worth mentioning that the GaN technology is flavored by two useful components Silicon and Silicon Carbide. They overcome the thermal dissipation problem shown in the pure

GaN technology and introduce two more suitable productions in GaN technology: GaN on Si and GaN on SiC. Because of the high cost of the SiC substrate, the development number of GaN on Si is 200 or 300 times greater than that of GaN on SiC [9], [10].

2- At the circuit level:

The main approach in this level is related to PA operation classes (i.e. Class A, AB, C, etc.). Each PAs are classified in specific classes based on its conductivity angle. This amount indicates the level of the conducted signal from the input to the output of the PA, and it has a direct relationship with both the power efficiency and the linearity of the PA. Typically, the theoretical conduction angles in these classes are 100% for class-A, 50% for class-B, and less than 50% for class C. Table 1.1 indicates the compromise between linearity and efficiency based on the operation class of PAs. In class C, the PA exhibits poor linearity and high efficiency. In classes A, B, and AB, the PAs present as linear PAs, with poorer efficiency. Classes D, E, and F behave as a nonlinear switching PA with a higher efficiency and it will mention in the next sections. For example, based on the structure of classes D and E, the energy stored in the used capacitor is dissipated into heat through the switching operation. Moreover, in class F, the PAs have a complicated structure; also the harmonic resonators are difficult to control, which causes a loss of efficiency. Furthermore, the class-C, class-D, class-E, and class-F power amplifiers are, in different degrees, insufficient for non-constant amplitude applications [11].

| Class of operation | Operation<br>Mode      | Maximum<br>(theoretical) Efficiency<br>(%) | Linearity                                  |

|--------------------|------------------------|--------------------------------------------|--------------------------------------------|

| Class-A            | Current source mode    | 50                                         | Good                                       |

| Class-AB           | Current source mode    | Better than Class-AB Worse than<br>Class-B | Better than Class-B worse than<br>Class-AB |

| Class-B            | Current source<br>mode | 78.5                                       | Moderate                                   |

| Class-C            | Current source<br>mode | 100                                        | Poor                                       |

| Class-D            | Switch mode            | 100                                        | Poor                                       |

| Class-E            | Switch mode            | 100                                        | Poor                                       |

| Class-F            | Switch mode            | 100                                        | Poor                                       |

Table 1.1 Theoretical efficiency and linearity performance for different PA classes of operation

In addition, linearization at the circuit level can be faced in three main approaches:

#### A. Cancellation of Nonlinearities and Linear Transconductance Gain approach

The main objective in this method is to cancel or reduce the nonlinearities which appears in the band due to the nonlinear gain of the PA device. Two techniques are considered as follows:

#### • Harmonic Terminations:

This technique applies the components to decrease the effects of third-order nonlinearities in the Intermodulation Products (IMP) generation. In this technique, a modulated second harmonic signal (centered at  $2f_0$ ) is slowly mixed with the input of the power amplifier with the fundamental tone through the second-order non-linearity due to produce an in-band contribution. It can be adjusted to compensate or even completely cancel the corresponding term arising from third-order nonlinearity. For instance, in modern transmitters, PAs provide the harmonic termination network using open-circuit impedance in the drain of the transistors at odd-order harmonics and the short-circuit impedance at the even-order harmonics for class-F operation [12]. For more details, kindly refer to [13], [14], [15], [16] and [17]. The complexity of the harmonic termination circuit and its associated loss and required chip area are some drawbacks of this technique. Besides, inter-modulation distortion (IMD) sweet spots (operating points in the PA, where the nonlinearity is locally reduced from a two-tone test) can be used in order to improve linearity by controlling some relating factors to cancel the intermodulation components in PAs. The control factors such as gate bias voltage, input power, load impedance and temperature can affect the sweet spots. These relations are presented in [18], [19], [20]. In other words, the linearity modification using IMD sweet spots has been performed by controlling the load impedances and gate bias voltages in parallel-configuration PAs such as the N-way DPAs or balanced PAs [21], [22].

#### Derivative Superposition and Transconductance compensation:

Nonlinearity in Common Source (CS) FET amplifiers, mostly depends on the transconductance  $(g_m)$  non-linearity. This non-linearity can be expressed by applying the Taylor expansion series for the drain-source current  $i_{ds}$  such a CS FET:  $i_{ds} = I_{dc} + g_m V_{gs} + (g_m'/2!)V_{gs2} + (g_m''/3!)V_{gs}^3$ , where  $V_{gs}$  is a small-signal gate-source voltage and  $g_m$  (n) indicates the n-th

derivative of  $g_m$  with respect to  $V_{gs}$ . The derivative superposition technique [23] enhances linearity in the main transistor by minimizing the value of  $(g_m''/3!)$   $V_{gs3}$ . Some relevant examples have been mentioned in [24] and [25].

#### B. Active bias for dynamic power supply approach

In this approach, using of active bias circuits to continuously optimize the performance of the circuit has a significant effect on improvement of the power efficiency in active devices. Active bias provides a possibility for lowering the power dissipation without a dominant decline in the circuit dynamic range or linearity. This method modulates the bias circuits when the receiver is near or in compression point [26], [27]. Since this technique utilizes active components such as transistor alongside other passive components, therefore, it prevents energy loss in the form of heat, size and cost increment.

#### C. Thermal compensation approach

Memory effects in power amplifiers can be divided into two main groups: electrical and thermal memory effects. Electrical memory effects are caused in a device by the delayed charge transport as so called charge carrier traps. This issue can be significantly reduced by a precise design of the biasing and matching circuit. Thermal memory effects fit into low modulation frequencies up to a few MHz and are brought by electro-thermal couplings. To overcome the difficulties associated with thermal memory effects, a compensation module can be employed. It required an accurate measurement of the memory effects in order to synthesize an allocated compensation module. For example, the compensation module could be found out by adding a memory effects compensator to a memoryless PD polynomial function. Some notable solutions are presented in [28] and [29].

#### 3- At the System Level:

The system level of linearization can be categorized in 4 main families. Those four main families can be classified into two groups based on the linearity operation reason related to the distortion cancellation. These groups are as follows:

#### 1. Linearity aiming at distortion reduction:

The two principal families of operation to reduce the distortion in the PA output area:

- FB:

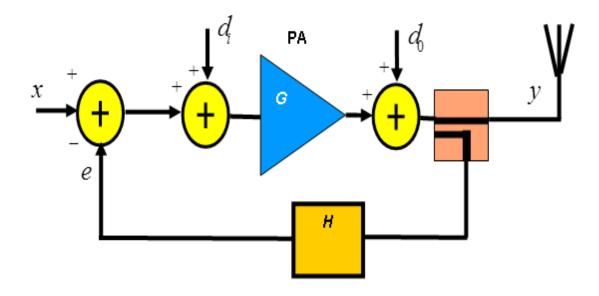

In this technique, cancelling the distortion products are partially reduced by sampling the amplifier's output waveform and then processing, inverting and adding that with the input as it can be seen in Fig 1.1.

FB theory has been developed over time and plenty of advanced FB schemes have been proposed depending on the type of signal that is feed-backed ([30], [31], [32], [33] and [34]). This technique has a high risk of instability because the time delay introduced in the FB signal path. This fact causes in gain reduction and the bandwidth limitation. So, due to the enlarged BW needs in modern communications standards nowadays the use of FB technique is less common than before.

Figure 1.1 Basic structure of a classical FB

- FF:

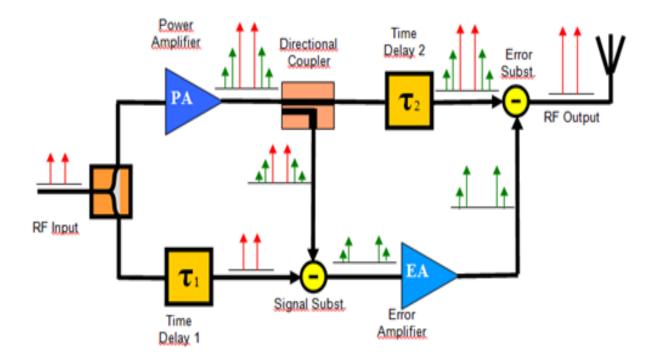

The FF amplifier is recognized as a usable analog structure for wideband operation. It cancels the output signal distortion like FB method, but without considering the stability of the time delay of re-introducing an output sample at the input. As shown in Fig 1.2, two signal paths are included in this method. One of them is highly linear and carries a sample of the undistorted

output signal. The result of the comparison between this signal and sample of the main signal output path is an error signal consisting (ideally) of only distortion products. This error is inverted and added to the output signal to cancel some of the distortion products. Furthermore, delays are presented to match the main signal and the error channels.

FF is unconditionally stable (nevertheless, it does not imply a good behavior) and efficient for wide-bandwidth systems. Some patented progresses in basic FF structure are used to produce an arranged signal to control the phase and amplitude imbalances by using some pilot tones ([35], [36]). Moreover, in order to control the gain and phase components, compensation circuits have been used ([37], [38] and [39]). Generally, the problems with this technique consist of two aspects. First, the power efficiency is not high enough due to the need of using two PAs. Second, it is difficult to adjust the gain and phase compensation components if not using the automatic systems such as least mean square (LMS).

Figure 1.2 FF simplified block diagram and principles of operation

#### 2. Linearization aiming at avoiding distortion:

In this principle the objective is to prevent from arising nonlinearities at the PA output by adjusting the operating point or from a previous source signal processing. The main linearizing techniques related to this principle are:

- Power back-off tuning (not strictly a linearization technique, but the simplest one)

- Predistortion (analog or digital)

The basic idea of predistortion (PD) is the compensation of the nonlinearity of the PA by making a correction module. Typically, linearity improvement in RF systems by analog PD method is occurred by implementing a piecewise approximation of an amplitude transfer function that is opposite of the nonlinear amplifying device ([40], [41], [29] and [42]). In this way, the modification degree is limited by the accuracy and stability of the circuitry. Furthermore, considering the disadvantages of low bandwidth (in FB) or low power efficiency (in FF), PD linearization (analog and digital) provides a higher bandwidth and higher power efficiency linearization option. Digital predistortion (DPD) is nowadays a common solution for modern broadband communication transmitters, while the application of analog PD is shrinking and practically reduced to some particular satellite uses.

After the introduced solutions to linearity issues, the solutions for enhancing the efficiency are addressed as follows.

#### **1.2.2** Power efficiency

The solutions of efficiency enhancement are classified into three levels as mentioned in the linearity section.

1. At the device level:

According to mentioned in linearity section, GaAs HEMT and InP HEMT technologies have a proper linearity and efficiency in RF applications. In addition, by developing high bandgap semiconductor materials, e.g. SiC and GaN, their roles are highlighted in the RF power technology [43]. Individually, GaN devices are recognized due to their high power density, gain and efficiency [44]. By comparing the material properties of Si, GaAs, SiC and GaN (Table. 1.2), it can be said that the technology of GaN is more suitable than other technologies for higher efficiency systems. In Table. 1.3, it has been indicated the advantages of

GaN-HEMT amplifier.

| Material | Breakdown<br>electron field<br>(MV/cm) | Heat<br>conductivity(W/cm/K) | Traveling<br>electron<br>density(/cm <sup>2</sup> ) | Mobility (cm <sup>2</sup> /Vs) | Saturated<br>electron<br>speed<br>(cm/s) |

|----------|----------------------------------------|------------------------------|-----------------------------------------------------|--------------------------------|------------------------------------------|

| Si       | 0.3                                    | 1.5                          | Up to $10^{12}$                                     | 1300                           | $1*10^{7}$                               |

| GaAs     | 0.4                                    | 0.5                          | Up to 10 <sup>12</sup>                              | 2000-<br>4000(MESFET)          | $1.3*10^{7}$                             |

| SiC      | 3                                      | 4.9                          | Up to $10^{12}$                                     | 600                            | $2*10^{7}$                               |

| GaN      | 3 📕                                    | 1.5                          | Up to 10 <sup>13</sup>                              | 1500(HEMT)                     | 2.7*10 <sup>7</sup>                      |

|          |                                        |                              | V                                                   | $\checkmark$                   |                                          |

| High b   | oreakdown voltag                       | e High-current-der           | sity operation                                      | High-speed o                   | operation                                |

| High-v   | oltage operation                       | High-temperature             | e operation                                         | High-efficiency                | operation                                |

Table. 1.2 Material properties of common semiconductors devices [45]

| Table. 1.3 A | dvantages of | GaN-HEMT | amplifier | [45] |  |

|--------------|--------------|----------|-----------|------|--|

|              |              |          |           |      |  |

| Physical property     | Advantage of HEMT          | Advantage of HEMT as an amplifier            |

|-----------------------|----------------------------|----------------------------------------------|

|                       | technology                 |                                              |

| High breakdown        | High-voltage operation     | Easy harmonic processing (higher efficiency) |

| voltage               | -High load impedance-Good  | -Low matching loss                           |

|                       | linearity                  | -Simplified voltage conversion               |

| Wide band gap         | High-temperature operation | Small, lightweight cooling system            |

| High heat             |                            |                                              |

| conductivity          | High-voltage operation     | Small, lightweight amplifier                 |

| -High current density | -Small chip size           |                                              |

#### 2. At the circuit level:

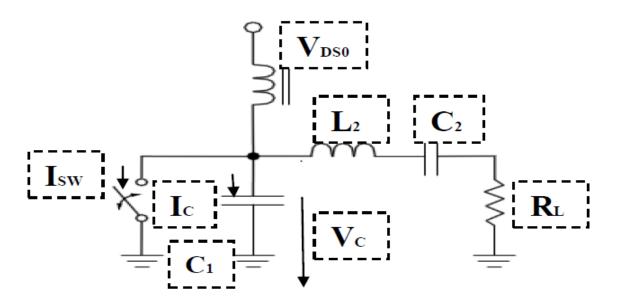

As shown in Table. 1.3, the linearity of PAs operation classes such as the class-D, class-E and class-F have a benefit to higher efficiency applications respect to other conventional PAs classes. Totally, these methods can be classified into two kinds of amplifiers: class F and switch-mode amplifiers. For instance, the class-D and class-E PAs are switch-mode. In these amplifiers, switch operation is performed by charging and discharging of the output capacitor (Fig 1.3). Furthermore, adjusting all harmonic components is conducted by using the LC resonator in these amplifiers. Hence, this performance is led to high efficiency in PAs. However, this point should not pass up the class-D PAs, which are limited to low-medium frequency

applications like, AM and short-wave broadcasting [46], [47]. Furthermore, an important drawback of these PAs (class-D and class-E) is based on the structure: the energy stored in the used capacitor is dissipated into heat through the switching operation.

Figure 1.3 Schematic diagram of class- E amplifier

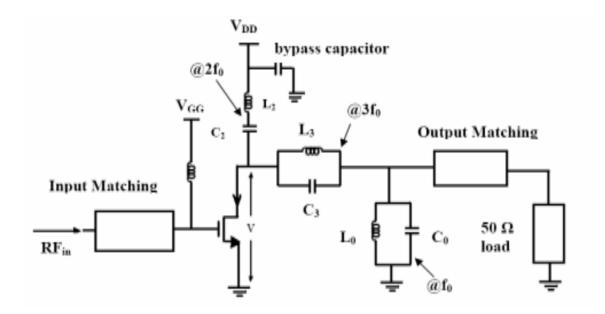

In addition, high efficiency can be fulfilled using the harmonically tuned PAs, such as class-F and class-F<sup>-1</sup>amplifiers at the high frequency. The ideal class-F amplifier includes halfsinusoidal current and rectangular voltage waveforms. According to the Fourier series of both signals (just even harmonics for the rectified waveform of the sinusoidal current and odd harmonics for the rectangular voltage), the circuitry forces their profile by short or open circuiting through resonant networks in order to eliminate undesired harmonics, as shown in Fig 1.4. Thus, close to ideal waveform profiles avoids overlaps between the current and voltage, and so the internal dissipated power is theoretically null. Since harmonic power does not exist, the theoretical efficiency is 100% in class-F PAs. However, as mentioned above in practice this amount will be reduced based on more losses in coordination of even and odd harmonic components. Moreover, the drawback of class F PAs is related to complicated structure and also the harmonic resonators are difficult to control which cause the loss of efficiency due to the compromise between the harmonic filtering and the impedance matching.

Figure 1.4 Schematic diagram of class-F amplifier [48]

The alternative way is the class- $F^{-1}$ . It has used a dual of the class-F PA where the current and voltage waveforms are interchanged. This method can be another solution to enhance the efficiency as it is presented in [48], [49], [50], [51], [52], [53], [54], [55], [56], [57], [58], [59], [60], [61] and [62]. Furthermore, there are some other high efficiency classes such as G, H, and S. Such classes use different techniques to increase the efficiency. For example, G and H use resonators and multi power-supply voltage to reduce the average power consumption. While class-S uses a similar switching technique like class D and E.

#### 3. At the system level:

This level can be organized by five different methods: EER, ET, PT, Chireix and DPA. Based on previous sections, the conventional and harmonically-tuned/switch mode PAs provide high efficiency in only near the maximum output power. Furthermore, the enhancement of the efficiency in output back- off could be a need. Thus, the five above techniques in system level can be proper for solving this problem.

#### -EER technique:

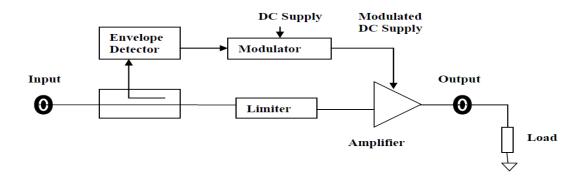

The EER method is a simple concept for improving amplifier efficiency. In this method the input signal passes through a limiter before being amplified. The output signal has

the constant amplitude besides retaining the phase modulation information. The amplifier can then be nonlinear, designed to operate in saturation plus maximum efficiency. In order to reform any amplitude modulation information to the signal, the envelope of the signal is extracted (before the limiter). This information is utilized to modulate the DC power supply of the amplifier as shown in Fig 1.5.

Figure 1.5 EER circuit design

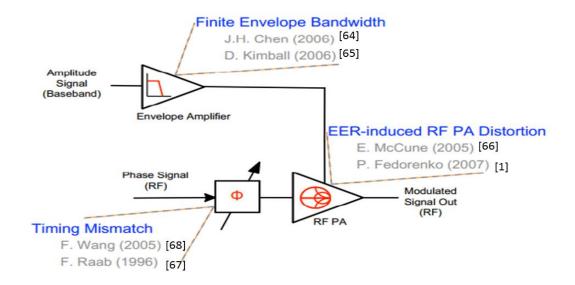

The EER technique can have an excellent efficiency for all values of input power. However, in order to achieve the desired property numbers of challenges are inevitable. The most significant is necessity of a high efficiency power converter realization. Besides, all the major challenges for practical realization of EER RF PAs are outlined in Fig 1.6. More information is described in [63], [1], [2], [64], [65], and [66].

Figure 1.6 Challenges in practical implementation of EER systems

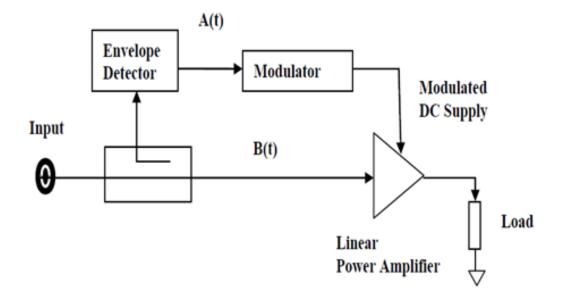

-ET technique:

ET method is similar to the EER method described previously. The limiter circuit is not essential as shown in Fig 1.7.

Figure 1.7 ET technique

The difference between this technique and EER is that the RF input signal contains both amplitude and phase information. Furthermore, the transistor is operated in a linear condition where the DC supply voltage is modulated with the input signal envelope. So, having a power source consummation is proportioned to the instantaneous value of the envelope. Based on that, gain reduction occurred in PA performance when operated in low-current conditions. The design of a highly-efficient DC modulator (with high output voltage and current) can be another challenge in this technique. In addition, since in this technique the supply modulation concept is applied by the voltage modulator, the challenging issue is to fulfill the high bandwidth requirements and a high efficiency at the same time. Nevertheless, this technique is more appealing than EER due to its simplicity and usage. Also, it has already been implemented in several RF applications for communication standards [67], [68].

#### -PT technique:

The PT is a modern type of EER that uses a DSP or similar device (i.e. FPGA) to generate the signals [69]. It provides a single architecture for different systems that may

eliminate some RF mixers with their associated spurious and leakage problems. The concept of polar modulation techniques is built on using magnitude and phase. In this way, applying the two resulting modulation components (phase and magnitude) is provided differently and more efficiently. Typically, the phase component PM and the amplitude component AM are applied using the phase-locked loop (PLL) and the PA respectively. Although, this technique can increase efficiency, extending battery life and leading to the higher output power capability but it has some drawbacks. One these depend on the restriction of bandwidth in the DC-DC converter in Polar system. Another one is related to mismatching the delays of the amplitude and phase paths that cause the increment of dissipation in the system [63].

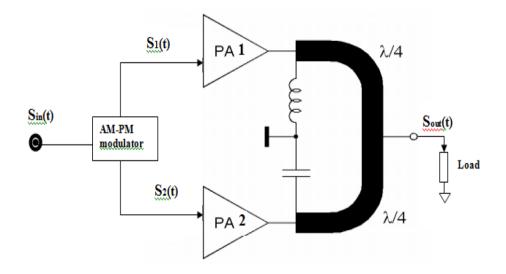

#### - Chireix technique:

This technique is used to merge the output of two nonlinear amplifiers to amplify two input signals which have been obtained from the separation of an input signal into two components of constant amplitude and with different phases, as it has been elaborated in the previous section in the LINC transmitter (Fig 1.8). Important components in this technique are the AM-PM modulator and the output design of the power combiner. In the power combiner, inputted signals to combiner which convey two different paths have non-synchronous phase characteristics. However, this issue has been solved by a reactance compensation load design technique (combined LC resonance with the joint operation of the output impedances of both amplifiers) that has been led to improve the efficiency [4], [70].

Figure 1.8 Chireix technique

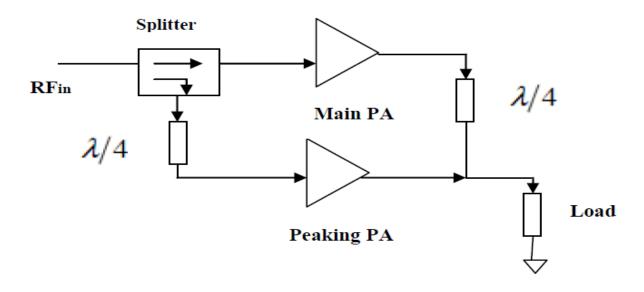

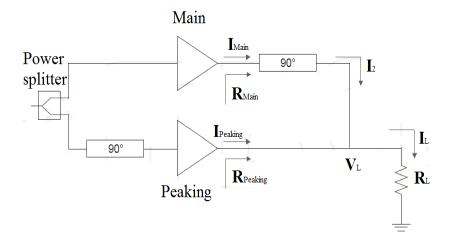

The Doherty amplification, the core of this thesis, is one of the methods with a multi transistor approach to solve the low-efficiency PAs driven by communication signals with high PAPR. Typically, the implementation of a conventional Doherty amplifier consists of two amplifiers in which one operates as a class AB (main) and the other one as a class C (peaking) power stage (see Fig 1.9).

Figure 1.9 DPA technique

In this technique, the switching between each amplifier is performed directly without need to additional circuits, by the input power level when the PA is working. Besides, the output impedances of each amplifier are controlled by the loading from another amplifier. In this way, according to the close relation between load modulation and Doherty technique, this technique is described as below.

## **1.3 Load modulation**

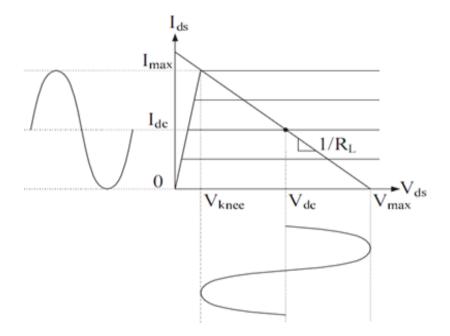

Load modulation is a technique in order to reach to a high efficiency for RF PAs in all of the cases. This technique performs by changing the effective load impedance seen by the transistor that is occurred during the variations in level of output power. Based on the DC load line of transistors (see Fig 1.10), we can find the optimum load to reach the maximum efficiency. In this way, the so-called optimum load ( $R_{opt}$ ) can be approximated from the DC load-line theory as shown in following:

$$R_{opt} = \frac{(V_{dc} - V_{Knee})}{I_{dc}}$$

1.4

Where  $V_{dc}$  and  $I_{dc}$  are output bias voltage and current, and  $V_{knee}$  is the knee voltage. With this  $R_{opt}$  the maximum output power ( $P_{max}$ ) and maximum drain efficiency ( $\eta_{max}$ ) are given by:

$$P_{\max} = \frac{(V_{dc} - V_{Knee})^2}{R_{opt}} = (V_{dc} - V_{Knee})I_{dc}$$

1.5

$$\eta_{\max} = \frac{P_{\max}}{P_{dc}} = \frac{V_{dc} - V_{Knee}}{V_{dc}}$$

1.6

Figure 1.10 Ideal dc load line for the calculation of optimum load

By considering 1.5 can observe the maximum efficiency (about 100% theoretical) of PA by eliminating the  $V_{Knee}$ .

The load-line represents the maximum sinusoidal swing of the voltage (within the range between  $V_{max}$  and  $V_{Knee}$ ) and current (between  $I_{max}$  and 0) of the transistor. This theory is used to

get a rough estimate of the load. Based on the target application, which could be maximum gain, maximum output power, maximum efficiency or maximum linearity of PAs, the load measurement is performed starting from this approach. Despite the practical problems, for example, parasitic of the components and biasing networks causing oscillation, this method is still a good approach for RF PAs [71]. Apart from DPA, feasibility of dynamic load modulation with varactor based networks is a proper method to modify the load and efficiency [72].

The basic concept in load modulation is to dynamically change the load line match depending on the instantaneous demand of output power level. As it can be seen, the mechanism of load modulation is shown in Fig 1.11. Based on the applied input power level the load line will change until reaching the maximum saturated power. These lines present the load values change from low power to maximum power in green, red and blue lines respectively (see Fig 1.11). As indicated the load impedance will be smaller by increasing the power level. More details on this technique, which has a vital role in DPAs, will be given in the next section.

Figure 1.11 The performance of load curves in load modulation.

## **1.4 Doherty Power Amplifiers (DPAs)**

As mentioned before, there are different approaches to achieve the efficiency enhancement PAs. For example, the Doherty amplifier and PAs with dynamically tunable matching networks are based on the dynamic modulation of the load. In DPA technique, it is easier to replace the power amplifiers using DPAs in the base stations rather than other techniques, which require the whole transmitter replacement instead of just the PA, a fact that affects the compatibility and cost.

The key advantages and disadvantages of DPAs, which they will be described in the next sub-sections, are the following [73],

#### Advantages:

**1- Simpler to implement:** The microwave Doherty amplifier can be realized using pure RF techniques to improve efficiency without using complex sub-paths and envelope control circuits which are used in envelope tracking techniques such as EER or ET.

**2- Better power efficiency, respect to other techniques:** The load modulation technique, using a quarter-wave transmission line, can deliver efficiency comparable to other advanced methods.

**3- Direct replacement of, already existing PAs:** The remaining sub-systems in the transmitter have not to be modified.

4- Adds little additional cost, as a consequence of the previous point.

#### **Disadvantages**:

1- Narrow bandwidth: Typically, caused by the quarter-wave transformer.

2- Poor output Standing Wave Ratio (SWR): It would be a problem if our concern is the possible impedance misadjustments due to the load modulation process which they may be solved by placing an isolator at the output guarantees good SWR.

**3- Low IMD performance:** The PkA may generate a large distortion due to a low biasing condition (class AB or C). The distortion components of the PkA can be released by the distortion components generated by the main amplifier if the bias condition is properly adjusted.

**4-** Questionable suitability in low power transmitters: the worthiness has to be carefully assessed in low power applications.

#### **1.4.1** Fundamentals of the DPA

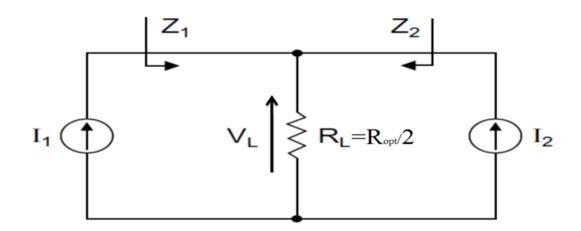

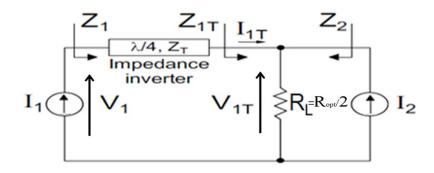

The DPA technique is one of the most common efficiency enhancement techniques. Due to its relatively simple circuits, it can achieve a significant efficiency enhancement at back-off operation with its inherent linearity [74], [75]. Its operation is based on the active load modulation principle. This principle is illustrated in Fig 1.12. Two amplifiers (modelled as current sources, generating the currents  $I_1$  and  $I_2$ ) are connected to a common load  $R_L$ .

Figure 1.12 A simple schematic of load modulation [76]

The load modulation principle equations are the following:

$$V_{\rm L} = R_{\rm L}(I_1 + I_2)$$

1.7

$$Z_{1} = \frac{V_{L}}{I_{1}} = R_{L} \frac{I_{1} + I_{2}}{I_{1}} = R_{L} \left( 1 + \frac{I_{2}}{I_{1}} \right)$$

1.8

$$Z_2 = R_L \frac{I_1 + I_2}{I_2}$$

1.9

From (1.7) it can be clearly noticed that the impedance seen by the amplifier to the left  $Z_1$  can be changed (pulled) by changing the magnitude and/or the phase of the current  $I_2$

generated by the other amplifier. As above mentioned the DPAs have used two devices; the main and the peaking devices having a common load and interconnected through a quarter-wave impedance inverter as shown in Fig 1.13. Since based on the changing load, need to the maximum efficiency of the main devices is important (by the current supplied by the peaking device), the output voltage swing should be kept at a constant value. Therefore, to reach this target, it is necessary to interpose an Impedance Inverter Network (IIN) between the load ( $R_L$ ) and the main source, as shown in Fig 1.13. Based on this approach, the constant voltage value  $V_1$ at the main terminal will be transformed in a constant current value  $I_{1T}$  at the other IIN terminal, without considering the independent value of  $R_L$ .

Figure 1.13 Simplified schematic of the Doherty amplifier [76]

Figure 1.14 Quarter-wave transformer line as impedance inverter

Although, several design solutions could be chosen for the IIN implementations, but the most typical implementation is applying a quarter-wave transmission line ( $\frac{\lambda}{4}$  TL) (see Fig 1.14) which is defined by an ABCD matrix as follows:

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} 0 & j. Z_0 \\ j \\ \overline{Z_0} & 0 \end{bmatrix} \cdot \begin{bmatrix} V_{1T} \\ I_{1T} \end{bmatrix}$$

1.10

Where  $Z_0$  is the characteristic impedance of the line. Considering the equation 1.10, the direct dependence of the voltage at one side (V<sub>1</sub>) with only the current at the other side (I<sub>1T</sub>) through  $Z_0$  is observable.

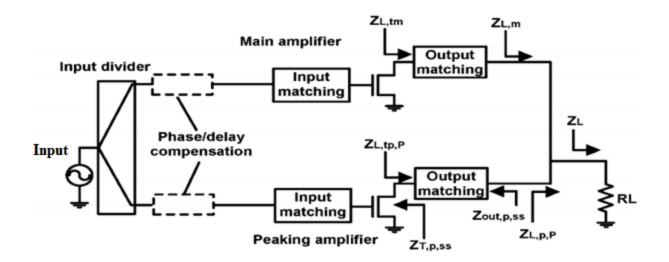

For a more details on the Doherty amplifiers, a typical DPA structure is presented in Fig 1.15. Its structure consists of two active devices that are connected by an IIN at the output of the main branch, a Phase Compensation Network (PCN) which are connected to the input of the peaking device and to the output of the main one (90 ° in the Fig 1.15). In addition, an input power splitter used to transfer the input signal in the proper ratio between two paths besides the output load ( $R_L$ ).

Figure 1.15 Typical Doherty amplifier structure

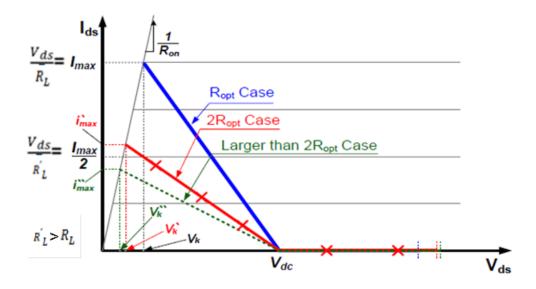

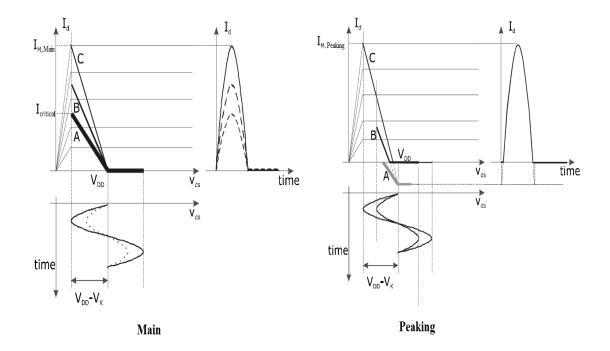

The PCN plays an important role to create a phase delay for coordination in phase of the output signals from the two active devices. Typically, the performance of conventional DPA is separated to two operating conditions. First, in the low input power level in which only the main device is on and the peaking device is kept off based on its class C bias behavior. Second, by increasing the input power level, the current fed the R<sub>L</sub> by the main device rises, while the main device reaches to the saturation condition (I *critical*). This causes the maximum efficiency condition. In this way, as we can see the expected load curve of both devices (main and peaking) in Fig 1.16 with the letter A, the corresponding input power level touches a "break point" condition. By increasing the input power level ( $P_{in_DPA} > P_{in_DPA (break point)}$ ), the peaking device will turn on and the current will flow into the output load R<sub>L</sub>. Based on this view, the impedance (Z<sub>1</sub>) seen by the main device will modulate to a lower value by using the quarter-wave length

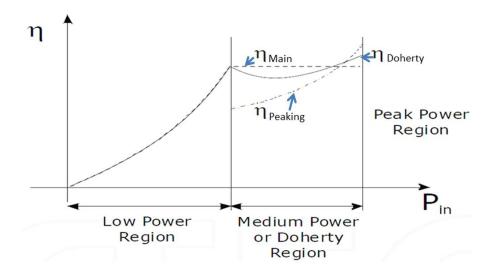

impedance inverter at the break point as shown in Fig 1.16 (load curve "A"). Besides, the efficiency of the main device will keep a constant value, while the increment of the efficiency of the peaking device will occur (see Fig 1.16) (referred as Doherty region). According to Fig 1.16 (letter "C"), in the peak envelope value, where both devices reach to their saturation corresponding the performance of DPA will terminate. Also, overall DPA efficiency (including the efficiency of the main and peaking devices separately) is presented in the Fig 1.17 based on the previous mentioned conditions (in low and medium level of input power).

Figure 1.16 Evolution of the load curves for both DPA active devices: main (left) and peaking (right) amplifiers [77]

Figure 1.17 Typical DPA efficiency behavior versus input power [77]

The behavior of DPA can be analyzed regarding the changing the load impedances of two devices (main and peaking) based on mentioned conditions (at low power level and Doherty region) (see Fig 1.18a) as follows:

In this way, the value of OBO that will introduce below is assumed to be 6dB. The theoretical load impedances of the two amplifiers are expressed as (see Fig 1.13):

$$Z_{1} = \begin{cases} \frac{Z_{T}^{2}}{R_{L}}, & 0 < v_{in} < V_{in,max/2} \\ \frac{Z_{T}^{2}}{R_{L}(1 + \frac{I_{2}}{I_{1}})}, & V_{in,max/2} < v_{in} < V_{in,max} \end{cases}$$

$$1.11$$

$$Z_{2} = \begin{cases} \infty & , & 0 < v_{in} < V_{in,max/2} \\ R_{L} \left( 1 + \frac{I_{1}}{I_{2}} \right) & , & V_{in,max/2} < v_{in} < V_{in,max} \end{cases}$$

1.12

The output load impedances of the main and peaking amplifiers are shown in Fig 1.18b. Considering the low-power region (0 to  $V_{in, max}/2$ ), the peaking amplifier is off, and the load impedance of the main amplifier is two times larger than that of the conventional amplifier (i.e.  $Z_{opt}=50 \ \Omega$ ). When the input voltage reaches to  $(V_{in, max})/2$ , the saturation state obtains by the main amplifier. In other words, the maximum fundamental current swing is half and the maximum voltage swing reaches  $V_{dc}$ . Therefore, the maximum power level will result in half value of allowable power level in main amplifier (as shown in Fig 1.20 at 6 dB down from the total maximum power).

Figure 1.18 Fundamental currents versus input voltage (a), Load impedances versus input drive (b) in DPAs [78]

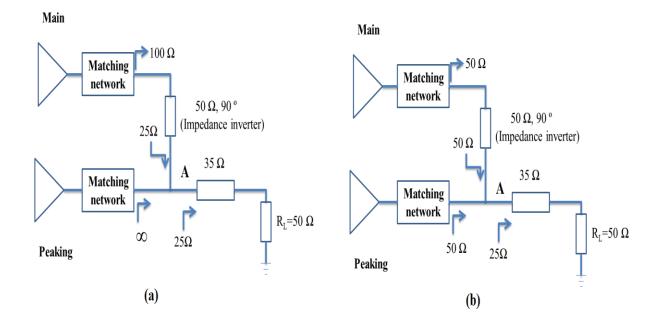

Furthermore, in the high-power region ( $V_{in, max/2}$  to  $V_{in, max}$ ), the peaking amplifier is starting to be on. As it has been described in Fig 1.18a, the current and voltage swings of the peaking amplifier increase depending on the input voltage level and the voltage swing reaches the maximum voltage swing of  $V_{dc}$ . Thus, changing the load impedances of the main and peaking amplifiers occur from  $2Z_{opt}$  (100  $\Omega$ ) to  $Z_{opt}$  (50  $\Omega$ ) and  $\infty$  to  $Z_{opt}$  (50  $\Omega$ ) respectively depends on the input voltage level as shown in Fig 1.18b. These changes would also be shown in Figs 1.19a and 1.19b based on  $Z_{opt}=50 \ \Omega$ . In this view, Figs 1.19a and 1.19b indicate the performance of DPA in the low and high power levels respectively. In both conditions, considering the impedance inverter (90 ° in Fig 1.15) performance, the load impedances of the main and peaking amplifiers change based on given information and the value of impedance in point ''A'' lead to 25  $\Omega$ . This impedance would be transformed to the output impedance ( $R_L=50 \ \Omega$ ) by using a 35  $\Omega$  transmission line as depicted in Fig 1.19.

Figure 1.19 Schematic of DPA performance based on changing the load impedances of the main and peaking amplifiers in low (a) and high (b) power region

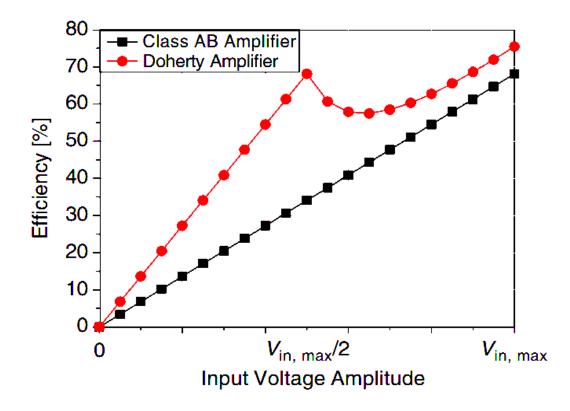

Regarding the change in impedances performance in different power levels of the main and peaking amplifiers, the efficiency of DPA is shown in Fig 1.20. Furthermore, it can be said a DPA with a high efficiency for a large PAPR signal in comparison with conventional class AB amplifiers as depicted in Fig 1.20.

Figure 1.20 Plot of efficiencies versus the input drive level for the Doherty amplifier and the class AB amplifier [78]

#### 1.4.2 Asymmetrical power splitting

In the previous sub-section we have introduced the DPA by assuming a 6 dB OBO value, which is the usual value for basic designs and for explanations because the associated voltage level is 1:2 (Fig 1.18a): the peaking power amplifier is switched-on at half the dynamic range of the input voltage. However, the OBO value has to be compliant with the PAPR of the signal in order to be amplified, and this is happening by adjusting asymmetrically the power splitter. Additionally, because, the different types of PAs are used in the DPA, the gain of the main and the peaking ones are different, and so it should be necessary to readjust the splitting of the input power to compensate the gain differences.

The first design step begins by identifying the OBO level that can be affected to the efficiency of DPA. Also, it is necessary in DPA for accounting the PAPR of the application which applied by the relative DPA. The definition of OBO is following the equation 1.13:

$$0B0 = \frac{P_{out,DPA(x=x_{break})}}{P_{out,DPA(x=1)}} = \frac{P_{out,Main(x=x_{break})}}{P_{out,Main(x=1)} + P_{out,peaking(x=1)}}$$

1.13

Where the mentioned subscripts depend on the whole DPA (in the main and peaking amplifiers). Besides, a parameter x ( $0 \le x \le 1$ ) is used in order to determine the dynamic point depends on the applied input power. For example, the quiescent state (when the RF signal is not applied to the input) points to x=0, and the saturation condition (when the DPA reaches its maximum output power level) presents by x=1. Plus, the break point condition (when the peaking amplifier is turned on) identifies by x =  $x_{break}$ .

In continue, by considering the changes of the load lines of main and peaking amplifiers for  $x = x_{break}$  (load curves "A" in Fig 1.16) and x=1 (load curves "C" in Fig 1.16) the relation of OBO and the ratio between the main device currents at x=1 and x =  $x_{break}$  can be estimated.

The value of bias voltage and drain voltage amplitude of the main device for  $x = x_{break}$  and x=1 are assumed  $V_{DD}$  and  $V_{DD}$ - $V_k$  respectively. Besides, as presented in Fig 1.16 (load curve "C"), the drain voltage of the peaking device for x=1 will reach the same amplitude value.

Based on the mentioned criteria, the output powers delivered by the main and peaking amplifiers will define:

$$P_{out,main(x=x_{break})} = \frac{1}{2} \cdot (V_{DD} - V_K) \cdot I_{1,main(x=x_{break})}$$

1.14

$$P_{out,main(x=1)} = \frac{1}{2} \cdot (V_{DD} - V_K) \cdot I_{1.main(x=1)}$$

1.15

$$P_{\text{out,peaking}(x=1)} = \frac{1}{2} \cdot (V_{\text{DD}} - V_{\text{K}}) \cdot I_{1,\text{peaking}(x=1)}$$

1.16

Where the added subscript "1" in the current is referred to its fundamental component By considering the performance of the lambda quarter wave length based on its defined by ABCD matrix and the combination of some equations that refer to [79] with the above ones, it can be written:

$$V_{L,(x=x_{break})} = (V_{DD} - V_k) \cdot \frac{I_{1,main(x=x_{break})}}{I_{1,main(x=1)}} = \alpha \cdot (V_{DD} - V_k)$$

1.17

Where  $\alpha$  is the ratio between the currents of the main amplifier at  $x = x_{break}$  and x=1.

$$\alpha = \frac{I_{1,\text{main}(x=x_{\text{break}})}}{I_{1,\text{main}(x=1)}}$$

1.18

Accordingly to satisfy two conditions occurred by the voltage and current ratios at  $x = x_{break}$  and x=1, the output resistance (R<sub>L</sub>) calculates respectively:

$$R_{L} = \frac{V_{L,(x=x_{break})}}{I_{2(x=x_{break})}} = \frac{\alpha.(V_{DD} - V_{k})}{I_{1,main(x=1)}}$$

1.19

Thus, from combining the previous equations it follows:

$$I_{1,\text{peaking}(x=1)} = \frac{1-\alpha}{\alpha} I_{1,\text{main}(x=1)}$$

1.20

$$0B0 = \alpha^2$$

1.21

Which shows that, the ratio between the main amplifier currents for  $x = x_{break}$  and x=1 is fixed also by choosing the desired OBO. Based on the mentioned relation between OBO and the ratio of the main device current at  $x = x_{break}$  and x = 1, a degradation of power efficiency by increasing the value of OBO and inversely can be seen.

Consequently, since the maximum output power value of DPA is obtained in x=1, it can be estimated in another way by the following equation:

$$P_{out,DPA(x=1)} = P_{out,main(x=1)} + P_{out,peaking(x=1)} = \frac{1}{\alpha} \cdot \frac{1}{2} \cdot (V_{DD} - V_k) \cdot I_{1,main(x=1)} \quad 1.22$$

Also, by identifying the maximum current at fundamental, the values of  $R_L$  will compute by 1.19 and it is possible to calculate the required characteristic impedance of the output  $\frac{\lambda}{4}$  TL (Z<sub>0</sub>) as follows:

$$Z_{0} = \frac{(V_{DD} - V_{k})}{I_{1,\text{main}(x=1)}}$$

1.23