**ADVERTIMENT.** L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

# **Architectural Explorations for Streaming Accelerators with Customized Memory Layouts**

# Author: Muhammad Shafiq

Advisors:

Dr. Miquel Pericàs, Prof. Nacho Navarro, Prof. Eduard Ayguadé

Department of Computer Architecture

Submitted to the Departament d'Arquitectura de Computadors in Partial Fulfillment of the Requirements for

Doctor of Philosophy (PhD)

Barcelona - April 2012

# بسحراله الرحم الرحيحر

To my great father Prof. Ch. Faqir Muhammad, my sweet mother Kaniz Fatima, my lovely wife Sofia Shafiq and my charming little kids Muhammad Hamza, Hamail Shafiq and Muhammad Hanzalah

## Acknowledgements

\* All the praises and thanks be to Allah(swt), Lord of the worlds. The Most Gracious, The Most Merciful. The Owner of the day of the Judgment. He alone we worship and alone His aid we seek. We ask Him to guide us to the straight way. The way of those on whom He has bestowed His Grace, not the way of those who earned His anger nor of those who went astray.

\* This work was not possible to complete without the help of my advisors Prof. Eduard Ayguadé, Prof. Nacho Navarro and specially Dr. Miquel Pericas. Dr. Miquel Pericas is the one who was actually absorbing and tolerating my strange ideas and helping me extraordinarily to bring them into a good and meaningful shape before that these are presented to our seniors and as well at various research platforms. He has been conducting regular weekly meetings throughout the years. I always found him ready to spare time for the research discussions. Prof. Nacho Navarro is the one who is guiding me in my studies since the very first time I joined UPC. He always been with a tight time schedule due to his teaching activities at UPC, his collaborations with university of Illinois and also due to the responsibility of taking care of his father suffering from the health problems. In-spite of all this, he always rushed to join the research meetings by sparing time from his schedule. Prof. Eduard Ayguadé is the great gentleman because of whom I am here. I found him so much experienced researcher that his few precise words on our research activities have always been enough to highlight the possible issues in a research direction. Moreover, he is the one who actually helped me and my family both socially and financially to survive in the costly city of Barcelona. I am really thankful to all of my advisors from the depths of my heart.

- \* I would like to express my gratitude to Prof. Mark Oskin, Dr. Yoav Etsion, Dr. Nikola Puzovic, Dr. Felipe Cabarcas, Alejandro Rico and Mauricio Araya-Polo. I did many sittings with all of them to push this work ahead in the right direction. I am also thankful to Dr. Isaac Gelado for his feed-back on some of my questions about the internals of GPU architecture. It is not possible to forget to say many thanks to Prof. Marisa Gil Gomez and Dr. Mauricio Alvarez Mesa. They are the really ones who actually gave me a startup in my studies at UPC. I did a project on the CABAC decoder for H.264 under their and Prof. Nacho Navarro's supervision. This learning helped me a lot to effectively pursue later studies.

- \* I am extremely grateful to my father and a great educator Prof. Ch. Faqir Muhammad and my mother Kaniz Fatima. They always encouraged me in my studies and I believe that all of my successes in the life are just because of their prayers and supplications for me. My wife Sofia Shafiq also deserve lot of thanks. In-fact, she exactly demonstrated the saying: Behind Every Successful Man, There Is a Woman. I would also like to express my gratitude to my brothers Muhammad Yasin Shami and Muhammad Saeed for their full support to me in dealing various social and administrative issues in Pakistan while I am sitting here abroad. I also wish to thank my friends and colleagues Branimir Dickov, Tassadaq Hussain, Islam Almalkawi and Ahmed Helmi for sharing their time and having nice technical and non-technical discussions on the lunch and coffee breaks.

- \* The acknowledgements will remain incomplete if I do not quote the organizations and the projects who financially supported this thesis. These include National Engineering and Scientific Commission Pakistan, Barcelona Supercomputing Center (BSC), Technical University of Catalonia (UPC), The Ministry of Science and Innovation of Spain (Project: Computación de Altas Prestaciones V, TIN2007-60625), The European Union Framework Program-7 (Project: Scalable Computer Architecture, IST-2006-27648) and the HiPEAC Network of Excellence (High-performance and Embedded Architectures and Compilers, ICT 217068). I am extremely thankful to all these organizations for their full support during the work.

## **Abstract**

The basic concept behind the architecture of a general purpose CPU core conforms well to a serial programming model. The integration of more cores on a single chip helped CPUs in running parts of a program in parallel. However, the utilization of huge parallelism available from many high performance applications and the corresponding data is hard to achieve from these general purpose multicores. Streaming accelerators and the corresponding programing models improve upon this situation by providing throughput oriented architectures. The basic idea behind the design of these architectures matches the everyday increasing requirements of processing huge data sets. These high-performance throughput oriented devices help in high performance processing of data by using efficient parallel computations and streaming based communications.

The throughput oriented streaming accelerators – similar to the other processors – consist of numerous types of micro-architectural components including the memory structures, compute units, control units, I/O channels and I/O controls etc. However, the throughput requirements add some special features and impose other restrictions for the performance purposes. These devices, normally, offer a large number of compute resources but restrict the applications to arrange parallel and maximally independent data sets to feed the compute resources in the form of streams.

The arrangement of data into independent sets of parallel streams is not an easy and simple task. It may need to change the structure of an algorithm as a whole or even it can require to write a new algorithm from scratch for the target application. However, all these efforts for the re-arrangement of application data access patterns may still not be very helpful to achieve the optimal performance. This is because of the possible micro-architectural

constraints of the target platform for the hardware pre-fetching mechanisms, the size and the granularity of the local storage and the flexibility in data marshaling inside the local storage. The constraints of a general purpose streaming platform on the data pre-fetching, storing and maneuvering to arrange and maintain it in the form of parallel and independent streams could be removed by employing micro-architectural level design approaches. This includes the usage of application specific customized memories in the front-end of a streaming architecture.

The focus of this thesis is to present architectural explorations for the streaming accelerators using customized memory layouts. In general the thesis covers three main aspects of such streaming accelerators in this research. These aspects can be categorized as: i) Design of Application Specific Accelerators with Customized Memory Layout ii) Template Based Design Support for Customized Memory Accelerators and iii) Design Space Explorations for Throughput Oriented Devices with Standard and Customized Memories

This thesis concludes with a conceptual proposal on a Blacksmith Streaming Architecture (*BSArc*). The Blacksmith Computing allow the hardware-level adoption of an application specific front-end with a GPU like streaming back-end. This gives an opportunity to exploit maximum possible data locality and the data level parallelism from an application while providing a throughput natured powerful back-end. We consider that the design of these specialized memory layouts for the front-end of the device are provided by the application domain experts in the form of templates. These templates are adjustable according to a device and the problem size at the device's configuration time. The physical availability of such an architecture may still take time. However, simulation framework helps in architectural explorations to give insight into the proposal and predicts potential performance benefits for such an architecture.

# **Contents**

| Lı     |      |          |                                                                     | XV      |

|--------|------|----------|---------------------------------------------------------------------|---------|

| Li     |      |          |                                                                     | xix     |

| 1      | Intr | oductio  | on                                                                  | 1       |

|        | 1.1  | Strean   | ning Architectures                                                  | . 2     |

|        | 1.2  | Target   | Computing Architecture                                              | . 3     |

|        | 1.3  | Thesis   | S Contributions                                                     | . 6     |

|        |      | 1.3.1    | Design of Application Specific Accelerators with Customized Memory  |         |

|        |      |          | Layouts                                                             | . 7     |

|        |      | 1.3.2    | Template Based Design Support for Customized Memory Accelerators    | 8       |

|        |      | 1.3.3    | Deign Space Explorations for Throughput Oriented Devices with Stan- |         |

|        |      |          | dard & Customized Memories                                          | . 9     |

|        | 1.4  | State of | of the Art of Streaming Accelerators                                | . 10    |

|        |      | 1.4.1    | Imagine                                                             | . 11    |

|        |      | 1.4.2    | Raw                                                                 | . 12    |

|        |      | 1.4.3    | IBM Cell/B.E                                                        | . 12    |

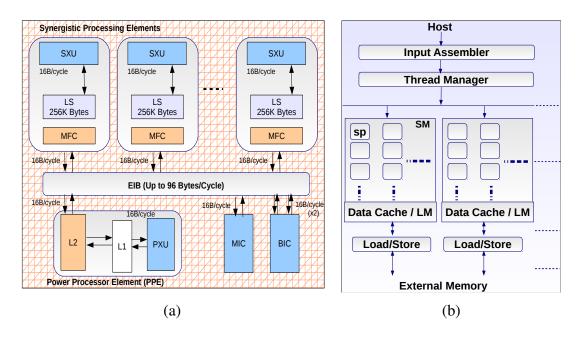

|        |      | 1.4.4    | GPU                                                                 | . 13    |

|        | 1.5  | Thesis   | S Organization                                                      | . 14    |

|        | 1.6  | Summ     | nary                                                                | . 15    |

| I<br>L |      | _        | of Application Specific Accelerators with Customized ory Layout     | d<br>17 |

| 2      | A D  | esign of | f Streaming Architecture for Structured Grid Application            | 19      |

|        | 2.1  | High I   | Performance Computing for Structured Grids                          | . 20    |

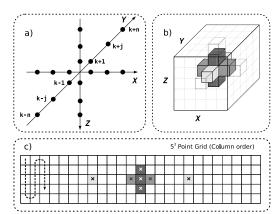

|        | 2.2  | 3D Ste   | encil Computations                                                  | . 22    |

|   | 2.3 | 3D Me    | emory Org  | anizations for Stencil Computations in Reconfigurable Logic . | 26 |

|---|-----|----------|------------|---------------------------------------------------------------|----|

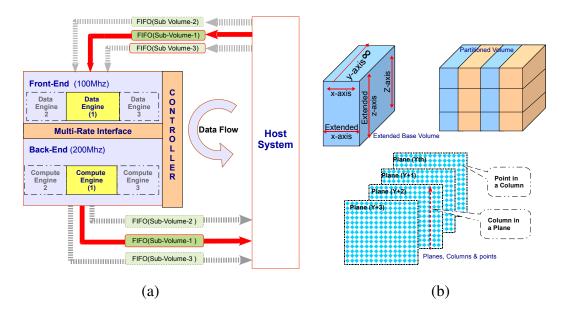

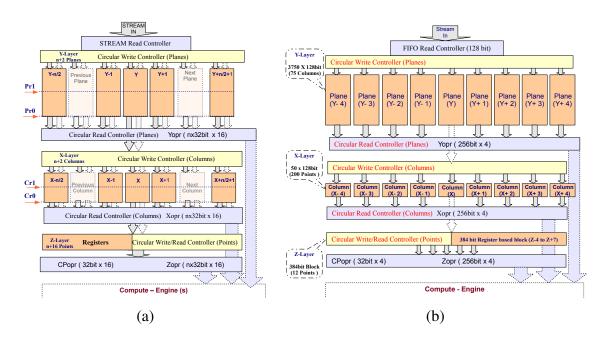

|   |     | 2.3.1    | Front-En   | nd (Data-Engine)                                              | 27 |

|   |     | 2.3.2    | Working    | Principle of the Data-Engine                                  | 29 |

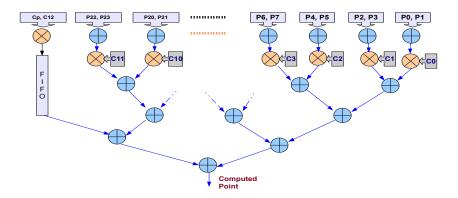

|   |     | 2.3.3    | Back-En    | d (Compute-Engine)                                            | 31 |

|   |     | 2.3.4    | Control-   | Engine                                                        | 32 |

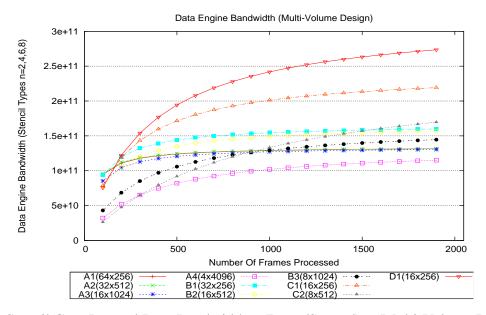

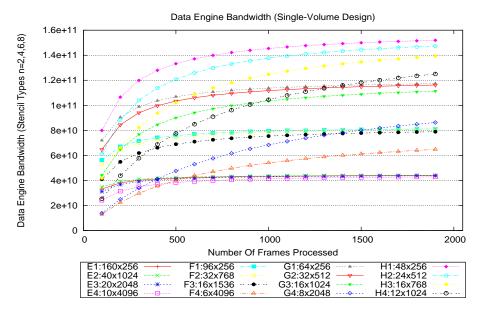

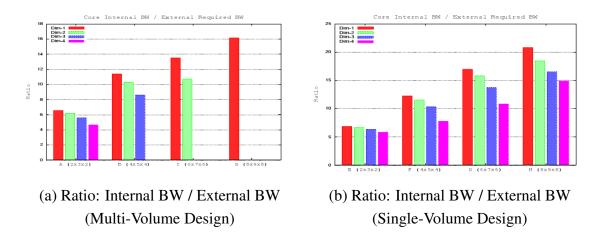

|   |     | 2.3.5    | Evaluation | ons                                                           | 32 |

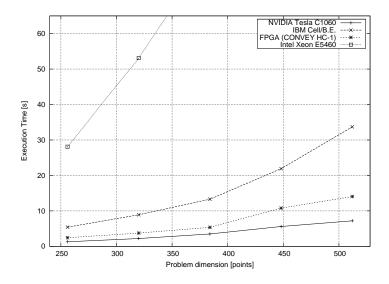

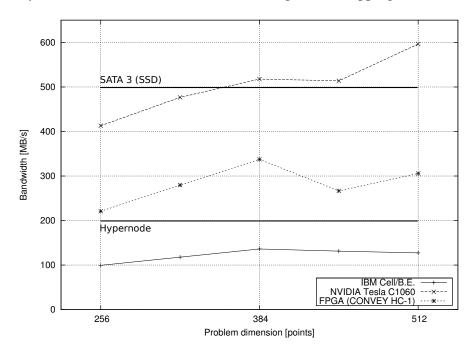

|   |     | 2.3.6    | Results a  | and Discussion                                                | 33 |

|   | 2.4 | RTM A    | Algorithm  | and its Mapping on FPGA                                       | 36 |

|   |     | 2.4.1    | RTM Im     | plementation Problems                                         | 38 |

|   |     |          | 2.4.1.1    | Memory                                                        | 38 |

|   |     |          | 2.4.1.2    | Input/Output                                                  | 39 |

|   |     |          | 2.4.1.3    | Computation                                                   | 40 |

|   |     | 2.4.2    | Applicat   | ion Specific Design of RTM                                    | 40 |

|   |     |          | 2.4.2.1    | ABC                                                           | 42 |

|   |     |          | 2.4.2.2    | Correlation and Illumination                                  | 42 |

|   |     |          | 2.4.2.3    | Compression and decompression                                 | 43 |

|   | 2.5 | Result   | s and Disc | eussion                                                       | 43 |

|   | 2.6 | Summ     | ary        |                                                               | 45 |

| 3 | Gen | eralizat | ion of 3D  | -Memory as a Common Memory Layout                             | 47 |

| J | 3.1 |          |            | cific Front-Ends                                              | 48 |

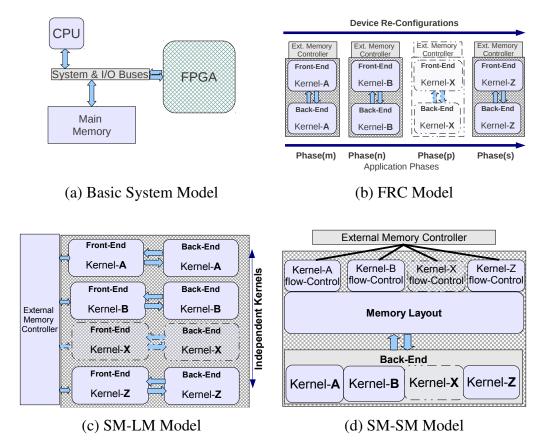

|   | 3.2 |          | •          | s for Multi-Kernel Applications                               |    |

|   | 3.2 | Compt    | 3.2.0.4    | Full Reconfiguration (FRC)                                    |    |

|   |     |          | 3.2.0.5    | Spatially Mapped-Local Memory (SM-LM)                         |    |

|   |     |          | 3.2.0.6    | Spatially Mapped-Shared Memory (SM-SM)                        |    |

|   | 3.3 | Front I  |            | ory Layout For Reconfigurable Accelerators                    |    |

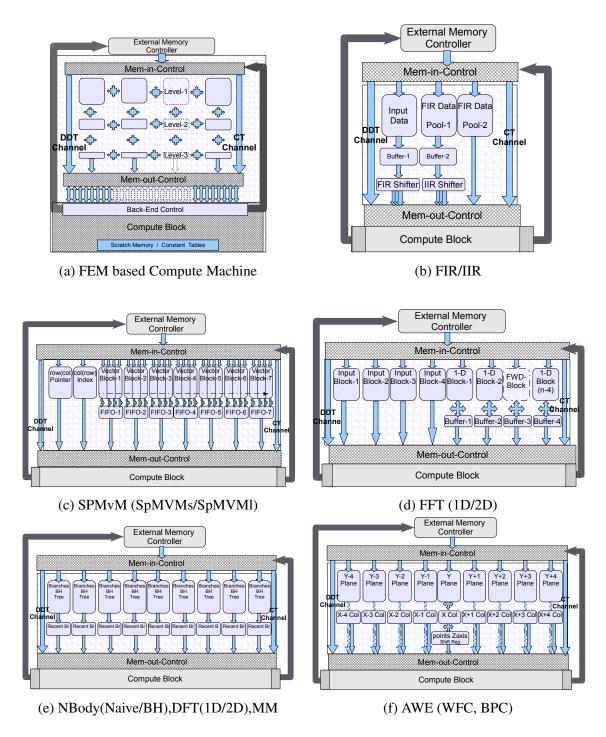

|   |     | 3.3.1    |            | FEM layouts for Scientific Kernels                            |    |

|   |     |          | 3.3.1.1    | Digital Filters                                               |    |

|   |     |          | 3.3.1.2    | Sparse Matrix-Vector Multiplication (SpMVM)                   | 54 |

|   |     |          | 3.3.1.3    | Fast Fourier Transform (1D & 2D)                              |    |

|   |     |          | 3.3.1.4    | N-Body (Naive/Barnes-Hut), DFT (1D/2D) and Matrix Mul-        |    |

|   |     |          | 2.2.1.     | tiplication                                                   | 54 |

|   |     |          | 3.3.1.5    | Acoustic Wave Equation Solver (AWE)                           | 55 |

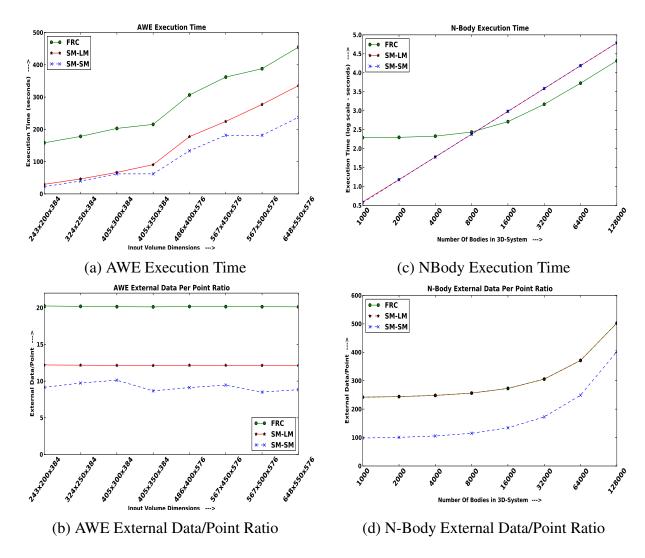

|   | 3.4 | Evalua   |            |                                                               | 55 |

|   | 3.5 |          |            | eussion                                                       | 56 |

|   |     |          |            |                                                               |    |

|          | 3.6         | 3.5.2<br>Summ | N-Body Hermite Algorithm                                     |    |

|----------|-------------|---------------|--------------------------------------------------------------|----|

| II<br>ce | To<br>elera | _             | te Based Design Support for Customized Memory Ac-            | 61 |

| 4        | The         | DATE S        | System                                                       | 63 |

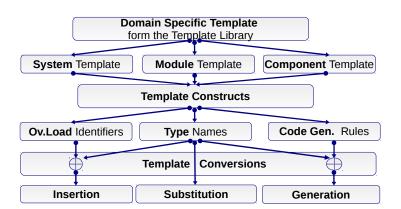

|          | 4.1         | Templa        | ates in Reconfigurable Computing                             | 63 |

|          | 4.2         | Backg         | round                                                        | 67 |

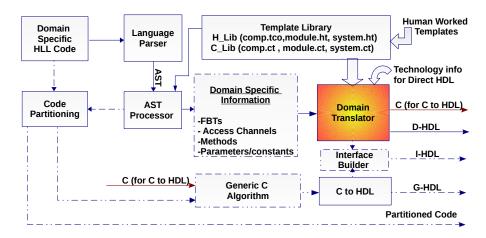

|          | 4.3         | The D         | ATE System                                                   | 68 |

|          |             | 4.3.1         | The DATE System: From The Front-Side                         | 68 |

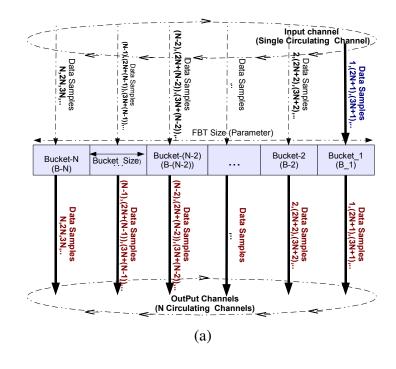

|          |             |               | 4.3.1.1 Functional Bucket Types (FBT)                        | 69 |

|          |             |               | 4.3.1.2 Read/Write Data Access Channels (DACs)               | 70 |

|          |             |               | 4.3.1.3 Abstract Methods                                     | 70 |

|          |             |               | 4.3.1.4 Parameter Set                                        | 70 |

|          |             |               | 4.3.1.5 System I/O                                           | 70 |

|          |             |               | 4.3.1.6 The Translations                                     | 71 |

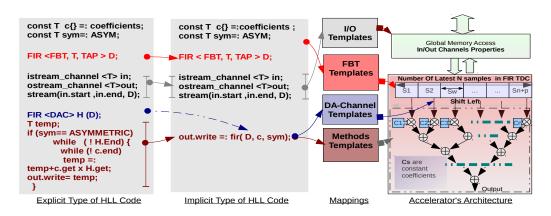

|          |             |               | 4.3.1.7 DATE Input Source Code Types (Implicit and Explicit) | 71 |

|          |             | 4.3.2         | The DATE System : At The Back-End                            | 72 |

|          |             |               | 4.3.2.1 Template's Expansion to C                            | 72 |

|          |             |               | 4.3.2.2 Template's Expansion to HDL                          | 73 |

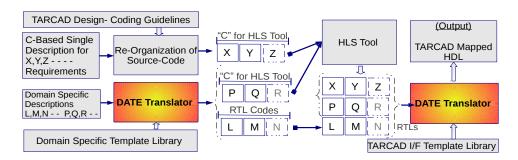

|          |             | 4.3.3         | The DATE System Center: The Domain-Translator                | 73 |

|          |             |               | 4.3.3.1 Template Design                                      | 75 |

|          |             | 4.3.4         | The Date System: Template Library                            | 76 |

|          |             |               | 4.3.4.1 Example HDL Template (The FIR Domain)                | 77 |

|          |             |               | 4.3.4.2 Example C Template (The FIR Domain)                  | 78 |

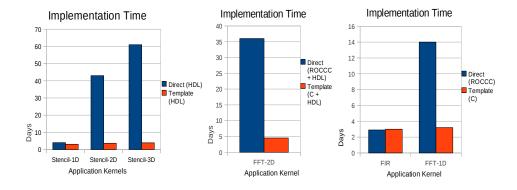

|          | 4.4         | Genera        | ation of Complete System Architecture Using DATE System      | 79 |

|          |             | 4.4.1         | DATE System for Generation of TARCAD Based Designs           | 80 |

|          | 4.5         | Evalua        | ntions                                                       | 82 |

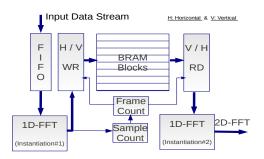

|          |             | 4.5.1         | A Stencil Template Scalable to Multidimensional Stencil      | 82 |

|          |             |               | 4.5.1.1 Stencil Type                                         | 84 |

|          |             |               | 4.5.1.2 Stencil Dimensions                                   | 84 |

|          |             |               | 4.5.1.3 Parallel Computations                                | 84 |

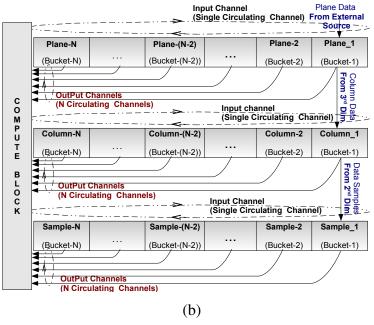

|          |             | 4.5.2         | 2D-FFT Translations                                          | 85 |

|          |             | 4.5.3         | Handling Applications with Multiple Kernels                  | 86 |

|          |             | 454           |                                                              | 87 |

|    | 4.6    | Summ   | ary                                                                                      |

|----|--------|--------|------------------------------------------------------------------------------------------|

| 5  | A T    | hrough | put Oriented Template Based Streaming Accelerator 91                                     |

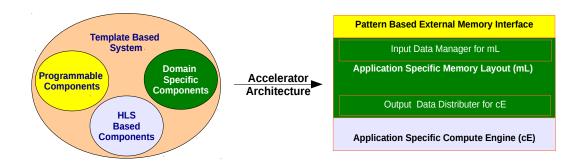

|    | 5.1    | Custon | mized Accelerators                                                                       |

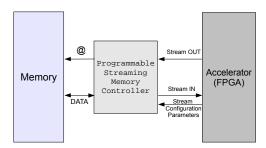

|    | 5.2    | The Ta | ARCAD Architecture                                                                       |

|    |        | 5.2.1  | Accelerator Models for Supercomputing                                                    |

|    |        | 5.2.2  | The External Memory Interface                                                            |

|    |        | 5.2.3  | The Application Specific Data Management Block 95                                        |

|    |        | 5.2.4  | The Algorithm Compute Back-End                                                           |

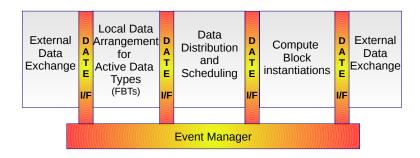

|    |        | 5.2.5  | The Event Managing Block                                                                 |

|    | 5.3    | TARC   | AD Implementation                                                                        |

|    | 5.4    | Applic | cation Kernels on TARCAD                                                                 |

|    |        | 5.4.1  | Matrix-Matrix Multiplication (MxM)                                                       |

|    |        | 5.4.2  | Acoustic Wave Equation (AWE)                                                             |

|    |        | 5.4.3  | Smith Waterman (SW)                                                                      |

|    |        | 5.4.4  | Fast Fourier Transform (FFT)                                                             |

|    |        | 5.4.5  | Sparse Matrix-Vector Multiplication (SpMV)                                               |

|    |        | 5.4.6  | Multiple Kernels On TARCAD                                                               |

|    | 5.5    | Evalua | ations                                                                                   |

|    | 5.6    | Result | s and Discussion                                                                         |

|    |        | 5.6.1  | Matrix-Matrix Multiplication (MxM)                                                       |

|    |        | 5.6.2  | Acoustic Wave Equation (AWE)                                                             |

|    |        | 5.6.3  | Smith-Waterman (SW)                                                                      |

|    |        | 5.6.4  | Fast Fourier Transform (FFT)                                                             |

|    |        | 5.6.5  | Sparse Matrix-Vector Multiplication (SpMV) 109                                           |

|    | 5.7    | Summ   | ary                                                                                      |

|    |        |        |                                                                                          |

|    |        | _      | n Space Explorations for Throughput Oriented De-<br>Standard and Customized Memories 111 |

| VI | ices , | WILL   | tandard and Customized Memories 111                                                      |

| 6  |        |        | r Framework for Performance Characterization of Streaming Archi-                         |

|    | tecti  |        | 113                                                                                      |

|    | 6.1    |        | ators and Computer Architecture Research                                                 |

|    | 6.2    |        | mulator Framework                                                                        |

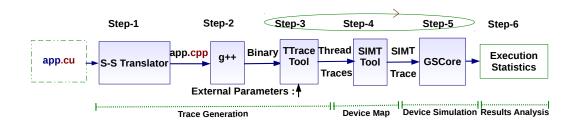

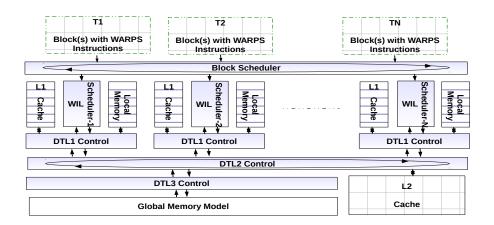

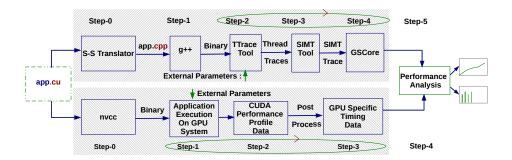

|    | 6.3    |        | Generation                                                                               |

|    |        | 6.3.1  | S-S Translator                                                                           |

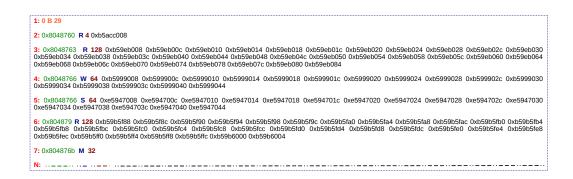

| 6.3.2 TTrace Tool 6.4 Device Map 6.4.1 Garbage (Built-in) Removal 6.4.2 WARP Instructions Formation 6.4.3 Coalescing Effects 6.4.4 Registers and Shared Memory Handling 6.4.5 Grouping Blocks 6.5 Device Simulation 6.6 Evaluations 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SAres Limitations and the Future Work 6.8 Summary  7 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication 7.6.3 3D-Stencil                                                            |   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 6.4.1 Garbage (Built-in) Removal 6.4.2 WARP Instructions Formation 6.4.3 Coalescing Effects 6.4.4 Registers and Shared Memory Handling 6.4.5 Grouping Blocks 6.5 Device Simulation 6.6 Evaluations 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication |   |            | 6.3.2 TTrace Tool                                                                                                                                                                                                                                                                                                                                                                                                                               | . 120                                                                                           |

| 6.4.2 WARP Instructions Formation 6.4.3 Coalescing Effects 6.4.4 Registers and Shared Memory Handling 6.4.5 Grouping Blocks 6.5 Device Simulation 6.6 Evaluations 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SAres Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SAres 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                  |   | 6.4        | Device Map                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 121                                                                                           |

| 6.4.3 Coalescing Effects 6.4.4 Registers and Shared Memory Handling 6.4.5 Grouping Blocks 6.5 Device Simulation 6.6 Evaluations 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                    |   |            | 6.4.1 Garbage (Built-in) Removal                                                                                                                                                                                                                                                                                                                                                                                                                | . 122                                                                                           |

| 6.4.4 Registers and Shared Memory Handling 6.4.5 Grouping Blocks 6.5 Device Simulation 6.6 Evaluations 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                             |   |            | 6.4.2 WARP Instructions Formation                                                                                                                                                                                                                                                                                                                                                                                                               | . 122                                                                                           |

| 6.4.5 Grouping Blocks 6.5 Device Simulation 6.6 Evaluations 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                        |   |            | 6.4.3 Coalescing Effects                                                                                                                                                                                                                                                                                                                                                                                                                        | . 123                                                                                           |

| 6.5 Device Simulation 6.6 Evaluations 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                              |   |            | 6.4.4 Registers and Shared Memory Handling                                                                                                                                                                                                                                                                                                                                                                                                      | . 123                                                                                           |

| 6.6 Evaluations 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                    |   |            | 6.4.5 Grouping Blocks                                                                                                                                                                                                                                                                                                                                                                                                                           | . 123                                                                                           |

| 6.6.1 Case 1: Memory Micro-Kernels 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                    |   | 6.5        | Device Simulation                                                                                                                                                                                                                                                                                                                                                                                                                               | . 124                                                                                           |

| 6.6.1.1 (a) SM Level Evaluations 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary 7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                        |   | 6.6        | Evaluations                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 126                                                                                           |

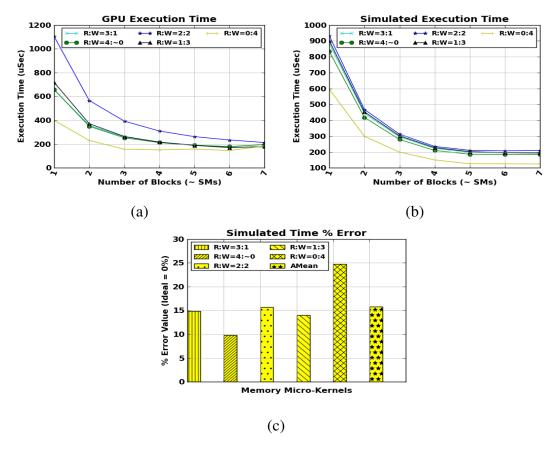

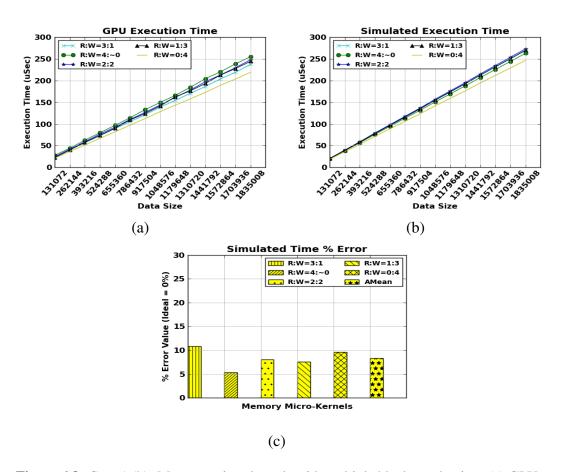

| 6.6.1.2 (b) Multiple Block Evaluations 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors  7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model  7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                      |   |            | 6.6.1 Case 1: Memory Micro-Kernels                                                                                                                                                                                                                                                                                                                                                                                                              | . 127                                                                                           |

| 6.6.2 Case 2. Application Kernels 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors  7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                              |   |            | 6.6.1.1 (a) SM Level Evaluations                                                                                                                                                                                                                                                                                                                                                                                                                | . 127                                                                                           |

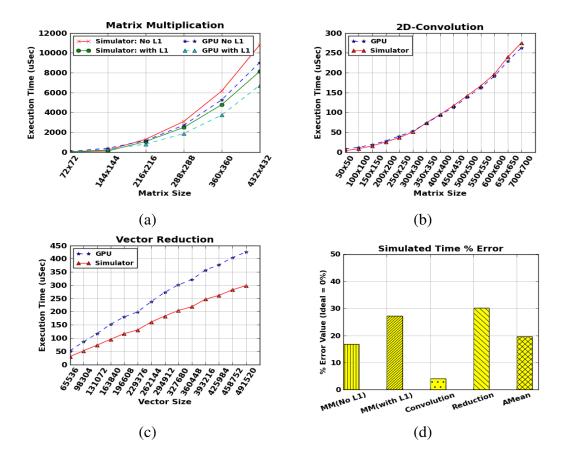

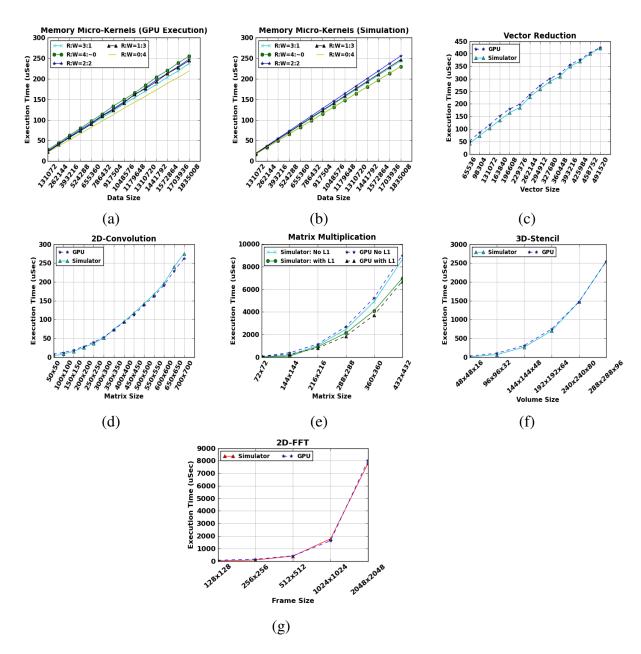

| 6.7 Results and Discussion 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                              |   |            | 6.6.1.2 (b) Multiple Block Evaluations                                                                                                                                                                                                                                                                                                                                                                                                          | . 127                                                                                           |

| 6.7.1 SArcs Limitations and the Future Work 6.8 Summary  7 Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                            |   |            | 6.6.2 Case 2. Application Kernels                                                                                                                                                                                                                                                                                                                                                                                                               | . 127                                                                                           |

| Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 6.7        | Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                          | . 128                                                                                           |

| 7. Design Space Explorations for Streaming Architectures using SArcs 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |            | 6.7.1 SArcs Limitations and the Future Work                                                                                                                                                                                                                                                                                                                                                                                                     | . 131                                                                                           |

| 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 6.8        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 132                                                                                           |

| 7.1 Design Space Explorations 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7 | Deci       | ign Snace Evnlorations for Streaming Architectures using SArcs                                                                                                                                                                                                                                                                                                                                                                                  | 133                                                                                             |

| 7.2 Effectiveness of the Design Space Exploration Tool 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |

| 7.3 Design Space Explorations for GPU 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 7.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |

| 7.3.1 Application Kernels 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 1.4        | Effectiveness of the Design Space Exploration Tool                                                                                                                                                                                                                                                                                                                                                                                              | . 137                                                                                           |

| 7.3.2 Base Line Architecture 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |

| 7.3.3 Simulation Platform 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |            | Design Space Explorations for GPU                                                                                                                                                                                                                                                                                                                                                                                                               | . 140                                                                                           |

| 7.3.4 Evaluated Architectural Configurations 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |            | Design Space Explorations for GPU                                                                                                                                                                                                                                                                                                                                                                                                               | . 140<br>. 140                                                                                  |

| 7.3.4.1 Global Memory Bandwidth 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |            | Design Space Explorations for GPU                                                                                                                                                                                                                                                                                                                                                                                                               | . 140<br>. 140<br>. 141                                                                         |

| 7.3.4.2 Data Channels Between Memory Hierarchy and SMs 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |            | Design Space Explorations for GPU  7.3.1 Application Kernels  7.3.2 Base Line Architecture  7.3.3 Simulation Platform                                                                                                                                                                                                                                                                                                                           | <ul><li>. 140</li><li>. 140</li><li>. 141</li><li>. 141</li></ul>                               |

| 7.3.4.3 Cache Memory 7.3.4.4 Streaming Multiprocessors 7.4 Results and Discussion 7.5 Blacksmith Computing 7.5.1 Target Platform Model 7.6 Application Specific Front-Ends 7.6.1 2D-FFT 7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |            | Design Space Explorations for GPU  7.3.1 Application Kernels  7.3.2 Base Line Architecture  7.3.3 Simulation Platform  7.3.4 Evaluated Architectural Configurations                                                                                                                                                                                                                                                                             | <ul><li>. 140</li><li>. 140</li><li>. 141</li><li>. 141</li><li>. 142</li></ul>                 |

| 7.3.4.4 Streaming Multiprocessors  7.4 Results and Discussion  7.5 Blacksmith Computing  7.5.1 Target Platform Model  7.6 Application Specific Front-Ends  7.6.1 2D-FFT  7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |            | Design Space Explorations for GPU  7.3.1 Application Kernels  7.3.2 Base Line Architecture  7.3.3 Simulation Platform  7.3.4 Evaluated Architectural Configurations  7.3.4.1 Global Memory Bandwidth                                                                                                                                                                                                                                            | . 140<br>. 140<br>. 141<br>. 141<br>. 142                                                       |

| 7.4 Results and Discussion  7.5 Blacksmith Computing  7.5.1 Target Platform Model  7.6 Application Specific Front-Ends  7.6.1 2D-FFT  7.6.2 Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |            | Design Space Explorations for GPU  7.3.1 Application Kernels  7.3.2 Base Line Architecture  7.3.3 Simulation Platform  7.3.4 Evaluated Architectural Configurations  7.3.4.1 Global Memory Bandwidth  7.3.4.2 Data Channels Between Memory Hierarchy and SMs                                                                                                                                                                                    | . 140<br>. 141<br>. 141<br>. 142<br>. 142                                                       |

| 7.5 Blacksmith Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |            | Design Space Explorations for GPU  7.3.1 Application Kernels  7.3.2 Base Line Architecture  7.3.3 Simulation Platform  7.3.4 Evaluated Architectural Configurations  7.3.4.1 Global Memory Bandwidth  7.3.4.2 Data Channels Between Memory Hierarchy and SMs  7.3.4.3 Cache Memory                                                                                                                                                              | . 140<br>. 141<br>. 141<br>. 142<br>. 142<br>. 143                                              |

| 7.5.1 Target Platform Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 7.3        | Design Space Explorations for GPU  7.3.1 Application Kernels  7.3.2 Base Line Architecture  7.3.3 Simulation Platform  7.3.4 Evaluated Architectural Configurations  7.3.4.1 Global Memory Bandwidth  7.3.4.2 Data Channels Between Memory Hierarchy and SMs  7.3.4.3 Cache Memory  7.3.4.4 Streaming Multiprocessors                                                                                                                           | . 140<br>. 140<br>. 141<br>. 141<br>. 142<br>. 142<br>. 143<br>. 143                            |

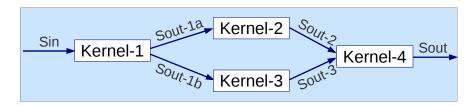

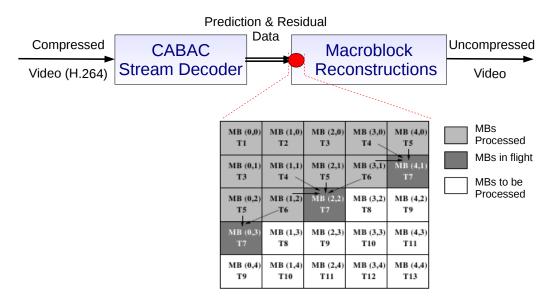

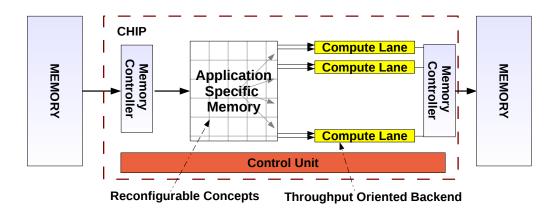

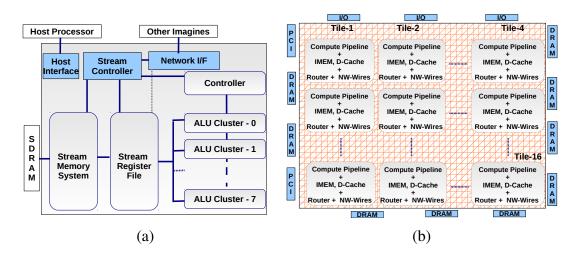

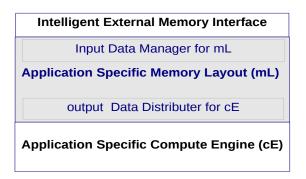

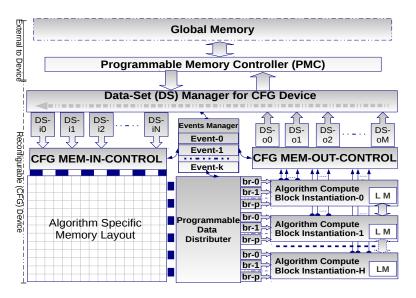

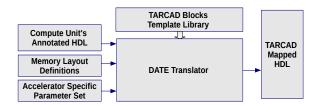

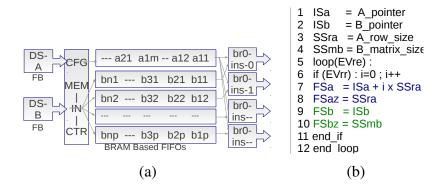

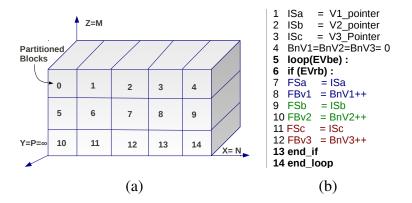

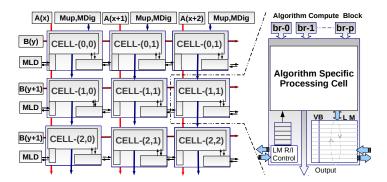

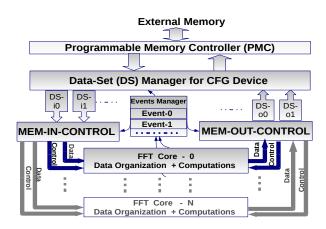

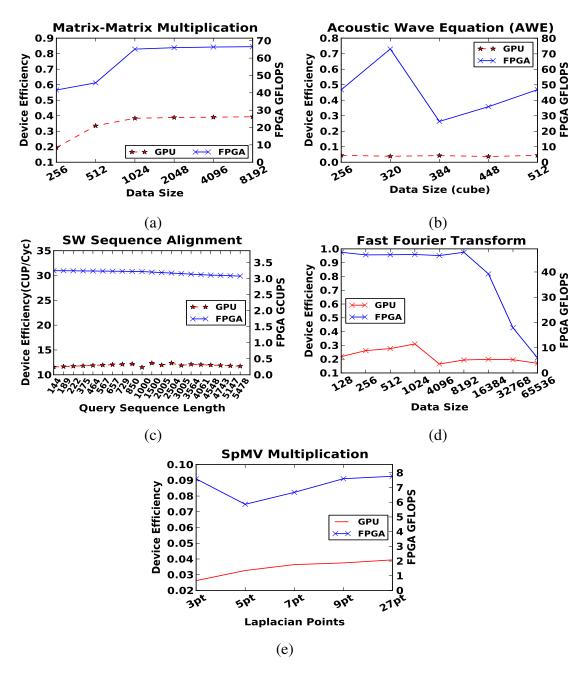

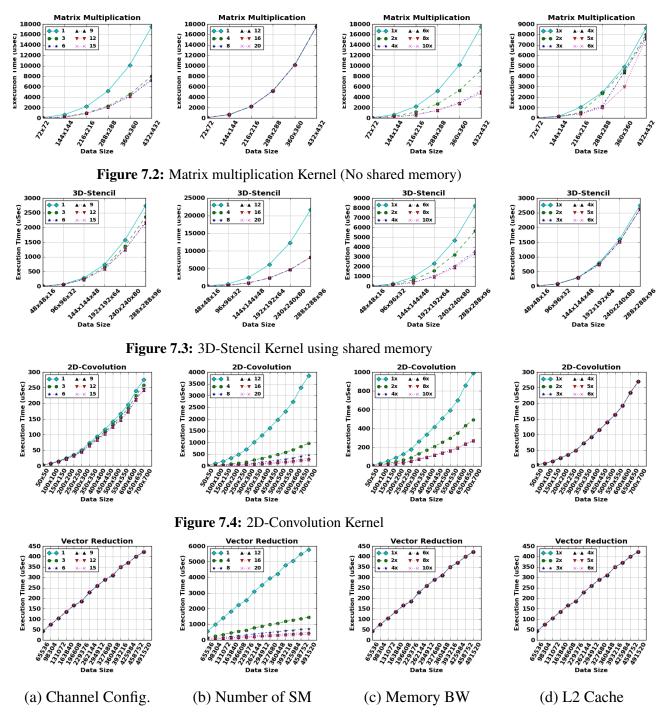

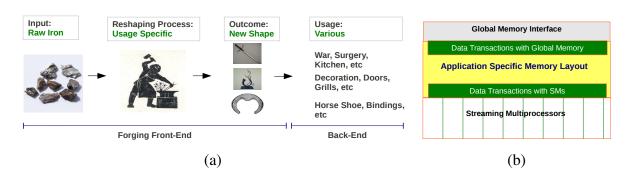

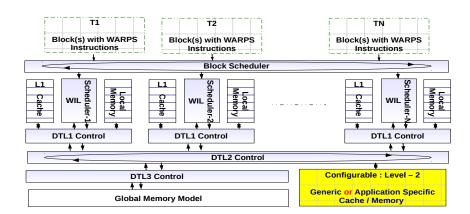

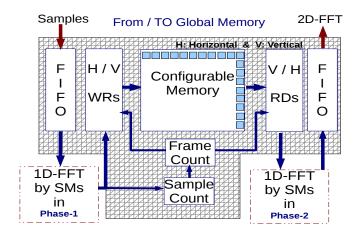

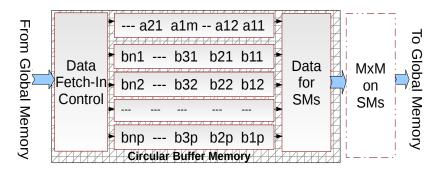

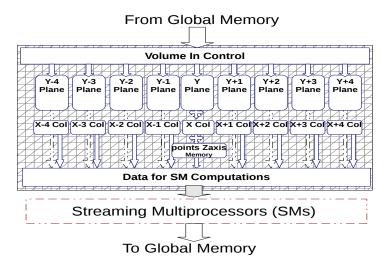

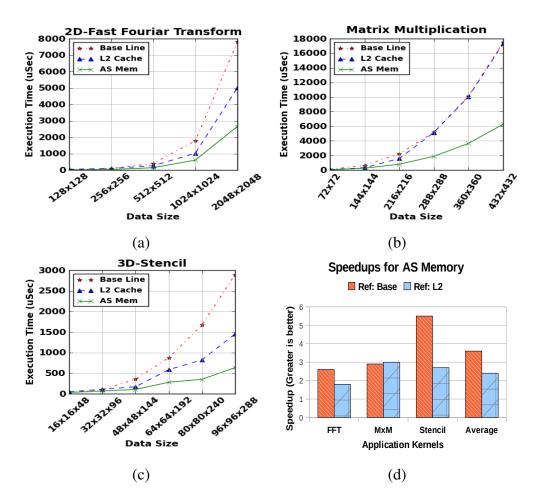

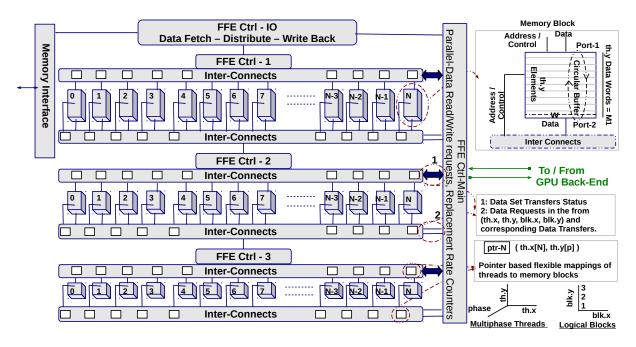

| 7.6 Application Specific Front-Ends                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 7.3        | Design Space Explorations for GPU  7.3.1 Application Kernels  7.3.2 Base Line Architecture  7.3.3 Simulation Platform  7.3.4 Evaluated Architectural Configurations  7.3.4.1 Global Memory Bandwidth  7.3.4.2 Data Channels Between Memory Hierarchy and SMs  7.3.4.3 Cache Memory  7.3.4.4 Streaming Multiprocessors  Results and Discussion                                                                                                   | . 140<br>. 141<br>. 141<br>. 142<br>. 142<br>. 142<br>. 143<br>. 143                            |