**ADVERTIMENT.** L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

# Universitat Politècnica de Catalunya

Departament d'Enginyeria Electrònica

# Design of Frequency Divider with Voltage Controlled Oscillator for 60 GHz Low Power Phase-Locked Loops in 65 nm RF CMOS

Dissertation for the Ph. D. Degree submitted by:

**Davide Brandano**

Thesis Advisor: Jose Luis González Jiménez Commissariat à l'Energie Atomique et les Energies Alternatives (CEA) Laboratoire de l'Electronique et la Technologies de l'Information (LETI) MINATEC Campus, Grenoble, France I hereby certify that the work presented in this thesis is my own and that work performed by others is appropriately cited.

# TABLE OF CONTENTS

| List | of Figures             | 3                                                                                                             | vii      |

|------|------------------------|---------------------------------------------------------------------------------------------------------------|----------|

| Ack  | nowledgm               | nents                                                                                                         | xii      |

| Sun  | nmary                  |                                                                                                               | xiii     |

| 1    | Introduct              | ion                                                                                                           | 16       |

|      | 1.1                    | Why 60 GHz?                                                                                                   | 16       |

|      |                        | 1.1.1 List of Applications                                                                                    | 18       |

|      | 1.2                    | 60 GHz RF Front-End: a cost issue                                                                             | 20       |

|      |                        | 1.2.1 mm-W on CMOS Technology                                                                                 | 21       |

|      | 1.3<br>1.4<br>1.5      | Critical Issues in CMOS Frequency Synthesizers Design Objectives and Methodology Thesis Report Organization   | 24       |

| Bibl | iography .             |                                                                                                               | 30       |

| 2    | Architect              | ures For CMOS Transceivers in mm-W Band                                                                       | 31       |

|      | 2.1                    | Heterodyne Transceiver Architecture                                                                           | 33       |

|      |                        | 2.1.1 Double Conversion Heterodyne                                                                            | 34       |

|      | 2.2<br>2.3<br>2.4      | Homodyne Transceiver Architecture  Summary of Transceivers Architectures  Frequency Synthesizers Architecture | 38       |

|      |                        | 2.4.1 Type-I PLL 2.4.2 Type-II PLL 2.4.3 N-Integer PLL 2.4.4 Fractional-N PLL                                 | 41<br>42 |

|      | 2.5                    | PLL at mm-W Frequencies                                                                                       | 44       |

| Bibl | iography .             |                                                                                                               | 46       |

| 3    | State-Of-              | Art Review of mm-W Frequency Dividers                                                                         | 47       |

|      | 3.1<br>3.2<br>for mm-\ | Frequency Dividers Topologies  Performance and Efficiency Comparison of Frequency Divider  WARDICATIONS       |          |

| 3.3<br>3.4   | PVT Impact in sub-100 nm RF CMOS Technology Current-Mode Logic (CML) Frequency Dividers |                   |

|--------------|-----------------------------------------------------------------------------------------|-------------------|

|              | 3.4.1 Conventional CML Latch                                                            | 58                |

| 3.5          | Injection-Locked Frequency Dividers                                                     | 63                |

|              | 3.5.1 CMOS ILFDs for 60 GHz Applications                                                | 66                |

| 3.6          | Calibration Techniques                                                                  | 70                |

| Bibliography |                                                                                         | 73                |

| 4 60 GHz I   | _C-VCO Design                                                                           | 77                |

| 4.1          | Motivation and Objective                                                                | 78                |

| 4.2          | Circuit Level Analysis of the Inductor                                                  | 79                |

| 4.3          | Varactors Design                                                                        | 81                |

|              | 4.3.1 Fine Tuning Varactor (FTV)                                                        |                   |

| 4.4<br>4.5   | Unloaded Tank Analysis Transistor Sizing and VCO PSS Simulation                         |                   |

|              | 4.5.1 DC Analysis and Loaded Tank Simulation                                            | 91<br>94          |

| 4.6          | VCO Core Simulations including a PMOS Current Source.                                   | 97                |

|              | 4.6.1 Phase Noise Optimization                                                          | 99                |

| 4.7          | Conclusions                                                                             | 103               |

| Bibliography |                                                                                         | 104               |

| 5 60 GHz I   | _C-ILFD Design                                                                          | 105               |

| 5.1<br>5.2   | Motivation, Objective and Methodology Continuous Tuning ILFD Design                     |                   |

|              | 5.2.1 Circuit Level Analysis of the Inductor 5.2.2 Fine-Tuning Varactor Sizing          | 108<br>111<br>114 |

| 5           | 3 Impact of Tank Q in Divide-by-Two ILFD Locking Range   | 124                      |

|-------------|----------------------------------------------------------|--------------------------|

|             | 5.3.1 High Q / Low Q ILFD Tanks Design                   | 131<br>133               |

| 5.          | 4 Dual-Mixing Discrete Tuned ILFD Design                 | 138                      |

|             | 5.4.1 Circuit Level Analysis of the Inductor             | 142<br>143<br>145<br>147 |

| Bibliograph | y 1                                                      | 154                      |

| 6 EM Sir    | nulations - Output Buffers Design - Layout 1             | 155                      |

| 6           | 1 VCO and ILFD Cores Layout                              | 156                      |

|             | 6.1.1 Inductors                                          | 158                      |

| 6           | 2 Output Buffers Design and Layout                       | 172                      |

|             | 6.2.1 ILFD Output Buffers 6.2.2 VCO Output Buffers 6.2.2 |                          |

| 6           | , ,                                                      |                          |

|             | 6.4.1 VCO ON - ILFD OFF                                  | 200                      |

| 6           | 5 Conclusions                                            | 209                      |

| Bibliograph | y 2                                                      | 211                      |

| 7 PVT V     | ariations Simulation and Calibration Technique2          | 212                      |

| 7.<br>7.    | 1 Introduction                                           |                          |

|             | 7.2.1 ILFD-VCO Locking                                   |                          |

| 7.          | 3 Calibration Technique2                                 | 220                      |

| 7.4          | Conclusions                               | 224 |

|--------------|-------------------------------------------|-----|

| Bibliography |                                           | 225 |

| 8 Measure    | ments                                     | 226 |

| 8.1<br>8.2   | Introduction<br>VCO ON - ILFD OFF         |     |

|              | 8.2.1 VCO Post-Measurement Simulation     |     |

| 8.3          | VCO OFF - ILFD ON                         | 236 |

|              | 8.3.1 ILFD Post-Measurement Simulation    | 241 |

| 8.4<br>8.5   | VCO ON - ILFD ONConclusions               |     |

| Bibliography |                                           | 249 |

| 9 Conclusi   | ons                                       | 250 |

| 9.1          | Summary of Contributions and Future Works | 252 |

| Referencies  |                                           | 253 |

| Appendix A   |                                           | 254 |

| Appendix B   |                                           | 257 |

# LIST OF FIGURES

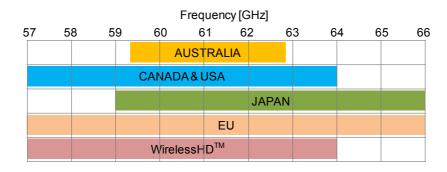

| Figure 1: Spectrum Available around 60 GHz                                                                | xiv |

|-----------------------------------------------------------------------------------------------------------|-----|

| Figure 2: Mobile users Standards                                                                          | 16  |

| Figure 3: Potential 60 GHz applications                                                                   | 17  |

| Figure 4: Long and Short Range Radar Applications                                                         | 19  |

| Figure 5: Indoor network scenario and interfacing to the outdoor network                                  | 19  |

| Figure 6: emerging mm-W imaging                                                                           | 20  |

| Figure 7: CMOS device and technology evolution for Si-based RF Integrated Circuits according              | to  |

| ITRS forecast                                                                                             | 21  |

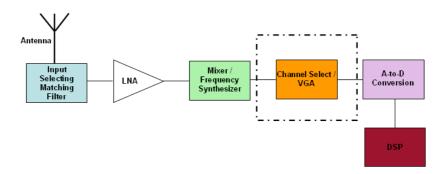

| Figure 8: Generic receiver block diagram                                                                  | 31  |

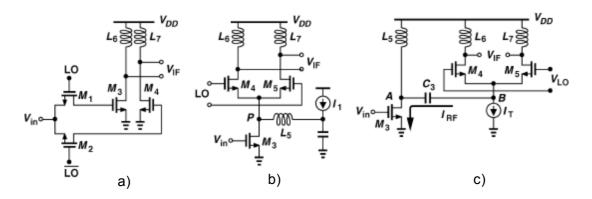

| Figure 9: Mixer topologies: a) passive, b) active with auxiliary current path, c) active with capacit     | ive |

| coupling                                                                                                  | 32  |

| Figure 10: Generic heterodyne down-conversion block diagram                                               | 33  |

| Figure 11: Double Conversion Heterodyne receiver                                                          | 34  |

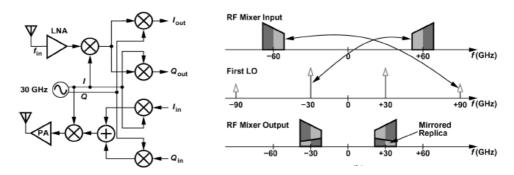

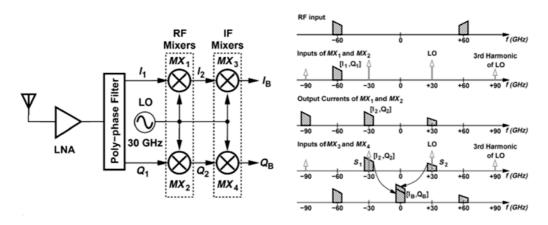

| Figure 12: Half-RF heterodyne transceiver architecture: receiver's scheme (left); signals spectra (right) | 35  |

| Figure 13: Heterodyne receiver with 30 GHz LO: receiver's scheme (left); signal spectra along the         | ne  |

| receiver chain (right)                                                                                    | 36  |

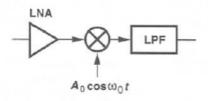

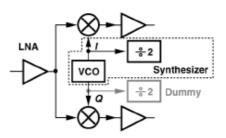

| Figure 14: Direct conversion architecture                                                                 | 37  |

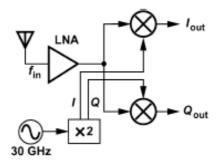

| Figure 15: Zero-IF architecture with frequency doubler                                                    | 38  |

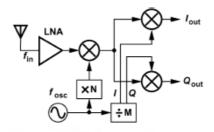

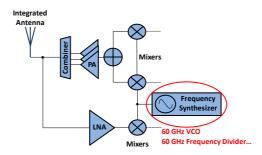

| Figure 16: 60 GHz Direct-Conversion Transceiver for mm-W band                                             | 39  |

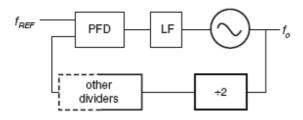

| Figure 17: mm-W band PLL architecture                                                                     | 40  |

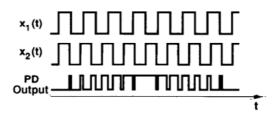

| Figure 18: Input and Output PD waveforms                                                                  | 41  |

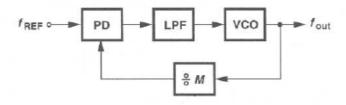

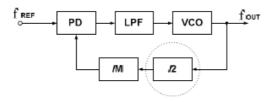

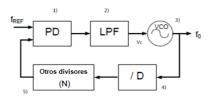

| Figure 19: N-Integer PLL architecture                                                                     | 42  |

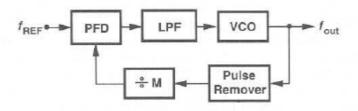

| Figure 20: Fractional-N PLL with prescaler                                                                | 43  |

| Figure 21: N-fractional PLL with dual modulus prescaler                                                   | 43  |

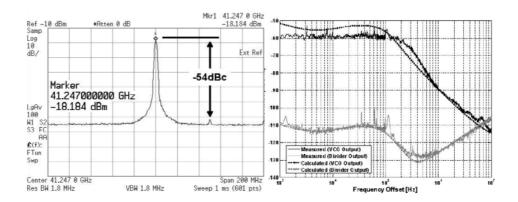

| Figure 22: Output spectrum of Figure 19 PLL (left); Frequency Synthesizer Phase Noise at VCO              | )   |

| and at FD chain output (right)                                                                            | 45  |

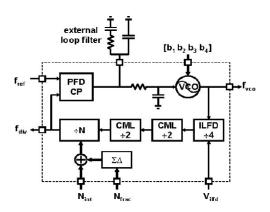

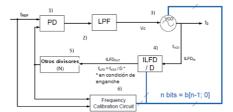

| Figure 23: Typical high speed PLL blocks diagram                                                          | 48  |

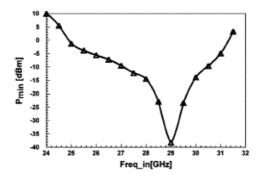

| Figure 24: Frequency Divider input sensitivity                                                            | 48  |

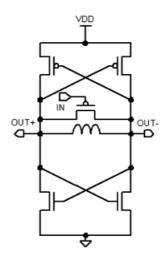

| Figure 25: Conventional ILFD structure                                                                    | 50  |

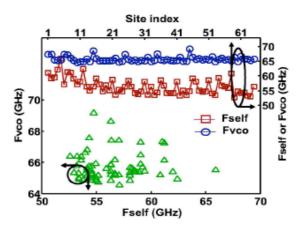

| Figure 26: Inter-die variation of VCO frequency and FD self-oscillation frequency over a wafer w          | ith |

| scattering diagram                                                                                        | 53  |

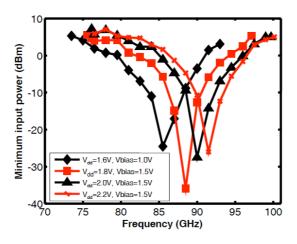

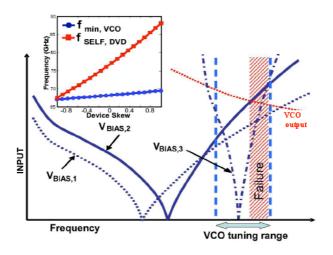

| Figure 27: Sensitivity curves at different V <sub>BIAS</sub>                                              | 54  |

| Figure 28: Effects of voltage variations in input sensitivity and locking-range                           | 55  |

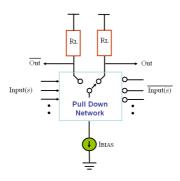

| Figure 29: Generic CML structure                                                                          | 56  |

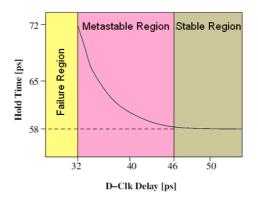

| Figure 30: Hold Time for MOS CML latch                                                                    | 57  |

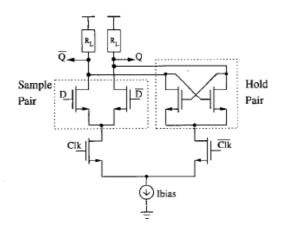

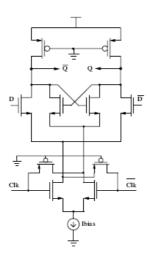

| Figure 31: Conventional CML latch                                                                         | 58  |

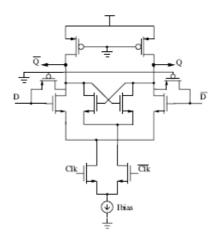

| Figure 32: Feedback CML latch                                                                             | 59  |

| Figure 33: Clock-feedback CML latch                                                                       | 60  |

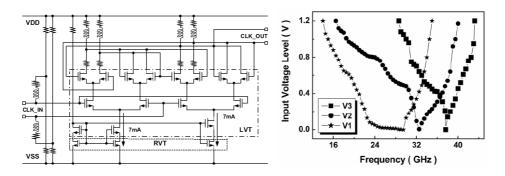

| Figure 34: 43 GHz CML frequency divider (left). Input Sensitivity curves (right)                          | 61  |

| Figure 35: 40 GHz CML FD w/o self-oscillation condition (left). Measured input sensitive curve of         | f   |

| the divider (right)                                                                                       | 62  |

| Figure 36: Conventional ILFD                                                                              | 64  |

| Figure 37: Direct ILFD arquitecture                                                                       | 65  |

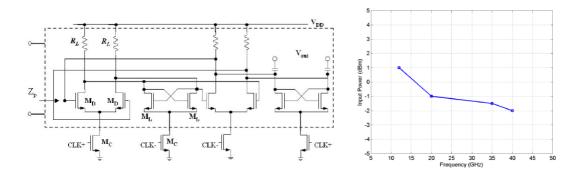

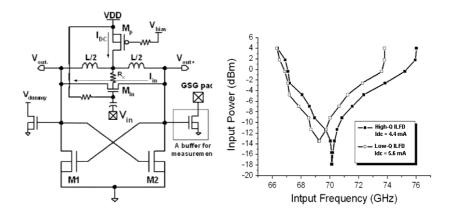

| Figure 38: Direct structure for the high -Q ILFD reported (left). Input sensitivity curves (right)        | 67  |

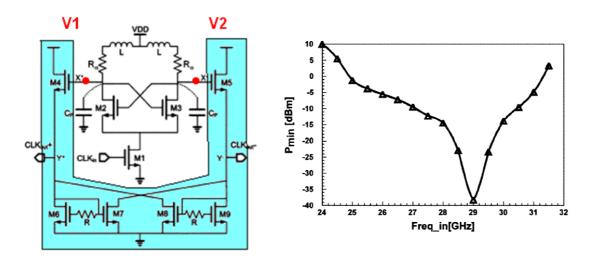

| Figure 39: 30 GHz ILFD schematic (left). Input sensitivity curves (right)                                 | 68  |

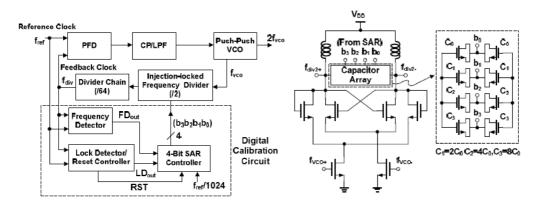

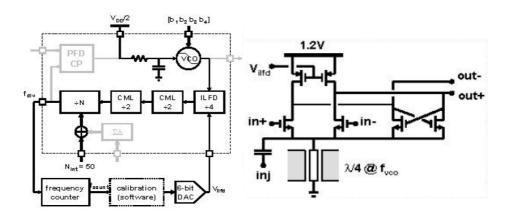

| Figure 40: Digitally calibrated 60 GHz PLL (left). Divide-by-two ILFD schematic (right)                   | 70  |

| Figure 41: Calibration circuit of PLL [1] (left). Divide-by-4 ILFD schematic (right)                      | 71  |

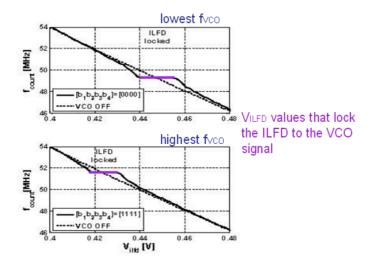

| Figure 42: Calibration algorithm plot                                                                                                    | 72         |

|------------------------------------------------------------------------------------------------------------------------------------------|------------|

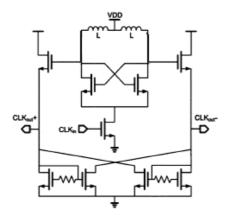

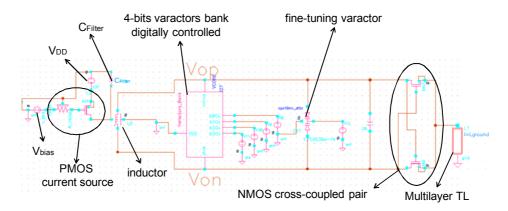

| Figure 43: 60 GHz LC-VCO core schematic                                                                                                  | 77         |

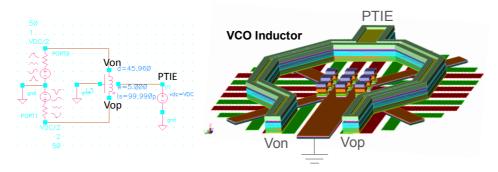

| Figure 44: Schematic circuit for Inductor analysis (left). Inductor 3D layout view (right)                                               | 80         |

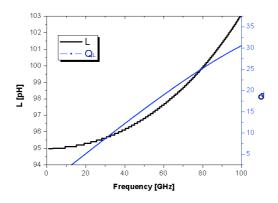

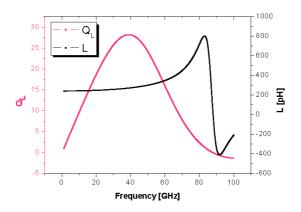

| Figure 45: Inductor quality factor (Q) and inductance                                                                                    | 80         |

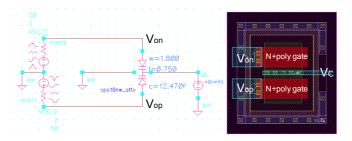

| Figure 46: cp018nw_atto (1x1) varactor available in the kit                                                                              | 81         |

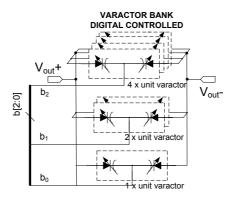

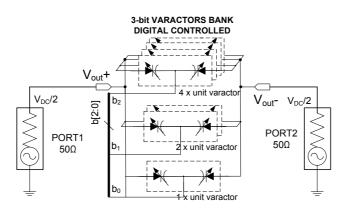

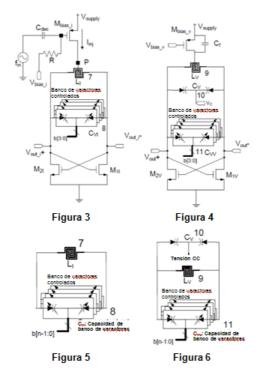

| Figure 47: 3-bit varactors bank binary scaled                                                                                            | 82         |

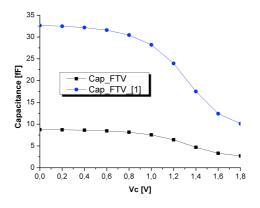

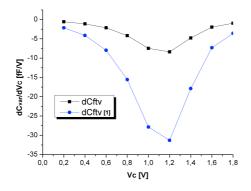

| Figure 48: FTV capacitance comparison                                                                                                    | 83         |

| Figure 49: FTV capacitance variation                                                                                                     | 84         |

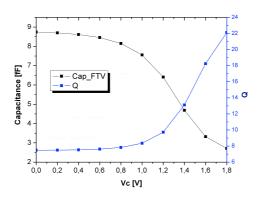

| Figure 50: FTV capacitance and quality factor                                                                                            | 84         |

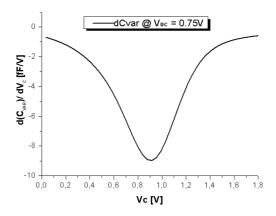

| Figure 51: FTV capacitance variation @ V <sub>DC</sub> =0.75V                                                                            | 85         |

| Figure 52: Simulated UVC capacitance and quality factor                                                                                  | 86         |

| Figure 53: Schematic circuit for VCO tank S-parameters simulation                                                                        | 87         |

| Figure 54: Tank resonance frequency curves                                                                                               | 88         |

| Figure 55: C <sub>F</sub> impact on tuning range                                                                                         | 89         |

| Figure 56: Real{1/Y <sub>D</sub> } curves                                                                                                | 90         |

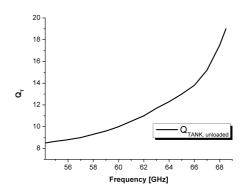

| Figure 57: Unloaded tank quality factor                                                                                                  | 91         |

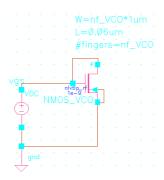

| Figure 58: Schematic circuit for NMOS DC simulation                                                                                      | 91         |

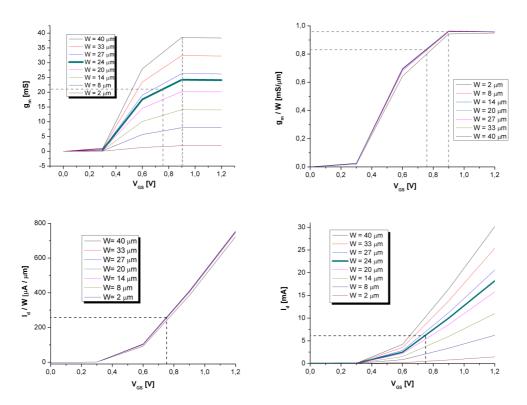

| Figure 59: NMOS DC simulation. $g_m$ (upper-left); $g_m$ /W (upper-right); $I_d$ (lower-right); $I_d$ /W (lower-                         |            |

| rigare oc. Times 20 simulation. giii (apportion), giii (apportight), ii (ionor light), iii (ionor                                        | 92         |

| Figure 60: Loaded tank circuit for [S] and DC simulations                                                                                | 93         |

| Figure 61: Resonance Frequency and quality factor of the loaded tank                                                                     | 93         |

| Figure 62: 60 GHz VCO schematic circuit for PSS and PN analysis: ideal current source                                                    | 94         |

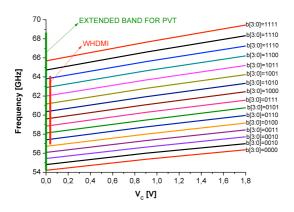

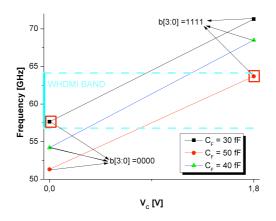

| Figure 63: PSS simulation: VCO tuning range (left); VCO output curves for b[3:0]=1111 (right)                                            | 94         |

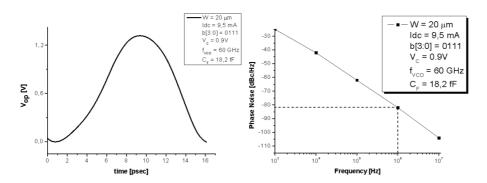

| Figure 64: VCO output voltage (left); VCO PN @ 1 MHz frequency offset (right)                                                            | 95         |

| Figure 65: VCO output wave (left) and its phase noise (right) for reduced W                                                              | 96         |

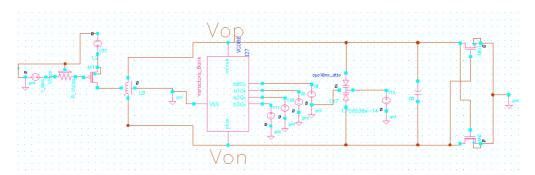

| Figure 66: 60 GHz VCO with PMOS current source                                                                                           | 97         |

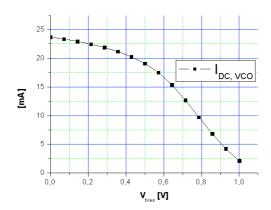

| Figure 67: I <sub>dc,VCO</sub> vs V <sub>bias</sub>                                                                                      | 98         |

| Figure 68: VCO core. Tuning range, V <sub>op</sub> output frequency (left); PN @ 1 MHz frequency offset                                  | 90         |

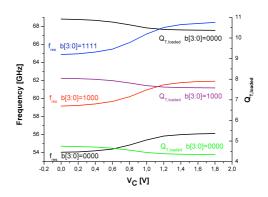

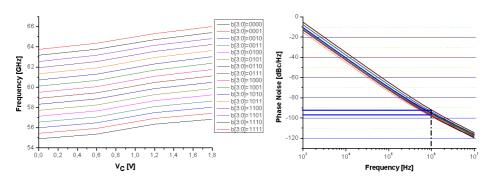

| (right)                                                                                                                                  | 99         |

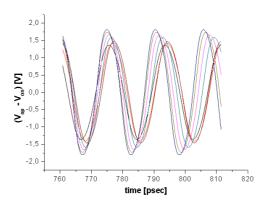

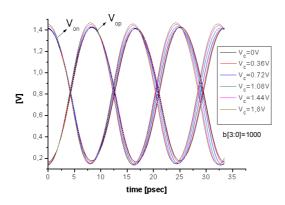

| Figure 69: Differential output waveforms V <sub>op</sub> -V <sub>on</sub>                                                                | 99         |

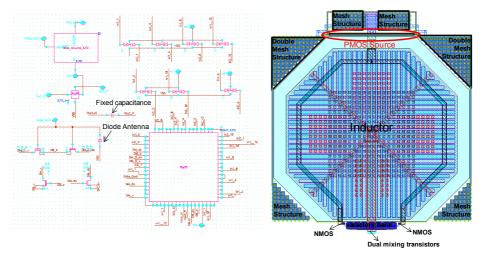

| Figure 70: VCO core schematic                                                                                                            | 100        |

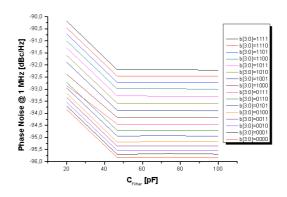

| Figure 71: PN @ 1 MHz vs C <sub>Filter</sub> , V <sub>C</sub> = 0.9V                                                                     | 100        |

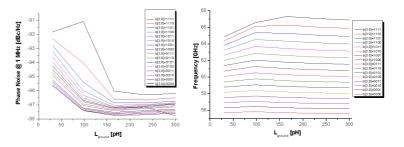

| Figure 72: PN @ 1 MHz vs L <sub>ground</sub> . $V_C = 0.9V$ (left); VCO output frequency $V_{op}$ vs L <sub>ground</sub> . $V_C = 0.9V$  |            |

| (right)                                                                                                                                  | 101        |

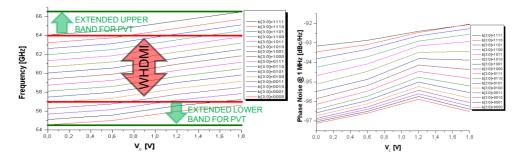

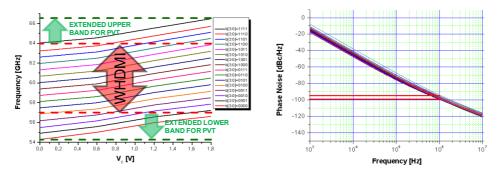

| Figure 73: 60 GHz VCO core. Frequency curves (left); Phase Noise (right)                                                                 | 101        |

|                                                                                                                                          |            |

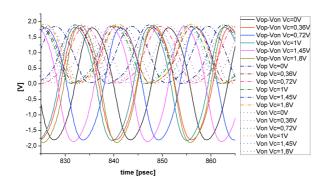

| Figure 74: VCO Output waveforms for V <sub>op</sub> , V <sub>on</sub> and (V <sub>op</sub> - V <sub>on</sub> ); b[3:0]=1111              | 102        |

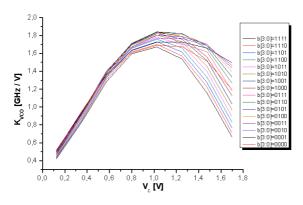

| Figure 75: K <sub>VCO</sub>                                                                                                              | 102<br>107 |

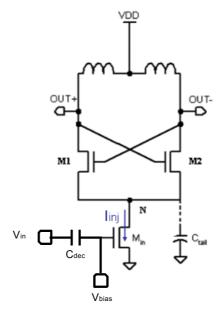

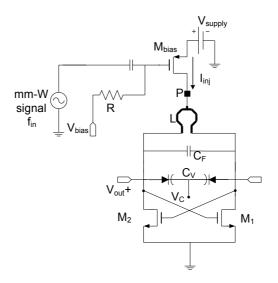

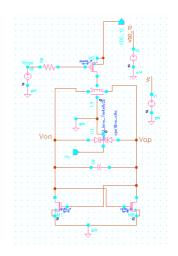

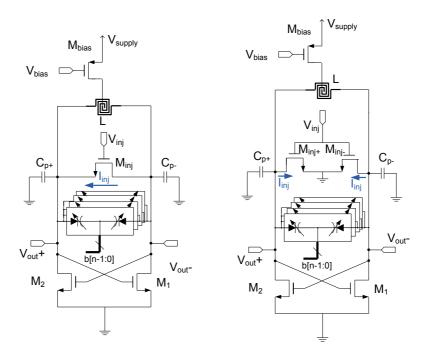

| Figure 76: Continuous tuning 60 GHz divide-by-two ILFD schematic                                                                         |            |

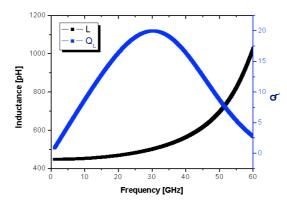

| Figure 77: Inductor quality factor and inductance                                                                                        | 108        |

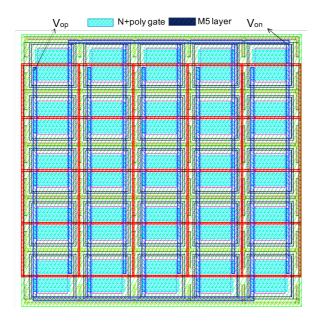

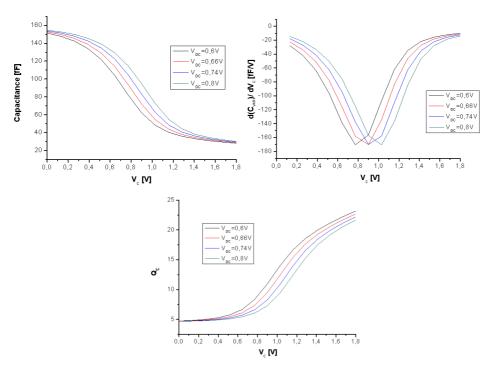

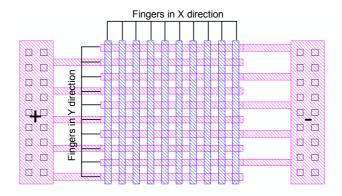

| Figure 78: Layout of the 5x5 cpo18nw_atto varactor, W=1.8 µm, L=0.75 µm                                                                  | 110        |

| Figure 79: Varactor parameters at 30 GHz for different V <sub>DC</sub> : varactor capacitance (upper-left);                              | 440        |

| varactor capacitance variation dC/dV <sub>c</sub> (upper-right); varactor quality factor (lower)                                         | 110        |

| Figure 80: Schematic circuit for continuous tuning ILFD tank                                                                             | 111        |

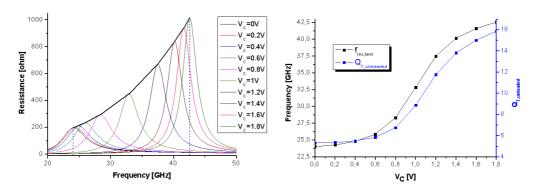

| Figure 81: Tank parallel equivalent resistance R <sub>p, eq</sub> (left); quality factor and resonance frequence                         |            |

| the unloaded tank (right)                                                                                                                | 112        |

| Figure 82: Continuous tuning ILO schematic                                                                                               | 113        |

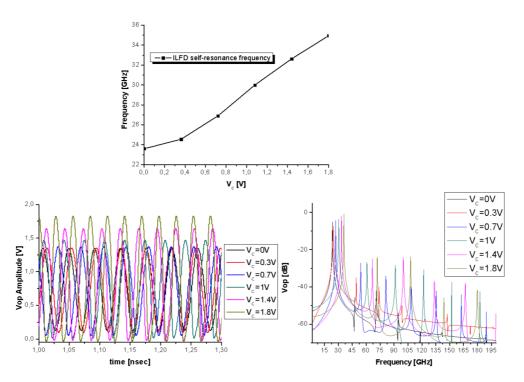

| Figure 83: ILFD self-resonance frequency (upper); single-ended V <sub>op</sub> output waveforms (lower-le                                |            |

| and their DFTs (lower-right)                                                                                                             | 114        |

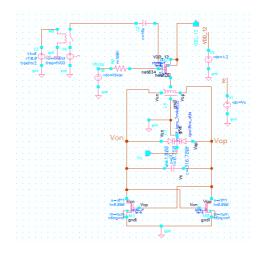

| Figure 84: 60 GHz divide-by-two continuous tuning ILFD                                                                                   | 115        |

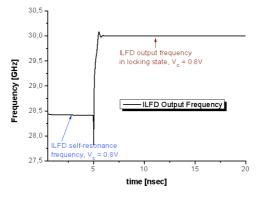

| Figure 85: ILFD output frequency, locking state, V <sub>C</sub> =0.8, f <sub>inj</sub> =60 GHz, V <sub>inj</sub> =300mV                  | 115        |

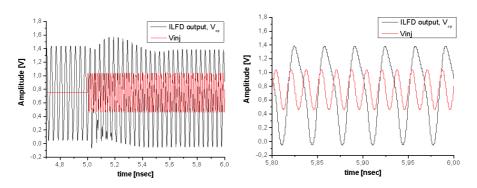

| Figure 86: $V_{inj}(t)$ and $V_{op}(t)$ , locking state, $V_{c}$ =0.8V, $f_{inj}$ =60 GHz, $V_{inj}$ =300mV at two different time scales | 116        |

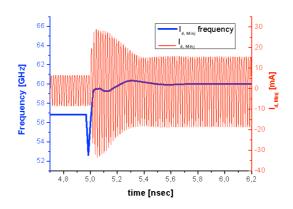

| Figure 87: M <sub>inj</sub> current, locking state, V <sub>C</sub> =0.8, f <sub>inj</sub> =60 GHz, V <sub>inj</sub> =300mV               | 116        |

| Figure | 88: ILFD output frequency, no-locking, V <sub>C</sub> =0.8, V <sub>ini</sub> =300mV                                           | 117    |

|--------|-------------------------------------------------------------------------------------------------------------------------------|--------|

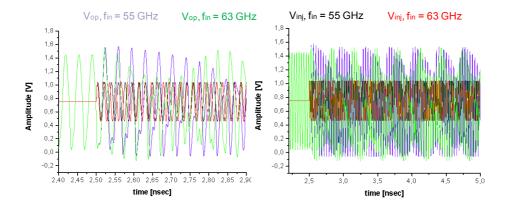

| Figure | 89: $V_{inj}(t)$ and $V_{op}(t)$ , no-locking state, $V_{C}=0.8$ , $V_{inj}=300$ mV at two different time scales              | 118    |

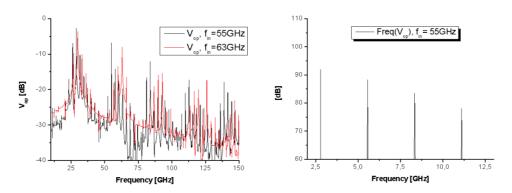

| Figure | 90: V <sub>op</sub> (t) DFTs (left); ILFD output frequency DFT (right). No-locking state V <sub>c</sub> =0.8,                 |        |

| •      | V <sub>ini</sub> =300mV                                                                                                       | 118    |

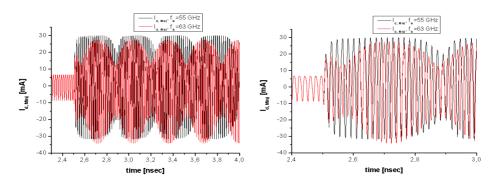

| Figure | 91: Available I <sub>inj</sub> in no-locking state, V <sub>C</sub> =0.8, V <sub>inj</sub> =300mV at two different time scales | 119    |

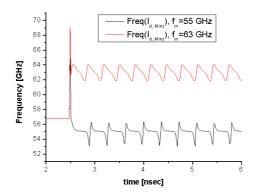

| -      | 92: Frequency function of the curves of Figure 91                                                                             | 119    |

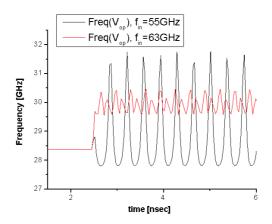

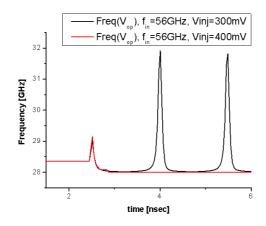

| -      | 93: ILFD output frequency, V <sub>C</sub> =0.8                                                                                | 120    |

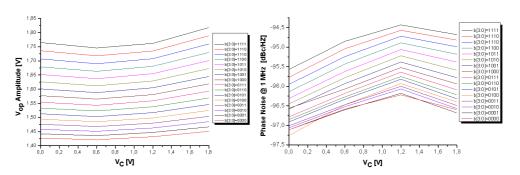

| •      | 94: ILFD output frequencies, V <sub>C</sub> = 1.8V                                                                            | 121    |

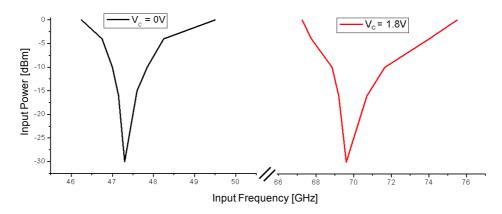

| -      | 95: Lower and upper ILFD input sensitivity curves                                                                             | 121    |

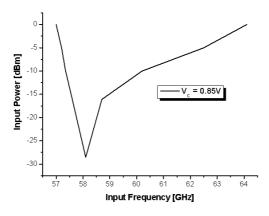

|        | 96: ILFD Input sensitivity curve, V <sub>C</sub> = 0.85V                                                                      | 122    |

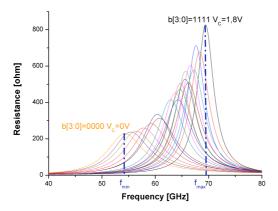

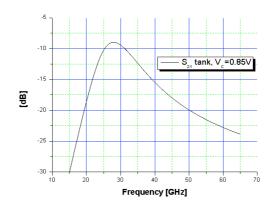

| -      | 97: S <sub>21</sub> ILFD tank                                                                                                 | 123    |

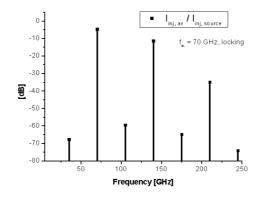

| -      | 98: I <sub>ini,av</sub> /I <sub>ini,source</sub> , V <sub>C</sub> =1.8                                                        | 123    |

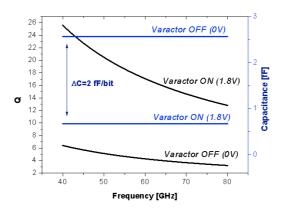

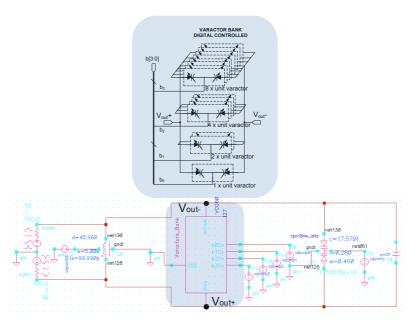

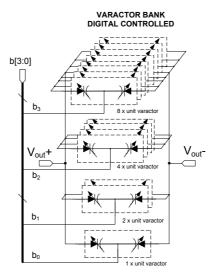

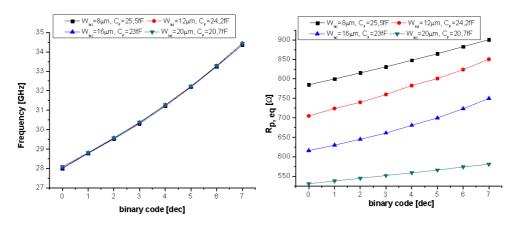

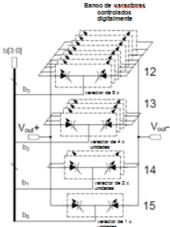

| -      | 99: 4-bit varactors bank binary scaled                                                                                        | 126    |

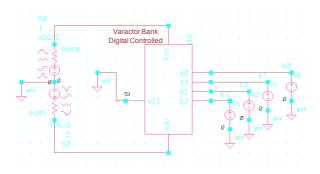

|        | 100: Schematic circuit for 4-bit varactors bank simulation                                                                    | 126    |

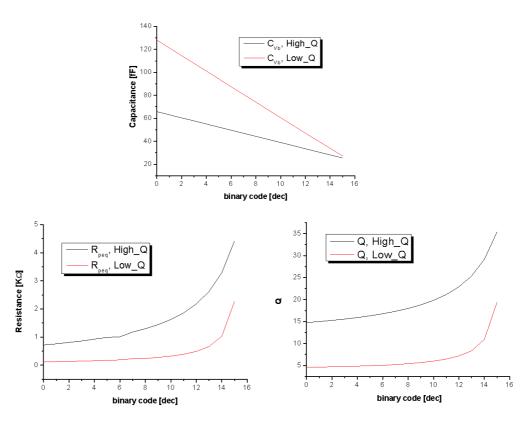

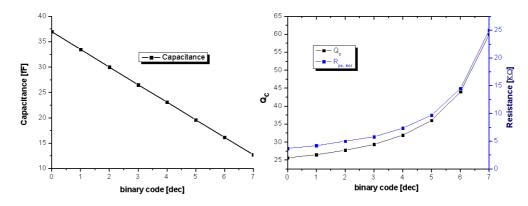

| -      | 101: Capacitance (upper), parallel losses (lower-left) and quality factor (lower-right) of t                                  |        |

| riguie | High/Low Q varactors banks                                                                                                    | 127    |

| Eiguro |                                                                                                                               |        |

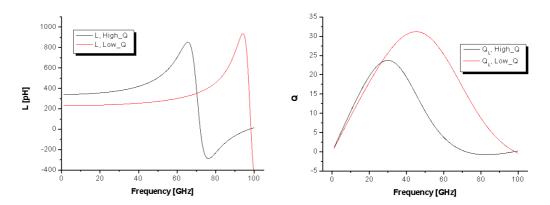

| -      | 102: High Q / Low Q inductance (left) and Q (right)                                                                           | 129    |

| -      | 103: Schematic circuit for low /high Q tank simulation                                                                        | 129    |

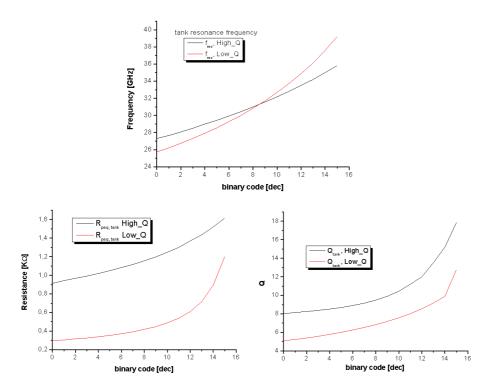

| •      | 104: Low / high Q tank parameters                                                                                             | 130    |

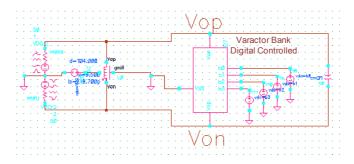

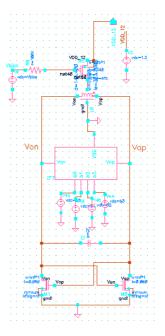

| -      | 105: 4-bit discrete tuned ILO                                                                                                 | 131    |

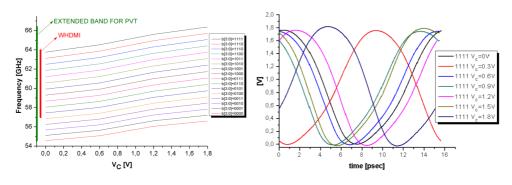

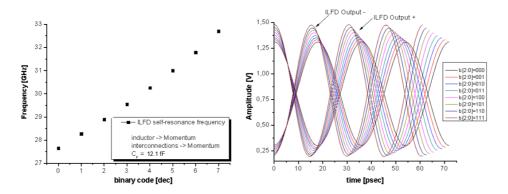

| -      | 106: Low / high Q ILFD self-resonance frequencies                                                                             | 132    |

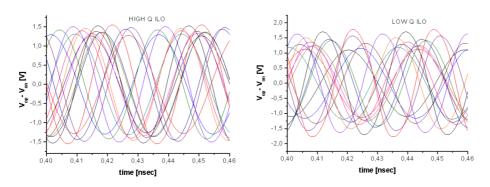

| -      | 107: Low / high Q ILFD differential output in self-oscillation                                                                | 132    |

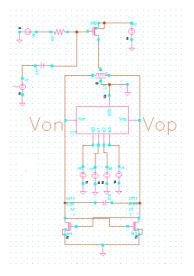

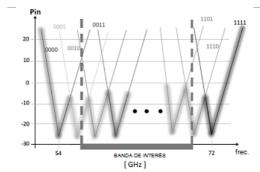

| -      | 108: 4-bit discrete tuned ILFD                                                                                                | 133    |

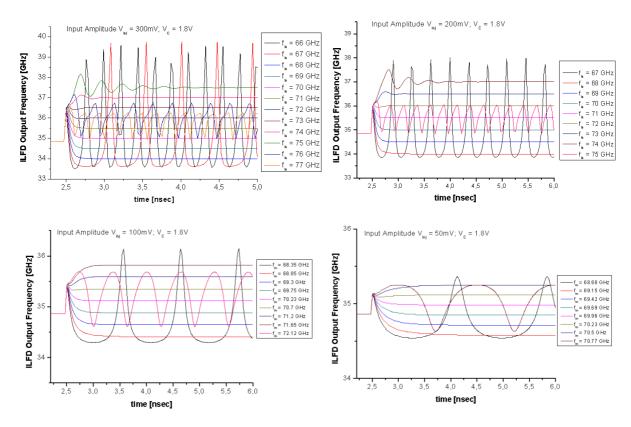

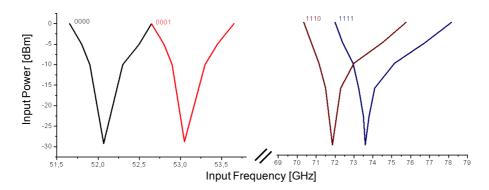

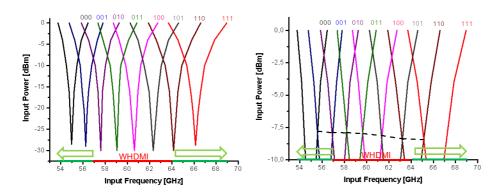

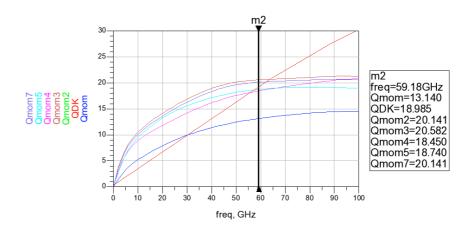

| -      | 109: High Q 4-bit discrete tuned ILFD input sensitivity curves                                                                | 133    |

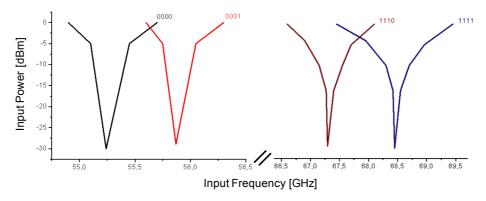

| •      | 110: Low Q 4-bit discrete tuned ILFD input sensitivity curves                                                                 | 134    |

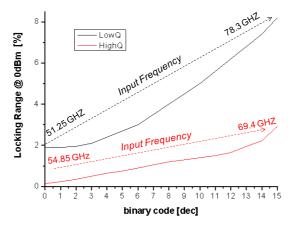

| -      | 111: Locking range of the single sensitivity curve                                                                            | 134    |

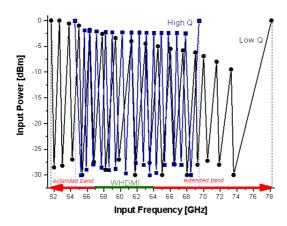

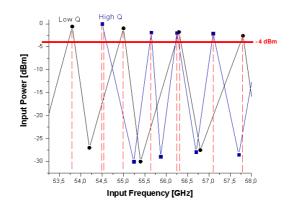

| Figure | 112: Resulting discrete tuned ILFD input sensitivity curves                                                                   | 136    |

| Figure | 113: Sensitivity analysis                                                                                                     | 137    |

| Figure | 114: ILFDs discrete tuned: conventional direct injection (left), dual-mixing injection (righ                                  | t) 139 |

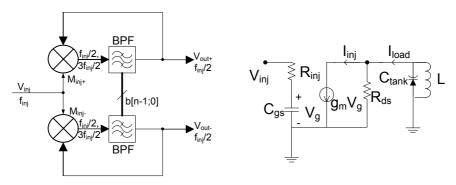

| Figure | 115: Dual-mixing ILFD block diagram (left); small signal circuit (right)                                                      | 139    |

| Figure | 116: Inductance and inductor quality factor for dual-mixing ILFD                                                              | 141    |

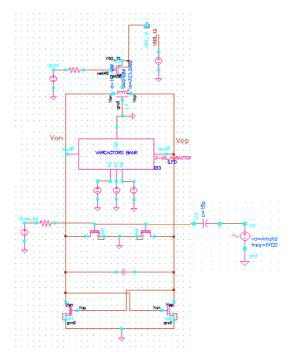

| Figure | 117: Schematic circuit for 3-bit varactors bank used for S-parameters simulation                                              | 142    |

| Figure | 118: 3-bit varactors bank for dual mixing ILFD. Capacitance (left); quality factor and part                                   | rallel |

|        | equivalent losses (right)                                                                                                     | 143    |

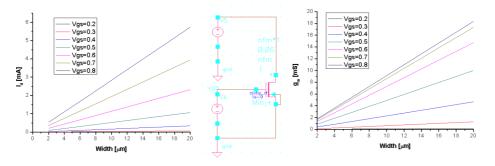

| Figure | 119: Injection transistor: DC current (left); g <sub>m</sub> (right)                                                          | 143    |

| Figure | 120: Dual-mixing ILFD tank schematic circuit                                                                                  | 144    |

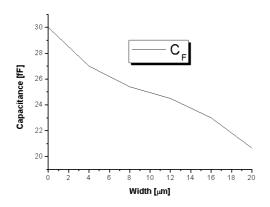

| Figure | 121: Tank fixed-capacitance as a function of W <sub>inj</sub>                                                                 | 144    |

| Figure | 122: Tank resonance frequencies (left); parallel equivalent losses (right)                                                    | 145    |

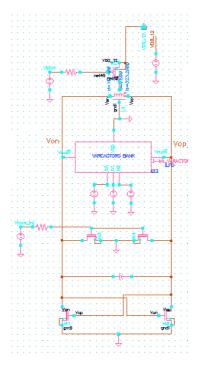

| Figure | 123: 3-bit discrete tuned dual-mixing ILO                                                                                     | 146    |

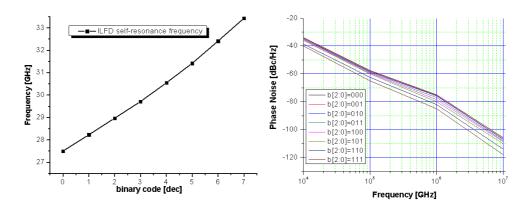

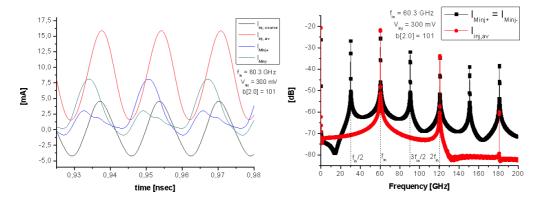

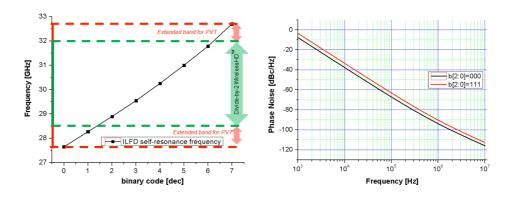

| Figure | 124: 3-bit dual mixing ILFD self-resonance frequencies (left); Phase Noise (right)                                            | 147    |

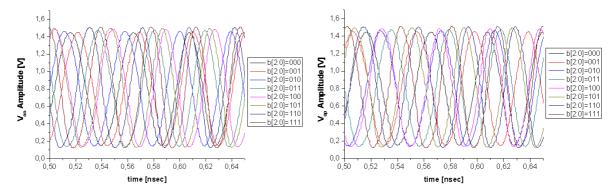

| Figure | 125: ILFD output waveforms in self-oscillation                                                                                | 147    |

| Figure | 126: 3-bit discrete tuned dual-mixing divide-by-two ILFD                                                                      | 148    |

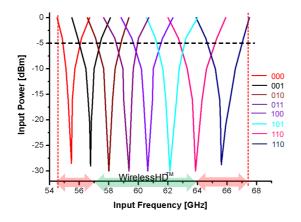

| Figure | 127: 3-bit discrete tuned dual-mixing divide-by-two ILFD input sensitivity curves (left). D                                   | etail  |

|        | for high input frequency (right)                                                                                              | 148    |

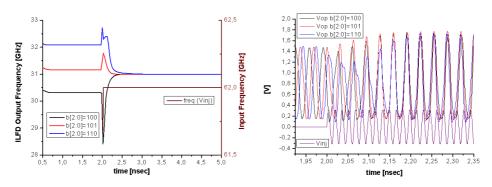

| Figure | 128: ILFD locking for three different binary codes                                                                            | 149    |

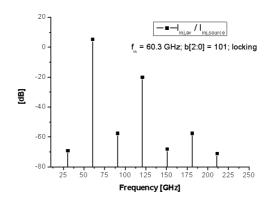

| Figure | 129: ILFD currents in locking state: f <sub>in</sub> =60.3 GHz                                                                | 150    |

|        | 130: Dual-mixing ILFD: I <sub>inj,av</sub> /I <sub>inj,source</sub>                                                           | 151    |

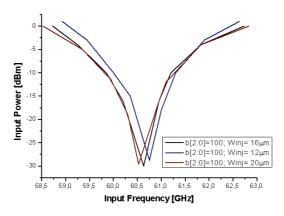

|        | 131: ILFD sensitivity curve (b[2:0]=100) for different injection transistor width                                             | 151    |

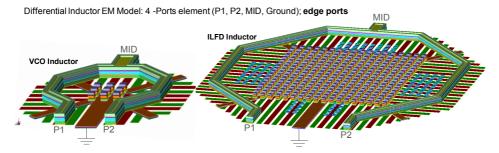

| -      | 132: 3D view of VCO inductor (left) and ILFD inductor (right) for EM simulation                                               | 156    |

| -      | 133: Momentum extracted model for inductor                                                                                    | 156    |

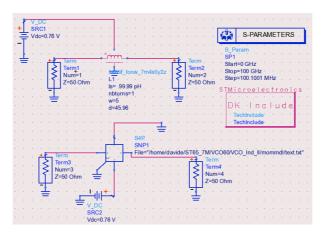

| -      | 134: Test bench circuit for inductors with ADS                                                                                | 157    |

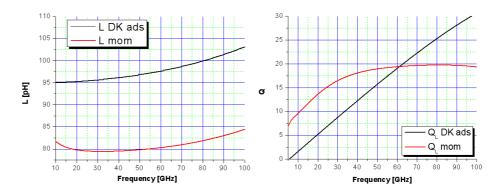

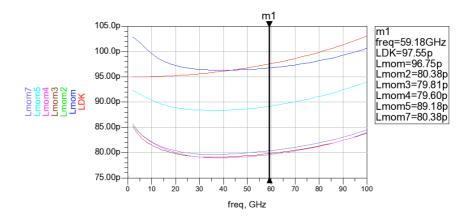

| -      | 135: VCO differential inductor: inductance (left); quality factor (right)                                                     | 157    |

| -      | 136: ILFD differential inductor: inductance (left); quality factor (right)                                                    | 158    |

|        |                                                                                                                               |        |

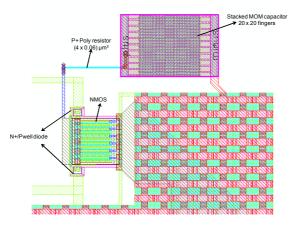

| Figure 13  | 7: VCO 4-bit varactors bank                                                                                                       | 159 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 13  | 8: NMOS layout in deep-Nwell (left); schematic of resulting N diodes                                                              | 160 |

| Figure 139 | 9: VCO active area layout interconnection                                                                                         | 160 |

| Figure 140 | 0: Momentum Vias and Contacts simplifications                                                                                     | 161 |

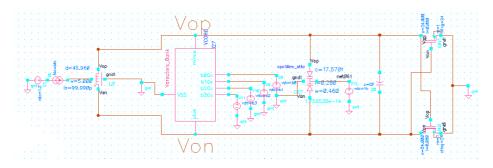

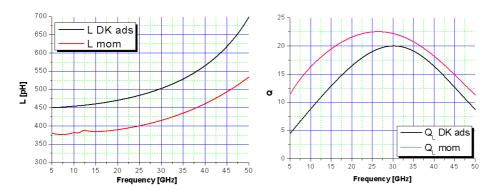

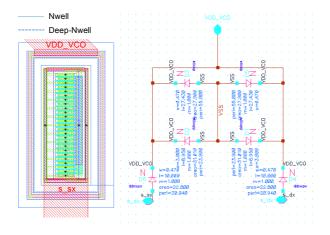

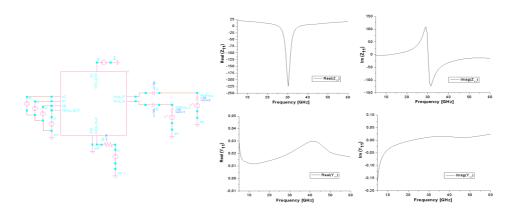

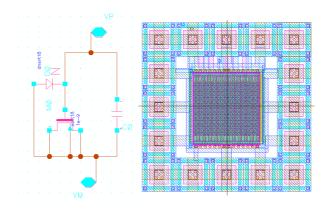

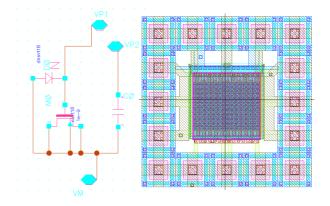

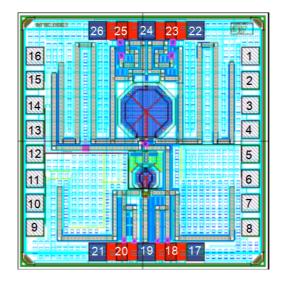

| Figure 14  | 1: VCO core schematic including EM extracted models (left). VCO core layout (right)                                               | 161 |

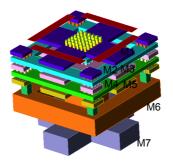

| Figure 14  | 2: Mesh Single 3D view                                                                                                            | 162 |

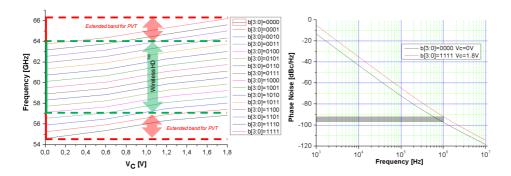

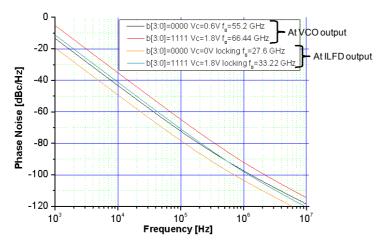

| igure 14   | 3: 60 GHz VCO core. Frequency curves (left); Phase Noise (right)                                                                  | 163 |

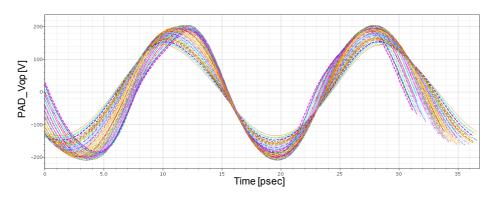

| igure 14   | 4: VCO core single-ended output waveforms                                                                                         | 164 |

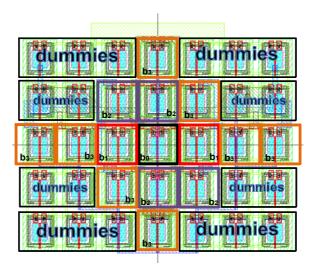

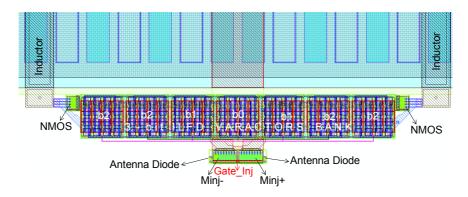

| igure 14   | 5: ILFD 3-bit varactors bank layout                                                                                               | 164 |

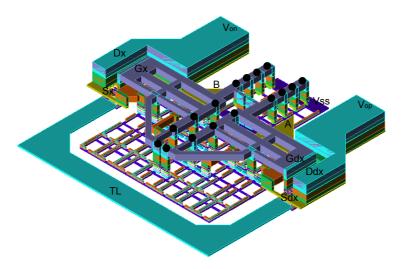

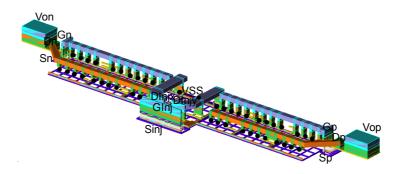

| igure 140  | 6: 3D view of the ILFD active area interconnections                                                                               | 165 |

| igure 14   | 7: ILFD core schematic including EM extracted models (left). ILFD core layout (right)                                             | 165 |

| igure 14   | 8: ILFD core: active area layout                                                                                                  | 166 |

| igure 149  | 9: Mesh Double 3D view                                                                                                            | 167 |

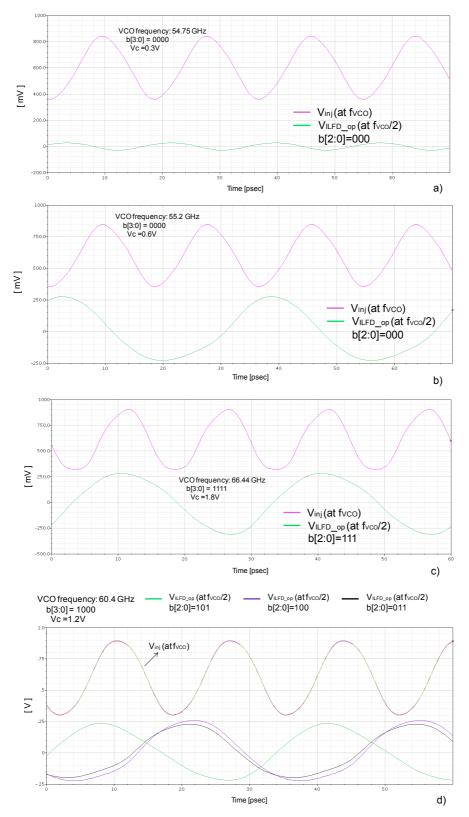

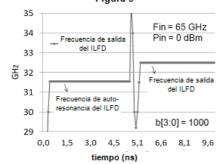

| Figure 150 | 0: Divide-by-two ILFD tuning range (left). Single-ended output waveforms (right)                                                  | 168 |

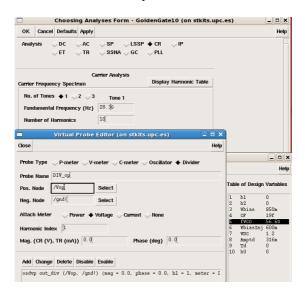

| Figure 15  | 1: GoldenGate windows to set the simulation for locking analysis with HB                                                          | 169 |

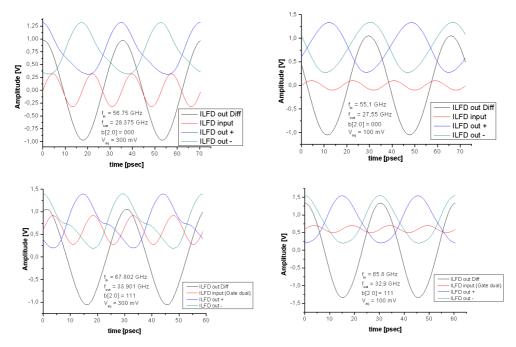

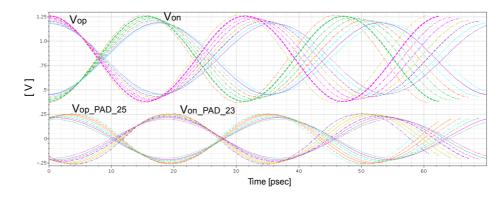

| Figure 15  | 2: Some ILFD waveforms in locking states                                                                                          | 170 |

| Figure 15  | 3: ILFD input sensitivity curves                                                                                                  | 171 |

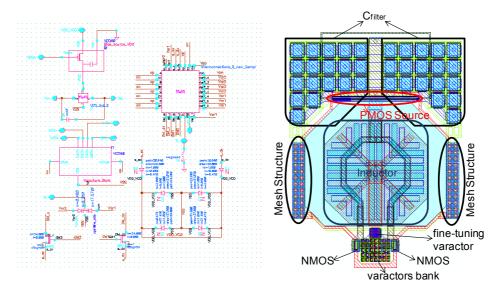

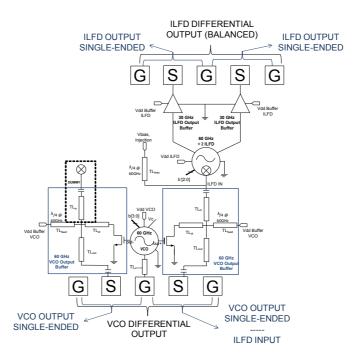

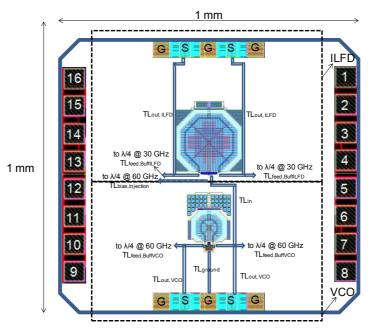

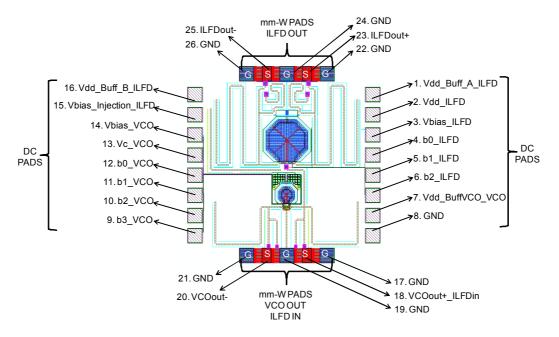

| Figure 15  | 4: Preliminary block diagram of the chip                                                                                          | 173 |

| _          | 5: Common source amplifier as output buffer                                                                                       | 173 |

| Figure 150 | 6: Preliminary chip floor-plan                                                                                                    | 174 |

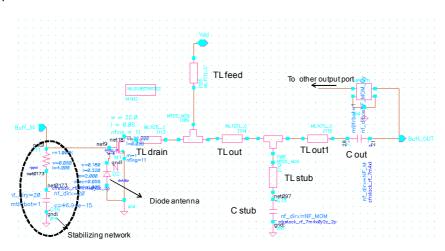

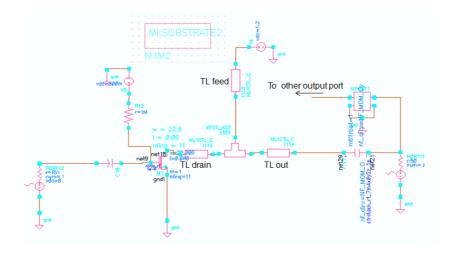

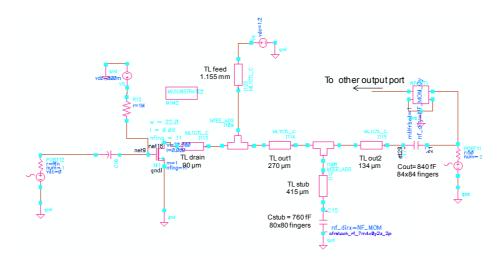

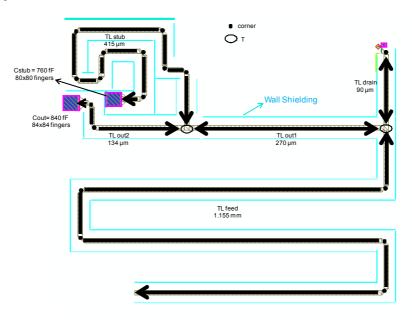

| _          | 7: ILFD output buffer schematic                                                                                                   | 176 |

| _          | 8: Test bench for ILFD output impedance (left). Z <sub>11</sub> and Y <sub>11</sub> plots (right)                                 | 177 |

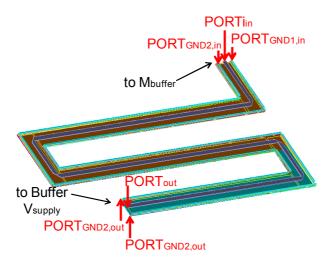

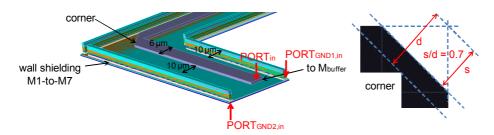

| Figure 159 | 9: Detailed images of the ground plane implementation for the TLs                                                                 | 177 |

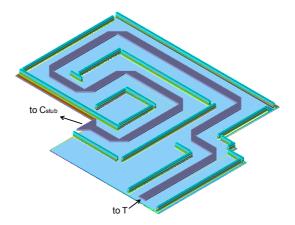

| _          | 0: 3D view of the 30 GHz λ/4 TL feed for ILFD buffer                                                                              | 178 |

| Figure 16  | 1: Detail of Figure 160 (left). Corners geometry (right)                                                                          | 178 |

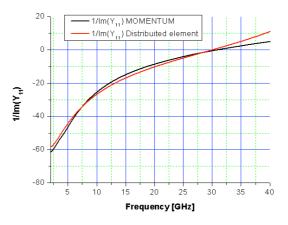

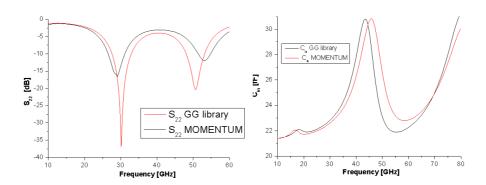

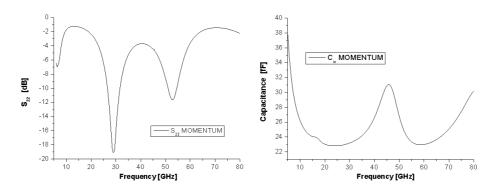

| -          | 2: 30 GHz λ/4 TL parameter                                                                                                        | 179 |

|            | 3: First version of ILFD buffer                                                                                                   | 180 |

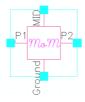

| Figure 16  | 4: 10x10 fingers stacked RF MOM capacitor                                                                                         | 181 |

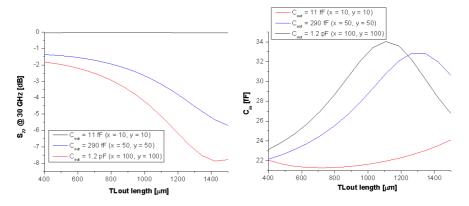

| Figure 16  | 5: 50Ω output matching at 30 GHz (left). Buffer input capacitance at 30 GHz (right)                                               | 181 |

| Figure 160 | 6: Second version of the ILFD buffer                                                                                              | 182 |

| Figure 16  | 7: ILFD output buffer, TL stub, 3D view                                                                                           | 182 |

| Figure 16  | 8: ILFD buffer layout                                                                                                             | 183 |

| -          | 9: 50Ω output matching (left). Buffer input capacitance (right)                                                                   | 183 |

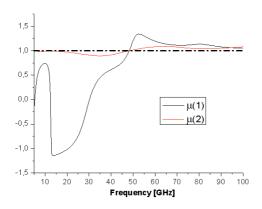

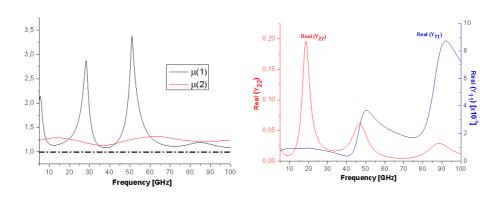

|            | $0$ : $\mu_1$ and $\mu_2$ factors                                                                                                 | 184 |

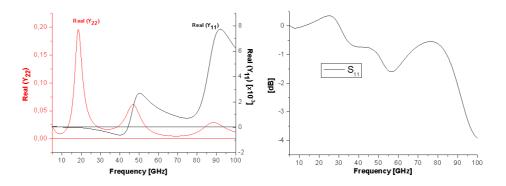

| Figure 17  | 1: $Re(Y_{11})$ and $Re(Y_{22})$ (left). $S_{11}$ parameter (right)                                                               | 184 |

|            | 2: Layout of the ILFD buffer input stage                                                                                          | 185 |

| _          | 3: Results of the solved instability                                                                                              | 185 |

| Figure 17  | 4: Final results. 50Ω output matching (left). Buffer input capacitance (right)                                                    | 186 |

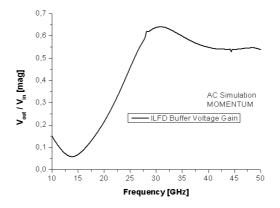

| -          | 5: Buffer voltage gain. AC simulation                                                                                             | 186 |

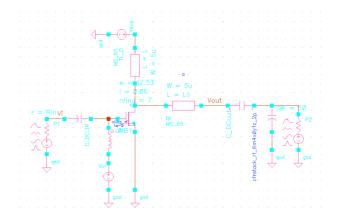

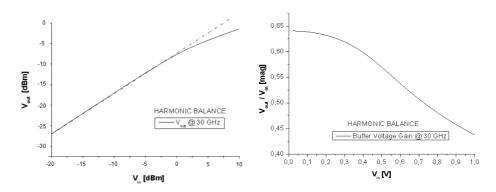

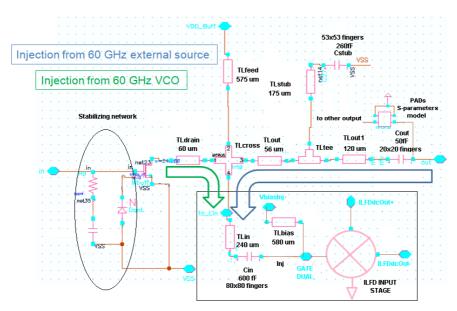

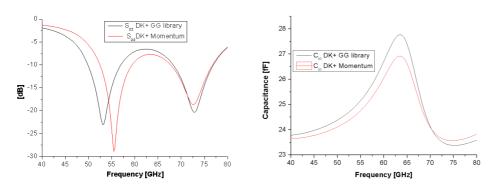

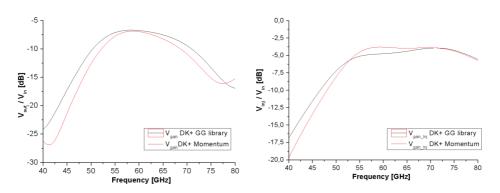

| -          | 6: HB results at 30 GHz. V <sub>out</sub> vs V <sub>in</sub> (left). Voltage gain (right)                                         | 187 |

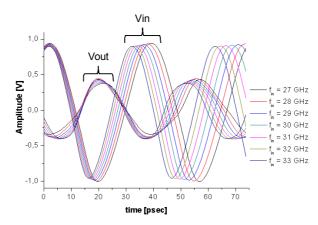

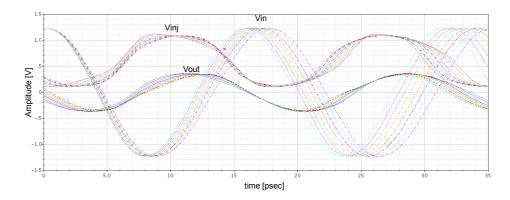

| -          | 7: Input and output Buffer waveforms                                                                                              | 187 |

| Figure 17  | 8: VCO output buffer schematic (ILFD input stage is included)                                                                     | 188 |

| -          | 9: 50Ω output matching (left). Buffer input capacitance (right)                                                                   | 190 |

| -          | 0: Buffer voltage gain V <sub>out</sub> /V <sub>in</sub> (left). Injection voltage gain V <sub>inj</sub> /V <sub>in</sub> (right) | 190 |

|            | 1: 60 GHz buffer waveforms                                                                                                        | 191 |

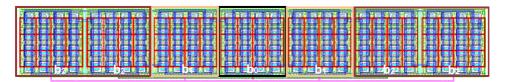

| _          | 2: ILFD-VCO TOP partial layout                                                                                                    | 192 |

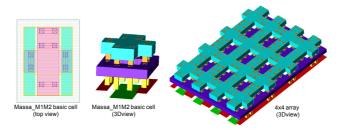

| •          | 3: Mesh Single Decoupling Capacitor Extended cell (total C <sub>dec</sub> =485 fF)                                                | 193 |

|            | 4: Mesh Double Decoupling Capacitor Extended cell (C <sub>dec1</sub> =240 fF (from VP1 to VM),                                    |     |

| -          | C <sub>dec2</sub> =212fF (from VP2 to VM))                                                                                        | 193 |

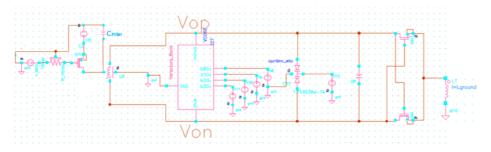

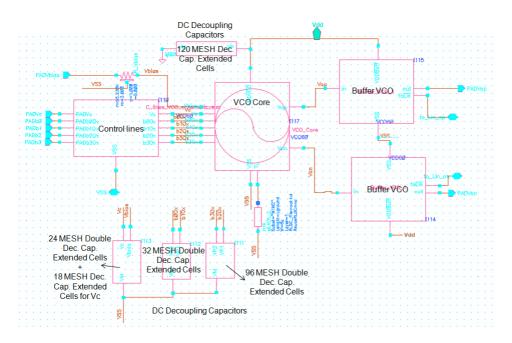

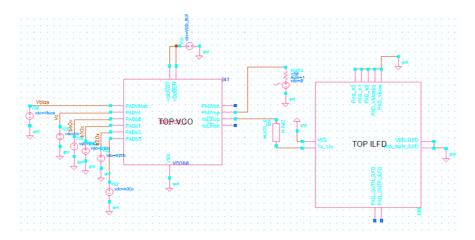

|            | 5: VCO TOP schematic                                                                                                              | 194 |

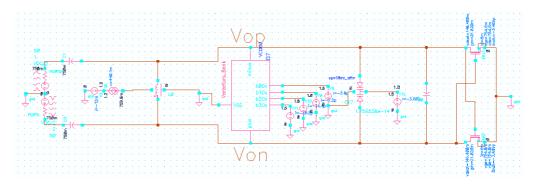

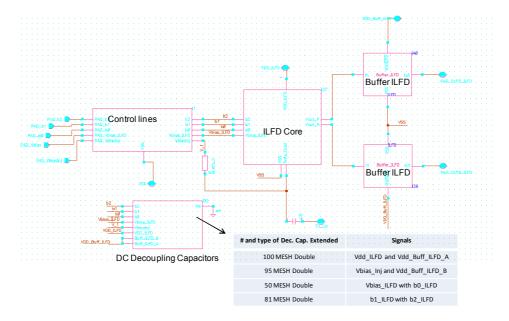

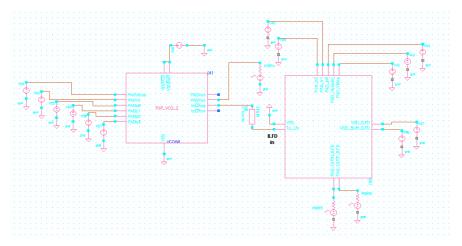

| •          | 6: ILFD TOP schematic                                                                                                             | 194 |

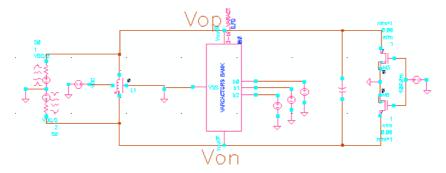

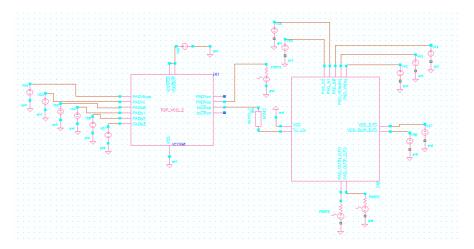

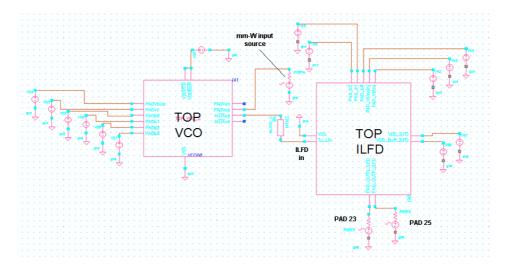

| -          | 7: VCO-ILFD TOP schematic                                                                                                         | 195 |

|            | 8: ILFD - VCO TOP layout                                                                                                          | 195 |

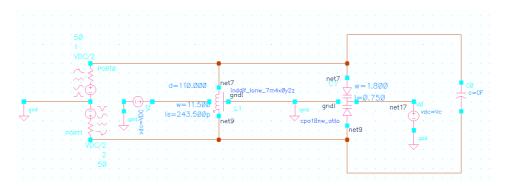

| Figure 189: VCO ON - ILFD OFF. Test bench circuit                                                 | 196        |

|---------------------------------------------------------------------------------------------------|------------|

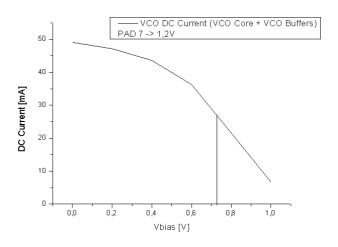

| Figure 190: VCO DC current consumption (RCc extraction of the top layout)                         | 197        |

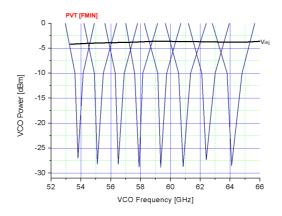

| Figure 191: VCO tuning range (left). VCO Phase-noise at Δf=1 MHz (right)                          | 198        |

| Figure 192: VCO single-ended output waveforms                                                     | 198        |

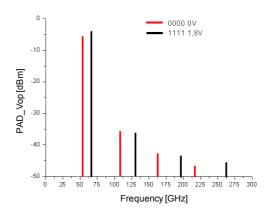

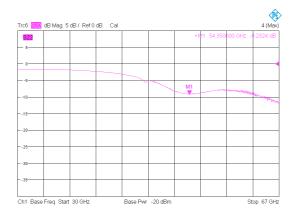

| Figure 193: VCO single-ended output spectrum                                                      | 199        |

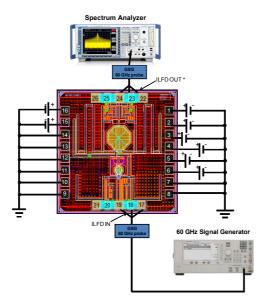

| Figure 194: VCO OFF - ILFD ON. Test bench circuit                                                 | 200        |

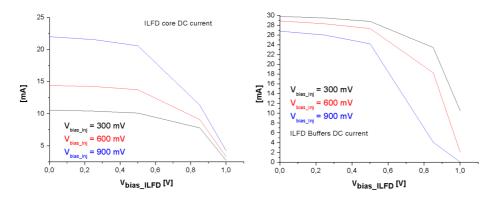

| Figure 195: ILFD DC current consumptions (RCc extraction of the top layout)                       | 200        |

| Figure 196: ILFD free-running state. Self-resonance frequencies (left). Phase Noise (rig          | ght) 201   |

| Figure 197: ILFD waveforms in free running                                                        | 201        |

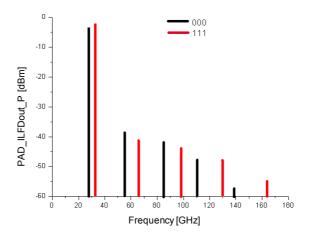

| Figure 198: ILFD output spectrum in free running state                                            | 202        |

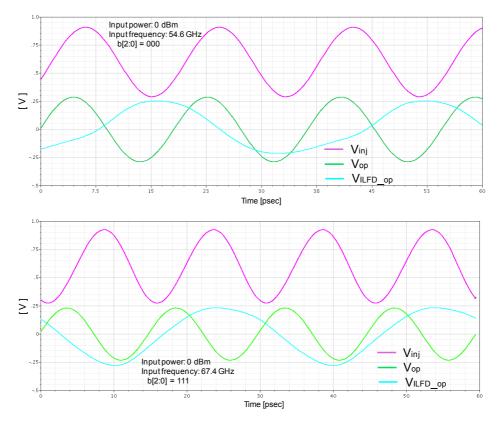

| Figure 199: Divide-by-two ILFD waveforms in locking condition                                     | 203        |

| Figure 200: Divide-by-two ILFD input sensitivity curves                                           | 204        |

| Figure 201: VCO ON - ILFD ON. Test bench circuit                                                  | 205        |

| Figure 202: ILFD - VCO waveforms in locking condition                                             | 206        |

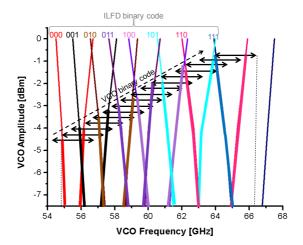

| Figure 203: VCO-ILFD sensitivity                                                                  | 208        |

| Figure 204: VCO phase noise in ILFD locking condition                                             | 208        |

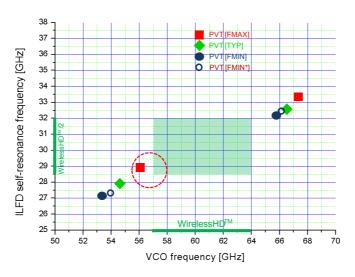

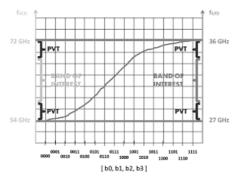

| Figure 205: VCO frequencies vs ILFD self-resonance frequencies                                    | 214        |

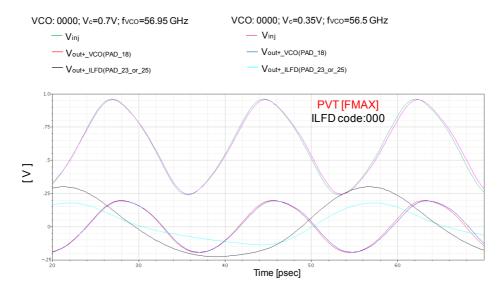

| Figure 206: VCO-ILFD locking around 57 GHz, FMAX corner                                           | 215        |

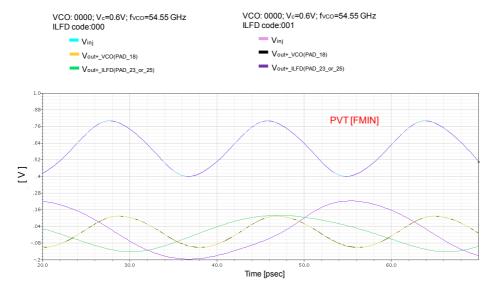

| Figure 207: VCO-ILFD locking. FMIN corner                                                         | 216        |

| Figure 208: ILFD dividing range: FMIN corner                                                      | 217        |

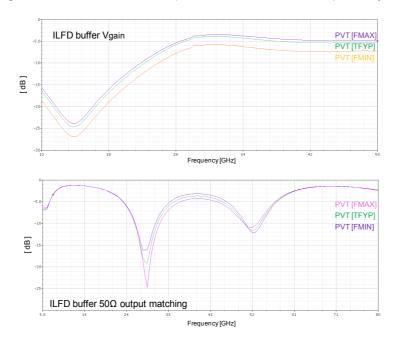

| Figure 209: ILFD output buffer: voltage gain (upper), output matching (lower).                    | 218        |

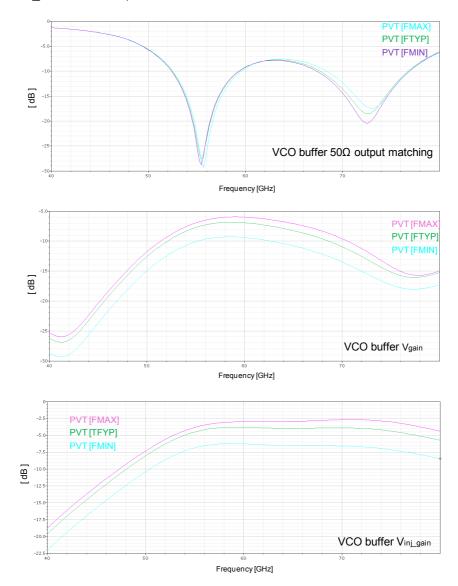

| Figure 210: VCO output buffer: output matching (upper), Vout/Vin (medium), Vini/Vin (lowe         | er). 219   |

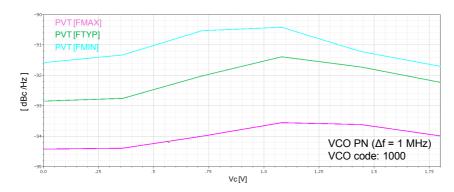

| Figure 211: VCO phase-noise                                                                       | 220        |

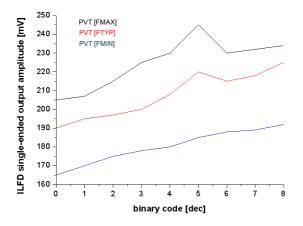

| Figure 212: ILFD output amplitude, single-ended, in free-running state                            | 220        |

| Figure 213: Frequency Synthesizer object of the invention                                         | 221        |

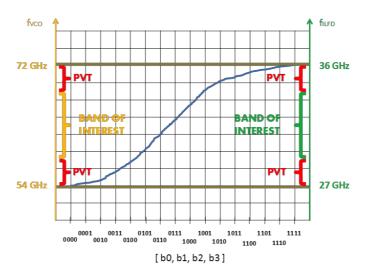

| Figure 214: ILFD Output frequency and VCO frequency in locking condition as a function            | on of the  |

| control bus, for a given VCO control voltage Vc.                                                  | 223        |

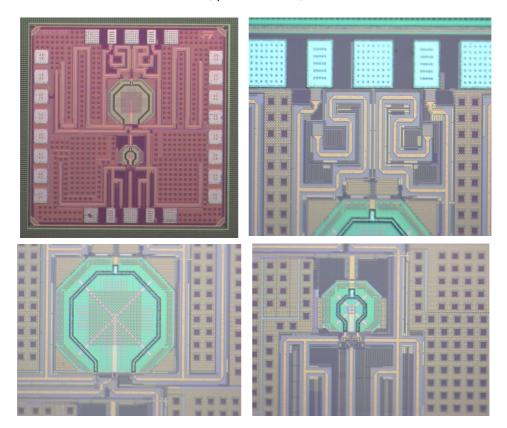

| Figure 215: Die photo (upper-left). ILFD out detail (upper-right). ILFD core (lower-left).        | VCO core   |

| (lower-right)                                                                                     | 226        |

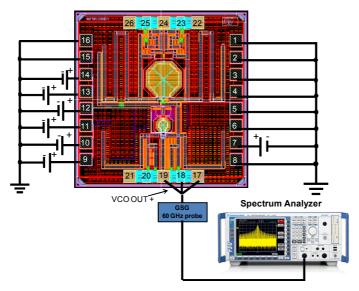

| Figure 216: Measurement layout for VCO characterization                                           | 228        |

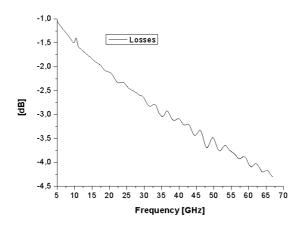

| Figure 217: Losses of the measurement system (GSG probe + transitions + coaxial)                  | 229        |

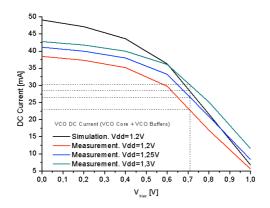

| Figure 218: VCO DC measurements                                                                   | 229        |

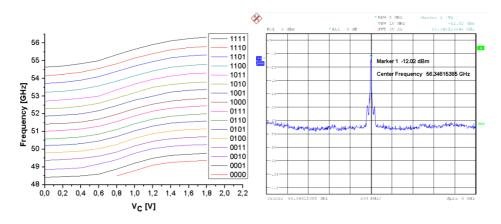

| Figure 219: VCO measured frequency curves (left). VCO highest frequency spectrum (                | right) 230 |

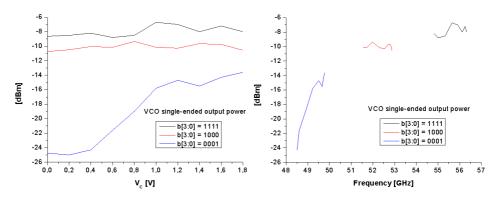

| Figure 220: VCO output power (single-ended)                                                       | 231        |

| Figure 221: VCO 50Ω output matching                                                               | 231        |

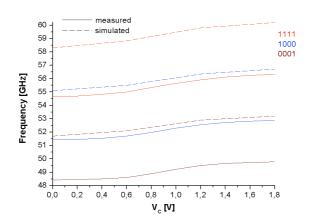

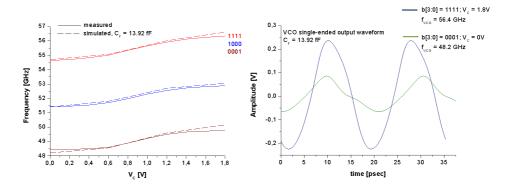

| Figure 222: VCO frequency curves comparison, L DK, C <sub>F</sub> =0                              | 232        |

| Figure 223: VCO with L DK, C <sub>F</sub> =13.92 fF. Frequency curves (left). Single-ended output | waveform   |

| (right)                                                                                           | 233        |

| Figure 224: VCO inductance                                                                        | 235        |

| Figure 225: Quality factor of the VCO inductor                                                    | 235        |

| Figure 226: Measurement layout for VCO characterization                                           | 236        |

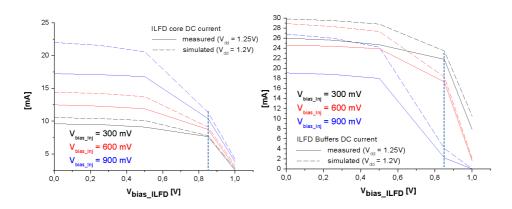

| Figure 227: ILFD DC measurements. ILFD core current (left). ILFD buffers current (righ            | nt) 237    |

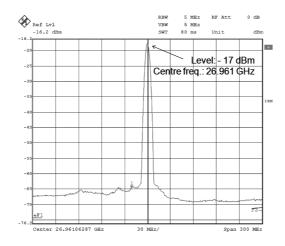

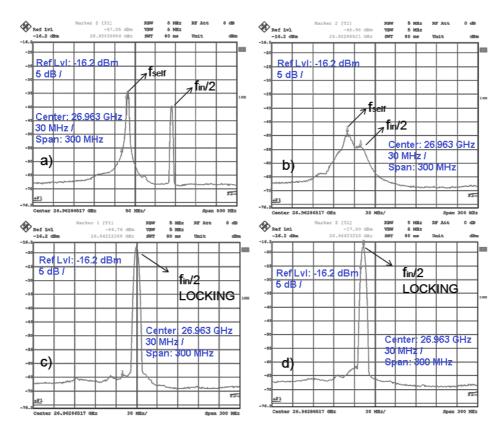

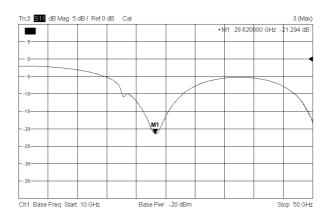

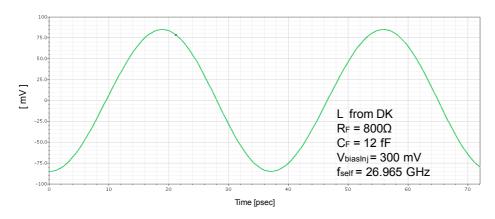

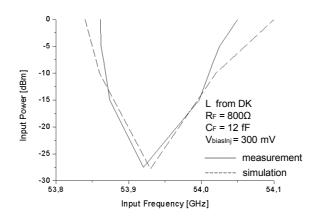

| Figure 228: ILFD self-resonance frequency, b[2:0] = 111, V <sub>bias Inj</sub> = 300mV            | 238        |

| Figure 229: Injection locking mechanism                                                           | 240        |

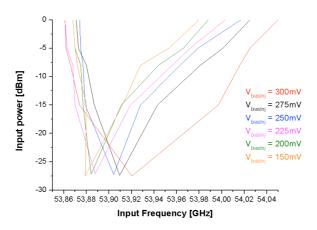

| Figure 230: Divide-by-two ILFD sensitivity curves                                                 | 240        |

| Figure 231: ILFD 50Ω output matching                                                              | 241        |

| Figure 232: Post measurement simulation. ILFD self-resonance frequency                            | 242        |

| Figure 233: Post measurement simulation. ILFD sensitivity curve                                   | 243        |

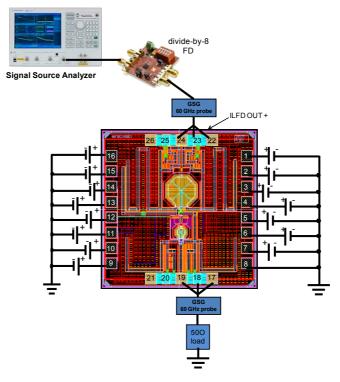

| Figure 234: VCO ON - ILFD ON measurement layout                                                   | 243        |

| Figure 235: Photo of the measurement in CEA-Leti MINATEC Laboratory                               | 244        |

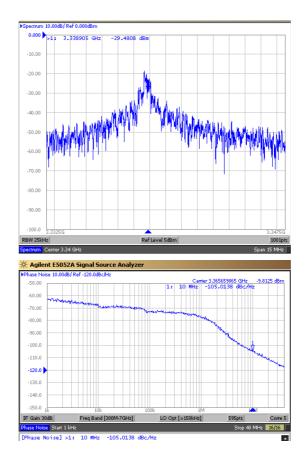

| Figure 236: Divided-by-16 VCO frequency spectrum (upper). VCO phase noise (lower)                 | 245        |

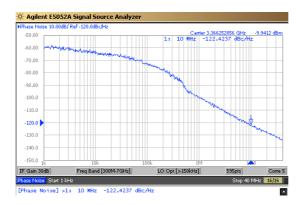

| Figure 237: ILFD phase noise (free-running)                                                       | 246        |

#### **ACKNOWLEDGMENTS**

I am grateful to several persons and institutions which have supported me in the course of the development of this Thesis.

A special thanks to my Thesis Advisor, for the constant support, suggestions, recommendations and, mostly, for the several and helpful reviews provided during the Research Period of the Ph. D.

I do not forget the first years of my Ph.D. in Seville, during the development of the Academic Period, at the Centro Nacional de Microelectrónica (CNM). Thanks to my first Advisor, Dr. Manuel Delgado Restituto, for introducing me in the world of the RF ICs design. Special thanks also to Dr. Jesus Ruiz Amaya, for the constant training provided.

I would like to express thanks to all the staff of the CEA-Leti Laboratory at MINATEC in Grenoble, for the support and helpfulness provided during the measurements.

A special thanks to the Company in which I work, that is FICOSA International, especially to the Advanced Communications Division, for the willingness and flexibility. Thanks to all my colleagues of the Advanced Automotive Antennas BU.

Thanks to my mother and father, to give me, with the education afforded, the passion for knowledge and the culture of abnegation.

Finally, thanks to my best friend, my love Carmen. It would never been possible without your support, suggestions and, mostly, patience. Actually, I am a co-author of this Thesis, with you. Thank you very much.

#### **SUMMARY**

Increasing memory capacity in mobile devices, together with the transition to wireless connections for consumer electronics and PC products, is driving the need for wireless equipment with data rates of up to 10 Gbits/sec.

The worldwide 7 GHz unlicensed band around 60GHz provides the opportunity for multi-gigabit persecond wireless communication and it is a real opportunity for developing next generation of Wireless High-Definition (WirelessHD<sup>TM1</sup>) devices. The notation WirelessHD<sup>TM</sup> has recently replaced the first definition of Wireless High-Definition Multimedia Interfaces (WHDMIs) for the frequency range around 60 GHz, as shown in Figure 1. The HDMI by wire, where it already exists, can be replaced by wireless systems transmitting uncompressed video streaming from DVD players, or from PCs to TV or monitor. Other applications are regarding cellular phone, or *smart* phones: considering an hypothetical 60 GHz enabled smart phone (i. e. Android, Iphone, etc.), which uses the 60 GHz connection to download movies from a stand (i.e. airport, train station, etc.), transmits audio/video to a larger screen for better viewing, and connects to several external and wireless peripherals (i.e. hard disk, optical networks, etc.). In this scenario, with reasonable low power consumption using inexpensive silicon technology like CMOS, it is possible to say that such phone with that capability can truly replace the laptop computer.

On one hand, addressing 10 Gbits/sec data speed with current standard Wi-Fi at 5 GHz will require extremely complex base-band modulation systems. Moreover, tight regulation specifications exist for this band, making it unlikely to be able to operate with 10 Gbits/sec at 5 GHz: current WirelessHD<sup>TM</sup> products that utilize the 5 GHz unlicensed spectrum have the critical drawback of the limited bandwidth. As a consequence, these systems implement lossy or lossless compression, dramatically adding components, design cost and product size. On the other hand, the nascent UWB technology could be a better

The frequency band requirement for the WirelessHD<sup>TM</sup> has been obtained from public documents available in Internet (e.g. <a href="http://www.ieee802.org/15/pub/TG3c.html">http://www.ieee802.org/15/pub/TG3c.html</a>), since neither UPC nor CEA-Leti are members of the WirelessHD<sup>TM</sup> Consortium.

solution, but it has some drawbacks including interference problems, limited data rates and limited SNR due to limited transmit power.

From Shannon theory, it is know that a way to increase communication data rate is to utilize more bandwidth. Since the information signal is usually modulated around a carrier frequency for proper propagation, the higher the carrier is, the more bandwidth is available for propagation: selecting the 60 GHz band will offer the benefits of 7 GHz unlicensed bandwidth with few regulatory specifications.

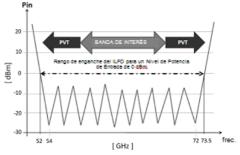

The actual allocated bandwidth at 60 GHz varies from country to country as shown in Figure 1. However, there is an overlap bandwidth of 3 GHz within the 60 GHz band which is available worldwide. The 60 GHz frequency also allows for small form factor antennas (easy antenna integration in the transceiver) and it is well suited for short range communication, as at 60 GHz 98% of energy is absorbed by  $O_2$  above 1km.

Figure 1: Spectrum Available around 60 GHz

Mass production requirements coupled with the cost constraints of mobile devices result in a need to identify an alternative to existing, expensive Gallium Arsenide (GaAs) and Indium Phosphide (InP) technologies, currently used widely in millimeter-Wave (mm-W) Microwave Monolithic Integrated Circuit (MMIC) fabrication. Radio Frequency (RF) Complementary Metal Oxide Semiconductor (CMOS) 65 nm and 45 nm technologies currently show very attractive performance for mm-W MMIC design, even if the technology environment is a critical issue in the design of frequency synthesizers operating at mm-W frequencies.

Recent developments in mm-W CMOS systems have begun to address the integration of building blocks to form transceivers. In addition to generic challenges such as high-frequency operation and low-noise design, the implementation of transceivers at these frequencies must deal with three critical issues related to the frequency synthesis:

- 1) generation of the Local Oscillator (LO) signal

- 2) division of the LO signal for the Phase-Locked Loop (PLL) closed loop

- 3) distribution of the LO signal

It is therefore important to develop "synthesizer-friendly" transceivers in order to alleviate these issues.

Therefore, transmitting and receiving using 60 GHz in CMOS remains an attractive and unsolved topic in the RF ICs design research field.

The aim of this thesis is to design a frequency divider for a PLL of a direct-conversion transceiver operating at mm-W frequencies in 65 nm RF CMOS technology; in order to achieve this goal, frequency synthesizers architectures and frequency divider topologies will be explored; several previous works in CMOS technologies operating at mm-W frequencies will be visited and analysed. Important issues such as Process, Voltage and Temperature (PVT) variations, Electro-Magnetic (EM) simulations and power consumption will be addressed in this context in order to select and design a frequency divider with high frequency dividing range.

Furthermore, the frequency generation issue will be experimentally faced up, since a wide tuning range, low phase noise 60 GHz Voltage Controlled Oscillator (VCO) will be also designed and integrated in the same die, in order to provide the frequency divider with mm-W input signal without using external RF source.

The implementation of calibration techniques will be also taken into account in the VCO and frequency divider co-design. In fact, in order to address the hard constraint of covering the required bandwidth, not still properly attained at the state-of-art due to the technology impairments at mm-W frequencies (PVT variations), the PLL wherein the two RF blocks will be embedded can implement self-compensation thanks to calibration mechanisms that will be exposed and which is the subject of a registered patent of the author.

# 1 INTRODUCTION

#### 1.1 Why 60 GHz?

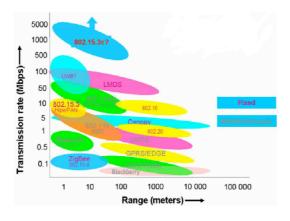

Wireless connectivity trends have tended to track but lag wired solutions in terms of data-rate. Current wireless standards address data rates on the order of tens of megabits per second, with 802.11b at up to 11 Mbps and 802.11a at up to 54 Mbps.

Standards that address mobile users at longer ranges provide much lower data rates as shown in Figure 2. Network interface cards operating at 1Gbps are now standard or available as an option in many new PC's and laptops. It is believed that as consumers grow accustomed to transferring files and other data at 1Gbps, they will also demand the option of doing it wirelessly. Other wired standards, such as Firewire/IEEE\_1394 are also following this trend upward in data rates. IEEE\_1394 has been deployed for some time at 400Mbps with the next generation in early deployment at 800Mbps, and there exist standards defined for the future at rates of up to 3.2Gbps. What is still missing is a wireless connection with USB transfer capability that can support high data rates, accorded to the demand of consumer electronics, like large data rate multimedia applications.

Figure 2: Mobile users Standards

The spectrum between 30 GHz and 300 GHz is referred to as the mm-W band because the wavelengths for these frequencies are about one to ten millimetres. The *Federal Communications Commission* (FCC) has allocated the 57-64 GHz mm-W band for general unlicensed use, which opens a door for very high data rate wireless applications over the 7 GHz unlicensed band. Since oxygen absorption peaks at 60 GHz, this frequency band is particularly interesting for high-dense, high-rate applications in Wireless Personal Area Networks (WPANs).

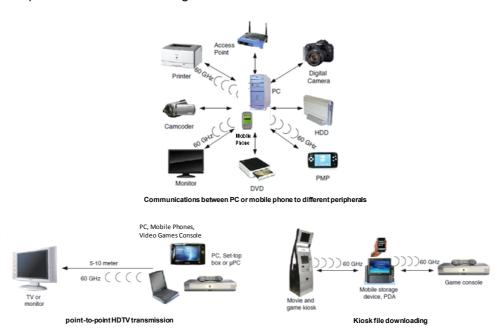

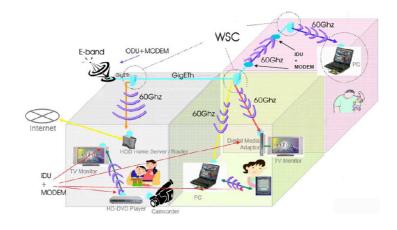

In an office but also in home environment, the 60 GHz connections can basically replace the wires bundle (USB, IEEE 1394), providing multi-gigabit wireless Ethernet and multimedia delivery. In such scenario, a PC can communicate to all external peripherals (i. e. DVD, printers, digital cameras, external hard disks, etc.). Both Wireless Gigabit Ethernet and Wireless ad-hoc networks using 60 GHz are attractive applications for conference room or library management. as well. Furthermore, commercial applications like that so called "Kiosk File Downloading", in which users can download movies, games, etc. from a stand placed at public locations such airport, train stations, markets, etc., could get a tremendous push to their diffusion in utilization. These applications examples are summarized in Figure 3.

Figure 3: Potential 60 GHz applications

IEEE 802.15.3c has been recently formed to develop a mm-W based alternative physical layer (PHY) for the existing 802.15.3 WPAN standard. The

mm-W based WPANs have many salient features. First, the mm-W communication is anticipated to achieve very high data rate (over 1 Gbits/sec), so it will enable many killer applications such as high speed Internet access, video on demand, HDTV, home theatre, etc. According to the standard, optional data rates in excess of 3 Gbps is anticipated. Second, mm-W systems can coexist with existing wireless communication systems, such as Wi-Fi (IEEE 802.11), Bluetooth, 2G/3G/4G cellular systems, and Ultra Wide Band (UWB) systems, because of the large frequency difference. Third, because of the larger path-loss, the interference among different mm-W WPANs is very limited, which allows mm-W WPANs to be widely and highly densely deployed. In addition, since the mm-W signal degrades significantly when passing through walls and over the distance, this will help ensure the security of the content. Although mm-W prototype chipsets according to IEEE 802.15.3c specification have been emerging, their performance in a networked environment is an open area beckoning for further investigation. To ensure the success of mm-W based WPANs, how to efficiently and effectively allocate resource for co-existing mm-W devices is a very critical issue.

#### 1.1.1 List of Applications

The data rate in the unlicensed 7 GHz band around 60 GHz should be between 50 Mbits/sec and 60 Gbits/sec, in order to satisfy consumer's requirement and market applications that are going to be detailed.

Briefly, a list of opportunities that this new-service can provide is shown, from the point of view of the consumers:

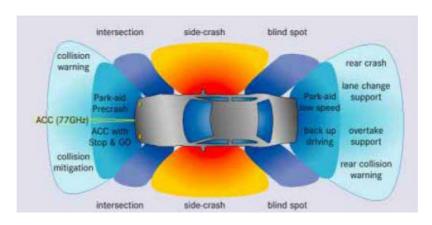

- Automotive applications

- Radar items

- Long Range Radar (ACC) (76-77GHz bands)

- Short Range Radar (Stop & Go) (77-81GHz bands)

- Ground to vehicle and vehicle to vehicle links (HDR Communications)

- High data-rate communications

- > Last Inch applications (57 to 66GHz bands)

- Wireless HDMI video streaming

- Communications between nomadic devices (such as pocket HD, ...)

- Communications between/with mobile devices such as: digital (still) cameras, mobile phones, PDAs)

- HD video transmission on home TV's

- Short Range Ultra fast file transfer

- ➤ Last Mile applications (71-76GHz, 81-86GHz licensed E-bands)

- Telecom backhauls

Figure 4: Long and Short Range Radar Applications

Figure 5: Indoor network scenario and interfacing to the outdoor network

- ❖ Low data-rate communications (94GHz, >100GHz bands)

- > Sensor network applications

- Optical communications

- Chip to chip wireless communications

- Imaging

- > Security non-intrusive investigations

- Medical/biological imaging

Figure 6: emerging mm-W imaging

#### 1.2 60 GHz RF Front-End: a cost issue

As it is possible to see in Figure 1, there is a more than 3 GHz overlap of unlicensed band around 60 GHz that is worldwide available; the IEEE standard 802.15.3c, alternate PHY for 802.15.3, specifically targets this application space. One of the most significant challenges in utilizing the potential of this frequency band is the cost of the RF front end.

Millimeter wave (mm-W) frequencies have historically been costly to utilize, and have been traditionally used almost exclusively for government, military and non-consumer products [1]. Recent advances in semiconductor technology and low cost high frequency packaging provide an opportunity for this spectrum to become useable for broadband consumer applications within the next 2-3 years [2].

Hardware operating at mm-W frequencies has been expensive to implement. The RF front end of these systems is considered by many to be a significant area of risk because of the high cost of implementation [3]. The RF front end is made up of three key components that drive its implementation which include the semiconductor technology/chipset, packaging along with manufacturing tolerances and yields.

Historically, monolithic microwave integrated circuits (MMICs) have been built using III-V semiconductor technologies, such as GaAs and InP, which

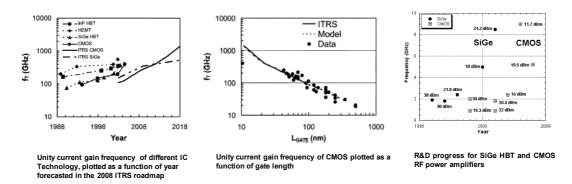

have superior performance compared to CMOS due to their higher electron mobility, higher breakdown voltage, and the availability of passives with high Q. But CMOS implementation ensures higher levels of integration and reduced cost. Several recent developments have combined to enable CMOS circuit blocks to operate at "ever"-increasing frequencies. Millimeter-Wave CMOS circuits directly benefit from the higher speed of the scaled technology. Up to 2009/2010, only CMOS oscillators have been demonstrated beyond 30/40 GHz, while CMOS amplifiers, mixers and frequency dividers are quite lagged regarding frequency operation. A key reason for this large discrepancy is the lack of accurate CMOS active and passive device models at mm-wave frequencies.

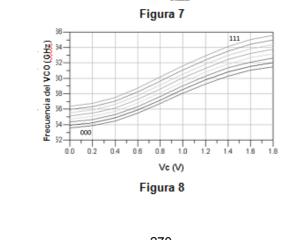

Technology advances and trends can be leveraged to cost reductions in these areas. Recent and ongoing advances in packaging and semiconductor technology continue to trend towards higher frequencies, as it is possible to see in the following figures. In addition to allowing for a lower "bill of materials" cost, these advances can also be leveraged to improve final assembly and yield; mm-W CMOS radios present formidable challenges at all levels of abstraction, demanding that designers ascend and descend the device-circuit-architecture-system ladder with ease and confidence; last advances of RF CMOS technology show that there is an alternative to existing, expensive GaAs and InP technologies, currently used widely in mm-W MMIC fabrication; furthermore, the technology scaling for CMOS allows to work in mm-W region, as shown in Figure 7 [4], where it is possible to note the attractive CMOS opportunities versus other technologies:

Figure 7: CMOS device and technology evolution for Si-based RF Integrated Circuits according to ITRS forecast

#### 1.2.1 mm-W on CMOS Technology

Currently, it is possible to say that devices and integrated circuits are manufactured on four substrate materials: GaAs, InP, SiC, and Si. While the ,

III-V compounds dominated the millimetre wave spectrum a decade ago, Sibased device technologies have crept into this applications arena, driven primarily by advantages in cost and integration level. In the future, we may see other III-V compound semiconductors, and even C-based semiconductors, including diamond, being developed for this spectrum. RF and Analog Mixed-Signal (AMS) technologies serve the rapidly growing wireless communications market and represent essential and critical technologies for the success of many semiconductor manufacturers. Communications products are becoming key drivers of volume manufacturing; the consumer products demand for mm-W applications is estimated in millions of 60 GHz transceivers that will be produced and sold by 2015 [5]. The consumer portions of wireless communications markets are very sensitive to cost. With different technologies capable of meeting technical requirements, time to market and overall system cost will govern technology selection.

Together with the recently reported 60GHz receiver in 90nm CMOS [6], other receivers in 65nm CMOS demonstrates [7] that scaling of entire mm-wave receivers is possible in both frequency coverage and across technology nodes, as predicted by Gordon Moore in the last paragraph of [8]. Furthermore, with the reduction of the die area occupied by lumped passives at higher frequencies, and with the intrinsic speed improvement anticipated in future CMOS technology nodes, one can expect that entire CMOS transceivers can be scaled to 120 GHz in 45nm, and to 160 GHz in 32nm technologies, as it is possible to note by observing the technology requirements in the 2010 (updated at 2011) International Technology Roadmap for Semiconductors (ITRS) [9] for Analog Mixed-Signal, RF CMOS Technology, as reported in Table 1. Also, mm-W transceivers can be integrated with antennas and other systems to implement wireless I/Os for chip-to-chip communication at 40Gb/s.

| Year of Production                                        | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 |

|-----------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|

| Device Technology—RF CMOS [common to High Performance     |      |      |      |      |      |      |      |      |      |      |      |

| CMOS with 2-year delay]                                   |      |      |      |      |      |      |      |      |      |      |      |

| V dd: Power Supply Voltage (V)                            | 1,1  | 1,1  | 1,1  | 1,1  | 1,0  | 1,0  | 1,0  | 1,0  | 1,0  | 0,9  | 0,9  |

| EOT: Equivalent Oxide Thickness (A)                       | 12   | 12   | 10   | 9,5  | 8,8  | 7,5  | 7,5  | 7,5  | 7    |      |      |

| Lg: Physical Lgate for High Performance logic (nm)        | 37   | 29   | 27   | 24   | 22   | 20   | 18   | 17   | 15   | 14   | 12,8 |

| Peak F <sub>t</sub> (GHz)                                 | 240  | 310  | 330  | 370  | 400  | 440  | 490  | 520  | 590  | 630  | 680  |

| Peak F <sub>max</sub> (GHz)                               | 300  | 330  | 360  | 410  | 450  | 500  | 560  | 590  | 680  | 730  | 810  |

| NF <sub>min</sub> (dB) at 24GHz                           | 1,8  | 1,6  | 1,6  | 1,5  | 1,4  | 1,4  | 1,3  | 1,3  | 1,2  | 1,2  | 1,1  |

| NF <sub>min</sub> (dB) at 60GHz                           | 3,5  | 3,3  | 3,2  | 3,0  | 3,0  | 2,9  | 2,7  | 2,7  | 2,6  | 2,5  | 2,4  |

| NF <sub>min</sub> (dB) at 94GHz                           | 4,7  | 4,4  | 4,3  | 4,1  | 4,0  | 3,9  | 3,8  | 3,7  | 3,5  | 3,5  | 3,4  |

| peak DC g <sub>m</sub> at V <sub>D</sub> =V <sub>DD</sub> | 1,46 | 1,75 | 1,84 | 2,00 | 2,12 | 2,25 | 2,41 | 2,49 | 2,68 | 2,79 | 2,93 |

| MSG/MAG (dB) at 24 GHz                                    | 14,8 | 15,9 | 16,2 | 16,7 | 17,0 | 17,4 | 17,9 | 18,1 | 18,7 | 19,0 | 19,3 |

| MSG/MAG (dB) at 60 GHz                                    | 10,8 | 11,9 | 12,2 | 12,7 | 13,0 | 13,4 | 13,9 | 14,1 | 14,7 | 15,0 | 15,3 |

| MSG/MAG (dB) at 94 GHz                                    | 8,8  | 10,0 | 10,2 | 10,7 | 11,1 | 11,5 | 11,9 | 12,2 | 12,7 | 13,0 | 13,4 |

Table 1: 2010 (updated 2011) ITRS Roadmap for RF CMOS. Near terms requirements

Nevertheless, there are two years lag in meeting the requirements for mm-W applications; one has to note that the yellow squared means that

manufacturable solutions are known, even if their process is still under optimization. In addition and more critical, red squared means that the manufacturable solutions are NOT known. If  $f_t$  is the transistor cut-off frequency and  $f_0$  is the operating frequency, usually the latter can be estimated as  $f_t/2\sqrt{3}$  and so the WirelessHD<sup>TM</sup> band is closed to the theoretical maximum operating frequency. Other technological critical points for CMOS technology are the performance degradation due to low gain, linearity constraints and poor noise.

#### 1.3 Critical Issues in CMOS Frequency Synthesizers Design

VCOs and Frequency Dividers (FDs) play critical roles in every synchronous circuit, such as the PLL. Both of them constitute the frequency synthesizer core components and they would need co-design, having a big impact in the overall performance especially because they are the blocks in the PLL that work at the highest frequency. We have seen in the last two decades a great proliferation of VCO and FD topologies in RF ICs on silicon, but reaching high performance VCOs and FDs operating at mm-W is in today's technology a enormous challenge.

When addressing the PLL design at circuit level, the challenges are several: low frequency blocks are not easily scalable to 60 GHz, due to foundry models not well characterized at this frequency; the parasitic elements of active devices also contribute to reduce high frequency operation; the devices are very sensitive to PVT variations at these frequencies. As a consequence, several margins have to be taken into account in the design resulting in high power consumption and big chip area. On the other hand, the fact that the components became affordable in terms of silicon footprint leads to the availability of poor models, in terms of uncertainty, for passive devices like inductors and to the need of EM simulations as well as dummy designs for initial dry-runs to characterize the components, resulting in highest design time. The quality factor (Q) of the varactors, widely used to give tuning capability to VCO and FD, decreases critically at mm-W frequencies, if compared to lower operation frequencies [10], resulting in a Q of the LC tanks that is very dependent on the varactors, while at lower frequencies the Q of the tank is completely dominated by the inductor. Moreover, low-ohmic substrate and low metals conductivity at 60 GHz are an effective further drag in order to approach a reasonably low lossy design.

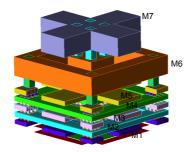

At layout level, as the 60 GHz wavelength is comparable to circuit dimension, the interconnections between components and blocks inside the chip, as well as supply voltages distribution, are a crucial part in the design. They must be EM simulated in order to take into account layout parasitic and, if it is the case, re-design the circuit in order to compensate or eliminate their

unwanted effects. As the number of metal layers in the selected 65nm RF CMOS design kit is seven (from M1 to M7), it is easy to understand that modelling and simulation steps are time consuming if all the metal layers and vias are included in the simulations. Also, due to the proximity of devices in the chip, EM simulations are needed also to evaluate unwanted coupling effects and losses: this issue must be taken into account in the layout design, with apposite strategies. Just for instance, a capacitance underestimation of 10 fF in a 60 GHz layout interconnections, i. e. with all metal layers and vias employed, can lead to a frequency shift of around 2 GHz!

Regarding measurements at 60 GHz, the critical points are related to the need of accurate calibrations, de-embedding techniques and, in some case, indirect measurements. Losses and mismatch of cables, connectors, adapters, etc., must be taken accurately into account. Additionally, stability and repeatability of the accurate measurements is a further critical points at this frequency.

So it is enough clear that there are several challenges in reaching the transceivers scaling previously mentioned, in terms of operating frequency and technological node, while the market opportunities are very attractive, taking into account consumers demands and trends, as well as CMOS costs.

In this work, all the challenges related to the previously mentioned issues (technological environment, circuits design and simulations, layout with EM simulations and measurements) for a 60 GHz FD and VCO co-design in 65 nm CMOS will be practically faced up and discussed.

### 1.4 Objectives and Methodology

The first main objective of this Thesis is to design a divide-by-two FD working in the 60 GHz band and showing a frequency dividing range of at least 7 GHz in order to cover the WirelessHD<sup>TM</sup> band. Indeed, this dividing range should be higher than 7 GHz, to take into account the frequency shifts and offsets due to PVT variations, which constitutes the second main objective of the Thesis.

Furthermore, a low phase-noise, wide tuning range VCO for the WirelessHD<sup>™</sup> band is also co-designed and implemented in the same die with the FD, in order to provide it with input frequency. The critical challenges related to PVT variations at 60 GHz and frequency distribution of the LO signal are faced up in the VCO-FD co design, being the third objective of this Thesis, to demonstrate that the FD is able to work along with the integrated VCO. The VCO and the FD are designed in order that each one can be measured separately, in "stand alone" (VCO ON - FD OFF or VCO OFF - FD ON) or both

operating simultaneously (VCO ON - FD ON) as would be the case in a 60 GHz PLL for direct-conversion transceivers operating in such band.

It has been already observed how the implementation of communication applications in the 60 GHz band for large market and hand-held devices require the utilization of low-cost state-of-the art CMOS technologies. Some transceivers built using such process (CMOS 90nm, 65nm) have been already demonstrated, as in [11] and [12]. There exist, however, some important issues to be solved. Most of the them use heterodyne principle with double conversion stages or sliding-IF architecture since the realization of a frequency synthesizer block covering the whole band (7 GHz) plus additional margin for PVT compensation has not been completely solved. Another reason to operate at lower frequency is due to the need of very low phase noise, and it is another still open research issue for 60 GHz CMOS direct-conversion transceiver design, not considered as objective of this thesis. This topic could be considered as future work when the first problem is solved, i. e. the operation frequency issue at 60 GHz.

Some oscillators have been proposed, like [13], that could be used to fulfil those requirements, but the implementation of the FD block that necessarily follows in the PLL of the frequency synthesizer was still an open research topic at the beginning of this Thesis.

The work reported in this Thesis describes the study, analysis and implementation of a 60 GHz FD and VCO co-design in 65 nm CMOS technology, to push on the research in 60 GHz PLLs for direct conversion transceivers for mm-W application. This has been the main motivation of this Thesis work.

As a summary of the aforementioned situation, the main challenge boarded in this Thesis is that the FD must work at 60 GHz and it has to cover the overall VCO tuning range, that is 7 GHz plus an additional margin for taking into account the effects of PVT variations and devices models. The goal is to maximize the tuning range of the ensemble VCO + FD with the minimum power consumption. The centre frequency of the tuning curves should be that required for a direct-conversion or very low-IF transceiver architecture.

These main objectives have been divided into the following subobjectives, that can be mapped to specific tasks: