### Pyramic array

An FPGA based platform for many-channel audio acquisition

Juan Azcarreta Ortiz

Presented the 24 August 2016 at Laboratory of Processors Architecture (LAP) and Laboratory of Audiovisual Communications (LCAV) École Polytechnique Fédérale de Lausanne

to obtain the Master's degree in Electronics Engineering by

Juan Azcarreta Ortiz

suppervised by:

Prof René Beuchat, supervisor LAP Robin Scheibler, supervisor LCAV Prof Ramon Bragos, supervisor UPC Lausanne, EPFL, 2016

"Microphones are to audio, what colors are to painting."

— Stanley R. Alten

To my family...

## Acknowledgements

First of all, I want to thank my supervisors, René Beuchat, expert professor at LAP and Robin Scheibler, PHD student at LCAV. Thanks for all your patiente and support, merci René for all the patiente and your help during the design, testing and building of the project. Thanks Robin for your great support and availability. I appreciate the interesting conversations sharing ideas we had during the project, arigatou. Special mention to my college, Sahand, who reviewed my project and helped a lot during design considerations. Without you this project would have not been the same, I am sure you will have a great success developing embeddeded systems. Thanks to Eric Bezzam and Balási Szabolcs, which collaborated in the project adding advanced knowledge and great times to it. Thanks to all of you.

I would like to thank UPC for giving me the chance to spend one year abroad at EPFL. Specially thanks to my supervisor, Ramón Bragos. Thanks to them, I was able to achieve my goal of performing my Master Thesis at EPFL.

I am greateful to my friends and colleagues I met during my Master and Bachelors at EPFL, UPC, University of Navarra and Cal Poly. Thanks to all the international friends I made during this period. I hope to see you again soon.

Last but not least, I want to thank my family, specially to my parents. They have always supported me, especially in the difficult times, thanks for your unconditional love and support.

### **Abstract**

Microphone arrays techniques present compelling applications for robotic applications. Those techniques can allow robots to listen to their environment and infer clues from it. Such features might enable capabilities such as natural interaction with humans, interpreting spoken commands or the localization of victims during search and rescue tasks.

However, under noisy conditions robotic implementations of microphone arrays might degrade their precision when localizing sound sources. For practical applications, human hearing still leaves behind microphone arrays. Daniel Kisch is an example of how humans are able to efficiently perform echo-localization to recognize their environment, even in noisy and reverberant environments. For ubiquitous computing, another limitation of acoustic localization algorithms is within their capabilities of performing real-time Digital Signal Processing (DSP) operations. To tackle those problems, tradeoffs between size, weight, cost and power consumption compromise the design of acoustic sensors for practical applications. This works presents the design and operation of a large microphone array for DSP applications in realistic environments.

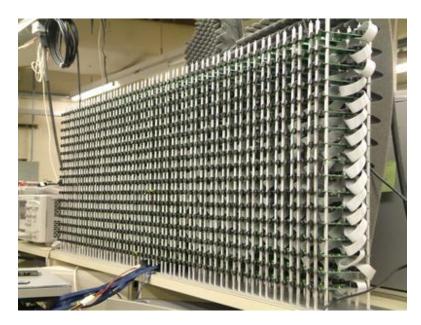

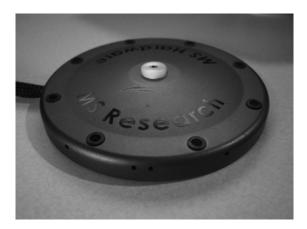

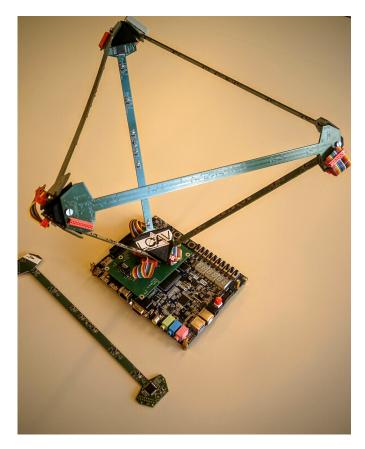

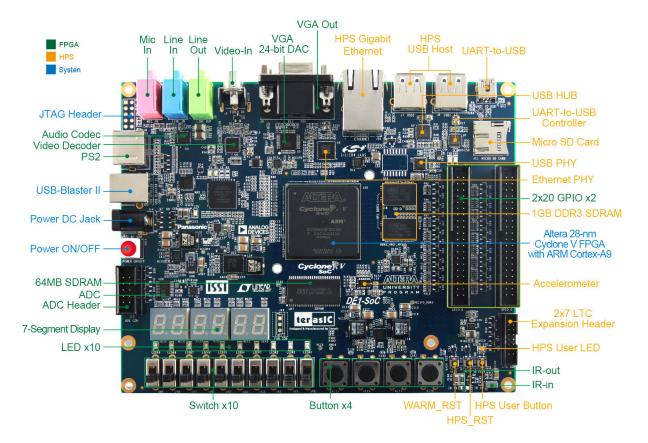

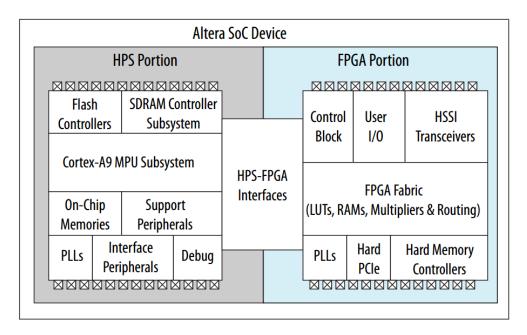

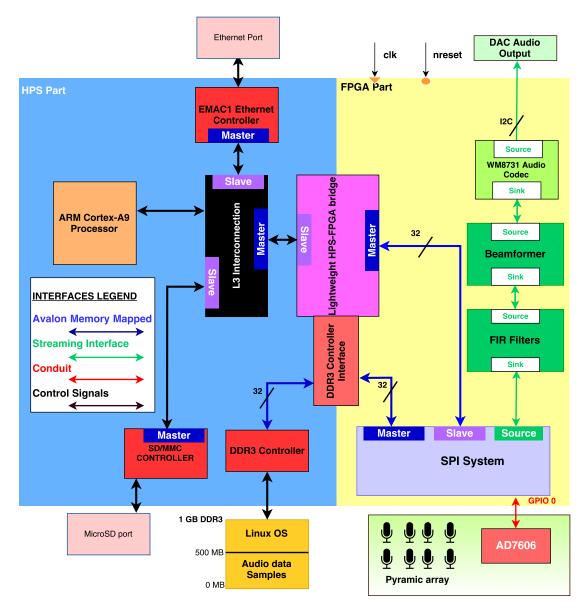

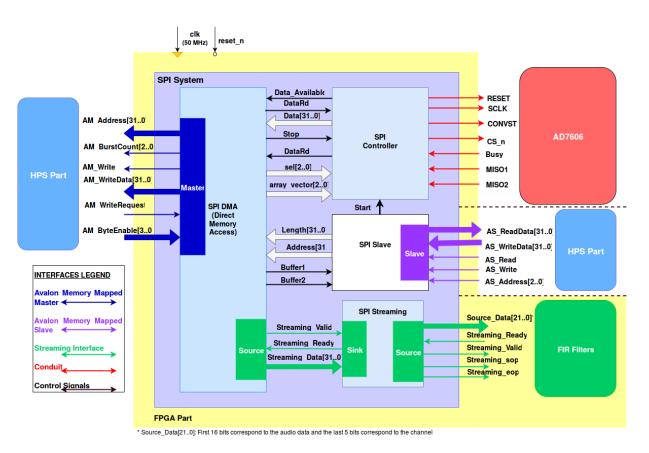

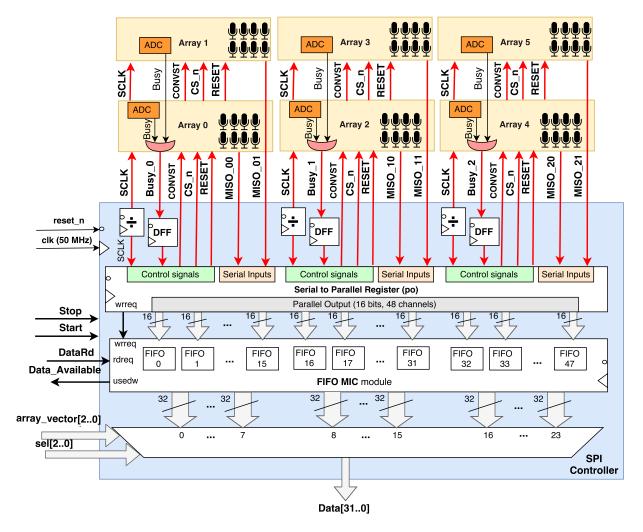

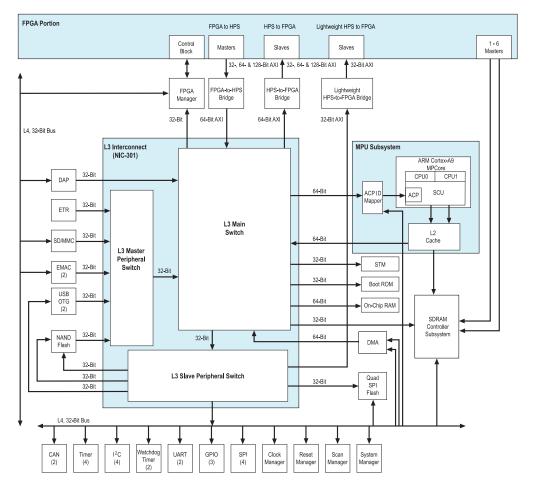

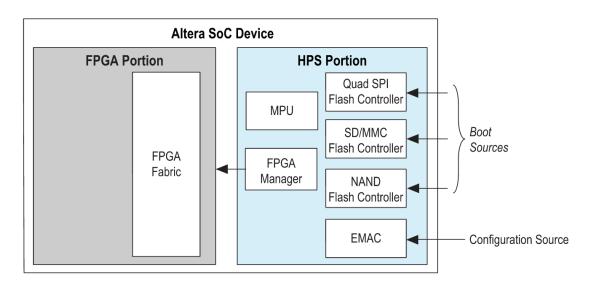

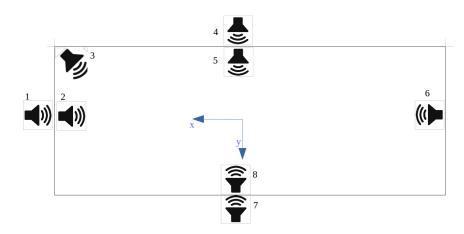

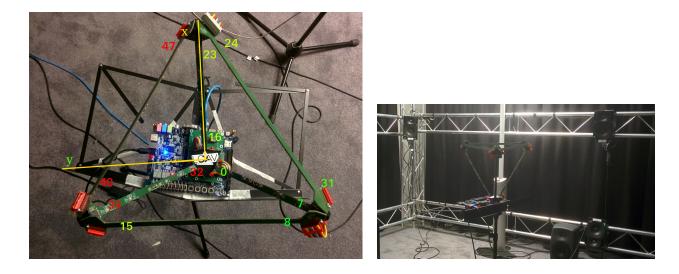

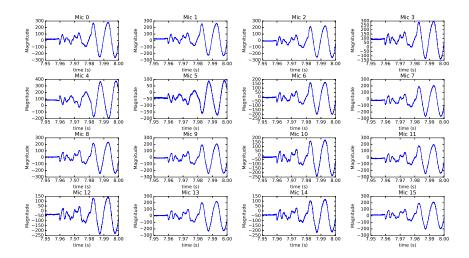

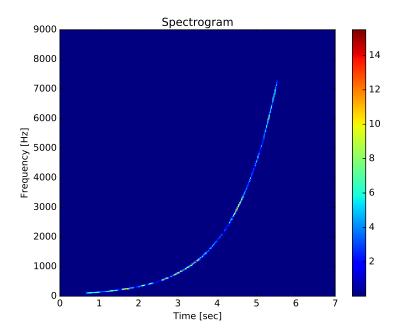

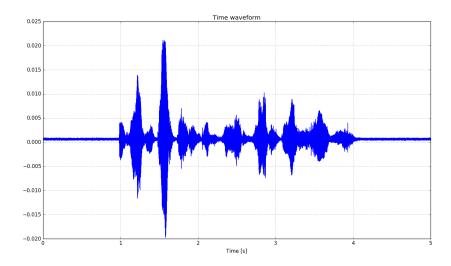

To address those problems this project introduces the Pyramic sound capture system designed at LAP in EPFL. Pyramic is a custom hardware which possesses 48 microphones distributed in the edges of a tetrahedron. The microphone arrays interact with a Terasic DE1-SoC board from Altera Cyclone V family devices, which combines a Hard Processor System (HPS) and a Field Programmable Gate Array (FPGA) in the same die. The HPS part integrates a dual-core ARM-based Cortex-A9 processor, which combined with the power of FPGA design suitable for processing multichannel microphone signals. This thesis explains the implementation of the Pyramic array. Moreover, FPGA-based hardware accelerators have been designed to implement a Master SPI communication with the array and a parallel 48 channels FIR filters cascade of the audio data for delay-and-sum beamforming applications. Additionally, the configuration of the HPS part allows the Pyramic array to be controlled through a Linux based OS. The main purpose of the project is to develop a flexible platform in which real-time echo-location algorithms can be implemented. The effectiveness of the Pyramic array design is illustrated by testing the recorded data with offline direction of arrival algorithms developed at LCAV in EPFL.

**Key words**: FPGA, HPS, microphone arrays, Altera Cyclone V, DE1-SoC, real-time DSP, beamforming, FIR filters.

# **Contents**

| Ał | Abstract (English/Français/Deutsch) i |                                          |    |  |  |  |  |

|----|---------------------------------------|------------------------------------------|----|--|--|--|--|

| Li | st of                                 | figures                                  | ix |  |  |  |  |

| Li | st of                                 | tables                                   | X  |  |  |  |  |

| 1  | Intr                                  | roduction                                | 1  |  |  |  |  |

|    | 1.1                                   | Motivation                               | 1  |  |  |  |  |

|    | 1.2                                   | Objective                                | 1  |  |  |  |  |

|    | 1.3                                   | Contributions                            | 2  |  |  |  |  |

|    | 1.4                                   | Structure of the thesis                  | 2  |  |  |  |  |

| 2  | Mic                                   | crophone arrays sound capturing systems  | 5  |  |  |  |  |

|    | 2.1                                   | Acoustic Noise                           | 5  |  |  |  |  |

|    |                                       | 2.1.1 Noise Sources                      | 5  |  |  |  |  |

|    |                                       | 2.1.2 Speech Signal                      | 7  |  |  |  |  |

|    | 2.2                                   | Microphone arrays                        | 8  |  |  |  |  |

|    |                                       | 2.2.1 Types of microphone arrays         | 8  |  |  |  |  |

|    | 2.3                                   | Sound Capture model                      | 10 |  |  |  |  |

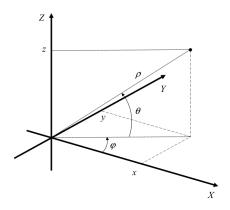

|    |                                       | 2.3.1 Coordinate system                  | 10 |  |  |  |  |

|    |                                       | 2.3.2 Far-field Model                    | 11 |  |  |  |  |

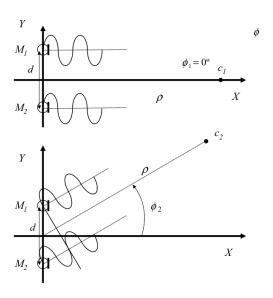

|    |                                       | 2.3.3 Spatial Aliasing and Ambiguity     | 11 |  |  |  |  |

|    | 2.4                                   | Summary                                  | 12 |  |  |  |  |

| 3  | Pyr                                   | amic Microphone array                    | 13 |  |  |  |  |

|    | 3.1                                   | Introduction                             | 13 |  |  |  |  |

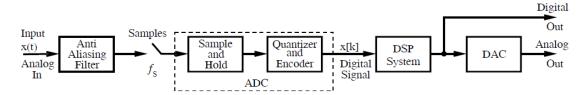

|    | 3.2                                   | Digital Signal Processing                | 13 |  |  |  |  |

|    | 3.3                                   | Pyramic Array                            | 14 |  |  |  |  |

|    |                                       | 3.3.1 Overview                           | 14 |  |  |  |  |

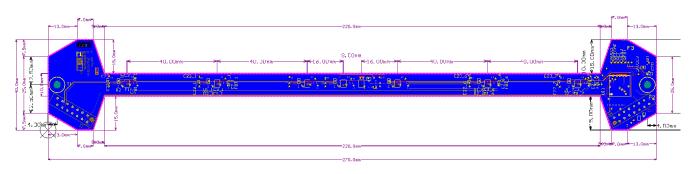

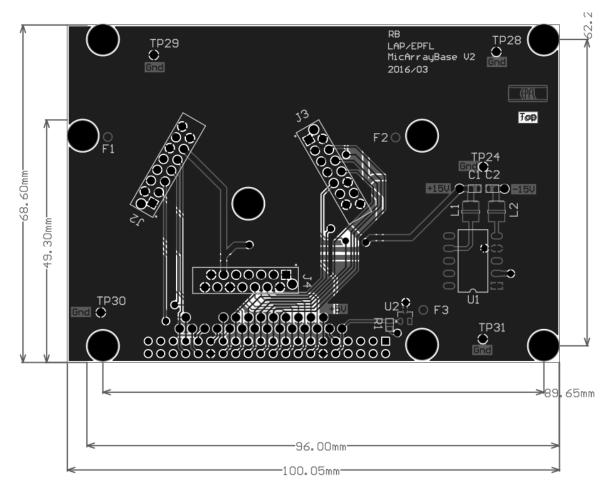

|    |                                       | 3.3.2 Pyramic array layout               | 15 |  |  |  |  |

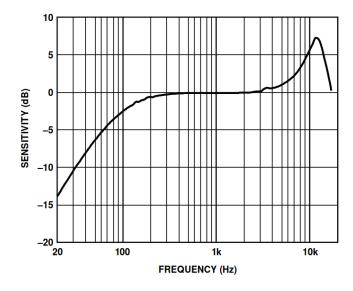

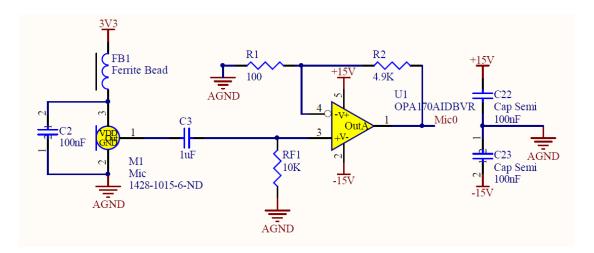

|    |                                       | 3.3.3 INMP504 microphone                 | 16 |  |  |  |  |

|    |                                       | 3.3.4 Signal conditioning                | 17 |  |  |  |  |

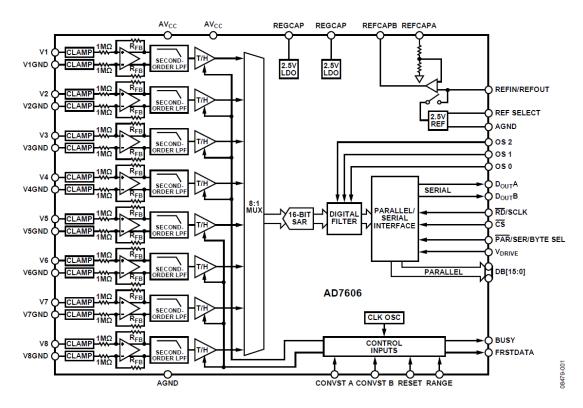

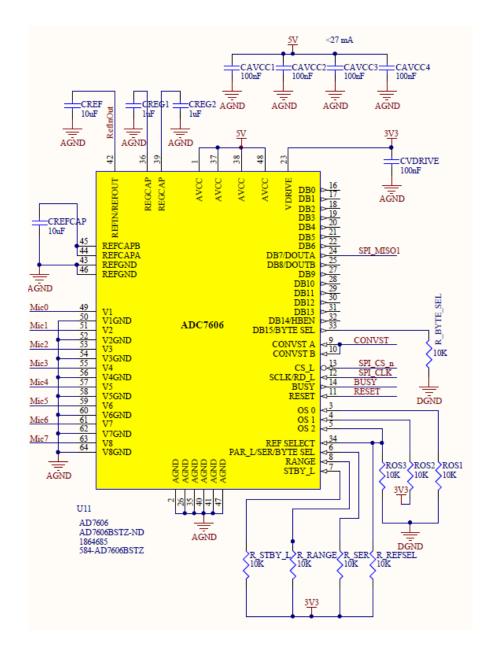

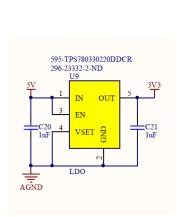

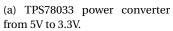

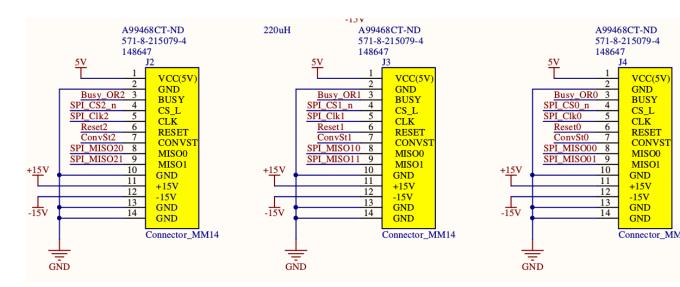

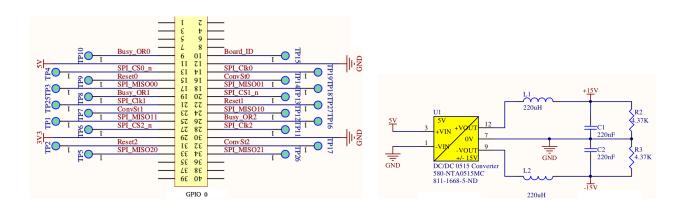

|    |                                       | 3.3.5 AD7606 Analog to Digital Converter | 17 |  |  |  |  |

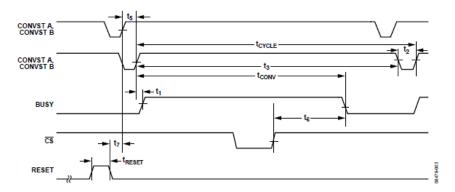

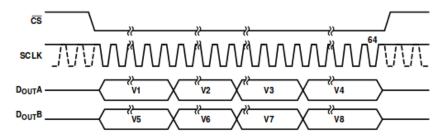

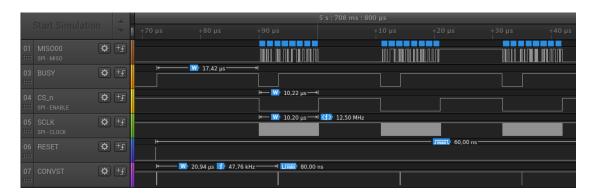

|    |                                       | 3.3.6 Timing requirements                | 19 |  |  |  |  |

#### **Contents**

|   | 3.4 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21       |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4 | FPG | GA Technologies: Terasic DE1-SoC Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23       |

|   | 4.1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23       |

|   | 4.2 | FPGA Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23       |

|   |     | 4.2.1 FPGA Benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23       |

|   |     | 4.2.2 Intelectual Property (IP) Cores design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24       |

|   |     | 4.2.3 FPGA Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25       |

|   | 4.3 | Terasic DE1-SoC Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25       |

|   |     | 4.3.1 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25       |

|   |     | 4.3.2 Cyclone V Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27       |

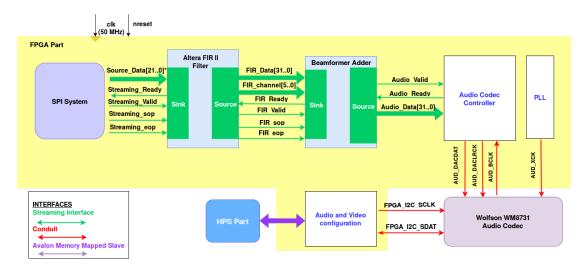

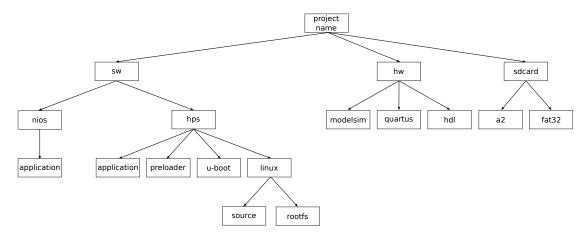

|   | 4.4 | Pyramic array overall design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28       |

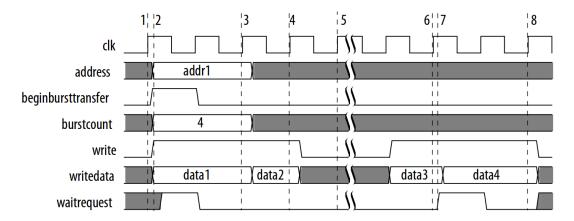

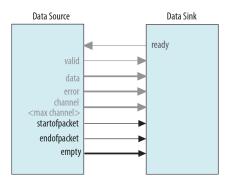

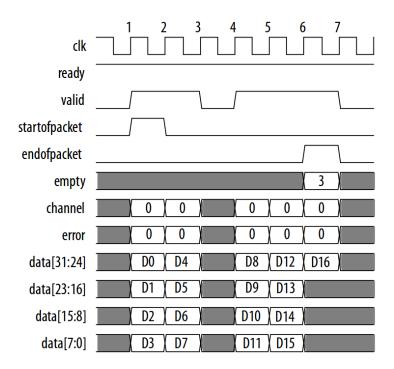

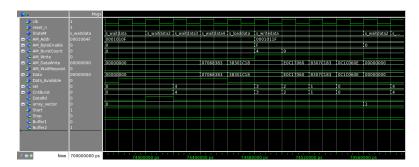

|   | 4.5 | FPGA interconnections: Avalon Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28       |

|   |     | 4.5.1 Avalon Memory-Mapped Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30       |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32       |

|   |     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33       |

|   | 4.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34       |

| 5 | FPG | GA Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35       |

| J | 5.1 | o a constant of the constant o | 35       |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35       |

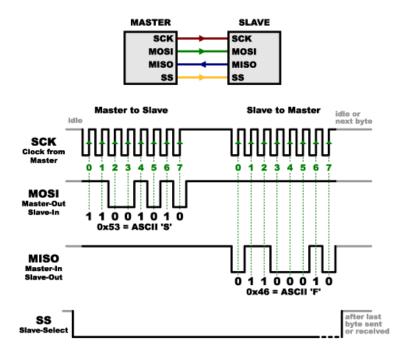

|   | 3.2 | o .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35       |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36       |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37       |

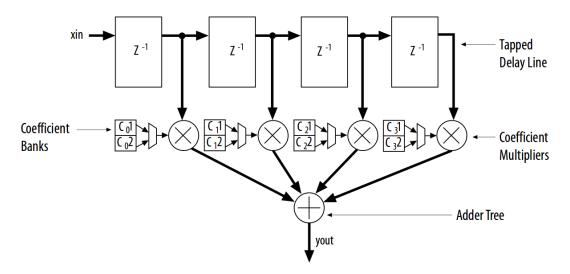

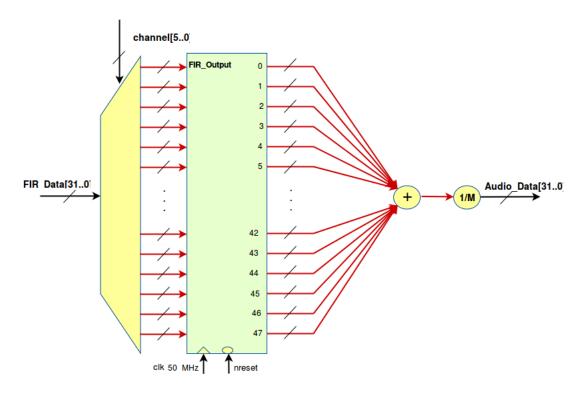

|   | 5.3 | , 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31<br>46 |

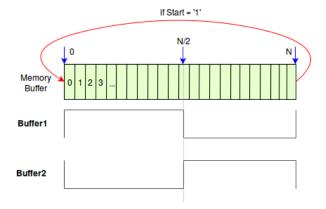

|   | 5.5 | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46<br>46 |

|   |     | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40<br>47 |

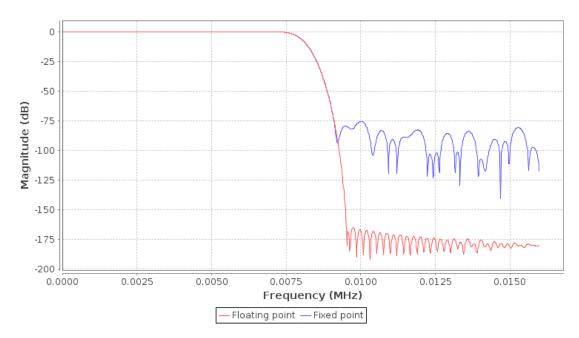

|   |     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41<br>48 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48<br>49 |

|   |     | o de la companya de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|   | E 1 | , 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51       |

|   | 5.4 | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54       |

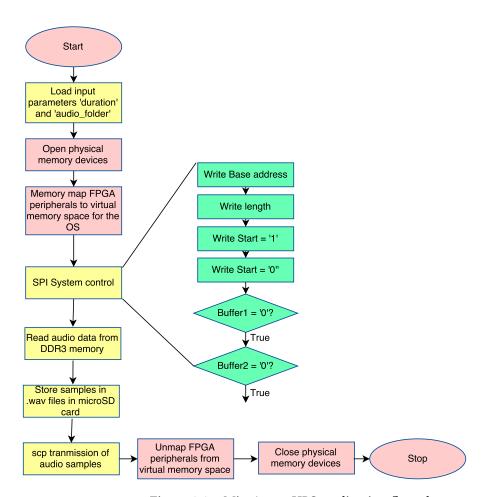

| 6 | HPS | 8 <b>r</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55       |

|   | 6.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55       |

|   | 6.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55       |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57       |