# Optimal Inductor Current in Boost DC/DC Converters Operating in Burst Mode under Light-Load Conditions

Ferran Reverter and Manel Gasulla, Member, IEEE

Abstract— This letter analyses how the efficiency of boost DC/DC converters operating in burst mode under light-load conditions can be improved by an appropriate selection of the inductor current that transfers energy from the input to the output. A theoretical analysis evaluates the main power losses (fixed, conduction and switching losses) involved in such converters and how do they depend on the inductor current. This analysis shows that there is an optimal value of this current that causes minimum losses and, hence, maximum efficiency. These theoretical predictions are then compared with experimental data resulting from a commercial boost DC/DC converter (TPS61252) whose average inductor current is adjustable. Experimental results show that the use of the optimal inductor current, which was around 340 mA for an output voltage of 5 V, provides an efficiency increase of 7%.

*Index Terms*— Boost converter, burst mode, DC/DC converter, efficiency, light-load conditions.

## I. INTRODUCTION

MANY portable devices operate in low-power standby modes for most of the time and, therefore, increasing the efficiency of voltage regulators under light-load conditions (i.e. for load currents of a few milliamperes) is crucial for extending the battery lifetime. Regrettably, switching DC/DC converters with a pulse-width modulation (PWM), which involves a fixed switching frequency, have a low efficiency (say, lower than 60 % [1]) at light loads mainly due to switching losses. To cope with this limitation, the efficiency of PWM converters can be improved by dynamically adjusting: (i) the gate driving voltage [2,3], (ii) the size of the switching transistors [4,5], and (iii) the number of active phases (i.e. phase shedding) in multiphase DC/DC converters [6]. Softswitching techniques, such as zero-voltage switching and zero-current switching, have also been proposed to reduce switching losses due to the voltage-current overlap in lowpower [7] and medium-power [8] DC/DC converters

Another way to tackle the light-load efficiency is the use of a hybrid control whereby the converter operates in PWM at

This work was supported by the Spanish Ministry of Science under project TEC2011-27397.

F. Reverter and M. Gasulla are with the e-CAT Research Group, Universitat Politècnica de Catalunya (UPC) – BarcelonaTech, 08860 Castelldefels, Spain (e-mail: <a href="mailto:ferran.reverter@upc.edu">ferran.reverter@upc.edu</a>; <a href="mailto:manel.gasulla@upc.edu">manel.gasulla@upc.edu</a>).

heavy loads, but it switches to a variable-frequency mode, such as pulse-frequency modulation (PFM) or burst mode (BM), at light loads. In PFM, the switching frequency is scaled down with the load current, thus reducing the switching losses at light loads. Two PFM-based approaches operating in discontinuous conduction mode (DCM) have been proposed [9]: (i) constant on-time [10], which can also be dynamically adapted [11], and (ii) constant peak inductor current [12]. In both cases, there is an optimal value of on-time and peak current that leads to maximum efficiency [9].

In BM (also known as pulse-skip mode), the transistors of the switching DC/DC converter are cyclically switched on and off at a fixed frequency (the same as in PWM) during an active period thus resulting in a burst of energy pulses transferred to the output, but they are permanently in off-state during an inactive period [13]. The lower the load current, the longer the inactive period and, hence, the lower the equivalent switching frequency. This principle has also been applied to improve the light-load efficiency of resonant DC/DC converters [14]. Two techniques have been proposed to control the burst in active period [15]: (i) constant duty cycle [13]; and (ii) constant average (or peak) inductor current [16], which has been applied in many commercial DC/DC converters such as TPS6120x, LT1303, L6920 and STBB1-AXX. Experimental results using the latter technique showed that the efficiency in continuous conduction mode (CCM) was higher than in DCM [16]. However, unlike what happens in PFM, the optimal value of inductor current that provides maximum efficiency in BM-CCM has not been analyzed so far. This is evaluated herein for a boost DC/DC converter showing that an appropriate selection of that current can provide an efficiency increase of 7%.

# II. OPERATING PRINCIPLE

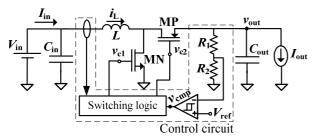

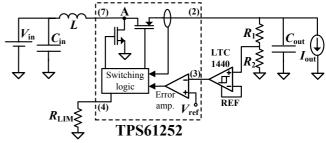

A schematic of a synchronous boost DC/DC converter is shown in Fig. 1. It relies on an inductor (L) and two power MOSFET transistors (MN and MP) with the corresponding gate control signals ( $v_{c1}$  and  $v_{c2}$ ) generated by a control circuit. This control circuit has two feedback loops: (i) a voltage loop that monitors the output voltage ( $v_{out}$ ) by a voltage divider  $R_1$ - $R_2$  and a comparator (with a hysteresis of  $\pm V_{hys}$ ) whose noninverting input is connected to a reference voltage ( $V_{ref}$ ), and (ii) a current loop that monitors the inductor current ( $i_L$ ) by either a shunt resistance in series with L or the voltage drop

Fig. 1. Schematic of a synchronous boost DC/DC converter.

across MN or MP. Current information has also been obtained by measuring the output voltage ripple, as suggested in  $V^2$ -controlled converters, but its application to boost converters has some limitations [17] that have been solved, for instance, by (a) an improved version of the  $V^2$  control called  $V^2$ C control [18], and (b) a differentiator-based analog processing of the output voltage ripple [19]. The input of the converter is connected to a DC voltage source ( $V_{\rm in}$ ), which models the voltage supplied by batteries, in parallel with a high-value input capacitor ( $C_{\rm in}$ ). On the other hand, the output of the converter is connected to a DC current source ( $I_{\rm out}$ ), which models the current consumed by the load, in parallel with a high-value output capacitor ( $C_{\rm out}$ ).

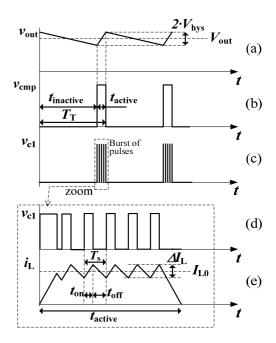

The circuit in Fig. 1 regulates  $v_{\text{out}}$  around a desired DC voltage  $(V_{\text{out}})$  by operating in BM. Its overall operating principle is represented in Figs. 2a, 2b and 2c with two stages that respectively last  $t_{\text{inactive}}$  and  $t_{\text{active}}$ , and an overall duty cycle  $D_{\rm T} = t_{\rm active}/T_{\rm T}$ , where  $T_{\rm T} = t_{\rm inactive} + t_{\rm active}$ . In the first stage, the converter is deactivated (i.e. both transistors are in off-state) and  $C_{\text{out}}$  supplies the DC current to the load, thus decreasing  $v_{\text{out}}$ . When  $v_{\text{out}} = V_{\text{out}} - V_{\text{hys}}$ , the state of the comparator output  $(v_{cmp})$  changes and the second stage starts. Then, input energy (mostly coming from  $C_{in}$ , but also from  $V_{in}$ ) is transferred to the output through a burst of energy pulses, thus increasing  $v_{\text{out}}$ . To do so, a burst of on/off pulses is applied to the gate of the transistors, as shown in Fig. 2c and with more details in Fig. 2d. When  $v_{\text{out}} = V_{\text{out}} + V_{\text{hys}}$ , the converter is deactivated and the process starts again. Note that the current coming from  $V_{\rm in}$  increases during  $t_{\rm active}$  providing part of the energy required, but it decreases towards zero during  $t_{\text{inactive}}$  with the recharge of  $C_{\rm in}$ . The average value of that current is  $I_{\rm in}$  =  $I_{\text{out}}V_{\text{out}}/V_{\text{in}}$  if losses are neglected.

During the active period, the converter has two operating phases that respectively last  $t_{\rm on}$  and  $t_{\rm off}$ , with a switching period  $T_{\rm s}=t_{\rm on}+t_{\rm off}$ . In steady state, the duty cycle (i.e.  $D=t_{\rm on}/T_{\rm s}$ ) depends on the operating conditions as  $1-V_{\rm in}/V_{\rm out}$ , assuming CCM and no losses. The switching frequency (i.e.  $f_{\rm s}=1/T_{\rm s}$ ) is fixed and equal to that employed in PWM. In the first phase (MN on, MP off), input energy is stored in L and  $i_{\rm L}$  increases, whereas in the second phase (MN off, MP on), the energy accumulated in L is transferred to the output and  $i_{\rm L}$  decreases. A current-programmed mode control in CCM is assumed so that  $i_{\rm L}$  has an average of  $I_{\rm L0}$  (whose value is analyzed herein so as to maximize the efficiency) and a ripple of  $\Delta I_{\rm L}$ . The resulting waveforms of  $v_{\rm c1}$  and  $i_{\rm L}$  are shown in Figs. 2d and 2e, respectively;  $v_{\rm c2}$  is the same as  $v_{\rm c1}$  but with

Fig. 2. Waveforms of interest from the circuit in Fig. 1 operating in BM-CCM.

some dead time between them to prevent cross conduction. Using this operating principle, the lower the load current, the lower the equivalent switching frequency (i.e.  $f_s D_T$ ) and, hence, the lower the effects of the switching losses on the efficiency.

### III. THEORETICAL ANALYSIS

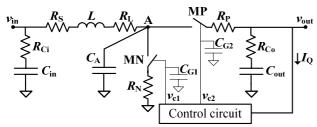

Power losses in the DC/DC converter shown in Fig. 1 are analyzed using the equivalent circuit model represented in Fig. 3, where  $R_{\rm S}$  is a shunt resistance to sense  $i_{\rm L}$ ,  $R_{\rm L}$  is the equivalent series resistance (ESR) of L,  $R_{\rm Ci}$  and  $R_{\rm Co}$  are the ESR of  $C_{\rm in}$  and  $C_{\rm out}$ , respectively,  $R_{\rm N}$  and  $R_{\rm P}$  are the onresistances of MN and MP, respectively,  $C_{\rm A}$  is the parasitic capacitance at node A (for example, due to the drain-bulk junction capacitance of MN), and  $C_{\rm G1}$  and  $C_{\rm G2}$  are the parasitic capacitances at the gate of MN and MP, respectively. The control circuit is assumed to be powered from the output, as usually happens in boost converters, and has a current consumption of  $I_{\rm Q,a}$  in active mode and  $I_{\rm Q,i}$  in inactive mode, where  $I_{\rm Q,i}$  is expected to be much lower than  $I_{\rm Q,a}$ .

The circuit in Fig. 3 has three types of power losses [9]: (i) fixed losses, which are mainly due to the quiescent current of the control circuit; (ii) conduction losses, which are generated by the Joule effect involved in the parasitic resistances; and (iii) switching losses, which are mostly caused by the charge-discharge process of the parasitic capacitances and the voltage-current overlap in MN during the transitions (with an average transition time of  $t_c$ ) from on to off and vice versa [20]. The expression of such losses in both active and inactive modes is summarized in Table I, where  $R_{\rm eq,a} = R_{\rm Ci} + R_{\rm S} + R_{\rm L} + R_{\rm N}D + (R_{\rm P} + R_{\rm Co})(1-D)$ ,  $R_{\rm eq,i} = R_{\rm Ci}(V_{\rm out}/V_{\rm in})^2 + R_{\rm Co}$  and  $C_{\rm eq} = C_{\rm G1} + C_{\rm G2} + C_{\rm A}$ . As for  $R_{\rm eq,a}$  it is assumed that, in active mode,  $i_{\rm L}$  is mostly provided by  $C_{\rm in}$  and that the current through MP is

Fig. 3. Equivalent circuit model for the analysis of power losses in the circuit shown in Fig. 1.

$TABLE\ I$  Power loss components of the circuit in Fig. 3 in both active and inactive modes

| 1.1101172.110323 |                                                                              |                            |

|------------------|------------------------------------------------------------------------------|----------------------------|

| Power losses     | Active mode                                                                  | Inactive mode              |

| Fixed            | $V_{ m out}I_{ m Q,a}$                                                       | $V_{ m out}I_{ m Q,i}$     |

| Conduction       | $R_{\mathrm{eq,a}}I_{\mathrm{L0}}^{2}$ (a)                                   | $R_{\rm eq,i}I_{ m out}^2$ |

| Switching        | $C_{\rm eq}V_{\rm out}^2f_{\rm s} + V_{\rm out}I_{\rm L0}t_{\rm c}f_{\rm s}$ | 0                          |

<sup>&</sup>lt;sup>a</sup> The RMS value of  $i_L$  is approximated to  $I_{L0}$  since  $\Delta I_L < I_{L0}$  [21].

much higher than  $I_{\rm out}$ , whereas for  $R_{\rm eq,i}$  it is considered that the current that charges  $C_{\rm in}$  in inactive mode is  $I_{\rm out}/V_{\rm out}/V_{\rm in}$ . Furthermore,  $C_{\rm G1}$ ,  $C_{\rm G2}$  and  $C_{\rm A}$  have been lumped in one equivalent capacitance ( $C_{\rm eq}$ ) since they have the same charging voltage (i.e.  $V_{\rm out}$ ); note that the control circuit is powered from the output and, hence, the gate driving voltage of MN and MP equals  $V_{\rm out}$ . Fixed losses due to leakage current of transistors and capacitors, and switching losses due to the body diode of MP during the dead time and to the inductor core have been considered negligible.

The average value of power losses over a whole period (i.e.  $T_{\rm T}$ ) can be expressed and approximated (assuming  $P_{\rm L,active} >> P_{\rm L.inactive}$ ) as

$$P_{\rm L} = P_{\rm L,active} D_{\rm T} + P_{\rm L,inactive} (1 - D_{\rm T}) =$$

$$\left( P_{\rm Lactive} - P_{\rm L,inactive} \right) D_{\rm T} + P_{\rm L,inactive} \approx P_{\rm L,active} D_{\rm T} + P_{\rm L,inactive}$$

(1)

where  $P_{\rm L,active}$  and  $P_{\rm L,inactive}$  are the overall power losses in active and inactive modes, respectively, obtained from Table I. Since the charge extracted from  $C_{\rm out}$  in inactive mode (i.e.  $I_{\rm out} I_{\rm inactive}$ ) equals that accumulated in  $C_{\rm out}$  in active mode (i.e.  $[I_{\rm L0}(1-D)-I_{\rm out}]I_{\rm active}$ ),  $D_{\rm T}$  can also be written as  $I_{\rm out} V_{\rm out}/I_{\rm L0} V_{\rm in}$ . Using this relation in (1), the efficiency in BM can be calculated as

$$\begin{split} \eta &= \frac{1}{1 + \frac{P_{\rm L}}{P_{\rm out}}} \approx 1 - \frac{P_{\rm L}}{P_{\rm out}} = \\ 1 - \frac{1}{V_{\rm in}} \left[ R_{\rm eq,a} I_{\rm L0} + \frac{V_{\rm out} I_{\rm Q,a} + C_{\rm eq} V_{\rm out}^2 f_{\rm s}}{I_{\rm L0}} + V_{\rm out} t_{\rm c} f_{\rm s} \right] - \frac{I_{\rm Q,i}}{I_{\rm out}} - \frac{I_{\rm out} R_{\rm eq,i}}{V_{\rm out}} \end{split}$$

(2)

where  $P_{\text{out}}$  is the output power (i.e.  $V_{\text{out}}I_{\text{out}}$ ). According to (2),  $\eta$  increases with increasing  $V_{\text{in}}$ , decreases with increasing  $V_{\text{out}}$ ,

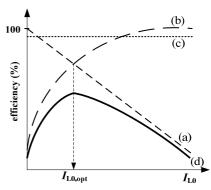

Fig. 4. Efficiency versus  $I_{\rm L0}$  considering the effects of different power loss components.

but slightly depends on  $I_{\rm out}$  because the last two terms on the right-hand side in (2) are the least significant factors; this performance will be verified later in Section IV. If we compare converters operating in BM with those that continuously operate in PWM [22], we realize that the effects of  $V_{\rm in}$  and  $V_{\rm out}$  on  $\eta$  are similar, but not those of  $I_{\rm out}$  since the light-load efficiency of PWM converters significantly decreases with decreasing  $I_{\rm out}$ .

Equation (2) also shows that  $\eta$  clearly depends on  $I_{L0}$ , but each power loss component has its own effects on such dependence. This is represented in Fig. 4 as follows: case (a) corresponds to conduction losses in active mode, where  $\eta$  decreases with increasing  $I_{L0}$ ; case (b) corresponds to fixed losses and switching losses due to  $C_{\rm eq}$  in active mode, where  $\eta$  increases with increasing  $I_{L0}$ ; case (c) corresponds to switching losses due to the voltage-current overlap in active mode together with losses in inactive mode, where  $\eta$  is independent of  $I_{L0}$ ; and case (d) shows the overall effects with a maximum of efficiency at an optimal value of  $I_{L0}$  ( $I_{L0,\rm opt}$ ). Taking the derivative of (2) with respect to  $I_{L0}$  and then making the result of the derivative equal zero, we can find the value of  $I_{L0}$  that causes the maximum:

$$I_{\text{L0,opt}} = \sqrt{\frac{V_{\text{out}}I_{\text{Q,a}} + C_{\text{eq}}V_{\text{out}}^2 f_{\text{s}}}{R_{\text{eq,a}}}}$$

(3)

which is independent of both  $I_{\text{out}}$  and  $V_{\text{in}}$ , but it increases with increasing  $V_{\text{out}}$ .

Fig. 5. Application circuit based on the TPS61252 employed to prove the concept of optimal inductor current; the numbers given in brackets are the pin numbers of the TPS61252.

### IV. EXPERIMENTAL RESULTS

The concept of optimal inductor current has been tested experimentally using a commercial boost DC/DC converter (TPS61252 from Texas Instruments [23]) that enables adjusting  $I_{L0}$  from 100 mA to 1500 mA by an external resistor  $(R_{LIM})$ ; such a current is measured on-chip through the voltage drop across MP and, hence,  $R_S = 0$  in this particular case. In order to have the BM-CCM operation shown in Fig. 2, it was necessary to place an external comparator (LTC1440 from Linear Technology) between the voltage divider  $R_1$ - $R_2$  and the feedback (FB) input of the converter, as shown in Fig. 5. Using this circuit, if  $v_{\text{out}}$  is lower than the desired voltage, then the comparator output is low, which brings the converter to active mode and, consequently,  $i_L$  is regulated around  $I_{L0}$ . Otherwise, if  $v_{out}$  is higher than the desired voltage, then the comparator output is high and the converter enters into inactive mode. The comparator LTC1440 is an ultralow-power model with a built-in reference (REF in Fig. 5) and a programmable hysteresis that was adjusted to have  $V_{\text{hys}}$ = 5 mV.

The circuit in Fig. 5 was subjected to different test conditions: (i) different values of  $I_{\rm out}$  (5, 10 and 20 mA) sunk by a DC current source (Agilent B2901), (ii) different values of  $V_{\rm out}$  (4, 5 and 6 V) set by an appropriate voltage divider  $R_1$ - $R_2$  and measured by a digital multimeter (Agilent 34410), and (iii) different values of  $V_{\rm in}$  (2.4, 2.7 and 3.0 V) supplied by a DC voltage source (Agilent E3631A); this range of  $V_{\rm in}$  emulates, for instance, that supplied by two cylindrical alkaline primary batteries in series. In all cases, a power analyzer (Yokogawa WT310) measured the average input power with a sampling frequency of 100 kSa/s and an update rate of 5 s.  $C_{\rm in}$  and  $C_{\rm out}$  were low-ESR tantalum capacitors of  $2\times1$  mF and  $4\times2.2$  mF, respectively, and L=2.2  $\mu$ H.

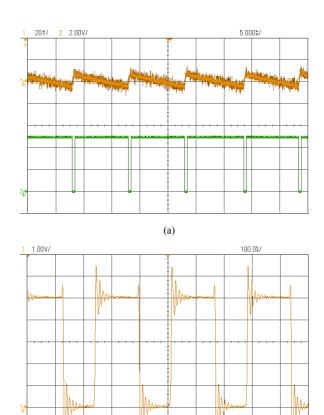

The operating principle of the circuit in Fig. 5 was first verified by monitoring the voltage waveform at the main nodes using a digital oscilloscope. Fig. 6 shows, for example, the resulting waveforms for  $V_{\text{in}} = 3.0 \text{ V}$ ,  $V_{\text{out}} = 5.0 \text{ V}$ ,  $I_{\rm out}$  = 10 mA and  $I_{\rm L0} \approx 370$  mA. The output voltage and the comparator output (i.e. pins #2 and #3 of the TPS61252, respectively) are represented in Fig. 6a for several active and inactive periods. Note that the signal at the comparator output is the complementary of that represented in Fig. 2b because this signal is then inverted by the on-chip error amplifier. In Fig. 6a we measured  $V_{\rm hys} \approx$  6-7 mV and  $D_{\rm T} = 5\%$ , which agrees with that estimated from  $I_{\rm out}V_{\rm out}/I_{\rm L0}V_{\rm in}$ . On the other hand, Fig. 6b shows the voltage at the switching node A (i.e. pin #7) within one active period; this signal is also the complementary of that represented in Fig. 2d since it is inverted through MN. In Fig. 6b we measured  $f_s = 3.7$  MHz, instead of the nominal value of 3.25 MHz, and D = 44%, which agrees with that estimated from  $1-\eta V_{\rm in}/V_{\rm out}$  assuming  $\eta = 91\%$  (reported later in Fig. 7). Moreover, the value of D was very stable during the active period, which means that the inductor current was well regulated around  $I_{L0}$ .

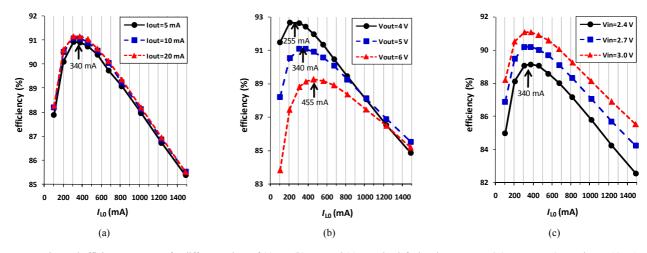

The experimental results of efficiency versus  $I_{L0}$  are shown in Fig. 7 for different values of (a)  $I_{out}$ , (b)  $V_{out}$ , and (c)  $V_{in}$ ,

Fig. 6. From the circuit in Fig. 5, experimental waveforms of (a) the output voltage (channel 1 in AC coupling) and the comparator output (channel 2) for several active and inactive periods, and (b) the voltage at the switching node A within one active period.

using  $V_{\rm in}$  = 3.0 V,  $V_{\rm out}$  = 5.0 V and  $I_{\rm out}$  = 10 mA as default values. The optimal value of  $I_{\rm L0}$  was independent of both  $I_{\rm out}$  (Fig. 7a) and  $V_{\rm in}$  (Fig. 7c), but it increased with increasing  $V_{\rm out}$  (Fig. 7b), which agrees with (3). To be precise,  $I_{\rm L0,opt}$   $\approx$  340 mA in Figs. 7a and 7c, and it increased from 255 to 455 mA in Fig. 7b. Moreover, the efficiency was almost constant with  $I_{\rm out}$  (Fig. 7a), decreased with increasing  $V_{\rm out}$  (Fig. 7b), and increased with increasing  $V_{\rm in}$  (Fig. 7c), as predicted by (2). With respect to the case with minimum efficiency (which was found at either the minimum or the maximum value of  $I_{\rm L0}$ ), the efficiency increased by 6%, 8% and 7% in Figs. 7a, 7b and 7c, respectively, when  $I_{\rm L0,opt}$  was applied.

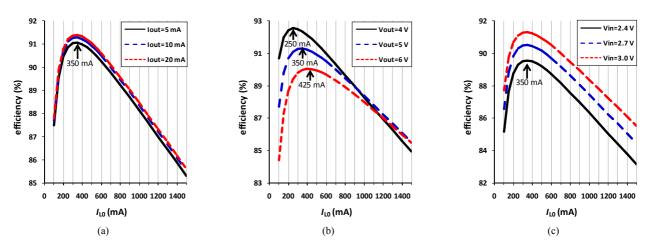

For the same test conditions represented in Fig. 7, Fig. 8 shows the efficiency predicted by (2) using the data available in datasheets; two remarks about Fig. 8: (i)  $C_{\rm eq}$  and  $t_{\rm c}$  were unknown and were initially extracted by fitting (2) to a set of experimental results, and (ii)  $R_{\rm N}$  and  $R_{\rm P}$  were assumed to be dependent on the gate driving voltage of the transistors (i.e.  $V_{\rm out}$ ) in Fig. 8b [2,4]. Figs. 7 and 8 show a very similar response both qualitatively and quantitatively (see, for example, the values of  $I_{\rm L0,opt}$  and  $\eta$ ). Therefore, we can conclude that the model proposed in Section 3 properly predicts the efficiency of DC/DC converters in BM-CCM at different operating conditions.

Fig. 7. Experimental efficiency versus  $I_{L0}$  for different values of (a)  $I_{out}$ , (b)  $V_{out}$ , and (c)  $V_{in}$ . The default values are  $V_{in} = 3.0 \text{ V}$ ,  $V_{out} = 5.0 \text{ V}$  and  $I_{out} = 10 \text{ mA}$ .

Fig. 8. Efficiency predicted by (2) versus  $I_{L0}$  for different values of (a)  $I_{out}$ , (b)  $V_{out}$ , and (c)  $V_{in}$ . The default values are  $V_{in} = 3.0 \text{ V}$ ,  $V_{out} = 5.0 \text{ V}$  and  $I_{out} = 10 \text{ mA}$ .

# V. CONCLUSION

A theoretical analysis and a set of experimental results have demonstrated that DC/DC converters operating in BM-CCM under light-load conditions have an optimal value of inductor current in terms of efficiency. This optimal current is independent of both (i) the input voltage and, hence, of the state (fresh or spent) of the input batteries, and (ii) the load current and, hence, of the variability of the current consumption of the electronics to be powered. However, such an optimal current does depend on the desired output voltage. Experimental tests with a commercial boost DC/DC converter operating in BM have shown that the use of the optimal inductor current (of 340 mA at  $V_{\text{out}} = 5 \text{ V}$ ) provides up to 7% increase in efficiency. DC/DC converters with a hybrid control (i.e. PWM and BM) can make good use of the results presented herein to increase their efficiency under light-load conditions.

### REFERENCES

[1] C. Lee, Y. Oh, K. Na, Y. Kim and N. Kim, "Integrated BiCMOS control circuits for high-performance DC-DC boost converter," *IEEE Trans. Power Electronics*, vol. 28, no. 5, pp. 2596-2603, May 2013.

- [2] M.D. Mulligan, B. Broach, and T.H. Lee, "A constant-frequency method for improving light-load efficiency in synchronous buck converters," *IEEE Power Electronics Letters*, vol. 3, no. 1, pp. 24-29, March 2005.

- [3] P. Liu, W. Ye, J. Tai, H. Chen, J. Chen and Y. Chen, "A high-efficiency CMOS DC-DC converter with 9-µs transient recovery time," *IEEE Trans. Circuits and Systems I: Regular Papers*, vol. 59, no. 3, pp. 575-583. March 2012.

- [4] V. Michal, "Peak-efficiency detection and peak-efficiency tracking algorithm for switched-mode DC-DC power converters," *IEEE Trans. Power Electronics*, vol. 29, no. 12, pp. 6555-6568, Dec. 2014.

- [5] P. Malcovati, M. Belloni, F. Gozzini, C. Bazzani and A. Baschirotto, "A 0.18-µm CMOS, 91%-efficiency, 2-A scalable buck-boost DC-DC converter for LED drivers," *IEEE Trans. Power Electronics*, vol. 29, no. 10, pp. 5392-5398, Oct. 2014.

- [6] J. Su and C. Liu, "A novel phase-shedding control scheme for improved light load efficiency of multiphase interleaved DC-DC converters," *IEEE Trans. Power Electronics*, vol. 28, no. 10, pp. 4742-4752, Oct. 2013.

- [7] S. Zhou and G.A. Rincón-Mora, "A high efficiency, soft switching DC-DC converter with adaptive current-ripple control for portable applications," *IEEE Trans. Circuits and Systems II: Express Briefs*, vol. 53, no. 4, pp. 319-323, April 2006.

- [8] H. Choe, Y. Chung, C. Sung, J. Yun and B. Kang, "Passive snubber for reducing switching-power losses of an IGBT in a DC–DC boost converter," *IEEE Trans. Power Electronics*, vol. 29, no. 12, pp. 6332-6341, Dec. 2014.

- [9] R. Erickson and D. Maksimovic, "High efficiency DC-DC converters for battery-operated systems with energy management," Worldwide Wireless Communications, Annual Reviews on Telecommunications, pp. 1-10, 1995.

- [10] J. Xiao, A.V. Peterchev, J. Zhang, and S.R. Sanders, "A 4-μA quiescentcurrent dual-mode digitally controlled buck converter IC for cellular phone applications," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 12, pp. 2342-2348, Dec. 2004.

- [11] B. Sahu and G.A. Rincón-Mora, "An accurate, low-voltage, CMOS switching power supply with adaptive on-time pulse-frequency modulation (PFM) control," *IEEE Trans. Circuits and Systems I: Regular Papers*, vol. 54, no. 2, pp. 312-321, Feb. 2007.

- [12] H. Deng, X. Duan, N. Sun, Y. Ma, A.Q. Huang, and D. Chen, "Monolithically integrated boost converter based on 0.5-µm CMOS process," *IEEE Trans. Power Electronics*, vol. 20, no. 3, pp. 628-638, May 2005.

- [13] S.K. Kok, M. Mao, and X. Gong, "Burst-mode operation of a switching converter," US 2012/0250378 A1 patent.

- [14] W. Feng, F. Lee and P. Mattavelli, "Optimal trajectory control of burst mode for LLC resonant converter," *IEEE Trans. Power Electronics*, vol. 28, no. 1, pp. 457-466, Jan. 2013.

- [15] O. Trescases and Y. Wen, "A survey of light-load efficiency improvement techniques for low-power DC-DC converters," in *Proc. Int. Conf. Power Electronics*, pp. 326-333, 2011.

[16] S. Angkititrakul and H. Hu, "Design and analysis of buck converter with

- [16] S. Angkititrakul and H. Hu, "Design and analysis of buck converter with pulse-skipping modulation," in *Proc. IEEE Power Electron. Spec. Conf.*, pp. 1151–1156, 2008.

- [17] G. Zhou, S.Z. He, X. Chen, and H. Cui, "Can V<sup>2</sup> control be applied to boost converter?," *Electronics Letters*, vol. 50, no. 8, pp. 627-629, April 2014

- [18] C. Mi, J. Xu, G. Zhou, and Y. Jin, "On the stability of V<sup>2</sup>C controlled boost converter in continuous conduction mode," in *Proc. IEEE 6th Int. Power Electronics and Motion Control Conf.*, pp. 1300-1304, 2009.

- [19] Y.S. Hwang, J.H. Shen, and J.J. Chen., "High-efficiency fast-transient-response V<sup>2</sup>-controlled boost converter with small ESR capacitor," *Electronics Letters*, vol. 49, no. 22, pp. 1402-1404, Oct. 2013.

- [20] N. Mohan, Power electronics. A first course. Hoboken, NJ: John Wiley & Sons, 2012.

- [21] A. Raj, "Calculating efficiency," Texas Instruments, Dallas, SLVA390, 2010

- [22] M.K. Kazimierczuk, *Pulse-width modulated DC-DC power converters*. Chichester, UK: John Wiley & Sons, 2008.

- [23] "TPS61252: Tiny 1.5-A boost converter with adjustable input current limit," Texas Instruments, Dallas, SLVSAG3A, Sept. 2010, Revised Dec. 2014.