#### **Portland State University**

## **PDXScholar**

**Dissertations and Theses**

Dissertations and Theses

Winter 3-20-2017

# **Certifying Loop Pipelining Transformations in Behavioral Synthesis**

Disha Puri Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Theory and Algorithms Commons

## Let us know how access to this document benefits you.

#### **Recommended Citation**

Puri, Disha, "Certifying Loop Pipelining Transformations in Behavioral Synthesis" (2017). Dissertations and Theses. Paper 3480.

https://doi.org/10.15760/etd.5364

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

## Certifying Loop Pipelining Transformations in Behavioral Synthesis

by

#### Disha Puri

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

Dissertation Committee:

Fei Xie, Chair

Jingke Li

Suresh Singh

Sandip Ray

Fu Li

Portland State University 2017

#### ABSTRACT

Due to the rapidly increasing complexity in hardware designs and competitive time to market trends in the industry, there is an inherent need to move designs to a higher level of abstraction. Behavioral Synthesis is the process of automatically compiling such Electronic System Level (ESL) designs written in high-level languages such as C, C++ or SystemC into Register-Transfer Level (RTL) implementation in hardware description languages such as Verilog or VHDL. However, the adoption of this flow is dependent on designers' faith in the correctness of behavioral synthesis tools.

Loop pipelining is a critical transformation employed in behavioral synthesis process, and ubiquitous in commercial and academic behavioral synthesis tools. It improves the throughput and reduces the latency of the synthesized hardware. It is complex and error-prone, and a small bug can result in faulty hardware with expensive ramifications. Therefore, it is critical to certify the loop pipelining transformation so that designers can trust the behaviorally synthesized pipelined designs. Certifying a loop pipelining transformation is however, a major research challenge because there is a huge semantic gap between the input sequential design and the output pipelined implementation, making it infeasible to verify their equivalence with automated sequential equivalence checking (SEC) techniques.

Complex loop pipelining transformations can be certified by a combination of theorem proving and SEC: (1) creating a certified pipelining algorithm which generates a reference pipeline model by exploiting pipeline generation information from the synthesis flow (e.g., the iteration interval of a generated pipeline) and (2) conduct SEC between the synthesized pipeline and this reference model. However, a key and arguably, the most complex component of this approach is the development of a formal, mechanically verifiable loop pipelining algorithm.

We show how to systematically construct such an algorithm, and carry out its verification using the ACL2 theorem prover. We propose a framework of certified pipelining primitives which are essential for designing pipelining algorithms. Using our framework, we build a certified loop pipelining algorithm. We also propose a key invariant in certifying this algorithm, which links sequential loops with their pipelined counterparts. This is unlike other invariants that have been used in proofs of microprocessor pipelines so far.

This dissertation provides a framework for creating certified pipelining algorithms utilizing a mechanical theorem prover. Using this framework, we have developed a certified loop pipelining algorithm. This certified algorithm is essential in the overall approach to certify behaviorally synthesized pipelined designs. We demonstrate the scalability and robustness of our algorithm on several ESL designs across various domains.

### **DEDICATION**

To my Grandparents

Mrs. Rama Devi & Mr. M. C. Arora

Mrs. Laxmi Devi & Mr. R. D. Gandhi

who have been the pillars of spiritual guidance in my life, and

whose loving spirits blesses and sustains me still

#### ACKNOWLEDGMENTS

In the process of working through this dissertation, I have been blessed with meeting people who have helped me unconditionally and supported me through the highs and lows of these past years. Even though it cannot be expressed in words, how much their support means to me, I want to take this opportunity to thank them from the bottom of my heart.

First and Foremost, I would like to thank my advisor Prof. Fei Xie. He is a great advisor whose mentorship and intellectual insights helped me get a wholesome view of formal verification and pick an area I love to work in. From helping me define the project, to the point of teaching me how to identify research problems and become an independent researcher - without his support and encouragement, this dissertation would not have been accomplished. His deep theoretical knowledge and passion about developing practical tools had a great influence on my Ph.D research and future career. Given my unique personal family situation, I am indebted to him for his patience and the kind of support he provided through the final years of dissertation.

I would also like to take this opportunity to thank Dr. Sandip Ray who has taken out his personal time to help me in all the facets of this research and has been a steady influence throughout my Ph.D. career. He has been my guide throughout and has oriented and supported me with a lot of patience. I have a huge respect for his knowledge in this area and will always be grateful to him for encouraging me to come up with new ideas in times of difficulties. I will fondly remember our

long thought provoking discussions irrespective of the time of the day.

Besides Prof. Fei Xie and Dr Sandip Ray, I would like to thank Prof. Suresh Singh, Prof. Feng Liu, and Prof. Fu Li for serving on my dissertation committee. Thanks for their valuable feedback and willingness to listen to my ideas. Thanks a lot for understanding my personal situation and supporting me in the final phase of this degree.

I would like to thank Dr. Kecheng Hao and Dr. Zhenkun Yang. Many research ideas of this dissertation come from fruitful discussions with them. I am grateful that I had great opportunity to work with talented group members: Dr. Kai Cong and Dr. Li Lei.

I would like to thank my in-laws who encouraged me to pursue post graduate studies. Their continuous encouragement and endless sacrifices have helped me to grow both personally and professionally and I can never thank them enough for their love and support. I would like to thank my parents who have always believed in me and motivated me throughout my life. They have instilled in me a feeling that God would guide and support me in every situation and that feeling has helped me overcome a lot of obstacles I have faced in the past few years.

I would like to thank my husband for his unconditional love and making me feel at all times that my education and my dreams are as important as his own. I am blessed to have found in him a guide and a friend. Finally, I would like to thank my 1 year old son whose contagious smile can brighten up any tiring day.

## TABLE OF CONTENTS

| Abstra  | nct                                                                  |     |

|---------|----------------------------------------------------------------------|-----|

| Dedica  | ation                                                                | ii  |

| Ackno   | wledgments                                                           | iv  |

| List of | Tables                                                               | vii |

| List of | Figures                                                              | iz  |

| Chapte  | er 1 Introduction                                                    | 1   |

| 1.1     | Dissertation Summary                                                 | -   |

| 1.2     | Motivation                                                           | -   |

| 1.3     | Problem Statement                                                    | ŗ   |

| 1.4     | Overview of our Approach                                             |     |

| 1.5     | Outline                                                              |     |

| Chapte  | er 2 Background and Context                                          | 10  |

| 2.1     | Behavioral Synthesis                                                 | 1(  |

| 2.2     | Overall Certification Model for Behaviorally Synthesized Pipelines . | 11  |

| 2.3     | A Reference Pipeline Approach                                        |     |

| Chapte  | er 3 Formalization                                                   | 16  |

| 3.1     | Intermediate Representation: CCDFG                                   | 16  |

| 3.2     | Correctness of Loop Pipelining                                       | 20  |

| Chapte  | er 4 Research Challenges                                             | 25  |

| 4.1     | Importance of using Formal Methods for checking correctness          | 25  |

| 4.2     | Challenges associated with Formal reasoning                          | 25  |

| 4.3     | Comparison with Previous Algorithm                                   |     |

| Chapte  | er 5 Our Approach                                                    | 29  |

|         |                                                                  | , 1 |

|---------|------------------------------------------------------------------|-----|

| 5.1     | Framework of Provable Pipelining Primitives                      | 30  |

| 5.2     | Our Loop Pipelining Algorithm                                    |     |

| Chapt   | er 6 Proof Sketch                                                | 45  |

| 6.1     | Correctness of Primitives                                        | 45  |

| 6.2     | Key Invariant on Correspondence Between Back-edges of Sequential | 48  |

| 6.3     | and Pipelined Loops                                              |     |

|         | Correctness of our algorithm                                     |     |

| 6.4     | Lessons from Previous False Starts                               | 63  |

| Chapt   | er 7 Viability of our Approach                                   | 65  |

| 7.1     | Experimental Results                                             | 65  |

| 7.2     | Walk Through of Our Approach on an Industrial Strength Design .  | 66  |

| Chapt   | er 8 Related Work and Novelty of Our Approach                    | 83  |

| 8.1     | Hardware Pipelines and Their Verification                        | 83  |

| 8.2     | Software Pipelines and Their Verification                        | 85  |

| 8.3     | Verification of Behaviorally Synthesized Designs                 | 87  |

| 8.4     | Use of Theorem Provers in Hardware Verification                  |     |

| Chapt   | er 9 Conclusion and Future Work                                  | 90  |

| 9.1     | Summary                                                          | 90  |

| 9.2     | Next Steps                                                       |     |

| Referen | ces                                                              | 93  |

## LIST OF TABLES

7.1 Behaviorally synthesized pipelined designs tested using our algorithm 66

## LIST OF FIGURES

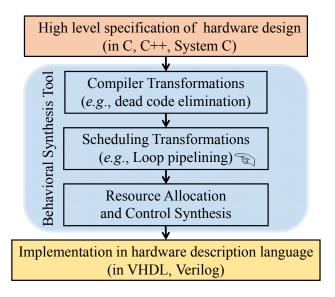

| 1.1          | Behavioral synthesis flow                                             | 2               |

|--------------|-----------------------------------------------------------------------|-----------------|

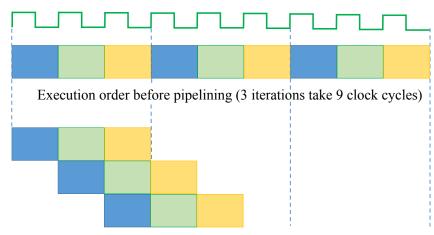

| 1.2          | Loop pipelining                                                       | 3               |

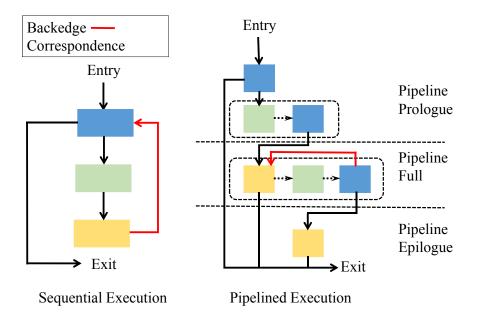

| 1.3          | Back-edge in sequential loop Vs back-edge in pipelined loop           | 5               |

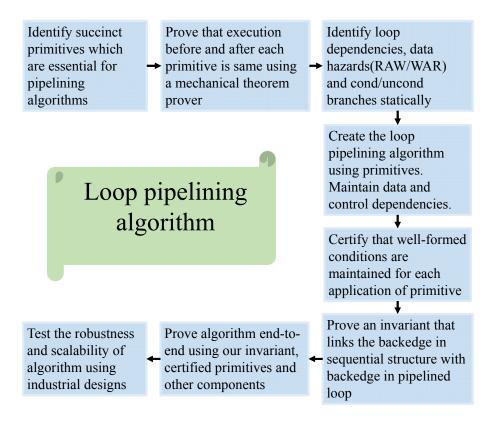

| 1.4          | Overview of our approach                                              | 7               |

| 2.1          | Certification model for behaviorally synthesized pipelines            | 11              |

| 2.2          | Certifying loop pipelining algorithm using SEC and theorem proving    | 14              |

| 3.1          | (a) Loop in C (b) Loop CCDFG before pipelining                        | 21              |

| 3.2          | Pipelining increases throughput                                       | 22              |

| 5.1          | Our framework of certified primitives                                 | 30              |

| 5.2          | Shadow register primitive                                             | 31              |

| 5.2          | Branch primitive                                                      | $\frac{31}{32}$ |

| 5.4          | Our loop pipelining algorithm (built using primitives)                | $\frac{32}{34}$ |

| $5.4 \\ 5.5$ | Sequential CCDFG with conditional branch                              | 35              |

| 5.6          | Sequential CCDFG with conditional branch. Note the addition           | 30              |

| 5.0          | •                                                                     | 26              |

| F 77         | of $S_{preExit}$ to explicitly define the control flow                | 36              |

| 5.7          | (a) Unrolling the loop once to separate the first iteration (b) After | 0.5             |

| <b>-</b> 0   | φ-removal transformation                                              | 37              |

| 5.8          | (a) Data propagation - first step (b) Data propagation - second step  | 39              |

| 5.9          | After shadow register                                                 | 41              |

| 5.10         | After superstep construction                                          | 42              |

| 5.11         | Final pipelined CCDFG                                                 | 43              |

| 6.1          | Correctness of $\phi$ -elimination primitive                          | 45              |

| 6.2          | Shadow register primitive                                             | 46              |

| 6.3          | Branch primitive                                                      | 48              |

| 6.4          | Superstep construction                                                | 49              |

| 6.5          | Invariant base case where $k = 1 \dots \dots \dots \dots$             | 51              |

| 6.6  | Invariant inductive step                                         | 52 |

|------|------------------------------------------------------------------|----|

| 6.7  | Correctness of invariant implies the correctness statement       | 53 |

| 6.8  | Proof sketch for remove branches stage                           | 58 |

| 6.9  | Proof sketch for $\phi$ -to-assign step                          | 59 |

| 6.10 | Proof sketch for Data Propagation Step Base Case                 | 61 |

| 6.11 | Proof sketch for data propagation step                           | 62 |

| 7.1  | TEA: C code                                                      | 66 |

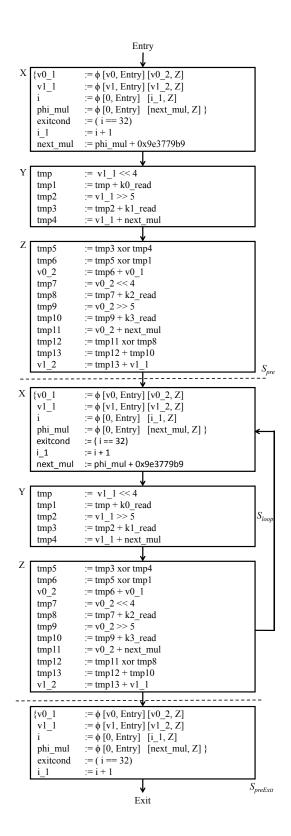

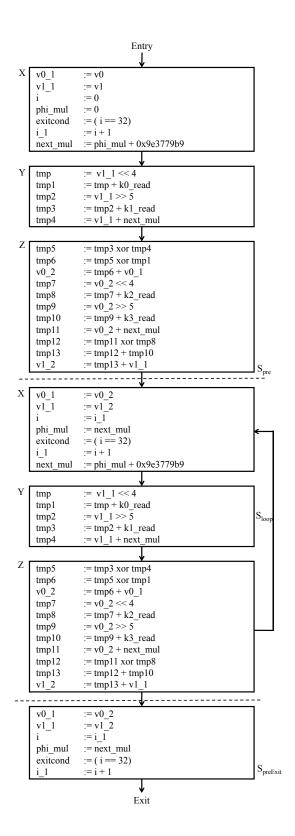

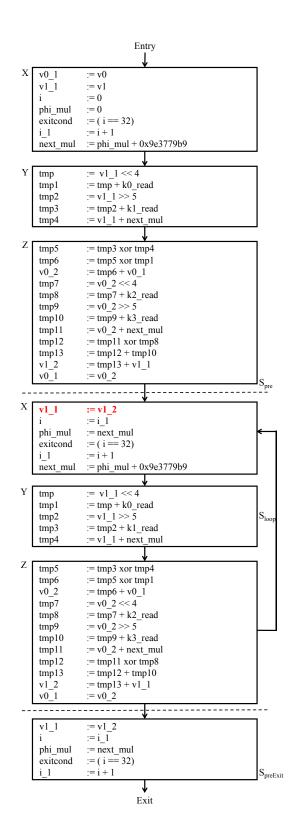

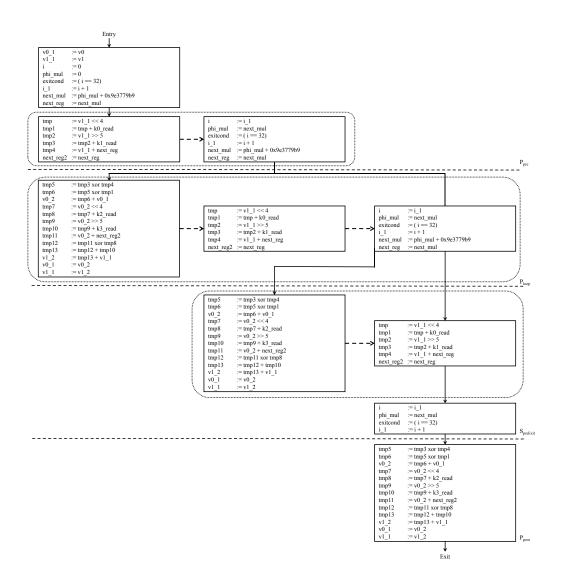

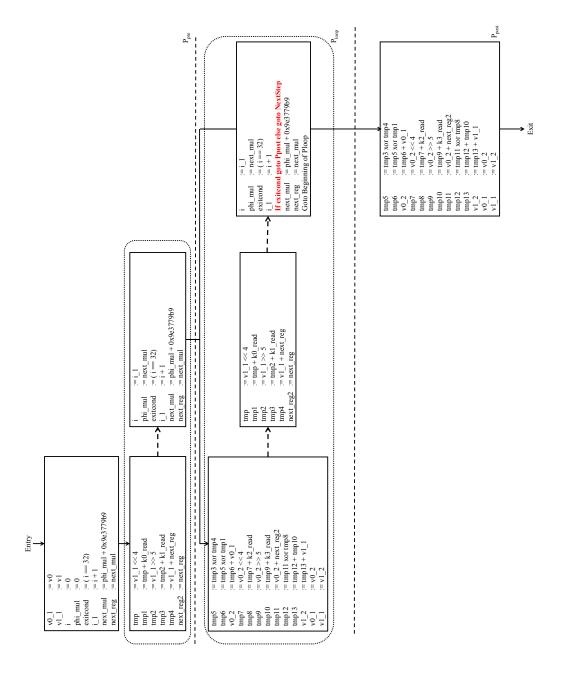

| 7.2  | TEA: Sequential loop CCDFG                                       | 68 |

| 7.3  | TEA: After removing branches                                     | 69 |

| 7.4  | TEA: After unrolling loop once                                   | 70 |

| 7.5  | TEA: After $\phi$ -removal                                       | 71 |

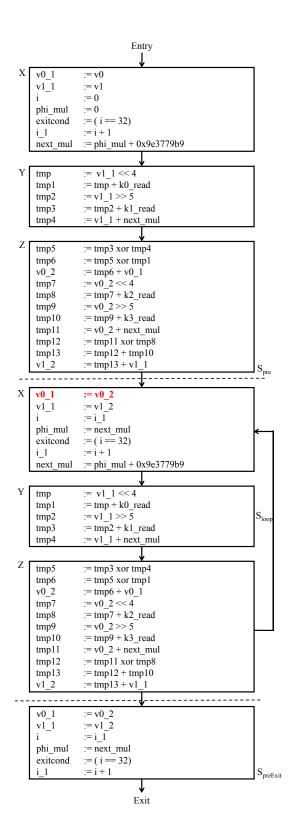

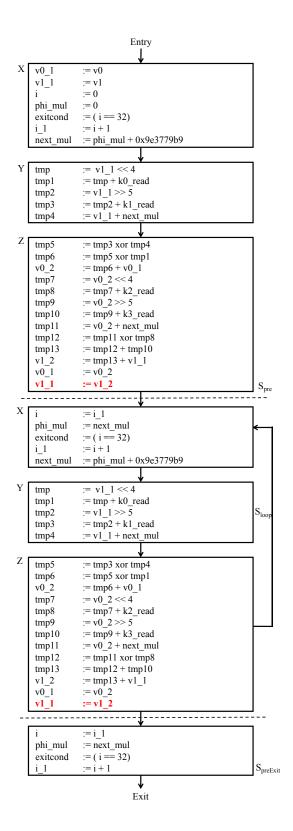

| 7.6  | TEA: After data propagation first step for $v0_{-}1 := v0_{-}2$  | 73 |

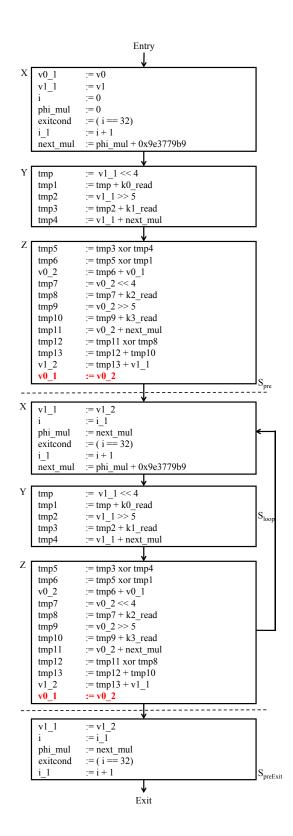

| 7.7  | TEA: After data propagation second step for $v0_{-}1 := v0_{-}2$ | 74 |

| 7.8  | TEA: After data propagation first step for $v1_{-}1 := v1_{-}2$  | 75 |

| 7.9  | TEA: After data propagation second step for $v1_{-}1 := v1_{-}2$ | 76 |

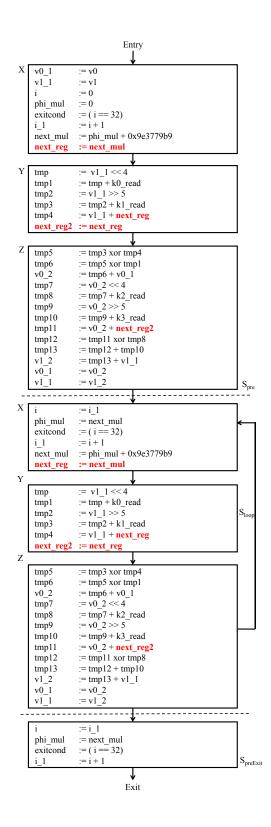

| 7.10 | TEA: After adding shadow registers                               | 78 |

| 7.11 | TEA: After superstep construction                                | 79 |

| 7.12 | TEA: After interchanging post with pre-exit                      | 80 |

| 7.13 | TEA: Pipelined CCDFG after adding branches back                  | 81 |

#### Chapter 1

#### INTRODUCTION

#### 1.1 DISSERTATION SUMMARY

Developing a certified loop pipelining algorithm is a complex problem. We have developed a certified loop pipelining algorithm for behavioral synthesis by proper application of theorem proving techniques. The result of this dissertation is a framework of certified pipelining primitives which are essential in developing any such pipelining algorithm. We systematically build a loop pipelining algorithm from ground up using these primitives and certify this algorithm using ACL2 theorem prover.

#### 1.2 MOTIVATION

Behavioral synthesis [15, 4] is the process of synthesizing an Electronic System-level (ESL) specification of a hardware design into a Register-Transfer Level (RTL) implementation. The idea of ESL is to raise the design abstraction by specifying the high-level, functional behavior of the hardware design. Designs are typically specified in a language such as C, C++, or SystemC. The approach is promising since the user is relieved of developing and optimizing low-level implementations. Studies have shown that ESL reduces the design effort by 50% or more while attaining excellent performance results [33]. It has recently received significant attention, as the steady increase in hardware complexity has made it increasingly

Figure 1.1: Behavioral synthesis flow

difficult to design high-quality designs through hand-crafted RTL under aggressive time-to-market schedules. A recent example is VP9 G2 hardware decoder IP developed by Google [2], which has been implemented primarily in standard C++ and synthesized to RTL logic for different target technologies and performance points using Calypto's Calatpult High Level Synthesis tool [8]. Nevertheless, and in spite of availability of several commercial behavioral synthesis tools [7, 48, 19], the adoption of the approach in main-stream hardware development for microprocessor and SoC design companies is dependent on designers' confidence that the synthesized RTL indeed corresponds to the ESL specification.

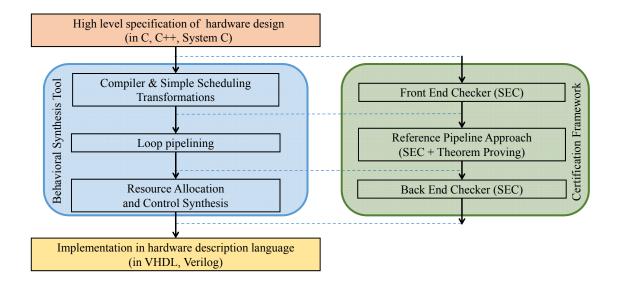

To satisfy the power and performance demands of modern applications, a behavioral synthesis tool applies hundreds of transformations. As shown in Figure 1.1, a typical behavioral synthesis flow can be roughly divided into three phases: compiler transformations; scheduling transformations; resource allocation and control synthesis. Commercial synthesis tools are highly complex software involving thousands to millions of lines of code; furthermore, they perform aggressive optimizations on the design being synthesized to satisfy constraints on power,

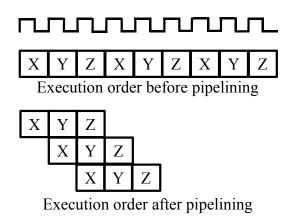

Execution order after pipelining (3 iterations take 5 clock cycles)

"Pipeline interval is 1"

Figure 1.2: Loop pipelining

performance, and area. Tools of such compelxity invariably contain subtle bugs, which undermine the very effectiveness of behavioral synthesis. Consequently, it is critical to develop a methodology for certifying synthesis transformations. Thus, it is critical to develop mechanized support for certifying the equivalence between ESL and RTL designs. However, the large difference in abstraction between the two representations makes such certification non-trivial.

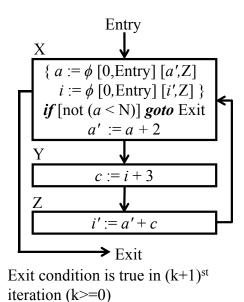

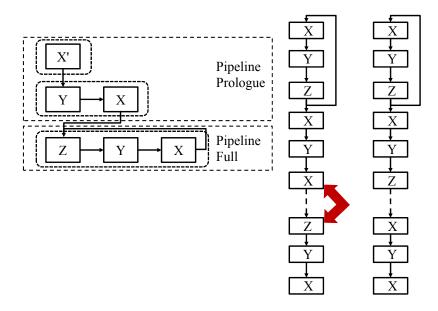

Loop pipelining is a critical transformation in behavioral synthesis. The goal of this transformation is to increase throughput and reduce latency of the synthesized hardware by allowing temporal overlap of successive loop iterations. As shown in Figure 1.2, the three iterations of overlapped pipeline structure takes only five clock cycles as opposed to nine clock cycles if executed sequentially. It is performed by most state-of-the-art synthesis tools [48, 19, 9].

Unfortunately, it is also highly complex [61] and error-prone, requiring subtle analysis of invariants to preclude data hazards arising from overlapping control/data flow of executions of successive loop iterations. Furthermore, certifying the result of this transformation is very difficult. In particular, the pipelined output

design from the transformation has a markedly different control/data flow structure from the sequential design that is input to the transformation; this makes it hard to find corresponding internal signals to serve as cutpoints, making it hard to compare them through Sequential Equivalence Checking (SEC). Another formal verification technique is theorem proving. However, applying theorem proving to certify the pipelining transformation is clearly cost-prohibitive given the complexity of the implementation; furthermore, most commercial transformation implementations are proprietary, making it infeasible to develop such a framework from a meth-dological perspective. As a result, hardware designers are vary of using current behavioral synthesis tools as they are often deemed either (a) aggressively optimized but error-prone or (b) reliable but overly conservative, thus often producing circuits of poor quality or performance [20, 40]. Therefore, ensuring correctness of behaviorally synthesized pipeline designs is a critical issue in bringing behavioral synthesis into practice.

An approach for certifying loop pipelining transformations using a combination of SEC and theorem proving techniques has been proposed by Hao et al. [24]. The most critical and complex component of their approach (c.f. Section 2.3) is developing a loop pipelining algorithm with two key properties: (1) it generates a reference pipeline model by exploiting pipeline generation information from the synthesis flow (e.g., the iteration interval of a generated pipeline) and the reference model can be compared with a pipelined RTL implementation using SEC effectively, and (2) it can be mechanically verified to correctly preserve the semantics of sequential (non-pipelined) specification of loop execution. Hao et al. showed viability of their approach by comparing pipeline generated from their algorithm with RTL implementation using SEC. However, their algorithm was not certified as well as incomplete as explained later in Section 2.3. Certification is a key component without which correctness of behavioral synthesis process for pipelined designs cannot be claimed. Therefore, this dissertation on developing a certified

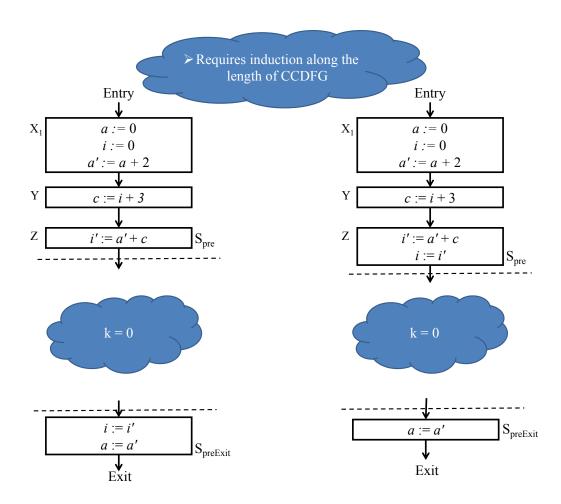

Figure 1.3: Back-edge in sequential loop Vs back-edge in pipelined loop

loop pipelining algorithm using our framework of certified primitives is important in facilitating formal verification of behaviorally synthesized pipeline designs.

#### 1.3 PROBLEM STATEMENT

Certifying an algorithm especially as complex as loop pipelining is not easy by any known conventional methods. To develop a certified loop pipelining algorithm in behavioral synthesis, we need to address the following key challenges brought about by the semantic gap between the sequential and pipelined designs.

- Formalizing an invariant that links loop in a sequential design with loop in the corresponding pipelined design. As shown in Figure 1.3, a sequential loop executes its iterations in sequence. The previous loop iteration is complete before the next iteration starts. A pipelined design, however, overlaps the consecutive iterations of a given design based on the pipeline interval. As a result, a loop in

the pipelined design executes statements from different iterations of the corresponding sequential loop design. Identifying a provable inductive invariant that links the backedge in the sequential loop with the backedge in the pipelined loop is, therefore, a major challenge.

- Identify and certify underlying primitives in a loop pipelining algorithm. Certifying a loop pipelining algorithm requires a complex invariant to prove that executing a sequential loop is equivalent to executing a pipelined loop. Identifying the pieces which would make this certification managable is a difficult task. We decompose the algorithm into certifiable primitives. We prove that if each primitive maintains an invariant that the execution of the intermediate representation before and after application of the primitive is same, we can prove that the algorithm also maintains the invariant. This approach, however, requires a crisp understanding of the essential steps involved in developing a pipeline loop from a sequential loop. We need to succinctly identify primitives which maintain the given invariant and are also certifiable by theorem proving. Each primitive would require a systematic approach for its proof.

- Identify and maintain control flow by proper placement of branches. Branch conditions dictate the control flow. Presence of conditional and unconditional branch instructions in a loop means that the loop is no longer executed in a straight line. At each application of primitive, we need to ensure that this control flow is not disturbed and is well accounted for.

- Certifying the complete loop pipelining algorithm based on certified primitives. Although, the primitives act as backbone for our algorithm, their certification alone does not automatically certify the entire algorithm. We need to identify the conditions under which a primitive is correct and make sure that every application of the primitive in the algorithm has the required assumptions.

Figure 1.4: Overview of our approach

#### 1.4 OVERVIEW OF OUR APPROACH

Our work shows that a certified loop pipelining algorithm can be developed by systematic application of theorem proving techniques.

We have basically divided our approach into eight broad steps as shown in Figure 1.4. The first two steps define our framework of certified primitives which we believe are essential for any certified pipelining algorithm. We have identified these primitives based on a realization that in order to generate a pipelined loop design from a sequential loop design, there are three broad steps: (1) identification and removal of data hazards, (2) overlapping the executions of subsequent iterations after the removal of data hazards, and (3) maintaining the correct control flow to preserve the exit condition and state at the time of exit from the loop. Our

primitives are such that they can be applied alone or in combination with other primitives to remove data hazards, reason about branches and to overlap iterations. We certify each primitive by proving that execution before and after each primitive is correct. Certification of each primitive requires separate careful reasoning in a mechanical theorem prover which we describe later in Chapter 6. We have defined the syntax and semantics of intermediate design representation in ACL2 [39, 55]. We have formalized and certified all of our primitives in ACL2 theorem prover.

The next six steps are for creating the certified loop pipelining algorithm using our framework of certified primitives. Certifying an application of a primitive in the context of the algorithm further involves ensuring that addition of any primitive does not alter the underlying assumptions in the syntax, for example, if we assume there are no return statements in a given representation, applying any primitive should also maintain that assumption. We use these primitives as a backbone to build our loop pipelining algorithm with distinct decomposable components one step at a time. Besides primitives, there are also additional components in the algorithm such as for identifying data hazards and for unrolling the loop. Each component satisfies the invariant that execution of intermediate representations before and after the component is same. We elaborate on our approach later in Chapter 5.

We have also identified a unique invariant which proves that executing overlapped iterations is equivalent to executing sequential iterations. It differs from a typical invariant used for correctness of pipelined systems in that it explicitly specifies the correspondence between the sequential and pipelined programs at each transition. We elaborate on our invariant in Chapter 6. We have proved that our algorithm satisfies this invariant.

We have certified the algorithm end-to-end which means that given a wellformed pipelinable loop (definition explained later in Chapter 5), we show that executing a sequential loop is equivalent to executing the pipelined loop created using our algorithm. We elaborate on the proof in our proof sketch in Chapter 6. Our proof sketch shows that our primitives are sufficient and essential and that we can build a complete certified loop pipelining algorithm from ground up using our framework.

The major **contributions** of our dissertation are:

- Identifying the key provable primitives essential in pipelining algorithms for behavioral synthesis and certifying these primitives in ACL2 theorem prover;

- Formalizing an invariant to link the sequential loop before pipelining with the pipelined loop;

- Developing our own executable loop pipelining algorithm in ACL2 using those

primitives and certifying this algorithm using ACL2 theorem prover;

- Testing our certified loop pipelining algorithm on varied designs

#### 1.5 OUTLINE

The remainder of this dissertation is organized as follows. Chapter 2 provides background on the overall project and explains the context of our theorem proving work. Chapter 3 discusses our formalization of the intermediate representations used in behavioral synthesis. We also discuss the correctness statement for loop pipelining algorithms. Chapter 4 discusses an earlier proposed algorithm and how and why we have chosen a different approach. Chapter 5 discusses our framework and a certified loop pipelining algorithm we have developed using the framework. Chapter 6 provides a proof sketch for our algorithm. Chapter 7 provides evaluation of robustness and scalability of our algorithm on various designs from different application domains. The related work is discussed in Chapter 8. We then conclude with the major contributions of this dissertation and future work in Chapter 9.

#### Chapter 2

#### BACKGROUND AND CONTEXT

In this Chapter, we discuss the overall project of verifying behaviorally synthesized designs, and how the certification of loop pipelining fits into this project. The reader interested in a thorough understanding of other components of the project is welcome to review the prior publications [52, 25].

#### 2.1 BEHAVIORAL SYNTHESIS

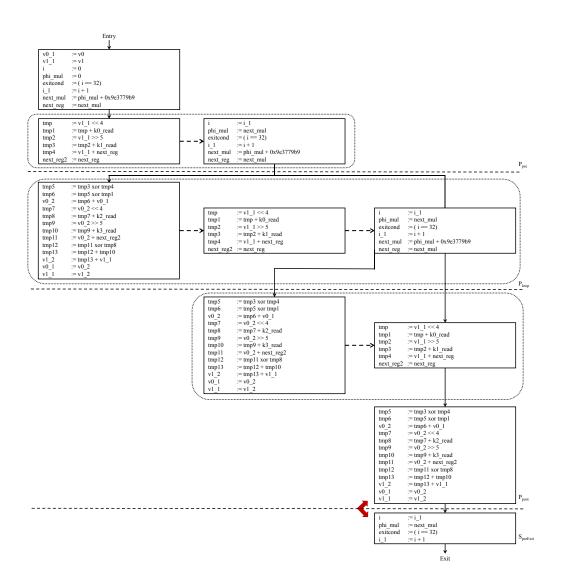

Behavioral synthesis [44] is an automated compilation process where a behavioral synthesis tool [20, 14, 9] takes an ESL description, together with a library of hardware resources. Analogous to a regular compiler, the tool performs the standard lexical and syntax analysis to generate an intermediate representation (IR). The IR is then subjected to a number of transformations which can be categorized into three phases as shown in Figure 2.1.

- Compiler Transformations: These include typical compiler operations, e.g., dead-code elimination, constant propagation, loop unrolling, common subexpression elimination etc. Furthermore, expensive operations (e.g., division) may be replaced with simpler ones (e.g., subtraction). A design may undergo hundreds of compiler transformations.

- Scheduling Transformations: Scheduling entails computing for each operation the clock cycle of its execution, accounting for hardware resource constraints and control/data dependencies. Loop pipelining, the focus of our dissertation, is a component of this phase.

Figure 2.1: Certification model for behaviorally synthesized pipelines

- Resource Allocation and Control Synthesis: This phase involves mapping a hardware resource to each operation (the "+" operation may be mapped to a hardware adder), allocating registers to variables, and generating a controlling finite-state machine to implement the schedule.

After the three phases above, the design can be expressed in RTL. The synthesized RTL may be subjected to further manual tweaks to optimize for area, power, etc. Each transformation is non-trivial. The end result is a hardware implementation which has a huge abstraction gap from the input ESL description.

# 2.2 OVERALL CERTIFICATION MODEL FOR BEHAVIORALLY SYNTHESIZED PIPELINES

The overall goal of the project is to provide a mechanized framework for certifying hardware designs synthesized from ESL specifications by commercial behavioral synthesis tools. One obvious approach is to apply standard verification techniques (SEC or theorem proving) on the synthesized RTL itself. Unfortunately, such a

methodology is not practical. As mentioned earlier, the large gap in abstraction between the ESL and RTL descriptions means that there is little correspondence in internal variables between the two. Consequently, direct SEC between the two reduces to cost-prohibitive computation of input-output equivalence. On the other side, applying theorem proving is also troublesome since extensive manual effort is necessary and this effort needs to be replicated for each different synthesized design. It is also infeasible to directly certify the implementation of the *synthesis tool* via theorem proving. In addition to being highly complex and thus potentially requiring prohibitive effort to formally verify with any theorem prover, the implementations are typically closed-source and closely guarded by EDA vendors and thus out of reach of external automated reasoning communities.

To address this problem, previous work developed two key SEC solutions, which we will refer to below as *Back-end* and *Front-end*. We then discuss the gap between them, which is being filled by theorem proving efforts in this dissertation. The certification model is illustrated in Figure 2.1.

Back-end SEC: The key insight behind back-end SEC is that automated SEC techniques, while ineffective for directly comparing synthesized RTL with the top-level ESL description, are actually suitable to compare the RTL with the intermediate representation (IR) generated by the tools after the high-level (compiler and scheduling) transformations have been applied. In particular, operation-to-resource mappings generated by the synthesis tool provide the requisite correspondence between internal variables of the IR and RTL. Furthermore, a key insight is that while the implementations of transformations are unavailable for commercial EDA tools, most tools provide these IRs after each transformation application together with some other auxiliary information. To exploit these, an SEC algorithm was developed between the IR (extracted from synthesis tool flow after these transformations) and RTL [52, 25, 26, 70]. The approach scales to tens of thousands of lines of synthesized RTL.

Front-end SEC: Of course the back-end SEC above is only meaningful if we can certify that the input ESL indeed corresponds to the extracted IR produced after the compiler and scheduling transformations applied in the first two phases of synthesis. To address this, another SEC technique was developed to compare two IRs [67, 69, 68]. The idea then is to obtain the sequence of intermediate representations  $IR_0, \ldots, IR_n$  generated by the compiler and scheduling transformations, and compare each pair of consecutive IRs with this new algorithm. Then back-end SEC can be used to compare  $IR_n$  with the synthesized RTL, completing the flow.

A Methodology Gap: Unfortunately, the front-end SEC algorithm can only compare two IRs that are structurally close. If a transformation significantly transforms the structure of an IR then the heuristics for detecting corresponding variables between the two IRs will not succeed, causing equivalence checking to fail. Loop pipelining falls in the category of transformations that significantly change the structure of the IR. It is a quintessential transformation that changes the control/data flow and introduces additional control structures (to eliminate hazards). This makes front-end SEC infeasible for its certification. Furthermore, most commercial implementations are of course proprietary and consequently not available to us for review; applying theorem proving on those implementations is not viable from a methodology perspective. Thus a specialized approach is warranted for handling its certification.

#### 2.3 A REFERENCE PIPELINE APPROACH

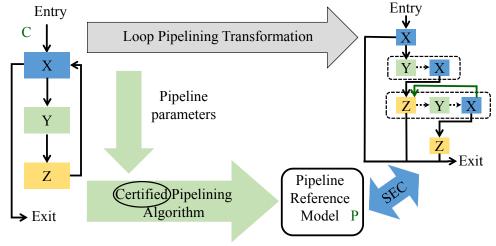

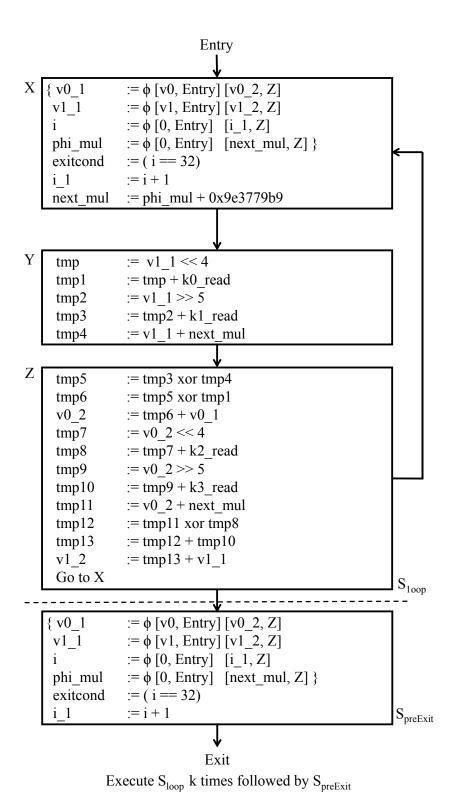

To develop a specialized approach for pipelines, a key observation is that while the transformation *implementation* is inaccessible to us, commercial synthesis tools typically generates a report specifying pipeline parameters (pipeline interval, number of loop iterations pipelined, etc.). The approach (c.f. Figure 2.2) then is to develop an algorithm that takes as inputs these parameters and an IR  $\mathcal{C}$  for the

- 1. Create a correct pipeline reference model

- 2. Compare using sequential equivalence checking (SEC)

Figure 2.2: Certifying loop pipelining algorithm using SEC and theorem proving

design before pipelining, and generates a reference pipelined IR  $\mathcal{P}$ . Note that this algorithm would be much simpler than that employed during synthesis; while the former includes advanced heuristics to compute pipeline parameters (like pipeline interval, number of iterations pipelined etc.), this algorithm would merely use the values provided by its report. To certify a synthesized RTL with pipelines, it is sufficient to (1) check that the given algorithm can generate a pipeline  $\mathcal{P}$  for the parameters reported by synthesis, (2) use SEC to compare  $\mathcal{P}$  with the synthesized RTL, and (3) prove (using theorem proving) the correctness of this algorithm.

A previous work [24] justified the viability of steps 1 and 2 above; such a reference pipeline generation algorithm was developed and used to successfully compare a variety of pipelined designs across various application domains. This suggested that the approach of using a reference implementation is viable for certifying varied behaviorally synthesized pipelines. However, a key (and perhaps the most complicated) component of the approach was missing. The algorithm was not verified (indeed, not implemented in a formal language), rendering the "certification" flow

unsound.

The unsoundness mentioned above is not just an academic notion. The approach showed no systematic approach for creating the reference pipeline generation algorithm. In fact, the specific reference algorithm developed was in fact heavily influenced by the synthesis tool under consideration (AutoESL), and highly complex. In fact, merely by going through the formalization process and thinking about necessary invariants, we have already found a bug in the implementation of the algorithm. Thus it is critical to develop a mechanized proof of correctness for this implementation. Unfortunately, it is not easy to verify the original pipeline generation algorithm as written. Its author was an expert in behavioral synthesis but not in program verification or theorem proving; consequently, the algorithm, while simpler than the one implemented in a synthesis tool, was still a highly complex piece of code. In particular, since it was not written with correctness certification in mind, it is difficult to decompose the algorithm into manageable pieces with succint invariants. One way to address this problem is to "buckle down" and verify the pipeline generation algorithm (and fixing the bugs found in the process). However, a key insight in our case is that we can get away without verifying such a complex implementation. After all, there is nothing "sacred" about this specific algorithm for pipeline generation: given the steps described above, any verifiable pipeline generation algorithm would suffice.<sup>1</sup>

Thus the approach of our dissertation can be viewed as systematic approach to write a loop pipelining algorithm which is amenable to mechanical theorem proving. We identify the key invariant that we need to maintain for proving computational equivalence between the pipelined and un-pipelined loops and design an algorithm to explicitly maintain that invariant.

$<sup>^{1}</sup>$ Note that our algorithm must create a pipeline in accordance with the pipeline parameters obtained from the behavioral synthesis tools; otherwise we may fail to certify correct designs. However, in practice, we have not found this to be a problem.

#### Chapter 3

#### FORMALIZATION

#### 3.1 INTERMEDIATE REPRESENTATION: CCDFG

In order to formalize and prove the correspondence between pipelined and unpipelined IRs, a first step is to define a formalization of the IRs themselves. We call our formalization of IRs Clocked Control Data Flow Graph (CCDFG). An informal description of CCDFG has been provided before [52]. It can be best viewed as a traditional control/data flow graph used by most compilers, augmented with a schedule. Control flow is broken into basic blocks. Instructions are grouped into microsteps which can be executed concurrently. A scheduling step is a group of microsteps which can be executed in a single clock cycle. The state of a CCDFG at a particular microstep is a list of all the variables of a CCDFG with their corresponding values.

The semantics of CCDFG require a formalization of the underlying language used to represent the individual instructions in each scheduling step. The underlying language we use is the LLVM [36]. It is a popular compiler infrastructure for many behavioral synthesis tools [14, 9] and includes an assembly language frontend. We currently support only a subset of LLVM operations which are required to handle all the designs we have seen. Instructions supported include assignment, load, store, bounded arithmetic, bit vectors, arrays, and pointer manipulation instructions. Note that the reasoning involved in creating a pipelined CCDFG does not involve the exact syntax of any operation. We are merely concerned with a way to find the variables which are read and written at each step. Increasing

the operations database in our algorithm is expected to increase the time taken to prove certain primitives as much more analysis needs to be done. However, it would not affect the logical reasoning of the primitives, the overall algorithm and the proof. We define the syntax of each type of statement by defining an ACL2 predicate. For example, in our syntax, an assignment statement can be expressed as a list of a variable and an expression.

An expression can further be of multiple types, load expression (loading the value of a variable from memory), add expression (addition of two variables), xor expression (xor of two variables) etc., where each expression includes the operation applied to the appropriate number of arguments.

We provide semantics to these instructions through a state-based operational formalization as is common with ACL2 [45]. We define the notion of a CCDFG state, which includes the states of the variables, memory, pointers, etc. Then we define the semantics of each instruction by specifying how it changes the state. Thus, for an assignment statement we will have a function execute-assignment that specifies the effect of executing the assignment statement on a CCDFG state.

```

(defun expression-p (x)

(and (consp x)

(or (load-expression-p x)

(add-expression-p x)

(xor-expression-p x)...)))

```

Defining the semantics of most supported statements is straightforward, with one exception. The exception is the so-called " $\phi$ -construct" available in LLVM [1]. A  $\phi$ -construct is a list of  $\phi$ -statements. A  $\phi$ -statement is  $v := \phi[\sigma, bb1][\tau, bb2]$ , where v is a variable,  $\sigma$  and  $\tau$  are expressions, and bb1 and bb2 are basic blocks: if it is reached from bb1 then it is the same as the assignment statement  $v := \sigma$ ; if reached from bb2, it is the same as  $v := \tau$ ; the meaning is undefined otherwise. The construct is complex since the effect of executing this statement on a CCDFG state s depends not only on the state s but also on how s is reached by the control flow.  $\phi$ -statements are inevitable in loop designs — they are used to evaluate the value of loop carried dependencies. Consequently, the complexity induced by this instruction cannot be avoided.

Here phi-1 recognizes an expression of the form ((E0 b) (E1 b-prime)) where E0 and E1 are expressions and b and b-prime are symbols representing

basic blocks. Thus in ACL2, the  $\phi$ -statement looks like (v (phi ((E0 b) (E1 b-prime)))). Finally, the execution semantics requires the additional parameter prev-bb to track the previous basic block.

```

(defun choose (choices prev-bb)

(if (or (equal (nth 1 (first choices)) prev-bb)

(equal (symbol-name (nth 1 (first choices))) prev-bb))

(nth 0 (first choices))

(nth 0 (second choices))))

(defun evaluate-val (val bindings)

(if (symbolp val)

(cdr (assoc-equal val bindings))

val))

(defun execute-phi (stmt init-state prev-bb)

(let* ((expr (cdr stmt))

(var (first stmt))

(val (evaluate-val (choose (cdr (car expr)) prev-bb)

(car init-state))))

(list (replace-var var val (variables-of init-state))

(memory-of init-state)

(pointers-of init-state))))

```

The *init-state* represents the state of a CCDFG before executing  $\phi$ -statement. The function variables-of is used to get a list of all the variables of init-state with their corresponding values. replace-var replaces the values of the variable var to val in the list of those variables.

#### 3.2 CORRECTNESS OF LOOP PIPELINING

For the purposes of this dissertation, a *pipelinable loop* is a loop with the following restrictions [24]:

- 1. no nested loop;

- 2. only one Entry and one Exit block; and

- 3. no branching between the scheduling steps.

A well-formed pipelinable loop is expected to have only one conditional branch and one unconditional branch. Unconditional branch is at the end of the loop dictating the back edge which enforces that the loop CCDFG is executed again from the first step. Conditional branch ensures that depending on the current value of the exit condition variable, a loop can exit if required. Other intermediate branches have already been handled by compiler and scheduling transformations prior to the pipelining transformation so we need not consider them in our reasoning. There is one  $\phi$ -construct in the first scheduling step which handles the value assigned to loop carried variables depending on whether we are entering loop for the first time or not.

These restrictions are not just meant to simplify the problem, but reflect the kind of loops that can be actually pipelined during behavioral synthesis. For instance, synthesis tools typically require inner loops to have been fully unrolled (perhaps by a previous compiler transformation) in order to pipeline the outer loop.

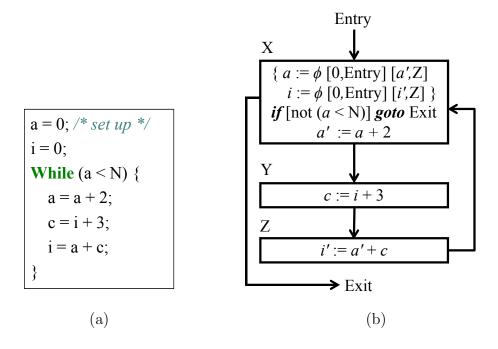

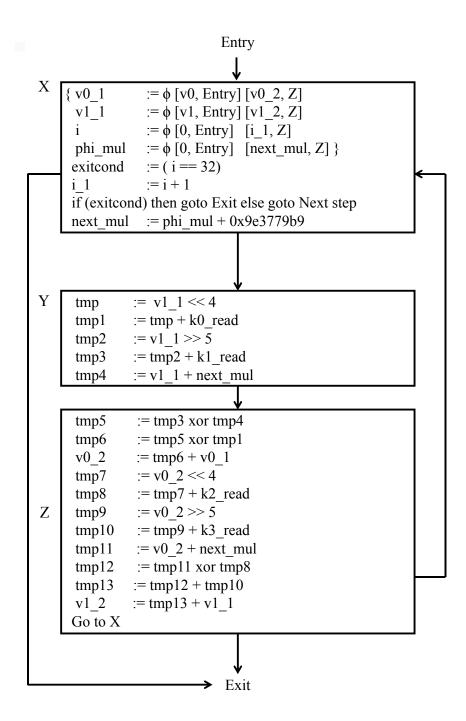

Figure 3.1: (a) Loop in C (b) Loop CCDFG before pipelining

Figure 3.1(a) illustrates the C code (ESL description) for a loop. The C code does not have a schedule or the concept of a clock cycle. Figure 3.1(b) shows CCDFG of the sequential loop just before loop pipelining. The loop has three scheduling steps: X, Y and Z. The scheduling step before the loop is Entry and after the loop is Exit. The edges in the CCDFG indicate the control flow. Note that the sequential CCDFG has Static Single Assignment (SSA) structure, as a result variable a and i are not assigned more than once and we require the quoted variables a' and i'. Note that there is a  $\phi$ -statement in the first scheduling step of the loop. This  $\phi$ -statement accounts for those variables whose values are dependent on the variables evaluated in a previous iteration.

Behavioral synthesis tools use complicated heuristics and aggressive scheduling strategies to find an optimized pipeline interval (clock cycles after which a new iteration can be started such that there are no data hazards). One iteration of the sequential design takes three clock cycles. Observe in Figure 3.2 that with the

Figure 3.2: Pipelining increases throughput

pipeline interval of one, the three iterations of the pipelined loop take five clock cycles as opposed to nine clock cycles in the sequential loop. Loop pipelining reduces the number of clock cycles required to execute the loop, hence this transformation is used by synthesis tools to increase throughput and reduce overall latency.

The main lemma involved in the correspondence proof between the sequential and pipelined CCDFG can be paraphrased in English as follows.

If the pipeline generation succeeds without error, executing the pipelined CCDFG loop for k iterations generates the same state of the relevant variables as executing the sequential CCDFG for some k' iterations. The explicit value of k' is given by the term (+ (- k 1) (ceil m pp-interval)).

The theorem can be stated in ACL2 as follows.<sup>1</sup>

(defthm correctness-statement-key-lemma

<sup>&</sup>lt;sup>1</sup>The theorem mentioned in the paper does not contain all the hypotheses. Please refer to our proof scripts for final form of this theorem.

The theorem involves several ACL2 functions, e.g., get-real, superstep-construction, etc. For details, one can refer to our proof-scripts. We provide a brief, informal description of some of the critical functions in the theorem. Two key functions that appear in the theorem above are superstep-construction and run-ccdfg.

The function run-ccdfg runs a CCDFG including a pipelinable loop in three parts, first the prologue before the loop, next the loop itself, and finally the epilogue past the loop.<sup>2</sup>

This function is defined as follows, where prefix determines the previous scheduling step of the iteration (required to resolve  $\phi$ -statements).

```

(defun run-ccdfg (pre loop post iterations init-state prev)

(let* ((state1 (run-block-set pre init-state nil prev))

```

<sup>&</sup>lt;sup>2</sup>Of course one can have the standard function run that executes the entire CCDFG rather than in parts. However, for reasons that will be clear when we define the invariant, in our case it is easier to do most of the work with the execution in three parts and then assemble them into a final theorem about the CCDFG run in the end.

The function superstep-construction combines the scheduling steps of successive iterations to create the "scheduling supersteps" of pipelined CCDFG. If there are data-hazards and pipelined CCDFG cannot be generated as per the ppinterval given, the function generates an "error".

Finally, the function get-real removes from the pipelined CCDFG state, all auxiliary variables introduced by the pipeline generation algorithm itself, leaving only the variables that correspond to the sequential CCDFG,<sup>3</sup> and in-order normalizes "sorts" the components in a CCDFG state in a normal form so that the sequential and pipelined CCDFG states can be compared with equal.

<sup>&</sup>lt;sup>3</sup>The algorithm has to introduce new variables in order to eliminate hazards. One consequence of this is that the new variables so introduced must not conflict with any variable subsequently used in the CCDFG. Since we do not have a way to ensure generation of fresh variables, this constraint has to be imposed in the hypothesis.

### Chapter 4

#### RESEARCH CHALLENGES

# 4.1 IMPORTANCE OF USING FORMAL METHODS FOR CHECK-ING CORRECTNESS

Formally certifying an algorithm gives confidence that the pipelined design is indeed correct. We can claim that if a pipeline loop is created, then there are no additional data hazards which have not been accounted for. Also, since our final theorem proves that executing a sequential loop is same as executing the pipelined loop generated from our algorithm, we can confidently say that our algorithm is complete and data and control flows are well-maintained.

Note that our framework is independent of the inner workings of a specific tool, and can be applied to certify designs synthesized by different tools from a broad class of ESL descriptions. Also, the approach produces a certified reference flow, which makes explicit generic invariants that must be preserved by different transformations.

## 4.2 CHALLENGES ASSOCIATED WITH FORMAL REASONING

To understand the complexities involved in mechanical certification of an algorithm through interactive theorem proving that was not designed originally with certification in mind, we need to re-visit the general approach to applying formal reasoning on software programs. The typical approach is to break the program into a number of pieces, prove key lemmas characterizing the role of each piece,

and then chain these lemmas together into a proof of the correctness of the entire program. Crucial to this approach, however, is the requirement that each program piece can be characterized by a succinct invariant that can be easily verified. However, in a program not developed with theorem proving certification in mind, optimizations typically destroy the structural disciplines and modularity of the individual program pieces. This makes it difficult to identify and isolate the components that actually maintain succinct, interesting invariants.

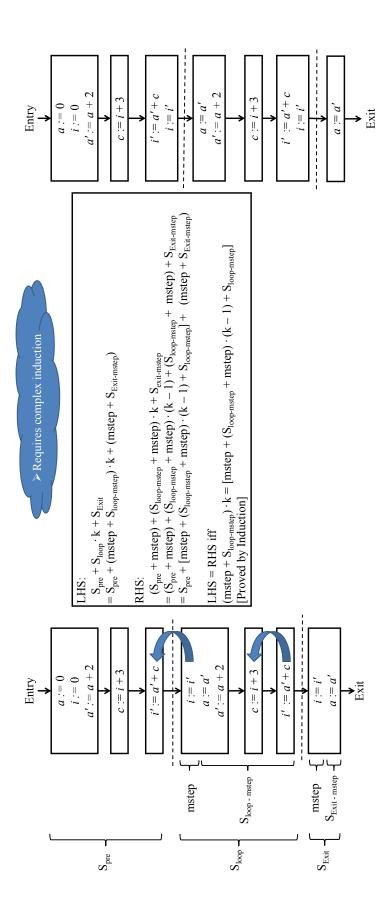

### 4.3 COMPARISON WITH PREVIOUS ALGORITHM

The previous algorithm is composed of four concrete steps: generate scheduling steps, add shadow register, add edges and data propagation. To prove the correctness statement in the previous algorithm, we want to prove that the complete algorithm follows the invariant that the execution of input CCDFG is equal to execution of the output CCDFG. We intuitively expect the individual steps or at least a combination of steps in sequence to follow this invariant. However, since the algorithm has not been designed keeping theorem proving in mind, that is not the case. For example, if we consider the first step of the proposed algorithm "generating new scheduling steps" by overlapping executions of an unrolled loop, we know that the execution of the sequential scheduling steps is not the same as the execution of new scheduling steps unless we prove that there are no data hazards. But, data hazards are not completely eliminated till the last step of the algorithm. Note, that the complete algorithm does follow the invariant as expected, but reasoning about the structure of the complete algorithm at once is not easy.

Our first approach was to certify their implementation as it is using theorem proving. But, our experience was that it is a difficult approach, one that we need not endure. In general, in order to certify such an arbitrary implementation, one has to either (1) restructure the implementation into one that is more disciplined,

and prove the equivalence between the two, or (2) come up with very complex invariants that essentially comprehend how invariants from each individual piece are conflated together in the implementation. Both approaches require extensive human interaction, resulting in the proverbial euphemism of proofs of programs being orders of magnitude more complex than the programs themselves [45].

In our work, however, we can "get away" without verifying the specific implementation while still being able to certify the design generated by behavioral synthesis without loss of fidelity. The key observation, as above, is that it is sufficient to develop *any* certifiable algorithm that generates a pipelined CCDFG from a sequential implementation which can be effectively applied with SEC. In particular, any certifiable algorithm that has the same input-output characteristic as the proposed algorithm is sufficient.

Checking correctness using formal methods prompted us to address the issues lacking in the previous algorithm. To ensure that control flow is maintained, we had to deal with branches. The previous algorithm introduces the concept of Exit edges but does not explain/implement them. The previous authors checked the output of their algorithm with RTL under the assumption that the loop never exits, hence they did not face any issue while testing. However, removing a conditional branch in a loop and furthermore, adding the conditional branch back in the middle of a pipelined loop requires complex reasoning which we manage using one of our primitives, explained in Chapter 5.

Also, the invariant that data flow is maintained at each step enabled us to find a bug in the previous algorithm. The previous algorithm moves a statement to make sure one particular data hazard is removed, but in doing so they move the statement across a conditional branch statement. Our primitves ensure that such a move is not possible. We have restructed the data propagation step so that instead of going across a conditional branch in the same iteration, the movement of step is now to the previous iteration, explained in Chapter 5.

Thus, our dissertation is on identifying certifiable primitives and invariants of a loop pipelining transformation and developing a pipeline generation algorithm using those primitives, achieving the dual goal of mechanical reasoning of the algorithm and amenability of the resulting reference model to SEC.

### Chapter 5

#### OUR APPROACH

As mentined earlier, one of the most complex requirements of verifying behaviorally synthesized pipelined designs is a certified loop pipelining algorithm which can generate a pipeline reference model for varied designs. This pipeline reference model must have a similar structure to the pipelined RTL generated by behavioral synthesis tools such that they can be compared using SEC.

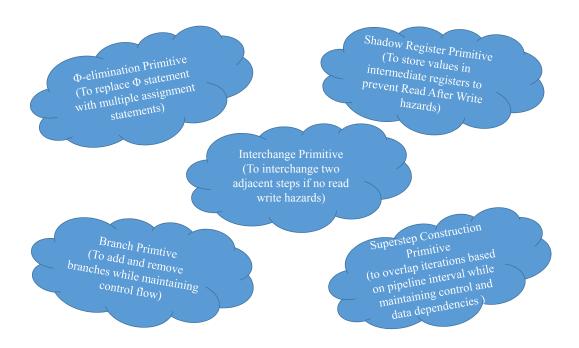

Pipeline synthesis is based on the key observation that execution of successive iterations can be overlapped without affecting execution as long as data and control dependecies are correctly maintained. Thus, the three main activities of a pipeline synthesis algorithm are to (1) identify and remove possible hazards (2) overlap the successive iterations according to the pipeline interval, and (3) ensure proper placement of conditional and unconditional branches. In our case, the identification of data hazards is simplified since the synthesis tool provides a pipeline interval. If we can use this pipeline interval to build our design, then the pipeline reference model is comparable to RTL in abstraction. Thus, instead of discovering a pipeline interval ourselves by analyzing read and write variables of every design so that no hazard is introduced, we reuse the provided interval. We have developed a framework of five certified pipelining primitives which allows us, among other things, to prevent possible data hazards. Our framework also provides a primitive to overlap successive iterations and a provision to add and remove branches when required while still maintaining the control flow. We now discuss the framework as shown in Figure 5.1 in detail.

Figure 5.1: Our framework of certified primitives

### 5.1 FRAMEWORK OF PROVABLE PIPELINING PRIMITIVES

We believe that the following primitives are necessary and essential in creating any pipelining algorithm in behavioral synthesis.

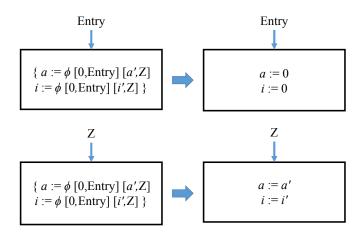

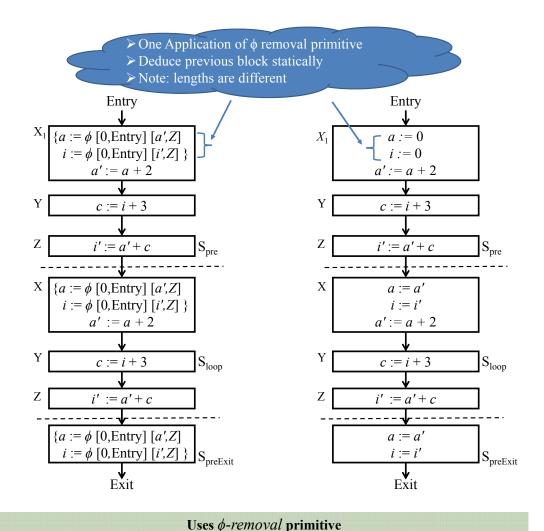

$\phi$ -elimination primitive – A  $\phi$ -statement is "v = phi [ $\sigma$  X] [ $\tau$  Y]", where v is a variable,  $\sigma$  and  $\tau$  are expressions, and X and Y are basic blocks: while execution, if the  $\phi$ -statement is reached from X then it is the same as the assignment statement v =  $\sigma$ ; if reached from Y, it is the same as v =  $\tau$ ; the meaning is undefined otherwise. Reasoning about the  $\phi$ -statement is complex since after its execution from a state, say s, the state reached depends not only on the state s but also on previous basic blocks in the execution history. However, we must handle it since it is used extensively in loops to perform different actions depending on whether the loop body is executed the first time. One of the key steps in loop pipelining is, therefore,  $\phi$ -elimination i.e., replacing  $\phi$ -statement with appropriate assignment statements when the previous basic block is explicitly known.

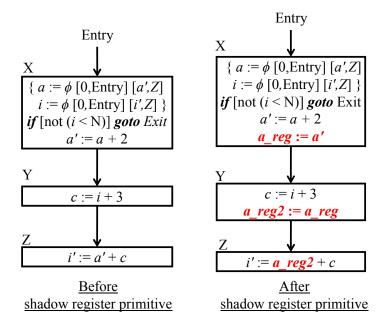

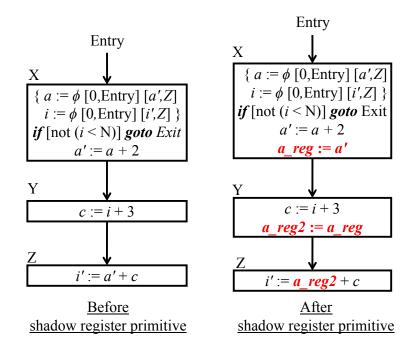

Figure 5.2: Shadow register primitive

Shadow register primitive – We define a shadow register microstep as simply an assignment statement with symbol expression (x) assigned to a new value  $(x\_reg)$ . We call all the new introduced variables as shadow registers. Intuitively, it is correct that in a sequence of steps, if we assign a variable to a shadow register and replace all occurences of x with  $x\_reg$  till the next write of x, we should not have made any difference in the execution. Also, since we are not changing the value of x itself, the state after end of execution for both CCDFGs as far as real variables are concerned (all variables excluding all shadow registers) is same. In Figure 5.2, if we assign a shadow register  $a\_reg$  value of a' at the end of X block, shadow register  $a\_reg2$  value of  $a\_reg$  in Y and replace the read occurence of a' in Z with  $a\_reg2$ , the sequential execution remains same. But, because of the addition of these shadow registers, the value of a' is stored in a new temporary variable in every new scheduling step which prevents data hazards.

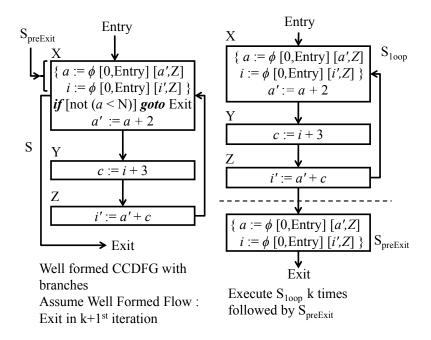

Figure 5.3: Branch primitive

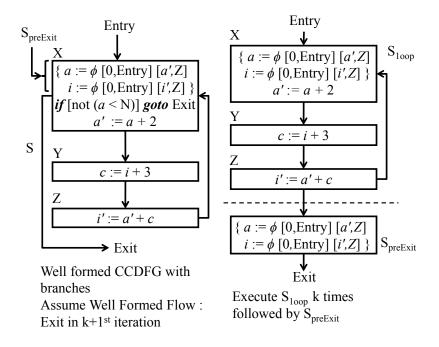

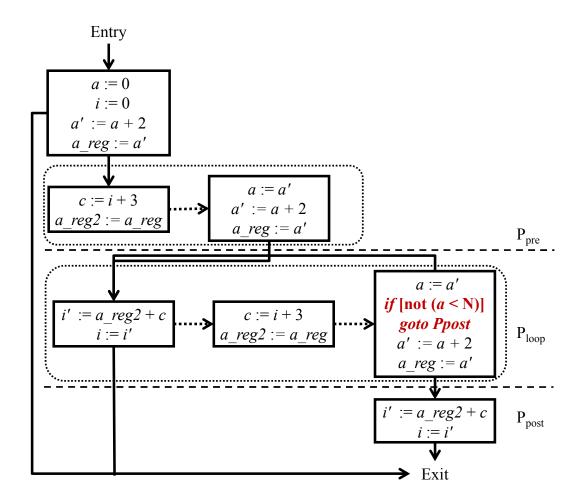

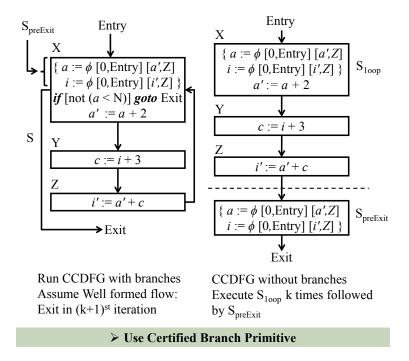

Branch primitive – Branch instructions are required to determine the control flow. However, reasoning about execution of branch instructions in a loop everytime we apply a primitive can make proof very complex. We note that if we specifically assume that the exit condition becomes true after completing k iterations, then we can remove the conditional branch. To understand the branch primitive (c.f. Figure 5.3), let's assume there is a conditional branch in the sequential loop structure S, which points to either the next microstep in sequence or exits the loop by branching to the scheduling step Exit. Let  $S_{preExit}$  be the collection of microsteps before this branch in S and let  $S_{loop}$  be the corresponding CCDFG loop without the conditional branch. The conditional branch primitive allows us to replace S with  $S_{loop}$  followed by  $S_{preExit}$ . Similarly, the primitive also allows us to introduce an exit conditional branch by replacing  $S_{loop}$  followed by  $S_{preExit}$  with S. Note that since k can take any value  $k \geq 0$ , we are not compromising on the correctness statement. It can be proved that executing S k times such that it exits

in the (k+1) st iteration is same as executing  $S_{loop}$  k times followed by  $S_{preExit}$ .

Interchange primitive – Let m and n be two adjacent scheduling steps (or in general, any collection of microsteps) in a CCDFG where both m and n do not have any microsteps containing branch statements. Also, there are no read write hazards between m and n. By read write hazards, we mean that m does not read or write any variable which is written in n and vice versa. Then, the interchange primitive allows us to interchange the order of m and n in the given CCDFG. Note that under the given assumptions, if initial state is the same, then the state reached after executing m followed by m is same as the state reached after executing n followed by m.

Superstep construction primitive – This operation entails combining the scheduling steps of the successive iterations, forming scheduling "supersteps" that act as scheduling steps for the pipelined implementation. Supersteps must account for read-after-write hazards, i.e, if a variable is written in a scheduling step X and read subsequently in Z then Z cannot be in a superstep that precedes X in the control/data flow. Note that we implement data forwarding (forward value of data within a single clock cycle); thus X and Z can be in a single superstep.

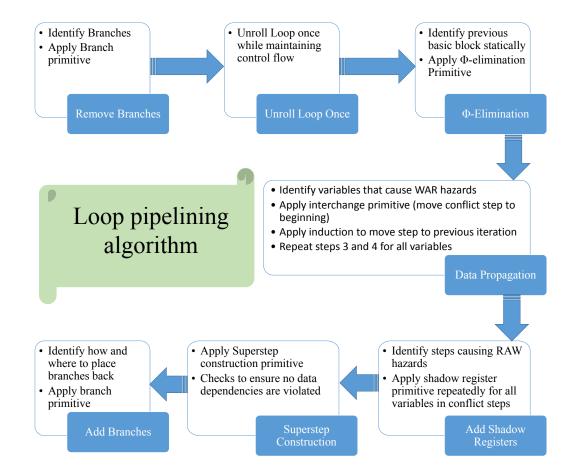

### 5.2 OUR LOOP PIPELINING ALGORITHM

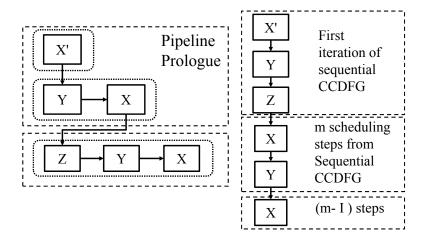

Given a sequential loop S in CCDFG C and pipeline interval I, we can create a pipelined loop P using Algorithm 1. Note that every step of the algorithm is built from ground up using our framework of provable primitives such that the algorithm can be certified by theorem proving. A quick overview of primitives used in the algorithm at each step are shown in Figure 5.4.

Figure 5.4: Our loop pipelining algorithm (built using primitives)

# Algorithm 1 Pipelining algorithm

- 1: procedure PipelineLoop(S, I)

- 2:  $S_1 \leftarrow RemoveBranches(S)$

- 3:  $S_2 \leftarrow UnrollLoopOnce(S_1)$

- 4:  $S_3 \leftarrow \phi Elimination(S_2)$ .

- 5:  $S_4 \leftarrow DataPropagation(S_3, I)$ .

- 6:  $S_5 \leftarrow GenerateShadowRegisters(S_4, I)$ .

- 7:  $S_6 \leftarrow SuperstepConstruction(S_5, I)$ .

- 8:  $P \leftarrow AddBranches(S_6)$

- 9:  $\mathbf{return}(P)$ .

- 10: end procedure

Now, we describe the steps to convert a sequential loop CCDFG (c.f. Figure 5.5) to a pipelined loop CCDFG in detail:

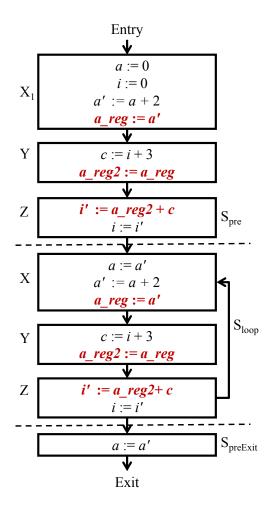

Figure 5.5: Sequential CCDFG with conditional branch

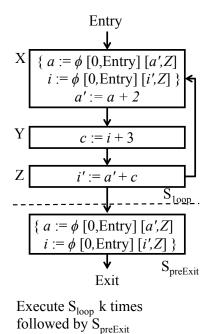

Remove Branches: We apply the branch primitive on S (c.f. Figure 5.5) to remove the conditional and unconditional branch by explicitly defining the control flow in S. The output is a sequence of two CCDFG's  $S_{loop}$  and  $S_{preExit}$  connected through an edge as shown in Figure 5.6. Note, that  $S_{loop}$  does not contain the conditional branch originally present in S. Executing S such that S exits in the (k+1)st iteration is same as executing  $S_{loop}$  k times followed by  $S_{preExit}$ . This is possible because the input CCDFG has only one conditional and one unconditional branch as per our definition of pipelinable well formed CCDFG's.

Figure 5.6: Sequential CCDFG without conditional branch. Note the addition of  $S_{preExit}$  to explicitly define the control flow

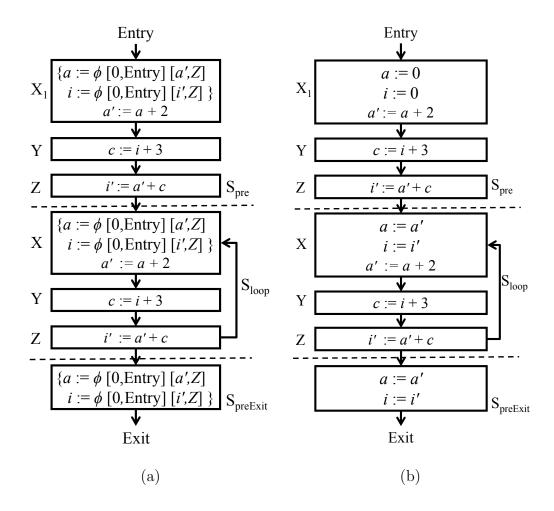

Unroll Loop Once: We have already established that the first iteration behaves differently than the rest of the iterations due to  $\phi$ -construct. So, in this particular step, we simply unroll the loop  $S_{loop}$  once. This step does not use any primitive. It is an intuitively correct step, although we also formally verify it using induction in the final proof. We call the first iteration  $S_{pre}$  as shown in Figure 5.7(a).

Figure 5.7: (a) Unrolling the loop once to separate the first iteration (b) After  $\phi$ -removal transformation

$\phi$ -elimination: We apply the  $\phi$ -elimination primitive on  $S_{pre}$ ,  $S_{loop}$  and  $S_{preExit}$  to return a CCDFG in which all the  $\phi$ -statements have been replaced with their corresponding assignment statements. Figure 5.7(b) shows the CCDFG after applying the  $\phi$ -elimination primitive. Note that  $\phi$ -construct is only in the first scheduling step of any iteration, so the remaining scheduling steps are the same in all the iterations.

**Data propagation:** Algorithm 2 describes how to compute candidates for data propagation across pipeline iterations. It is a critical step in removing data

## **Algorithm 2** Data propagation

```

1: procedure DataPropogration(L)

2:

msteps \leftarrow GetLoopCarriedDependencies(L)

3:

for each mstep in msteps do

if CheckConflict(L, mstep, N, I) \neq 0 then

4:

L \leftarrow RelocateMStep(L, mstep)

5:

end if

6:

7:

end for

8:

return (L)

9: end procedure

```

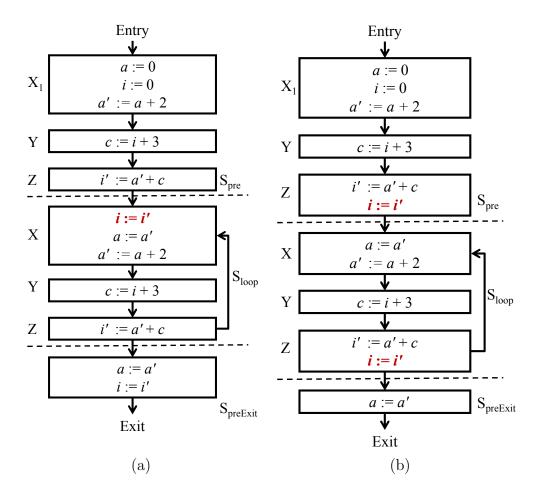

hazards. We want to make sure that when we pipeline a loop, we do not read a variable which has not yet been written. A critical observation is that data propagation is required only for loop carried dependencies. GetLoopCarriedDependencies identifies the microsteps where loop carried dependencies are being read. Then, CheckConflict checks whether there would be a conflict when we pipeline the loop. Conflict occurs when the value being read in a microstep is not yet written in the pipelined loop execution. If so, RelocateMSteps works in two steps. It first relocates the microstep which reads the variable in an iteration to the starting of  $S_{loop}$ . This step can be proved by the interchange primitive since we have already established that the value has not been written yet so there are no read write hazards in between. In the next step, we relocate the microstep to the end of  $S_{loop}$ . Note, to maintain the invariant that executing CCDFG before and after this relocation is the same, we need to add the microstep at the end of  $S_{pre}$  as well and remove it from  $S_{preExit}$ . This step ensures that any variable which is being read has already been written. Note that in order to maintain the invariant, only those microsteps can be propagated which exist in  $S_{preExit}$ , which means only those steps which occur before the conditional branch in original CCDFG can be relocated. This ensures that our algorithm does not have the bug which the previously proposed algorithm had. In Figure 5.7(b) we found that the loop carried dependency i' in X would create a conflict when we would move X before Z while

Figure 5.8: (a) Data propagation - first step (b) Data propagation - second step

pipelining. So, first we relocate the microstep i := i' to the beginning of  $S_{loop}$  using interchange primitive in Figure 5.8(a). Then, we move the microstep to end of  $S_{pre}$  and  $S_{loop}$  and remove the microstep from  $S_{preExit}$  in Figure 5.8(b). Note that this preserves execution as explained more in Chapter 6. This step needs to be repeated for every variable found using GetLoopCarriedDependencies.

Generate shadow registers: Algorithm 3 inserts shadow registers to prevent variables from being overwritten before being read.

## Algorithm 3 Generate shadow registers

```

1: procedure GENERATESHADOWREGISTERS(L, I)

V \leftarrow GetAllVariables(L).

2:

for each v in V do

3:

w_v \leftarrow WriteVariable(v, L).

4:

r_v \leftarrow LastReadVariable(v, L).

5:

if RequireShadowRegister(r_v, w_v, I) \neq 0 then

6:

L \leftarrow AddShadowRegister(w_v, L).

7:

end if

8:

9:

end for

10:

return (L).

11: end procedure

```

We first compute all program variables that may be overwritten before being read, which means these are the variables that require shadow registers. To find such variables, GetAllVariables first gets a set of all variables. Then, for each variable, we compare the distance (the number of scheduling steps) between the write of the variable  $w_v$  (WriteVariable) and the last read of the variable  $r_v$  (LastReadVariable) in an iteration; if the distance is greater than I (pipeline interval), the variable is assigned the new data value of the next iteration before the current iteration's value has been fully consumed; this warrants insertion of shadow registers in every scheduling step between the  $r_v$  and  $w_v$ . The value is propagated every clock cycle following the CCDFG data flow. We apply the shadow register primitive on the microstep which writes the variable (AddShadowRegister). We assign that variable to a new temporary variable called shadow register in every new scheduling step and replace all subsequent reads of that variable with the shadow register till its next write. In Figure 5.9, we introduce a shadow register  $a\_reg$  in X and  $a\_reg2$  in Y. This step is also repeated for all the variables found

Figure 5.9: After shadow register

using GetAllVariables.

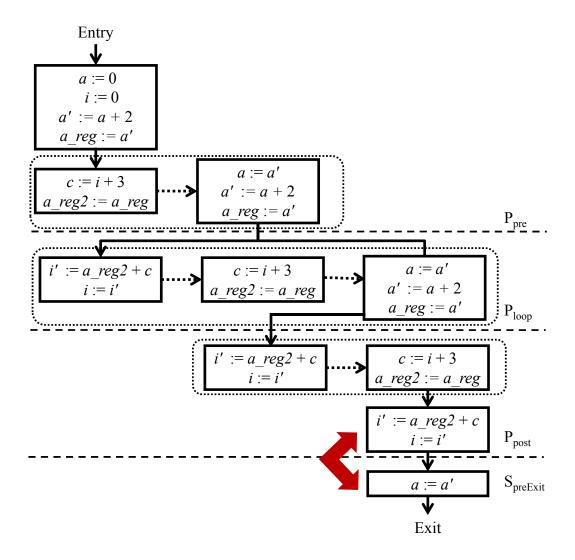

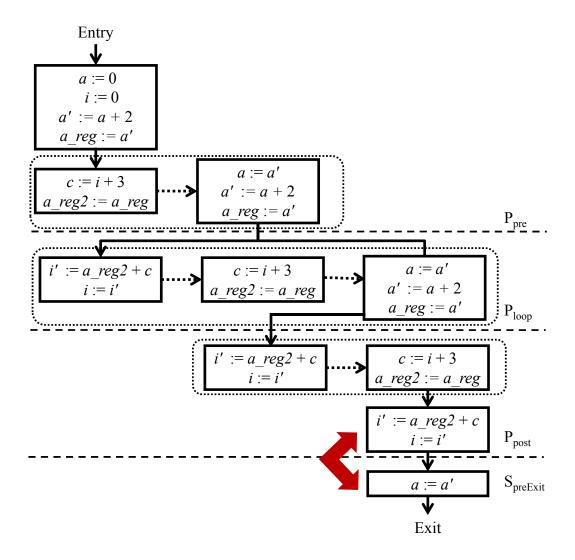

Superstep construction: Now that we have removed the data hazards, we can successfully pipeline the loop using the pipeline interval I. We combine the scheduling steps of the successive iterations, forming scheduling "supersteps" that act as scheduling steps for the pipelined implementation. Supersteps must account for read-after-write hazards, i.e., if a variable is written in a scheduling step s and read subsequently in s' then s' cannot be in a superstep that precedes s in the control/data flow. A scheduling step is allowed to move up another scheduling step only if there are no intermediate read and write conflicts. Note that we implement

Figure 5.10: After superstep construction

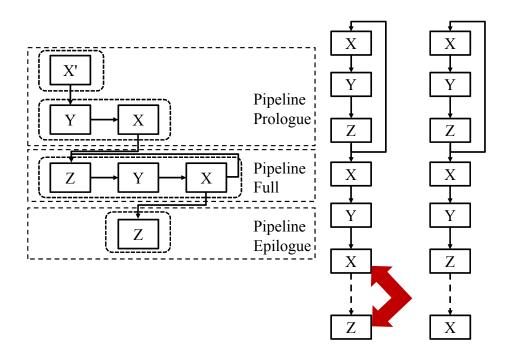

data forwarding; thus s and s' can be in a single scheduling superstep. Superstep construction on  $S_{pre}$  and  $S_{loop}$  creates a CCDFG with three parts: prologue  $P_{pre}$ ,  $P_{loop}$  which is the full pipeline stage and epilogue  $P_{post}$  as shown in Figure 5.10. We will later prove using our invariant that executing  $P_{pre}$  followed by k iterations of  $P_{loop}$  followed by  $P_{post}$  is equivalent to executing  $S_{pre}$  followed by x iterations of  $S_{loop}$ , where value of x is determined based on value of k, pipeline interval I and number of scheduling steps in S.

Figure 5.11: Final pipelined CCDFG

Add Branches: To add the branches back, we use the a combination of interchange primitive and reverse of Branch primitive. Note in Figure 5.10, if there are no read write hazards in between the last scheduling step Z of  $P_{post}$  and  $S_{preExit}$ , we can interchange them using interchange primitive. Now recall from the branch primitive that if there is a loop structure  $S_{loop}$  with a conditional branch, then executing  $S_{loop}$  such that it exits in the (k+1)st iteration is same as executing  $S_{loop}$  without the conditional branch followed by only those steps from  $S_{loop}$  which occur before the branch  $S_{preExit}$ . Now, we apply the reverse of branch primitive here.  $P_{loop}$  in Figure 5.10 is a loop structure without a conditional branch, followed

by a collection of microsteps  $P_{preExit}$  (here, a collection of Z, Y and  $S_{preExit}$ ). Then, we can add an exit conditional branch in  $P_{loop}$  after the microsteps  $P_{preExit}$ . This branch points to the next scheduling step after the loop  $P_{post}$  if the exit condition is true. We can add the conditional and the unconditional branch as shown in Figure 5.11.

We now have the final pipelined loop structure. We describe a proof sketch for the primitives and the algorithm in the next chapter.

## Chapter 6

### PROOF SKETCH

Certification of our loop pipelining algorithm naturally requires a certification of each of our primitives. In addition, we need to ensure that every time a primitive needs to be applied, the conditions under which the primitive can be applied are maintained. We discuss both aspects below.

### 6.1 CORRECTNESS OF PRIMITIVES

We must prove that applying a particular primitive is correct, *i.e.*, maintaining a certain invariant. This is proven without considering how it is applied in the context of a pipeline synthesis algorithm. We give an outline of the proof to justify that the primitives are correct.

Figure 6.1: Correctness of  $\phi$ -elimination primitive

$\phi$ -elimination primitive: We prove that the execution of a  $\phi$ -construct is same as executing the corresponding assignment statements assuming that we already know the previous basic block for the  $\phi$ -construct. In essence, we prove that the algorithm correctly resolves the  $\phi$  to create multiple assignment statements. We induct along the length of each sub-microstep of  $\phi$ -construct and relate it to one corresponding assignment statement as shown in Figure 6.1.

Figure 6.2: Shadow register primitive

Shadow register primitive: We prove that adding a shadow register microstep,  $a\_reg = a'$  (as shown in Figure 6.2), does not change the value of any variable in the state except the shadow variable. In essence, we prove that if a variable is not written in a microstep, then its value in the state before and after executing that microstep is same. Also, we prove that after executing the shadow register microstep, value of  $a\_reg$  in the state is equal to value of a'. Furthermore, since now the value of  $a\_reg$  is equal to value of a', we prove that executing a

statement which reads a' has the same effect on the state as executing a statement which reads  $a\_reg$  till the next write of a'. This needs to be done for all types of statements e.g., assignment statements (with different types of operations like load, add, mul, getelementptr e.t.c.), store statement, branch statement etc. We determine the variables read and written in a statement by analyzing the statements. Note that  $a\_reg$  is a new variable which is neither written nor read in the given statements.

Interchange primitive: We prove that we can interchange any two adjacent microsteps (excluding branch microsteps) which do not have read-write conflict. We prove that given an initial state, the state after executing microsteps m and n is same as the state after executing n then m if m and n have no read-write conflict. Suppose, the state after executing m and n is  $s_1$  and that after executing n and m is  $s_2$ . We prove that for any variable x, its value remains same in  $s_1$  and  $s_2$ . After normalizing the states, we can prove that  $s_1$  is equal to  $s_2$ , i.e., the states are the same after executing the two microsteps in a sequence or in an interchanged order. Again, reasoning about read and write of statements involves reasoning about execution semantics of all types of microsteps present in the language which is not trivial.

Branch primitive: We prove that executing S k times such that it exits in the (k+1) st iteration is same as executing  $S_{loop}$  k times followed by  $S_{preExit}$ . (c.f Figure 6.3). We need to define a notion of a well-formed-flow to ensure that we can show that the branch does not exit in the first k iterations. We also need a way to track the backedge along the unconditional branch and ensure that it points back to the beginning of loop S.

Superstep construction primitive: This primitive is for overlapping iterations while maintaining data and control dependencies. It is built on interchange primitive but while interchange primitive handles only two adjacent microsteps, superstep construction moves around scheduling steps with multiple microsteps.

Figure 6.3: Branch primitive

The interchange primitive is extended by non-trivial induction along the length of the scheduling steps to achieve the desired result. Superstep construction primitive is proved using the interchange primitive and our key invariant described in detail below.