The HKU Scholars Hub The University of Hong Kong 香港大學學術庫

| Title       | Negative capacitance transistors with monolayer black phosphorus                                                      |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Author(s)   | Liu, F; Zhou, Y; Wang, YJ; Liu, XY; Wang, J; Guo, H                                                                   |  |  |

| Citation    | npj Quantum Materials, 2016, v. 2016, p. 16004:1-6                                                                    |  |  |

| Issued Date | 2016                                                                                                                  |  |  |

| URL         | http://hdl.handle.net/10722/238698                                                                                    |  |  |

| Rights      | This work is licensed under a Creative Commons Attribution-<br>NonCommercial-NoDerivatives 4.0 International License. |  |  |

# **ARTICLE** OPEN Negative capacitance transistors with monolayer black phosphorus

Fei Liu<sup>1,2</sup>, Yan Zhou<sup>1,3</sup>, Yijiao Wang<sup>4</sup>, Xiaoyan Liu<sup>4</sup>, Jian Wang<sup>1</sup> and Hong Guo<sup>2</sup>

Quantum transport properties of negative capacitance transistors (NC-FETs) with monolayer black phosphorus (ML-BP) are theoretically studied. Our calculations show that atomistic thin ML-BP can enhance the amplification effect of the ferroelectric layer, and subthreshold swing is effectively reduced to 27 mV per decade in ML-BP NC-FETs. Device performance can be further improved by increasing the thickness of ferroelectric layer and using thinner or high-*k* insulate layer. Due to the temperature dependence of ferroelectric layer ML-BP NC-FETs have higher on-state current at low temperature, which is different from that of MOSFETs. By considering the metal–ferroelectric interface layer, our calculations show that the device performance is degraded by the interface. Compared with the International Technology Roadmap (ITRS) 2013 requirements, ML-BP NC-FETs can fulfil the ITRS requirements for high-performance logic with a reduced supply voltage. The new device can achieve very low power delay product per device width at  $V_D = 0.3$  V, which is just 44% of that in ML-BP FETs.

npj Quantum Materials (2016) 1, 16004; doi:10.1038/npjquantmats.2016.4; published online 27 July 2016

## INTRODUCTION

The development of complementary metal-oxide-semiconductor (CMOS) technology in the past half century has followed the Moore's law<sup>1</sup> to a very good extent. This path is however reaching the physical limit where power dissipation in circuits has become the game-breaker. Even though various technologies have been applied to improve device performance in CMOS-strained silicon, high-k metal gate, FinFET, etc.,<sup>2</sup> these do not change the operation principle of metal oxide semiconductor field effect transistor (MOSFET) in which the current is controlled by modulating the thermionic carriers over the potential barrier of the transistor channel. A consequence is that the subthreshold swing (SS) can not be made smaller than the thermal limit of 60 mV per decade,<sup>3</sup> which is a limit dictated by the fundamental physics of the Boltzmann distribution. On the other hand, if somehow SS could break this limit, one would be able to reduce the external voltages for the transistor operation, thereby reducing power dissipation and prolonging the Moore's law scaling. The economic impact of such a scenario would be enormous.

To this end, an extremely interesting idea is the negative capacitance field effect transistor (NC-FET), which was theoretically proposed to achieve SS below the 60 mV per decade limit.<sup>4</sup> In NC-FETs, a ferroelectric (FE) gate layer is applied and couples with a positive capacitor to realise a bistable state. The combination of the external electric field and the polarisation in the FE material gives rise to a negative voltage drop through the FE layer and, in effect, results in a 'voltage amplification' that improves the subthreshold characteristics. This possibility of achieving sub 60-mV per decade has excited great interests on NC-FETs.<sup>5–11</sup> Experimentally, a sub-60 mV per decade has been achieved in polymer FE MOSFETs<sup>5</sup> and the capacitance

of FE-dielectric bilayer has been enhanced due to the negative capacitance effect.<sup>6</sup> Very recently, a direct measurement of negative differential capacitance has been achieved,<sup>12</sup> and negative capacitance FinFETs have be realised to achieve extremely low-steep swings.<sup>13</sup>

In this work, we show that the voltage amplification effect in NC-FETs can be further enhanced if the transistor channel is made of two-dimensional (2D) materials because 2D channels have better gate control to begin with. More importantly, it turns out that SS can be expressed by a transport factor multiplying a body-factor, and the use of 2D materials decreases the latter (see below) thus reduces the SS. From the practical point of view, the thin layer of 2D materials makes them a natural choice for producing flexible structures due to their out-of-plane flexibility and, for flexible and wearable consumer electronics.<sup>14</sup> Therefore, in this work we propose and theoretically investigate the interesting device physics of a new class of emerging nanoelectronics where FE is combined with 2D materials leading to the 2D NC-FETs.

To be more specific but without losing generality, we consider the newly discovered monolayer (ML) black phosphorus (BP) as the channel material. ML-BP is a direct gap semiconductor and has a relatively high mobility.<sup>15–20</sup> Therefore, higher on-state current and faster switching speed can be achieved in ML-BP devices compared with monolayer transition metal dichalcogenides (TMDCs) FETs.<sup>20</sup> We predict that the proposed device has a good gate control and can achieve low-power performance at the drain voltage  $V_D = 0.3$  V, which is much smaller than that of the Si FETs. The power delay product per device width is predicted to be much smaller than the requirement of the International Technology Roadmap (ITRS) 2013 for high-performance (HP) applications in the 2024 horizon.<sup>21</sup> We present design

Received 4 May 2016; revised 15 June 2016; accepted 15 June 2016

<sup>&</sup>lt;sup>1</sup>Department of Physics and the Center of Theoretical and Computational Physics, The University of Hong Kong, Hong Kong, China; <sup>2</sup>Department of Physics, McGill University, Montreal, QC, Canada; <sup>3</sup>School of Electronic Science and Engineering and Collaborative Innovation Center of Advanced Microstructures, Nanjing University, Nanjing, China and <sup>4</sup>The Key Laboratory of Microelectronic and Circuits, Institute of Microelectronics, Peking University, Beijing, China. Correspondence: F Liu (fliu003@gmail.com) or Y Zhou (yanzhou@hku.hk)

considerations for optimising the performance, namely by using thicker FE layer and thinner or high-*k* insulator layers. The temperature dependence, electrode–FE interface effects and scaling behaviour of NC-FETs are also determined.

### RESULTS

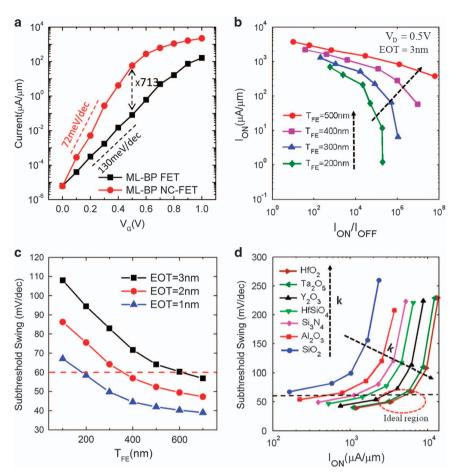

We consider a device with a 400 nm FE layer, 3 nm equivalent oxide thickness (EOT) layer and 20 nm thickness substrate as shown in Figure 1a. We first compared the device characteristics of FETs and NC-FETs. The drain current  $I_{\rm D}$  versus  $V_{\rm G}$  characteristic is presented in Figure 2a. From the figure, we can clearly see that the device performance is greatly improved in NC-FETs. When the FE layer is applied, the SS is reduced from 130 to 72 mV per decade and the current at  $V_{\rm G} = 0.5 \,\rm V$  is increased by 713 times as demonstrated in Figure 2a. Even though the SS is improved, it is still greater than the thermal limit. For Equation (2), there are three different ways to further improve device performance: decreasing C<sub>FE</sub> and increasing C<sub>INS1</sub> or C<sub>B</sub>. We first analyse the effects of the FE layer thickness. Increasing the thickness, the device performance is improved as shown in Figure 2b. With a fix  $I_{ON}/I_{OFF}$  ratio, higher ION can be obtained in NC-FETs with thicker FE layer. Here, on-state and off-state currents are calculated with a fixed  $V_{G}$ window equal to the supply voltage  $V_{\rm D}$  of 0.5 V. Another improvement of device performance is achieved by increasing the capacitance of the insulator layer. Here different EOT and gate oxide layer materials are applied. When the thickness of FE layer reaches 700 nm, SS smaller than 60 mV per decade is obtained in NC-FETs with 3 nm EOT as shown in Figure 2c. It is also found that the performance of NC-FETs can be improved by using high-k gate oxide layer. Seven different gate oxide materials are applied and smaller SS can be achieved at the same ION current in NC-FETs with high-k gate oxide layer as shown in Figure 2d.

Regarding the design guidelines of NC-FETs as low power devices, the temperature effect on device performance is studied. It is well known that the polarisation of FE layer greatly depends on the temperature and the state of transistor is modulated by controlling the thermionic carrier over the barrier. Therefore, the temperature has a great impact on the performance of NC-FETs. The dynamic of FE polarisation can be described by the Landau–Khalatnikov (LK) equation<sup>4</sup>

$$\rho \frac{d\overrightarrow{P}}{dt} + \nabla_{\overrightarrow{P}} U = 0 \tag{1}$$

where the free energy of FE material is the function of a series expansion of polarisation:  $\!\!\!\!^4$

$$U = \alpha P^2 + \beta P^4 + \gamma P^6 - \overrightarrow{E}_{ext} \cdot \overrightarrow{P}$$

<sup>(2)</sup>

where  $\alpha$ ,  $\beta$  and  $\gamma$  are laudau coefficients and *P* is the polarisation,

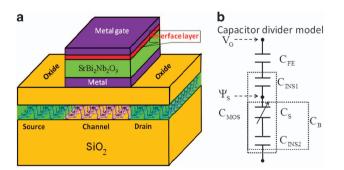

**Figure 1.** The negative capacitance (NC) transistor (FET) based on monolayer black phosphorus (ML-BP). (a) Sketch of the simulated ML-BP NC-FET. Transport direction is assumed to be the armchair direction of ML-BP. (b) Equivalent capacitor divider model of ML-BP NC-FETs.

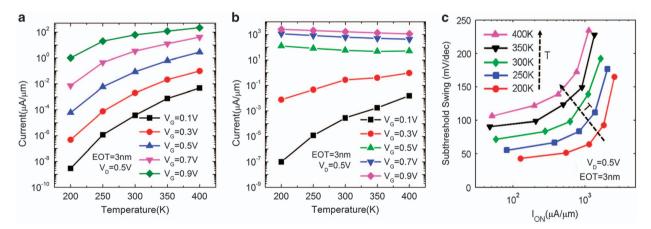

room temperature.<sup>22</sup> The  $\alpha$  is a coefficient with a temperature dependence:  $a = a_0(T - T_c)$ ,  $a_0 = -1.03 \times 10^6$ ,  $T_c = 663$  K is curie temperature. On the basis of the model, the temperature dependence of NC-FETs can be simulated. Due to the existence of the FE layer, NC-FETs have different temperature dependence of the drain current from FETs. For a classical FET, the carrier follows Fermi–Dirac distribution. As the temperature increases, the Boltzmann tail broadens and more thermionic carriers transport over the barrier, and the drain current increases at all gate voltages as shown in Figure 3a, which shows the  $I_{\rm D}$  as a function of T for 15 nm ML-BP FETs at different gate voltages. With the decreasing of temperature, the current is markedly reduced. The NC-FETs have different temperature dependence due to the existence of FE layer as shown in Figure 3b. We observe that at lower T, the drain current is reduced at  $V_{\rm G}$  < 0.3 V and is increased at  $V_{\rm G}$  > 0.5 V, which results in smaller SS at lower temperature as shown in Figure 3c. NC-FETs also work on the control of thermionic current over the barrier but with additional FE layer. Hence, the phenonmena can be attributed to the temperature dependence of the FE layer. The polarisation of FE layer has a phase change with the evolution of temperature. There is a transition temperature  $T_c$ . At a lower temperature below  $T_c$ , the polarisation of the SrBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub> layer is very large and the material is in FE phase and the gate voltage is greatly amplified. Even though the carrier is partly frozen with the decreasing temperature, the lowered barrier due to the amplification effect leads to large current as shown in Figure 3b. As the temperature is increased to  $T_{cr}$  the material reaches phase change point and would change from the FE state to a paraelectric phase. With the increasing of temperature, the sign of laudau parameter  $\alpha$  will be changed from negative to positive, and the free energy does not have the unstable equilibrium state. Therefore, above  $T_{c}$ , NC-FETs cannot work in the negative capacitance region and the

$\alpha = -3.74 \times 10^8$ ,  $\beta = -9.4 \times 10^7$ ,  $\gamma = 1.18 \times 10^9$ , for SrBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub> at

Although the device performance can be optimised in properly engineered devices and sub-60 mV per decade can be achieved, and ideal condition is assumed and many effects will deteriorate the performance of NC-FETs. Various interfacial effects including the strain, impurities, bonding and screening etc at both interfaces of the FE layer will inevitably change the ferroelectricity and further modulate the charge transport process.<sup>23–25</sup> Due to broken symmetry at the top and bottom interfaces of FE layer, there will be asymmetrical charge screening effects that can be modelled by a different extrapolation length of the interfacial polarisation. All these effects can be important especially for ultrathin FE layer. However, for our parameter space where the thickness of the FE layer is not too thin, the size-driven phase changes can be safely disregarded and the well-known interfacial capacitance model can be employed to study the interfacial effects for temperature and thickness space investigated in this work. In reality, perfect contact between the metal electrode and FE layer is hard to obtain and an interface layer is usually sandwiched between the two materials as shown in Figure 1a. Interface between metal electrodes and FE layer is an important effect, which leads to many abnormal behaviours of FE material. Interface capacitance model is applied to modelling the interface effect.<sup>26</sup> Here, just the interface between the top gate and the FE layer is considered and the interface under the FE layer is neglected. So, the effective capacitance  $C_{\text{EFF}}$  of the FE layer including interface effect can be described as a series connection of pure FE layer capacitance C<sub>FE</sub> and interface layer capacitance C<sub>INT</sub> as following:<sup>26</sup>

amplification effect of the FE layer will disappear.

$$\frac{1}{C_{\text{EFF}}} = \frac{1}{C_{\text{FE}}} + \frac{1}{C_{\text{INT}}} \tag{3}$$

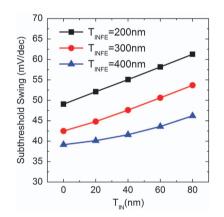

With the model, the interface impact on device performance can be simulated as illustrated in Figure 4. The figure presents the SS with different interface thicknesses. It can be seen that the SS

**Figure 2.** Device characteristics of FETs and NC-FETs. (**a**)  $I_D-V_G$  for 15 nm ML-BP NC-FETs and ML-BP FETs at  $V_D = 0.5$  V and T = 300 K. The equivalent oxide thickness (EOT) is 3 nm and the thickness of ferroelectric layer is 400 nm. (**b**)  $I_{ON} - I_{ON}/I_{OFF}$  for 15 nm ML-BP NC-FETs with different ferroelectric layer thickness ( $T_{FE}$ ) and 3 nm EOT at  $V_D = 0.5$  V and T = 300 K. (**c**) Subthreshold swing (SS) as the change of ferroelectric layer thickness for 15 nm ML-BP NC-FETs with different EOT at  $V_D = 0.5$  V and T = 300 K. (**d**) SS versus  $I_{ON}$  of ML-BP NC-FETs with 400 nm ferroelectric layer, 3 nm insulator layer and different gate insulator materials with  $V_G$  window set at the supply voltage  $V_D = 0.5$  V.

**Figure 3.**  $I_D$  as a function of temperature (*T*) for (**a**) 15 nm ML-BP FETs with 3 nm EOT and (**b**) 15 nm ML-BP NC-FETs with 400 nm ferroelectric layer and 3 nm EOT at different gate voltages. (**c**) SS versus  $I_{ON}$  of ML-BP NC-FETs with 400 nm ferroelectric layer and 3 nm EOT at different temperatures.

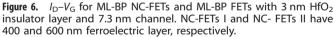

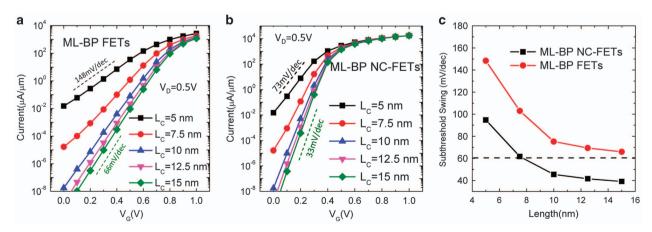

increases linearly with the thickness of the interface layer. Due to the existence of the interface layer, the effective thickness of FE layer is reduced and the amplification of FE layer is degraded. So, it is important to reduce the thickness of the interface layer to realise NC-FETs experimentally. At last, we studied the scaling behaviour of NC-FETs and estimated the device performance for HP applications from ITRS 2013. The simulated channel length ranges from 5 to 15 nm. Figure 5a,b shows drain current of ML-BP FETs and ML-BP NC-FETs as a function of the gate voltage with a fixed  $V_D = 0.5$  V,

np

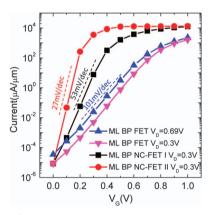

respectively.  $I_{\rm D}$  decreases with the increasing channel length  $L_{\rm C}$  for the two kinds of devices, and for NC-FETs current becomes nearly independent of channel length for  $V_{\rm G}$  > 0.7 V. SS decreases fast when the channel length increases as shown in Figure 5c and SS of ML-BP NC-FETs can be smaller than the 60 mV per decade limit. It has been shown that the ballistic performance of ML-BP FETs can meet the ITRS requirements for HP logic applications in 10 years horizon.<sup>20</sup> In ideal conditions, NC-FETs have better gate control compared with the FETs due to the amplification of FE laver. Hence, ML-BP NC-FETs are also suitable for logic applications. For lower-power consumption, reducing the supply voltage is critical, which determines the dynamic and static power dissipation. Figure 6 shows  $I_{D}-V_{C}$  characteristics for ML-BP NC-FETs and ML-BP FETs at different supply voltages. For ML-BP FETs, when  $V_{\rm D}$  decreases from 0.69 to 0.3 V, the drain current drops clearly. Therefore, in FETs lowering the supply voltage is not an effective method to reduce the power dissipation because a reasonable-driven current cannot be kept. In NC-FETs, the control voltage can be amplified by the FE layer. Even though the supply voltage is reduced to 0.3 V, ML-BP NC-FETs can obtain good device performance than ML-BP FETs as shown in Figure 6. SS reaches 53 mV per decade in NC-FETs with 400 nm FE layer and can be further reduced to 27 mV per decade in NC-FETs with 600 nm FE layer. In Table 1, performance metrics of ML-BP NC-FETs with

**Figure 4.** SS as a function of interface layer thickness ( $T_{IN}$ ) for 15 nm ML-BP NC-FETs with 3 nm HfO<sub>2</sub> insulator layer and 400 nm ferroelectric layer at  $V_D = 0.5$  V.  $T_{INFE} = T_{IN} + T_{FE}$ , where  $T_{FE}$  is effective ferroelectric layer thickness.

400 nm FE layer and ML-BP FETs are compared with the requirements of ITRS 2013 for HP applications.<sup>21</sup> The off-state current is fixed at 0.1  $\mu$ A/ $\mu$ m and the gate voltage windows are set to be equal to the value of bias voltage:  $V_G^{ON} - V_G^{OFF} = V_D$ . The intrinsic delay is computed as  $\tau = (Q_{ON} - Q_{OFF})/I_D$  and the power delay product (PDP) per device width is calculated as PDP =  $(Q_{ON} - Q_{OFF})V_D$ . The two compared devices can meet technique requirements for HP applications of ITRS 2013 for the year 2024. In NC-FETs, PDP is effectively reduced and only 44% of that of FETs. Due to the low on-state current, the intrinsic delay is longer than that of ML BP FETs but still lower than the requirement of ITRS 2013.

#### DISCUSSION

Compared with the classical FETs, the NC-FETs have an additional FE layer deposited on the metal gate as shown in Figure1a. Therefore, the transport mechanism of NC-FETs is the same as that of FETs, and the NC-FET device can be viewed as a FET connected to a gate voltage 'amplifier'. The electrostatics due to the gate of NC-FETs can be roughly described by the capacitor divider model<sup>4</sup> of Figure1b where  $C_{\text{FE}}$ .  $C_{\text{INS1}}$  and  $C_{\text{B}}$  are capacitors due to the FE layer, the insulator layer and the body structure that includes the channel and the

**Figure 5.** The scaling behaviour of NC-FETs. (a)  $I_D-V_G$  for ML-BP FETs with 3 nm HfO<sub>2</sub> insulator layer and different channel lengths ( $L_c$ ) at  $V_D = 0.5$  V and T = 300 K. (b)  $I_D-V_G$  for ML-BP NC-FETs with 400 nm ferroelectric layer, 3 nm HfO<sub>2</sub> insulator layer and different channel lengths at  $V_D = 0.5$  V and T = 300 K. (c) SS as a function of channel length of 15 nm ML-BP FETs and ML-BP NC-FETs with 400 nm ferroelectric layer at  $V_D = 0.5$  V and T = 300 K. (c) SS as a function of channel length of 15 nm ML-BP FETs and ML-BP NC-FETs with 400 nm ferroelectric layer at  $V_D = 0.5$  V and T = 300 K.

Table 1.

Performance metrics of ML-BP NC-FETs with 400 nm

ferroelectric layer, DG ML-BP FETs and the ITRS requirements for high-performance applications in the 2024 horizon

|                          | Node 2024 | NC-FETs | DG FETs |

|--------------------------|-----------|---------|---------|

| L <sub>G</sub> (nm)      | 7.3       | 7.3     | 7.3     |

| $V_{\rm D}$ (V)          | 0.69      | 0.3     | 0.69    |

| EOT (nm)                 | 0.49      | 0.49    | 0.49    |

| I <sub>OFF</sub> (μΑ/μm) | 0.1       | 0.1     | 0.1     |

| I <sub>ON</sub> (μΑ/μm)  | 1170      | 1828    | 2798    |

| τ (ps)                   | 0.451     | 0.044   | 0.028   |

| PDP (fJ/µm)              | 0.36      | 0.024   | 0.055   |

Compared with DG FETs, NC-FETs can work at lower driven voltage  $V_{\rm D}$  = 0.3 V and power consumption can be effectively reduced. A fixed  $V_{\rm G}$  window equals to the power supply voltage  $V_{\rm D}$ .

Abbreviations: DG, double gate; EOT, equivalent oxide thickness; ITRS, International Technology Roadmap; ML-BP, monolayer black phosphorus; NC-FET, negative capacitance field effect transistor; PDP, power delay product.

substrate. The gate control can be quantified by the SS which is defined as:  $\!\!\!\!^4$

$$SS \equiv \frac{\partial V_{G}}{\partial (\log_{10} l_{D})} = \frac{\partial \psi_{s}}{\partial (\log_{10} l_{D}) \partial \psi_{s}} \equiv n \times m$$

(4)

where the last equality defines the parameters *n* and *m*: the parameter *n* is related to the transport mechanism (called the transport factor) and the parameter *m* is determined by the device structure (called the body factor). The quantity  $\psi_s$  is the surface potential in the transistor channel as shown in Figure 1b. In a classical FET, the current is mainly composed of thermionic carriers over the potential barrier that follows the Boltzmann distribution, hence the transport factor *n* is a constant of 60 mV per decade at room temperature. The ultimate value of SS therefore depends on the body-factor *m*, which turns out to be always greater than unity due to the positive capacitances in the capacitor divider model if there is no FE layer in Figure1b. Hence for traditional FETs, SS is always greater than the 60 mV per decade limit.

By adding a FE layer, it is possible to reduce the body-factor m smaller than unity, so that SS can be made smaller than 60 mV per decade. Using the capacitor divider model again, the body-factor m can be expressed as:

$$m = \frac{\partial V_{\rm G}}{\partial \psi_{\rm s}} = 1 + \frac{C_{\rm B}(C_{\rm INS1} + C_{\rm FE})}{C_{\rm INS1}C_{\rm FE}}.$$

(5)

From this we obtain 0 < m < 1 if the following inequality holds:<sup>7</sup>

$$C_{\rm MOS} = \frac{C_{\rm INS1}C_{\rm B}}{C_{\rm INS1} + C_{\rm B}} < -C_{\rm FE} < C_{\rm INS1} \tag{6}$$

where  $C_{MOS}$  is the capacitance of the underlying transistor. Equation (3) can be used as the design rule for NC-FETs.

From Equation (2), noting that since  $C_{FE}$  is negative, the body-factor *m* can be further decreased by increasing  $C_B$ . Compared with bulk silicon or even ultrathin body FETs, 2D materials can reach larger capacitance  $C_B$  due to atomically thin structures. Therefore the idea of NC-FETs can in principle be better realised in 2D channels. In the rest of the paper, we focus on the ML-BP material as the channel and quantitatively investigate the device properties of the 2D NC-FETs.

In this work, monolayer BP is applied as the channel material of NC-FETs. Other 2D materials such as layered TMDCs can also be used in NC-FETs for achieving good gate control. Layered BP film undergoes degradation in ambient air, which will likely degrade the performance of BP devices. Recently, various methods have

been proposed to keep a clean BP film, such as encapsulation by  $AO_x$  layers,<sup>27</sup> covering by copolymer capping layer,<sup>28</sup> graphene and hexagonal boron nitride.<sup>29</sup> It is theoretically predicted that monolayer BP can be well maintained on the HfO<sub>2</sub> (111) surface<sup>30</sup> and H-passivated Al<sub>2</sub>O<sub>3</sub>.<sup>31</sup> Further progress should make it feasible to manage the degradation of BP film for real device applications. The device performance of NC-FETs greatly depends on properties of the channel material and FE layer as well as the device structure. 2D materials with high carrier mobility and reasonable band gap are beneficial for achieving higher on-current and on/off current ratio of NC-FETs. The amplification effect of FE layer can be optimised by adjusting the FE material parameters such as increasing the FE layer thickness and coercive voltage, and decreasing the remnant polarisation.<sup>32</sup>

# CONCLUSION

Negative capacitance transistor based on 2D material-monolayer black phosphorus is proposed, which combines 2D material-ML-BP with sub-60 mV per decade operation. By using 2D material amplification effect of FE layer can be enhanced. We show that the combination of ML-BP and negative capacitance transistor can effectively reduce subthreshold swing due to the atomistic thin structure and the amplification effect of the FE layer. The new device can achieve a subthreshold swing as small as 27 mV per decade at  $V_{\rm D}$  = 0.3 V. Device performance of ML-BP NC-FETs can be optimised by increasing the thickness of FE layer and using thinner or high-k insulate layer. ML-BP NC-FETs show different temperature dependence from MOSFET and can reach higher on current at low temperature due to the polarisation of FE layer. By considering the metal-FE interface layer, our calculation shows that the device performance is degraded by the interface. Compared with the ITRS 2013 requirements, ML-BP NC-FETs can fulfil the ITRS requirements for HP applications in 2024 and the power delay product per device width can be effectively reduced. Therefore, the proposed ML-BP NC-FETs should be very helpful for designing low-power circuits.

# MATERIALS AND METHODS

Figure 1 schematically shows the device structure of ML-BP NC-FETs. A SrBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub> FE layer is deposited on the metallic gate of the underlying transistor. In our simulation hysteretic effect is neglected, corresponding to a relatively thick FE. In the underlying MOSFET, ML-BP is used as the channel material. The source/drain of FET is n-type doped with a density of  $7.0 \times 10^{13} \text{cm}^{-2}$ , and the channel under the gate is intrinsic. The length of source or drain is 10 nm and the channel length ranges from 5 to 15 nm. The ballistic transport of ML-BP is calculated by self-consistently solving the Schrodinger and Poisson equations within nonequilibrium Green's function formalism. A four band tight binding Hamiltonian is used to describe the ML-BP material and can well fit the low-energy band structures.<sup>33</sup> The amplifying effect of the FE layer is calculated by solving the 1D Landau model.<sup>4</sup> Landau parameters of SrBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub> and temperature dependence model are taken from ref. 22 The effect of the electrode-FE interface is described by the interface capacitance model,<sup>26</sup> which is coupled with the 1D Landau model to study interface effect in ML-BP NC-FETs.

# ACKNOWLEDGEMENTS

This work was supported by the University Grant Council (contract no. AoE/P-04/08) of the Government of HKSAR, National Natural Science Foundation of China with no.11374246 (J.W.) and NSERC of Canada (H.G.).

## CONTRIBUTIONS

F.L. and Y.Z. conceived and designed the research. F.L. and Y.Z. contribute to this work equally. Y.Z. developed the capacitor model. F.L. performed the calculations. Y.W. and X.L. assisted in simulation and physical analysis. J.W. and H.G. participated in the explanation of results. F.L., Y.Z., J.W. and H.G. wrote the manuscript.

#### **COMPETING INTERESTS**

The authors declare no conflict of interest.

#### REFERENCES

- 1. Moore, G. E. Cramming more components onto integrated circuits. *Proc. IEEE* 86, 82 (1998).

- Bohr, M. The evolution of scaling from the homogeneous era to the heterogeneous era. *Proc. IEEE IEDM* 1.1.1–1.1.6, doi:10.1109/IEDM.2011. 6131469 (2011).

- Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy efficient electronic switches. *Nature* 479, 329–337 (2011).

- Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 (2008).

- Rusu, A., Salvatore, G. A., Jimnez, D. & Ionescu, A. M. Metal-ferroelectric-metaloxide-semiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification. *Proc. IEEE IEDM* 16.3.1–16.3.4, doi:10.1109/IEDM.2010.5703374 (2010).

- Khan, A. I. et al. Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures. Appl. Phys. Lett. 99, 113501 (2011).

- Salvatore, G. A., Rusu, A. & Ionescu, A. M. Experimental confirmation of temperature dependent negative capacitance in ferroelectric field effect transistor. *Appl. Phys. Lett.* **100**, 163504 (2012).

- Then, H. W. *et al.* Experimental observation and physics of negative capacitance and steeper than 40mV/decade subthreshold swing in Al<sub>0.83</sub>In<sub>0.17</sub>N/AIN/GaN MOS-HEMT on SiC substrate. *Proc. IEEE IEDM* 28.3.1–28.3.4, doi:10.1109/IEDM. 2013.6724709 (2013).

- Jain, A. & Alam, M. A. Stability constraints define the minimum subthreshold swing of a negative capacitance field-effect transistor. *IEEE Trans. Electron Devices* 61, 2235–2242 (2014).

- Masuduzzaman, M. & Alam, M. A. Effective nanometer airgap of NEMS devices using negative capacitance of ferroelectric materials. *Nano Lett.* 14, 3160–3165 (2014).

- Appleby, D. J. R. et al. Experimental observation of negative capacitance in ferroelectrics at room temperature. Nano Lett. 14, 3864–3868 (2014).

- Khan, A. I. et al. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 7, 182–186 (2015).

- Khan, A. I. et al. Negative capacitance in short-channel FinFETs externally connected to an epitaxial ferroelectric capacitor. *IEEE Electron Device Lett.* 37, 111–114 (2016).

- Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. Nat. Commun. 5, 5678 (2014).

- Li, L. K. et al. Black phosphorus field-effect transistors. Nat. Nanotechnol. 9, 372–377 (2014).

- Liu, H. et al. Phosphorene: an unexplored 2D semiconductor with a high hole mobility. ACS Nano 8, 4033–4041 (2014).

- Koenig, S. P., Doganov, R. A., Schmidt, H., Neto, A. H. C. & Özyilmaz, B. Electric field effect in ultrathin black phosphorus. *Appl. Phys. Lett.* **104**, 103106 (2014).

- Xia, F. N., Wang, H. & Jia, Y. Rediscovering black phosphorus: A unique anisotropic 2D material for optoelectronics and electronics. *Nat. Commun.* 5, 4458 (2014).

- Lam, K.-T., Dong, Z. & Guo, J. Performance limits projection of black phosphorous field-effect transistors. *IEEE Electron Device Lett.* 9, 963–965 (2014).

- Liu, F., Wang, Y. J., Liu, X. Y., Wang, J. & Guo, H. Ballistic transport in monolayer black phosphorus transistors. *IEEE Trans. Electron Devices* **11**, 3871–3876 (2014).

- International Technology Roadmap for Semiconductors. http://www.itrs2.net/ 2013-itrs.html (2013).

- 22. Rabe, K. M., Ahn, C. H. & Triscone, J. M. Topics in Applied Physics (Springer, 2007).

- Zhou, Y. Tunneling magnetoresistance modulation in a magnetic tunnel junction with a ferroelectric barrier. *Nanotechnology* 22, 085202 (2011).

- Zou, Y. Y., Chew, K. H. & Zhou, Y. Dynamic control of tunneling conductance in ferroelectric tunnel junctions. *Chinese Phys. Lett.* **30**, 107701 (2013).

- Zhou, Y., Chan, H. K., Lam, C. H. & Shin, F. G. Mechanisms of imprint effect on ferroelectric thin films. J. Appl. Phys. 98, 024111 (2005).

- Tyunina, M. & Levoska, J. Application of the interface capacitance model to thin-film relaxors and ferroelectrics. *Appl. Phys. Lett.* 88, 262904 (2006).

- Wood, J. D. et al. Effective passivation of exfoliated black phosphorus transistors against ambient degradation. Nano Lett. 14, 6964 (2014).

- Tayari, V. et al. Two-dimensional magnetotransport in a black phosphorus naked quantum well. Nat. Commun. 6, 7702 (2015).

- Doganov, R. A. *et al.* Transport properties of pristine few-layer black phosphorus by van der Waals passivation in an inert atmosphere. *Nat. Commun.* 6, 6647 (2015).

- Liu, F., Shi, Q., Wang, J. & Guo, H. Device performance simulations of multilayer black phosphorus tunneling transistors. *Appl. Phys. Lett.* **107**, 203501 (2015).

- Shi, Q., Guo, H. & Liu, F. Dielectric material for monolayer black phosphorus transistors: a first-principles investigation. *Proc. IEEE SISPAD* 56–59, doi:10.1109/SISPAD.2015.7292257 (2015).

- Lin, C. I., Khan, A. I., Salahuddin, S. & Hu, C. Effects of the variation of ferroelectric properties on negative capacitance FET characteristics. *IEEE Trans. Electron Devices* 63, 2197 (2016).

- Rudenko, A. N. & Katsnelson, M. I. Quasiparticle band structure and tight-binding model for single- and bilayer black phosphorus. *Phys. Rev. B* 89, 201408 (2014).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/ by/4.0/

© The Author(s) 2016