| Title       | Effects of thermal annealing on La2O3 gate dielectric of InGaZnO thin-film transistor                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)   | Huang, XD; Song, J; Lai, PT                                                                                                                                                                    |

| Citation    | ECS Solid State Letters, 2015, v. 4 n. 9, p. Q44-Q46                                                                                                                                           |

| Issued Date | 2015                                                                                                                                                                                           |

| URL         | http://hdl.handle.net/10722/234050                                                                                                                                                             |

| Rights      | ECS Solid State Letters. Copyright © Electrochemical Society,<br>Inc.; This work is licensed under a Creative Commons<br>Attribution-NonCommercial-NoDerivatives 4.0 International<br>License. |

# Effects of thermal annealing on La<sub>2</sub>O<sub>3</sub> gate dielectric of InGaZnO

## thin-film transistor

X. D. Huang<sup>a)</sup>

Key Laboratory of MEMS of the Ministry of Education, Southeast University, Nanjing 210096, China J. Q. Song and P. T. Lai<sup>a)</sup> Department of Electrical & Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong

**Abstract:** The effects of thermal annealing on  $La_2O_3$  gate dielectric of InGaZnO thin-film transistor (TFT) are investigated by varying annealing temperature. Due to densification and enhanced moisture resistance of the  $La_2O_3$  film, its surface roughness and interface with InGaZnO are improved by the thermal annealing, thus leading to significant improvement in the TFT electrical performance. However, higher-temperature (450 °C) annealing deteriorates the dielectric roughness and induces more traps associated with grain boundaries in the  $La_2O_3$  film. The TFT with an appropriate annealing (350 °C) shows the best performance with smallest sub-threshold swing (0.276 V/dec), lowest threshold voltage (3.01 V), highest field-effect mobility (23.2 cm<sup>2</sup>/V.s) and largest on-off current ratio (3.52×10<sup>8</sup>).

### a) Electronic mail: eexdhuang@gmail.com, laip@eee.hku.hk

Compared with conventional Si-based thin-film transistors (TFT), InGaZnO TFTs have advantages including low processing temperature, high field-effect mobility as well as good uniformity, and thus have received intensive attention over the last decade. <sup>1</sup> Recently, high-*k* dielectrics, such as Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, AlZrO and Lu<sub>2</sub>O<sub>3</sub>, have been widely investigated to replace SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub> as gate dielectrics in InGaZnO TFTs for improving their driving ability and reducing their operating voltage and power consumption. <sup>2-6</sup> Among various high-*k* materials, La<sub>2</sub>O<sub>3</sub> displays high dielectric constant (~ 30), large band gap (~ 6.0 eV) and good thermodynamic stability with InGaZnO, and thus should be a promising candidate as the gate dielectrics of InGaZnO TFTs. <sup>7,8</sup> It has been demonstrated that Ta incorporated in La<sub>2</sub>O<sub>3</sub> (LaTaO) can further improve the TFT performance by suppressing moisture absorption of the La<sub>2</sub>O<sub>3</sub> film; however, the TFT performance is quite sensitive to Ta content in the LaTaO film, thus leading to uniformity issues. <sup>8</sup> It must be noted that not only the dielectric itself but also the thermal and electrical characteristics of InGaZnO TFTs with La<sub>2</sub>O<sub>3</sub> gate dielectric prepared at different annealing temperatures.

TFT devices with bottom-gate top-contact configuration were fabricated on heavily p-type Si substrate. The substrate was cleaned by a standard RCA cleaning: firstly, the substrate was submerged in solution I (H<sub>2</sub>O:H<sub>2</sub>O<sub>2</sub>:NH<sub>4</sub>OH=5:1:1) at 80 °C for 10 min to remove organics and particles; then, the substrate was cleaned in solution II (H<sub>2</sub>O:H<sub>2</sub>O<sub>2</sub>:HCl=5:1:1) at 80 °C for 10 min to remove metallic contaminants; finally, the substrate was dipped in 2% hydrofluoric acid for 1 min to remove native oxide. After the cleaning, 40-nm La<sub>2</sub>O<sub>3</sub> was deposited on the substrate by radio-frequency sputterer using a La<sub>2</sub>O<sub>3</sub> target in an Ar/O<sub>2</sub> ambient. Then, the samples were divided into four groups: two of the groups went through post-deposition annealing (PDA) in N<sub>2</sub> at 350 °C and 450 °C for 10 min respectively, denoted as LaO\_350 and LaO\_450 samples; the third and fourth groups did not receive PDA, denoted as the as\_deposited and control samples respectively. Following that, a 60-nm IGZO active layer was deposited by sputterer using an InGaZnO target in an Ar/O<sub>2</sub> ambient. Then, source/drain (S/D) electrodes consisting of 20-nm Ti/80-nm Au were formed by electron-beam evaporation combined with lift-off technique, where Ti was used to enhance the electrode adhesion and also reduce the barrier height between the electrodes and InGaZnO. The channel width (*W*) and length (*L*) were 100 µm and 20 µm

respectively. Finally, the LaO\_350, LaO\_450 and control samples received a post-metallization annealing (PMA) in forming gas ( $H_2/O_2=5\%/95\%$ ) at 350 °C for 20 min to improve the electrical contacts. The samples with different annealing conditions are summarized in Table 1.

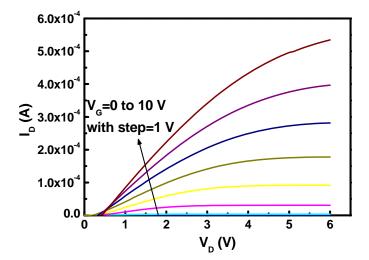

Fig. 1 shows the X-ray diffraction (XRD) patterns of the samples with various annealing conditions measured under theta-theta mode, where all the samples display a polycrystalline structure and consists of La<sub>2</sub>O<sub>3</sub> and La(OH)<sub>3</sub> in the La<sub>2</sub>O<sub>3</sub> film. La(OH)<sub>3</sub> is formed by the reaction of La<sub>2</sub>O<sub>3</sub> with moisture due to the hydroscopic nature of La<sub>2</sub>O<sub>3</sub>. <sup>8</sup> For the LaO\_350 and LaO\_450 samples, the peak (3 1 1) of La(OH)<sub>3</sub> decreases significantly relative to that of the sample with no PDA, indicating suppressed formation of La(OH)<sub>3</sub> and thus enhanced moisture resistance of La<sub>2</sub>O<sub>3</sub> by the thermal annealing. In addition, compared with the LaO\_350 sample, the intense peak (1 1 0) attributed to La<sub>2</sub>O<sub>3</sub> component for the LaO\_450 sample exhibits stronger intensity and smaller FWHM (full width at half maximum), indicating more crystallized structure with larger grain size and more grain boundaries induced by the higher-temperature annealing. Moreover, compared with the LaO\_350 sample, the dielectric film, thus enhancing the formation of La(OH)<sub>3</sub>.

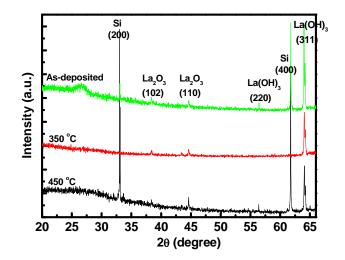

Fig. 2 shows the atomic force microscopy (AFM) images of the samples, where the root-mean-square (RMS) roughness is 1.39 nm, 0.90 nm and 1.11 nm for the as\_deposited, LaO\_350 and LaO\_450 samples respectively. Both of the LaO\_350 and LaO\_450 samples have smoother surface than the as\_deposited one because of densification as well as enhanced moisture resistance of the La<sub>2</sub>O<sub>3</sub> film induced by the thermal annealing, which is helpful to suppress the volume expansion of the La<sub>2</sub>O<sub>3</sub> film caused by moisture absorption and thus the formation of La(OH)<sub>3</sub>. <sup>8</sup> Moreover, the rougher surface of the LaO\_450 sample than the LaO\_350 one is mainly ascribed to larger grain size induced by the higher-temperature annealing.

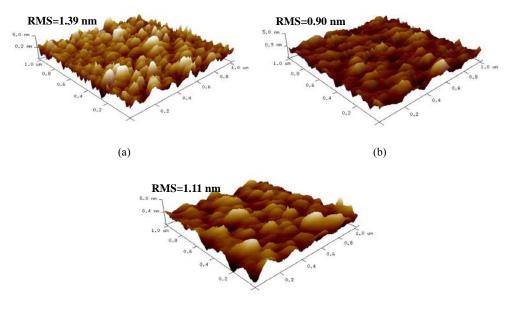

Fig. 3 shows the transfer characteristics of the devices. The sub-threshold swing SS, saturation carrier mobility  $\mu_{sat}$ , threshold voltage  $V_{th}$ , on-current  $I_{on}$  (defined as  $I_D$  at  $V_G = 10$  V and  $V_D = 5$  V) and on-off current ratio  $I_{on}/I_{off}$  of the devices are extracted from Fig. 3 and summarized in Table 2. In terms of the parameters listed in Table 2, the control sample shows better performance than the as\_deposited one mainly due to the improved electrical contacts and InGaZnO film by PMA. Moreover, the LaO\_350 and LaO\_450 samples exhibit much better performance than the control one, suggesting that PDA plays a key role in the device performance.

The smaller SS of the LaO 350 and LaO 450 samples (LaO  $350 \sim 0.276$  V/dec; LaO  $450 \sim 0.276$  V 411V/dec) than the control one (~ 2.11 V/dec) suggests fewer interface states at the dielectric/semiconductor interface, demonstrating that the thermal annealing can effectively improve the interface quality by densifying the dielectric film and improving the interface roughness. Additionally, for the LaO 350 and LaO 450 samples, the better dielectric /semiconductor interface with fewer interface states can suppress the trapping of charge carriers and the trap-related scattering of charge carriers in the conduction channel, thus resulting in lower  $V_{th}$  (LaO\_350 ~ 3.01 V; LaO\_450 ~ 4.01 V; control ~ 5.00 V) and higher  $\mu_{sat}$  (LaO\_350 ~ 23.2  $cm^2/V.s$ ; LaO\_450 ~ 5.63  $cm^2/V.s$ ; control ~ 2.11  $cm^2/V.s$ ) than the control one. Moreover, it is known that the by-product  $La(OH)_3$  formed by the reaction of  $La_2O_3$  with moisture increases the negative charge in the dielectric film due to OH<sup>-</sup> replacing O<sup>2-</sup>.<sup>9</sup> This increased negative charge density in the dielectric film screens the electric field from the gate, and thus larger gate voltage is required to induce a conduction channel; also, the increased charge density can induce Coulombic scattering on the charge carriers, thus degrading  $\mu_{sat}$ . Consequently, the suppressed formation of  $La(OH)_3$  for the LaO\_350 and LaO\_450 samples further contributes to their lower V<sub>th</sub> and higher  $\mu_{sat}$ . Owing to the lower  $V_{th}$  and higher  $\mu_{sat}$ , the LaO\_350 and LaO\_450 samples achieve much higher  $I_{on}$  (LaO\_350 ~ 495  $\mu$ A; LaO\_450 ~ 118  $\mu$ A) than that of the control one (~ 24.7  $\mu$ A). Moreover, the higher Ion and suppressed off-state leakage path by thermal annealing of the LaO\_350 and LaO\_450 samples lead to higher  $I_{on}/I_{off}$  ratio (LaO\_350 ~ 3.52×10<sup>8</sup>; LaO\_450 ~  $4.29 \times 10^6$ ) than the control one (~  $1.72 \times 10^6$ ). The control sample displays much larger current under negative  $V_G$  than the other samples. For the control sample, the PMA would lead to Ti diffusion in the gate dielectric film, thus degrading the quality of the dielectric film and resulting in large leakage current under negative V<sub>G</sub>.<sup>10</sup> The as\_deposited sample did not receive PMA, thus leading to smaller leakage under negative  $V_G$  than the control one. Although the LaO\_350 and LaO 450 samples received the same PMA as the control one, the PDA before the PMA could densify the dielectric film, thus suppressing the Ti diffusion in the dielectric film. Therefore, they also have smaller leakage than the control one. The above analysis needs to be further confirmed. Compared with the LaO 350 sample, the LaO 450 one with higher annealing temperature displays worse performance mainly due to larger grains formed in the dielectric at higher annealing temperature, resulting in more traps along the grain boundaries as well as degraded

dielectric/semiconductor interface associated with rougher dielectric film (shown in AFM results in Fig. 2). <sup>7</sup> Therefore, it is believed that the superior performance of the LaO\_350 sample is mainly ascribed to the high quality of both the dielectric bulk itself and its interface with the semiconductor achieved by appropriate annealing temperature. Moreover, the LaO\_350 sample displays similar  $\mu_{sat}$  (~ 23.2 cm<sup>2</sup>/V.s) as that (~ 23.4 cm<sup>2</sup>/V.s) of the TFT with LaTaO gate dielectric, but much higher  $I_{on}/I_{off}$  ratio (~ 3.52×10<sup>8</sup>) than the latter (~ 2.60×10<sup>7</sup>), demonstrating that the appropriate annealing is an effective way to improve the TFT performance.<sup>8</sup>

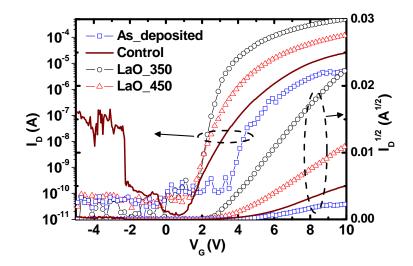

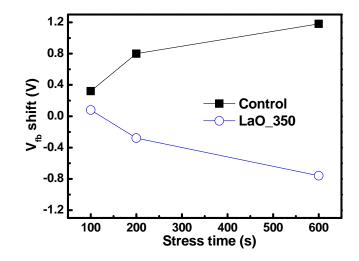

Fig. 4(a) shows the  $V_{th}$  shift ( $\Delta V_{th}$ ) of the samples as a function of stress time under positive gate-bias stress (PGBS). The  $V_{th}$  of the control sample exhibits a positive shift with increasing stress time. However, the LaO\_350 sample displays a positive  $V_{th}$  shift initially, but then a negative V<sub>th</sub> shift with the stress time. There are two mechanisms responsible for V<sub>th</sub> shift under PGBS: electrons move towards the InGaZnO/dielectric interface and are trapped at the interface (denoted as electron trapping), leading to reduced electrons in the InGaZnO film and thus positive V<sub>th</sub> shift; On the other hand, adsorbed H<sub>2</sub>O molecules on the back channel can act as donors (denoted as electron injection), resulting in increased electrons in the InGaZnO film and thus negative V<sub>th</sub> shift. <sup>11</sup> It is known that OH group at dielectric interface usually acts as electron trap. <sup>12</sup> Due to severer moisture absorption of the La<sub>2</sub>O<sub>3</sub> film for the control sample, it has much more OH<sup>-</sup> groups than the LaO 350 one. Therefore, electron trapping at the dielectric/semiconductor interface is dominant over electron injection from the back channel under PGBS for the control sample, thus leading to the continual positive  $\Delta V_{th}$  with the stress time and severer  $V_{th}$  instability. For the LaO sample, the insertion of a passivation layer between the InGaZnO and ambient should effectively suppress the V<sub>th</sub> instability by blocking the H<sub>2</sub>O adsorption on the back channel. Fig. 4(b) shows the output characteristics of the LaO 350 sample, where a high drain current of 534  $\mu$ A can be obtained with the device biased at V<sub>G</sub> = 10 V and V<sub>D</sub> = 6V, demonstrating its strong driving ability for high-speed applications. The current crowding at low  $V_D$  should be due to parasitic resistance from the source/drain contacts.<sup>13</sup>

In summary, the impact of thermal annealing on La<sub>2</sub>O<sub>3</sub> gate dielectric of InGaZnO TFT has been studied. Compared with the TFT with no or higher-temperature (450 °C) PDA, the one with suitable annealing temperature (350 °C) displays better electrical performance mainly due to smoother dielectric/semiconductor interface with fewer interface states as well as higher quality of the bulk dielectric film with lower charge density and fewer grain boundaries. Therefore,  $La_2O_3$  film with appropriate thermal annealing is a promising gate dielectric for high-performance InGaZnO TFT.

Acknowledgments This work was financially supported by the Natural Science Foundation of Jiangsu Province (No. BK20140639), the Fundamental Research Funds for the Central Universities (No. 2242014K10016), RGC of HKSAR, China (No. HKU 17203814) and the University Development Fund (Nanotechnology Research Institute, No. 00600009) of the University of Hong Kong.

#### Reference

- 1) T. Kamiya, K. Nomura, and H. Hosono, Sci. Technol. Adv. Mater., 11, 044305 (2010).

- 2) C. J. Chiu, S. P. Chang, and S. J. Chang, IEEE Electron Device Lett., 31,1245 (2010)

- 3) J. S. Lee, S. Chang, S. M. Koo, and S. Y. Lee, IEEE Electron Device Lett., 31, 225 (2010).

- 4) T. M. Pan, C. H. Chen, J. L. Her, and K. Koyama, J. Appl. Phys., 116, 194510 (2014).

- 5) I. K. Lee, S. W. Lee, J. G. Gu, K. S. Kim, and W. J. Cho, Jpn. J. Appl. Phys., **52**, 06GE05 (2013).

- 6) Y. Gao, X. Li, L. Chen, J. Shi, X. Wei, and J. Zhang, IEEE Electron Device Lett., **35**, 554 (2014).

- 7) J. Robertson, Rep. Prog. Phys., 69, 327(2006).

- 8) L. X. Qian, P. T. Lai, and W. M, Tang, Appl. Phys. Lett., 104, 123505 (2014).

- 9) J. Molina, K. Tachi, K. Kakushima, P. Ahmet, K. Tsutsui, N. Sugii, T. Hattori, and H. Iwai, J. Electrochem. Soc., **154**, G110 (2007).

- S. H. Choi, M. H. Lim, W. S. Jung, and J. H. Park, IEEE Electron Device Lett., 35, 835 (2014).

- F. H. Chen, T. M. Pan, C. H. Chen, J. H. Liu, W. H. Lin, and P. H. Chen, IEEE Electron Device Lett., 34, 635 (2013).

- 12) S. Owgawa, Y. Kimura, and M. Niwano, Appl. Phys. Lett., 90, 033504 (2007).

- 13) M. C. Hamilton, S. Martin, and J. Kanicki, IEEE Trans. Electron Device, 51, 877 (2004).

## Captions

- Fig. 1. XRD patterns of the  $La_2O_3$  films on the Si substrate with various annealing temperatures, where the diffraction peaks are also indexed (JCPDS No. 40–1281; 06–0588).

- Fig. 2. AFM images of the La<sub>2</sub>O<sub>3</sub> films on the Si substrate with various annealing temperatures: (a) as-depostied, (b) 350 °C and (c) 450 °C.

Fig. 3. Transfer characteristics of the TFTs with various annealing conditions.

- Fig. 4. (a)  $\Delta V_{th}$  of the control and LaO\_350 samples as a function of stress time under PGBS (V<sub>GS</sub>=+7

- V, V<sub>DS</sub>=0 V). (b) Output characteristics of the LaO\_350 sample.

| Sample | As_deposited | Control        | LaO_350        | LaO_450        |

|--------|--------------|----------------|----------------|----------------|

| PDA    | no           | no             | 350 °C, 10 min | 450 °C, 10 min |

| PMA    | no           | 350 °C, 20 min | 350 °C, 20 min | 350 °C, 20 min |

Table 1. Comparison of the annealing conditions for each sample

| Sample                             | As_deposited         | Control              | LaO_350              | LaO_450              |

|------------------------------------|----------------------|----------------------|----------------------|----------------------|

| SS (V/dec)                         | 0.456                | 0.454                | 0.276                | 0.411                |

| $\mu_{sat}$ (cm <sup>2</sup> /V.s) | 0.623                | 2.11                 | 23.2                 | 5.63                 |

| V <sub>th</sub> (V)                | 5.22                 | 5.01                 | 3.01                 | 4.02                 |

| $I_{on}\left(\mu A\right)$         | 5.13                 | 24.7                 | 495                  | 118                  |

| $I_{on}/I_{off}$                   | $8.44 \times 10^{5}$ | $1.72 \times 10^{6}$ | 3.52×10 <sup>8</sup> | $4.29 \times 10^{6}$ |

Table 2. Key parameters extracted from the transfer characteristics in Fig. 3 for the TFTs.

Fig. 1 X.D. Huang

Fig. 2 X.D. Huang

(c)

Fig. 3 X.D. Huang

Fig. 4 X.D. Huang

(a)