# IMPROVING LINEARITY UTILISING ADAPTIVE PREDISTORTION FOR POWER AMPLIFIERS AT mm-WAVE FREQUENCIES

by

# Joe Valliarampath

Submitted in partial fulfilment of the requirements for the degree

**Philosophiae Doctor (Electronic Engineering)**

in the

Department of Electrical, Electronic and Computer Engineering

Faculty of Engineering, Built Environment and Information Technology

UNIVERSITY OF PRETORIA

April 2014

#### **SUMMARY**

# IMPROVING LINEARITY UTILISING ADAPTIVE PREDISTORTION FOR POWER AMPLIFIERS AT mm-WAVE FREQUENCIES

by

# Joe Valliarampath

Supervisor: Prof. S Sinha

Department: Electrical, Electronic and Computer Engineering

University: University of Pretoria

Degree: Philosophiae Doctor (Electronic Engineering)

Keywords: Linearisation techniques, predistortion, power amplifiers, millimetre

wave integrated circuits, silicon germanium, heterojunction bipolar

transistor, BiCMOS integrated circuits, intermodulation distortion.

The large unlicensed 3 GHz overlapping bandwidth that is available worldwide at 60 GHz has resulted in renewed interest in 60 GHz technology. This frequency band has made it attractive for short-range gigabit wireless communication. The power amplifier (PA) directly influences the performance and quality of this entire communication chain, as it is one of the final subsystems in the transmitter. Spectral efficient modulation schemes used at 60 GHz pose challenging requirements for the linearity of the PA. To improve the linearity, several external linearisation techniques currently exist, such as feedback, feedforward, envelope elimination and restoration, linear amplification with non-linear components and predistortion.

This thesis is aimed at investigating and characterising the distortion components found in PAs at mm-wave frequencies and evaluating whether an adaptive predistortion (APD) linearisation technique is suitable to reduce these distortion components. After a thorough literature study and mathematical analysis, it was found that the third-order intermodulation distortion (IMD3) components were the most severe distortion components. Predistortion was identified as the most effective linearisation technique in terms of minimising these IMD3 components and was therefore proposed in this research. It does not introduce additional complexity and can easily be integrated with the PA.

Furthermore, the approach is stable and has lower power consumption when compared to the aforementioned linearisation techniques. The proposed predistortion technique was developed compositely through this research by making it a function of the PA's output power that was measured using a power detector. A comparator was used with the detected output power and the reference voltages to control the dynamic bias circuit of the variable gain amplifier. This provided control and flexibility on when to apply the predistortion to the PA and therefore allowing the linearity of the PA to be optimised. Three-stage non-linear and linear PAs were also designed at 60 GHz and implemented to compare the performance of the APD technique and form part of the hypothesis verification process.

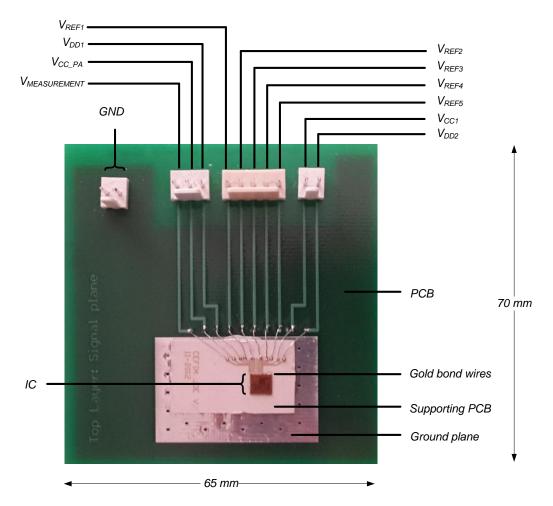

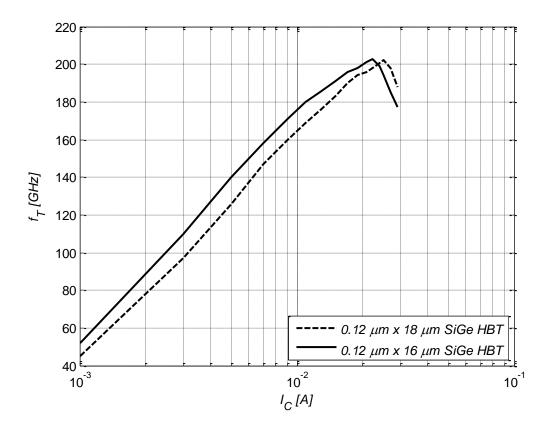

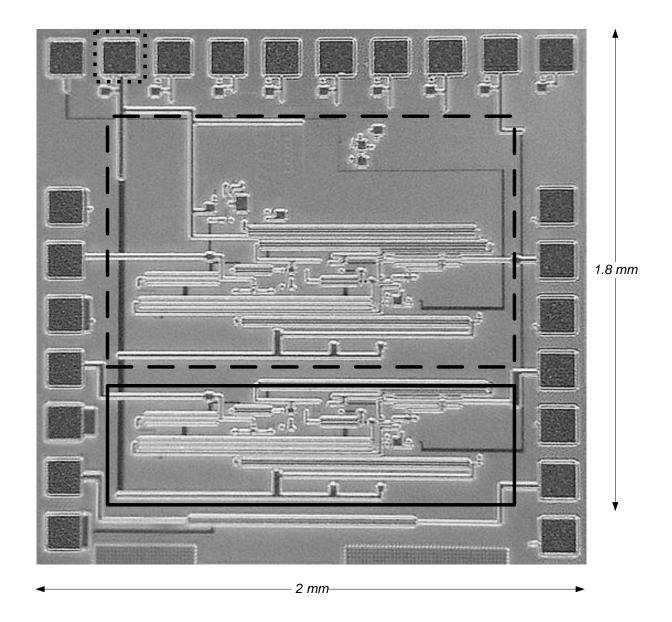

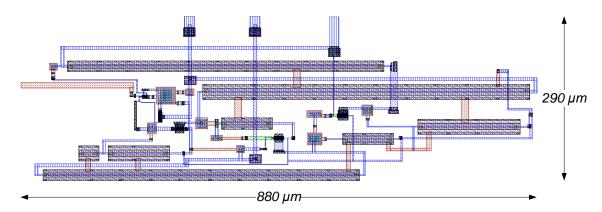

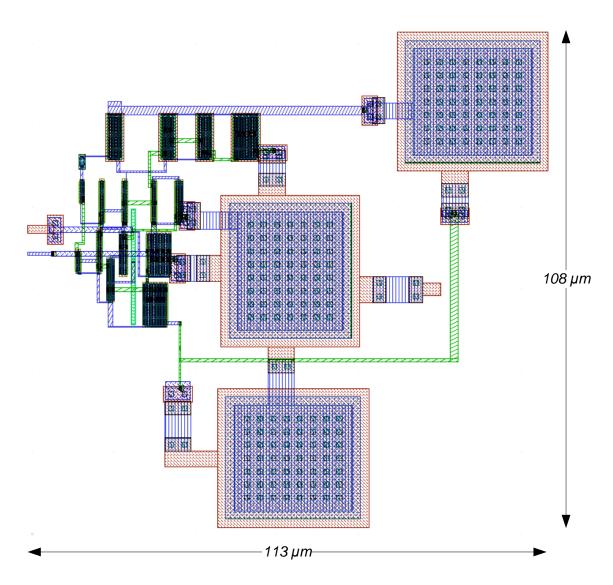

The 130 nm silicon-germanium (SiGe) bipolar and complementary metal oxide semiconductor (BiCMOS) technology from IBM was used for the simulation of the entire APD and PA design and for the fabrication of the prototype integrated circuits (ICs). This technology has the advantage of integrating the high performance, low power intensive SiGe heterojunction bipolar transistors (HBTs) with the CMOS technology. The SiGe HBTs have a high cut-off frequency ( $f_T > 200$  GHz), which is ideal for mm-wave PA applications and the CMOS components were integrated in the control logic of the digital circuitry. The simulations and IC layout were accomplished with Cadence Virtuoso. The implemented IC occupies an area of 1.8 mm by 2.0 mm.

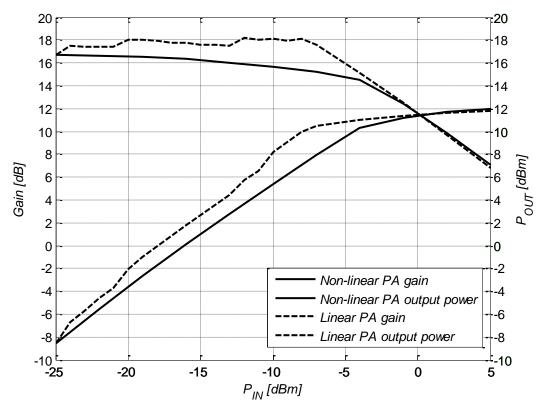

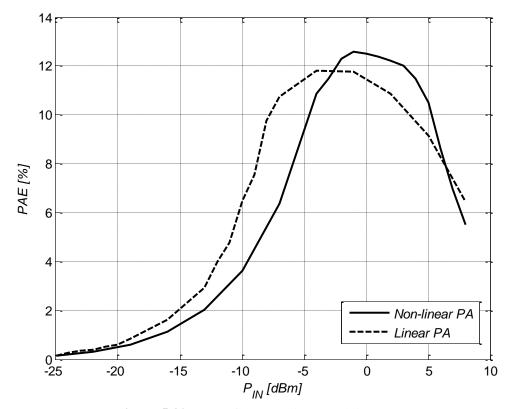

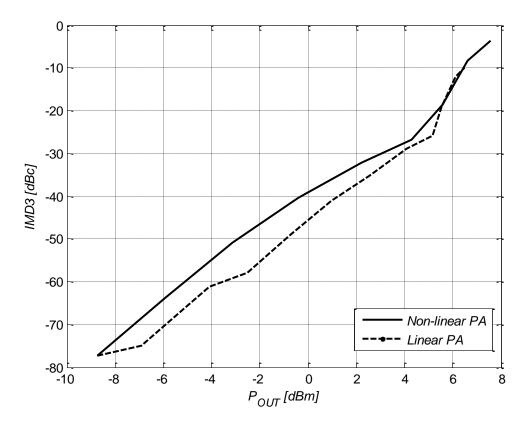

The non-linear PA achieves a  $P_{SAT}$  of 11.97 dBm and an  $IP_{1\,dB}$  of -10 dBm. With the APD technique applied, the linearity of the PA is significantly improved with an  $IP_{1\,dB}$  of -6 dBm and an optimum IMD3 reduction of 10 dB. Based on the findings and results of the applied APD technique, APD reduced intermodulation distortion (especially the IMD3) and is thus suitable to improve the linearity of PAs at mm-wave frequencies. To the knowledge of this author, no APD technique has been applied for PAs at 60 GHz, therefore the contribution of this research will assist future PA designers to characterise and optimise the reduction of the IMD3 components. This will result in improved linear output power from the PA and the use of complex modulation schemes at 60 GHz.

#### **OPSOMMING**

# VERBETERING VAN LINEARITEIT DEUR DIE GEBRUIK VAN AANPASSENDE PREDISTORSIE VIR DRYWINGSVERSTERKERS BY mm-GOLFFREKWENSIES

#### deur

# Joe Valliarampath

Studieleier: Prof S. Sinha

Departement: Elektriese, Elektroniese en Rekenaaringenieurswese

Universiteit: Universiteit van Pretoria

Graad: Philosophiae Doctor (Elektroniese Ingenieurswese)

Sleutelwoorde: Linearisasietegniek, predistorsie, drywingsversterker, millimetergolf

geïntegreerde stroombaan, silikon-germanium, heterovoegvlakbipolêre transistors, BiCMOS geïntegreerde stroombaan,

intermodulasiedistorsie.

Die groot ongelisensieerde oorvleuelde bandwydte van 3 GHz wat wêreldwyd by 60 GHz beskikbaar is, het hernude belangstelling in 60 GHz-tegnologie tot gevolg gehad. Hierdie frekwensieband het dit aantreklik gemaak vir kortafstand-gigabis draadlose kommunikasie. Aangesien die drywingsversterker een van die finale subsisteme in die seintoestel is, het dit 'n direkte invloed op die werkverrigting en kwaliteit van die hele kommunikasieketting. Spektraaldoeltreffende modulasieskemas wat by 60 GHz gebruik word, stel uitdagende vereistes vir die lineariteit van die drywingsversterker. Om die lineariteit te verbeter, is daar tans verskeie eksterne linearisasietegnieke beskikbaar, soos terugvoer, vooruitvoer, omhullende eliminasie en -restorasie, lineêre versterking met nie-lineêre komponente en predistorsie.

Hierdie tesis het ten doel om die distorsiekomponente wat by millimetergolffrekwensies in drywingsversterkers gevind word, te ondersoek en te karakteriseer en om te bepaal of 'n aanpassende predistorsielinearisasietegniek geskik is om hierdie distorsiekomponente te verminder. Na 'n deeglike literatuurstudie en wiskundige analise is gevind dat die derdeorde-intermodulasiedistorsiekomponente (IMD3) die ergste distorsiekomponente was.

Predistorsie is geïdentifiseer as die mees effektiewe linearisasietegniek om hierdie IMD3-komponente te minimeer en die gebruik daarvan is gevolglik in hierdie navorsing voorgestel. Dit bring nie addisionele kompleksiteit mee nie en kan maklik met die drywingsversterker geïntegreer word. Daarbenewens is die benadering stabiel, met laer kragverbruik in vergelyking met die linearisasietegnieke wat voorheen genoem is. Die voorgestelde predistorsietegniek is in hierdie navorsing ontwikkel deur dit 'n funksie van die drywingsversterker se uitsetkrag te maak, wat gemeet is deur 'n kragdetektor te gebruik. 'n Vergelyker is saam met die gemete uitsetkrag en die verwysingspannings gebruik om die dinamiese voorspanningsbaan van die veranderlike winsversterker te beheer. Dit het toegelaat vir beheer en buigsaamheid in die aanwending van die predistorsie op die drywingsversterker en gevolglik vir die optimering van die lineêriteit van die drywingsversterker. Driefase- nie-lineêre en lineêre drywingsversterkers is ook by 60 GHz ontwerp en geïmplementeer om die werkverrigting van die aanpassende predistorsietegniek te vergelyk en dit vorm deel van die verifikasieproses van die hipotese.

Die 130 nm-silikon-germanium (SiGe) bipolêre en metaaloksiedhalfgeleier- (BiCMOS) tegnologie van IBM is gebruik vir die simulasie van die hele aanpassende predistorsietegniek- en drywingsversterkerontwerp en vir die vervaardiging van die prototipe- geïntegreerde stroombane. Hierdie tegnologie het die voordeel dat dit die hoë werkverrigting en lae krag-intensiewe SiGe-heterovoegvlak-bipolêre transistors (HBTs) met die CMOS-tegnologie integreer. Die SiGe-HBTs het 'n hoë afsnyfrekwensie ( $f_T > 200 \text{ GHz}$ ), wat ideaal is vir mm-golfdrywingsversterkeraanwendings en die CMOS-komponente is in die beheer-logika van die digitale stroombaan geïntegreer. Die geïntegreerde stroombaan beslaan 'n area van 1.8 mm by 2.0 mm.

Die nie-lineêre drywingsversterker behaal 'n  $P_{SAT}$  van 11.97 dBm en 'n  $IP_{1 \text{ dB}}$  van -10 dBm. As die APD-tegniek toegepas word, word die lineariteit van die drywingsversterker beduidend verbeter tot 'n  $IP_{1 \text{ dB}}$  van -6 dBm en 'n optimum-IMD3-vermindering van 10 dB. Volgens die bevindings en resultate van die APD-tegniek wat toegepas is, verminder APD intermodulasiedistorsie (veral die IMD3) en is gevolglik geskik om die lineariteit van drywingsversterkers by mm-golffrekwensies te verbeter. Na die wete van hierdie skrywer is daar nie voorheen enige APD tegniek toegepas vir drywingsversterkers by 60 GHz nie, gevolglik sal die bydrae van hierdie navorsing toekomstige drywingsversterkerontwerpers help om die vermindering van die IMD3-komponente te karakteriseer en optimeer. Dit sal

verbeterde lineêre uitsetkrag van die drywingsversterker tot gevolg hê, asook meer komplekse modulasieskemas by 60 GHz toelaat.

#### **ACKNOWLEDGEMENT**

To God for this wonderful life.

To my wonderful wife, Liz. Thank you for your patience, your continuous support, for putting a smile on my face and for always believing in me and encouraging me. Thank you to my parents, Thomas and Tessy Valliarampath, for instilling within me from a young age the passion to always question, investigate and to never stop learning. To my sisters, Fabin and Mereen, and my brothers, Tim and Tom, thank you for your love and support.

To my dear friend Reuben Abraham who passed away, you will always be loved and remembered. To Philip Zachariah and Seema Mathew, thank you for those interesting engineering questions.

I have been very privileged to be advised and guided by a study leader and mentor such as Prof. Saurabh Sinha. Thank you for your constant support, encouragement and for being a source of inspiration providing the most insightful ideas and thought-provoking questions.

To Metal Oxide Semiconductor Implementation Service (MOSIS) for sponsoring the multi-project wafer run to fabricate my design and to the National Research Foundation in South Africa for partially sponsoring this work. To Dr Tinus Stander for his helpful advice and support with the PCB design. To Denel Dynamics for making the wire bonder available to me for wirebonding. To Johan Schoeman and Ms. Nel for their help in translating the summary into Afrikaans. To my Carl and Emily Fuchs Institute for Microelectronics (CEFIM) colleagues Antonie Alberts, Reeshen Reddy, Johny Sebastian, Dr Deepa George and Dr Jannes Venter for their advice and friendship.

# TABLE OF CONTENTS

| CHAP | TER  | 1 INTRODUCTION                           | 1  |

|------|------|------------------------------------------|----|

| 1.1  | BA   | CKGROUNG TO THE RESEARCH                 | 1  |

| 1.2  | RE   | SEARCH PROBLEM AND HYPOTHESIS            | 2  |

| 1.3  | JU   | STIFICATION FOR THE RESEARCH             | 4  |

| 1.4  | ME   | ETHODOLOGY                               | 5  |

| 1.5  | OU   | TLINE OF THE THESIS                      | 5  |

| 1.6  | DE   | LIMITATIONS OF THE SCOPE OF THE RESEARCH | 6  |

| 1.7  |      | NTRIBUTION TO THE FIELD                  |    |

| 1.8  | PU   | BLICATION LEADING FROM THIS RESEARCH     | 9  |

| 1.9  | CO   | NCLUSION                                 | 10 |

| CHAP |      | 2 LITERATURE REVIEW                      |    |

| 2.1  | IN   | TRODUCTION                               | 11 |

| 2.2  | PO   | WER AMPLIFIERS                           | 11 |

| 2.2  | 2.1  | PA class of operation                    |    |

| 2.2  | 2.2  | PA topologies                            |    |

| 2.2  | 2.3  | Output power                             |    |

| 2.2  | 2.4  | Power matching                           |    |

| 2.2  | 2.5  | Power efficiency                         |    |

| 2.2  | 2.6  | Modulation schemes                       |    |

|      | 2.7  | Non-linear phenomena in PA               |    |

|      | 2.8  | Harmonic distortion                      |    |

|      | 2.9  | IM distortion                            |    |

|      | 2.10 | Gain compression                         |    |

| 2.2  | 2.11 | AM-AM and AM-PM distortion               |    |

| 2.3  |      | N-LINEARITY COMPONENTS IN SIGE HBT       |    |

| 2.4  |      | MICONDUCTOR TECHNOLOGIES                 |    |

|      | 4.1  | Active devices                           |    |

|      | 4.2  | Passive devices                          |    |

| 2.4  | 4.3  | Layout and parasitics                    |    |

| 2.5  |      | MODELLING                                |    |

|      | 5.1  | Quasi-memory-less non-linear model       |    |

|      | 5.2  | Memory effect non-linear model           |    |

| 2.6  |      | DUCING DISTORTION IN PAS                 |    |

| 2.0  | 6.1  | Predistortion linearisation operation    |    |

| 2.0  | 6.2  | Types of predistortion                   | 37 |

| 2.7  | CO  | NCLUSION                                     | 40  |

|------|-----|----------------------------------------------|-----|

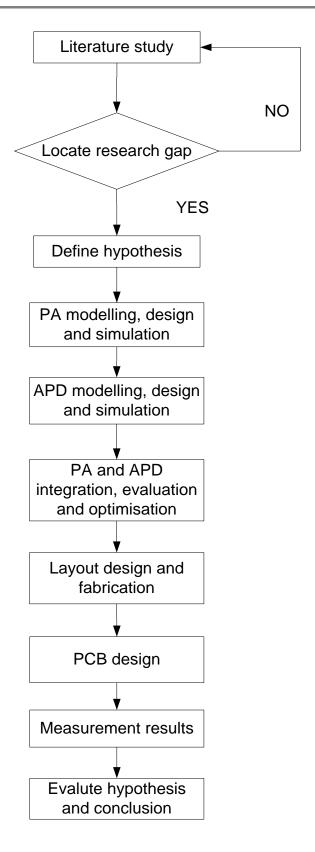

| CHAP | ΓER | 3 RESEARCH METHODOLOGY                       | 41  |

| 3.1  | INT | FRODUCTION                                   | 41  |

| 3.2  | JUS | STIFICATION FOR THE PARADIGM AND METHODOGOLY | 41  |

| 3.3  | OU  | TLINE OF THE METHODOLOGY                     | 41  |

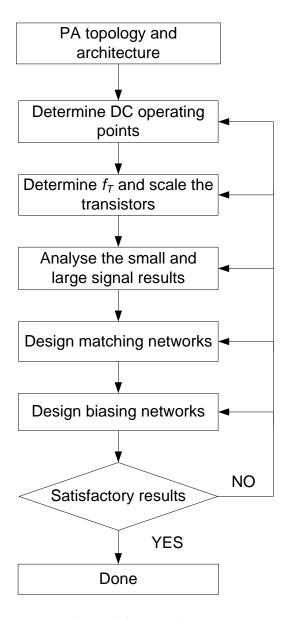

| 3.4  | PA  | AND APD DESIGN METHODOLOGY                   | 44  |

| 3.5  | SIN | MULATION SOFTWARE                            | 46  |

| 3.6  | MA  | ANUFACTURING PROCESS                         | 48  |

| 3.6  | 5.1 | SiGe HBTs                                    | 49  |

| 3.6  | 5.2 | MIM capacitors                               | 50  |

| 3.6  | 5.3 | TLs                                          | 50  |

| 3.7  | ME  | ASUREMENT EQUIPMENT                          | 51  |

| 3.8  | ME  | ASUREMENT SETUP                              | 55  |

| 3.9  | CO  | NCLUSION                                     | 58  |

| CHAP | ГER | 4 MATHEMATICAL ANALYSIS                      | 59  |

| 4.1  | INT | TRODUCTION                                   | 59  |

| 4.2  | MA  | ATHEMATICAL ANALYSIS                         | 59  |

| 4.3  | CO  | NCLUSION                                     | 65  |

| CHAP | ΓER | 5 PA AND APD DESIGN AND RESULTS              | 66  |

| 5.1  | INT | TRODUCTION                                   | 66  |

| 5.2  | PA  | AND VGA                                      | 66  |

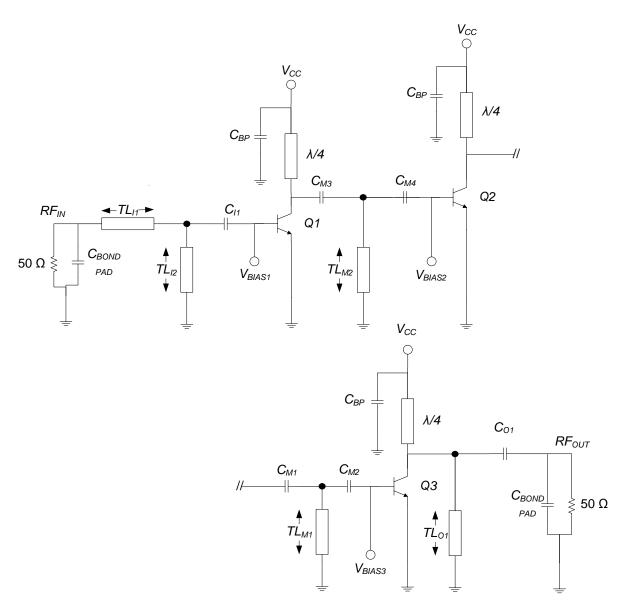

| 5.2  | 2.1 | PA and VGA design                            | 67  |

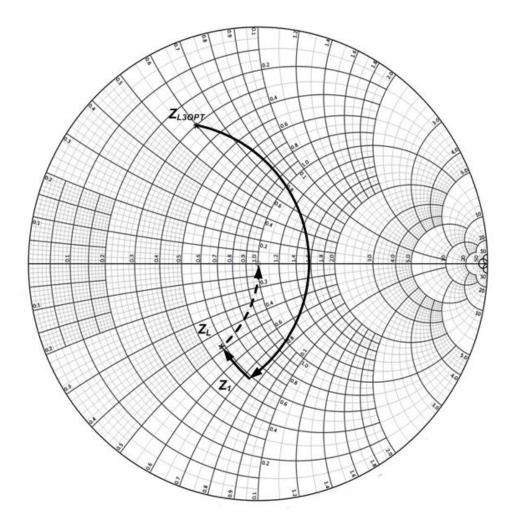

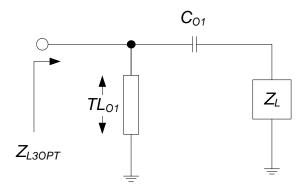

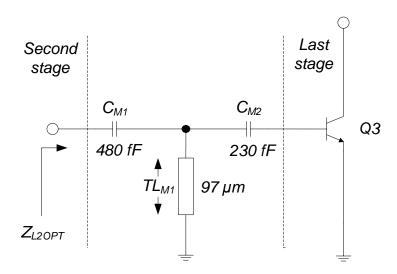

| 5.2  | 2.2 | Matching networks                            |     |

| 5.2  | 2.3 | Biasing network                              | 76  |

| 5.2  | 2.4 | Final PA schematic                           | 78  |

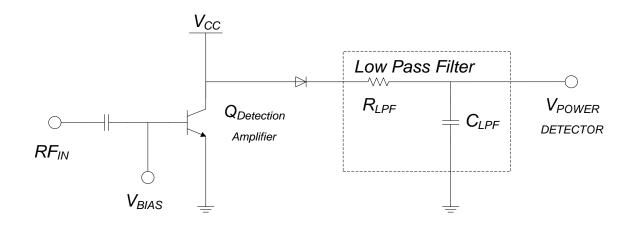

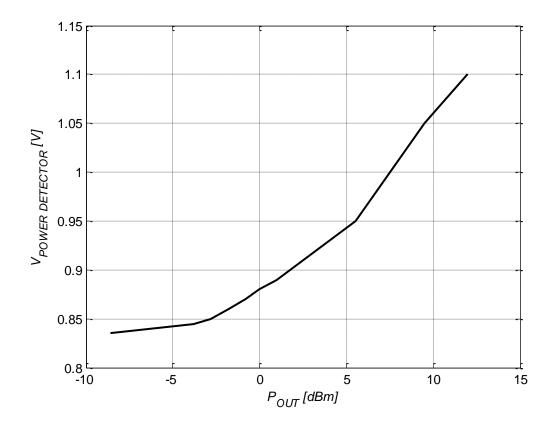

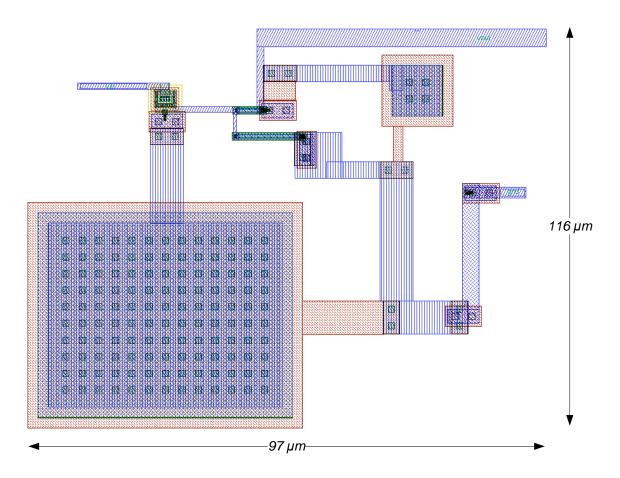

| 5.3  | PO  | WER DETECTOR                                 | 79  |

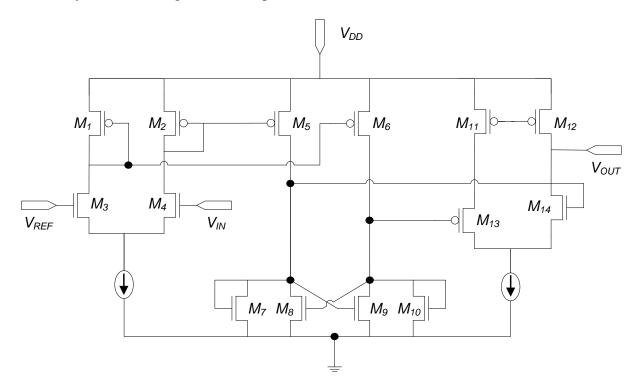

| 5.4  | AD  | C                                            | 81  |

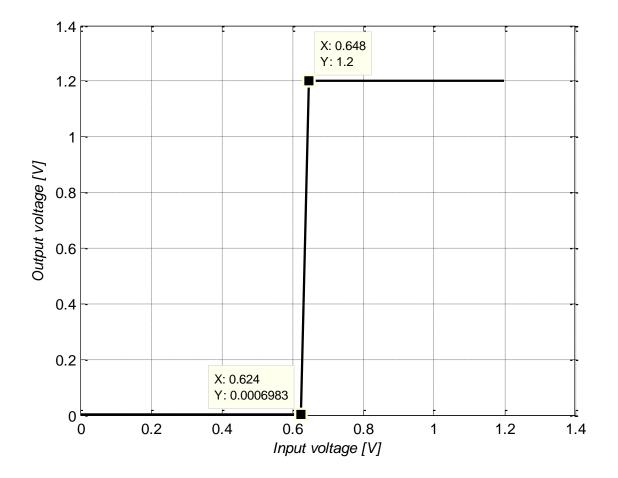

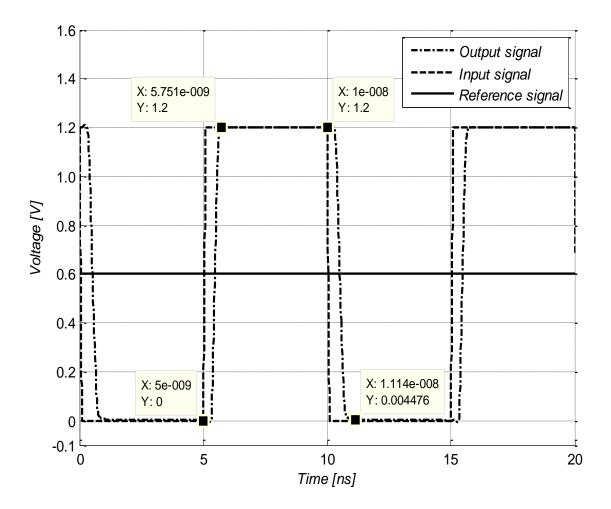

| 5.4  | 1.1 | Comparator                                   | 81  |

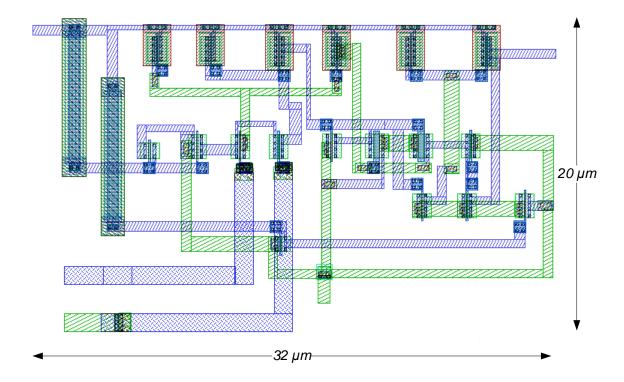

| 5.5  | CO  | NTROL LOGIC SUBSYSTEMS                       | 84  |

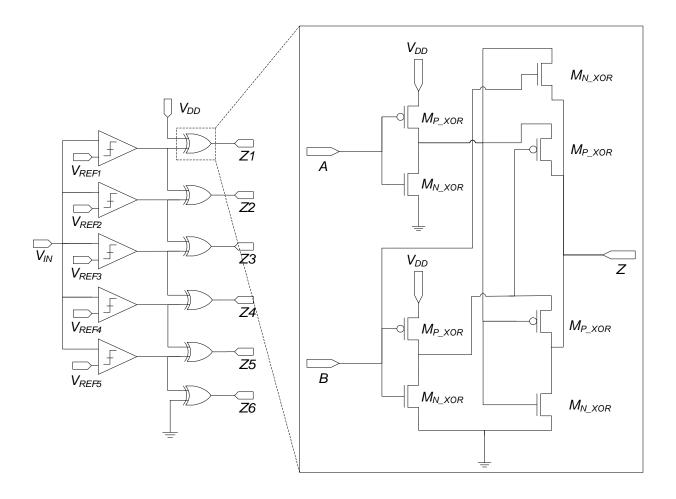

| 5.5  | 5.1 | XOR gates                                    | 85  |

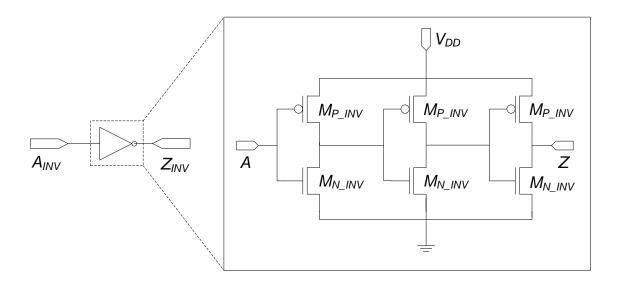

| 5.5  |     | Inverters                                    |     |

| 5.6  | DA  | C                                            | 87  |

| 5.7  |     | MPLETE SYSTEM INTEGRATION                    |     |

| 5.8  | SIN | MULATION RESULTS                             |     |

| 5.8  | 3.1 | PA without predistortion                     |     |

| 5.8  | 3.2 | PA with predistortion                        | 95  |

| 5.8  | 3.3 | IMD3 simulations                             | 100 |

| 5.9  | ME  | ASUREMENT RESULTS                            |     |

| 5.9  | 9.1 | DC biasing problem                           | 102 |

| 5.9   | .2 Future design improvements  | 105 |

|-------|--------------------------------|-----|

| 5.10  | CONCLUSION                     | 106 |

| CHAPT | TER 6 CONCLUSION               | 108 |

| 6.1   | INTRODUCTION                   | 108 |

| 6.2   | CRITICAL HYPOTHESIS EVALUATION | 108 |

| 6.3   | CHALLENGES AND LIMITATIONS     | 110 |

| 6.4   | SUGGESTED FUTURE WORK          | 111 |

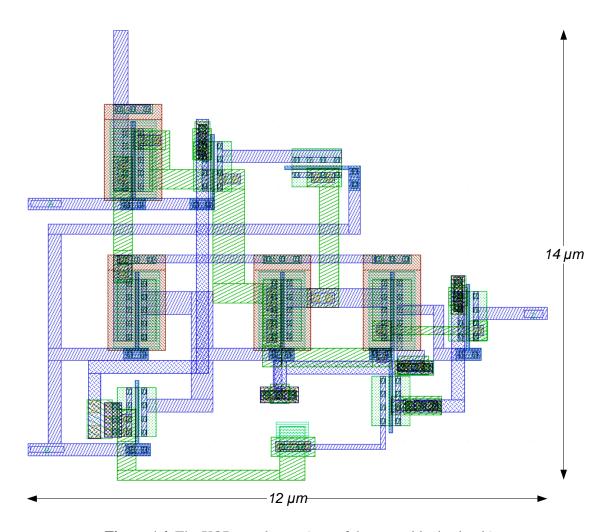

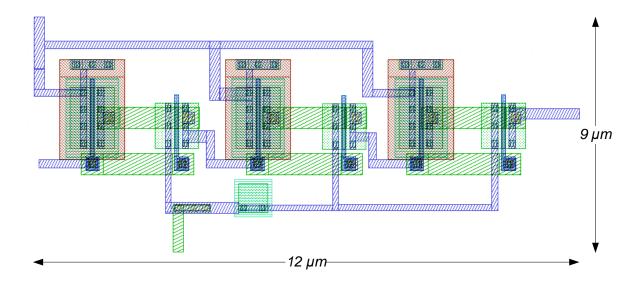

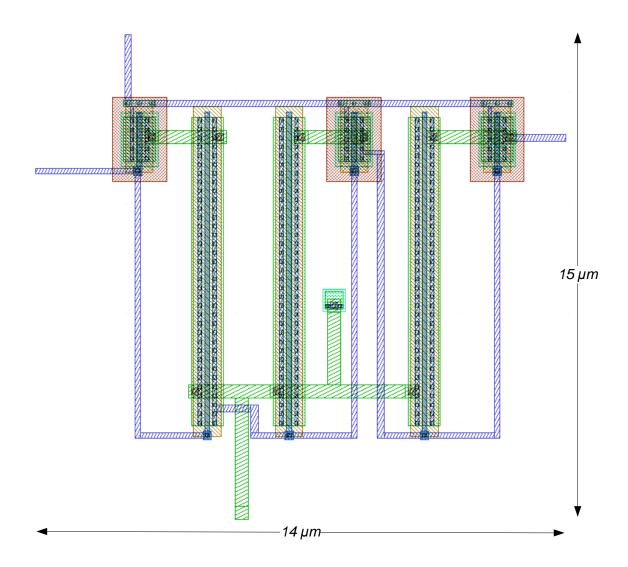

| APPEN | DIX A: CIRCUIT LAYOUTS         | 119 |

# LIST OF ABBREVIATIONS

III-V Periodic table group 3-4

AC Alternating current

ACLR/ACPR Adjacent channel leakage ratio/Adjacent channel power ratio

AM-AM Amplitude-to-amplitude conversion

AM-PM Amplitude-to-phase conversion

ADBPD Adaptive digital baseband predistortion

ADC Analogue-to-digital converter

ADRFPD Adaptive digital RF predistortion

AMS Analog Mixed Signal

APD Adaptive predistortion

BEOL Back-end-of-line

$BV_{CBO}$  Breakdown voltage collector base (open base)

BV<sub>CEO</sub> Breakdown voltage collector emitter (open emitter)

$BV_{CER}$  Breakdown voltage collector emitter (open emitter) with resistor

BiCMOS Bipolar and CMOS

BJT Bipolar junction transistor

CAD Computer aided design

CE Common emitter

CMOS Complementary metal oxide semiconductor

DAC Digital-to-analogue converter

DC Direct current

DRC Design rule check

DSP Digital signal processor

DBPD Digital baseband predistortion

EER Envelope elimination and restoration

EVM Error vector magnitude

FET Field effect transistor

GaAs Gallium arsenide

GSG Ground-signal-ground

HBT Heterojunction bipolar transistor

HiCuM High current model

HB High breakdown

HP High performance

IBM International Business Machines

IC Integrated circuit

IF Intermediate frequency

IIP<sub>3</sub> Input third-order intercept point

$IP_{1 dB}$  Input power 1 dB compression point

IM Inter-modulation

LINC Linear amplification with non-linear components

LUT Look-up table

LVS Layout versus schematic

MESFET Metal semiconductor field effect transistor

MIM Metal insulator metal

MOSFET Metal oxide semiconductor field effect transistor

MOSIS Metal Oxide Semiconductor Implementation Service

mm-wave Millimetre-wave

MPW Multi-project wafer

NDA Non-disclosure agreement

N/PFET N/P-type field effect transistor

OFDM Orthogonal frequency division multiplexing

QAM Quadrature amplitude modulation

RF Radio frequency

Si Silicon

SiGe Silicon-germanium

*p*-cells Parametric cells

PA Power amplifier

PAC Periodic AC

PAE Power added efficiency

PCB Printed circuit board

PDK Process design kit

PSS Periodic steady state

IMD3 Third-order intermodulation distortion

RFC RF choke

TL Transmission line

VBIC Vertical bipolar intercompany

VGA Variable gain amplifier

VNA Vector network analyser

XOR Exclusive OR

# CHAPTER 1 INTRODUCTION

#### 1.1 BACKGROUNG TO THE RESEARCH

In today's information-dependent world, there is an increase in demand for faster communication speeds and larger bandwidth. Current microwave frequency bands have become saturated and recent advancements in technology, especially in silicon-germanium (SiGe) technology, has resulted in a growing necessity to use new frequency spectrums such as the millimetre-wave (mm-wave) frequency band. In particular, the 60 GHz band is very useful for wireless communication. It offers a very wide frequency and higher transmission speed and it is unlicensed [1].

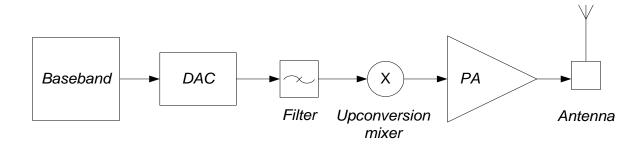

The wireless transmitter needed for mm-wave communication comprises many building blocks, as shown in Figure 1.1, and of particular interest is the power amplifier (PA). The purpose of the PA is to amplify the input signal to an acceptable power level so that the signal can be transmitted from the transmitter to the receiver through the air interface. PAs are the final subsystems prior to the antenna in the transmitter and directly affect the performance of the transmitter.

Figure 1.1. Wireless transmitter.

Unlike wired line communications, wireless systems must share a common transmission medium. The available spectrum is therefore limited. The demand for greater spectral efficiency has resulted in orthogonal frequency division multiplexing (OFDM) being considered as the modulation scheme for communication systems in the mm-wave frequency band [2]. This modulation scheme results in amplitude and phase modulated signals with large peak-to-average ratios.

These signals are very sensitive to disturbances that affect the amplitude and phase of the signal, such as non-linear amplification, which causes distortion in the output signal. This distortion causes the signal to expand to the other adjacent channels, resulting in interference, and deteriorates the performance of the communication system. For this reason it is important for a PA to operate linearly. Linearity and efficiency are mutually exclusive. Designing linear PAs is possible, but most linear PAs are not efficient [3]. The PA efficiency is a very important factor especially in mobile communications. The design of linear and efficient mm-wave PA presents one of the most challenging design problems.

Therefore, in order to achieve good linearity with sufficient efficiency, some kind of linearisation technique has to be implemented [4]. This research focuses on improving the linearity of PAs for mm-wave frequencies using adaptive predistortion (APD) as the linearisation technique. Predistortion's chief attribute is its conceptual simplicity and it does not suffer from bandwidth limitations, which makes it suitable for wideband PAs.

#### 1.2 RESEARCH PROBLEM AND HYPOTHESIS

The primary research question addressed in this thesis:

How can a low-complexity, high-performance APD be integrated with a PA and reduce distortion and improve the linearity of PAs at 60 GHz?

The distortion makes it difficult for the receiver to detect the information correctly. Reducing distortion components will improve the linearity of the PA and also the overall transmitter performance. Existing predistortion linearisation techniques using digital and analogue predistortion methods have been implemented. The analogue predistortion is the simplest predistortion technique and can be realised using a diode or a cubic predistorter at the input of the PA. Digital predistortion is mostly found in an adaptive form in the baseband region where the predistortion is applied with a look-up table (LUT) using a digital signal processor (DSP). Table 1.1 shows the current existing predistortion linearisation methods and their performance in terms of either the adjacent channel leakage ratio/adjacent channel power ratio (ACLR/ACPR), error vector magnitude (EVM) or third-order intermodulation distortion (IMD3) reduction.

| Reference | Frequency | Predistortion | Linearity improvement | Impact | Cited     |

|-----------|-----------|---------------|-----------------------|--------|-----------|

|           | [GHz]     |               |                       | factor | half-life |

|           |           |               |                       | (2012) | (2012)    |

| [5]       | 2.14      | Analogue      | 16.1 dB <sup>†</sup>  | 1.784  | 5.2       |

| [6]       | 1.96      | Digital       | 15 dB <sup>†</sup>    | 2.229  | 9.0       |

| [7]       | 1.8       | Analogue      | 20 dB #               | -      | -         |

| [8]       | 2.14      | Analogue      | 16.4 dBc <sup>†</sup> | 1.784  | 5.2       |

| [9]       | 60        | Digital       | *                     | -      | -         |

| [10]      | 60        | Analogue      | 25 dB <sup>#</sup>    | 1.784  | 5.2       |

| [11]      | 1.95      | Analogue      | **                    | 2.229  | 9.0       |

| [12]      | 60        | Analogue      | 10 dB #               | 0.585  | 5.6       |

| This Work |           |               |                       |        |           |

**Table 1.1.** Summary of existing predistortion linearisation techniques implemented.

As shown in Table 1.1, few predistortion linearisation techniques are implemented at 60 GHz. Furthermore, few of these on-chip predistortion linearisation techniques have been fabricated using the International Business Machines (IBM) SiGe bipolar and complementary metal oxide semiconductor (BiCMOS) process. The proposed research is focused on an APD linearisation technique at 60 GHz using SiGe BiCMOS technology.

The research hypothesis can be stated by means of the following:

If the linearity of PAs is related to the distortion in PAs, then if APD is used to reduce the distortion in PAs, this will improve the linearity in PAs.

Based on the hypothesis, the following secondary research questions are asked:

- How can the APD circuit be realised and integrated with PAs at mm-wave frequencies?

- Determine the distortion reduction and linearity improvement that can be achieved by using APD for PAs at mm-wave frequencies.

- How can the overall PA performance be influenced by using APD?

<sup>†</sup> Reduction in ACLR/ACPR.

<sup>\*</sup> Linearity improvement of -28 dB in EVM.

<sup>&</sup>lt;sup>#</sup>Optimum IMD3 reduction.

<sup>\*\*</sup> A minimum input third-order intercept point (IIP<sub>3</sub>) of 7.5 dBm.

To validate the hypothesis and to address the above questions, different APD options and PA architectures and performance metrics were evaluated and their trade-offs were investigated. The optimal solution for the PA and APD was then designed and simulated at 60 GHz using circuit models separately and then integrated. The PA and APD performance was then evaluated in terms of linearity improvement. After the optimisation of the PA and APD design, both the PA and APD were fabricated onto an integrated circuit (IC). Measurement results were performed on the prototyped solution to determine the performance and feasibility of the design and validate the hypothesis practically.

#### 1.3 JUSTIFICATION FOR THE RESEARCH

The huge bandwidth around 60 GHz is one of the largest unlicensed bandwidth allocations available. This band provides at least 3 GHz (59-62 GHz) overlap that is available worldwide, offering high data-rate communications. Even though this band suffers from severe attenuation of 10 dB/km due to oxygen absorption, this further justifies its use for short-range communication.

The IEEE 802.15.3c and the WirelessHD task teams have defined standards for the 60 GHz band with 30 dBi gain for the antennas and 10 dBm output power for the PA [13]. In addition, OFDM has strict requirements for linearity. Therefore designing a PA at this frequency is challenging, as these PAs must deliver high linear output power and be efficient.

Linearisation techniques can be used to improve the linearity of PAs and meet the demands of mm-wave communications. Not much attention has been focused on linearisation techniques of PAs at 60 GHz. Therefore there is a need to investigate and characterise these linearisation techniques to determine their ability to improve the linearity of 60 GHz PAs.

In addition there is an increasing demand for PAs to be reliable and cost-effective and to yield high performance to satisfy the mm-wave requirements. SiGe BiCMOS technology provides low cost and superior performance and can be used as the building blocks to realise these demands of mm-wave systems.

#### 1.4 METHODOLOGY

The initial step in the research was conducting a thorough literature study focusing on linearity limitations on PAs, the semiconductor building blocks realising PAs at 60 GHz and techniques to improve the linearity of PAs specifically focusing on predistortion, as it provides low complexity and yields good performance in improving the linearity of PAs. The literature study was done to locate a gap in the current research in order to formulate and define a hypothesis.

The optimal PA and APD solution was determined by simulating the design on a schematic level. The PA and APD were then fabricated and prototyped to obtain measurement results. The PA and APD were therefore critically evaluated on a practical level to determine realistically the performance of the PA and APD and the PA separately, therefore validating the hypothesis.

#### 1.5 OUTLINE OF THE THESIS

This thesis is organised as follows:

# • Chapter 1: Introduction

This chapter highlights the research problem, the hypothesis and the motivation for the research. The research is also placed into context with other research conducted in PA linearisation using predistortion.

# Chapter 2: Literature Review

The existing body of knowledge in this area of research is presented and analysed in this chapter. The chapter describes the fundamentals of PAs, the non-linear phenomena in PAs that result in distortion, the semiconductor technologies available for PAs and methods to reduce the distortion in PAs using current linearisation techniques focusing specifically on using predistortion at mm-wave frequencies.

# Chapter 3: Research Methodology

The method and procedures used to validate the hypothesis and answer the research questions are explained in this chapter. An overview of the software package used for simulation is also presented. The fabrication process in the design of the PA and APD is discussed, as well as the details of the measurement equipment used on the prototyped IC. Finally a set of measurement tests is presented that was conducted to validate the hypothesis practically.

# Chapter 4: Mathematical Analysis

The distortion components in the SiGe heterojunction bipolar transistor (HBT) are analysed in this chapter with the use of the Volterra series analysis. The mathematical analysis describes the effects of the IMD3 component on the fundamental signal and provides techniques to overcome this problem.

# Chapter 5: PA and APD Design and Results

The detailed design of the PA and the APD is described in this chapter. The chapter is divided into the following main sections, viz. the PA design, APD design and implementation and results. All the subsystems are designed from first principles using mathematical analysis and then optimised during system integration.

# Chapter 6: Conclusion

This chapter concludes the thesis and provides the critical evaluation of the hypothesis. The challenges and limitations experienced during this research work are also mentioned, as well as possible future work and improvements on this research work.

#### 1.6 DELIMITATIONS OF THE SCOPE OF THE RESEARCH

The scope of this research is limited to reducing the distortion caused by non-linearities found in PAs at mm-wave frequencies, especially at 60 GHz using APD. The PA was designed and fabricated to integrate with the APD to determine the linearity improvement that can be obtained at 60 GHz, therefore validating the hypothesis.

Since no prior experimental data were available for the PA and APD, both these systems were designed using first principles. Approximations were made from literature and from the limitations set by the process models (operating ranges of the transistors and the dimensions of the passive and active models) from the foundry.

For the APD, different types and configurations are available. The chosen APD focuses on amplitude non-linearity and the IMD3 components and this choice is justified in chapters 4 and 5. The end result is a low-complexity, high-performance APD in terms of linearising the PA and ease of integration with the PA. Although this APD design can easily be integrated with a PA to provide sufficient linearity improvement, because of the limited space available on the multi-project wafer (MPW) run and complexity of the PA, additional PA designs could not be fabricated. Therefore the APD with different PA designs could not be evaluated.

# 1.7 CONTRIBUTION TO THE FIELD

A new predistortion method using APD for the linearity improvement of PAs has been proposed for use in mm-wave frequencies (specifically 60 GHz). A detailed list of the resulting contributions to the body of knowledge is given here.

- Non-linearity has been identified as a major source of transmitter degradation especially at 60 GHz where efficient and linear PAs are required. The main contribution of this research is the identification and characterisation of these non-linear properties (the IMD3 components) found in HBTs. This research also provides a new solution to reduce the IMD3 components for PAs at 60 GHz.

- The proposed solution followed a thorough literature study on existing PA linearisation techniques. This allowed to find the current trends, performance, strengths and weaknesses of these techniques which are discussed below and in chapter 2.

- The use of spectral efficient modulation schemes such as OFDM at mmwave frequencies, results in a need for highly linear PAs at 60 GHz. Previously, linearity analysis in PAs were focused at lower frequencies

(< 5 GHz) using mostly algorithms in DSPs in the baseband region to apply the linearisation techniques. Baseband linearisation is not a true PA linearisation technique but more a transmitter linearisation technique. Only recently has attention been given to the linearity of PAs at 60 GHz [9, 10, 14]. The proposed linearisation technique is a true PA predistortion linearisation technique that can be implemented completely on-chip not requiring any auxiliary circuitry such as in [9, 14].

- The current radio frequency (RF) predistortion linearisation technique at 60 GHz shown in [10] provides a non-adaptive predistortion function to the PA and therefore does not optimise the linearity improvement. It has been shown that using an adaptive predistortion technique approach can improve the linearity of the PA as it provides greater control of the predistortion function.

- Previous 60 GHz predistortion techniques have looked at CMOS transistors [9, 10]. This research analyses the SiGe HBT which is known to have better performance at mm-wave frequencies than CMOS transistors and reduced cost compared to gallium arsenide (GaAs) technologies.

- The non-linearity components were analysed and characterised using the Volterra series analysis. This mathematical analysis identified the major contributors to the non-linearity phenomena in HBTs. The large signal analysis of the PA was also investigated separately. Using these analyses, a solution was derived to reduce IMD3 components in the HBT.

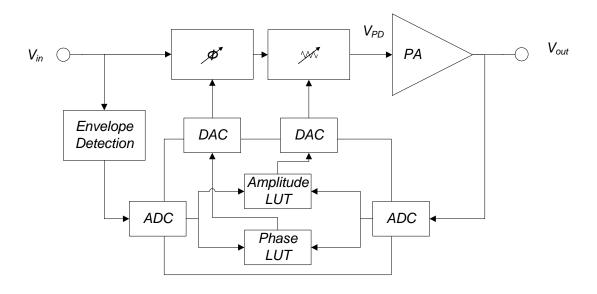

- The proposed solution was enhanced further making it adaptable using an on-chip power detector, analogue-to-digital converter (ADC), control logic, digital-toanalogue converter (DAC) and dynamic bias circuitry. This is the first time a complete APD has been implemented on-chip to improve the linearity of PAs at 60 GHz.

- The APD design provides full control to the user allowing the PA to be optimally linearised. Although the APD in this research was integrated with a three-stage single-ended common emitter (CE) PA, it can be applied to any PA topology. This is because the adaptation is applied to the bias circuitry of the PA.

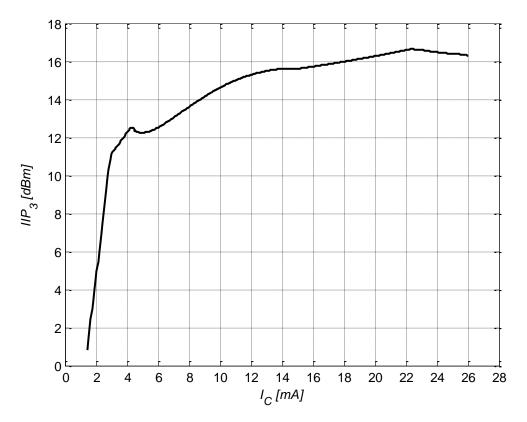

• The mathematical analysis has been verified by analysing the linearity performance of the HBT using simulations. It was observed that by increasing the bias current up to 23 mA, the  $IIP_3$  increased for the 0.12  $\mu$ m × 16  $\mu$ m SiGe HBT therefore validating that the linearity of the HBT based PA can be improved.

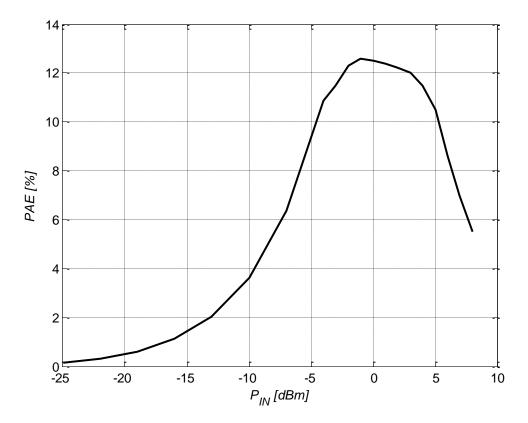

- The APD proposed in this research has been demonstrated successfully through the design and simulation of a non-linear and linear PA at 60 GHz. The PAs were designed from first principles. Both the non-linear and linear PAs were submitted for fabrication. The non-linear PA achieves a  $P_{SAT}$  of 11.97 dBm, an input power 1 dB compression point ( $IP_{1\ dB}$ ) of -10 dBm and a peak power added efficiency (PAE) of 12.6 %. When the APD is applied, the PA has an improved  $IP_{1\ dB}$  of -6 dBm, a peak PAE of 11.8 % and an optimum IMD3 reduction of 10 dB is achieved. The linear PA also has an improved linear output power of 2.5 dBm compared to the non-linear PA.

- The mathematical model can be applied easily into any computer aided design (CAD) software as this analysis is independent of the CAD software. This thesis also presents a complete design and implementation of a three-stage 60 GHz PA and the APD subsystems. The use of the BiCMOS process from IBM allowed the integration of both SiGe HBT and CMOS technology nodes.

# 1.8 PUBLICATION LEADING FROM THIS RESEARCH

The following peer-reviewed journal article related to this work has been accepted:

• J. Valliarampath and S. Sinha, "Linearity Improvement Analysis for PAs at mm-Wave Frequencies", *Microwave and Optical Technology Letters*, vol. 56, no. 3, pp. 743-748, March 2014.

The journal is listed by Thomson Reuters Web of Knowledge (formerly ISI).

# 1.9 CONCLUSION

This chapter laid the foundation for this thesis. The background of the research was presented and the need to characterise and minimise the IMD3 components for PAs at 60 GHz was emphasised in this chapter. This allowed the identification of the research problem and the formulation of the hypothesis. The methodology to validate the hypothesis, as well as the organisation of the thesis, was also outlined to indicate how the research was conducted.

# CHAPTER 2 LITERATURE REVIEW

#### 2.1 INTRODUCTION

The 3 GHz overlap unlicensed bandwidth allocation at 60 GHz has made this mm-wave spectrum lucrative for fast gigabit applications. This has resulted in numerous RF transceivers currently being developed to operate within the 60 GHz band. One of the most challenging functional blocks in the transceiver at 60 GHz is the PA [15]. Its function is to amplify the input signal and deliver high output linear power while being efficient, but its performance is severely affected by the scaled semiconductor technology and the operating frequency. It is for this reason that PA linearisation techniques should be investigated to improve the linearity and maintain efficiency, enhancing the performance of the PA.

The first part of this chapter focuses on the fundamental concepts, parameters and figures of merit for PAs. The current semiconductor technologies as the building blocks of the PA are also discussed. The second part of this chapter analyses the various distortion components in the PAs. This important property contributes to the understanding of non-linearity in PAs. The last part investigates several linearisation techniques, evaluating their trade-offs and specifically concentrating on the predistortion linearisation technique for mm-wave PAs.

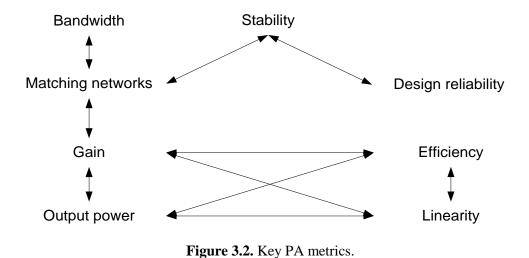

# 2.2 POWER AMPLIFIERS

The PA usually consumes the largest amount of static power of the transmitter. It is therefore desirable to operate the PA in the saturation region to achieve maximum power efficiency of the PA. The trade-off is that all real PAs have non-linear characteristics and this is most noticeable in the saturation region. This trade-off becomes even more stringent at 60 GHz, where desirable Si-based technology for low-cost production cannot provide sufficient output power in PAs while maintaining high linearity [16]. PAs are therefore designed and evaluated on several trade-offs, each trying to accomplish a conflicting requirement such as linearity versus efficiency or high output power versus minimum

distortion. Consequently understanding the characteristics and operation of PAs is essential to ensure PAs are correctly designed to meet the requirements [17].

#### 2.2.1 PA CLASS OF OPERATION

The performance of any PA will be influenced by how the PA is biased. There are several groups of classes; each has been well documented and is briefly discussed here. The most common group is the biasing class, which can be defined as Class A, B, AB or C. The choice of PA class determines the amount of distortion and the power efficiency of the output signal. The class of operation to use is determined by the linearity and efficiency requirements of the system using the PA [17]. Table 2.1 summarises the biasing classes from Class A to Class C.

**Table 2.1.** Comparison of PA biasing classes [17]. Copyright © 2009, John Wiley and Sons, Inc. All rights reserved.

| Class | Current Conduction | Bias Point           | Maximum Theoretical |

|-------|--------------------|----------------------|---------------------|

|       | Angle $\theta$     |                      | Efficiency (%)      |

| A     | 360 °              | Midway between       | 50                  |

|       |                    | device pinch-off and |                     |

|       |                    | saturation.          |                     |

| В     | θ = 180 °          | Device pinch-off.    | 78.5                |

| AB    | 180 ° < θ < 360 °  | Above pinch-off.     | 50 – 78.5           |

| С     | θ < 180°           | Below pinch-off.     | 78.5 - 100          |

As shown in Table 2.1, the Class A PA operates in the linear region of the transistor's *i-v* curve and is on 100 % of the time. The output therefore experiences minimum distortion but offers the least amount of efficiency. Class B PAs are on 50 % of the time and therefore the output is not as linear; however, they do provide improved efficiency compared to Class A. The Class AB PA is a compromise between the Class A and B PA in terms of linearity and efficiency, while the Class C PA is most efficient, but suffers most distortion, as its bias point is below the pinch-off region. Class AB PAs produce distortion components that are considered low enough to use an external linearisation technique to improve the linearity of these PAs. However, Class C PAs produce such a large amount of distortion that they are not ever considered for use with external linearisation techniques [18].

# 2.2.2 PA TOPOLOGIES

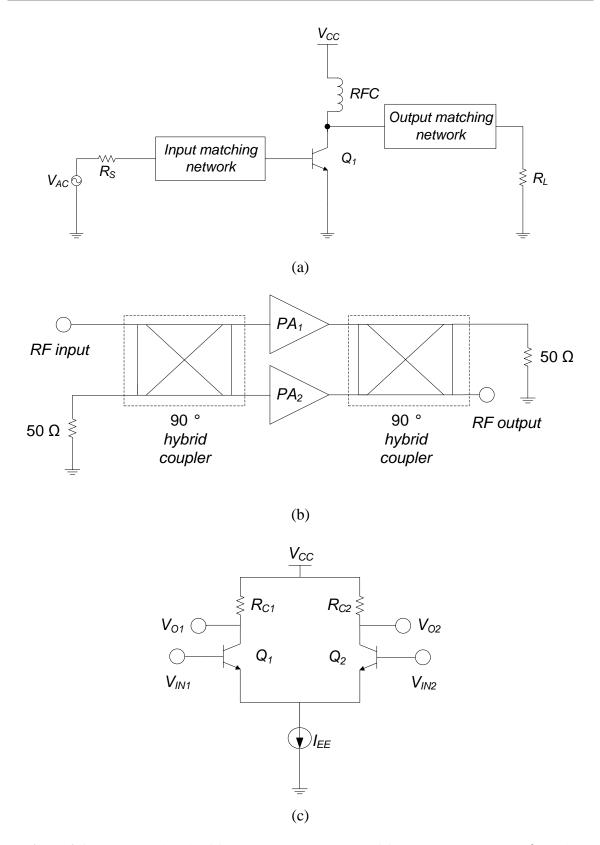

Three basic PA topologies exist, viz. single-ended, balanced and differential. The criteria for choosing the particular topology depend on the PA requirement. Table 2.2 provides a comparison between these PA topologies and Figure 2.1 shows the circuit configurations of these topologies.

Table 2.2. Comparison of PA topologies.

| Topology               | Advantages                                                                                                                  | Disadvantages                                                                                      |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Single-ended           | Low complexity. Reduced cost.                                                                                               | Reduced performance compared to other PA topologies.                                               |

| Balanced               | Higher output saturated power and 1 dB compression point. Excellent impedance matching. Improved reliability and stability. | Additional components required. Losses of couplers reduce overall PA performance. Increased costs. |

| Differential/Push-pull | Higher output saturated power and 1 dB compression point.                                                                   | Consumes more static power than single-ended. Increased cost.                                      |

As shown in Table 2.2 and in Figure 2.1 (a), the single-ended topology is the least complex PA topology and is commonly used in either the CE/common source or cascode configuration. The cascode typically provides higher gain and improved efficiency and can be operated above the breakdown voltage that usually restricts the CE configuration [19]. The single-ended has the smallest chip area and is the most cost-effective PA topology [13].

**Figure 2.1.** PA topologies viz. (a) general single-ended PA (b) balanced PA using 90 ° hybrid couplers (c) differential CE PA.

The balanced and differential PA topology is able to obtain higher output saturated power and a 1 dB compression point compared to the singled-ended PA topology. The balanced topology shown in Figure 2.1 (b) provides improved input and output matching capability as long as the amplifier cells are identical and also results in improved stability. In case one of the single-ended transistors fails, the PA is still able to function; however, the gain will be reduced by 6 dB. The major drawback of the balanced topology is the use of couplers because it introduces losses into the system and also consumes a large chip area as shown in [20], therefore increasing the cost of the design. The disadvantage of the differential topology is that it consumes 50 % more static power compared to the singled-ended PA topology. It also occupies a larger chip area because it consists of two singled-ended PAs as shown in Figure 2.1 (c) and therefore increases the cost as well [13].

#### 2.2.3 OUTPUT POWER

The primary goal of the PA is to deliver maximum power to the load. The output power can be determined from the power supply voltage and the load for a single-ended PA, as shown in Figure 2.1 (a). This PA consists of the transistor  $Q_1$ , the input and output matching networks, the RF choke (RFC), in the form of an inductor and the source ( $R_S$ ) and load resistors ( $R_L$ ). The transistor  $Q_1$  is usually constrained by the breakdown voltage and the collector saturation current and this must be taken into account when designing the PA. The maximum power delivered to the load for a Class A PA can be determined using (2.1),

$$P_{OUT} = \frac{v_{CC}^2}{2R_L},\tag{2.1}$$

where  $V_{CC}$  is the power supply voltage.

# 2.2.4 POWER MATCHING

The maximum power theorem states that the maximum power transfer occurs when the PA is conjugately matched and is given by (2.2) and (2.3):

$$\Gamma_{\mathcal{S}} = S_{11}^{*}, \tag{2.2}$$

$$\Gamma_L = S_{22}^*,$$

(2.3)

where  $\Gamma_S$  and  $\Gamma_L$  are the source and load reflection coefficients respectively. The above equations are only valid when the PA is unilateral.

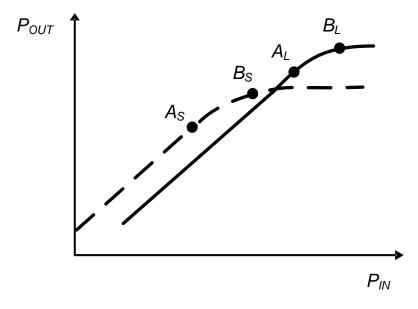

This theorem is valid only for low input power, i.e. small-signal operation where the PA is linear and can only be used on the input side and not at the output side of the PA. For large-signal operation the load-line/load-pull approach is used instead to obtain maximum output power, which transforms the output load to a  $\Gamma_{OPT}$ . The load-line maximises the output power by using the maximum current and voltage swings, while the load-pull determines  $\Gamma_{OPT}$  using an exhaustive search approach. The results of the load-line/load-pull approach and the conjugately match method are shown in Figure 2.2.

**Figure 2.2.** Optimal matching versus small-signal matching [21]. © 2003 Artech House, Inc.

As shown in Figure 2.2, the dashed line and solid line are the small-signal matching and optimal matching approaches respectively. Points  $A_S$ ,  $A_L$  and  $B_S$ ,  $B_L$  are the small-signal and optimal matching maximum uncompressed power and 1 dB gain compression points respectively. Although higher output power is achieved using the load-line/load-pull approach, it does come at the cost of reduced gain.

#### 2.2.5 POWER EFFICIENCY

Efficiency is a key performance metric of mm-wave PAs and is a measure of the RF output power to the direct current (DC) input power. Efficiency is either defined as the drain efficiency  $(\eta_D)$  or collector efficiency  $(\eta_C)$  and is given by (2.4)

$$\eta_{D/C} = \frac{P_{OUT}}{P_{DC}}. (2.4)$$

Another key performance metric is the PAE. This metric is the ratio of the output RF power minus the input RF power to the DC input power and is calculated using (2.5)

$$PAE = \frac{P_{OUT} - P_{IN}}{P_{DC}}. (2.5)$$

# 2.2.6 MODULATION SCHEMES

There has been a growing trend in utilising complex digital modulation schemes that are bandwidth efficient for mm-wave applications. The IEEE 802.15.3.c and WirelessHD have developed a modulation scheme standard for the 60 GHz frequency band focusing mainly on OFDM because of its high spectral efficiency [2]. Using OFDM results in a stronger and clearer signal because the signal is split into several narrowband channels at different frequencies, which reduces wireless interference. The use of an OFDM modulation scheme is known as an effective way to mitigate selective multipath fading effects in wireless channels [22]. However, OFDM is more complex and expensive because it requires the analysis of many frequencies and the characteristics of those frequencies.

Typically with OFDM, quadrature amplitude modulation (QAM) is employed, which uses both amplitude and phase for encoding data for higher data rates. It has been reported that using an OFDM 16-QAM modulation is sufficient to achieve a 3.8 Gbps data rate [23]. These modulation schemes require high linearity PAs in order to maximise system performance and satisfy the increasing demand for higher data rates at 60 GHz.

#### 2.2.7 NON-LINEAR PHENOMENA IN PA

In order to achieve high efficiency output power, PAs have to operate in the non-linear area near the saturation region. This increases the PA's non-linearity, which affects the spectrum of the signal. One way to model this non-linearity and to calculate the spectral components is by using a memory-less polynomial model. The output of a system modelled using a third-degree polynomial is given by (2.6),

$$I = aV(t) + bV(t)^{2} + cV(t)^{3},$$

(2.6)

where a, b and c are real coefficients. Assume the input signal, V(t) is of the form as shown in (2.7):

$$V(t) = V_1 \cos(\omega_1 t) + V_2 \cos(\omega_2 t). \tag{2.7}$$

Substituting (2.7) into (2.6), results in three terms, as shown in (2.8) to (2.10):

$$i_1(t) = aV_1 \cos(\omega_1 t) + aV_2 \cos(\omega_2 t),$$

(2.8)

$$i_{2}(t) = \frac{b}{2} \{V_{1}^{2} + V_{2}^{2} + V_{1}^{2} \cos(2\omega_{1}t) + V_{2}^{2} \cos(2\omega_{2}t) + 2V_{1}V_{2}[\cos((\omega_{1} + \omega_{2})t)] + \cos((\omega_{1} - \omega_{2})t)] \},$$

(2.9)

$$i_{3}(t) = \frac{c}{4} \{V_{1}^{3} \cos(3\omega_{1}t) + V_{2}^{3} \cos(3\omega_{1}t) + 3V_{1}^{2}V_{2}[\cos((2\omega_{1} + \omega_{2})t) + \cos((2\omega_{1} - \omega_{2})t)] + 3V_{1}V_{2}^{2}[\cos((\omega_{1} + 2\omega_{2})t) + \cos((\omega_{1} - 2\omega_{2})t)] + 3(V_{1}^{3} + 2V_{1}V_{2}^{2})\cos(\omega_{1}t) + 3(V_{2}^{3} + 2V_{1}^{2}V_{2})\cos(\omega_{2}t)\}.$$

$$(2.10)$$

From (2.8) to (2.10), the generated frequencies all occur at a linear combination of the two excitation frequencies (2.11),

$$\omega_{m,n} = m\omega_1 + n\omega_2,\tag{2.11}$$

where m, n = ..., -3, -2, -1, 0, 1, 2, 3, ...

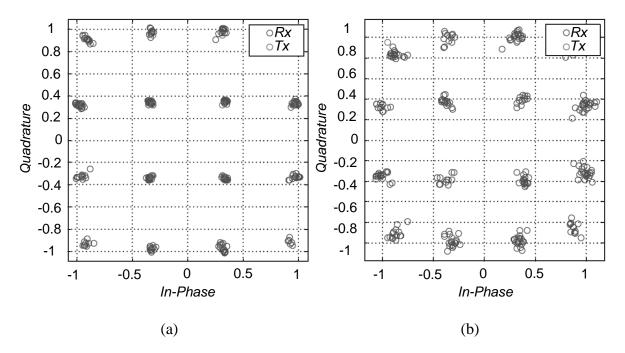

The current or the voltage components at the mixing frequency,  $\omega_{m,n}$ , result in many non-linear problems such as harmonics, intermodulation (IM), amplitude-to-amplitude conversion (AM-AM) and amplitude-to-phase conversion (AM-PM) distortion. The non-linear effect on the 16-QAM signal is shown in Figure 2.3.

**Figure 2.3.** 16-QAM constellation before and after non-linear amplification under (a) 3 dB and (b) 1 dB output back-off [16].

Copyright © 2011, John Wiley and Sons, Inc. All rights reserved.

The non-linear effect results in a distorted QAM constellation, as shown in Figure 2.3. The modulation data points lie outside their correct decision areas. This increases the probability that the receiver will misinterpret these values, thus increasing the bit error rate.

#### 2.2.8 HARMONIC DISTORTION

One obvious result from the non-linear PA is the generation of harmonics shown in (2.8) to (2.10) at  $m\omega_1$  and  $n\omega_2$ . Generally harmonics are not a serious problem because these components are situated far from the desired signals and are removed using filters.

#### 2.2.9 IM DISTORTION

Two or more tones added in (2.8) to (2.10) are called IM components. IM components pose a very serious problem, because these components can be mistaken for the desired signals.

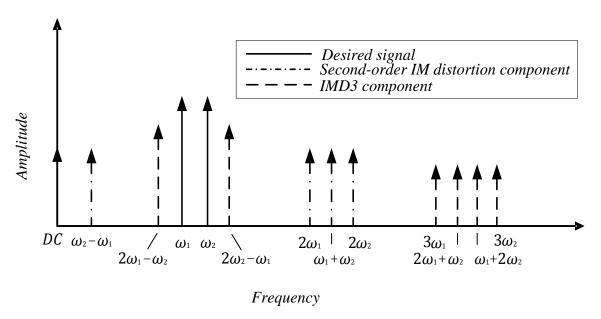

Figure 2.4. Second-order IM distortion and IMD3 components.

Even-order IM products are often of little concern because they occur at frequencies that are situated well above or below the desired signals. The odd-order IM products are of greatest concern, especially the third-order ones that occur at  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$ , as shown in Figure 2.4. The IMD3 components are the strongest of all odd-order products and lie very close to the desired signals. These IMD3 components also fall both on the signal band and out of the signal band, resulting in spectral regrowth, and cannot easily be rejected by filters.

The IM distortion components (predominately the IMD3 and fifth-order IM distortion) are used to calculate the ACPR. This is a ratio between the power in the main channel and the power in the adjacent channels. It is a measure of the amount of spectral regrowth within the PA. The lower the ACPR value, the better the linearity of the PA.

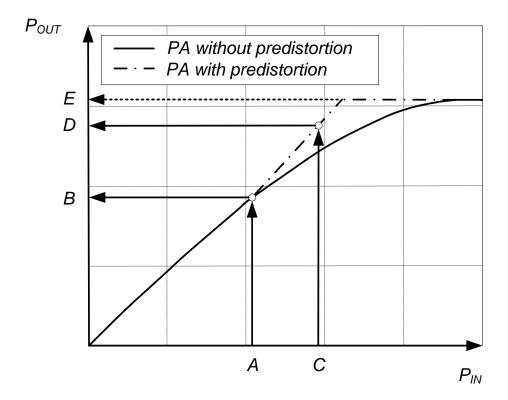

#### 2.2.10 GAIN COMPRESSION

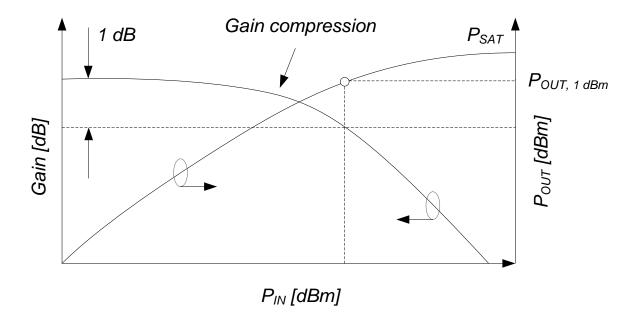

The non-linear phenomenon known as gain compression occurs when the output gain decreases with increased input power due to the PA's physical limits. This effect results in the output power of the PA saturating at a certain point, as shown in Figure 2.5.

Figure 2.5. A typical PA experiencing gain compression.

The point where the output power level deviates by 1 dB from the linear output power characteristic is known as the 1 dB compression point as shown in Figure 2.5. This point separates the almost linear output power from the non-linear output power.

# 2.2.11 AM-AM AND AM-PM DISTORTION

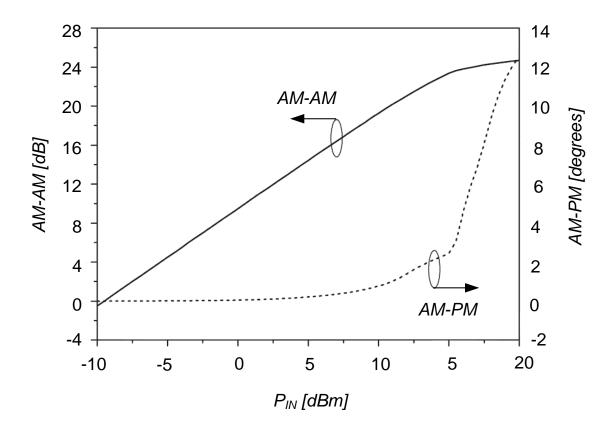

AM-AM and AM-PM distortion will occur in a memory reactive non-linear circuit owing to amplitude distortion and phase difference with the input signal only. If the distortion components are dependent on the current input signal as well as the previous input signal, then these distortion components will be affected by memory effects [16]. The effect of these distortions is illustrated in Figure 2.6.

**Figure 2.6.** AM-AM and AM-PM distortion due to PA non-linearities [17]. Copyright © 2009, John Wiley and Sons, Inc. All rights reserved.

In Figure 2.6, the AM-AM distortion indicates non-linearity only in the amplitude and is associated with gain compression. To avoid AM-AM, the amplifier can be operated in the output back-off region, but this will reduce the power efficiency of the PA. AM-PM conversion occurs when changes in the amplitude of a signal applied to a PA cause a phase shift and affect the linearity of the PA. AM-PM often begins to affect the linearity of the PA at several dBs below the compression point [24]. Ideally, the amplitude and phase shift should be linear and constant respectively as input power is increased, resulting in little amplitude and phase distortion with increasing input power levels.

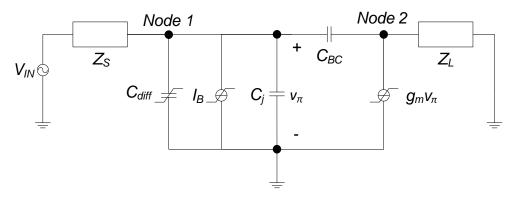

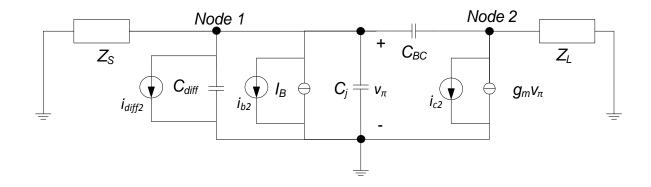

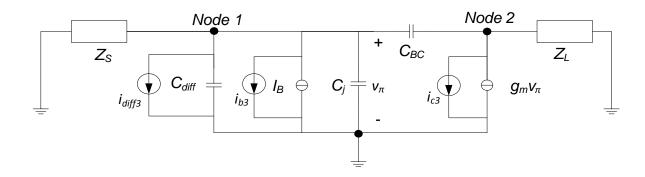

#### 2.3 NON-LINEARITY COMPONENTS IN SIGE HBT

The dominant *i-v* and C-V non-linearities found in the SiGe HBT result in the following non-linearity components [25]:

• The collector current,  $I_C$ , is a non-linear function of the control voltage,  $v_{\pi}$ , and relates to a non-linear transconductance.

- The base current,  $I_B$ , is also a non-linear function of  $v_{\pi}$  and therefore follows the non-linear characteristics of the transconductance.

- The diffusion capacitance,  $C_{diff}$ , is directly proportional to  $I_C$  and is therefore inherently non-linear.

#### 2.4 SEMICONDUCTOR TECHNOLOGIES

The performance achieved by the mm-wave PA and APD is highly dependent on the semiconductor building blocks. These include both active and passive devices. Several semiconductor technologies are available to fabricate mm-wave PAs. Accurate active and passive models are necessary to predict the real performance of the PA during the design process.

#### 2.4.1 ACTIVE DEVICES

The requirements to integrate analogue and digital circuits and extend the capabilities of the same PA chip have become very important. Historically metal oxide semiconductor field effect transistor (MOSFET) and metal semiconductor field effect transistor (MESFET) devices were used in PAs. However, owing to higher gains and current densities required at microwave and mm-wave frequencies, bipolar devices have been the preferred choice at higher frequencies [26]. Bipolar junction transistor (BJT) devices based on Si and periodic table group 3-4 (III-V) compound technologies such as GaAs are now found in microwave and mm-wave PA designs.

GaAs technology has a significant performance advantage due to the higher electron drift mobility and semi-insulating substrate compared to Si. This was the reason for GaAs being favoured for RF applications. However, recent advancements in Si-based technologies, particularly the SiGe HBTs, offer a significant challenge to III-V technologies. SiGe HBT technology reduces manufacturing costs as well as power consumption compared to semiconductor technologies based on GaAs and indium phosphide [15], [26].

Germanium has a bandgap of 0.66 eV compared to Si, which has a bandgap of 1.12 eV. However SiGe has a narrower bandgap than Si, where Ge is graded across the otherwise Si base, forming the SiGe HBT. This results in the overall bandgap of the base region being reduced. This bandgap difference between the emitter and the base in the HBT results in a higher CE current gain [27]. Semiconductor device performance is shown for SiGe HBT and GaAs HBT in Table 2.3.

**Table 2.3.** Process parameters for SiGe HBT and GaAs HBT technologies [28]. Copyright © 2004, IEEE.

|                                                   | SiGe HBT | GaAs HBT |

|---------------------------------------------------|----------|----------|

| $f_T(GHz)$                                        | 44       | 46       |

| Forward gain, $\beta$                             | 200      | 120      |

| Base-emitter voltage, $V_{be}(V)$                 | 0.8      | 1.33     |

| Early voltage, $V_A$ (V)                          | 100      | 1223     |

| Collector-emitter breakdown voltage, $V_{ce}$ (V) | 6        | 14.3     |

| Collector-base breakdown voltage, $V_{cb}$ (V)    | 12       | 26       |

| Emitter-base breakdown voltage, $V_{eb}$ (V)      | 5        | 6.9      |

| Power density (mW/\mu <sup>2</sup> )              | 2        | 0.9      |

| Thermal conductivity (W/cm-°C)                    | 1.5      | 0.49     |

| Base-emitter capacitance, $C_{be}$ (fF)           | 10       | 2.4      |

| Base-collector capacitance, $C_{bc}$ (fF)         | 3.3      | 1        |

| Possibility of N-type and P-type metal oxide      | Yes      | No       |

| semiconductor integration                         |          |          |

As shown in Table 2.3, HBTs based on III-V semiconductors are currently the fastest devices and offer better performance than SiGe HBTs because of their superior breakdown voltage and smaller parasitic capacitances. Nevertheless, recently higher  $f_T$  and  $f_{max}$  values (which determine the ultimate circuit speed) of 230 GHz and 280 GHz respectively have been reported for SiGe HBTs [29]. An advantage of SiGe HBTs over GaAs HBTs, where PA is concerned, is represented by the higher linearity of the former. Table 2.4 [30] shows the comparison of the linearity efficiency of the SiGe BiCMOS HBT technology against different semiconductor device technologies.

**Table 2.4.** Comparison of different semiconductor technologies in terms of linearity [30]. Copyright © 2001, IEEE.

| Technology                             | $OIP_3$ (dBm) | $P_{DC}$ (mW) | Linearity efficiency |

|----------------------------------------|---------------|---------------|----------------------|

| IBM SiGe HBT                           | 25            | 27            | 12                   |

| GaAs HBT                               | 25            | 29.1          | 11                   |

| GaAs high electron mobility transistor | 31.5          | 240           | 6                    |

| GaAs MESFET                            | 28            | 60            | 10.5                 |

| Si BJT (high $f_T$ )                   | 17            | 14            | 4                    |

The linearity efficiency in Table 2.4 is calculated by dividing the power at the output third-order intercept point  $(OIP_3)$  by the DC power  $(P_{DC})$ . It shows that the SiGe HBT has the highest linearity efficiency compared to the other technology processes. Based on the trends in linearity efficiency, the current SiGe HBT technology with its reduced cost and improved performance, as compared to GaAs HBT technology, makes it favourable for high-linearity circuit designs.

The availability of HBTs and MOSFETs in SiGe BiCMOS technologies offer increased design flexibility in PA circuits. SiGe HBTs are generally integrated with MOSFETs in a BiCMOS technology. The SiGe HBTs are used in the mm-wave circuits and the MOSFETs are used in the digital CMOS circuits. BiCMOS technologies incorporating SiGe HBTs are therefore well suited for producing mm-wave PAs.

# 2.4.1.1 Breakdown voltage

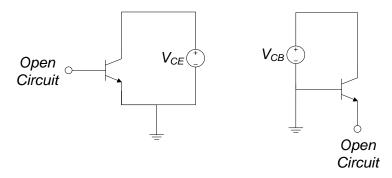

The continuous scaling down of the SiGe HBT technology has achieved cut-off frequencies greater than 300 GHz. The higher operating frequencies are achieved by increasing the collector doping, which increases the operating current density. This in turn leads to high electric fields at the collector-base junction. However, improvements in the transit frequencies lead to a reduction in the collector-emitter breakdown voltage ( $BV_{CEO}$ ) [31]. Another breakdown voltage also exists and is the result of the breakdown of the collector-base junction, which is known as collector-base breakdown voltage ( $BV_{CBO}$ ). Both these circuit configurations are shown in Figure 2.7.

**Figure 2.7.** Transistor in the open base and open emitter configurations [32]. Copyright © 2005, IEEE.

The CE and common base configurations that result in  $BV_{CEO}$  and  $BV_{CBO}$  respectively are shown in Figure 2.7. Impact ionisation is the main cause of the breakdown voltages and results in the generation of electron-hole pairs by accelerated electrons, resulting in the necessary base recombination current. This effect reduces the transistor's  $BV_{CEO}$ . Operation above  $BV_{CEO}$  is possible if an external base resistor is used, which will extract the generated majority carriers from the base. In [33] a base resistance of 300  $\Omega$  was used, extending the  $BV_{CEO}$  limit from 1.7 V to 4 V ( $BV_{CEO}$ ) for the IBM BiCMOS8HP SiGe HBT. The  $BV_{CBO}$  is higher than the  $BV_{CEO}$  [34] and is the maximum limit of operating the transistor and  $BV_{CEO}$  is bounded between  $BV_{CBO}$  and  $BV_{CEO}$ .

#### 2.4.1.2 Transistor device models

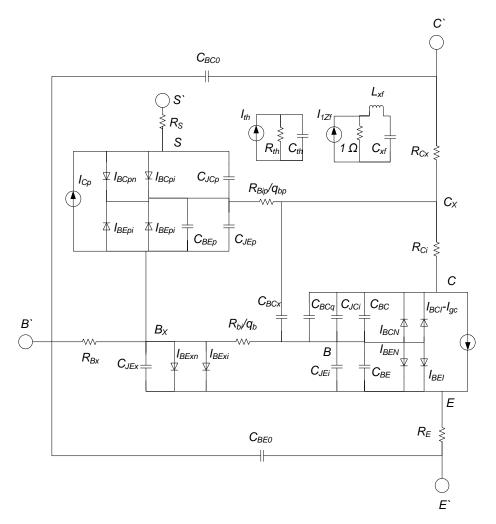

There are different device models such as the Ebers-Moll, Gummel-Poon, vertical bipolar intercompany (VBIC), most exquisite transistor model and high current model (HiCuM) to describe BJTs and HBTs. The Eber-Moll and the Gummel-Poon are simple transistor models and suffer from limitations especially in transistor modelling at very high frequencies. VBIC has several improvements compared to the previous two models; however, there are still some shortcomings in this model. While the HiCuM has proven to be the most accurate model, correlating closely with the measured results [35], the VBIC model is still widely used and is used to describe the IBM BiCMOS8HP SiGe HBT. The schematic of this model is shown in Figure 2.8.

**Figure 2.8.** Equivalent circuit for the VBIC model [36]. Copyright © 2008, John Wiley and Sons, Inc. All rights reserved.

As shown in Figure 2.8, the following important parameters are included and computed by the VBIC model:

- The base resistance,  $R_B$ , is calculated using  $R_{Bi}/q_b$  and  $R_{Bx}$ , where  $R_{Bi}$ ,  $R_{Bx}$  and  $q_b$  are the intrinsic base resistance, the extrinsic base resistance and the normalised base charge respectively.

- A quasi-saturation effect is achieved using the constant extrinsic resistance,  $R_{Cx}$  and variable intrinsic resistance,  $R_{Ci}$ .

- The substrate model consists of a parasitic substrate transistor and is computed using a simplified Gummel-Poon model.

- The weak avalanche current is applied to the *b-c* component of the base current to model avalanche multiplication.

- A subcircuit is added to model self-heating.

- Non-ideal and ideal current sources are used to calculate the b-c and the b-e component of the base current.

## 2.4.2 PASSIVE DEVICES

Passive device elements consist of distributed transmission lines (TLs) and lumped components such as capacitors and resistors at mm-wave frequencies. Semiconductor Si substrates with 1-20  $\Omega$ .cm resistivity have been used to manufacture mixed signal RF-ICs and the conductive substrate is well known to cause signal loss in passives [37]. Although the Si substrate is lossy, passive elements with Q factors above 10 at 60 GHz are still feasible [13]. The shorter wavelengths at mm-wave frequencies make it possible to integrate these devices on-chip. Owing to the low resonance frequency of lumped components, distributed TLs are preferred in mm-wave designs [38].

By adjusting the lengths of the TLs, various passive components can be realised as follows:

- Inductors can be realised if the length, L, is less than  $\lambda/4$ .

- RFC can be obtained if the L equals  $\lambda/4$ .

- A capacitor can be formed if  $\lambda/4 < L < \lambda/2$ .

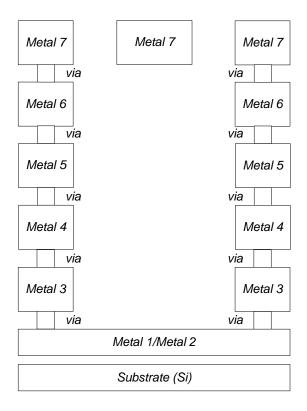

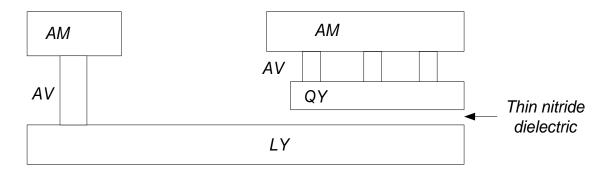

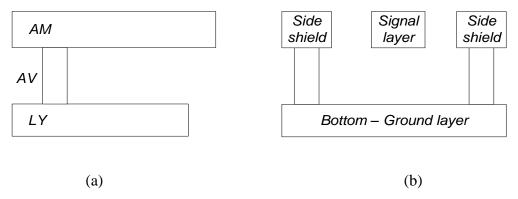

The cross-section of a typical microstrip TL implemented with a Si substrate is shown in Figure 2.9.

**Figure 2.9.** Cross-section of a typical microstrip line with side shielding.

As shown in Figure 2.9, the microstrip line is constructed using various metal levels. Depending on the technology process, usually the top metal level is used as the signal path with either the metal-1 or metal-2 as ground planes [39]. Side shielding can also be used and is connected to the ground plane using vias.

Lumped metal insulator metal (MIM) capacitors are also commonly used in mm-wave frequencies. These capacitors can achieve high Q factors and are typically realised by inserting an intermetal dielectric in the higher metal levels [13].

Transformers are also found in mm-wave designs and can be used for AC coupling, impedance matching and as baluns. A typical transformer can be constructed using two spiral inductors. One way to increase the output power of a PA is to use additional PAs and sum the output power using either parallel or series power combiners.

In [40], a transformer was implemented in a 60 GHz PA design using stacked coupled wires. This transformer provided power combining and efficient impedance transformation simultaneously. Transformers if implemented correctly can also achieve a compact layout

size. The challenge with using transformers is that as the frequency increases, the inductance of the primary coil should decrease, therefore it becomes more sensitive to parasitic values.

#### 2.4.3 LAYOUT AND PARASITICS

At mm-wave frequencies, system performance is affected by the device layout. The designer can actually change the device performance by changing the device layout. This allows the designer more freedom in modifying the device performance. The layout of the circuit will also introduce parasitics especially in the interconnects. These parasitics can be defined as resistive, capacitive or inductive parasitics and become more prominent as the frequency increases resulting in severe degradation of the system.

It is important to incorporate these parasitics in the design of the circuit. To model the parasitic effects, S-parameter characterisation as well as modelling the impedance mismatches and losses are required. Some process design kits (PDKs) include parasitic effects based on experimental data in their device models. The designer can therefore measure the parasitic effects for different conditions. Another method in predicting the effect of parasitic impedances is through the use of an electromagnetic simulator. This is especially useful in analysing interconnects. Post-layout simulations can provide further insight into the layout, highlighting the effect of parasitics and device performance. The design can then be further optimised using these data.

## 2.5 PA MODELLING

To understand the non-linear behaviour of PAs, behavioural models, viz. memory-less non-linear and memory non-linear PA models, are used. These two models are described in the following subsections.

# 2.5.1 QUASI-MEMORY-LESS NON-LINEAR MODEL

This model characterises the current AM-AM and AM-PM non-linearities only. As stated in [16], at 60 GHz the transmitter power is usually around 10 dBm and memory effects can be neglected. Assuming an input signal given by (2.12),

$$x(t) = G[A(t)]\cos[\omega_f t + \theta(t) + \varphi[A(t)]], \qquad (2.12)$$

where G[A(t)] and  $\varphi[A(t)]$  are the AM-AM and AM-PM non-linearities respectively. The Rapp model, which describes the SiGe HBT, can provide the small-signal gain G shown in (2.13),

$$G[A(t)] = \frac{G|A(t)|}{(1 + (\frac{G|A(t)|}{V_{SAT}})^{2p})^{1/2p}},$$

(2.13)

where  $V_{SAT}$  and p are the saturation voltage and smoothing factor respectively, while a modified Rapp model provides the AM-PM effects given by (2.14),

$$\varphi[A(t)] = \frac{\alpha |A(t)|^q}{1 + (\frac{|A(t)|}{\beta})^q},$$

(2.14)

where  $\alpha$ ,  $\beta$  and q are fitting parameters.

# 2.5.2 MEMORY EFFECT NON-LINEAR MODEL

As stated previously, if the AM-AM and AM-PM non-linearities are affected by both the current and previous input values, then the PA suffers from memory effects. There are two main types of memory effects, viz. electrical and thermal memory effects [41], and these will be discussed in the following subsections.

## 2.5.2.1 Electrical memory effects

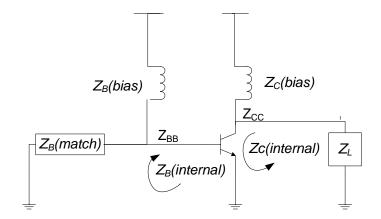

This form of memory effect is caused by non-constant node impedances within the frequency bands. The node impedance is the impedance level at the node. The CE BJT amplifier is shown in Figure 2.10.

Figure 2.10. CE BJT amplifier schematic [41]. © 2003 Artech House, Inc.

In Figure 2.10,  $Z_B(match)$  is the matching impedance,  $Z_B(internal)$  is the internal base impedance and  $Z_B(bias)$  is the base bias impedance. The total impedance at the base is shown in (2.15):

$$Z_{BB} = Z_B(match)||Z_B(internal)||Z_B(bias).$$

(2.15)

$Z_C(bias)$  is the collector bias impedance,  $Z_C(internal)$  is the internal collector impedance and  $Z_L$  is the load impedance. The total impedance at the collector is shown in (2.16):

$$Z_{CC} = Z_L ||Z_C(internal)||Z_C(bias).$$

(2.16)

By analogy, the node impedance at the gate and drain for a MESFET amplifier can be calculated with (2.17) and (2.18) respectively,

$$Z_{GG} = Z_G(match)||Z_G(internal)||Z_G(bias), \qquad (2.17)$$

$$Z_{DD} = Z_L ||Z_D(internal)||Z_D(bias). \tag{2.18}$$

These non-constant impedances are due to the bias networks of the transistors that cannot be made wideband and therefore these impedances change with frequency. Electrical memory effects mostly affect wideband systems [41]. In [8], memory effects were reduced using a high drain bias voltage, as well as a wide bias line and several decoupling capacitors.

# 2.5.2.2 Thermal memory effects

Thermal memory effects are generated by the junction temperature [42]. The junction temperature of the transistor can be expressed in (2.19):

$$T_j = T_{amb} + R_{th} \cdot P_{dissip} + Z_{th}(\omega_1 - \omega_2) \cdot P_{dissip}(\omega_1 - \omega_2). \tag{2.19}$$

The temperature at the junction consists of three components, viz. the ambient temperature, the thermal resistance multiplied by the DC power dissipation and the envelope signal multiplied by the thermal impedance at the same frequency [42]. This shows that the temperature fluctuates as a function of the bandwidth of the signal and changes the electrical characteristics of the transistors and other components, resulting in variations in the generated distortion components. Thermal memory effects generally affect systems using narrowband signals [41, 42].

# 2.5.2.3 Volterra series analysis

The Volterra series analysis is an extension of the Taylor series analysis and is a powerful tool used for modelling and calculating the distortion components of weakly non-linear systems with memory effects. Weakly non-linear systems can be defined quite accurately up to the first three terms. The analysis can be described in both the time domain and frequency domain for RF behavioural models of PAs. The frequency domain is preferred because the non-linearity components can be analysed better. The non-linearities are described as polynomials on the i-v and Q-V functions and the method is independent of semiconductor physics.

The Volterra time series model that describes the distorted output signal is shown in (2.20):

$$D(t) = \sum_{n=0}^{\infty} D_n(t), \tag{2.20}$$

where

$$D_n(t) = \int_{-\infty}^{\infty} \dots \int_{-\infty}^{\infty} h_n(\tau_1, \dots, \tau_n) x(t - t_n) d\tau_1 \dots d\tau_n$$

.

The functions  $h_n(\tau_1, ..., \tau_n)$  are the *n*-th order Volterra kernels. The Fourier series is then applied to the time domain to transform (2.20) into the frequency domain, as shown in (2.21):

$$H_{n}(\omega_{1}, ..., \omega_{n}) = F\{h_{n}(\tau_{1}, ..., \tau_{n})\},$$

$$= \int_{-\infty}^{\infty} ... \int_{-\infty}^{\infty} h_{n}(\tau_{1}, ..., \tau_{n}) x(t - t_{n}) e^{-(s_{1}\tau_{1} + ... + s_{n}\tau_{n})} d\tau_{1} ... d\tau_{n},$$

(2.21)

where  $H_n$  is the frequency domain Volterra kernel and  $F\{\cdot\}$  is the Fourier transformation.

These kernels can completely characterise a system. The disadvantage of the Volterra series analysis is that for strong non-linear systems such as Class C PAs, the sum may begin to diverge and a solution may not be possible. Therefore the Volterra series analysis can only be used for weakly non-linear systems.

There are other simpler non-linear models that take into account memory effects such as the Wiener, Hammerstein and memory polynomial non-linear models. These models are variations of the Volterra series model and have limitations because of their simplified approach in characterising the system.

## 2.6 REDUCING DISTORTION IN PAS

In many applications, the distortion at full output power should be minimised. One approach is to reduce the PA's output power, which is known as back-off. This improves the linearity of the PA and reduces the distortion at the expense of efficiency [15, 17]. At mm-wave frequencies this should be avoided, as efficient PAs are needed. To reduce distortion, an external linearisation technique is needed. The basic idea is to operate the PA as close to saturation as possible to maximise its power efficiency, and then use some linearisation technique to suppress the distortion generated at the saturated region. Many linearisation techniques are used in practice, such as feedback, feedforward, linear amplification with non-linear components (LINC), envelope elimination and restoration (EER), digital and analogue predistortion.

Feedback is the simplest method of reducing PA distortion. It uses the difference between the PA's input and output signal to compensate for the distortion components. Feedback linearisation can reduce the distortion as long as the feedback loop has sufficient loop gain. The feedback technique can be divided into four categories, viz. envelope, Cartesian, polar and RF feedback [43]. Cartesian feedback is widely used in PA linearisation; it is a

baseband feedback linearisation technique and strictly speaking should be referred to as a transmitter linearisation technique. Current Cartesian feedback techniques have been able to achieve 8.2 dB ACLR suppression [44] and 10 dB distortion reduction in [45].

Feedforward linearisation is similar to feedback, but instead subtracts the difference between the PA input and output signal from the PA output signal. Feedforward has the ability to linearise a wide bandwidth and it is unconditionally stable. The disadvantage of feedforward is the complexity of the system. However, current feedforward techniques have tried to reduce this complexity by performing the feedforward function in a DSP, resulting in ACLR improvement of 10 dB [46].

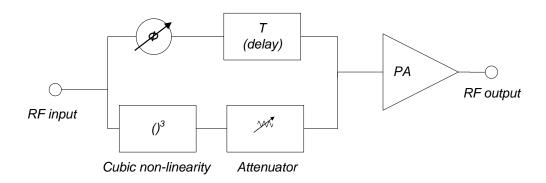

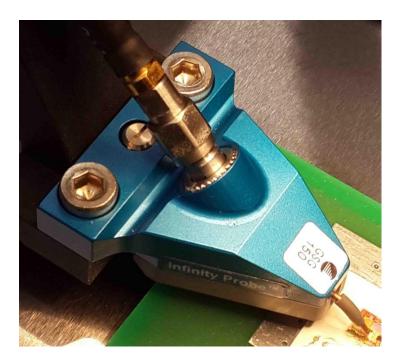

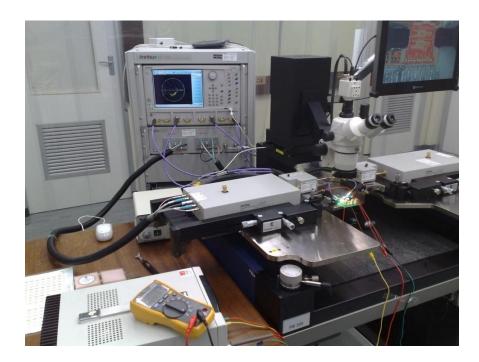

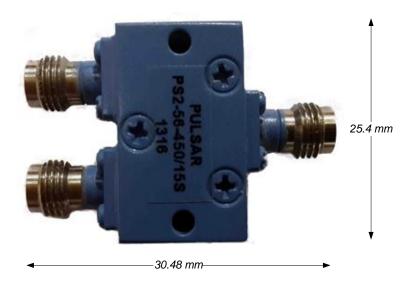

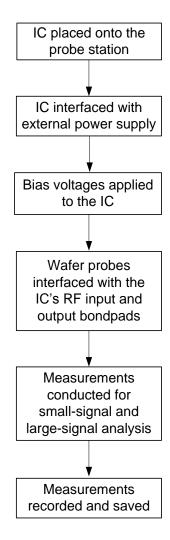

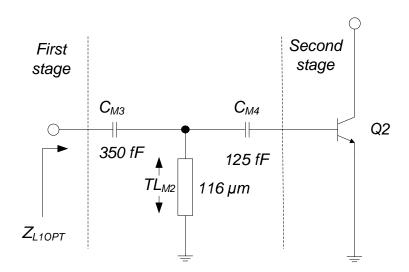

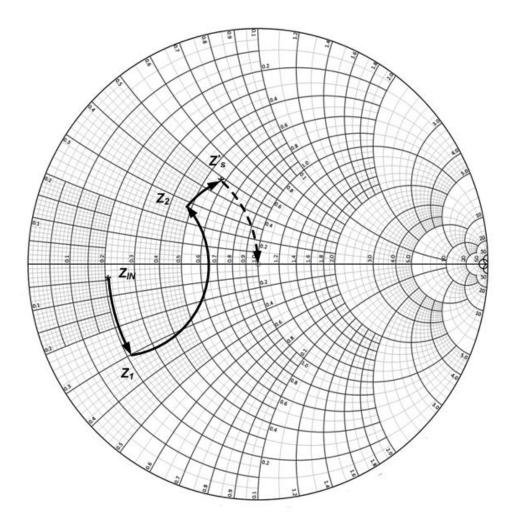

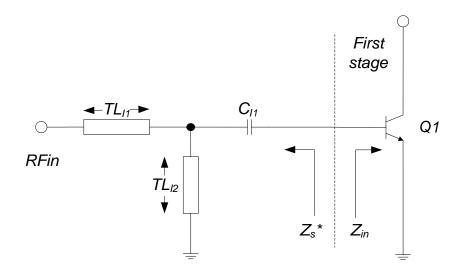

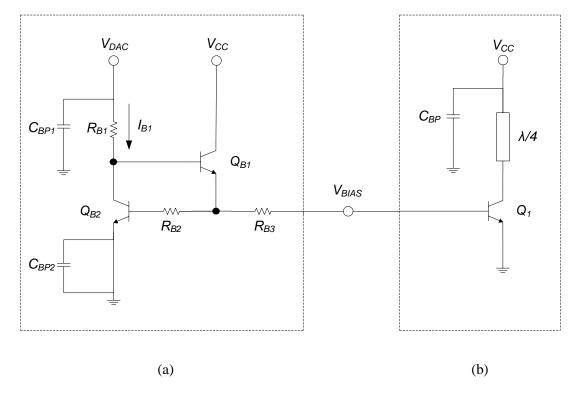

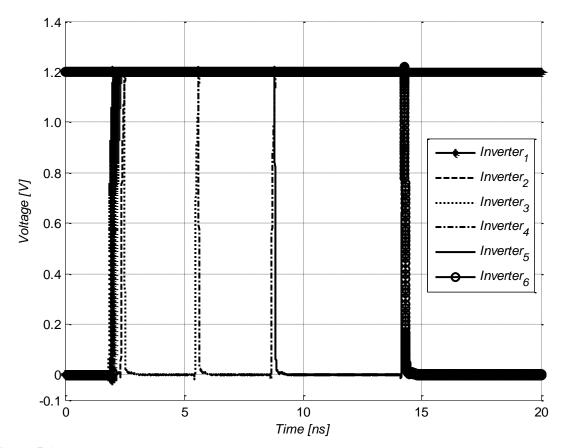

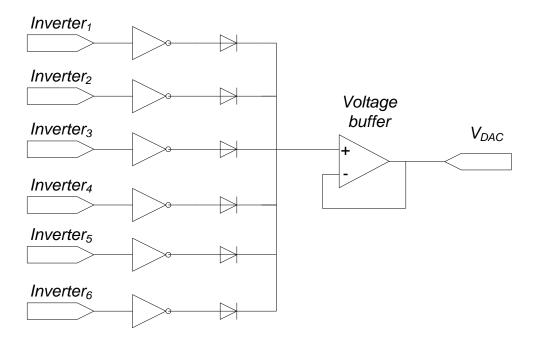

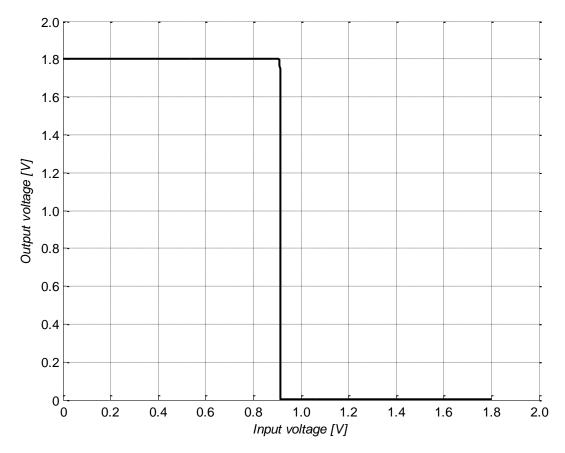

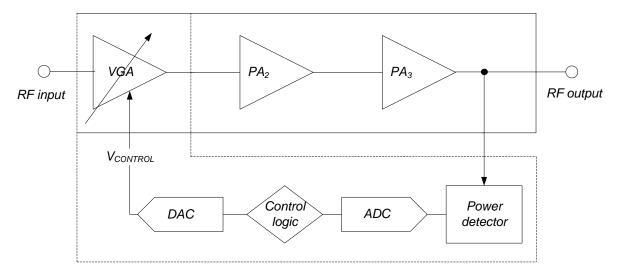

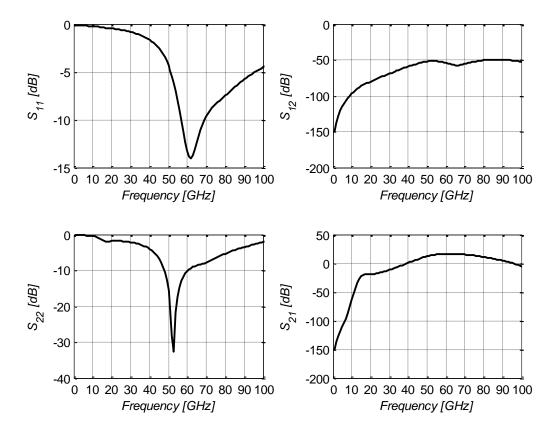

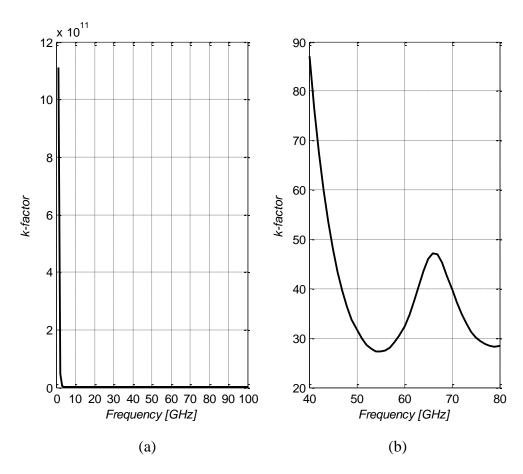

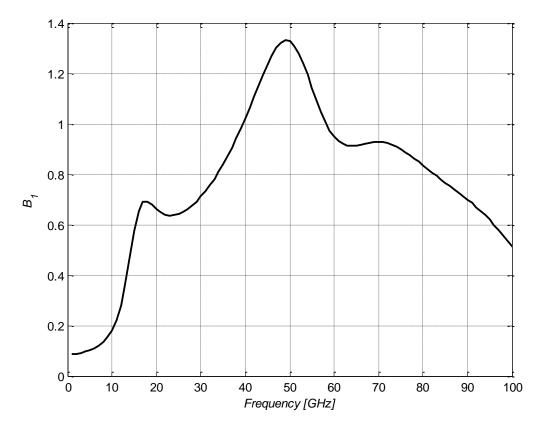

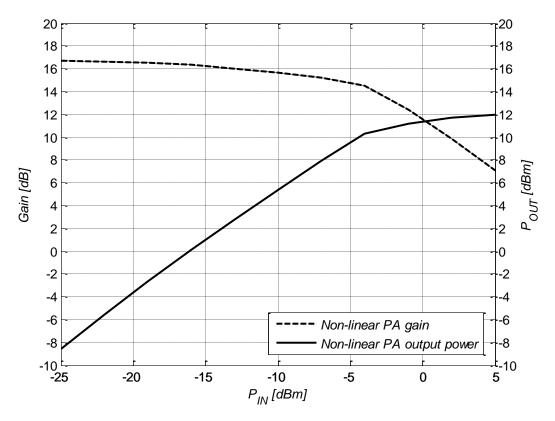

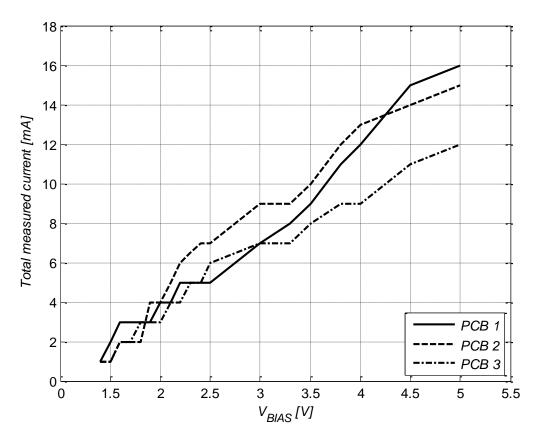

The LINC technique decomposes the amplitude varying signal into two out-phased constant envelope signals. These two signals are then amplified using high-efficiency switching mode PAs and then combined to generate a linear amplified version of the input signal. The LINC system in [47] has reported a 15 dB reduction in ACPR. The EER technique separates the input signal into two signals, viz. the amplitude and the phase. The phase signal is passed through a non-linear amplifier while the amplitude is removed. The amplitude is then returned onto the carrier by modulating the power supply of the PA. Similar to LINC, the drawback of EER is managing the synchronisation between the amplitude and the phase signals. A PA with a carrier frequency of 100 MHz using the EER technique has obtained an attenuation of the IMD3 component by 40 dB [48].