# REDUCING JITTER UTILISING ADAPTIVE PRE-EMPHASIS FIR FILTER FOR HIGH SPEED SERIAL LINKS

by

## Marius Eugene Goosen

Submitted in partial fulfilment of the requirements for the degree

**Master of Engineering (Microelectronic Engineering)**

in the

Faculty of Engineering, Built Environment & Information Technology

UNIVERSITY OF PRETORIA

February 2011

# REDUCING JITTER UTILISING ADAPTIVE PRE-EMPHASIS FIR FILTER FOR HIGH SPEED SERIAL LINKS

#### BY MARIUS EUGENE GOOSEN

Supervisor: Prof S Sinha

Department of Electrical, Electronic & Computer Engineering

Degree: MEng. (Microelectronic Engineering)

Jitter requirements have become more stringent with higher speed serial communication links. Reducing jitter, with the main focus on reducing data dependant jitter (DDJ), is presented by employing adaptive finite impulse response (FIR) filter pre-emphasis. The adaptive FIR pre-emphasis is implemented in the IBM 7WL 0.18  $\mu$ m SiGe BiCMOS process. SiGe heterojunction bipolar transistors (HBTs) provide high bandwidth, low noise devices which could reduce the total system jitter. The trade-offs between utilising metal oxide semiconductor (MOS) current mode logic (CML) and SiGe bipolar CML are also discussed in comparison with a very high  $f_T$  (IBM 8HP process with  $f_T$  = 200 GHz) process. A reduction in total system jitter can be achieved by keeping the sub-components of the system jitter constant while optimising the DDJ.

High speed CML circuits have been employed to allow data rates in excess of 5 Gb/s to be transmitted whilst still maintaining an internal voltage swing of at least 300 mV. This allows the final FIR filter adaptation scheme to minimise the DDJ within 12.5 % of a unit interval, at a data rate of 5 Gb/s implementing 6 FIR pre-emphasis filter taps, for a worst case copper backplane channel (30" FR-4 channel). The implemented integrated circuit (IC) designed as part of the verification process takes up less than 1 mm<sup>2</sup> of silicon real estate.

In this dissertation, SPICE simulation results are presented, as well as the novel IC implementation of the proposed FIR filter adaptation technique as part of the hypothesis verification procedure. The implemented transmitter and receiver were tested for functionality, and showed the successful functional behaviour of all the implemented CML gates associated with the first filter tap. However, due to the slow charge and discharge rate of the pulse generation circuit in both the transmitter and receiver, only the main operational state of the transmitter could be experimentally validated. As a result of the adaptation scheme implemented, the contribution in this research lies in that a designer

utilising such an IC can optimise the DDJ, reducing the total system jitter, and hence increasing the data fidelity with minimal effort.

**Keywords:** High speed serial links, backplane serial link, jitter, data dependant jitter, inter-symbol interference, FIR pre-emphasis, adaptive pre-emphasis, SiGe, BiCMOS, IBM  $7WL\ 0.18\ \mu m\ BiCMOS$ .

## VERMINDERING VAN TYDAFWYKING DEUR GEBRUIK TE MAAK VAN 'N SELF-AANPASBARE VOORAFBEKLEMTOONDE FIR FILTER VIR HOË SPOED SERIE KOMMUNIKASIE

#### DEUR MARIUS EUGENE GOOSEN

Toesighouer: Prof. S Sinha Departement Elektriese, Elektroniese en Rekenaars-ingenieurswese

Graad: MIng. (Mikroelektroniese Ingenieurswese)

Tydafwyking spesifikasies het strenger geword met hoër spoed seriekommunikasie koppelinge. Vermindering van die tydafwyking, met die fokus op die vermindering van data afhanklike tydafwyking (DDJ), word aangebied deur gebruik te maak van selfaanpasbare, eindigende impuls respons (FIR) filter voorafbeklemtoning. Die selfaanpasbare FIR voorafbeklemtoning is geïmplementeer in die IBM 7WL 0.18 μm SiGe BiCMOS proses.

SiGe hetero-vlak bipolêre transistors (HBTs) voorsien hoë bandwydte, lae ruis komponente om moontlik die totale stelsel tydafwyking te verminder. Die oorwegings tussen die gebruik van metaaloksied halfgeleier (MOS) stroom-mode logika (CML) en bipolêre CML word ook bespreek in vergelyking met 'n baie hoë  $f_T$  proses (IBM 8HP proses met  $f_T$  = 200 GHz). 'n Vermindering in totale stelsel tydafwyking kan behaal word deur die subkomponente van die stelsel tydafwyking konstant te hou terwyl die DDJ geoptimeer word.

Hoë spoed CML stroombane is geïmplementeer om die transmissie van datatempos van meer as 5 Gb/s moontlik te maak en steeds 'n interne spanning swaai van meer as 300 mV te behou. Gevolglik minimeer die finale self-aanpasbare FIR voorafbeklemtonings filter die DDJ tot binne 12.5 % van 'n eenheidsinterval, met die implementasie van 6 FIR voorafbeklemtonings filtertappe en teen 'n datatempo van 5 Gb/s, vir 'n swak koper rugkantkanaal (30" FR-4 kanaal). Die geïmplementeerde geïntegreerde stroombaan (IC) is ontwerp as deel van die verifiëringsproses en beslaan minder as 1 mm² silikon eiendom.

In hierdie verhandeling word SPICE simulasie resultate, sowel as die nuwe IC implementasie van die voorgestelde self-aanpasbare FIR filter tegniek as deel van die hipotese verifiëringsproses aangebied. Beide die sender en ontvanger van die stelsel is getoets vir funksionaliteit en het getoon dat die sender CML-stroombane ge-assosieer met

die eerste filtertap suksesvol werk. Ongelukkig, as gevolg van lae laai en ontlaai tempos van die puls bronne in beide die sender en die ontvanger kon slegs die hoof toestand van die stelsel eksperimenteel getoets word. As gevolg van die self-aanpasbare skema wat geïmplementeer word, berus die bydrae van die navorsing dat 'n ontwerper wat van so 'n IC gebruik maak, die DDJ kan optimeer. Dit het tot gevolg dat die totale stelsel tydafwyking verminder kan word en sodoende die data integriteit kan verbeter met minimale moeite.

**Sleutelwoorde:** Hoë spoed serie kommunikasie, tyddeviasie, data afhanklike tyddeviasie, inter-simbool interferensie, voorafbeklemtoonde FIR filter, self-aanpasbare voorafbeklemtoning, SiGe, BiCMOS, IBM 7WL 0.18 µm BiCMOS.

## **ACKNOWLEDGMENTS**

I would firstly like to thank our heavenly Father for my talents and strength to carry this through. I would also like to thank Karen Mostert, my family (Eugene and Trudie Goosen, Frikkie and Liesel Fourie, Roelf and Lydia Mostert) for all their help and encouragement. I would especially like to thank Karen for her proofreading as well.

Then, I would like to thank my friends in CEFIM, Jannes Venter, Wayne MacLean, Mladen Božanić, Marnus Weststrate, Johan Schoeman and Christo Janse van Rensburg who have been there with advice whenever I needed it. I would also like to thank my study leader, Prof Saurabh Sinha for his support, time and effort that he put into this. I would also like to thank Mrs Loubser for all the effort she puts in to keep CEFIM operating like it is.

I also thank Armscor, the Armaments Corporation of South Africa Ltd, (Act 51 of 2003) and the Council for Scientific and Industrial Research (CSIR) for the financial support for the duration of the dissertation. Without their financial support it would not have been possible to carry out this research. I also thank MOSIS for the approval of our educational wafer run, allowing us to tape-out in testing and validation of the hypothesis under question.

In the words of Albert Einstein: Science is the attempt to make the chaotic diversity of our sense-experience correspond to a logically uniform system of thought.

## TABLE OF CONTENTS

| ACKNOWLEDGMENTS                                                  | VI  |

|------------------------------------------------------------------|-----|

| TABLE OF CONTENTS                                                | VII |

| LIST OF ABBREVIATIONS                                            | IX  |

| CHAPTER 1: INTRODUCTION                                          | 1   |

| 1.1 BACKGROUND TO THE RESEARCH                                   |     |

| 1.2 RESEARCH PROBLEM AND HYPOTHESIS                              |     |

| 1.3 JUSTIFICATION FOR THE RESEARCH                               | 4   |

| 1.4 Methodology                                                  | 5   |

| 1.5 RESEARCH CONTRIBUTION                                        |     |

| 1.6 OUTLINE OF THE DISSERTATION                                  |     |

| 1.7 DELIMITATIONS OF THE SCOPE OF THE RESEARCH                   |     |

| 1.8 Conclusion                                                   |     |

| CHAPTER 2: LITERATURE REVIEW                                     |     |

| 2.1 Introduction                                                 |     |

| 2.2 HIGH SPEED SERIAL COMMUNICATION                              |     |

| 2.2.1 Overview                                                   |     |

| 2.2.2 Trends and standards                                       |     |

| 2.2.3 Different types of serial links and data transfer rates    |     |

| 2.2.5 Backplane serial communication links                       |     |

| 2.2.6 Backplane channel modelling                                |     |

| 2.3 JITTER                                                       |     |

| 2.3.1 Jitter in high speed serial links                          |     |

| 2.3.2 Causes of jitter in high speed serial links                |     |

| 2.3.3 Mathematical definitions                                   |     |

| 2.3.4 Eye diagram analysis                                       |     |

| 2.3.5 Statistical jitter analysis                                |     |

| 2.4 Integrated circuit technology                                |     |

| 2.5 REDUCING JITTER IN HIGH SPEED SERIAL COMMUNICATION LINKS     |     |

| 2.5.1 Overcoming data dependant jitter                           |     |

| 2.5.2 Equalisation                                               |     |

| 2.5.3 Pre-emphasis                                               |     |

| 2.5.5 FIR filter implementation                                  |     |

| 2.6 CONCLUSION                                                   |     |

| CHAPTER 3: RESEARCH METHODOLOGY                                  |     |

|                                                                  |     |

| 3.1 Introduction                                                 |     |

| 3.2 JUSTIFICATION FOR THE PARADIGM AND METHODOLOGY               |     |

| 3.3 RESEARCH METHODOLOGY AND OUTLINE                             |     |

| 3.4.1 Mathematical modelling                                     |     |

| 3.4.2 Circuit level modelling and simulation                     |     |

| 3.4.3 Layout design and verification.                            |     |

| 3.5 SPICE MODELS USED IN THE DESIGN                              |     |

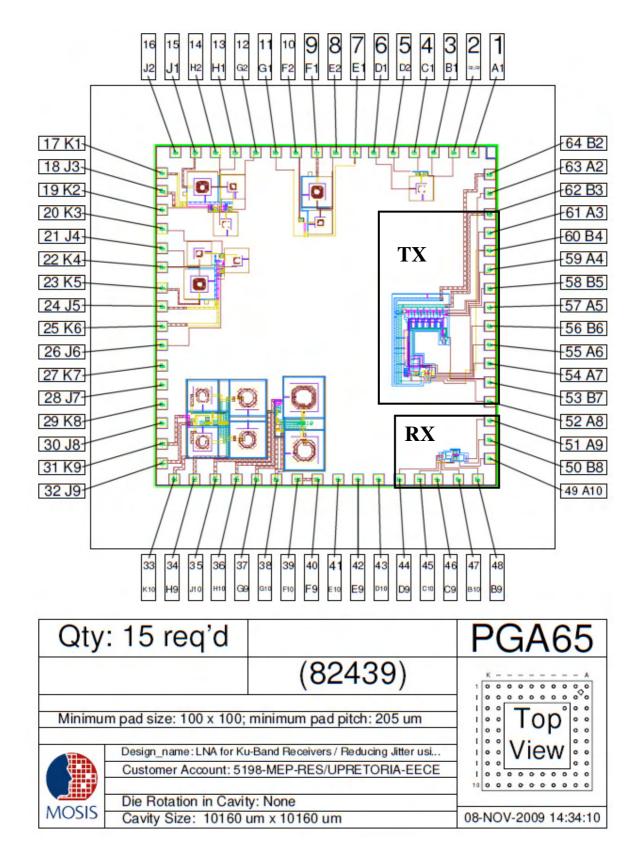

| 3.6 PACKAGING AND EXPERIMENTAL MEASUREMENT EQUIPMENT             | 46  |

| 3.7 Measurement setup                                            | 48  |

| 3.8 CONCLUSION                                                   | 50  |

| CHAPTER 4: MATHEMATICAL AND SYSTEMS DESIGN                       | 51  |

| 4.1 Chapter organisation                                         | 51  |

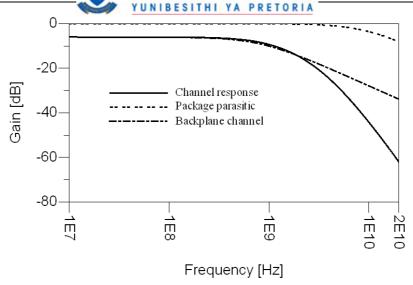

| 4.2 MATHEMATICAL MODELLING OF CHANNEL RESPONSE                   |     |

| 4.2.1 Package parasitic modelling                                |     |

| 4.2.2 Copper backplane channel                                   |     |

| 4.2.3 Complete channel response                                  |     |

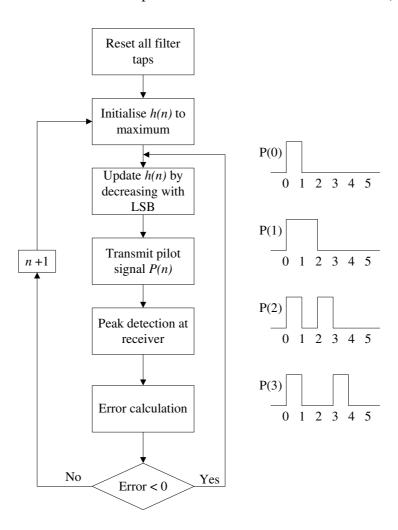

| 4.3 MATHEMATICAL MODELLING OF ADAPTIVE FIR FILTER IMPLEMENTATION |     |

| т.э.1 Quantanve aescription ој те итритенича адарианон SCHeme    | 9/  |

| UNIVERSITEIT VAN PRETORIA<br>UNIVERSITY OF PRETORIA                 |     |

|---------------------------------------------------------------------|-----|

| YUNIBESITHI YA PRETORIA                                             |     |

| 4.3.2 Quantitative description of the implemented adaptation scheme |     |

| 4.3.3 Mathematical simulation results                               |     |

| 4.4 BIPOLAR CML VERSUS MOS CML                                      |     |

| 4.4.1 Background                                                    |     |

| 4.4.3 Rise and fall times                                           |     |

| 4.5 COMPLETE SYSTEM INTEGRATION                                     |     |

| 4.6 PILOT SIGNAL GENERATOR                                          |     |

| 4.7 Adaptive FIR pre-emphasis driver                                |     |

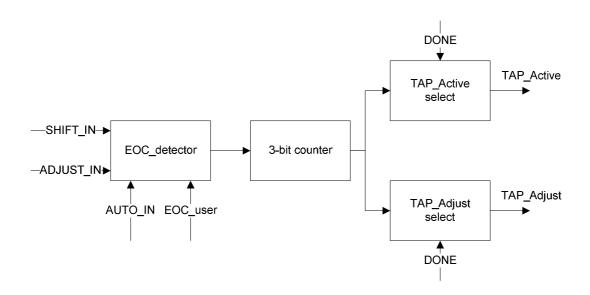

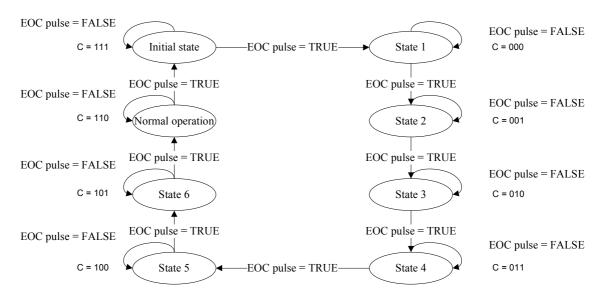

| 4.8 Control logic design.                                           |     |

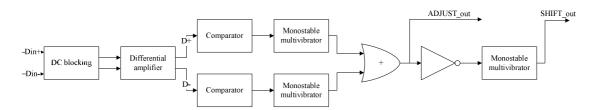

| 4.9 Receiver design                                                 |     |

| 4.10 CONCLUSION                                                     | 87  |

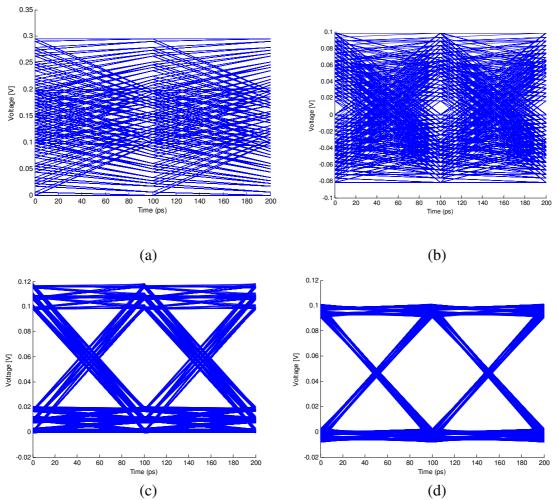

| CHAPTER 5: SIMULATION RESULTS                                       | 88  |

| 5.1 Introduction                                                    | 88  |

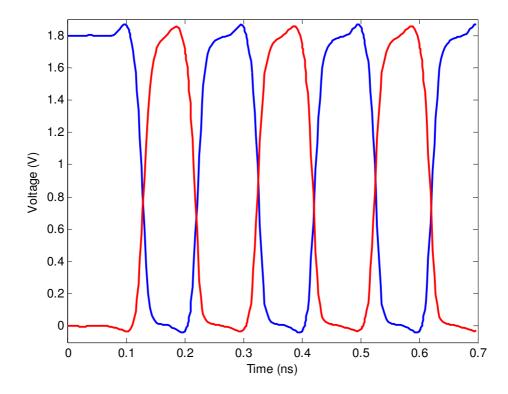

| 5.2 PILOT SIGNAL GENERATOR                                          |     |

| 5.3 CONTROL LOGIC                                                   |     |

| 5.4 Receiver                                                        |     |

| 5.5 ADAPTIVE FIR PRE-EMPHASIS DRIVER                                |     |

| 5.6 CONCLUSION                                                      |     |

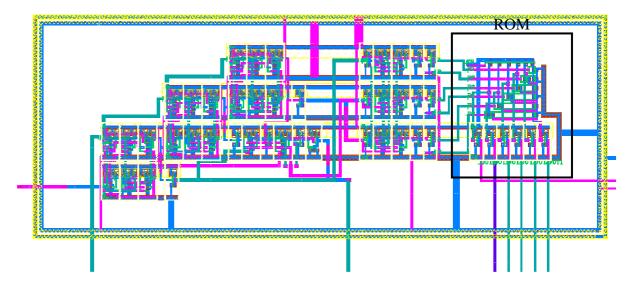

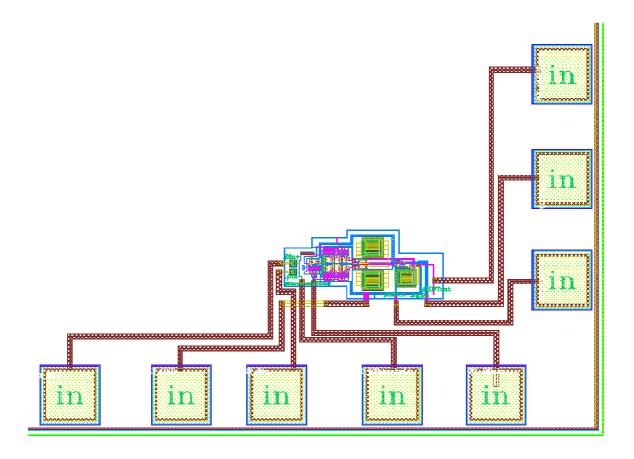

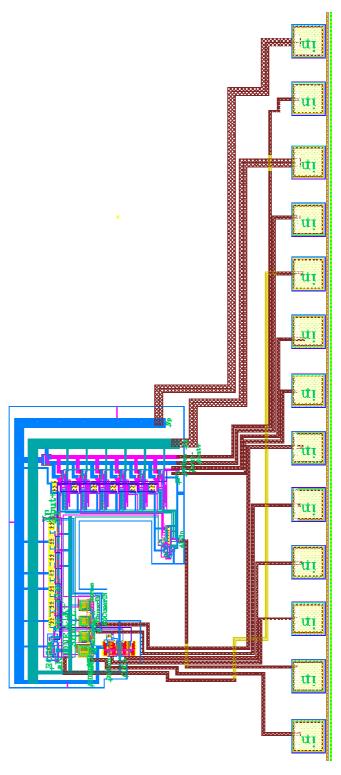

| CHAPTER 6: LAYOUT AND FABRICATION                                   |     |

| 6.1 Introduction                                                    |     |

| 6.2 CIRCUIT LAYOUTS                                                 |     |

| 6.3 TRANSCEIVER CONFIGURATION                                       |     |

| 6.4 LAYOUT CONSIDERATIONS                                           |     |

| 6.5 CONCLUSION                                                      |     |

| CHAPTER 7: EXPERIMENTAL RESULTS                                     |     |

| 7.1 Introduction                                                    |     |

| 7.2 MANUFACTURING AND MOUNTING                                      |     |

| 7.3 TRANSMITTER RESULTS                                             |     |

| 7.4 Receiver results                                                |     |

| 7.5 POWER DISSIPATION                                               |     |

| 7.6 CONCLUSION                                                      |     |

| CHAPTER 8: CONCLUSION                                               |     |

| 8.1 Introduction                                                    |     |

| 8.2 CRITICAL EVALUATION OF THE HYPOTHESIS                           |     |

| 8.3 LIMITATIONS AND ASSUMPTIONS                                     |     |

|                                                                     |     |

| REFERENCES                                                          |     |

| APPENDIX A: MATLAB CODE FOR FIR ADAPTATION                          | 125 |

APPENDIX B: DETAILED LAYOUTS OF THE SYSTEM

130

APPENDIX C: DATASHEET FOR THE PRE-EMPHASIS IMPLEMENTATION

136

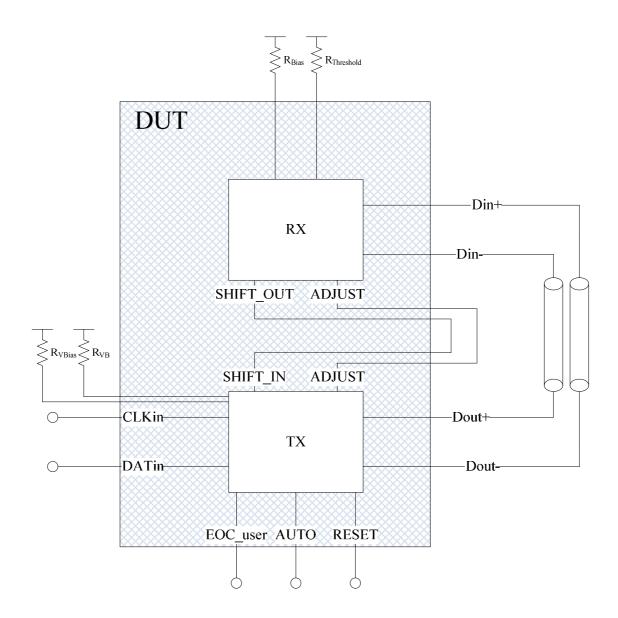

OVERVIEW

136

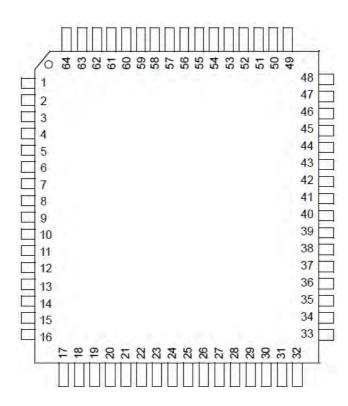

PIN LAYOUT AND DESCRIPTION

136

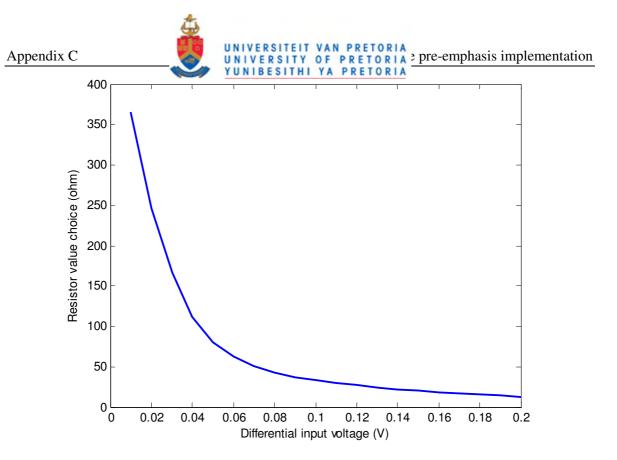

BIASING RESISTORS

138

Transmitter

138

Receiver

138

THRESHOLD VOLTAGE

138

### LIST OF ABBREVIATIONS

ADE Analog design environment

AMS Austriamicrosystems

BER Bit error rate

BERT BER tester

BCML Bipolar CML

BiCMOS Bipolar complementary metal oxide semiconductor

BGA Ball grid array

BJT Bipolar junction transistor

BUJ Bounded uncorrelated jitter

CDF Cumulative distribution function

CDR Clock and data recovery

CML Current mode logic

CMOS Complementary metal oxide semiconductor

DAC Digital to analogue converter

DCD Duty cycle distortion

DDJ Data dependant jitter

DFE Decision feedback equaliser

DFF D-flip-flop

DJ Deterministic jitter

DRC Design rule check

DSP Digital signal processor

DUT Device under test

ECL Emitter coupled logic

EDA Electronic design automation

EMI Electromagnetic interference

EOC End of conversion

ESD Electro-static discharge

FFE Feed forward equaliser

FIR Finite impulse response

FPGA Field programmable gate array

FSF Fractionally spaced filter

GaAs Gallium arsenide

HBT Heterojunction bipolar transistor

HIT-Kit High performance interface toolkit

IBM International business machines corporation

IC Integrated circuit

IEEE Institute of electrical and electronic engineers

IIR Infinite impulse response

InP Indium phosphide

I/O Input/ output

IP Internet protocol

ISI Inter-symbol interference

LMS Least mean squares

LSB Least significant bit

LTI Linear time invariant

LVDS Low voltage differential signalling

LVS Layout versus schematic

MOS Metal oxide semiconductor

MOSIS MOS implementation system

MEP MOSIS educational program,

MOSFET MOS field effect transistor

MPW Multi-project wafer

MSE Mean square error

NPF Network processing forum

NRZ Non-return to zero

OIF Optical internetworking forum

PAM Pulse amplitude modulation

PCB Printed circuit board

PCI-SIG Peripheral component interconnect – special interest group.

PDF Probability density function

PJ Periodic jitter

PLL Phase locked loop

PPM Pulse position modulation

PRBS Pseudo random bit sequence

PWM Pulse width modulation

QFN Quad flat no-lead

RF Radio frequency

RJ Random jitter

RMS Root mean square

ROM Read only memory

RX Receiver

RZ Return to zero

SerDes Serialiser and deserialiser

SiGe Silicon germanium

SMA Sub-Miniature version A

SNR Signal-to-noise ratio

SPICE Simulation program with integrated circuit emphasis

SSF Symbol space filter

TJ Total jitterTX TransmitterUI Unit interval

VBIC Vertical bipolar inter-company

VCO Voltage controlled oscillator

XOR Exclusive-or

## **CHAPTER 1: INTRODUCTION**

#### 1.1 Background to the research

The popularity of serial communication links has outgrown conventional parallel links due to its high bandwidth implementation ability immune to clock skew between data buses [1]. The reduced pin count of serial links coupled with its high bandwidth capability increases the bandwidth per pin allowing for lower cost and higher component population density on implementation. High speed serial links do however suffer its own set of non-idealities, one of which is jitter.

There are various ways to implement serial communication links each set apart by the type of channel implemented. Serial communication link channels can consist of plain copper cable, fibre optic cable or backplane copper channels. A backplane copper channel is the preferred type of transmission media for discrete system implementations and is the focus of this research.

Integrated circuit (IC) technology plays an important part in high speed serial communication links. ICs provide high bandwidth circuits and devices with which high speed serial link transceivers can be developed and implemented. Complementary metal oxide semiconductor (CMOS) devices have been the popular choice for implementing high speed serial link transceivers, but improved silicon germanium (SiGe) bipolar CMOS (BiCMOS) processes simultaneously provide high bandwidth, low noise, low base resistance and high current gain which make it a great contender in radio frequency (RF) IC design [2].

Jitter requirements in high speed serial links are becoming increasingly stringent due to the small pulse widths associated with increased data transfer rates. Channel bandwidth limitations restrict current serial links on the maximum achievable data transfer rates and various techniques are being implemented to alleviate or bypass this limitation. Alleviating the channel limitation will prove to be a significant contribution for future high speed serial links over copper channels with data transfer rates in the excess of 10 Gb/s.

An example of the stringent jitter requirements is presented in [3]. With a data transfer rate of 10 Gb/s utilising non-return to zero (NRZ) signalling, the root mean square (RMS)

value of the total jitter should be below 0.7 ps to achieve a bit error rate (BER) of less than  $10^{-12}$ . This jitter requirement is about 10 % of the transmitted pulse width.

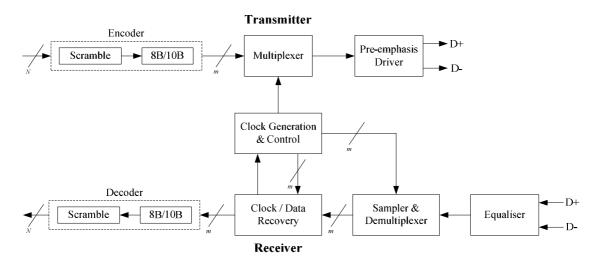

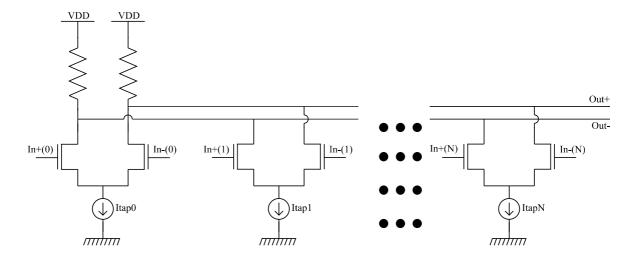

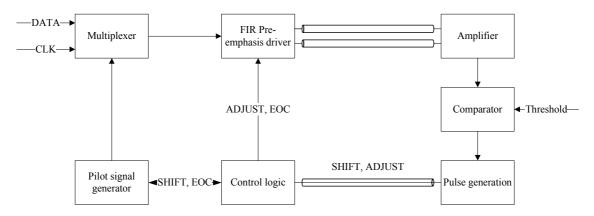

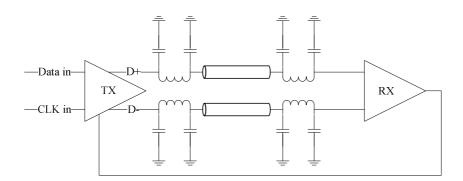

Data dependant jitter (DDJ) is one of the main contributors to the total system jitter [4]. This type of deterministic jitter (DJ) is caused by the channel bandwidth limitation. The channel bandwidth limitation exhibits a low pass filter response attenuating the different frequency components within the data signal by different amounts. Thus higher data rates result in lower amplitude signals at the receiver as well as received signals exhibiting a long "tail", directly interfering with adjacent bits. This leads to uncertainty in determining the exact pulse edge with regards to the optimal sampling instant. To alleviate the DDJ imposed by the backplane channel, the transmitted data is pre-distorted by a pre-emphasis filter. Figure 1.1 illustrates the subsystems within a typical serialiser and deserialiser (SerDes) serial link and the context of a pre-emphasis filter in the system.

Figure 1.1. Subsystems depicting a typical SerDes serial link employing pre-emphasis in the transmitter. Adapted from [5].

Figure 1.1 shows the common subsystems depicting a typical serial communication link. A number *N* low speed data lines are encoded and retimed to be combined into a single serial bit stream. In a system employing NRZ signalling, this bit stream is ready for transmission. Pre-emphasis is employed in the driver just before transmission in order to decrease the inter-symbol interference (ISI) present at the receiver. The data bit stream is then transmitted over the bandwidth limited channel utilising low voltage differential signalling (LVDS).

The distorted data with embedded clock is received and equalised to open the eye diagram for sampling to increase the data integrity. The clock is recovered from the data and is used to recover the data with as little as possible erroneous bits. The recovered serial bit stream is de-serialised and decoded into the same amount, *N*, low speed data lines.

An 8B/10B transmission method has become a standard for many high speed serial links [5]. The 8B/10B encoding scheme creates a DC balanced bit stream, thus equal amount of positive and negative pulses, preventing any distortion caused by AC coupling [6]. Furthermore, together with scrambling, the encoding ensures at least one signal transition in every five transmitted bits [6]. This provides efficient signal transitions for stable clock and data recovery.

#### 1.2 Research problem and hypothesis

DDJ caused by backplane channel bandwidth limitations imposes a restriction on the maximum achievable data transfer rates [7]. Alleviating DDJ while keeping other jitter subcomponents small in relation to the data pulse width opens a new possibility of increased data transfer rates or alternatively reduced BERs. Alleviating DDJ by reducing the effect of the bandwidth limitations of the channel has been exploited by various designers [1], [8], [9], [10], [11], [12], [13].

High speed serial links have been widely implemented to achieve high data transfer rates otherwise not achievable by conventional parallel links. Table I illustrates some of the high speed serial links implemented as well as the type of implementation technology used.

TABLE I.

COMPARISON OF IMPLEMENTED SERIAL LINKS

| Reference | Data rate | Technology  | Pre-emphasis |

|-----------|-----------|-------------|--------------|

| [1]       | 10 Gb/s   | CMOS        | 5-tap FIR    |

| [3]       | 10 Gb/s   | SiGe BiCMOS | None         |

| [8]       | 5 Gb/s    | CMOS        | 3-tap FIR    |

| [9]       | 10 Gb/s   | CMOS        | 3-tap FIR    |

| [10]      | 5 Gb/s    | CMOS        | 3-tap FIR    |

| [11]      | 10 Gb/s   | CMOS        | 3-tap FIR    |

| [12]      | +10 Gb/s  | CMOS        | 8-tap FIR    |

| [13] | 8 Gb/s | CMOS | 3-tap FIR |

|------|--------|------|-----------|

| [14] | 1 Gb/s | CMOS | None      |

Although high speed serial links have been widely implemented using CMOS technology, few attempts have been made using SiGe. Furthermore, serial link designs that have not utilised pre-emphasis are only implemented for use over cables or shorter distances [3]. The proposed research is focused on backplane copper channels which by its nature has higher distortion and attenuation. Although CMOS technology is a more economically viable solution for the implementation of a serial link, SiGe technology provides numerous advantages to be investigated in designing higher performance serial links.

Pre-emphasis has been implemented to pre-distort the transmitted signal by emphasising the high frequency components attenuated by the channel. Finite impulse response (FIR) filters are the preferred type of transmitter pre-emphasis implemented due to its ease of implementation and its easy adjustable nature. Channel impulse responses change for each application and initial installation and tuning of a fixed pre-emphasis filter can become tedious due to its trial and error nature.

A need for adaptive pre-emphasis clearly exist whereby the optimal tap coefficients of the FIR filter can reached automatically without the need for tedious tuning processes. The adaptive FIR pre-emphasis filter research can be stated by means of the following hypothesis:

A fully functional high speed serial link transmitter employing adaptive FIR pre-emphasis filtering implemented in the 0.18 µm SiGe BiCMOS process for the improvement of off-chip bandwidth and data speeds. The adaptive FIR pre-emphasis filter is proposed to reduce DDJ and improve the timing and sampling uncertainty introduced by it, hence improving the BER of the serial link.

#### 1.3 Justification for the research

Serial communication links have been established as a well developed technology, but this does not mean that the technology market for high speed serial links has been saturated. Data transfer rates are on the increase and overcoming current limitations is one of the

main challenges remaining in achieving higher data transfer rates. Thus the design challenges are far from over, as discussed in [15].

Adaptive pre-emphasis provides the advantage of always pre-distorting the transmitted data by the optimal amount leading to an optimally open eye diagram at the far end of the serial link. Thus, higher data transfer rates could be realised if the channel bandwidth limitation is optimally alleviated.

In order to keep the delays imposed by the implemented technology to a minimum, the gate delay has to be as small as possible to achieve the necessary switching speed. Table II illustrates the gate delays of three popular SiGe technologies. The respective technologies are from international business machines (IBM) corporation and Austriamicrosystems (AMS).

TABLE II. GATE DELAY COMPARISON

|                      | IBM 8HP SiGe | IBM 7WL SiGe | AMS S35 SiGe     |

|----------------------|--------------|--------------|------------------|

| Minimum Feature size | 0.13 μm      | 0.18 μm      | 0.35 μm          |

| <b>Gate Delay</b>    | 0.01 ns      | 0.05 ns      | 0.1 ns (typical) |

For data speeds in the region of 10 Gb/s the signal period is about 0.1 ns, thus clearly from Table II, the IBM 8HP process should be chosen for the application at hand. The possible advantages that could be gained from utilising the IBM 8HP process over the IBM 7WL process are presented in Chapter 4. Due to budgetary constraints, as well as a research grant from MOS implementation system (MOSIS¹) for a free wafer run under their MOSIS educational program (MEP), the SiGe technology used to validate the hypothesis is the IBM 7WL process. This process still outperforms the AMS S35 SiGe process as can be seen in Table II, giving the advantage to be able to use fast bipolar devices to possibly provide faster switching circuits. This is discussed in section 4.4.

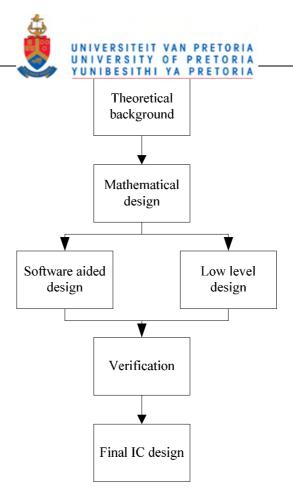

#### 1.4 Methodology

High speed serial links are mainly integrated on ICs to achieve high speed capability and maintain low noise. Modern integrated circuit processes have increased in speed and noise performance allowing the designer to improve previous designs with the use of higher

www.mosis.com. MOSIS approved an educational run suitable for this research.

bandwidth devices and circuits. SiGe processes are becoming the technology of choice where high signal integrity is important. These implementations, previously dominated by the more expensive indium phosphide (InP) and gallium arsenide (GaAs) processes, are moving towards SiGe implementations due to lower cost while maintaining comparable noise performance. SiGe heterojunction bipolar transistors (HBTs) however do not necessarily provide an increase in performance under certain conditions as is discussed in this dissertation.

#### 1.5 Research contribution

A method of adaptive FIR pre-emphasis for application in a high speed serial link has been proposed, evaluated and implemented as part of this research. Although the fundamental idea of pilot signalling and peak detection is not novel [16], the implementation and the test of the hypothesis through an IC design is to the authors' knowledge completely novel. A detailed list of the resulting contributions to the body of knowledge is given here.

- The pilot signalling and peak detection method of determining the optimal FIR filter tap coefficients has been demonstrated both on a mathematical level as well as on a circuit level.

- The reduction in DDJ achieved through the implementation of such a FIR filtering pre-emphasis scheme is also presented.

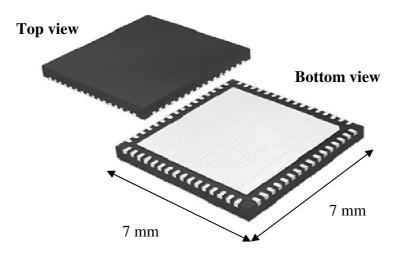

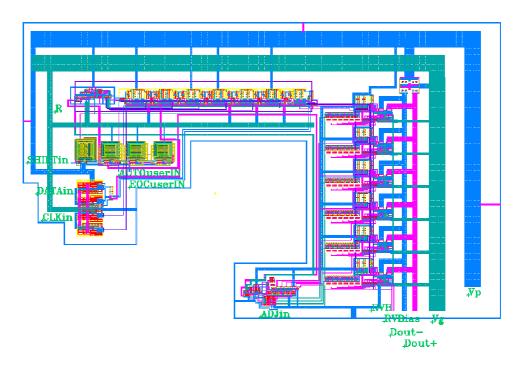

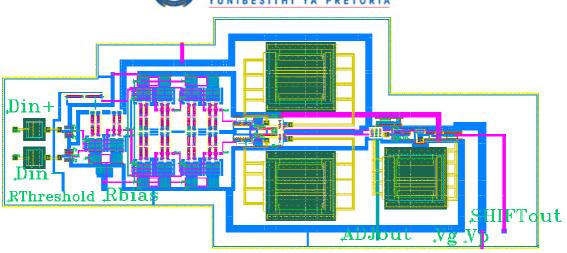

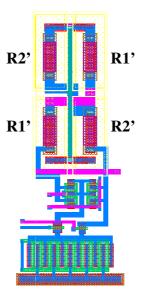

- The novel prototype design for testing the proposed hypothesis occupies an area of 0.8 mm<sup>2</sup>. The design incorporated CMOS circuits for low speed switching and control circuits and current mode logic (CML) circuits for high speed switching in the order of 5 10 GHz.

- The advantages of utilising HBTs in CML drivers has been presented and compared regarding the unity gain frequency, and comparing to optimally sized MOS CML. The final design utilised only CMOS devices for the complete system design.

- The circuit level implementation has been verified through simulations in Cadence Virtuoso using the chosen IBM high performance interface toolkit (HIT-Kit). The prototype IC has been submitted for fabrication as part in a multi-project wafer (MPW) run.

The fabricated IC was mounted on a custom designed printed circuit board (PCB)

for experimental hypothesis validation. The experimental validation of the

transmitter and receiver is presented, although limited due to unexpected outcomes

of a critical subsystem.

The following peer reviewed conference articles have been published and presented as part of this research:

- M.E. Goosen, S. Sinha, A. Müller and M. du Plessis, "A low switching time transmitter for high speed adaptive pre-emphasis serial links," *Proc. of IEEE CAS* 2009, pp. 481-484, Sinaia, 12-14 Oct. 2009.

- M.E. Goosen and S. Sinha, "Analysis of adaptive FIR filter pre-emphasis for high speed serial links", *Proc. of IEEE Africon* 2009, Nairobi, 23-26 Sept. 2009.

- M.E. Goosen and S. Sinha, "Adaptive FIR filter pre-emphasis for high speed serial links," *Proc. of the South African conf. on semi and superconductor technology* (SACSST), Stellenbosch, pp. 37-42, 8-9 April 2009.

The author has also submitted two articles to accredited (listed by the Institute for Scientific Information (ISI)) peer reviewed journals on the following topics:

- M.E. Goosen and S. Sinha, "Reducing data dependent jitter utilising adaptive FIR pre-emphasis in 0.18 µm CMOS", submitted to *Elsevier Microelectronics Journal*.

- M.E. Goosen and S. Sinha, "A low switching time BiCMOS CML transmitter for high speed adaptive pre-emphasis serial links", submitted to *Romanian Journal of Information Science and Technology (ROMJIST)*.

#### 1.6 Outline of the dissertation

The dissertation is organised as follows:

☐ Chapter 1: Introduction

The chapter introduces the research problem to be addressed as well as the hypotheses and motivation behind the research. The research conducted is placed into context with other research conducted globally as well as common implementation practices.

#### ☐ Chapter 2: Literature review

The chapter brings forward the body of knowledge incorporated within the research conducted. The chapter is divided into the four main fields of knowledge namely, high speed serial communication links, jitter, integrated circuit technology and pre-emphasis filtering and the associated implementation. The chapter serves to show the narrowing down of a broadly defined research topic to arrive at specific research questions addressed in the hypothesis.

#### ☐ Chapter 3: Research methodology

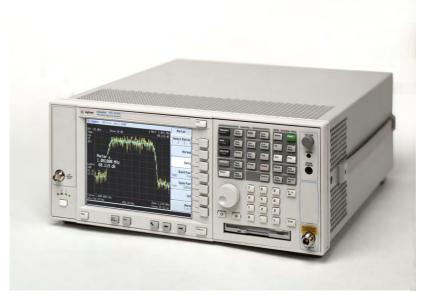

The chapter elaborates on the research methodology used for data gathering, simulation and analysis in proof of the hypothesis. Justification and limitations to the methodology is also presented and discussed. The implemented IC verification using experimental testing is also presented in this chapter. Details on the software suites used for testing of the hypothesis are also provided.

#### ☐ Chapter 4: Mathematical and systems design

The chapter describes the mathematical, system design and simulation. The chapter is divided into three main parts namely, mathematical design and simulation, system design, sub-system implementation. System design incorporates all the knowledge needed to move from a working mathematical model to a system that can be implemented. The most important aspects of the design are covered in the section about sub-system implementation.

#### ☐ Chapter 5: Simulation results

The chapter contains relevant simulation program with IC emphasis (SPICE) simulation results to verify the hypothesis under consideration. The methodology and tools used in the simulation of the system is discussed in Chapter 3.

#### ☐ Chapter 6: Layout and fabrication

The layouts of the main parts of the prototype IC are presented as well as some discussion on implementation techniques employed for improved matching.

#### ☐ Chapter 7: Experimental Results

8

This chapter contains the corresponding experimental results obtained from testing the IC after being mounted on a PCB. Although limited due to the slow charge and discharge rates of the pulse generation circuits, basic functionality of the system under the main operational state is shown.

#### ☐ Chapter 8: Conclusion and future work

The chapter finishes the dissertation with the conclusions and critical evaluation of the research hypothesis presented. The limitations to the current research are discussed, leading to a discussion on future areas of research spawning from this research, as well as proposed future technical improvements.

#### 1.7 Delimitations of the scope of the research

The scope of the research is limited to reducing DDJ imposed by the bandwidth limited copper backplane channel implemented in discrete system solutions. DDJ will be investigated and ways of alleviating the jitter requirements of current system implementations through adaptive FIR filtering will form the core of the research conducted.

#### 1.8 Conclusion

This chapter laid the core foundations for the dissertation. The core research problem and hypotheses were presented, as well as the background to the research. Abbreviations, definitions and initial methodology were presented. The organisation of the dissertation was outlined to introduce the path to be followed through the dissertation. Chapter 2 follows with a detailed literature review of the body of knowledge followed by Chapter 3 continuing with a discussion on the method for data gathering, simulation and experimental testing of the research presented. Chapter 4 contains the mathematical verification, system level design and the design considerations used in this research. The simulated and experimental results used in the verification of the hypothesis are presented in Chapter 5. Chapter 6 elaborated the layout design of the prototype IC. Chapter 7 discusses the limited experimental results achieved before Chapter 8 concludes the

research leading from this study.

### **CHAPTER 2: LITERATURE REVIEW**

#### 2.1 Introduction

In the development of discrete solutions regardless of the application field, serial communication links provide a data interconnect capable of high speed and large bandwidth with lower implementation cost. The interconnection of different systems requires a common path through which all communication should take place. Focussing on large discrete system implementations, the common path for data interconnects is provided by a backplane.

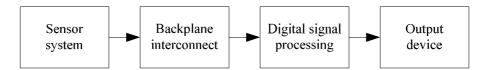

As suggested, the backplane provides interconnectivity between systems. Figure 2.1 provides an overview of how the backplane fits into a discrete system implementation.

Figure 2.1. Overview of backplane communication in discrete system level design and implementation.

Figure 2.1 illustrates a simplified block diagram of a system consisting of subsystems responsible for sensing "real-world" signals and processing it to produce information about the application. The sensor system is usually located as a separate subsystem within a larger system and is usually also physically separated from the digital signal processing unit. Thus, to provide interconnectivity between the sensors and the digital signal processing, a backplane is utilised to allow for continuity while maintaining signal integrity.

In the determination of the effectiveness of a communication system, signal integrity and data recovery are of utmost importance. The data transmitted should be able to be recovered with minimum amount of error bits received. Impediments inherent in any communication system include noise, limited channel bandwidth and jitter. All of these impediments add in degrading the performance of the communication system.

Differential serial interconnection provides various advantages over increased bus width interconnections (conventional parallel buses) [15]. By increasing the bus width the total amount of clock skew between signal lines increase, thereby negatively affecting the data integrity of the communication system. The added signal lines of the increased bus width connection also require a larger connector and ultimately a larger, more expensive solution to provide multiple line interconnections. Serial links have the advantage of a reduced pin count. By reducing the pin count and making good use of differential signalling, high speed serial connections can be established with a bandwidth exceeding that of increased bus width implementations. This inherently reduces the overall cost by increasing the bandwidth per pin unrivalled by increased bus width implementations.

When increasing the operating speed of a serial link the noise margin of the link reduces, requiring better design techniques to accompany the serial link. The most important technique is that of differential signalling. Differential signalling, by its true nature, has the ability to effectively reject common-mode noise. This is increasingly important in a discretely implemented system where matched PCB traces will have the same induced common-mode noise. Further, with the decrease in supply voltages of IC processes to provide for faster switching and higher unity gain frequencies, the noise margin becomes an increasingly important factor to consider.

LVDS is a low noise, low power and low amplitude method for high speed multi Gb/s data transmission over copper channels [15]. LVDS further reduce crosstalk and electromagnetic interference (EMI) due to the lower amplitude levels. The following section covers all aspects of a high speed serial communication link. This includes trends and standards, popular high speed serial link implementations, signalling schemes and finally copper backplane serial links which is the focus area of this research.

#### 2.2 High speed serial communication

#### 2.2.1 Overview

High speed data transport from one point to another and device integration are two of the main requirements of system development and design [15]. Demand for higher bandwidth serial links has been increasing as communication systems require higher quality of information at an increased rate [14]. This also refers to the increase in demand for userend bandwidth [3]. The goal of high speed interconnect design is the optimisation of bandwidth, power, pin count, number of wires and total implementation cost [17].

One popular application of high user-end bandwidth is in multimedia applications where high definition video is transmitted. The high definition video requires data rates of hundreds of Mb/s to a few Gb/s to satisfy the need for real time imaging [8].

The increase in the demand for high user-end bandwidth, pushing the speed of serial transceivers and channel interconnects, led to the fact that leading field programmable gate array (FPGA) suppliers provide core standards already integrated on their high-end programmable devices. Although these implementations already provide high speed serial communication links, do not mean that the design struggle to implement more reliable and faster data interconnects have been solved. In contrary, the device community is viewing such offerings as an indication that even higher data transport rates are possible, hence the design challenge continues [15]. System vendors, especially backplane vendors, want to avoid deploying new backplanes due to the high development and production costs, thus new transmitter and receiver circuit technology need to be developed to achieve increased bandwidth over legacy copper channels [9]. This also opens a market for short to medium distance serial links for use in ASICs and microprocessors [12].

#### 2.2.2 Trends and standards

In order to understand the trends of high speed serial communication links, the current requirements and limitations of existing communication links need to be understood. Many techniques have been applied to increase the bandwidth per pin such as increasing frequency, widening the interface, pipelining and out of order completion, but continuing to work with the bus creates several design issues such as increased complexity or increased noise [15].

Various standards have been established to govern the fast growing high speed serial communication link market. These include optical channels, copper cable channels and copper backplane channels. The Optical Internetworking Forum (OIF), the Network Processing Forum (NPF), the Institute of Electrical and Electronic Engineers (IEEE) and the Peripheral Component Interconnect – Special Interest Group (PCI-SIG) are only some of the institutions working on the development of commercial high speed serial links.

Ultimately, the emerging trend is that of built-in scalability that can provide for longer lasting input/output (I/O) standards both on frequency and on a data bandwidth level [15]. An example of this is the implementation of high speed serial link transceivers in leading FPGAs.

#### 2.2.3 Different types of serial links and data transfer rates

There are various types of serial links currently available in industry. These range from backplane serial communication links to cable-based serial communication links, whether it is a fibre optic cable or simply a copper cable. Fibre optic cables have the advantage over conventional copper cable for its ability to carry information over much longer distances due to its low loss. Copper on the other hand exhibits a high loss factor with a -3 dB cut-off frequency of in the region of 400 MHz [8]. Using coaxial cable (PE-142LL) a 3-dB cut-off frequency of 1.2 GHz is achieved [10]. This low pass filter effect exhibited by the copper cable causes an attenuation of more than 40 dB at 10 GHz. Table III illustrates the different types of serial links and their respective maximum achievable data transfer rates.

TABLE III.

DIFFERENT TYPES OF SERIAL LINKS AND THEIR RESPECTIVE DATA RATES.

| Standard             | Speed              | Туре                         |

|----------------------|--------------------|------------------------------|

| USB 2.0 (High speed) | 480 Mb/s           | Copper cables                |

| USB 3                | 4.8 Gb/s (Planned) | Fibre and copper cables      |

| IEEE 802.3           | 1 Gb/s             | Copper cables                |

| IEEE 1394b           | 1.6 – 3.2 Gb/s     | Copper cables and backplanes |

| Infiniband           | 2.5 Gb/s           | All                          |

| RapidIO              | 10 Gb/s            | Copper cables and backplanes |

| SATA                 | 3 Gb/s             | Copper cables                |

| Fibre Channel        | 1.0625 Gb/s        | Fibre and copper cables      |

| PCI-Express          | 2.5 Gb/s           | Copper cables and backplanes |

Table III shows some of the most popular serial communication buses and standards. RapidIO is currently increasing in popularity for its high data rates of up to 10 Gb/s. RapidIO primarily provides connectivity between components, which include digital signal processors (DSPs) and FPGAs. The problem currently faced with implementing and using RapidIO is its stringent design requirements to successfully acquire a working, high integrity RapidIO serial communication link at 10 Gb/s. Therefore, RapidIO is usually scaled down to 6.25 Gb/s.

Most FPGA manufacturers are moving toward the general trend of implementing RapidIO serial transceivers in their product. This provides the design engineer with a configurable high speed serial link to interface between other devices and systems.

Due to its high speed and hence also its high frequency content, a RapidIO link undergoes significant distortion when passed through the bandwidth limited channel. The distortion at the far end of the serial link consists mainly of DDJ. The clock jitter in the transmitter adds to the DDJ. One way to alleviate the problem of DDJ causing bit errors is to reduce the frequency content of the transmitted signal. To reduce the frequency content of a signal without having to pay in terms of data transfer rate, different signalling and modulation schemes are used.

#### 2.2.4 Signalling

The vast majority of serial links on fibre, backplanes or copper wire implement NRZ signalling [1], [8], [18]. NRZ is popular for its advantage in simplicity of the design and compatibility with conventional digital logic switching techniques, but comes at a cost of a higher bandwidth requirement.

As data rates increase, ISI in NRZ signalling schemes increase to the point at which the simplicity of NRZ is no longer feasible and a more complex signalling scheme needs to be implemented to alleviate the problem of ISI. Return to zero (RZ) signalling alleviate the problem of increased ISI, but requires higher bandwidth. This restricts the use of RZ signalling schemes to fibre optic channel implementations since copper channels have a limited bandwidth when comparing to fibre optic channels [18].

Multilevel signalling techniques are emerging to increase the data rates without increasing the frequency content of the signal. The most popular multilevel signalling technique implemented is pulse amplitude modulation (PAM) [14], [18], [19], while pulse width

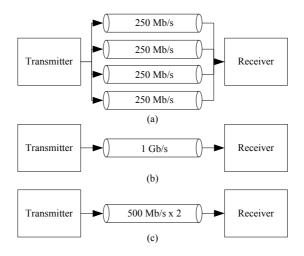

modulation (PWM) is also used [20]. By making use of N-PAM the spectral efficiency is given by  $2*log_2(N)$ , where N is the number of PAM levels [15]. This implies that by using 2 bits, which equates to four PAM levels, the spectral efficiency is increased by a factor of 4. In other words, the same data rate can be achieved with half of the original frequency content. Channel spectral efficiency is measured in terms of the number of bits per second per hertz (b/s/Hz) and is determined by the bandwidth of the basis waveform [10], [13]. To illustrate the idea of acquiring higher data rates without increasing the frequency content of the signal refer to Figure 2.2.

Figure 2.2. Illustration of spectral efficiency improvement by using N-PAM techniques [14]. (a) Conventional parallel communication. (b) Serial communication utilising NRZ signalling. (c) Serial communication using 4-PAM signalling.

As illustrated by Figure 2.2, all the data links have exactly the same data transfer rate, namely 1 Gb/s. Figure 2.2 (a) suffer from crosstalk and clock skew due to the increased bus width. To overcome the limitations of parallel communication, serial communication is adopted. Figure 2.2 (b) shows a conventional serial link which utilises NRZ signalling. Figure 2.2 (c) shows a 4-PAM serial link. The maximum frequency content of the 4-PAM signal is equal to the frequency content of two of the lower speed parallel busses multiplexed, but has the same transfer rate as a conventional serial link with four multiplexed signals. This shows that N-PAM can increase the data rates without increasing the frequency content of the signal [14].

Apart from 4-PAM signalling, 4-bit PWM-PAM signalling was implemented to utilise a 1 Gb/s serial link. In that way, the data transfer rate of 1 Gb/s is exactly equivalent to transmitting 250 MS/s. In other words, the 4-bit PWM/PAM scheme transmits 4-bits per symbol effectively transmitting at a data transfer rate of 1 Gb/s with the frequency content

of a 250 MHz NRZ signal. *N*-PAM systems with more than four levels have also been implemented [21].

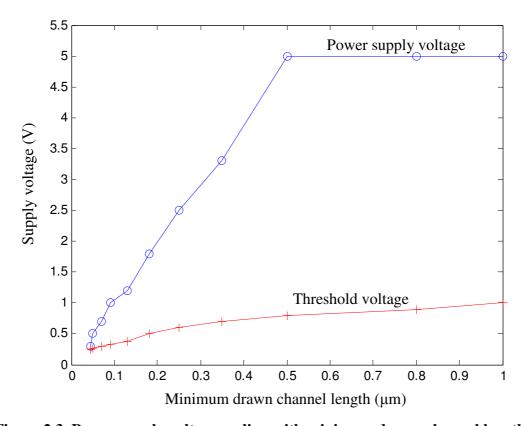

When using signalling techniques, only Gray-code mapping guarantees that every neighbouring symbol error results in only 1 bit error [10]. When using coding with added parity bits, one error bit can usually be corrected whereas two bit correction is not usually compensated for with the amount of parity bits added to the data. *N*-PAM implementations suffer from the limited supply voltages in modern high speed IC processes. This implies that the receiver decision circuit should be carefully designed to still obtain a BER of less than 10<sup>-12</sup> which is commonly accepted. This relies heavily on advances in IC fabrication technology producing faster transistors. Figure 2.3 illustrates the scaling of supply voltage with the minimum drawn channel length of a transistor in order to produce higher speed devices [22].

Figure 2.3. Power supply voltage scaling with minimum drawn channel length [22].

Figure 2.3 illustrates the problem facing design engineers. The margin between the power supply voltage and the threshold voltage is edging closer to each other limiting the amount of devices which can be stacked telescopically. Thus alternative design techniques need to

be implemented to help with the design. One such method is using the inversion coefficient design technique [22].

#### 2.2.5 Backplane serial communication links

Backplane channels are used to provide a common, easily used interconnect between different subsystems to produce a final system with a value greater than the sum of its parts. Backplane channels are an example of a mature technology with various backplanes developed and commercially available. Physical copper interconnects provide the interconnections on the backplane. Although backplane channels have long since been used, frequency dependant distortion of the signal is becoming increasingly problematic at higher data transfer rates.

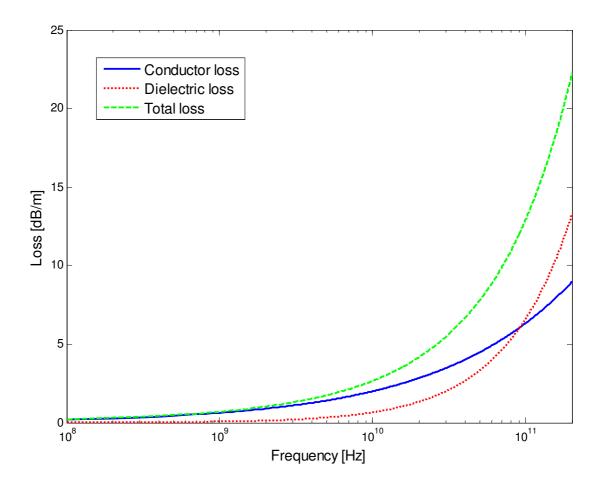

The frequency dependant distortion introduced by the copper backplane channel arises from the skin effect, dielectric losses and signal reflections of the backplane [7], [15]. Skin effect is the phenomenon whereby the current flow tends to concentrate on the surface of a conductor at high frequencies due to the conductor self-inductance [7]. Dielectric loss is due to the delay of polarisation in the dielectric material when subjected to changing electric fields [7]. Reflections on the other hand are caused by discontinuities in the transmission line path as well as impedance mismatches of the transmission line.

Non-ideal electrical performance can be grouped as: channel loss, DJ and random jitter (RJ) [17]. Channel loss is divided into skin effect loss which is proportional to the square root of frequency and dielectric loss which is proportional to the frequency. Skin effect loss dominates cable loss, while dielectric loss dominates PCB trace loss at high frequencies (excess of 10 GHz) [17]. One way of equalising for the non-ideal electric performance is channel equalisation, whereby the channel (cable) contains two types of materials with different resistivities to effectively equalise the frequency response of the channel itself [17].

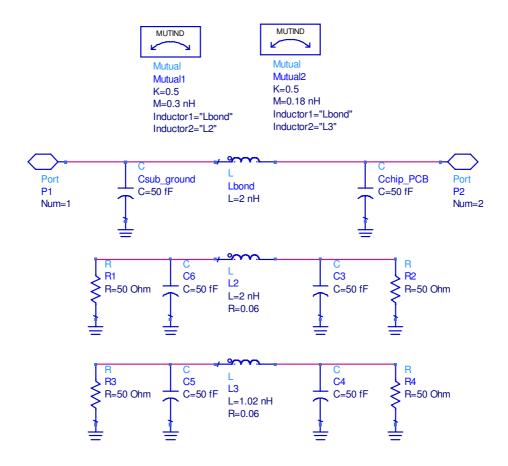

Apart from the backplane causing frequency dependant distortion, the package in which the chip is finally mounted also produces a significant amount of distortion due to parasitic capacitors and inductors. This is mainly caused by the bonding wire (typically 1 nH/mm) [1]. The parasitic components are mainly caused by [23]:

• parasitic capacitance of I/O pad,

- bond wire between chip and package,

- transmission line effects of lines on the package, and

- connection between package and PCB [24].

Three methods of attaching the package to the PCB are discussed in [24]. These include wire bonding, tape automated bonding and flip-chip package bonding. The last mentioned method is electrically the best option, with the parasitic components associated with the packaging at a minimum, but mechanically and thermally the flip-chip package performance is miserable [24]. A typical flip-chip package attached to a PCB can be modelled by Figure 2.4.

Figure 2.4. Typical parasitic element model for a flip-chip package connected to a PCB [23].

From Figure 2.4 it can be seen that the parasitic elements caused by the package will contribute significant frequency dependant distortion. The bonding wire and package thus add in producing pattern dependant jitter or distortion. It is important to note that if the backplane channel is physically long, the distortion caused by the channel will be dominant and the bonding wire and package distortion will be negligible, but for physically short channels, the bonding wire and package distortion will become more critical.

In a recent implementation, cable or trace attenuation roughly accounted for half of the total loss while the other half is contributed by the component package, connectors and path discontinuities [17]. The loss imposed by the IC package can be improved by making use of techniques such as transmitter-side shunt peaking. With the implementation of shunt peaking, the bandwidth of the bond wire connection can be improved by a factor of 1.8 with the use of a 2 mm length of bond wire [10].

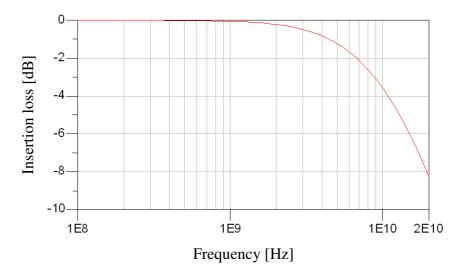

#### 2.2.6 Backplane channel modelling

Any backplane channel characteristics can be completely modelled by taking the differential scattering parameters as presented in [25]. Traditional methods were based on applying a test voltage or current and measuring the output at the far end of the link. This has become increasingly difficult at RF and microwave frequencies. Primarily, scattering parameters were developed for such a case but were only applicable to single-ended systems. These single-ended scattering parameters were adjusted [25] to form differential scattering parameters to be used in differential system characterisation.

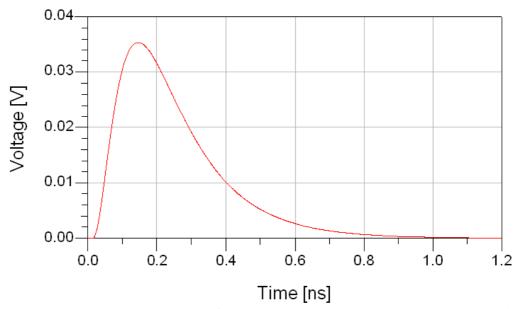

By assuming at first that the backplane channel is a linear time-invariant (LTI) system, the backplane channel can be completely characterised by its impulse response. This is a fair assumption as the environmental conditions affecting the backplane channel model exhibit large time constants and change very little over time.

Due to the low pass filter characteristic of a copper channel, the impulse response exhibits a long tail which interferes with the following adjacent bit [10]. The long tail of the impulse response causes ISI, degrading the BER and ultimately the performance of the serial link. Recent transmitter designs were designed with prior knowledge of the channel model. The channel was fully characterised beforehand and therefore the design could be optimised for the specific channel [1], [8]. Due to the cost of implementing and manufacturing an IC, this is not a feasible solution for large scale implementation using different legacy channels.

Group delay, which is defined as the phase distortion caused by channel, should be taken into account in the channel characterisation and modelling since the group delay will increase the tail of the impulse response and worsen the ISI [26], [27].

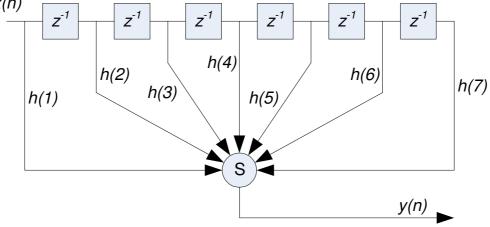

ISI is a major factor limiting the maximum distance and data transmission rates for backplane data transmission. Using FIR filter pre-emphasis at the transmit side is a popular technique for counteracting ISI in backplane data transmission links [1], [17].

#### 2.3 Jitter

#### 2.3.1 Jitter in high speed serial links

Jitter is defined as the deviation of a timing event of a signal from its intended or ideal occurrence in time. Thus jitter can be seen as unwanted pulse position modulation (PPM)

[28]. The timing event in serial communication links is the rising and/or falling edges of the pulses. Jitter degrades the performance of high-speed serial links by limiting the maximum achievable data rates [29]. Jitter impedes the ability to successfully recover the transmitted data at the far end of the link. In a serial link, the data and the clock are sent in a single serial bit stream, since the clock signal is embedded within the data signal. The receiver then extracts the clock and the data using a clock and data recovery (CDR) circuit. The transmitter introduces clock jitter while the receiver further introduces clock jitter in the CDR circuit. This is due to the fact that the receiver is extracting a clock signal from a distorted and already jittery signal. Link performance is typically measured in BER using a bit error rate tester (BERT), however, long simulation times are needed to evaluate the performance. Analytical and statistical methods are thus presented [29], [30] to reduce long simulation times required in determining the effect of jitter on the signal integrity.

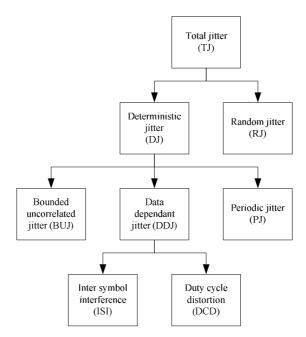

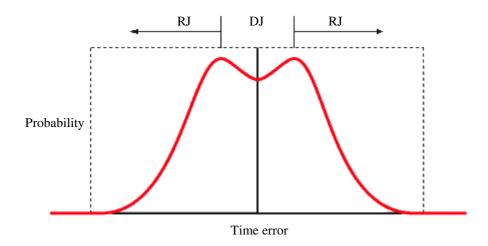

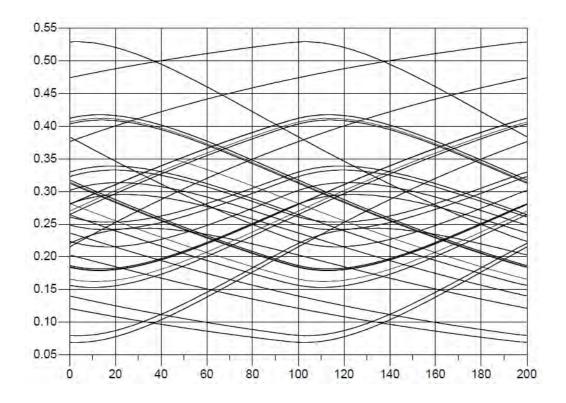

Total jitter (TJ) can be divided into two main categories: RJ and DJ. Figure 2.5 illustrates how the different sub-components of jitter contribute to the TJ.

Figure 2.5. Jitter sub-components constituting the total system jitter. Figure adapted from [4].

Periodic jitter (PJ) refers to periodic variations of the signal edge positions over time. Bounded uncorrelated jitter (BUJ) is typically due to coupling from adjacent data-carrying links or on-chip random logic switching [4]. Duty cycle distortion (DCD) describes the jitter amounting to a signal having unequal pulse widths for high and low values. ISI is

jitter that is dependant on both the data bit stream as well as the channel I/O bandwidth. DDJ corresponds to a variable jitter that is dependent on the bit pattern transmitted on the current channel under test [7]. RJ can be measured either with the use of histograms or with curve fitting algorithms depending on whether the DJ component is absent or not. Whenever the RJ distribution is non-Gaussian, other techniques have to be employed to measure the RJ, for example frequency domain analysis [7].

By transmitting a clock like pattern the DCD can be measured directly by noting the periods of logical high and logical low. The DCD distribution can then be developed by making use of a histogram and the data obtained experimentally. ISI and DCD can also be measured using spectral analysis. To measure only ISI, a data pattern containing both long and short bit run lengths can be transmitted while measuring the difference between the pulse edges for the different run lengths [7]. For this research, DCD is assumed to be negligible and ISI dominates the introduced DDJ.

#### 2.3.2 Causes of jitter in high speed serial links

TJ, as illustrated in Figure 2.5, can be subdivided into two categories, namely, RJ and DJ. RJ is mainly caused by thermal vibrations, semiconductor doping and process variations for instance thermal noise, flicker noise or 1/f noise and shot noise [7], [17]. Flicker noise has different origins but is mainly caused by traps associated with the contamination and crystal defects. These traps capture and release carriers in a random fashion and give rise to a noise signal with energy concentrated at lower frequencies [31]. Shot noise is ever present in any system incorporating diodes, bipolar transistors and metal oxide semiconductor (MOS) transistors. Shot noise is the random fluctuations in the current flowing through a pn-junction [31]. Thermal noise is caused by the random thermal motion of electrons [31].

DJ is mainly caused by crosstalk, switching noise, insufficient power delivery, EMI, DCD, ISI and discontinuities in the transmission path [17]. EMI is the interference caused from energy radiated or conducted from other devices or systems in the vicinity [7]. Discontinuities and impedance mismatches between the load and the transmission line cause signal reflections which further degrade the signal-to-noise ratio (SNR). These reflections are frequency dependant and will thus fall under the classification of DDJ. Signal slew rate limitations of the driver at the transmitter further introduce DDJ and can

be modelled as a low pass filter. Crosstalk is the main contributor to BUJ and is caused by interference from other signal traces in the vicinity. BUJ measurements have been performed [7] as a means to characterise it and determine its contribution to DJ in a typical communication link.

#### 2.3.3 Mathematical definitions

In data transmission, the data pulse width is determined by the timing instant of the transmit clock at both begin or end pulse edges [29]. NRZ pulses are commonly used as basis for discrete data transmission while multi-level signalling schemes such as 4-PAM is also being implemented to increase the spectral efficiency. A jitter-free transmit clock can be written as [29]:

$$\phi(t) = \sum_{k=-\infty}^{\infty} (d[kT] - d[kT - T]) u(t - kT)$$

(2.1)

where T is equal to the bit period and u(t) is a unit step function. Since a channel can be approximated as an LTI system, it can be accurately characterised by its impulse response. Thus the output of the channel is evaluated by convoluting the jitter-free transmit clock with the channel impulse response. The output signal can thus be evaluated as follows:

$$y(t) = \left[\sum_{k=-\infty}^{\infty} (d[kT] - d[kT - T]).u(t - kT)\right] \otimes h(t)$$

$$= \sum_{k=-\infty}^{\infty} (d[kT] - d[kT - T]).s(t - kT)$$

(2.2)

where h(t) is the impulse response of the channel, y(t) is the output signal and s(t) is the convolution of the unit step function with the channel impulse response. As seen from (2.2), the sampling instant kT determines the pulse width of the  $k^{th}$  transmitted pulse [29]. Jitter can be included in the above equation by defining a transmitter jitter sequence  $\{j_{tx}\}$  such that  $j_{tx}[k]$  is associated with the  $k_{th}$  clock edge.

A CDR circuit locked to the serial data stream generates a receiver clock phase that is aligned with the incoming data to maximise the voltage margin at the input of the detector. Due to inherent noise of the receiver, the receiver also introduces clock jitter. By defining a

jitter sequence  $\{j_{rx}\}$  such that  $j_{rx}[n]$  is the jitter associated with the  $n^{th}$  sampling edge, both the transmitter and receiver clock jitter in the output signal can be written as:

$$y(nT) = \sum_{k=-\infty}^{\infty} [(a[kT]).s(nT - kT + j_{rx}[nT] + j_{tx}[kT])]$$

(2.3)

where a[kT] = d[kT] - d[kT - T]. After applying a first order Taylor series approximation [29], the following equation is obtained:

$$y[n] \approx a[n] \otimes s[n] + (a[n] \otimes h[n]). j_{rx}[n] + (a[n].j_{tx}[n]) \otimes h[n]$$

(2.4)

In (2.4), the first term is the channel output when both the transmitter and the receiver clocks are jitter-free. The second and the third term represent the voltage margin degradation due to the transmitter and receiver clock jitter introduced. This explicit separation of the transmitter clock jitter and the recovered receiver clock jitter enable worst-case simulations without performing long BER time domain simulations [29]. This research focuses on the DDJ introduced, hence the clock signal is assumed to be jitter-free.

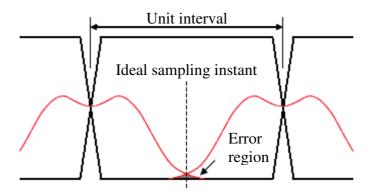

#### 2.3.4 Eye diagram analysis

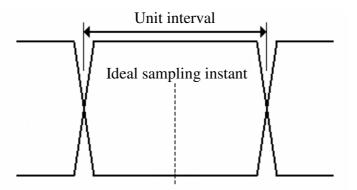

A graphical measure of data integrity can be done by using an eye diagram. An eye diagram is a composite of all the bit periods superimposed on each other. Figure 2.6 shows an eye diagram with a perfect open eye and well defined edges.

Figure 2.6. Perfectly open eye diagram with well defined left and right pulse edges.

A perfect open eye diagram as shown in Figure 2.6 is the ideal scenario eye diagram to be received at the far end of the transmission link. Due to DDJ, DCD and channel attenuation,

the eye diagram closes both horizontally and vertically. DDJ which is associated with the horizontal eye closing becomes more stringent as the pulse widths decrease with higher data transfer rates.

Clock jitter on the other hand exhibits a Gaussian distribution. Thus the ideal sampling instant as shown in Figure 2.6 will vary about its centre with a Gaussian distribution, placing further limitations on the jitter requirements. Since most of the jitter components are caused by noise the only way to characterise jitter is by means of statistical analysis.

#### 2.3.5 Statistical jitter analysis

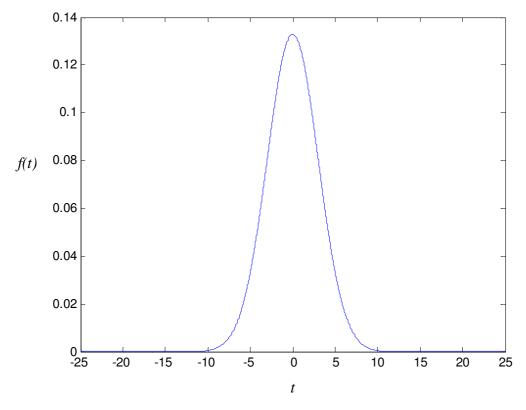

The probability density function (PDF) of the TJ is the convolution of its RJ and DJ components [32]. This however requires both the RJ and DJ components to be described by their PDFs rather than their peak-to-peak or RMS values [7]. In most practical cases, RJ is characterised as having a Gaussian distribution. A Gaussian distribution is characterised by the well-known equation:

$$f_{RJ}(t) = \frac{1}{\sqrt{2\pi\sigma}} e^{\frac{-(t-\mu)^2}{2\sigma^2}}$$

(2.5)

where  $\mu$  is the average and  $\sigma$  is the standard deviation [33]. Figure 2.7 shows a Gaussian distribution with a zero mean and a standard deviation of two.

Figure 2.7. Gaussian distribution with a mean of zero and a standard deviation of two. Adapted from [33].

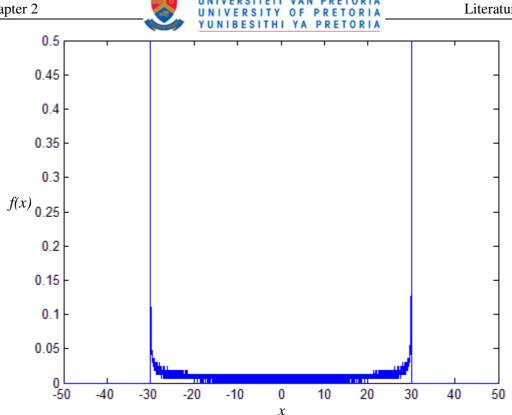

Contrary to RJ, the DJ PDF is usually estimated as two delta-Dirac functions. A deconvolution method for determining the DJ which mainly consists of ISI and DCD is presented in [28]. A real solution can be obtained through the deconvolution method as opposed to the estimated double delta-Dirac distribution [28]. A mathematical expression for the double delta-Dirac approximation is:

$$f_{DJ}(t) = \frac{1}{2} \left[ \delta \left( t - \frac{D}{2} \right) + \delta \left( t + \frac{D}{2} \right) \right]$$

(2.6)

where D is the width between the two delta-Dirac functions and  $\delta$  is the delta-Dirac function itself.

Figure 2.8 shows an approximation of DJ by taking the PDF of a sinusoidal function, which is a good estimate for PJ. The PJ and the DJ PDFs are almost the same due to the double delta-Dirac approximation.

Figure 2.8. PDF of DJ estimating two Dirac delta functions. Adapted from [34].

By convoluting the RJ PDF of Figure 2.7 and the DJ PDF of Figure 2.8, the TJ of the system can be approximated. The TJ PDF is shown in Figure 2.9.

Figure 2.9. Convolution of RJ and DJ to produce the TJ of the system. Adapted from [34].

The TJ PDF can be used to estimate the BER by using Q-factor theory developed for optical channels. The BER is essentially the cumulative distribution function (CDF) of the TJ PDFs of the left and right eye crossings over the time interval where a bit error occurs [7]. Figure 2.10 shows an overlay of the distortion, imposed on the pulse edges due to the TJ, and a perfect open eye diagram.

Figure 2.10. Distortion imposed by total system jitter affecting pulse edges. Adapted from [34].

Figure 2.10 shows that the TJ will distort the pulse edges, with the probability as shown, at the far end of the transmission link closing the eye significantly and ultimately degrading the BER.

From a measurement and characterisation perspective, a closed eye diagram at the far end (receiver) does not indicate data integrity failure if the receiver is implementing equalisation. Therefore, oscilloscopes and data analysers need to implement mathematical routines to emulate receiver equalisation to obtain a clear way of measuring the performance of the link [17].

Jitter specifications of a serial communication link are usually specified in terms of the TJ, RJ and DJ. Adherence to existing protocol specifications can be tested by overlaying the protocol eye masks with the achieved eye diagram. Any signal crossing the eye mask is considered a specification violation [7]. Jitter is usually specified to not exceed 10 % of a unit interval (UI). A UI is defined as the ideal or average time duration of a single bit. The more stringent jitter requirements rely on newer IC technologies to achieve the necessary specifications.

#### 2.4 Integrated circuit technology

The building of networks to handle data, voice and internet protocol (IP) traffic has brought forward a need for ICs that can transmit and receive large amounts of information

with high data integrity [18]. Considering the amount of constraints and limitations on high speed backplane serial transceivers, a designer will need all the aid from the technology implemented. Among the more mature silicon-based technologies, the SiGe BiCMOS successfully fulfils this need of the designer by providing high density integration capability as well as high performance and low noise levels [3].

One of the advantages of SiGe devices over bulk silicon devices is that carrier mobility in strained p-channels or tensile strained n-channels are adequate to build metal oxide semiconductor field effect transistors (MOSFETs) whose speed is higher than that of a bulk silicon device with similar size and structure [35]. The reason for the growing popularity of SiGe technology is for its ability to simultaneously achieve high cut-off frequency ( $f_T$ ), low base resistance ( $f_T$ ) and high common emitter current gain ( $f_T$ ). The main reason for the success of SiGe HBT devices are due to its low noise capabilities [2].

SiGe technology has reached the point in which more expensive processes like InP and GaAs are becoming more application specific as performance of SiGe devices are increasing and can provide a lower cost high speed device. Due to the competitive device characteristics of SiGe devices, a shift to the lower cost SiGe devices are likely to occur more often [3].

High speed data communication networks of the 21<sup>st</sup> century will continue to require high performance, low power, low noise and low bit error rates at an affordable price forcing the IC industry to higher integration levels and lower power devices [3]. SiGe technologies will further continue to move into market segments previously believed to be the stronghold of more expensive GaAs and InP-based technologies. Thus SiGe processes are expected to be the technology of choice for future multi Gb/s throughput parallel links [3].

Integrated circuit implementation techniques form an important consideration in the implementation of a high speed serial link. The switching speed of the logic circuits as well as the noise levels of the devices form an integral part of a high speed design. Techniques such as emitter coupled logic (ECL) were employed in the past for its low voltage levels, but CML is preferred for higher speed operation [1]. Chapter 4 discusses the considerations taken into account in choosing between conventional MOS CML and bipolar CML.

#### 2.5 Reducing jitter in high speed serial communication links

Jitter can be decomposed into several sub-components each having their specific characteristics and root causes [7]. Traditionally, the performance of a communication link has been measured by its BER, but when the data rate increases, the jitter magnitude as well as the signal amplitude noise need to decrease proportionally in order to achieve the same acceptable BER [7]. A common acceptable BER for serial links is  $10^{-12}$ . This translates into a jitter requirement of less than 10% of a UI.

One of the areas in which a large amount of effort has gone into is in designing of a low phase noise voltage controlled oscillator (VCO) [36]. The phase noise of a VCO can be seen as small variations in the zero crossings of the signal. Jitter is defined as variations from the expected time of an event. Thus by reducing the VCO phase noise the clock jitter introduced by the phase locked loop (PLL) at the transmitter and at the receiver can be reduced. The total amount of clock jitter should be kept as low as possible and should be insignificant in relation to a UI. It is important to note that power supply induced jitter (random fluctuations in supply voltage influencing the tuning voltage and hence oscillation frequency) directly influence the VCO, introducing further phase noise.

The DDJ on the other hand causes the receiver eye diagram to close completely, hence making a correct decision virtually impossible, resulting in a large BER. Techniques to overcome DDJ are developed to improve the BER of high speed serial communication links.

# 2.5.1 Overcoming data dependant jitter

There are two main limitations in the propagation of a multi-Gb/s data signal. These are the frequency dependant characteristics of the channel and the package [8]. As discussed earlier, the backplane channel, the chip package and the bonding wires contain frequency dependant devices which translate into data dependant distortion.

The chip pads conventionally contain electro-static discharge (ESD) protection circuitry and together with the chip package and bonding wires form an effective low pass LC filter. This parasitic filter causes the high frequency roll off causing the DDJ in the signal. The ISI is not only determined by the high frequency roll off but also by the non linear phase response of the effective LC filter [18].

To overcome the low pass filter effect of the complete channel one of two methods can be used to overcome the channel and package limitations. These two methods are preemphasis at the transmitter or equalisation at the receiver [37]. Both ways of overcoming the DDJ rely on multiplying the channel (including the chip and bonding wires) transfer function with a certain transfer function to obtain a perfect flat frequency response. Both the pre-emphasis and the equalisation will act as a high pass filters, shaping the signal to produce an overall flat frequency response. Ideally a flat magnitude frequency response and a linear phase response are required for perfect error free transmission. The criterion for error free transmission, namely a flat frequency response and a linear phase response are mathematically expressed as follows [38]:

$$|H_{P}(\omega)H_{C}(\omega)| = C$$

$$\theta_{P}(\omega) + \theta_{C}(\omega) = -\omega t_{d}$$

(2.7)

where  $H_P(\omega)$  is the FIR pre-emphasis filter transfer function,  $H_C(\omega)$  is the channel transfer function and C is a constant.  $\theta_P(\omega)$  is the FIR pre-emphasis filter phase response and  $\theta_C(\omega)$  is the channel phase response.

#### 2.5.2 Equalisation

To compensate for the lossy characteristics of the channel, equalisation techniques such as a feed-forward equaliser (FFE), decision feedback equaliser (DFE) and receiver preamplifiers have been proposed [17]. For cost effective high performance designs, the channel, transmitter and receiver should complement each other as discussed in [17]. The major limitation with DFE is the time constraints of the feedback loop [37], [39].

The most common transmitter side equalisation (transmitter pre-emphasis) is the FFE which uses the current transmitting bit and one or more of its adjacent bits. This effectively implements a FIR filter [17]. A high pass filter is used for transmitter pre-emphasis to obtain a flat frequency response over the frequency range of interest.

Equalisers at the receiver are easier to implement and to make adaptive since the signal being fed back for coefficient updates are already present with the CDR circuit. An adaptive equaliser architecture is presented [11] implementing an infinite impulse response (IIR) filter for its simplicity in an adaptive circuit. The effective IIR filter produced can be viewed as an adjustable high pass filter [11]. Although equalisation can correct some of the

data dependant distortion, if the signal is too weak or too distorted, an equaliser cannot produce an open eye diagram to the sampling and decision circuitry. Thus a need for effective pre-emphasis or pre-shaping circuits in high speed serial links arises.

#### 2.5.3 Pre-emphasis

Transmit pre-emphasis (also called pre-distortion or pre-shaping) exhibits lower power consumption, superior performance and better interoperability as compared to receiver equalisation [40]. Pre-emphasis pre-distorts the transmission data by amplifying the higher frequency components boosting the high frequency components before entering the non-ideal channel [26].

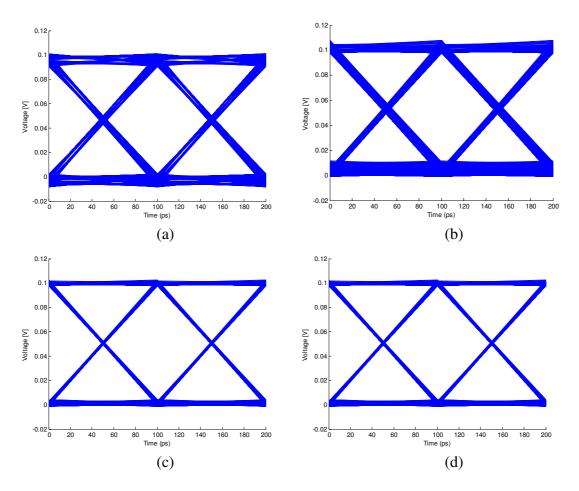

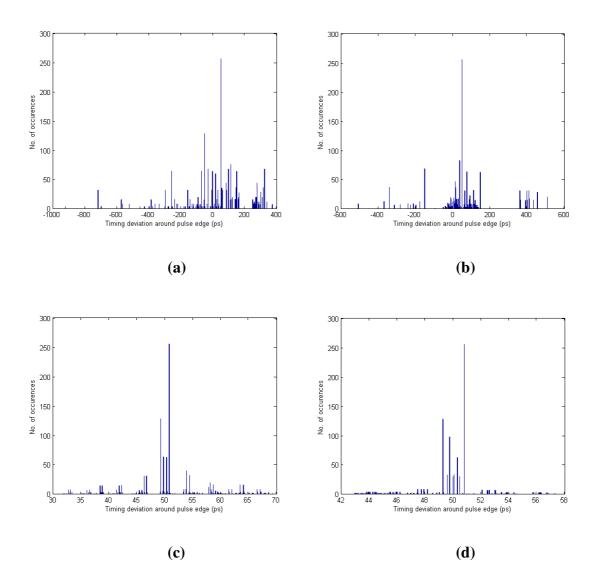

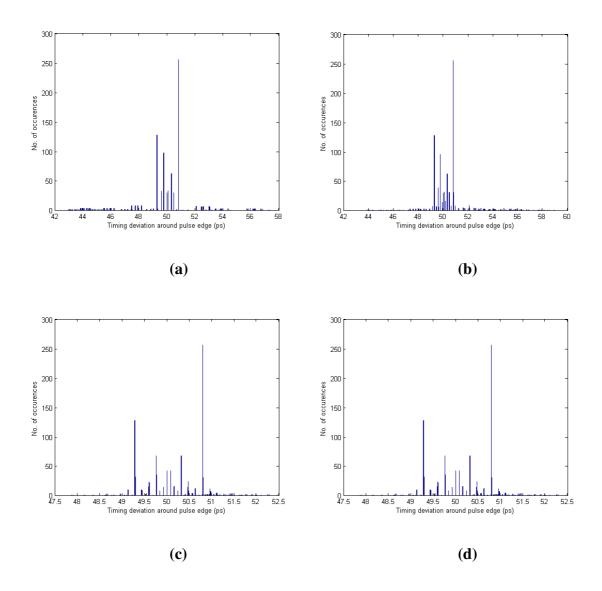

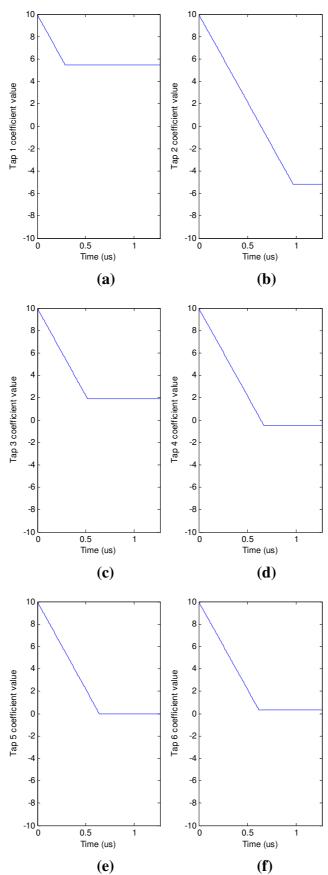

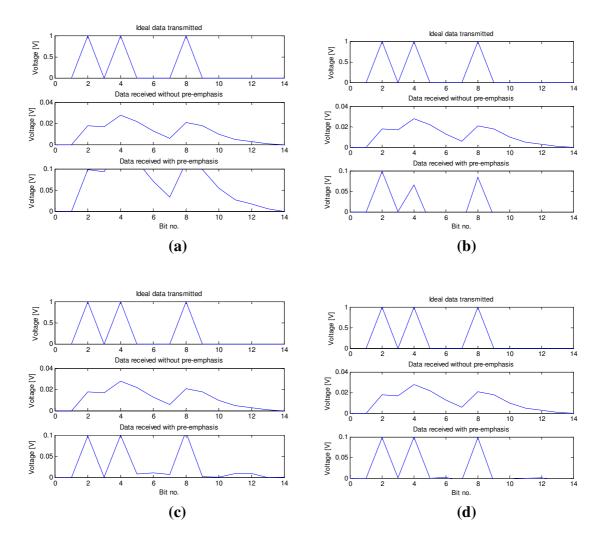

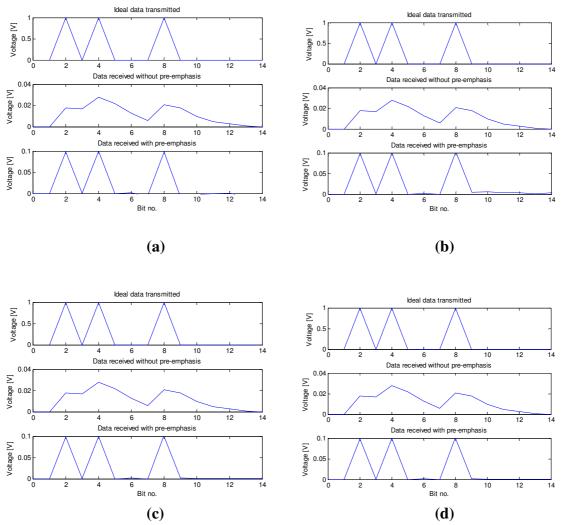

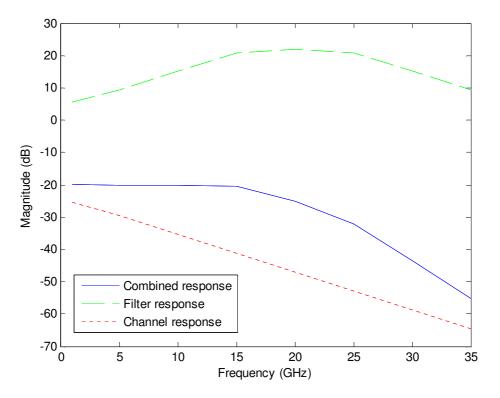

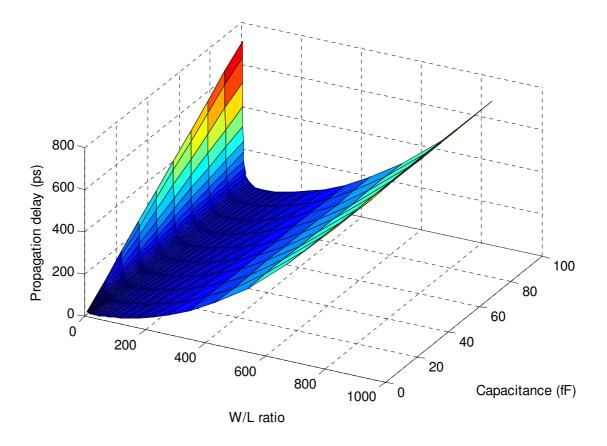

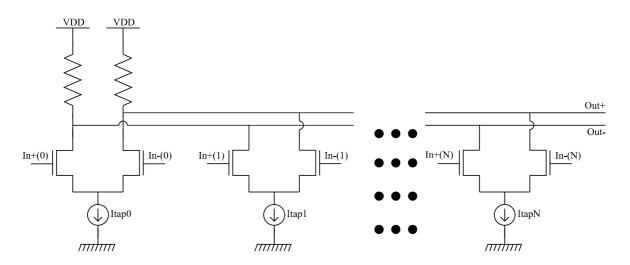

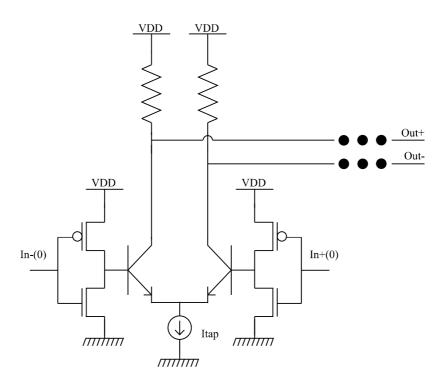

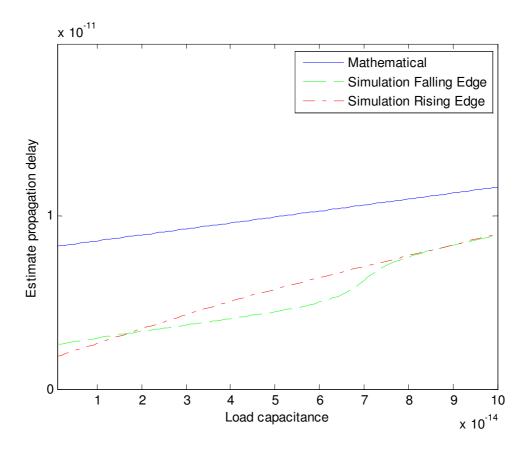

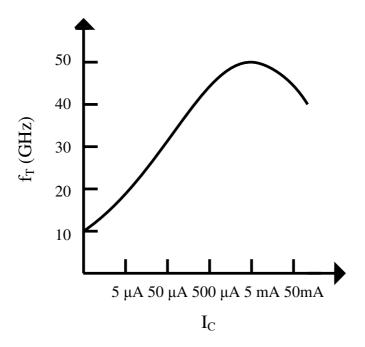

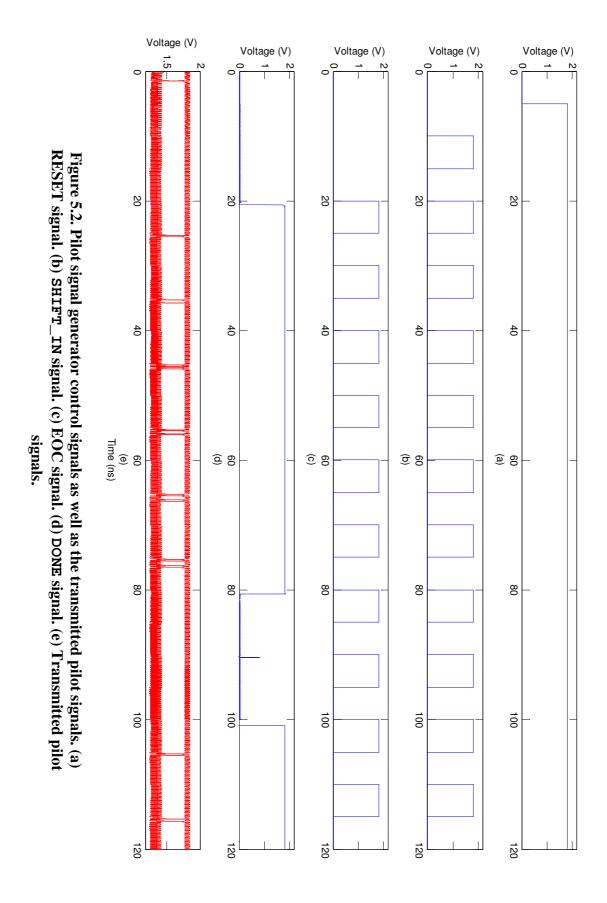

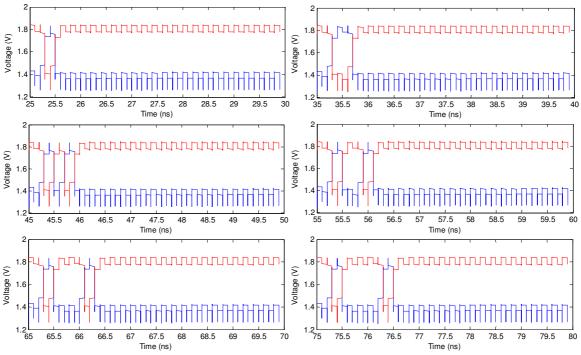

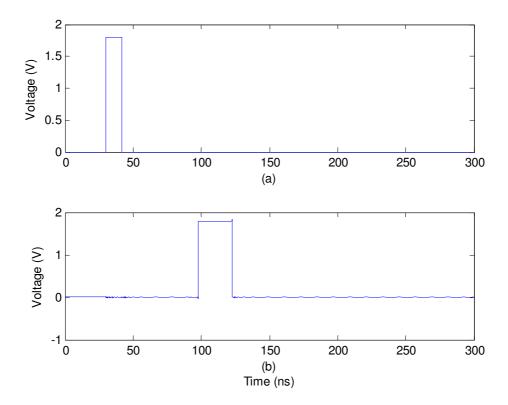

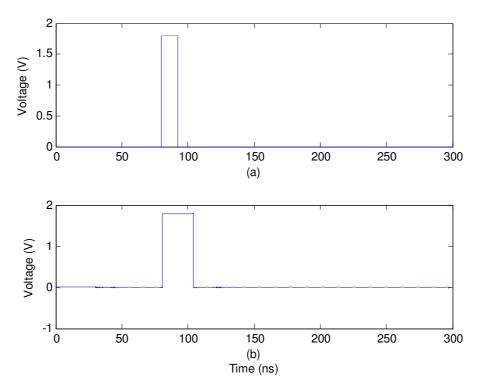

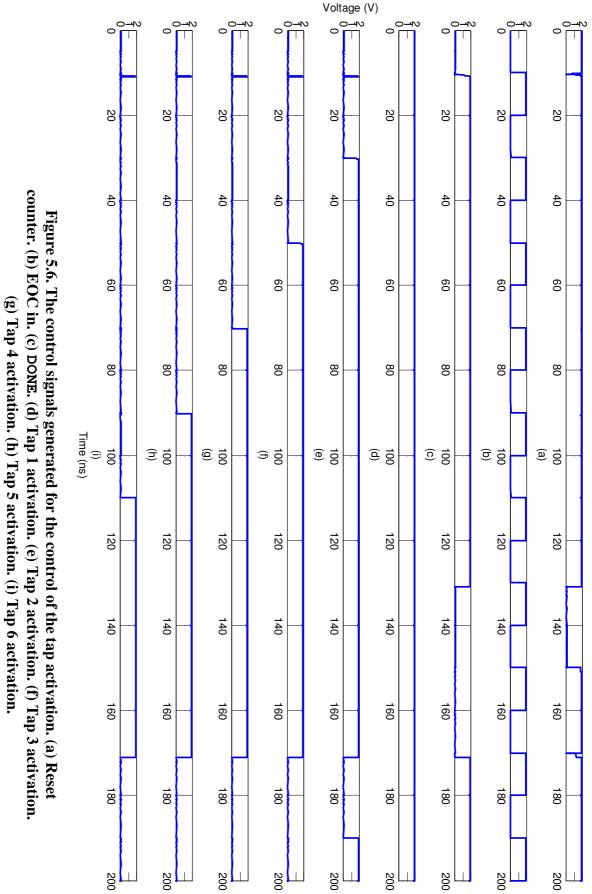

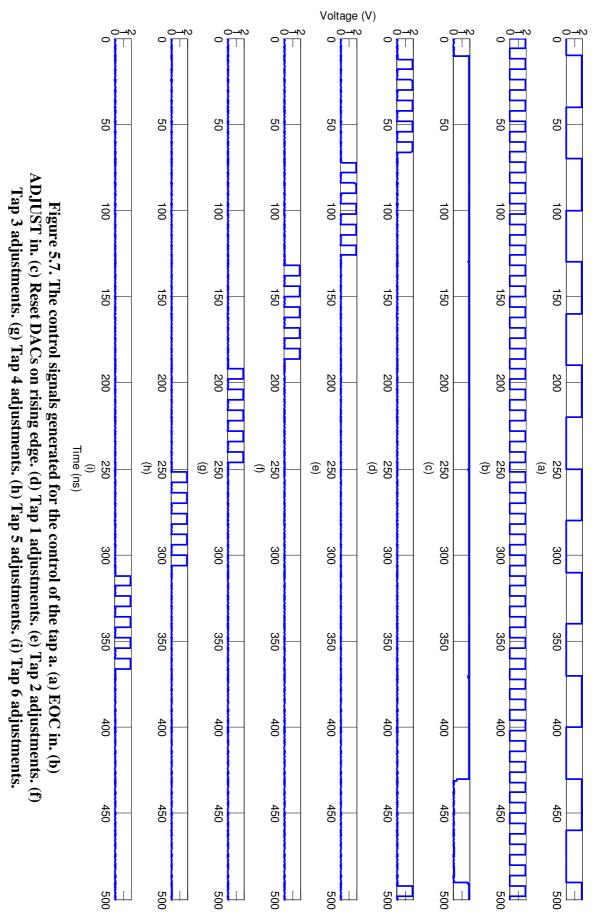

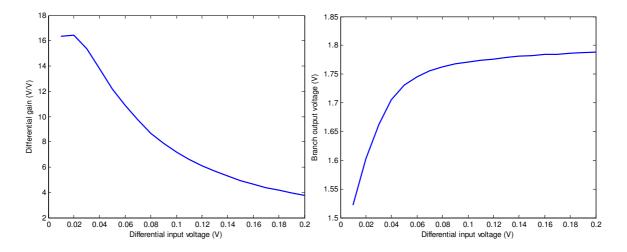

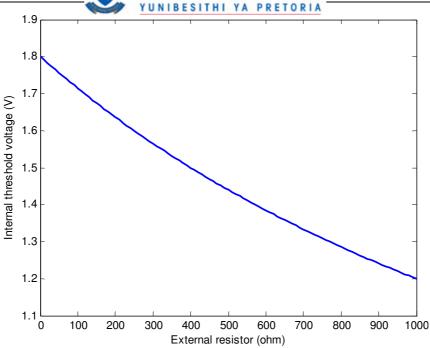

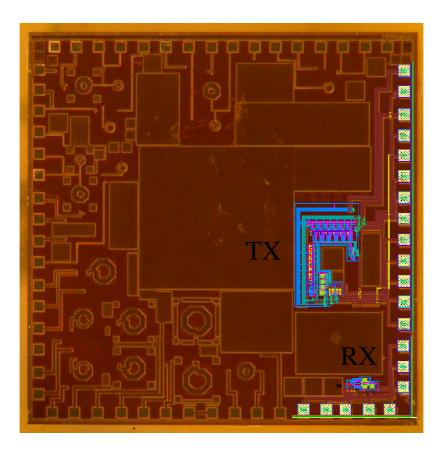

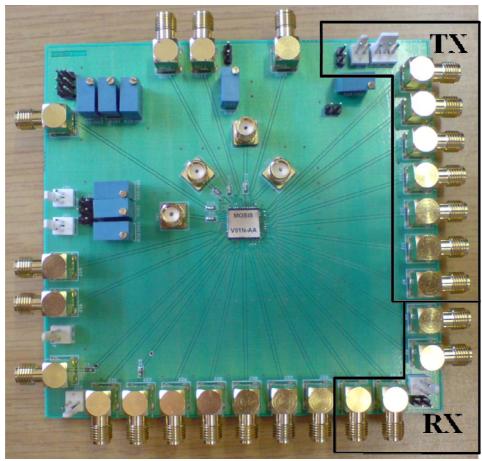

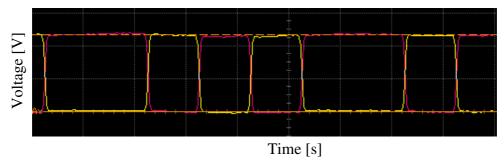

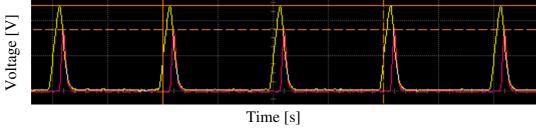

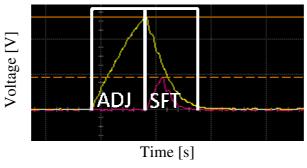

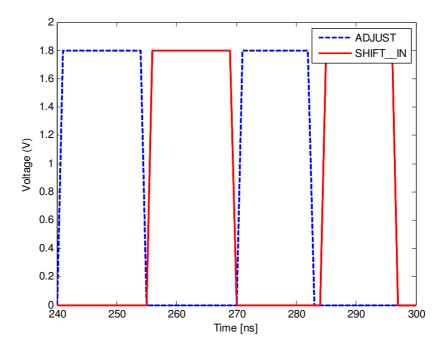

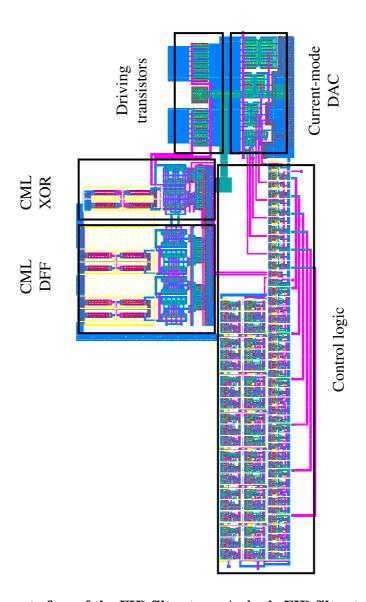

FIR filter based pre-emphasis has been used by various authors to overcome ISI (effectively DDJ) in high speed serial links [1], [8], [26]. Phase distortion caused by the non-linear phase response of the combined channel produces group delay distortion that should be taken into account for channel modelling and FIR filter design [26]. Methods for correcting the group delay distortion as well as the amplitude distortion is discussed in [27], [41], [42].