### A METHOD OF VOLTAGE TRACKING

## FOR

## POWER SYSTEM APPLICATIONS

BY

## JACOBUS VISSER

Submitted in partial fulfillment of the requirement for the degree

Master of Science: Applied Sciences (Electrotechnics)

in the

Faculty of Engineering, Built Environment and Information Technology

**UNIVERSITY OF PRETORIA**

**JULY 2010**

© University of Pretoria

## SUMMARY (ENGLISH)

Title: A method of voltage tracking for power system applications.

Student: Jacobus Visser

Study Leader: Dr. Raj Naidoo

Department: Department of Electric, Electronic and Computer Engineering, University of Pretoria

Degree: M.Sc: Applied Sciences (Electrotechnics)

An algorithm that is capable of estimating the parameters of non-stationary sinusoids in real-time lends application to various branches of engineering. Non-stationary sinusoids are sinusoidal signals with time-varying parameters.

In this dissertation, a nonlinear filter is applied to power system applications to test its performance. The filter has a structure which renders it fully adaptive to tracking time variations in the parameters of the targeted sinusoid, including its phase and frequency. Mathematical properties of the differential equations which govern the proposed filter are presented. The performance of the proposed filter in the field of power systems is demonstrated with the aid of computer simulations and practical experimentations.

The filter is applied to synchronous generator excitation control, voltage dip mitigation as well as the real-time estimation of symmetrical components. The parameter settings of the filter are tested and optimized for each of the applications.

This dissertation demonstrates the simulation and experimental results of the filter when applied to the various power system applications.

**Keywords:** Non-linear filter, Parameter setting optimization, Diode bridge rectifier, Amplitude tracking, Synchronous generator control, Voltage dips, Symmetrical components.

## **OPSOMMING**

Titel: A method of voltage tracking for power system applications.

Student: Jacobus Visser

Studie Leier: Dr. Raj Naidoo

Departement: Department of Electric, Electronic and Computer Engineering, University of Pretoria

Kursus: M.Sc: Toegepaste Wetenskappe (Electrotechnics)

'n Filter wat bevoeglik is met die beraming van die parameters van beweeglike sinusoïdale in ware-tyd, kan bruikbaar aangewend word in verskeie takke van ingenieurswese. Beweeglike sinuskrommes is sinusoïdale seine met tyd-wisselende parameters.

In hierdie verhandeling word `n nie-liniêre filter aangewend in verskeie kragstelseltoepassings om die werksverrigting van die filter te toets. Die filter het 'n struktuur wat dit toelaat om wisselende tydvariasies in die parameters van die teikensinusoïdaal op te spoor, insluitende die fase en frekwensie. Wiskundige eienskappe van die differensiaalvergelykings wat die voorgestelde filter beheer is ondersoek. Die werksverrigting van die voorgestelde filter in die veld van kragstelsels is gedemonstreer met die hulp van rekenaarsimulasies asook praktiese eksperimente.

Die filter is toegepas tot opgewekte, sinkrone eksitasie-beheer, spanningsverlaging versagting, asook die ware tyd estimasie van simmetriese komponente. Die parameter verstellings van die filter is getoets en geoptimeer vir elk van die toepassings.

Hierdie verhandeling demonstreer die simulering en eksperimentele resultate van die filter wat aangewend is vir verskeie kragstelseltoepassings.

**Kernwoorde:** Nie-liniêre filter, Parameter verstelling optimering, Diodebrug gelykrigter, Amplituderaming, Synkrone-generator-beheer, Spanningverlagings, Simmetriese komponente.

## LIST OF ABBREVIATIONS

This list contains the abbreviations and acronyms used in this document.

| AC    | Alternating Current                                   |

|-------|-------------------------------------------------------|

| AVR   | Automatic Voltage Regulation                          |

| CBEMA | Computer Business Equipment Manufacturers Association |

| CPU   | Central Processing Unit                               |

| CSV   | Comma Delimited Excel File                            |

| DBR   | Diode Bridge Rectifier                                |

| DC    | Direct Current                                        |

| DFT   | Discrete Fourier Transform                            |

| EMF   | Electromagnetic Force                                 |

| HT    | Hilbert Transform                                     |

| HTS   | High Temperature Superconductors                      |

| Hz    | Hertz                                                 |

| IEEE  | Institute of Electrical and Electronic Engineers      |

| L     | Inductance                                            |

| LAV   | Least Absolute Value                                  |

| LFC   | Load Frequency Controlled                             |

| LMS   | Least Mean Squares                                    |

| MVA   | Mega Voltage-Ampere                                   |

| PC    | Personal Computer                                     |

| PLL   | Phase Locked Loop                                     |

| RMS   | Root Mean Squares                                     |

| SCR   | Silicon Controlled Rectifier                          |

| ST    | Static                                                |

| TEO   | Teager Energy Operator                                |

| VAR   | Voltage-Ampere Reactive                               |

# TABLE OF CONTENTS

|             | TER 1                                                     |         |

|-------------|-----------------------------------------------------------|---------|

| INTRO       | DUCTION                                                   |         |

| 1.1         | REVIEW OF CONVENTIONAL METHODS                            | 7       |

| 1.2         | OBJECTIVE OF THE DISSERTATION                             | 9       |

| 1.3         | OUTLINE OF THE DISSERTATION                               | 9       |

| 1.4         | CONTRIBUTION OF THIS DISSERTATION                         |         |

|             |                                                           |         |

| CHAP        | TER 2                                                     | 11      |

| MATH        | EMATICAL MODEL AND PARAMETER OPTIMIZATION                 | 11      |

| 2.1         | INTRODUCTION                                              | 11      |

| 2.2         | FORMULATION OF THE ALGORITHM                              | 12      |

| 2.3         | IMPLEMENTATION OF THE PROPOSED ALGORITHM                  | 14      |

| 2.4         | PARAMETER OPTIMIZATION FOR AMPLITUDE TRACKING             | 16      |

| 2.5         | PARAMETER OPTIMIZATION FOR PHASE AND FREQUENCY            |         |

|             | TRACKING                                                  | 20      |

| 2.5.1       | Parameter Optimization for Phase Changes                  |         |

| 2.5.2       | Parameter Optimization for Frequency Changes              |         |

| 2.6         | CONCLUDING REMARKS                                        |         |

|             |                                                           |         |

| CHAP        | TER 3                                                     | 27      |

|             | ATION CONTROL ON A SYNCHRONOUS GENERATOR                  |         |

| 3.1         | INTRODUCTION                                              |         |

| 3.2         | BASIC SYNCHRONOUS MACHINE AND EXCITATION CONTROL          |         |

| 0.12        | THEORY                                                    |         |

| 3.2.1       | The Synchronous Machine                                   |         |

| 3.2.2       | Basic Control of a Synchronous Machine                    |         |

| 3.2.3       | The Excitation System                                     |         |

| 3.2.4       | The Static Excitation System                              |         |

| 3.3         | BASIC THEORY OF THE DIODE BRIDGE RECTIFIER                |         |

| 3.3.1       | Operation of the Diode Bridge Rectifier                   |         |

| 3.3.2       | Calculation of the DC Ripple Voltage for Constant Loading | 36      |

| 3.4         | DIODE BRIDGE RECTIFIER MODEL                              |         |

| 3.5         | PERFORMANCE OF BOTH METHODS FOR A CHANGE IN THE           | ••••••• |

| 5.5         | VOLTAGE MAGNITUDE                                         | 40      |

| 3.7         | THE CLOSED-LOOP SYSTEMS                                   |         |

| 3.8         | GENERATOR RESPONSE USING BOTH METHODS AS INPUT TO THE     |         |

| 5.0         | AVR                                                       |         |

| 3.8.1       | Introduction                                              |         |

| 3.8.2       | Algorithm Model Simulation Tests                          |         |

| 3.8.3       | Diode Bridge Rectifier Model                              |         |

| 3.8.3       | Performance and Results                                   |         |

| 3.9         | SUMMARY OF RESULTS                                        |         |

| 3.10        | CONCLUDING REMARKS                                        |         |

| 5.10        |                                                           | ••••••• |

| СНАРТ       | TER 4                                                     | 61      |

|             | CATION OF THE ALGORITHM TO VOLTAGE DIP MITIGATION         |         |

| <b>4</b> .1 | INTRODUCTION                                              |         |

| 4.2         | SYNCHRONOUS CONDENSER CONTROL                             |         |

| 4.2.1       | Basic Synchronous Condenser Theory                        |         |

|             |                                                           |         |

|             | nent of Electrical, Electronic and Computer Engineering   | 5       |

| Univers     | ity of Pretoria                                           |         |

| 4.2.2   | Closed Loop Voltage Mitigation Studies                                  |

|---------|-------------------------------------------------------------------------|

| 4.2.3.  | Simulations for Changes in Loading Conditions                           |

| 4.2.4   | Voltage Dip Mitigation under Fault Conditions on the Network            |

| 4.2.4.1 | 400kV Three Phase to Ground Fault Simulations                           |

| 4.2.4.2 | 132kV Three-Phase to Ground Fault Simulations                           |

| 4.2.4.3 | 11kV Three-Phase to Ground Fault Simulations                            |

| 4.2.5   | Summary of Results                                                      |

| 4.3     | MITIGATING DECAYING DC BUS VOLTAGES                                     |

| 4.3.1   | Introduction                                                            |

| 4.3.2   | Experimental Setup                                                      |

| 4.2.4   | Summary of Results                                                      |

| 4.4.    | CONCLUDING REMARKS                                                      |

| 4.4.    | CUNCLUDING REMARKS                                                      |

| CHAPT   | ER 5                                                                    |

|         | ATION OF THE PROPOSED ALGORITHM FOR REAL-TIME                           |

|         | TRICAL COMPONENT ESTIMATION                                             |

| 5.1     | INTRODUCTION                                                            |

| 5.2     | PERFORMANCE                                                             |

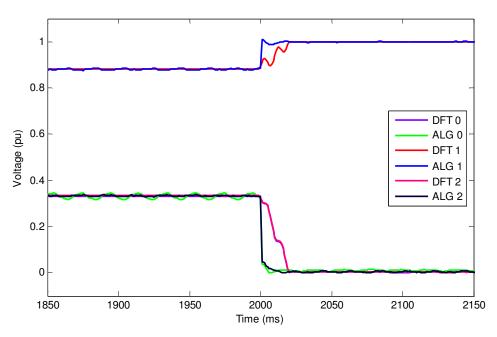

| 5.2.1   | Case 1: Effects of a Change in Amplitude                                |

| 5.2.2   | Case 2: Effects of a Change in Phase                                    |

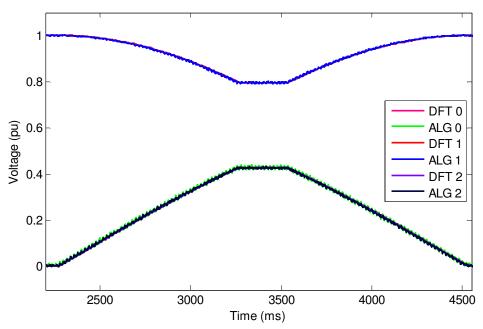

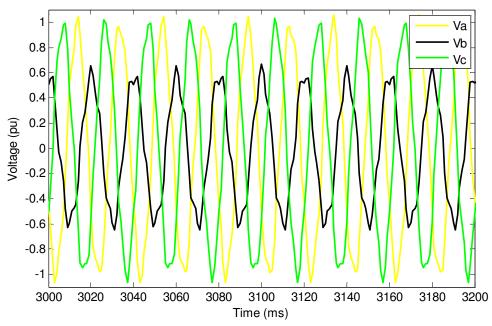

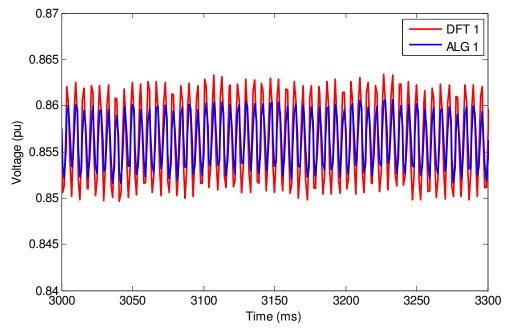

| 5.2.3   | Case 3: Influence of Harmonics                                          |

| 5.3     | APPLICATION TO FIELD DATA                                               |

| 5.3.1   | Case 1: 400kV Transmission Line Single Phase Fault                      |

| 5.3.2   | Case 2: 275kV Transmission Line Single Phase Fault                      |

| 5.4     | SUMMARY OF RESULTS                                                      |

| 5.5     | CONCLUDING REMARKS                                                      |

| 5.5     | CONCLUDING REMARKS                                                      |

| СПАДТІ  | ER 6101                                                                 |

|         | USION                                                                   |

| 6.1     | INTRODUCTION                                                            |

| 6.2     | SUMMARY OF RESULTS                                                      |

|         |                                                                         |

| 6.2.1   | Control of an Automatic Voltage Regulator on a Synchronous Generator101 |

| 6.2.2   | Voltage Dip Mitigation                                                  |

| 6.2.3   | Real time symmetrical component estimation                              |

| 6.3     | FUTURE WORK103                                                          |

| REFERI  | ENCES                                                                   |

|         |                                                                         |

| LIST OF | 5 FIGURES                                                               |

|         |                                                                         |

| LIST OF | <b>F TABLES</b> 109                                                     |

## **CHAPTER 1**

## **INTRODUCTION**

## **1.1 REVIEW OF CONVENTIONAL METHODS**

Non-stationary sinusoids are sinusoidal signals with time-varying parameters. An algorithm that is capable of estimating the parameters of non-stationary sinusoids in realtime lends application to various branches of engineering. The algorithm has been applied to the problem of elimination of power line noise potentially present on electrocardiogram and telephone cables, the estimation of low-level biomedical signals polluted by noise and the refinement and analysis of ultrasonic waves used in non-destructive testing of materials.

Numerous techniques have been developed for the extraction of a single sinusoidal signal out of a given multi-component input signal [1]. The fast and accurate estimation of magnitude, phase and frequency of a sinusoidal signal has vast importance in the control, monitoring and analysis of a power system.

Fourier-based techniques include the Short-time Fourier Transform, the Fast Fourier Transform and the Discrete Fourier Transform (DFT). The main disadvantage of the Fourier-based techniques is that measurement errors are incurred when the frequency deviates from the nominal frequency. The Fourier-based techniques are vulnerable to noise and require long measurement windows when small frequency deviations from nominal value occur. The Fourier methods are of an approximating nature and presuppose only small variations in the characteristics of the sinusoidal signal under study [1-3].

The Least Absolute Value (LAV) technique is appropriate for non-stationary signals. It has the major drawback: it assumes the frequency parameter in advance. The LAV also has a slow convergence rate, taking at least three cycles to settle to the correct value. This is because of a time delay. Consequently the LAV technique is not effective for online tracking [4, 5].

The Kalman and Extended Kalman Filter suffer from complexity of structure and are sensitive to the setting of parameters and initial conditions. Furthermore, it has a relatively long transient response if used recursively [6]. It also has high computational requirements because it evaluates the transcendental functions in real-time [1, 4].

Root Mean Squares (RMS) and Least Mean Squares (LMS) methods are supplemented with forgetting and adaptation factors. They can each provide dynamic estimates of the voltage phasor. The LMS is based on the minimization of the mean square error between the measured values for the amplitudes and phase angles. For a nonlinear power system model, this technique results in a reasonable parameter estimation. The RMS and LMS methods disclose a satisfactory and similar performance. Extensive experiments on actual data clearly demonstrates that in order to improve accuracy, pre-filtering of the raw data is needed in order to eliminate the unavoidable effects of harmonics and offsets [6-7].

The Wavelet Transform is a powerful tool that is used to analyze sinusoidal signals. It involves computational complexity and batch processing and it is difficult to choose the correct wavelet. Wavelet Transform is only suitable for offline diagnosis and analysis [4].

The nonlinear Teager Energy Operator (TEO) and the linear Hilbert Transform (HT) are novel tools for assessment and tracking as they are fast, accurate and easy to implement for voltage tracking. TEO has a low computational burden, but in the presence of harmonics and high frequency components a filtering operation to the input signal is mandatory to avoid instability of the TEO operation and to smooth over the output from the HT algorithm. HT, when used with a long filter length, provides a minimum error in tracking both voltage and frequency. However, HT has the highest computational cost and large time delay [4-5].

Phase-locked Loops (PLL) aims to extract a specified component of the input signal and to track its phase variations over time. It is a fundamental concept that is used and it has the ability to generate a sinusoidal signal, the phase of which coherently follows that of the main component of the input signals. PLL's have a limited frequency lock-in range and provides only phase/frequency-adjusted sinusoidal signals. Extraction of non-stationary sinusoids implies the adjustment of the synthesized sinusoidal signal and is not common to

PLLs [1]. PLLs can reduce the measurement time, but it does not have very good resolution or dynamic properties.

### **1.2 OBJECTIVE OF THE DISSERTATION**

A recently developed algorithm by Ziarani [1] can be used to extract and estimate the amplitude, phase and frequency of a non-stationery signal. The algorithm has a nonlinear structure and is a generalization of two previously developed nonlinear adaptive algorithms. Its successful application has been demonstrated for a number of applications and it has shown its superiority over conventional Fourier analysis and linear adaptive methods for sinusoidal tracking. The algorithm used in this dissertation exhibits a high degree of immunity with regard to both external noise and internal parameter settings, while offering structural simplicity that is crucial for real-time applications [8].

The objective of this dissertation is the application of this algorithm to selected applications in power systems. In this dissertation the method is applied to track the voltage amplitude, phase and frequency. Optimization of parameters and performance issues are investigated.

### **1.3 OUTLINE OF THE DISSERTATION**

The scope of this dissertation covers the application of the signal processing algorithm to various power system applications. The organization of the dissertation is divided into two parts.

Part I of the dissertation presents the mathematical properties and digital implementation of the algorithm. Chapter 2 outlines the mathematical model and simulation for parameter optimization for a desired performance. This is compared against common methods of voltage amplitude tracking. Chapter 3 outlines the application of the algorithm to voltage amplitude tracking for an automatic voltage regulator (AVR).

Part II of the dissertation presents examples of the application of the algorithm to problems in power systems. This includes voltage dip mitigation and symmetrical component estimation. Chapter 4 presents new methods of voltage dip mitigation with the application of the algorithm for voltage tracking for AVR of synchronous condensers as well voltage

dip mitigation on DC bus voltages through fast tracking of the input waveform for switching purposes. Chapter 5 presents the application of the algorithm for rapid estimation of symmetrical components in three-phase power systems. The algorithm is applied to tracking voltage amplitude, phase and frequency in real time.

Finally, concluding remarks are presented including an outline of recommended future research directions.

The results are documented and presented both graphically and numerically. All simulations were done using Matlab Simulink<sup>TM</sup>.

## 1.4 CONTRIBUTION OF THIS DISSERTATION

The research identifies applications in the power system field and applies a non-linear filter to these applications. The research includes results showing comparisons and improvements to conventional methods in some cases. The contribution to this field of study is the optimization of the non-linear filter to track voltage amplitude, phase and frequency of a non-stationary sinusoid in the power system field. The non-linear filter was applied to AVR for a synchronous generator and compared to a conventional method of AVR for a synchronous generator. The non-linear filter is also applied to voltage dip mitigation through the excitation control of a synchronous condenser, as well as the control and switching of a static storage device during the occurrence of voltage dips. Finally the non-linear filter is applied to real time symmetrical component estimation and compared to the conventional DFT.

# **CHAPTER 2**

## MATHEMATICAL MODEL AND PARAMETER OPTIMIZATION

## 2.1 INTRODUCTION

The Ziarani/Konrad algorithm has been developed to extract and estimate the amplitude, phase and frequency of a non-stationary signal. It has a nonlinear structure and is a generalization of two previously developed nonlinear adaptive algorithms. The successful application in a number of applications has shown its superiority over conventional Fourier analysis and linear adaptive methods for sinusoidal tracking. It exhibits a high degree of immunity with regard to both external noise and internal parameter settings while offering structural simplicity that is crucial for real-time applications.

The signal processing algorithm that is described is very simple in structure consisting of a few arithmetic and trigonometric operations. It is easily implemented in software, or in a schematic design environment. The derivation of the algorithm is outlined in the following section. The derivation is parallel to the way that the Fourier analysis was developed. Since the approximation is no longer a linear combination of basis vectors, the estimation cannot be obtained in a closed form such as an inner product - a direct method of minimization has to be employed. To this end, the gradient descent method is employed to provide a means of estimating parameters [1, 9].

## 2.2 FORMULATION OF THE ALGORITHM

Let v(t) represent a voltage signal in which n(t) denotes the superimposed disturbance or noise. In a typical operation i.e. a power system, v(t) has a general form of:

$$v(t) = \sum_{i=0}^{\infty} V_i \sin(\omega t + \phi) + n(t)$$

(2.1)

where V,  $\omega$  and  $\varphi$  are functions of time. In a power system this function is usually continuous and almost periodic. The sinusoidal component of this function is:

$$s(t) = V_s \sin(\omega t + \delta_s) \tag{2.2}$$

where  $V_s$  is the amplitude,  $\omega$  the frequency and  $\delta_s$  the phase angle. These parameters will vary with time depending on the load on the power system, as well as with the occurrence of faults in the power system.

The objective of the algorithm is to extract a specified component of v(t). Let M be a manifold containing all sinusoidal signals defined as:

$$M = \{V(t)\sin(\omega(t)t + \delta(t))\}$$

(2.3)

where:

$$V(t) \in [V_{\min}, V_{\max}], \, \omega(t) \in [\omega_{\min}, \omega_{\max}], \, \delta(t) \in [\delta_{\min}, \delta_{\max}]$$

(2.4)

Thus:

$$\mathfrak{S}(t) = [V(t), \boldsymbol{\omega}(t), \boldsymbol{\delta}(t)]^T$$

(2.5)

is the vector of the parameters which belongs to the parameter space:

$$\boldsymbol{\vartheta} = \left[ V, \boldsymbol{\omega}, \boldsymbol{\delta} \right]^T \tag{2.6}$$

with T denoting the transposition matrix. The output is defined as the desired sinusoidal component:

$$s(t, \Im(t)) = V(t)\sin(\omega(t)t + \delta(t))$$

(2.7)

In order to extract a certain sinusoidal component of v(t), the solution has to be an orthogonal projection of v(t) onto the manifold M, or alternatively it has to be an optimum  $\phi$  that minimizes the distance function d between  $y(t, \theta(t))$  and v(t) i.e.:

$$\mathfrak{S}_{opt} = \arg\min_{\mathfrak{I}(t)\in\vartheta} d[s(t,\mathfrak{I}(t)), v(t)]$$

(2.8)

without being concerned about the mathematical correctness of the definition of least squared error, which strictly speaking has to continue onto the set of real numbers.

The instantaneous distance function *d* is used:

$$d^{2}(t, \Im(t)) = [v(t) - s(t, \Im(t))]^{2} \Delta = e(t)^{2}$$

(2.9)

The cost function is defined as:

$$J(\mathfrak{I}(t),t)\underline{\Delta} d^{2}(t,\mathfrak{I}(t))$$

(2.10)

Although the cost function is not quadratic, the parameter vector  $\Im$  is estimated using the quadratic decent method:

$$\frac{d\Im(t)}{dt} = \mu \frac{\partial [J(t,\Im(t))]}{\partial\Im(t)}$$

(2.11)

The estimated parameter vector is thus denoted by:

$$\hat{\mathfrak{Z}}(t) = [V(t), \hat{\boldsymbol{\omega}}(t), \hat{\boldsymbol{\delta}}(t)]^{T}$$

(2.12)

The complete mathematical proof is presented in [1]. The governing set of equations for the algorithm is:

$$V = k_1 e \sin \phi \tag{2.13}$$

$$\omega = k_2 eV \cos\phi \tag{2.14}$$

$$\dot{\phi} = k_3 e A \cos \phi + \omega \tag{2.15}$$

$$s(t) = V\sin\phi \tag{2.16}$$

$$e(t) = v(t) - s(t)$$

(2.17)

where v(t) and s(t) are the respective input and output signals of the core algorithm. The dot represents the differentiation with respect to time and the error signal e(t) is v(t) - s(t). The state variables V, f and  $\omega$  directly provide estimates of the amplitude, phase and frequency of v(t). Parameters  $k_1$ ,  $k_2$ , and  $k_3$  are positive numbers that determine the behavior of the algorithm in terms of convergence speed and accuracy. Parameter  $k_1$  controls the speed of the transient response of the algorithm with respect to variations in the amplitude of the interfering signal. Parameters  $k_2$ , and  $k_3$  control the speed of the transient response of the variations in the frequency of the algorithm with respect to variations in the frequency of the algorithm with respect to variations in the frequency of the interfering signal [9].

### 2.3 IMPLEMENTATION OF THE PROPOSED ALGORITHM

The dynamics of the proposed algorithm present a notch filter in the sense that it extracts one specific sinusoidal component and rejects all other components, including noise.

It is adaptive in the sense that the notch filter accommodates variations of the characteristics of the desired output over time. The center frequency of such an adaptive filter is specified by the initial condition frequency  $\omega$ . It is the form of simple blocks suitable for schematic software development tools.

Implementation of the proposed algorithm entails the discretization of the differential equations describing the algorithm. The discretized form of the governing equations of the proposed algorithm can be written as:

$$V[n+1] = V[n] + 2T_s k_1 e[n] \sin \phi[n]$$

(2.18)

$$\boldsymbol{\omega}[n+1] = \boldsymbol{\omega}[n] + 2T_{s}k_{2}\boldsymbol{e}[n]\boldsymbol{V}[n]\cos\phi[n]$$

(2.19)

$$\phi[n+1] = \phi[n] + T_s \varpi[n] + 2T_s k_2 k_3 e[n] V[n] \cos \phi[n]$$

(2.20)

$$s[n] = V[n]\sin\phi[n] \tag{2.21}$$

$$e[n] = v[n] - s[n]$$

(2.22)

The first order approximation for the derivative is assumed,  $T_s$  is the sampling time and n is the time step index.

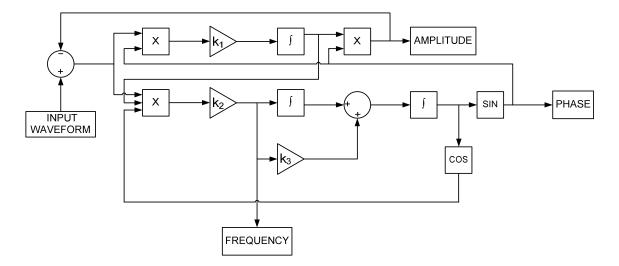

The algorithm can also be implemented as a Simulink model. Figure 2.1 shows an example of the implementation of the algorithm within Simulink. The function of each block within the Simulink model is self-evident. The  $\int$  block is an integrator generating quantity *x* by inputting its derivative (*dx/dt*). The initial conditions are defined within such integrators. The role of the upper branch of Figure 2.1 can be described as the amplitude estimation process and the role of the lower branch as the phase estimation process. The two branches are not self-sufficient and are somewhat interdependent [1].

Figure 2.1: Implementation of the algorithm as a Simulink model [1].

The values of the *k* parameters determine the convergence speed of the algorithm. It is shown in [1] that the values of the *k* parameters have to be chosen such that the two conditions of  $0 < k_1 < 2f_0$  and  $0 < k_2 < \left(\frac{2f_0}{V}\right)^2$  are roughly satisfied. Quantity  $f_0$  is the frequency of the sinusoidal signal of interest and *V* is the amplitude. The choice of  $k_3$  is independent of  $k_2$ . The proposed algorithm is found to be robust not only with regards to its internal structure, but most importantly with regards to the adjustment of its *k* parameters. Numerical experiments show that the performance of the proposed algorithm is almost unaffected by parameter variations as large as 50%. It is also shown that the proposed algorithm is robust with regards to its external conditions [9].

In terms of the engineering performance of the system, this indicates that the output of the system will approach a sinusoidal component of the input signal v(t). Moreover, time variations of the parameters in v(t) are tolerated by the system. One of the issues that needs to be considered when using the proposed algorithm is the setting of its parameters  $k_1$ ,  $k_2$  and  $k_3$ . The value of the parameters  $k_1$ ,  $k_2$  and  $k_3$  determine the convergence speed versus error compromise. The values of the k parameters were changed to better suit the application that is presented. This was done by a trial-and-error basis as there is no specification to determine the k parameters but only guidelines on the ranges for certain functionalities and applications [1].

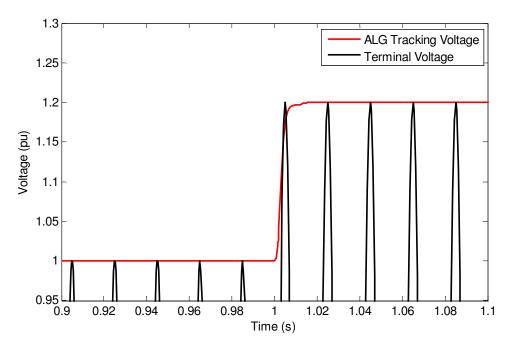

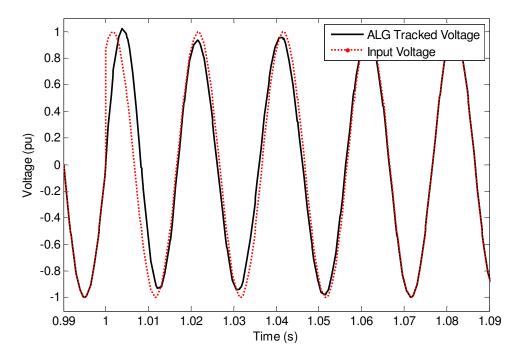

The following k parameters were used to test whether the proposed algorithm does indeed track the amplitude of the terminal voltage if  $k_1 = 800$ ,  $k_2 = 20$  and  $k_3 = 0.01$ .

These parameters do not satisfy the above conditions but were found to trace the amplitude very rapidly and accurately without any oscillations. This is shown in Figure 2.2. The figure also shows the algorithm tracking changes in the terminal voltage. The results are shown in per unit.

Figure 2.2: Terminal voltage magnitude tracked by the algorithm.

## 2.4 PARAMETER OPTIMIZATION FOR AMPLITUDE TRACKING

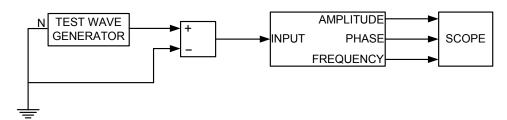

Simulations were performed to demonstrate the performance of the algorithm and to determine the optimal parameter settings of the proposed technique. Table 2.1 shows the parameter settings that were used for step changes in the terminal voltage. The model that was used is shown in Figure 2.3. Starting with the prescribed parameter settings, the parameters are then changed to test the performance and to illustrate the effect of the different parameter settings on the performance. The performance of the parameter settings was then benchmarked to determine the best response time of the algorithm to converge to within five percent of the steady state value. This was used to determine the parameter settings with the least steady state error after two cycles (40ms). The results are shown in Table 2.1. An input voltage of 110V was used. The voltage is converted to a 1pu input into the algorithm.

Figure 2.3: Simulink model used for the testing of the algorithm's parameter settings.

| TEST      | ALGORITHM          |                       | RESPONSE              |           | STEADY STATE |           |      |

|-----------|--------------------|-----------------------|-----------------------|-----------|--------------|-----------|------|

| CONDUCTED | PARAMETER SETTINGS |                       |                       | TIME (ms) |              | ERROR (%) |      |

|           | k <sub>1</sub>     | <b>k</b> <sub>2</sub> | <b>k</b> <sub>3</sub> | STEP      | STEP         | STEP      | STEP |

|           |                    |                       |                       | UP        | DOWN         | UP        | DOWN |

| 1         | 100                | 10000                 | 0.02                  | 57.4      | 56.9         | 12.95     | 12.5 |

| 2         | 1000               | 10000                 | 0.02                  | 12.8      | 22.1         | 1.75      | 12.5 |

| 3         | 800                | 10000                 | 0.02                  | 12.8      | 22.1         | 1.55      | 1.3  |

| 4         | 800                | 100000                | 0.02                  | 25        | 41.4         | 2.25      | 5.2  |

| 5         | 800                | 5000                  | 0.02                  | 21.4      | 31.2         | 0.45      | 3.15 |

| 6         | 800                | 20                    | 0.02                  | 6.3       | 6.3          | 0.05      | 0.15 |

| 7         | 800                | 20                    | 0.2                   | 6.2       | 6.3          | 0.3       | 0.5  |

| 8         | 800                | 20                    | 0.1                   | 6.3       | 6.3          | 0.15      | 0.35 |

| 9         | 800                | 20                    | 0.01                  | 6.3       | 6.3          | 0.05      | 0.15 |

Table 2.1: The proposed algorithm's parameter settings.

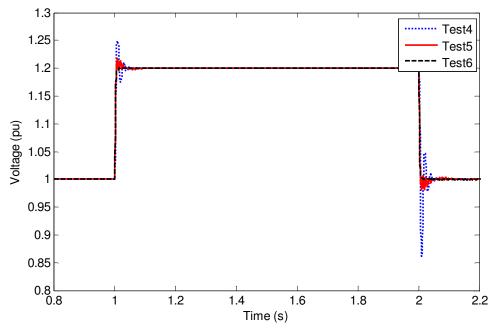

Tests 1 to 3 dealt with the change in the  $k_1$  parameter with the other two parameters kept constant. The results for Test 1 to 3 can be seen in Figure 2.4. For each test conducted a resultant waveform is shown. The results show how the proposed algorithm tracks the step-up (swell) and the step-down (dip) change. The response time and accuracy is unsatisfactory. Tests 2 and 3 show the best response in tracking the step-up change. Oscillations and overshooting is experienced in tracking the change of the terminal voltage. The result shows that as the  $k_1$  parameter is increased, the response time of the algorithm tracking ability decreases. However, inaccuracy due to oscillations and overshooting of up to 5% are experienced. The overshooting and oscillation result in time delays of the algorithm to reach the new nominal value.

Figure 2.4: Algorithm amplitude tracking results for tests 1 to 3.

The results for Tests 4 to 6 is shown in Figure 2.5. Tests 4 to 6 show the results when the  $k_2$  parameter is increased and decreased to the respective values depicted in Table 2.1. The results show that the algorithm tracks changes in voltage very quickly. The result also shows that when  $k_1$  and  $k_2$  are changed, the response of the algorithm increases for a change in the voltage. The accuracy and speed are however not satisfactory. Oscillations and overshooting of up to 15% are experienced in the tracking of the change in the terminal voltage. This makes the overall response of the algorithm inaccurate and slow.

Figure 2.5: Algorithm amplitude tracking results for tests 4 to 6.

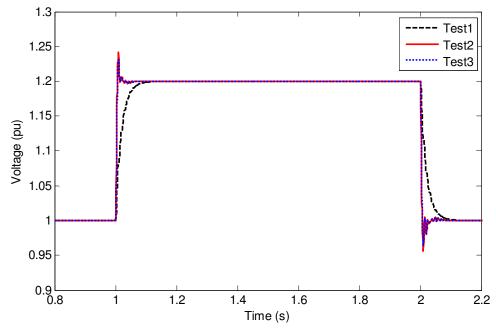

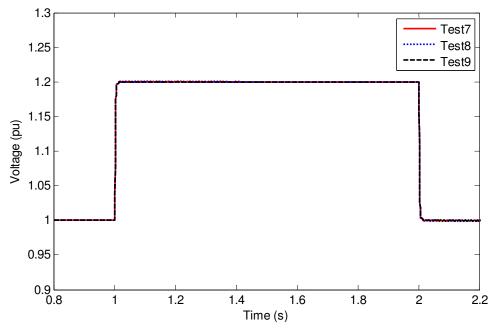

Tests 7 to 9 deal with the change in the  $k_3$  parameter with the other two parameters kept constant. The  $k_3$  parameter is increased and decreased to the respective values shown in Table 2.1. The results for Test 7 to 9 is shown in Figure 2.6. Figure 2.6 shows how the algorithm tracks the changes in the voltage amplitude. The result shows how the algorithm tracks the settings used in Test 7. A stable and a satisfactory output is achieved. The decrease in the  $k_3$  parameter had a major influence on the response of the algorithm. This caused a stable result in the value of the terminal voltage. The result for Test 9 shows that the algorithm can track the changes in the voltage amplitude very quickly and accurately with minor overshooting. The settings used for Test 9 vary with Tests 7 and 8. The results were found to be very close to each other for a step change in the amplitude.

Figure 2.6: Algorithm amplitude tracking results for tests 7 to 9.

# 2.5 PARAMETER OPTIMIZATION FOR PHASE AND FREQUENCY TRACKING

Simulations were performed to determine the optimal parameter settings of the proposed technique for phase and frequency changes. The same procedure was used as for the parameter optimization in section 2.3. Starting with the prescribed parameter settings, the parameters are then changed to test the performance and to illustrate the effect of the different parameter settings on the performance. The performance of the parameter settings was then benchmarked to determine the best response time for the algorithm to converge to within five percent of the steady state value. This was used to determine the parameter settings with the least steady state error after two cycles (40ms).

## 2.5.1 Parameter Optimization for Phase Changes

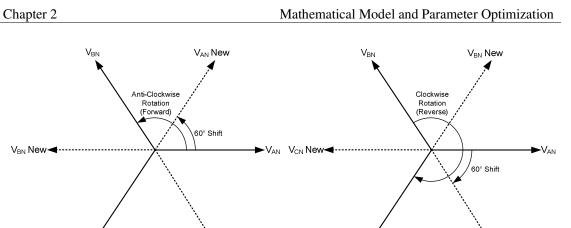

Simulations were performed to determine the optimum parameters for tracking the phase angle of an input signal under normal and changing conditions. A phase angle step change of 60° in a forward (anti-clockwise) and reverse (clockwise) direction were performed. The phase angle was first shifted forward by 60° and then in reverse by 60°. Figure 2.7 shows the 60° forward and reverse phase shift vectors. During the phase changes the voltage amplitude is kept constant.

Figure 2.7: Forward and reverse phase shifts.

V<sub>CN</sub>

V<sub>CN</sub> New

V<sub>CN</sub>

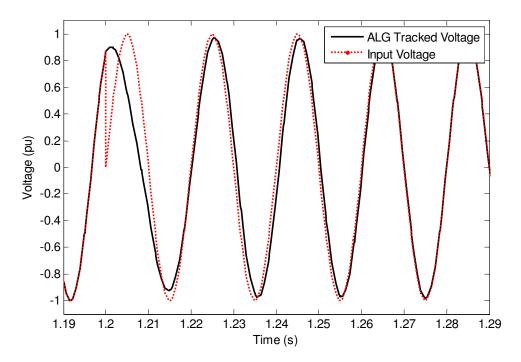

Figure 2.8 and 2.9 show the algorithm tracking the phase angle change of 60° in both directions with the normal parameter settings of  $k_1 = 100$ ,  $k_2 = 10000$  and  $k_3 = 0.02$ . The step changes in the phase angle were done at one second as shown in Figure 2.8 and at 1.2 seconds as shown in Figure 2.9. The results show that the algorithm can track the phase accurately and will track the change to converge in three cycles.

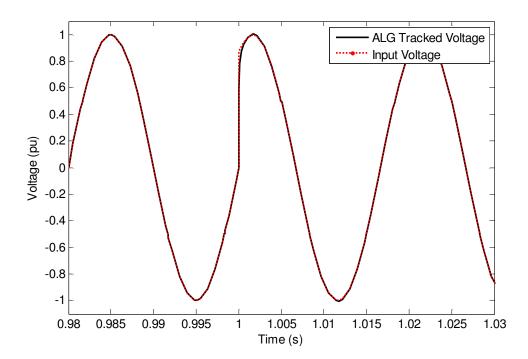

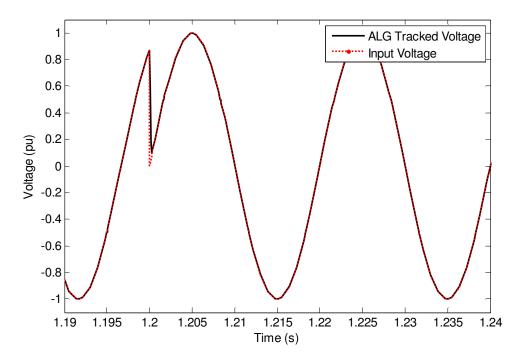

Figures 2.10 and 2.11 show the algorithm tracking the phase angle change of 60° in both directions. The optimized parameter settings of  $k_1 = 80$ ,  $k_2 = 10000$  and  $k_3 = 1.8$  was used. The step changes in the phase angle were done at one second as shown in Figure 2.10 and at 1.2 seconds as shown in Figure 2.11. The results show that the algorithm can track the phase accurately and will converge within half a cycle. Using the optimized parameter settings a two cycle improvement in the speed of the response is achieved.

$V_{AN}$  New

Figure 2.8: Algorithm phase tracking for 60° forward step change with normal parameters.

Figure 2.9: Phase tracking for 60° backward step change with normal parameters.

Figure 2.10: Phase tracking for 60° forward step change with optimized parameters.

Figure 2.11: Phase tracking for 60° backward step change with optimized parameters.

### 2.5.2 Parameter Optimization for Frequency Changes

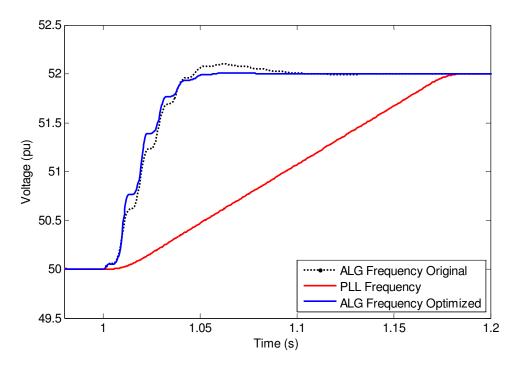

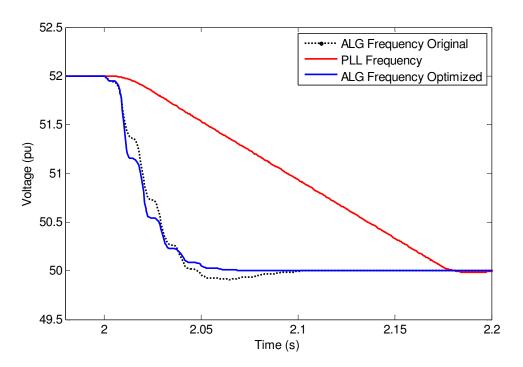

Simulations were performed to determine the optimum parameters for tracking frequency changes of an input signal under normal and changing conditions. A frequency step change of 2Hz was performed. The response of the algorithm was benchmarked against the PLL frequency tracking results of the same input signal. Figures 2.12 and 2.13 show the algorithm tracking the frequency with the normal parameter settings of  $k_1 = 100$ ,  $k_2 = 10000$  and  $k_3 = 0.02$  and the optimized settings of  $k_1 = 1500$ ,  $k_2 = 16500$  and  $k_3 = 0.02$ . The step changes in the frequency were done at one second as shown in Figure 2.12 and at two seconds as shown in Figure 2.13. The results show that the algorithm can track the frequency accurately and will track the change to converge in two cycles. With the normal parameters an overshoot of 1% is experienced. The results show that the algorithm can track the frequency change accurately and will track the change to converge within two cycles with no overshooting. With the optimized parameter settings no improvement in the speed of the response is achieved, an improvement in accuracy is achieved.

Figure 2.12: Frequency tracking for a 2Hz increase.

Figure 2.13: Frequency tracking for a 2Hz decrease.

### 2.6 CONCLUDING REMARKS

In this chapter a mathematical formulation of the nonlinear filter was presented. The algorithm's settings were optimized to produce the best response in terms of speed and accuracy. From the results of the tests that were conducted it is clear that the response of the algorithm for a step increase in the voltage amplitude is determined by the  $k_1$  parameter. The lower this parameter setting is, the slower the response from the algorithm for both an increase and decrease in the voltage amplitude. It was also seen that the combination of the  $k_2$  and  $k_3$  parameters controls the response of the algorithm for a decrease in the voltage amplitude. The lower the  $k_2$  parameter is the parameter that mostly influences the response of the algorithm for a decrease in the voltage amplitude. The lower the  $k_2$  parameter, the faster the response. However, this impacts overshooting.

The optimization of the parameters for tracking phase and frequency yielded satisfactory results. It showed that with optimized parameter settings the algorithm can respond fast and accurate for changes in phase and frequency.

Although the final settings used did not result in the algorithm's fastest response time, it did provide the most accurate and stable response for step increases or decreases in the voltage amplitude. One of the most important characteristics of the algorithm is that the settings can be customized according to the type of application as well as for the desired response and accuracy for an application.

# **CHAPTER 3**

# EXCITATION CONTROL ON A SYNCHRONOUS GENERATOR

# 3.1 INTRODUCTION

Michael Faraday discovered in 1831 that an electrical voltage is induced in a conductor when the conductor is moved through a magnetic field. The magnitude of this induced voltage is directly proportional to the strength of the magnetic field and the rate at which the magnetic field crosses the conductor.

There are two types of generators, namely Direct Current (DC) and Alternating Current (AC). AC generators are either asynchronous (induction) or synchronous. Synchronous generators are used because they can both supply or absorb active and reactive power. The synchronous machine consists of a stator and a rotor circuit.

When mutual flux develops between the rotor and the stator in the air gap, an Electromagnetic Force (EMF) is produced. The magnetic flux developed by the DC field poles crosses the air-gap and a sinusoidal voltage is developed at the generator output terminals. The magnitude of the output voltage is controlled by the amount of DC-exciting current that is applied to the field circuit [10-11]. This is accomplished through the exciter. The exciter is the power source that supplies the DC magnetizing current to the field windings of the synchronous generator. There are two basic types of exciters:

- Slip rings: older systems make use of slip rings to supply the rotor circuit with a DC voltage.

- Rotating rectifiers: modern systems use AC generators with rotating rectifiers. These are known as 'brushless exciters' [11].

Changes in real power mainly affect the system frequency. Voltage magnitudes depend on the system's reactive power requirement. The exciter, or Automatic Voltage Regulator (AVR), regulates the generator's reactive power output as well as the terminal voltage magnitude. Increasing the generator's reactive power output results in a drop in the magnitude of the terminal voltage.

This voltage drop is sensed through a potential transformer for either one or all three phases.

The voltage is then rectified and compared to the DC set point of the AVR. The error signal is amplified and it controls the exciter field. Through this action the generator field current is increased, resulting in an increased EMF. This increases the reactive power generation to a new equilibrium. The terminal voltage is increased to the desired value. Hence, control of the generator terminal voltage is achieved [12]. The amplifier may be magnetic, rotating or electronic.

A variety of different AVR models are used for power system studies. These are:

- DC Direct Current Commutation Exciters,

- AC Alternator Supplied Rectifier Exciter System, and

- ST Static Excitation System.

Modern AVR models use an AC power source through solid-state rectifiers such as a Silicon Controlled Rectifier (SCR). The AVR model of the Institute of Electrical and Electronic Engineers (IEEE) is an AC alternator-supplied rectifier excitation system. This is recommended for power systems [13].

An increase in the load requirement of the power system to near capacity results in difficulty of ensuring stable power system operation. This is especially the case when expansion of the transmission network does not follow growth on the system. When this occurs, security margins are smaller and the power system operates on the brink of instability. This can result in a blackout. It is therefore important to develop a means of monitoring and controlling the dynamics of the system for [11, 12]:

- stability monitoring and assessment,

- preventative emergency control, and

- increasing the transmission capability of existing assets.

The purpose of this chapter is to compare the voltage tracking abilities of the algorithm to that of a Diode Bridge Rectifier. The steady state errors as well as the response times are compared through the simulation of changes in magnitudes of the input voltage.

The two tracking methods are also compared through the response simulation of the synchronous generator using the algorithm and the diode bridge rectifier to track the voltage magnitude for input into the AVR. Both methods are simulated using parameters from an in use synchronous generator.

# **3.2 BASIC SYNCHRONOUS MACHINE AND EXCITATION CONTROL** THEORY

## 3.2.1 The Synchronous Machine

The synchronous machine is the principle source of electric energy to the power system. It delivers active and reactive power, but can also be used as a synchronous condenser providing only reactive power compensation to control the voltage of the power system.

The synchronous machine has two essential elements, namely the field circuit and the armature circuit. The field circuit carries DC and produces a magnetic field which induces an alternating voltage in the armature windings. The armature windings operate at a voltage that is much higher than that of the field windings and therefore require more space for insulation. The armature windings are also subject to high transient currents and must have adequate mechanical strength. It is therefore normal practice to have the armature on the stator. The three windings of the armature are distributed 120° apart in space, resulting in a voltage displacement of 120° during uniform rotation of the magnetic field.

When carrying balanced three-phase currents, the armature will produce a magnetic flux in the air-gap that is rotating at synchronous speed. The field produced by the direct current in the rotor winding revolves with the rotor. Therefore, for the production of a steady-state torque, the field of the stator and the rotor must rotate at the same, synchronous speed. The number of field poles is determined by the mechanical speed of the rotor and the electric frequency of the stator currents.

The DC in the field is produced by the synchronous machine's AVR. As this current directly influences the strength of the field in the armature, it thus controls the magnitude of the voltage induced in the armature and consequently controls the voltage on the synchronous machine's terminals [14].

### 3.2.2 Basic Control of a Synchronous Machine

The objective of the control of the synchronous generator is to generate and deliver power in an interconnected system as economically and reliably as possible, while still maintaining the voltage and frequency within permissible limits. A change in the real power affects the system frequency, while reactive power contributes to changes in the voltage magnitude. Real power and frequency are controlled by the Load Frequency Control (LFC) and the reactive power and voltage magnitude are controlled by the AVR.

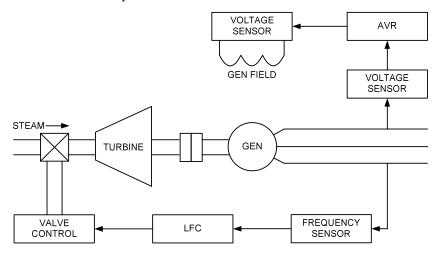

The LFC and AVR are installed for each generator. Figure 3.1 shows the schematic diagram for the two control loops.

Figure 3.1: Schematic diagram of LFC and AVR control loops [12].

The LFC and AVR are set to control small changes in load demand to maintain the frequency and voltage magnitude within specified limits of 1.5% for the frequency and 5% for the voltage magnitude continuously. Small changes in real power are dependent on changes in the rotor angle  $\delta$ , and thus also on the frequency. Reactive power is dependent on the voltage magnitude, and thus the excitation system [12].

The excitation time constant is much smaller than the prime mover time constant. Its transient decays much faster and it does not affect the LFC dynamics. This means that the cross-coupling between the LFC and the AVR is negligible and that the two control loops can be analyzed independently.

### **3.2.3** The Excitation System

The excitation system of the generator maintains the system voltage and controls reactive power flow. Typical sources of reactive power include generators, capacitors and reactors. As the reactive power requirement increases in the power system, the terminal voltage decreases. This change in the terminal voltage is sensed by a potential transformer in one phase. The voltage is rectified and compared to a DC set-point signal. The amplified error signal then controls the exciter field and increases the exciter terminal voltage. The generator field current is also increased. This results in an increase in the generated EMF. The resultant reactive power generated is increased to a new level. This in turn raises the terminal voltage to the desired value.

The function of the excitation system is to provide DC to the field winding of the synchronous machine. This enables the excitation system to control the terminal voltage and the reactive power. It also enables the excitation system to protect the synchronous machine and induces satisfactory performance from the power system by controlling the field voltage and thereby also the field current [12].

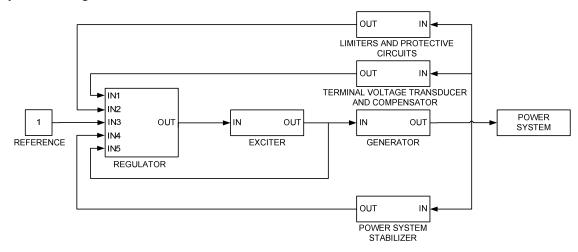

Figure 3.2 shows a functional block diagram for a typical excitation system for a large synchronous generator.

Figure 3.2: Block diagram for a synchronous machine excitation control system [12].

The exciter provides the field winding with direct current. This constitutes the power stage of the excitation system. The regulator processes and amplifies the input control signals to the appropriate level and form for control of the exciter. The generator's terminal voltage

is sensed, rectified and filtered to a DC quantity through the terminal voltage transducer and compensator. This DC quantity is then compared to a reference value which is the desired terminal voltage. The power system stabilizer provides an additional input signal to the regulator to dampen power system oscillations. Limiters and protective circuits include a wide array of control and protective functions. This ensure that the capability of limits of the exciter and the synchronous generator are not exceeded. A variety of different excitation types exist. Modern excitation systems use solid-state rectifiers (such as SCR) as power sources. The static excitation system was used for this research due to the simplicity involved to simulate the system [12].

### 3.2.4 The Static Excitation System

All components in the static excitation system are static or stationary. Static rectifiers, whether they are controlled or uncontrolled, supply the excitation current directly to the field of the synchronous generator through slip rings. Potential transformers are used to step-down the terminal voltage to an appropriate level for the excitation system used [12].

There are three types of static excitation systems, namely:

- potential-source controlled-rectifier systems,

- compound-source rectifier systems, and

- compound-controlled rectifier excitation systems.

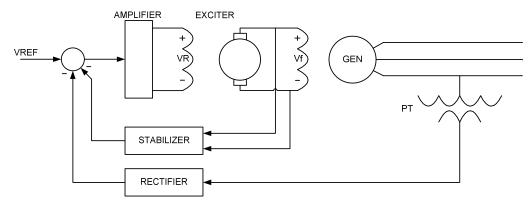

The potential-source controlled rectifier system, or bus/transformer fed system, was used in this study. The excitation power of this type of system is supplied through a transformer from the terminal or station's auxiliary bus of the generator. This voltage is regulated and controlled by a rectifier. This is shown in Figure 3.3.

Figure 3.3: Typical arrangement of a simple AVR [12].

The system that has been used in this study has an inherently small time constant. The maximum exciter output voltage is controlled by the input AC voltage. Under fault conditions the generator's terminal voltage is reduced. The limitation of this type of system is corrected by its virtually instantaneous response and high post-fault field-forcing capability. This type of system is inexpensive, easily maintainable and performs well for generators connected to large power systems. The rectifier is an important part of the Static Excitation System. It converts the AC feedback voltage to a DC quantity so that the AVR can control the system's terminal voltage.

Power electronics has gained widespread popularity and is vital in various applications. In such systems, the 50/60Hz input voltage is first converted into a desired DC voltage. This is subsequently converted into the voltages and currents of appropriate magnitude, frequency and phase in order to meet load requirements. The DC output of the rectifier must be as ripple-free as possible (5-10% of peak  $V_{dc}$ ) depending on the application. For this reason a large capacitor is connected as a filter on the DC side of the diode bridge. Since this capacitor is charged to a value close to the peak AC magnitude, the rectifier then draws a highly distorted current from the utility. For generators from a few kilowatts to a multi-megawatt power levels, the interface with the utility is preferred to be three phase rather than single phase because of the three-phase's lower ripple content in the waveforms and a higher power-handling capability [12].

## 3.3 BASIC THEORY OF THE DIODE BRIDGE RECTIFIER

## 3.3.1 Operation of the Diode Bridge Rectifier

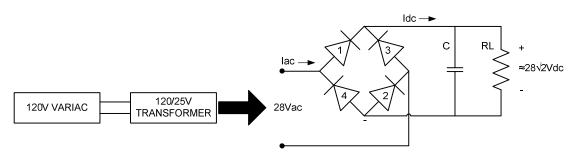

To explain the basic operation of the diode bridge rectifier, a single-phase diode bridge is used. The basic components of the single-phase rectifier are four diodes and a large electrolytic capacitor. The four diodes are often packaged together as one four-terminal device. The diodes rectify the incoming  $V_{ac}$  and smoothes the peak-to-peak voltage in  $V_{dc}$ to a reasonable value (5-10% of peak  $V_{dc}$ ). A rectifier circuit is shown below in Figure 3.4. When  $V_{ac}$  is positive, diodes 1 and 2 serve as conductors. Diodes 3 and 4 are reverse biased and open. When  $V_{ac}$  is negative, diodes 3 and 4 also serve as conductors. In this state diodes 1 and 2 are reverse biased and open [15].

Excitation Control on a Synchronous Generator

Figure 3.4: Single-phase diode bridge rectifier with capacitor filter [15].

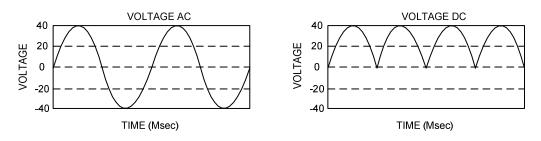

In Figure 3.4 above C =  $18000\mu$ F, P = 200W, F = 50Hz and V<sub>ac</sub> = 28V. In order to understand the operation of the circuit one can assume that the capacitor is removed and that the system impedance is small. The resulting voltage waveform with the V<sub>ac</sub> = 28V is shown in Figure 3.5.

Figure 3.5: AC and DC voltage waveforms with the DC load resistor and no capacitor [15].

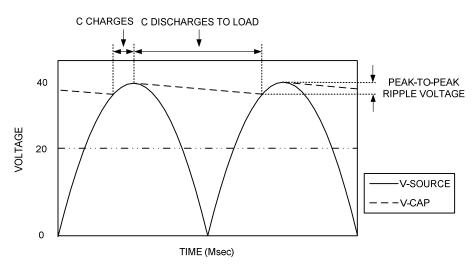

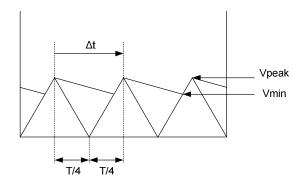

The addition of the capacitor C smoothes the DC voltage waveform. When the time constant RLC significantly exceeds (T/2), where (T = 1/f), the capacitor provides load power when the rectified AC voltage falls below the capacitor value. This is illustrated by Figure 3.6 below [15].

Figure 3.6: Impact of C on the load voltage [15].

As the load power increases, the capacitor discharges faster. The peak-to-peak ripple voltage increases and the average DC voltage (i.e. the average value of the  $V_{cap}$  curve in Figure 3.6) falls. For zero loads,  $V_{cap}$  remains equal to the peak of the rectified source voltage, and the ripple voltage is therefore zero.

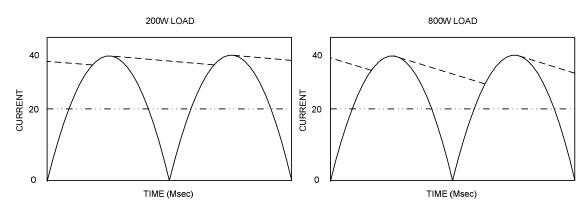

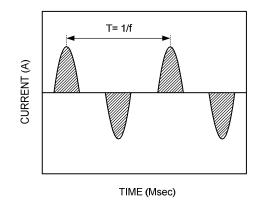

Current and power flow from the AC side only when C is charging. When C is discharging, the voltage on C is greater than the rectified source voltage and the diodes prevent current form flowing back to the AC side. Thus, the AC current and power flow into the circuit at relatively short bursts. As load power increases, the width of the current bursts becomes wider and taller as illustrated in Figure 3.7. The shape of the current pulse depends on the system impedance. If the impedance is mainly resistive, the current pulse resembles the top portion of the sine wave. Inductance in the system causes a skewing to the right. Figure 3.7 illustrates how the average voltage of the load drops as load power increases. This is due to the capacitor action and is not due to the DBR (Diode Bridge Rectifier) resistance.

Figure 3.7: DC-side current I<sub>dc</sub> for two different load levels [15].

Inductance in the power system and transformer will cause the current to flow after the peak of the voltage curve. In that case the capacitor voltage will follow the rectified voltage wave for some time after the peak. The higher the power level, the longer the current flows.

Reflected on the AC side, the current is alternating with the zero average value and halfwave symmetry for the 200W example, as shown below in Figure 3.8 [15].

Figure 3.8: AC-side current Iac [15].

## 3.3.2 Calculation of the DC Ripple Voltage for Constant Loading

Most power electronic loads require constant power. Representing the load as a fixed resistor, as shown in Figure 3.4, is inaccurate [15].

For constant power cases, the peak-to peak voltage ripple can be computed using energy balance in the capacitor as follows. If the "C discharging" period in Figure 3.6 is  $\Delta t$ ;

where

$$\frac{T}{4} \le \Delta t \le \frac{T}{2}$$

, then the energy provided by *C* during  $\Delta t$  is:

$$\frac{1}{2}C(V_{peak}^2 - V_{min}^2) = P\Delta t, \qquad (3.1)$$

and

$$V_{min}$$

are the peak and minimum capacitor voltages in Figure 3.6, and P is

where  $V_{peak}$  and  $V_{min}$  are the peak and minimum capacitor voltages in Figure 3.6, and *P* is the DC load power (approximately constant). From (3.1):

$$\left(V_{peak}^2 - V_{\min}^2\right) = \frac{2P\Delta t}{C}$$

(3.2)

Factorizing the quadratic yields:

$$\left(V_{peak} - V_{\min}\right) \times \left(V_{peak} + V_{\min}\right) = \frac{2P\Delta t}{C}$$

(3.3)

or:

$$\left(V_{peak} - V_{\min}\right) = \frac{2P\Delta t}{C(V_{peak} + V_{\min})}$$

(3.4)

At this point a simplification can be made if the following assumptions are made as shown in Figure 3.9. The AC sine wave of the voltage is approximated as a triangular wave, and a straight line decay of the voltage occurs [15].

Excitation Control on a Synchronous Generator

Figure 3.9: Approximation of the waveform used for ripple calculation formula [15].

The simple geometry shows the relationship between  $\Delta t$  and  $(V_{peak} - V_{min})$  to be:

$$\Delta t = \frac{T}{4} + \frac{V_{\min}}{V_{peak}} \times \frac{T}{4} = \frac{T}{4} \left( 1 + \frac{V_{\min}}{V_{peak}} \right), \text{ or } \Delta t = \frac{T}{4V_{peak}} \left( V_{peak} + V_{\min} \right)$$

(3.5)

Substituting (3.5) into (3.4) yields:

$$(V_{peak} - V_{min}) = \frac{2P \frac{T}{4V_{peak}} (V_{peak} - V_{min})}{C(V_{peak} + V_{min})} = \frac{PT}{2CV_{peak}}$$

(3.6)

Since (T = 1/f), the final expression for the ripple voltage becomes:

$$\left(V_{peak} - V_{\min}\right) = V_{peak-to-peak} = \frac{P}{2fCV_{peak}}$$

(3.7)

Thus for the example being used:

$$V_{peak-to-peak} = \frac{200}{2 \times 60 \times 18000 \times 10^{-6} \times 28\sqrt{2}} = 2.33V$$

(3.8)

Expressed as a percent of the peak voltage, the ripple voltage at 200W load is approximately:

$$\% V_{ripple} = \frac{V_{peak-to-peak}}{V_{peak}} = \frac{2.33}{28\sqrt{2}} = 5.88\%$$

(3.9)

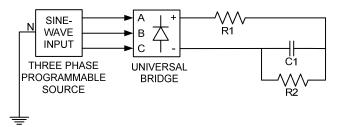

## **3.4 DIODE BRIDGE RECTIFIER MODEL**

This section shows the diode bridge rectifier model that is used in the simulations in Matlab Simulink as illustrated in Figure 3.10. The resistance and capacitance values, taken from an in-service exciter, for the filter equipment can be seen in Table 3.1. The diode bridge consists of one three-phase diode bridge rectifier and an RC filter circuit. The

Chapter 3

rectifier circuit has one input voltage. The circuit has a very small ripple voltage and a high accuracy of the output voltage.

Figure 3.10: Diode bridge rectifier used in the research simulations.

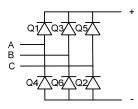

Figure 3.11 depicts the internal connection of the universal bridges. This shows the connection of the diodes internal to the universal bridges.

Figure 3.11: Diode bridge connections.

The diode bridges are identical and have snubber resistances as well as very low internal resistances. Snubber resistances are used to avoid numerical oscillations when the system is discretized. Snubber resistance and capacitance values for diode bridges need to be specified. To eliminate the snubbers from the circuit, one has to set the snubber resistance to zero and the capacitance to infinite. This, however, does not influence the characteristics of the capacitor's charge and discharge times.

Table 3.1: Filter parameters.

| FILTER EQUIPMENT | EQUIPMENT RATING | UNIT             |

|------------------|------------------|------------------|

| R1               | 12.9             | Kilo Ohm (kΩ)    |

| R2               | 24.8             | Kilo Ohm (kΩ)    |

| C1               | 4.7              | Micro Farad (µF) |

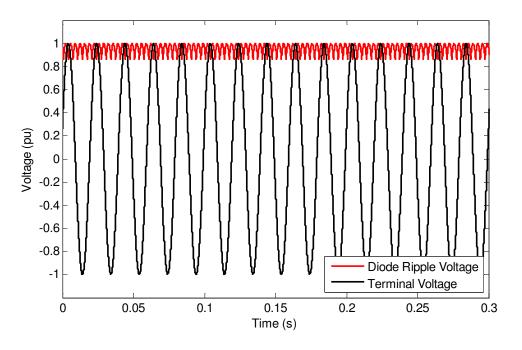

Figures 3.12 and 3.13 illustrate the output wave forms from the diode bridge rectifier with and without the filter circuit compared to the terminal input voltage. Note that the ripple voltage is very large without the filter circuit. The diode and filter output wave is shown in red with the terminal voltage shown in blue. All wave forms are shown in the per unit

scale. The resultant ripple voltage from the diode bridge rectifier is about 1.24V, which is less than 1% of the terminal voltage of 110V rms. This shows that the diode bridge rectifier is very accurate when used in the simulations for the research being done.

Figure 3.12: Terminal voltage vs. diode bridge rectifier output without filter circuit.

Figure 3.13: Terminal voltage vs. diode bridge rectifier output with filter circuit.

# **3.5 PERFORMANCE OF BOTH METHODS FOR A CHANGE IN THE VOLTAGE MAGNITUDE**

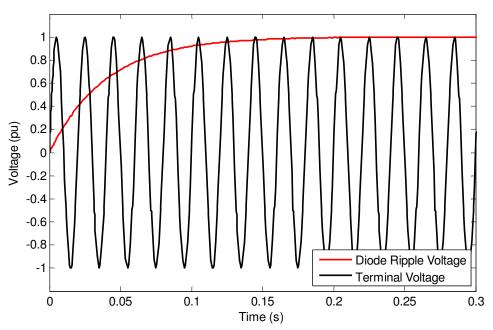

This section compares the performance of the diode bridge rectifier and the nonlinear filter to the track step changes in the voltage amplitude. The model uses a programmable voltage source to supply a controlled terminal voltage. The input signal from the sources feeds the diode bridge rectifier. It is then registered (measured) and scaled as a per-unit value into the algorithm. This is shown in Figure 3.14. The programmable voltage source was set to simulate step changes in the input voltages as would be experienced in the power system. The model was simulated as a combination of the diode bridge rectifier and algorithm.

Figure 3.14: Model for the direct comparison between the diode bridge rectifier and the algorithm.

Two sets of tests were performed to determine the nonlinear filter's response to that of the diode bridge rectifier. The first simulation tests the response for a change in the step magnitude. The tests ranges for a 10% (0.1pu) to a 100% (1pu) step change in the voltage amplitude. The tests and the response times for this type test are shown in Table 3.2 and Table 3.3 for the algorithm and diode bridge rectifier respectively.

An input voltage of 80V (1pu) RMS phase-to-phase is used. The step change is set to switch on at one second, and switch off at two seconds. The parameter settings used for the algorithm are the optimized settings obtained in Chapter 2. The same settings are used for the different magnitude input voltages. The diode bridge rectifier model is that of Section 3.4.

### Chapter 3

The performance was tested to determine the response time for both methods to converge to within 5% of the steady state value, and the steady state error after two cycles (40ms).

|     |               |               | Algorithm      |               |                    |  |  |

|-----|---------------|---------------|----------------|---------------|--------------------|--|--|

| Те  | est Conducted | Response Time | Response Time  | Steady-State  | Steady-State Error |  |  |

|     |               | Step-Up (ms)  | Step-Down (ms) | Error Step-Up | Step-Down          |  |  |

| 1.  | 1pu to 1.1pu  | 6.3           | 6.3            | 0.00          | 0.00               |  |  |

| 2.  | 1pu to 1.2pu  | 6.3           | 6.3            | 0.05          | 0.1                |  |  |

| 3.  | 1pu to 1.3pu  | 6.3           | 6.3            | 0.10          | 0.23               |  |  |

| 4.  | 1pu to 1.4pu  | 6.3           | 6.3            | 0.10          | 0.05               |  |  |

| 5.  | 1pu to 1.5pu  | 6.3           | 6.3            | 0.12          | 0.32               |  |  |

| 6.  | 1pu to 1.6pu  | 6.3           | 6.3            | 0.12          | 0.32               |  |  |

| 7.  | 1pu to 1.7pu  | 6.4           | 6.4            | 0.13          | 0.29               |  |  |

| 8.  | 1pu to 1.8pu  | 6.4           | 6.4            | 0.14          | 0.24               |  |  |

| 9.  | 1pu to 1.9pu  | 6.4           | 6.4            | 0.16          | 0.18               |  |  |

| 10. | 1pu to 2pu    | 6.4           | 6.4            | 0.17          | 0.17               |  |  |

Table 3.3: Diode bridge rectifier test set 1 results.

|    |               | Diode Bridge Rectifier |                |               |                    |

|----|---------------|------------------------|----------------|---------------|--------------------|

| Τe | est Conducted | Response Time          | Response Time  | Steady-State  | Steady-State Error |

|    |               | Step-Up (ms)           | Step-Down (ms) | Error Step-Up | Step-Down          |

| 1  | 1pu to 1.1pu  | 119.2                  | 127.4          | 35.50         | 37.50              |

| 2  | 1pu to 1.2pu  | 119.3                  | 121.2          | 35.95         | 37.10              |

| 3  | 1pu to 1.3pu  | 119.4                  | 120.8          | 36.17         | 36.83              |

| 4  | 1pu to 1.4pu  | 119.4                  | 118.5          | 36.18         | 36.78              |

| 5  | 1pu to 1.5pu  | 119.4                  | 118.5          | 36.24         | 36.76              |

| 6  | 1pu to 1.6pu  | 119.4                  | 118.5          | 36.25         | 36.73              |

| 7  | 1pu to 1.7pu  | 119.3                  | 118.5          | 36.21         | 36.81              |

| 8  | 1pu to 1.8pu  | 119.3                  | 118.6          | 36.26         | 36.90              |

| 9  | 1pu to 1.9pu  | 117.4                  | 118.8          | 36.24         | 37.26              |

| 10 | 1pu to 2pu    | 116.4                  | 119.6          | 36.28         | 37.74              |

#### Chapter 3

The second set of tests determined the response for a 10% step change in the magnitude. The tests and the response times for the algorithm are shown in Table 3.4. The results for the diode bridge rectifier are shown in Table 3.5.

|                | $\mathbf{c}$    |               |                |               |                 |  |

|----------------|-----------------|---------------|----------------|---------------|-----------------|--|

|                |                 | Algorithm     |                |               |                 |  |

| Test Conducted |                 | Response Time | Response Time  | Steady-State  | Steady-State    |  |

|                |                 | Step-Up (ms)  | Step-Down (ms) | Error Step-Up | Error Step-Down |  |

| 1              | 0.2pu to 0.22pu | 6.4           | 6.4            | 0.00          | 0.25            |  |

| 2              | 0.4pu to 0.44pu | 6.3           | 6.4            | 0.25          | 0.25            |  |

| 3              | 0.6pu to 0.66pu | 6.3           | 6.4            | 0.42          | 0.08            |  |

| 4              | 0.8pu to 0.88pu | 6.3           | 6.3            | 0.31          | 0.31            |  |

Table 3.5: Diode bridge rectifier test set 2 results.

|   |                 | Diode Bridge Rectifier |               |               |                 |  |

|---|-----------------|------------------------|---------------|---------------|-----------------|--|

|   | Test Conducted  | Response Time          | Response Time | Steady-State  | Steady-State    |  |

|   |                 | Step-Up                | Step-Down     | Error Step-Up | Error Step-Down |  |

| 1 | 0.2pu to 0.22pu | 102.6                  | 114.4         | 17.75         | 18.75           |  |

| 2 | 0.4pu to 0.44pu | 109.1                  | 134.2         | 17.13         | 19.63           |  |

| 3 | 0.6pu to 0.66pu | 119.5                  | 124.2         | 18.00         | 18.42           |  |

| 4 | 0.8pu to 0.88pu | 129.2                  | 120.9         | 18.31         | 18.25           |  |

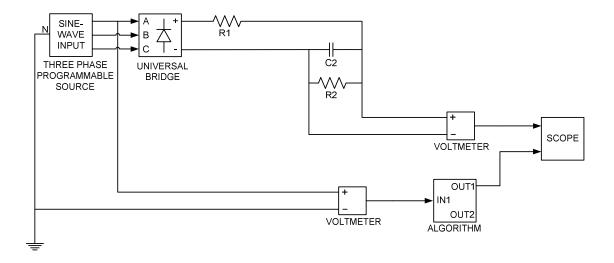

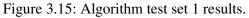

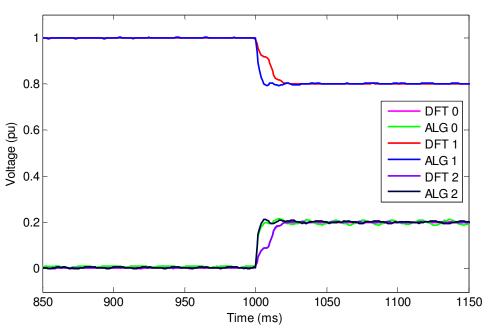

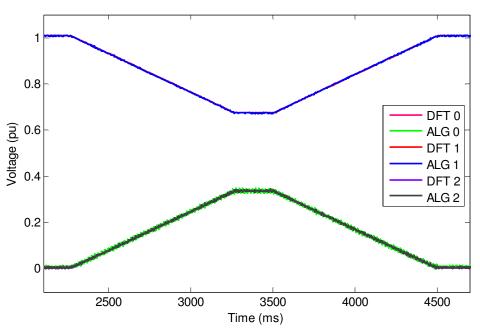

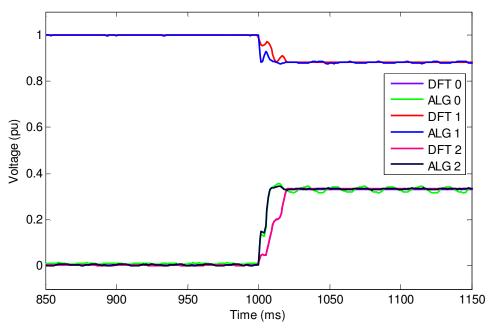

The results for the algorithm are shown in Figure 3.15 and Figure 3.16. It shows that the response time for both the increase and decrease in the voltage magnitude is very fast and accurate for both the types of tests conducted. The step-up and step-down changes are tracked within less than half a cycle.

Figure 3.16: Algorithm test set 2 results.

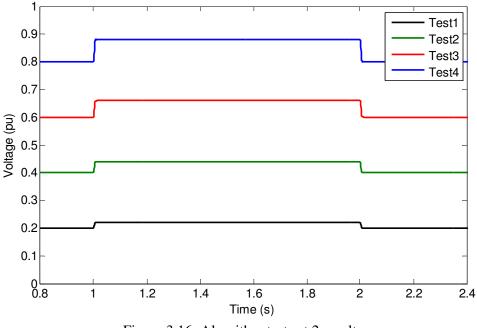

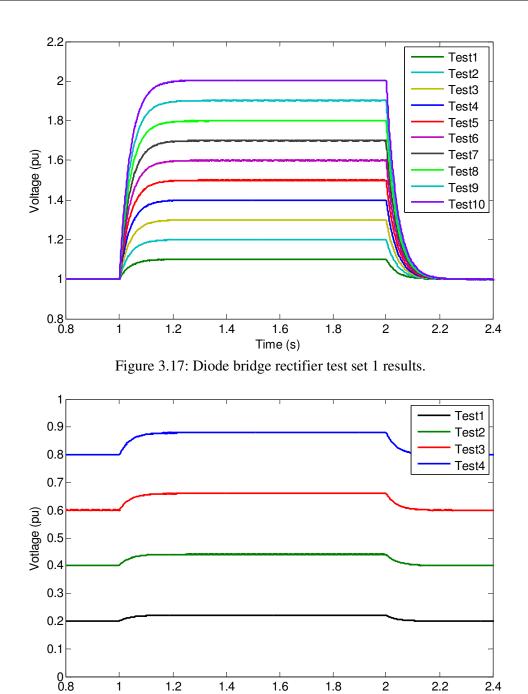

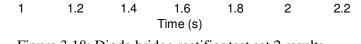

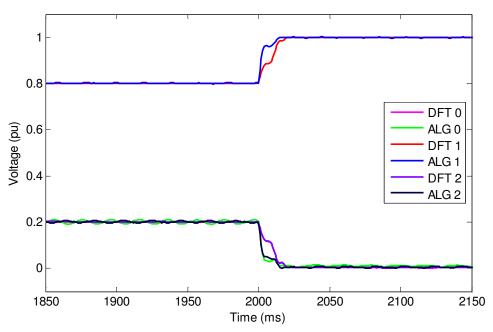

The results for the DBR shown in Figure 3.17 and Figure 3.18 demonstrate that the response time for both the increase and decrease in the voltage magnitude stay constant and less accurate than that of the algorithm for both the types of tests conducted. The step-up change is tracked within six cycles. The step-down change is tracked within seven cycles.

Figure 3.18: Diode bridge rectifier test set 2 results.

2.4

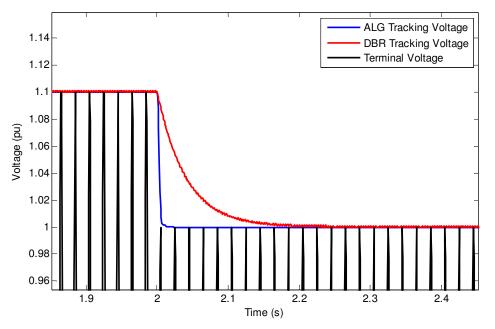

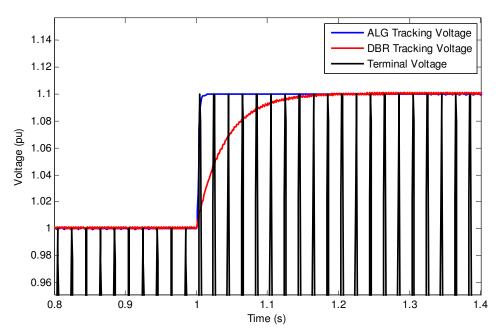

Figure 3.19 and Figure 3.20 show the comparison between the diode bridge rectifier and the algorithm tracking the changes in the voltage amplitude accurately and quickly. It clearly shows an improved performance of the algorithm over the diode bridge rectifier.

Figure 3.19: Diode bridge rectifier compared to the algorithm.

Figure 3.20: Diode bridge rectifier compared to the algorithm.

#### Chapter 3

### **3.7 THE CLOSED-LOOP SYSTEMS**

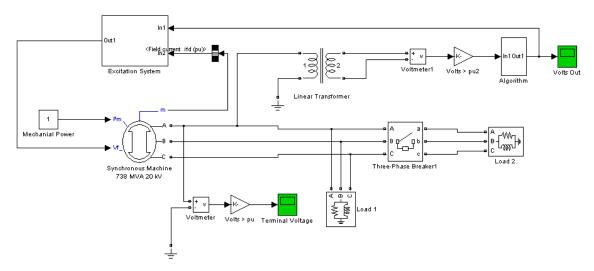

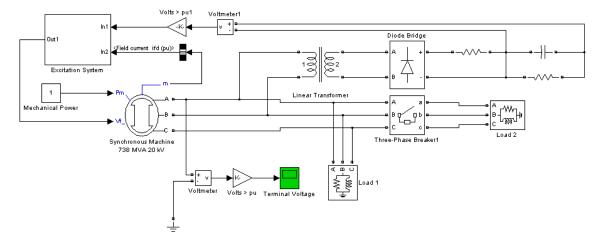

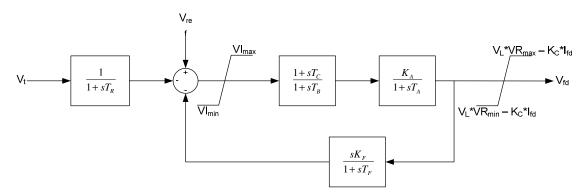

Two closed-loop models were developed to determine the performance of the synchronous generator using the algorithm and the diode bridge rectifier to track the terminal voltage. The two models used are shown in Figure 3.21 and Figure 3.22. The figures show the synchronous generator connected to two loads. Load 2 is connected to the generator through a circuit breaker. Load 1 is of constant loading. The variation in loading is done by opening or closing the circuit breaker. This switches Load 2 in or out. The terminal voltage is sensed by the linear transformers. This transforms the voltage from 20kV down to 400V. This voltage is then fed into the algorithm as well as the diode bridge rectifier. The output from the algorithm as well as from the diode bridge rectifiers are then connected to the input of the exciter model. The exciter model then calculates the appropriate per-unit field voltage. This is then fed into the synchronous generator to allow for automatic voltage regulation. The type of excitation model used is the standard IEEE type ST1 [14]. This is shown in Figure 3.23.

Figure 3.21: Closed-loop model using the algorithm.

Excitation Control on a Synchronous Generator

Figure 3.22: Closed-loop model using the diode bridge rectifier.

Figure 3.23: IEEE Type ST1- potential source control rectifier [14].

The synchronous generator used is that of a South African utility. The actual machine parameters can be seen in Table 3.6, with assumed machine parameters of a standard machine shown in Table 3.7. For the simulations no power system stabilizer is applied to the control system.

| Parameter        | Parameter Definition                          | Unit | Setting |

|------------------|-----------------------------------------------|------|---------|

| S                | Apparent power                                | MVA  | 738.539 |

| Rpm              | Rated speed                                   |      | 3000    |

| kV               | Rated voltage                                 | kV   | 20      |

| $\Delta V$       | Voltage variation                             | %    | ±5      |

| pf               | Power factor                                  | %    | 90      |

| f                | Frequency                                     | Hz   | 50      |

| X <sub>d</sub>   | Synchronous direct-axis (unsaturated)         | %    | 268     |

| X <sub>ds</sub>  | Synchronous direct-axis (saturated)           | %    | 250     |

| X' <sub>d</sub>  | Transient direct-axis (unsaturated)           | %    | 41      |

| X' <sub>ds</sub> | Transient direct-axis (saturated)             | %    | 36      |

| X" <sub>d</sub>  | Sub-transient direct-axis (unsaturated)       | %    | 28.7    |

| X" <sub>ds</sub> | Sub-transient direct-axis (saturated)         | %    | 24.4    |

| Xq               | Synchronous quadratic-axis (unsaturated)      |      | 249     |

| X"q              | Sub-transient quadratic-axis (unsaturated)    |      | 31.3    |

| X" <sub>qs</sub> | Sub-transient quadratic-axis (saturated)      |      | 26.6    |

| X <sub>is</sub>  | Negative phase-sequence reactance (saturated) |      | 25.5    |

| $X_0$            | Zero phase-sequence reactance (unsaturated)   |      | 13.6    |

| X <sub>s</sub>   | Armature leakage reactance                    | %    | 22      |

| T' <sub>do</sub> | Transient open-circuit direct-axis            | Sec. | 6.38    |

| T" <sub>do</sub> | Sub-transient open-circuit direct-axis        | Sec. | 0.048   |

| Ta               | Short-circuit armature time constant          | Sec. | 0.28    |

| T' <sub>d</sub>  | Transient short-circuit direct-axis           | Sec. | 0.98    |

| T" <sub>d</sub>  | Sub-transient short-circuit direct-axis       | Sec. | 0.033   |

| R <sub>s</sub>   | Stator resistance                             |      | 0.00245 |

| Н                | Coefficient of inertia                        |      | 3.2     |

| F                | Friction factor                               | p.u. | 0       |

| р                | Pole pairs                                    | No.  | 1       |

#### Table 3.6: Synchronous machine parameters.

| Parameter        | Parameter Definition                    | Unit | Setting |

|------------------|-----------------------------------------|------|---------|

| X'q              | Transient quadratic-axis (unsaturated)  | %    | 26.2    |

| T'qo             | Transient open-circuit direct-axis      | Sec. | 1.1     |

| T" <sub>qo</sub> | Sub-transient open-circuit direct-axis  | Sec. | 0.081   |

| T' <sub>so</sub> | Transient short-circuit direct-axis     | Sec. | 1.0     |

| T" <sub>so</sub> | Sub-transient short-circuit direct-axis | Sec. | 0.035   |

Table 3.7: Assumed synchronous machine parameters.

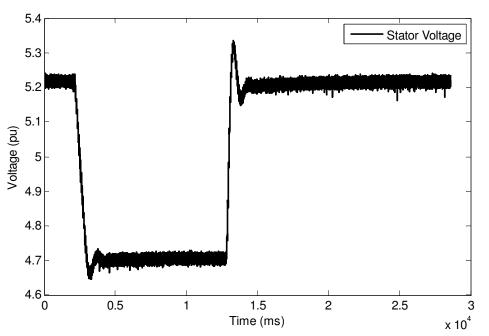

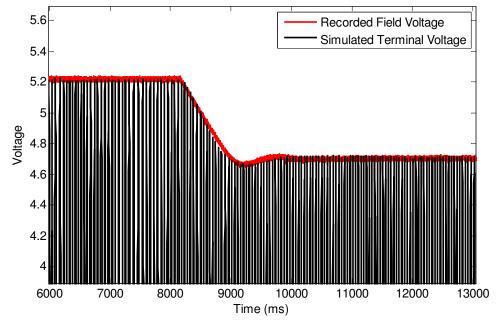

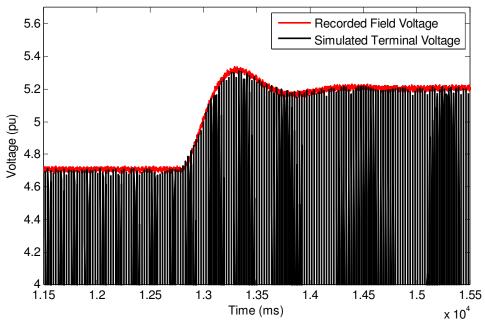

To validate the simulation model, a field measurement recorded during a step-change was used to set up the exciter settings of the simulation model. Using standard settings,  $k_1 = 100$ ,  $k_2 = 10000$  and  $k_3 = 0.02$ , a model was developed to determine the excitation settings such that the response of the simulation model matches that of the field recording. Figure 3.24 shows the recorded stator voltage (5V = Vnominal). A step change of 10% was recorded from 105% to 95% and from 95% to 105%. The results of the simulated step response tests can be seen in Figure 3.25 and Figure 3.26 for upwards and downwards step-changes. The resultant excitation settings for the model can be seen in Table 3.8. These settings were used for all the simulations.

Figure 3.24: Actual stator voltage measured for a 10% step-change in magnitude.

| Parameter                  | Parameter Definition                          |      | Parameter Setting |

|----------------------------|-----------------------------------------------|------|-------------------|

| VR <sub>max</sub>          | Max. value of the regulator output voltage    | p.u. | 6.43              |

| $VR_{min}$                 | Min. value of the regulator output voltage    | p.u. | -6                |

| VI <sub>max</sub>          | Max. internal signal within voltage regulator | p.u. | 10                |

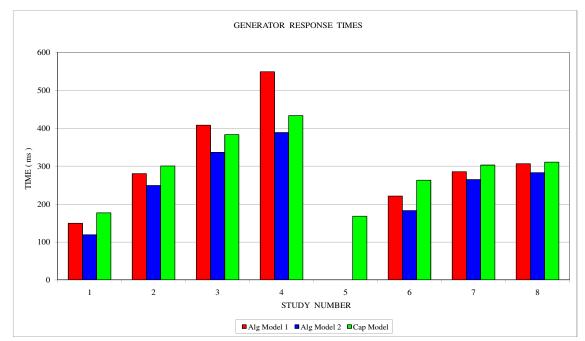

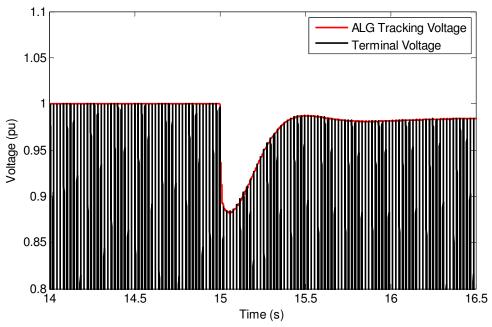

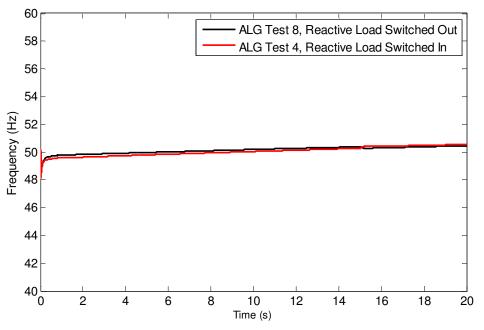

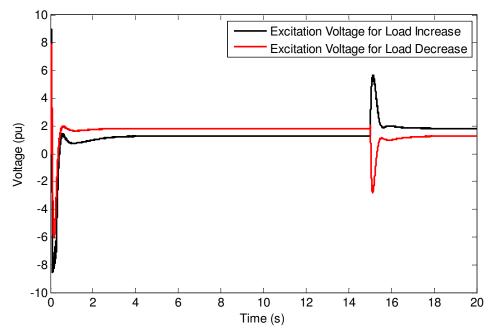

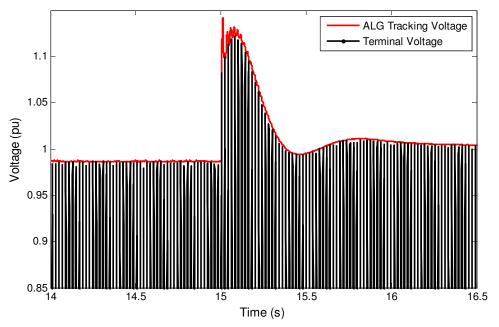

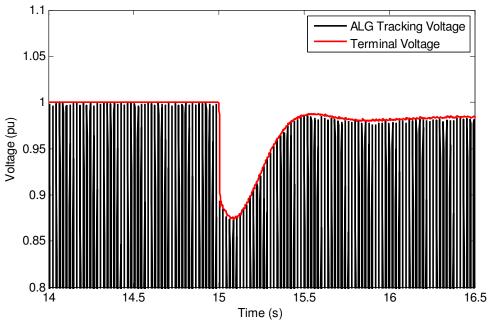

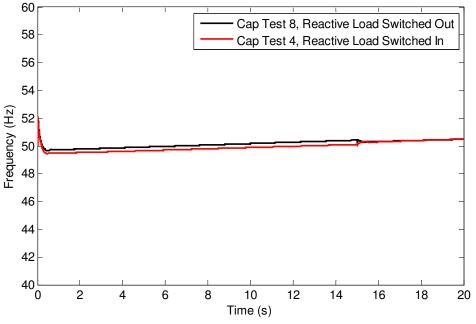

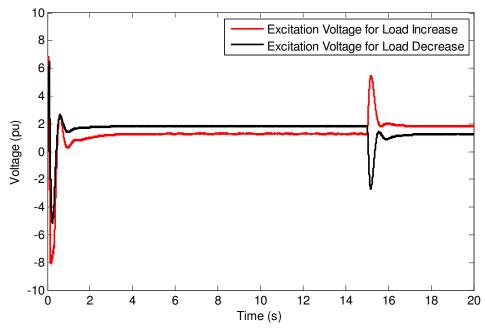

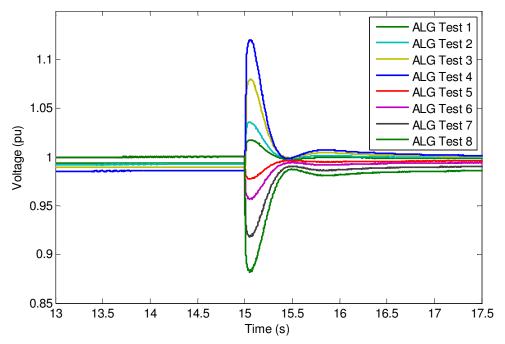

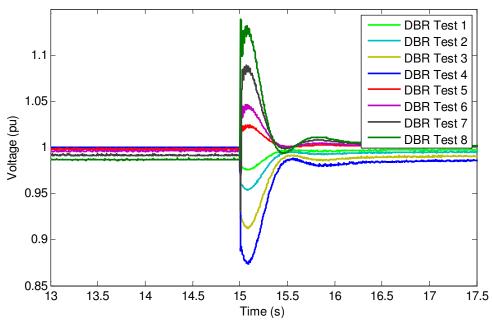

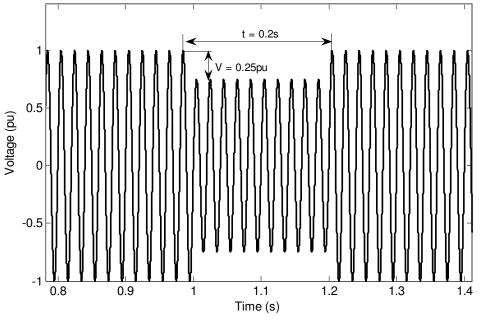

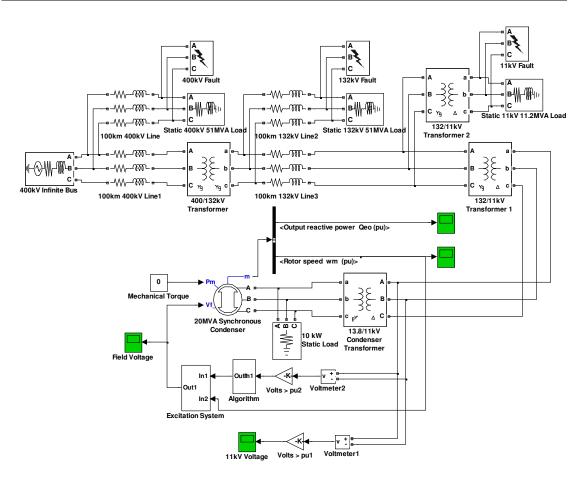

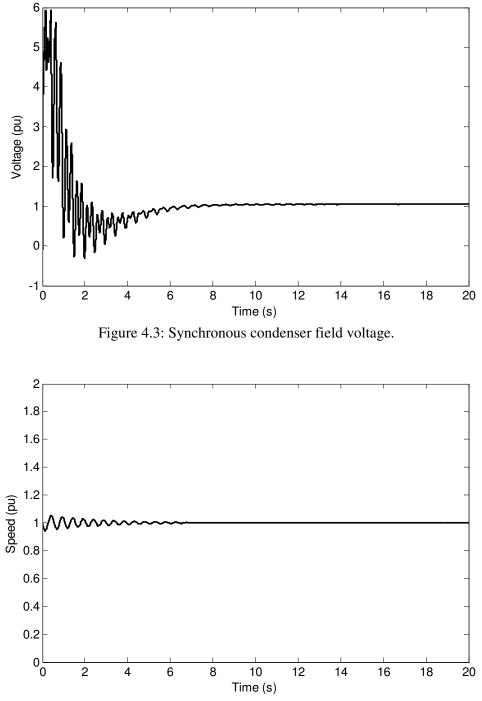

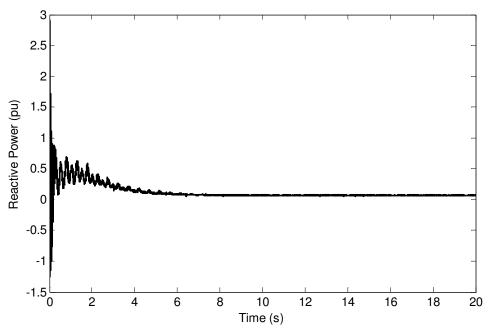

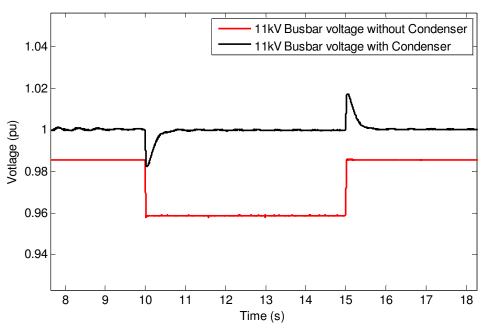

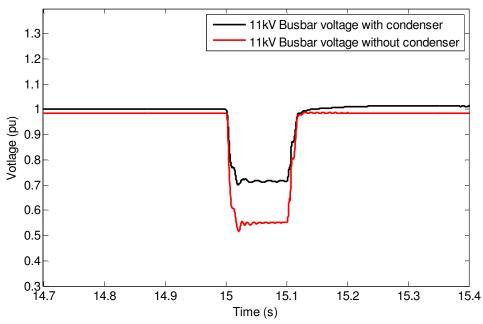

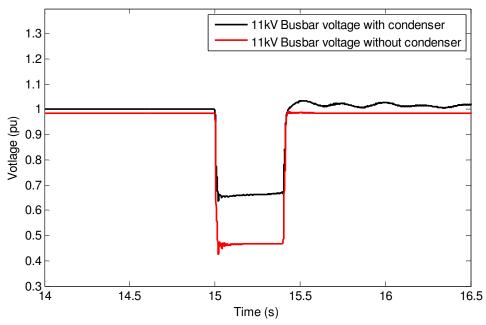

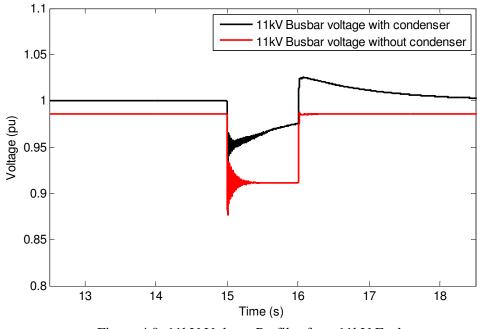

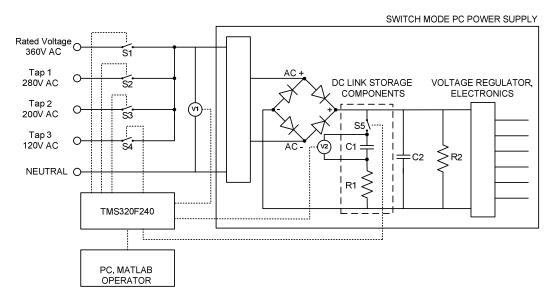

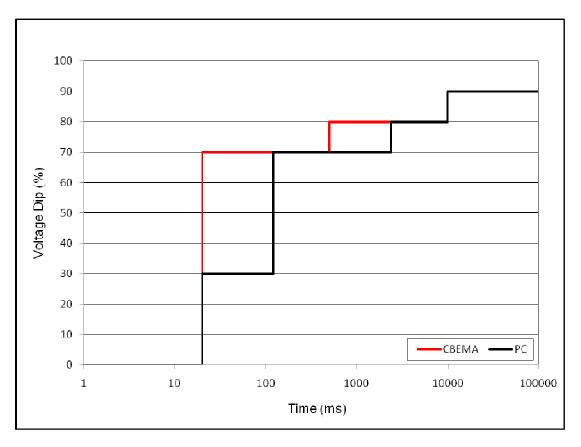

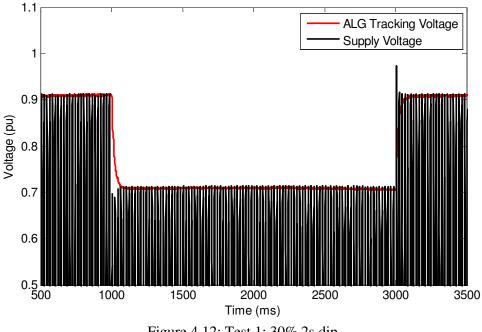

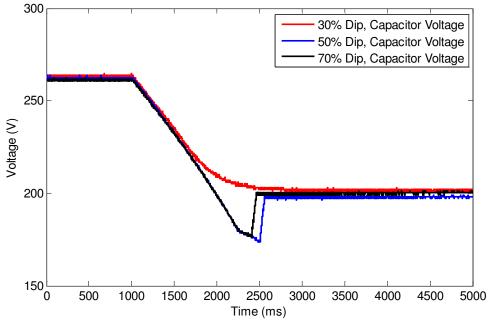

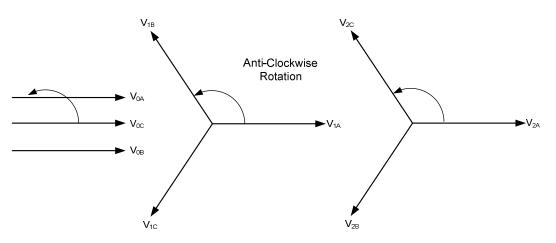

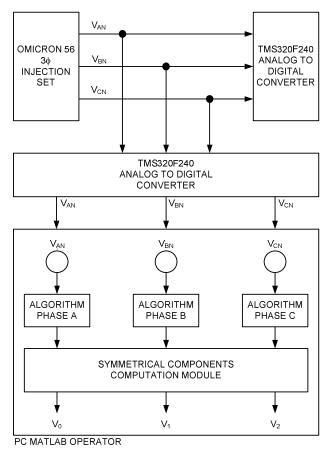

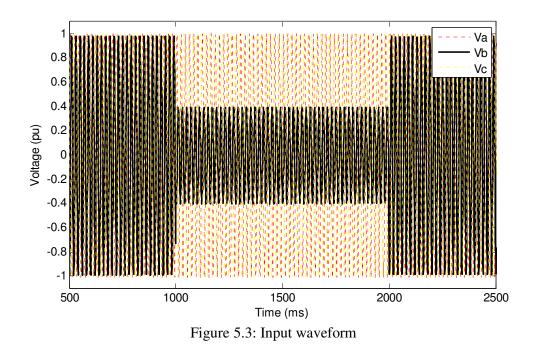

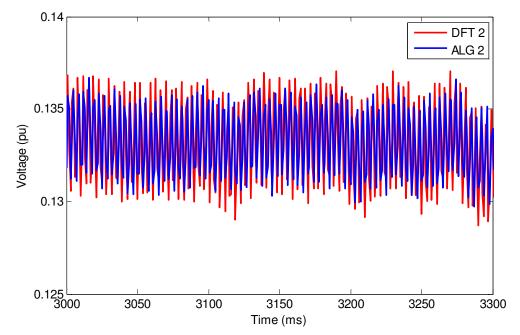

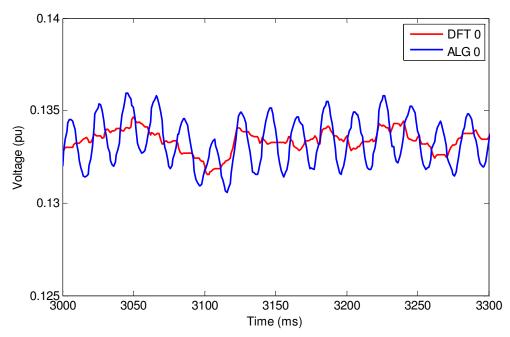

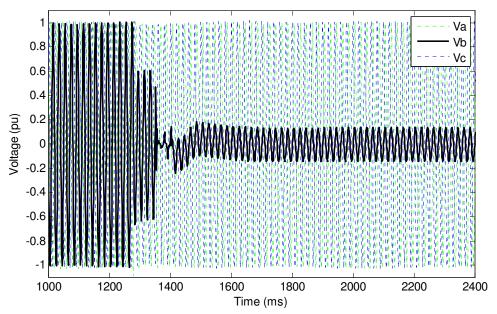

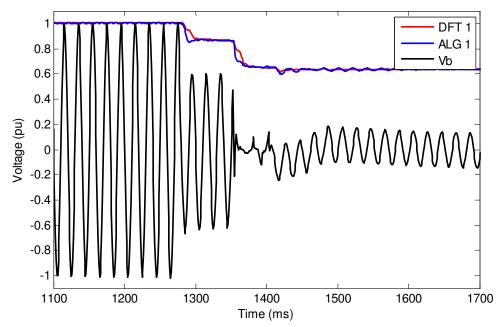

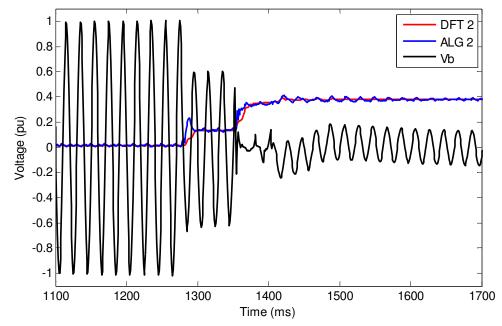

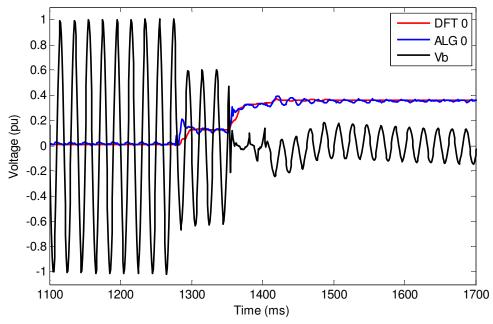

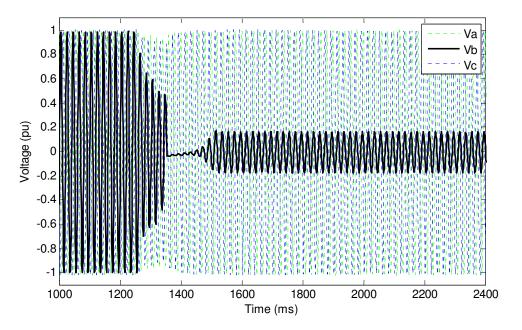

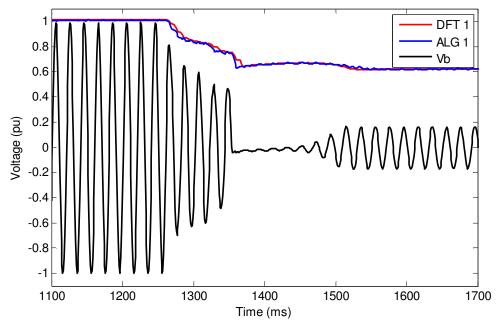

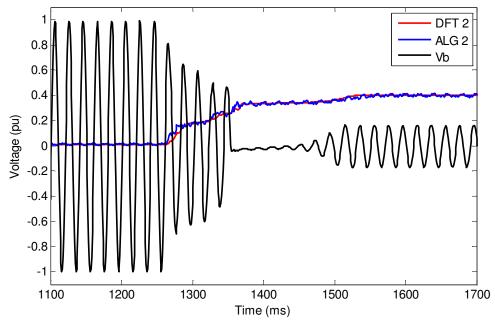

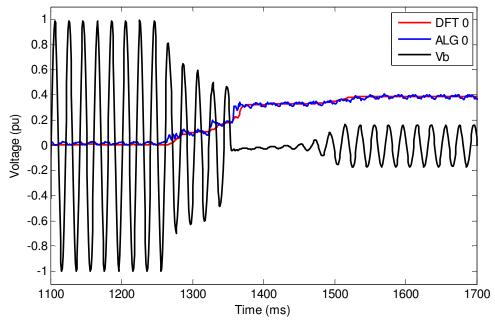

| $VR_{min}$                 | Min. internal signal within voltage regulator | p.u. | -10               |