Department of Computer Science University of Pretoria Pretoria South Africa

# Migrating to a Real-Time Distributed Parallel Simulator Architecture

by

Bernardt Duvenhage

June 18, 2008

Submitted in partial fulfilment of the requirements for the degree Masters of Science (Computer Science) in the Faculty of Engineering, Built Environment and Information Technology

> University of Pretoria Pretoria, South Africa

Superviser:

Professor D. G. Kourie

© University of Pretoria

# Acknowledgements

I would like to thank my supervisor and adviser, Professor Derrick G. Kourie. His support and excellent critical review of my research have brought me much appreciated insight and have certainly improved on the contents of this dissertation.

Many thanks to the my colleagues at the Council for Scientific and Industrial Research (CSIR)—especially Jan Roodt, Cobus Nel and Herman le Roux—with whom I have had many discussions surrounding modelling and simulation, our simulation capability and the various simulators that we have worked on. Herman le Roux is the technical team leader for the Systems Modelling simulation group and I would like to single him out and thank him for what I have learned from him.

The funding provided by the Armaments Corporation of SA (ARM-SCOR), the South-African DoD, the CSIR, the University of Pretoria and the National Research Foundation is very much appreciated. Without their funding the research would not have been possible.

Special thanks goes out to the modelling and simulation community for the work they are all doing and for their gargantuan shoulders that have helped me to reach where I am now.

Finally, I would like to thank my very lovely wife with all my heart for her patience and understanding while I was working long hours to finish off this dissertation. Also to the rest of my family and my friends, I would like you to know that I will be resurfacing in society soon and look forward to seeing you all more often.

# Abstract

The South African National Defence Force (SANDF) currently requires a system of systems simulation capability for supporting the different phases of a Ground Based Air Defence System (GBADS) acquisition program. A non-distributed, fast-as-possible simulator and its architectural predecessors developed by the Council for Scientific and Industrial Research (CSIR) was able to provide the required capability during the *concept and definition* phases of the acquisition life cycle. The non-distributed simulator implements a 100Hz logical time Discrete Time System Specification (DTSS) in support of the existing models. However, real-time simulation execution has become a prioritised requirement to support the development phase of the acquisition life cycle.

This dissertation is about the ongoing migration of *the non-distributed simulator* to a practical simulation architecture that supports the real-time requirement. The simulator simulates a synthetic environment inhabited by interacting GBAD systems and hostile airborne targets.

The non-distributed simulator was parallelised across multiple Commodity Off the Shelf (COTS) PC nodes connected by a commercial Gigabit Ethernet infrastructure. Since model reuse was important for cost effectiveness, it was decided to reuse all the existing models, by retaining their 100Hz logical time DTSSs.

The large scale and event-based High Level Architecture (HLA), an IEEE standard for large-scale distributed simulation interoperability, had been identified as the most suitable distribution and parallelisation technology. However, two categories of risks in directly migrating to the HLA were identified. The choice was made, with motivations, to mitigate the identified risks by developing a specialised custom distributed architecture.

In this dissertation, the custom discrete time, distributed, peer-to-peer, message-passing architecture that has been built by the author in support of the parallelised simulator requirements, is described and analysed. It reports on empirical studies in regard to performance and flexibility. The architecture is shown to be a suitable and cost effective distributed simulator architecture

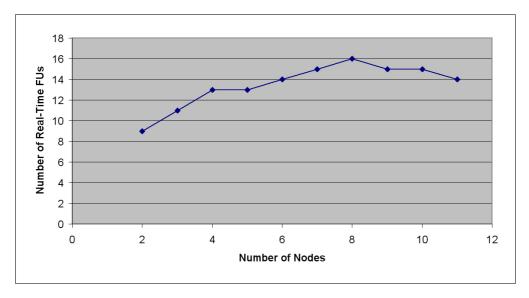

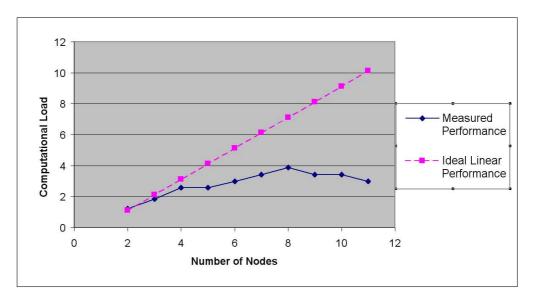

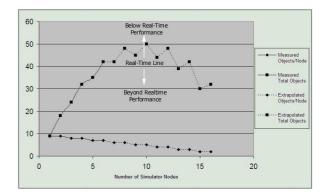

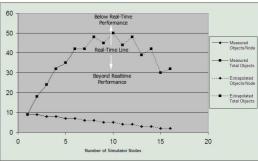

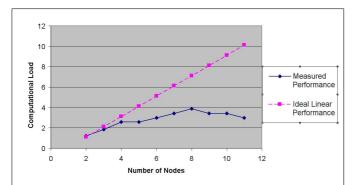

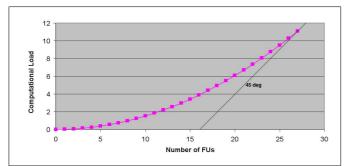

for supporting a speed-up of three to four times through parallelisation of the 100 Hz logical time DTSS. This distributed architecture is currently in use and working as expected, but results in a parallelisation speed-up ceiling irrespective of the number of distributed processors.

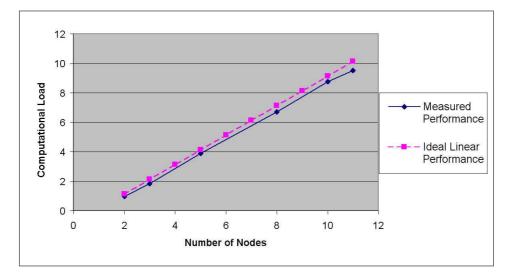

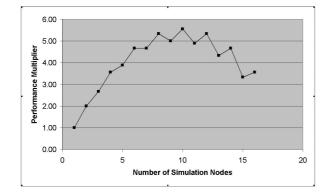

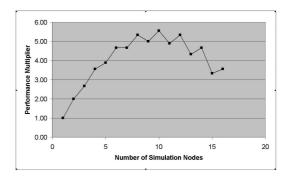

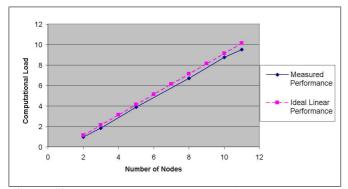

In addition, a hybrid discrete-time/discrete-event modelling approach and simulator is proposed that lowers the distributed communication and time synchronisation overhead—to improve on the scalability of the discrete time simulator—while still economically reusing the existing models. The proposed hybrid architecture was implemented and its real-time performance analysed. The hybrid architecture is found to support a parallelisation speedup that is not bounded, but *linearly related to the number of distributed processors* up to at least the 11 processing nodes available for experimentation.

# Contents

| Ι        | In   | trodu   | ction, Background and Literature                     | 15 |

|----------|------|---------|------------------------------------------------------|----|

| 1        | Intr | oduct   | ion                                                  | 17 |

|          | 1.1  | Backg   | ground                                               | 17 |

|          | 1.2  | Introd  | luction to the Literature                            | 23 |

|          | 1.3  | Resea   | rch Question and Approach                            | 24 |

|          | 1.4  | Disser  | tation Roadmap                                       | 25 |

| <b>2</b> | M&   | zS, Pri | nciples and Practice                                 | 29 |

|          | 2.1  | Levels  | s of System Knowledge and Specification              | 30 |

|          | 2.2  | Frame   | ework for Modelling and Simulation                   | 32 |

|          |      | 2.2.1   | Entities of framework                                | 33 |

|          |      | 2.2.2   | Relationships among entities                         | 36 |

|          |      | 2.2.3   | Model Characterisation, Validation, Verification and |    |

|          |      |         | Qualification                                        | 38 |

|          |      | 2.2.4   | A Taxonomy for Classifying Military Simulation Types | 40 |

|          |      | 2.2.5   | A Simulation Time Management Taxonomy                | 40 |

|          | 2.3  | Model   | lling Formalisms and System Specifications           | 42 |

|          |      | 2.3.1   | General Dynamical Systems                            | 43 |

|          |      | 2.3.2   | The Discrete Time System Specification (DTSS)        | 44 |

|          |      | 2.3.3   | The Discrete Event System Specification (DEVS)       | 45 |

|          |      | 2.3.4   | Interconnection of a DEVS and a DTSS                 | 46 |

|          |      | 2.3.5   | Universality of the DEVS                             | 48 |

|          | 2.4  | Parall  | el and Distributed Simulation                        | 49 |

|          |      | 2.4.1   | DEVS and DTSS Coupled Extensions                     | 50 |

|          |      | 2.4.2   | Distributed Time Management                          | 51 |

|          |      | 2.4.3   | Basic Hardware Infrastructures                       | 54 |

|          |      | 2.4.4   | The High Level Architecture                          | 57 |

|          | 2.5  | In Su   | mmary                                                | 60 |

| 3       | <b>Ris</b><br>3.1<br>3.2<br>3.3<br>3.4 | ks in Migrating to a DEVS<br>Simply Embedding a DTSS within a discrete event architecture<br>Viability of Interoperability Standards                                                                                                                                                                                                                                           | <b>61</b><br>62<br>63<br>63<br>64                          |

|---------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 4       | Usi:<br>4.1<br>4.2                     | ng UML and CSP         Unified Modelling Language         Communicating Sequential Processes         4.2.1         Fundamental Language Constructs         4.2.2         Parallel Operators         4.2.3         Using CSP to Describe Discrete Time and Discrete Event Simulators         In Summary                                                                         | <b>65</b><br>68<br>69<br>71<br>72<br>73                    |

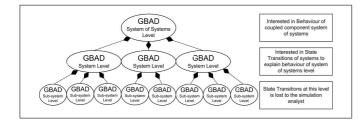

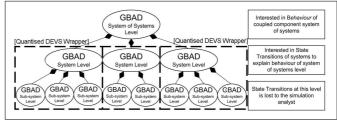

| 5       | <b>Intr</b><br>5.1<br>5.2<br>5.3       | coduction to the GBAD System ModelThe GBAD System of Systems (of Sub-Systems)GBADS Benchmark ScenariosIn Summary                                                                                                                                                                                                                                                               | <b>75</b><br>75<br>81<br>82                                |

| TT      |                                        |                                                                                                                                                                                                                                                                                                                                                                                |                                                            |

| II      | T                                      | he Discrete Time Simulator                                                                                                                                                                                                                                                                                                                                                     | 83                                                         |

| 11<br>6 | T                                      |                                                                                                                                                                                                                                                                                                                                                                                |                                                            |

|         | <b>The</b><br>6.1                      | <ul> <li>The Discrete Time Simulator</li> <li>Discrete Time Simulator</li> <li>Publish-Subscribe Simulation Model</li></ul>                                                                                                                                                                                                                                                    | <b>83</b><br><b>85</b><br>86<br>87<br>90<br>90<br>91<br>91 |

|         | <b>T</b><br><b>The</b><br>6.1          | <ul> <li>The Discrete Time Simulator</li> <li>Discrete Time Simulator</li> <li>Publish-Subscribe Simulation Model</li> <li>6.1.1 The Publish-Subscribe Object Communication Framework</li> <li>6.1.2 The Synthetic Environment Services</li> <li>Peer-to-Peer Message Passing and Node Synchronisation</li> <li>6.2.1 Messaging Implementation of Publish-Subscribe</li> </ul> | <b>83</b><br><b>85</b><br>86<br>87<br>90<br>90<br>91<br>91 |

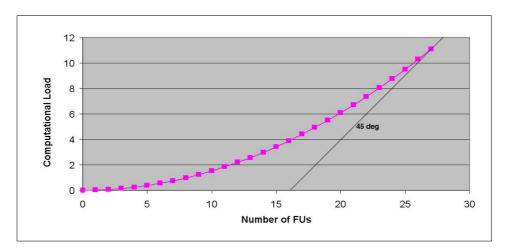

|     | 7.1.4 Initial Peer-to-Peer Scalability Test    | 03 |

|-----|------------------------------------------------|----|

| 7.2 | Benchmark Scenarios, Experiments and Results 1 | 05 |

| 7.3 | Analysis and Preliminary Conclusions           | 09 |

## III Migrating to a Hybrid Discrete-Event/Discrete-Time Modelling Approach and Simulator 111

| 8  | ΑH         | lybrid Modelling Approach                                                                                             | 113   |

|----|------------|-----------------------------------------------------------------------------------------------------------------------|-------|

|    | 8.1        | Aggregation of Sub-System Models                                                                                      | . 114 |

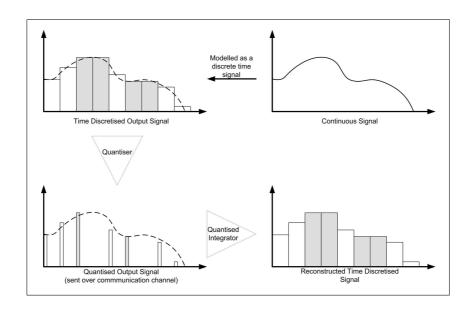

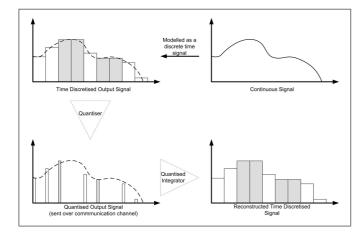

|    | 8.2        | Output Quantisers and Quantised Integrators                                                                           | . 117 |

|    |            | 8.2.1 Output Quantiser and Quantised Integrator Pairs                                                                 | . 117 |

|    |            | 8.2.2 Dead-Reckoning                                                                                                  | . 118 |

|    |            | 8.2.3 Implications of Quantisation                                                                                    | . 119 |

|    | 8.3        | Efficient Discrete Event Time Management                                                                              |       |

|    | 8.4        | Implementation for Running the Benchmark Scenarios                                                                    |       |

|    | 8.5        | In Summary                                                                                                            |       |

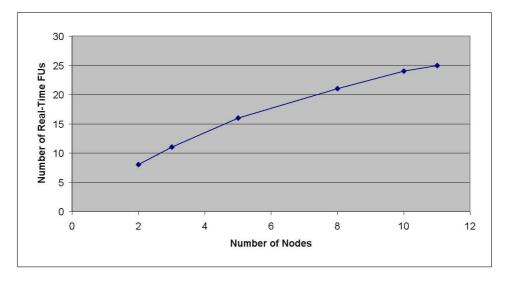

| 9  | 9.1<br>9.2 | Orid Simulator Analysis and Results         Benchmark Experiment Results         Analysis and Preliminary Conclusions |       |

| I۷ | 7 (        | Conclusion, Future Work and Final Remarks                                                                             | 129   |

| 10 | Con        | clusion                                                                                                               | 131   |

| 11 | Fut        | ure Work                                                                                                              | 137   |

| 12 | Diss       | sertation Self Evaluation                                                                                             | 141   |

# Glossary: List of Abbreviations and Definitions

Below is a list of abbreviations and often used definitions. It is intended to serve as a quick reference list.

- AFAP (As-Fast-As-Possible)

- C4I (Command, Control, Communications, Computers, Intelligence)

- COTS (Commodity Off The Shelf)

- CSIR (Council for Scientific and Industrial Research)

- CSP (Communicating Sequential Processes)

- Dead-reckoning Also referred to as *active quantisation*. Usually applied in the quantisation of the position, velocity, etc. of a body of mass under *forced* motion.

- DEDS (Discrete Event Dynamical System)

- DESS (Differential Equation System Specification)

- DEVS (Discrete Event System Specification)

- DIS (Distributed Interactive Simulation )

- DPSS (Defence, Peace, Safety and Security)

- DTSS (Discrete Time System Specification)

- Dynamical System The dynamical system concept is a mathematical formalization for any fixed rule which describes the time dependence of a point's (could be a real number) position in its ambient space. Examples include the mathematical models that describes the swinging of a clock pendulum, the flow of water in a pipe, and the number of fish that may be found each spring in a lake.

- Experimental Frame A specification of the conditions—due to the modelling objectives and outcome measures—under which the system is observed or experimented with. See Section 2.2.

- FOM (Federation Object Model)

- FU (Fire Unit)

- GBAD(S) (Ground Based Air Defence (System))

- Hybrid simulator/modelling-approach In this dissertation the meaning of hybrid with regards to a simulator or modelling approach implies that the simulator applies a mixture of discrete time and discrete event concepts. Hybrid *does not* refer to—as is sometimes the case—a simulator or modelling approach that integrates discrete and continuous models.

- HIL (Hardware In the Loop)

- HLA (High Level Architecture)

- IEEE (Institute for Electrical and Electronic Engineers)

- LOS (Line Of Sight)

- MCM (Mathematical and Computational Modelling Research Group of the CSIR)

- Model An executable specification of a system at a certain specification or knowledge level, within a certain experimental reference frame and to a certain degree of validaty. Discussed in Chapter 2.

- M&S (Modelling and Simulation)

- Object An instance of a model or component of a model. Sometimes referred to as the simulator if only one model is involved in the simulation.

- OEM (Original Equipment Manufacturer)

- OIL (Operator In the Loop)

- PADS (Parallel and Distributed Simulation)

- Parallelisation Speed-Up, S.

- $S(p) = \frac{Execution \ time \ using \ single \ processor \ system}{Execution \ time \ using \ a \ multiprocessor \ with \ p \ processors}$

- PDES (Parallel Discrete Event Simulation)

- Platform Has two meanings: Firstly, a *computing platform* or a *processing platform* generally refers to a computing machine or PC. Secondly, platform refers to a stationary or moving object in the synthetic environment which might carry a sensor, weapon or other item of interest.

- Relation connection between things: a meaningful connection or association between two or more things, e.g. one based on the similarity or relevance of one thing to another [Encarta World English Dictionary, North American Edition].

- SANDF (South African National Defence Force)

- Scenario In the case of the GBADS simulation, a scenario is a collection of interacting ground based air defence systems—composed of sub-systems—deployed in such a way within the environment as to defend against an expected threat scenario. A threat scenario may be a collection of incoming airborne targets such as aircraft and missiles.

- SDK (Software Development Kit)

- Scalability maximum attainable parallelisation speed-up, S, given an infinite supply of nodes.

- Simulation The combined input traces, output traces and object state transitions of the simulator during an execution run.

- Simulation Frame Similar to the image frame in a cartoon strip, a simulation frame is a snapshot of the simulation and the state of its simulator at a specific instance in time. Also sometimes referred to as just a *frame*

- Simulation Time The synthetic environment has its own notion of time i.e. the simulation time according to which the virtual inhabitants play out the action. The simulation time need not progress at the same second-to-second pace as real-time and may for example be paused or restarted as required.

- Simulator A computing system that executes the executable specification of each model instance and couples the instances' input ports to output ports

- SOM (Simulation Object Model)

- TCP/IP (Transport Control Protocol/Internet Protocol)

- Time Frame Same as *Simulation Frame*

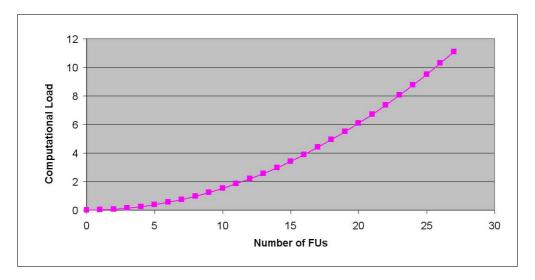

- Time Complexity The number of steps that it takes to solve an instance of a problem as a function of the size of the problem. Model time complexity refers to the number of computational steps to update by one unit the internal time of a model instance of size n—size possibly measured by the number of interacting sub-systems

- UML (Unified Modelling Language)

- VGD (Virtual GBADS Demonstrator)

# Part I

# Introduction, Background and Literature

# Chapter 1

# Introduction

The introduction to this dissertation provides an overview of the dissertation topic, the technology involved and the applicable literature for the development of a new distributed parallel battlefield simulator. The literature includes recent work on the need for modelling and simulation within the South African National Defence Force (SANDF). The discussion of the topic background identifies certain problems in the development of the simulator and the hypothesised solution is then formulated as a research question. The dissertation road map is finally presented.

## 1.1 Background

The Oxford English Dictionary (1989) describes simulation as "The technique of imitating the behaviour of some situation or system (economic, mechanical, etc.) by means of an analogous model, situation, or apparatus, either to gain information more conveniently or to train personnel".

The SANDF requires decision support and tactical doctrine development during the different phases of their Ground-Based Air Defence System (GBADS) acquisition program to gain information more conveniently. According to Pretorius[1], Baird and Nel[2] this need offered an opportunity to establish an indigenous and credible Modelling and Simulation Support capability within the South African Defence Acquisition environment. The broad requirement of the capability is to simulate a GBADS battery of existing and still to be acquired (possibly still under development) equipment and their related human operators at a system of systems level. A pilot systems simulation capability, provided by the Mathematical and Computational Modelling (MCM) research group of the CSIR's Defence Peace Safety and Security (DPSS) operating unit, was established during 1998 to 2003 in

### CHAPTER 1. INTRODUCTION

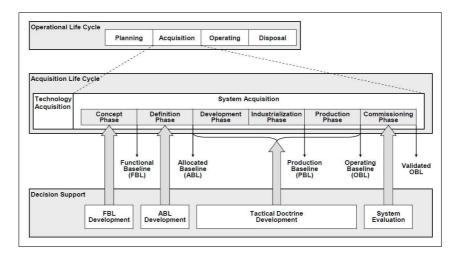

Figure 1.1: The System Life Cycle[3]

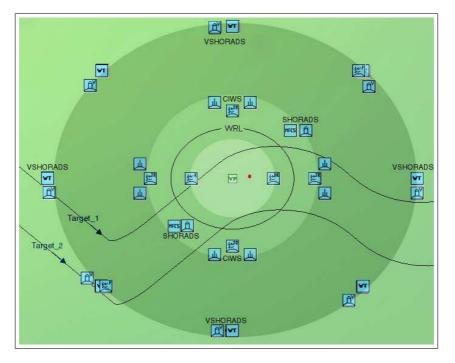

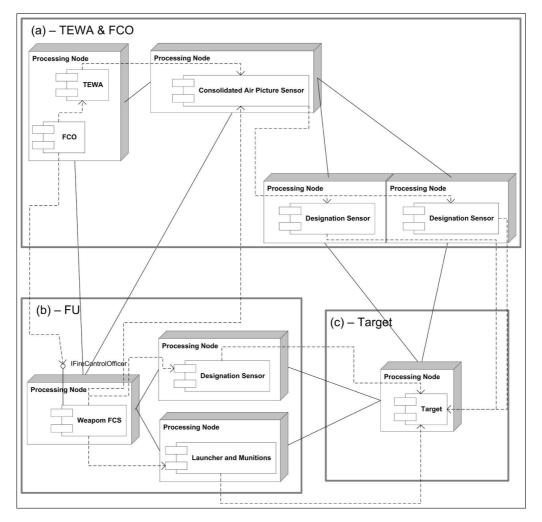

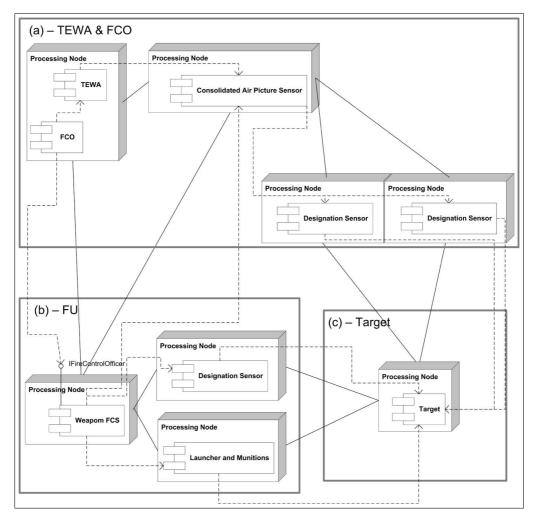

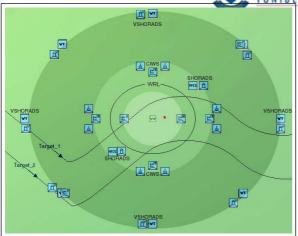

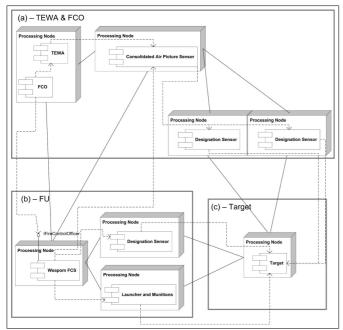

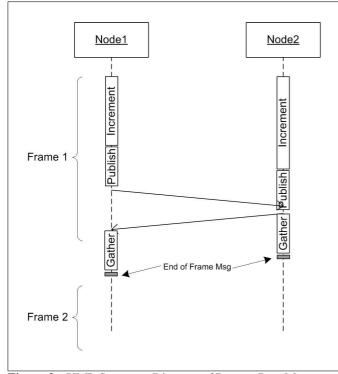

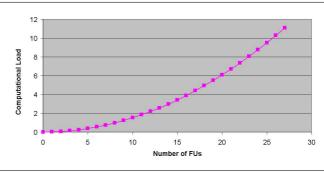

support of the concept and definition phases of the acquisition life cycle [3], which is part of the system life cycle shown in Figure 1.1. During this time the family of simulator architectures discussed by le Roux[4], also known as the Virtual GBADS Demonstrator (VGD), providing the systems simulation capability evolved as the value of modelling and simulation became better understood and as the project requirements also evolved. A GBADS deployment, such as shown in the map view scenario planning tool in Figure 1.2, consists of a layered air defence. The outer layer typically consists of eight very short range missile systems, each having a virtual operator and an accompanying buddy with a wide angle pair of binoculars. The second layer has four gun systems, each consisting of two guns, a tracking radar, a designation radar, a fire control system and at least three operators to operate the guns. The inner layer of defence usually has two short range missile systems, each consisting of a ground based launcher, a designation sensor, a fire control system and a few virtual operators. The deployment defends some Vulnerable Point (VP) against an airborne threat scenario—the GBAD system is discussed in more detail in Chapter 5. A selection of the models was derived from high fidelity engineering models, some developed by OEMs, that were based on direct numerical method solutions. The models were then developed further within a 100Hz logical Discrete Time System Specification (DTSS) that simplified the time and causality management.

The 2003 version of the architecture had its roots set in the High Level Architecture (HLA), an IEEE standard for large scale distributed simulation interoperability, but finally settled on a single process DTSS simulator architecture with a TCP message passing interface to the outside world. The

### 1.1. BACKGROUND

Figure 1.2: A Typical GBADS Deployment

tightly integrated single process architecture is, in a way, the HLA's archnemesis, but the history leading up to its adoption is explained below.

The HLA is introduced in the book by Kuhl et al.[5]. It is a software architecture and development process for creating distributed computer simulations out of component objects or other simulations, while ensuring component reuse and simulation interoperability of HLA compliant simulations as defined in the IEEE standard 1516[6][7]. In the late 1990s, the United States (US) Department of Defence (DoD) developed the HLA and mandated its use for all of its modelling and simulation activities. According to Page and Smith[8], the idea of interconnecting distributed simulation began to take shape in the mid 1970s and Straßburger[9] states that from a corporate perspective the demand for the HLA is a very clear business case in minimising duplication of effort and reducing expenditure. The design goals of the HLA standard are that resulting systems should have the following characteristics:

- 1. it should be possible to decompose a large simulation into smaller parts that are easier to define, build correctly and verify,

- 2. it should be possible to combine the resulting smaller simulations into a larger simulation system,

### CHAPTER 1. INTRODUCTION

- 3. it should be possible to combine the smaller simulations with other, perhaps unanticipated simulations to form a new simulation system,

- 4. those components that are generic to component-based simulation systems should be separable from specific simulations and reusable from one simulation system to the next, and

- 5. the interfaces between the simulations and the generic infrastructure should insulate the simulations from the changes in the technology used to implement the infrastructure, and insulate the infrastructure from technology in the simulations.

The key characteristics of the HLA are:

- 1. the HLA is a layered architecture, each layer providing services to the layer above it and serving as a client to the layer below it,

- 2. the HLA is a data abstraction architecture, where the architecture's infrastructure is unaffected by the changes in the simulation and *vice* versa, and

- 3. the HLA is an event based architecture, where a simulation component broadcasts one or more events, which other interested simulation components may associate with a procedure or function to execute on receiving the message.

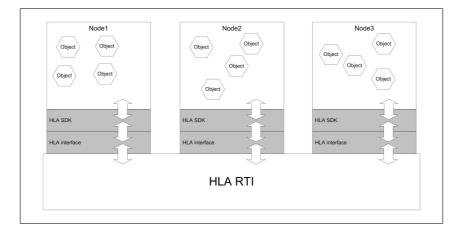

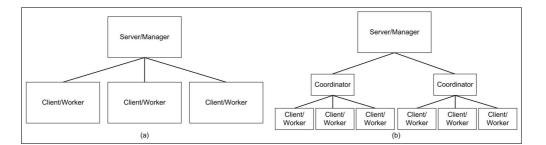

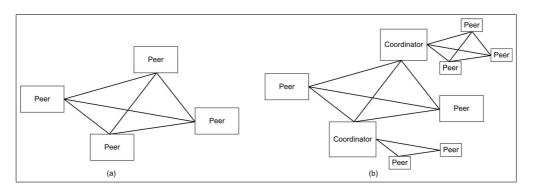

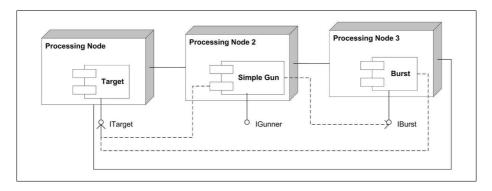

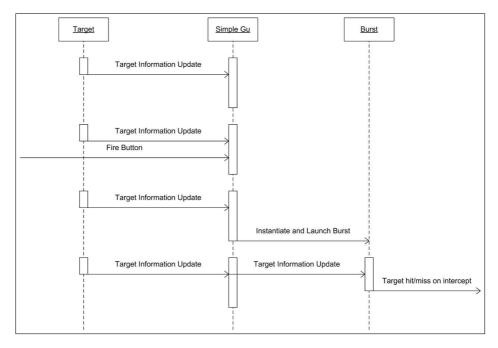

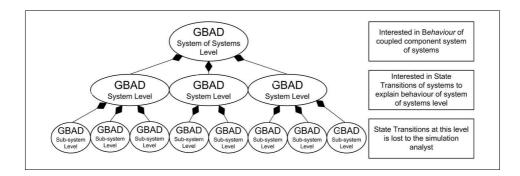

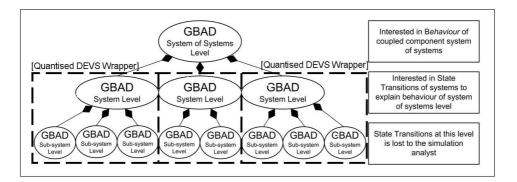

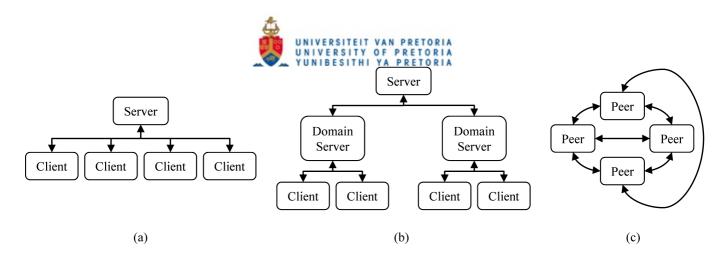

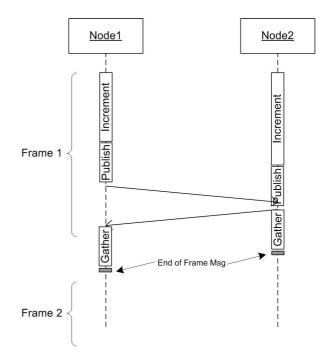

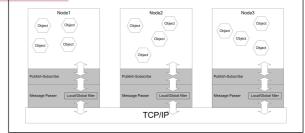

As mentioned, one of the earlier simulation architectures that was in use in 2002 did implement a logical time DTSS simulator within the HLA. This was done to help promote the HLA in South-Africa and get in line with international trends in the military modelling and simulation community in terms of simulation interoperability. This architecture, shown in Figure 1.3, supported distributed parallel small-scale real-time and as-fast-as-possible simulation using an in-house HLA SDK. As a capability demonstration, the architecture was integrated with a commercial flight simulator to provide realistic reactive human behaviour to the simulation. During the definition phase of the acquisition life cycle (around the beginning of 2003), accurate time-line analysis and Monte-Carlo experiments became increasingly important while supporting real-time execution, as the simulation capability evolved, lowered in priority. The unfortunate lack of a near-future integration requirement with other local simulators and the fact that pre-recorded repeatable flight profiles, requiring no run-time human interaction, had to be used for the Monte-Carlo type batch experiments, also made supporting the HLA for current and new models an unnecessary expense.

### 1.1. BACKGROUND

Figure 1.3: The High Level Architecture

To meet project time-line constraints, the statistical analysis results of the simulation runs had to be available for analysis in a timely fashion. This meant doing the batch runs of simulations in as an efficient manner as possible. It was proposed that the simulation be stripped of the HLA interface and HLA SDK code in an effort to remove from the architecture the overhead associated with the unused features and services of the HLA. This allows an undistributed simulator to, for example, execute one simulation job in a much shorter time than it would take an eight-machine-cluster to execute eight distributed (each job decomposed across all machines) jobs. Eight nondistributed simulators is therefore more efficient in executing many batch jobs—also referred to as *replicated trials*[10]—than an eight-machine-cluster spending all resources on one job at a time.

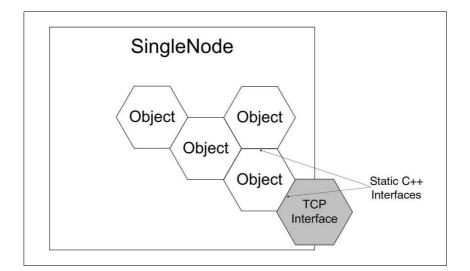

The resulting architecture, shown in Figure 1.4, employed a simple nondistributed *logical and conservative* (as opposed to *real-time and optimistic*, described further in Chapter 2) discrete time management scheme within a single process to interface the simulation objects directly with each other through their C++ interfaces. A TCP message passing interface served as the communication mechanism to an external 2D viewer and a human behavioural component.

In the beginning of 2004, entering the development phase of the acquisition life cycle, renewed interest in real-time simulation execution developed. This was due to a growing realisation of the positive impact of *realistic* human-simulation interaction when doing tactical doctrine development. Human interaction became a prioritised requirement and was to happen through an Operator In the Loop (OIL) console. The possibility of then recording the operator's actions to be re-used in statistical simulation runs when and as re-

Figure 1.4: Tightly Integrated Non-Distributed Architecture

quired also existed. Within the MCM development team, the author had the responsibility of developing and implementing the distributed parallel simulator that is currently in use and capable of distributing the computational load across multiple PC's. The simulator is capable of reaching at least soft real-time performance through parallel execution. Reusing as many components as possible, including the C++ models and their 100Hz logical discrete time management, from the previous simulation was a necessity for cost effectivity. An important related requirement that impacted the hardware infrastructure supporting the simulator architecture was that the simulator must be transportable to field deployments. This requirement necessitated a dedicated infrastructure and the cost implications of new hardware limited the technologies that may be employed in the construction of the hardware infrastructure.

The design goals and required characteristics of the new discrete time simulator architecture were very similar to those mentioned above in relation to the HLA. Given this similarity and the international trends in distributed military simulator architectures, the HLA was identified as the ideal candidate for the distributed simulation capability. The HLA is, however, a discrete event architecture which promotes the use of Discrete Event System Specification (DEVS) modelling formalisms for efficient execution. From experience in applying the HLA and from documented case studies and other literature on embedding a DTSS within an interoperability standard, some technical and economic viability risks were identified in directly migrating to the HLA. The risks are discussed in Chapter 3. An alternative architecture

### 1.2. INTRODUCTION TO THE LITERATURE

which would mitigate the migration risks had to be found. Even though the new architecture was not to be HLA, it nevertheless had to be a flexible, distributed, parallel simulator architecture.

## **1.2** Introduction to the Literature

Considerable work is currently being done on the need for modelling and simulation within the SANDF's GBADS and Joint Air Defence System (JADS) domain. Research feedback is being presented to, among others, the South African Joint Air Defence Symposium (SAJADS)[11], the European[4] and Fall[3][12] Simulation Interoperability Workshops(SIWs), and the European Air Defence Symposiums[13][2]. The article by Roodt et al.[14] looks forward past GBAD and JADS—to what a system-of-systems simulation architecture for command & control at the joint operations level should look like.

However, to develop, instantiate and further research the simulation capability to address these needs and even just to form a shared vision of, and communicate about the required capability, necessitates the study of a set of core disciplines.

The theory of modelling and simulation is the first of the set of core disciplines and is discussed by Zeigler et al. [15] in an authoritive textbook style. Systems theory is introduced as the mathematical formalism for specifying and understanding dynamical systems. System specification formalisms, of which the DEVS modelling formalism and the DTSS modelling formalism are two, are discussed in great detail by Zeigler et al. A summary of the applicable literature, theory, and principles and practice of modelling and simulation may be found in Chapter 2. A framework for modelling and simulation is discussed and shown to contain a source system, an experimental frame, a system model and a simulator. Modelling formalisms are then used to specify the different classes of system models. The simulator's architecture is dependent on the above mentioned aspects, but also on the target computational infrastructure. Section 2.4 discusses distributed simulation and the basic hardware infrastructures. The modelling formalism and time management approach most suitable to efficient distributed simulation is identified to be the DEVS modelling formalism and optimistic time management. Chapter 16 of Zeigler et al. provides a very good and comprehensive finale on the "DEVS Representation of Systems".

Kuhl et al.'s book [5] provides a simulation builders view of the HLA and Chapter 2 concludes by elaborating on the brief introduction to the HLA given earlier. The referenced suite of IEEE 1516 standards that further detail the HLA and some recommended practices in its use may be found in

[6].

Chapter 3 exposes the reader to:

- The MCM group's previous experience with the HLA,

- case studies on the use of the HLA and similar architectures in high resolution and logical discrete time management applications,

- a PhD (published as a book) by Straßburger on advances in simulation, and

- an article by Taylor et al.[16] on the potentials and pitfalls of distributed simulation.

Two categories of risks in migrating to a standardised discrete event interoperability architecture such as HLA, namely technical and economic viability, are then derived from these sources and the implications discussed.

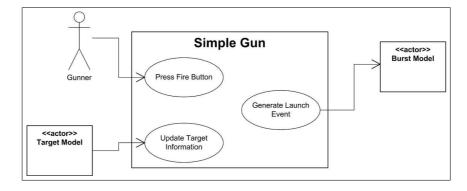

The notations that are used to further describe and present the system specifications, their simulators and the proposed architectures are Communicating Sequential Processes (CSP), presented by Roscoe in [17], and the Unified Modelling Language (UML), presented in [18]. Chapter 4 discusses CSP and UML for use in the description and visual representation of the system specifications and simulator architectures.

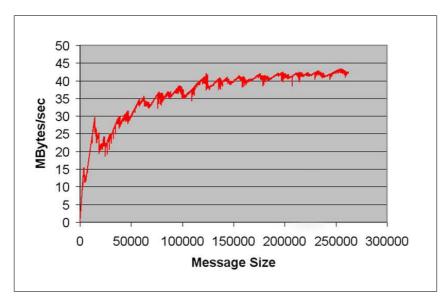

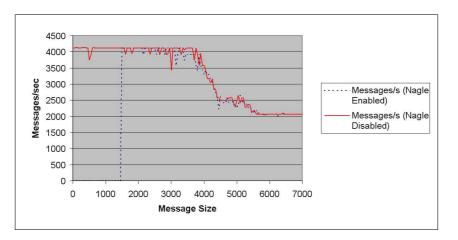

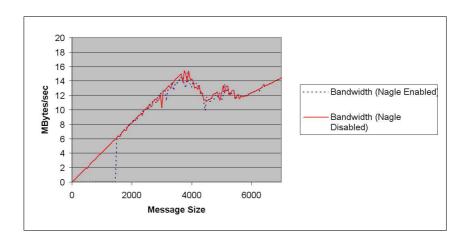

Within the above mentioned literature chapters, in particular Chapter 3, a gap is shown to exists between a single process high resolution DTSS simulator and a large scale parallelisation of the high resolution logical time DTSS. A DEVS is desirable for its documented advantages in building an efficient distributed simulator. A DTSS simply embedded within a discrete event interoperability architecture is however shown to be possible, but not efficient because the high resolution logical discrete time system has a high communication overhead between distributed nodes. The HLA and DIS are shown from case studies to hit a discrete time simulator frame rate ceiling of 25Hz-30Hz. Part II discusses the discrete time simulator that is currently in use to *fill the gap* in distributively parallelising the 100Hz logical time simulation.

## 1.3 Research Question and Approach

This chapter has thus far provided the background to the required simulation capability and briefly made reference to the applicable literature and the motivations behind the current custom discrete time simulator. This simulator, discussed fully in Part II of the dissertation, is in use and working as expected.

### 1.4. DISSERTATION ROADMAP

However, the limits in the architecture's continued and future use needed to be determined, specifically in terms of scalability. From the HLA and DIS case studies mentioned in Chapter 3 it is expected that the high simulation frame rate is a major scalability limiting factor. This is thought to be mostly due to the sequential nature of the inter-node communication channels. In response to these research issues the scalability limits of the existing discrete time simulator is experimentally analysed and the results discussed in Part II of the dissertation.

A further research question is whether the simulator's scalability can be improved by somehow following a different modelling approach instead of the current discrete time approach? And, if so, can this be done with the same model reuse economies as was required from the discrete time simulator?

Mention has been made of the large scale and event-based HLA interoperability standard and of the success of the DEVS modelling approach. An investigation has been carried out into whether a DEVS modelling approach may somehow be married to the current discrete time simulator to improve its scalability. A hybrid discrete-event/discrete-time simulator is therefore proposed, discussed and its performance analysed in Part III of the dissertation.

To summarise, this dissertation will follow a research approach of:

- Doing the relevant background study and, in doing so, describing the current distributed parallel simulator within the newly explored—but well known within the international military simulation community—body of knowledge,

- experimenting with, and analysing the current discrete time simulator,

- proposing and implementing a hybrid discrete-event/discrete-time simulator, and

- experimenting with, and analysing the proposed architecture, leading to various conclusions and future work proposals.

### 1.4 Dissertation Roadmap

The starting point for this dissertation is a requirement for a simulation capability within an air-defence context. The dissertation discusses the appropriate literature and the analysis of the requirements, design and implementation of the simulation architecture to support the capability as described.

The dissertation is laid out in three parts and a conclusion as follows:

### CHAPTER 1. INTRODUCTION

Part 1: Introduction, Background and Literature. Readers that have read the introduction and are familiar with the mentioned core disciplines and the SANDF GBADS domain may skip the remaining chapters of this part.

- The introduction to this dissertation has thus far provided an overview of the dissertation topic, the technology involved and the applicable literature. A gap is shown to exists between a single process high resolution DTSS simulator and a large scale parallelisation of the similator. An allusion is made to the specialised discrete time simulator that is currently implemented and discussed later in Part II. The future scalability of the discrete time simulator is under question in this dissertation and the hypothesised scalability *solution* is formulated as a research question.

- Chapter 2 gives an introduction to the principles and practice of modelling and simulation. An understanding of the theory, relevant concepts and a common M&S framework is required to generate a shared vision of the simulation capability between the parties involved such as system engineers, users and developers. Setting the description of the current discrete time simulator within a commonly known and used framework also allows and is absolutely necessary for applying existing theorems and corollaries in further research. The chapter leads up to and then does a proper introduction of the DTSS, the DEVS and, of importance for this dissertation, the advantages, in terms of the simulator, of using the DEVS modelling formalism for the specification of the system to be simulated. Basic distributed hardware infrastructures and the HLA are also discussed in more detail.

- Chapter 3 researches the risks involved in migrating from a specialised discrete time simulator to a DEVS and discrete event simulator. Once the migration risks are understood, an educated decision may be made on the way forward in migrating to a discrete event simulator.

- Chapter 4 gives an introduction to the notations used to formally describe and visually present the simulator processes. This is given to the level required for the analysis, design and implementation of the respective simulator architectures.

- Chapter 5 returns the focus to the GBAD domain. The intention is to now build a clear picture of the GBAD system of systems (of subsystems) such that the simulator may be properly analysed in terms of the system model scale. Representative scenarios are identified for use in

### 1.4. DISSERTATION ROADMAP

analysing the performance of both the current discrete time simulator and the proposed hybrid DEVS/DTTS simulator.

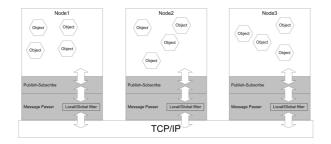

Part 2: The Current Discrete Time Simulator

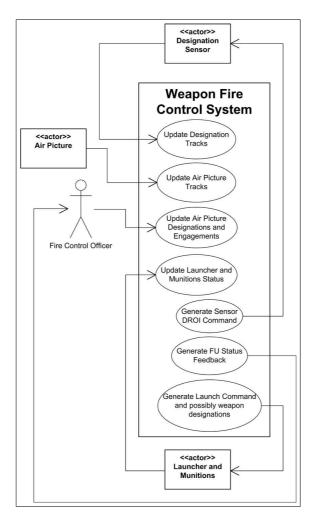

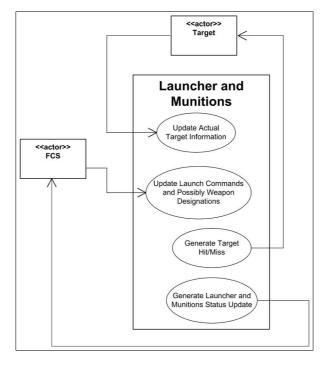

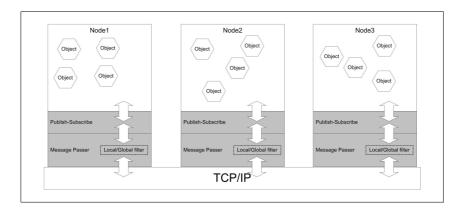

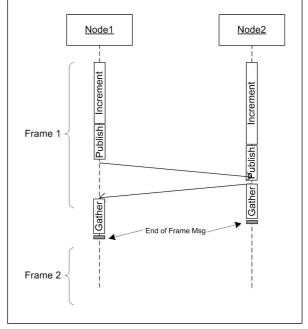

- Chapter 6 describes the layered simulator architecture. The publishsubscribe simulation model, the Synthetic Environment within which the model instances interact with each other and the lower level messaging are described. The GBADS simulation object model within which the GBADS simulation is implemented is then described.

- Chapter 7 analyses the simulation model and discrete time architecture performance results.

Part 3: Migrating to a Hybrid Discrete-Event/Discrete-Time Modelling Approach and Simulator

- Chapter 8 looks at applying a hybrid discrete-event/discrete-time modelling approach to increase the scalability of the simulator.

- Chapter 9 analyses the new hybrid modelling approach and simulator, and then presents the comparative performance results.

This dissertation thus, from existing research, builds up to a detailed description of the design and implementation of a new discrete event simulator and then subsequently finds resolution in the critique of the architecture as improving on the scalability of the current discrete time simulator. Chapters 10 and 11 respectively provide the conclusion to the dissertation and discuss the planned and potential future work. Chapter 12 contains a self examination of the dissertation.

# Chapter 2

# Modelling and Simulation, Principles and Practice

This chapter gives an introduction to modelling and simulation as an understanding of the theory, relevant concepts and technology involved is required to properly understand, specify and implement a simulation capability. As mentioned in the introduction, setting the description of the current simulator architecture within a commonly known and used framework also allows and is absolutely necessary for applying existing theorems and corollaries in doing further research.

The book by Zeigler et al. [15] introduces key concepts that underlie the theory, principles and practice of modelling and simulation. Although there are many references to most of these concepts in the literature, [19, 20, 21, 22, 23, 24, 10, 25] among others, the book by Zeigler, et al. is used as the authorative textbook reference and often referred to as only *Zeigler*, *et al.* in this dissertation. The most basic concept is that of mathematical systems theory. The theory provides a fundamental, rigorous mathematical formalism for representing dynamical systems. Only once it is understood how these dynamical systems may be represented can their simulators be built. The two main and orthogonal aspects to the theory are:

- Levels of system specification—These are differentiated levels of knowledge at which a system may be known and at which system behaviour can be described.

- System specification formalisms—These are the modelling formalisms that modellers can use to specify the models of dynamical systems.

Systems theory therefore distinguishes between the system's structure and its behaviour. An important structural and system specification concept

### CHAPTER 2. M&S, PRINCIPLES AND PRACTICE

is that of decomposition and composition. These indicate how a system may be broken down into component systems and how component systems may be coupled together to form a larger system. The system specification formalisms allow the specification of the structure and behaviour of dynamical systems at various levels of knowledge and system specification—as discussed in Section 2.3.1. Subclasses of dynamical systems such as Discrete Event Dynamical Systems (DEDS) and Discrete Time Dynamical Systems (DTDS) may however be defined with each having their own unique system specification formalism. Essential to distributed simulation, is the fact that systems theory—and each subclass of dynamical systems—is closed under composition. This allows hierarchical composition of systems with well defined structure and behaviour. The theme of atomic versus composed systems is revisited throughout the chapter.

The rest of this chapter does, however, not discuss the mathematics of systems theory and system specification formalisms in depth. Readers who are interested in this aspect are referred to [26][27][19][15]. This chapter rather attempts to establish a basic M&S framework based on systems theory within which the current discrete time simulation capability may be described and researched, and within which the SANDF, modellers and simulator builders can effectively communicate and align their future modelling and simulation efforts.

The levels of system knowledge and specification are introduced, followed as promised by a M&S framework that is well known within the international military simulation community. The system specification formalisms are introduced to provide insight into the different types of model specifications and their simulators. The focus is then narrowed slightly to parallel and distributed simulation and the simulators' architectural intricacies. The links to the HLA, which is a discrete event interoperability architecture, are also covered here.

## 2.1 Levels of System Knowledge and Specification

The difference between decomposed and non-decomposed systems may be phrased, within the M&S context, in terms of levels of system knowledge as discussed by Klir[28] and levels of system specification as discussed by Zeigler et al.[15]. According to these levels the decomposed system is at a higher level of knowledge and specification than the undecomposed system since more information is provided about the structure of the system.

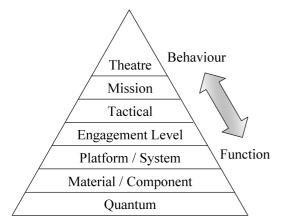

### 2.1. LEVELS OF SYSTEM KNOWLEDGE AND SPECIFICATION 31

| Level | Name       | What is known at this level                      |  |

|-------|------------|--------------------------------------------------|--|

| 3     | Structure  | Components (at lower levels) coupled together to |  |

|       |            | form a generative system                         |  |

| 2     | Generative | Means to generate data in a data system          |  |

| 1     | Data       | Data collected from a source system              |  |

| 0     | Source     | What variables to measure and how to observe     |  |

|       |            | them                                             |  |

Table 2.1: Klir's Levels of System Knowledge[15]

The four basic levels of system knowledge recognised by Klir is shown in Table 2.1. At each level some important things that were not know at lower levels become known. The *source level* identifies a portion of the world that is going to be modelled and how to observe it. The *data level* is the set of observations made for the source system. The *generative level* contains the means to generate the same data again which is knowledge that did not exist in the data level, for example. The concepts identified at this level are usually referred to as *models* of the system. At the top level, *structure level*, a special case generative system exists in which it is known how to generate the data observed at Level 1 through the interactions of the identified system components. These components are chosen to reflect what is believed to be the system's real underlying structure that generates (or leads to) the observed behaviour. This is again knowledge that possibly did not exist at the lower knowledge levels.

Klir's framework is useful in the sense of providing perspective on what is usually considered to be distinct concepts. Klir also reasons that, when moving to a lower level no new knowledge is generated, but what is implicit in the description already available is only made explicit. The reverse applies when moving to higher levels and is referred to as inferring new knowledge. There are therefore only three basic kinds of problems dealing with systems: systems analysis, systems inference and systems design. In *systems analysis*, the goal is to understand the behaviour of an existing or hypothetical system based on its known structure, moving from higher to lower knowledge levels. *Systems inference* tries to guess a black-box system's structure from observations, moving from lower to higher knowledge levels. Thirdly, in *systems design*, alternative structures for instantiating a certain system specified at the data level is investigated, in effect moving from lower to higher knowledge

### CHAPTER 2. M&S, PRINCIPLES AND PRACTICE

levels.

The levels (hierarchy) of systems specifications formulated by Zeigler include the concept of a dynamical system, and therefore time, which is more oriented towards the M&S context than Klir's knowledge levels. The systems are also viewed as having defined input ports and output ports through which they interact with other systems in a modular way. A system receives stimuli ordered in time—an input trajectory—on each of its input 'ports' and places a time-indexed response—an output trajectory—on each of its output ports. The system specification hierarchy, shown in Table 2.2, has an observation frame specification, I/O behaviour and I/O function specifications, a state transition specification and a coupled component specification. Table 2.2 also shows to which Klir level of system knowledge each of the system specifications correspond.

The Observation Frame specifies how to stimulate the system, which variables to measure and how to observe them against a time base. The decisions on what observation frame to use is dependent on the modelling choices made. These modelling choices are specified by the choice of an experimental reference frame which is explained in Section 2.2: Framework for Modelling and Simulation.

All the *observed* input trajectories along with their associated output trajectories are called the *IO Behaviour* of a system. If a method exists by which the IO behaviour of a system can be predicted, knowledge at the next level of the system, the *IO Function*, would have been attained. The IO function includes knowledge of the initial state and can determine a unique output for every input stimulus.

At the *State Transition* level of system specification, knowledge is gained of the system's (as a whole) state transitions as it responds to the input trajectories. The next level of system specification, *Coupled Components*, opens up the system to reveal more than just the system's aggregated state. At this specification level the system is composed of interacting components. The components may in turn be specified at levels 1 to 3 (or even at level 4) and are coupled using their input and output ports.

## 2.2 Framework for Modelling and Simulation

The framework presented in this subsection is done so that everyone involved in a simulation exercise—model developers, simulator developers and users alike—may use it to communicate effectively with each other and the wider military simulation community, and to align their research and development efforts. The system specification hierarchy (Section 2.1) provides the basis

### 2.2. FRAMEWORK FOR MODELLING AND SIMULATION

| Level | Specification    | Corrosponds | What is known at this level         |

|-------|------------------|-------------|-------------------------------------|

|       | Name             | to Klir's   |                                     |

| 4     | Coupled com-     | Structure   | Components and how they are         |

|       | ponent           | system      | coupled together. The compon-       |

|       |                  |             | ents can be specified at lower      |

|       |                  |             | levels or can even be structure     |

|       |                  |             | systems themselves - leading to     |

|       |                  |             | hierarchical structure.             |

| 3     | State transition | Generative  | How states are affected by inputs;  |

|       |                  | system      | given a state and an input what     |

|       |                  |             | is the state after the input stim-  |

|       |                  |             | ulus is over; what output event is  |

|       |                  |             | generated by a state.               |

| 2     | I/O function     |             | Knowledge of initial state; given   |

|       |                  |             | an initial state, every input stim- |

|       |                  |             | ulus produces a unique output.      |

| 1     | I/O behaviour    | Data system | Time-indexed data collected from    |

|       |                  |             | a source system; consists of in-    |

|       |                  |             | put/output pairs.                   |

| 0     | Observation      | Source sys- | How to stimulate the system with    |

|       | frame            | tem         | inputs; what variables to measure   |

|       |                  |             | and how to observe them over a      |

|       |                  |             | time base.                          |

Table 2.2: System Specification Hierarchy[15]

for the framework. The entities of the framework are introduced in the subsection below, followed by the relationships between them in a subsequent subsection.

The next subsection describing the framework then briefly introduces concepts related to model characterisation, validation, verification and qualification and links them to the framework. Finally, the different aspects of simulation time management and a classification for military simulation types are discussed.

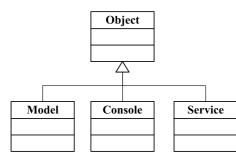

### 2.2.1 Entities of framework

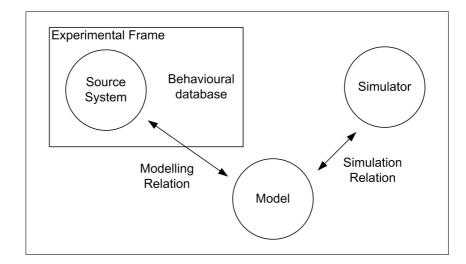

The basic entities of the framework, shown in Figure 2.1, are the *source* system, the *experimental frame*, the *model* and the *simulator*. The basic relationships between the entities, also shown, are the modelling and simulation

### CHAPTER 2. M&S, PRINCIPLES AND PRACTICE

Figure 2.1: The basic entities of an M&S framework and their relationships[15]

relationships.

The *Source System* is the environment that is of interest to the modeller; the source of the observable data. The system *behavioural database* contains the data that has been gathered by experimenting and observing the source system. The source system corresponds to level 0 of Klir's hierarchy, and the system behavioural data base corresponds to level 1 of Klir's hierarchy (the data system).

The behavioural data base is acquired within an *Experimental Frame* of interest to the modeller. The experimental frame is a specification of the conditions under which the system is observed or experimented with. Many experimental frames may be defined for the same source system and a single experimental frame may apply to many systems just as the same system may be modelled with respect to different objectives and different systems may be modelled with respect to the same objective.

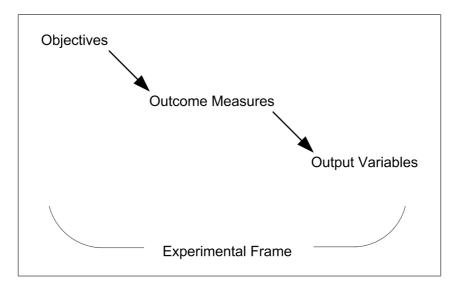

The statement of objectives serves to focus model construction on particular issues. Such a statement should be formulated as early as possible in the model development process so that parties involved may agree on their goals and align their efforts. These objectives may then be translated into more precise experimentation conditions for the source system or its models. The result of this translation, outlined in Figure 2.2, is the experimental frame.

The modelling objectives typically concern system design, in which case the *outcome measures* are measures of effectiveness in evaluating the system's design alternatives. In air defence system simulations, outcome measures are typically 'the number of threats successfully engaged before they could reach

#### 2.2. FRAMEWORK FOR MODELLING AND SIMULATION

Figure 2.2: Transforming objectives into experimental frames[15]

their weapon release line' or possibly 'the percentage hits of a particular weapon system'. In order to compute the relevant outcome measures the appropriate output variables must be defined, which in turn drive the modelling effort within the specific experimental frame.

As suggested, a *Model* may be defined as a system specification at any of the levels in Table 2.2. In the traditional context of M&S, though, the system specification is usually done at levels 3 and 4, corresponding to Klir's generative and structure levels. These models are typically instructions or equations for generation of IO behaviour. A typical Air Defence System consists of a number of subsystem models specified at level 3 which are coupled together to specify more complex system structure models at level 4. The various system models may then be coupled together to specify a more complex system of systems structure model, also at level 4.

As sets of instructions or equations, the model instances require a *third* party to execute the instructions or to evaluate the equations and to manage the coupling of output ports to input ports. This third party 'computing system' is the *Simulator*. The simulator is the final entity of the M&S framework and the focus of this dissertation. According to Zeigler et al., separating the model and simulator concepts provides a number of benefits for the framework, namely:

• The same model, expressed in a formalism, may be executed by different simulators, thus opening the way for portability and interoperability at a high level of abstraction, and

### CHAPTER 2. M&S, PRINCIPLES AND PRACTICE

• simulator algorithms for the various formalisms may be formulated and their correctness rigorously established.

## 2.2.2 Relationships among entities

According to Zeigler et al., the entities—system, experimental frame, model, simulator—become truly significant only when properly related to each other. As was seen in the previous section, a model of a system is built within a certain experimental frame according to certain objectives and it is critical for the success of the simulation that certain relationships hold. The two most fundamental are the *Modelling* and *Simulation* relations, also shown in Figure 2.1, as these ensure the validity of the model and the simulator's correctness respectively. A third relation that is important for understanding modelling and simulation work is *Modelling as Valid Simplification*. These three relations are now discussed.

### Modelling Relation

As shown, in Figure 2.1, the *Modelling Relation* refers to a relation between a system, the experimental frame and the model. In other words, the modelling relation, in effect *model validity*, describes to what degree a model faithfully represents the system being modelled within the experimental frame chosen. The degrees of validity that are differentiated here are:

- Replicative validity

- Predictive validity

- Structural validity

Replicative validity holds if, for all the experiments possible within the chosen experimental frame, the IO behaviour (observed input/output trajectories) of the model and system agree to within an acceptable tolerance. Replicative validity, therefore, holds if the model and the system are equivalent at a system specification level of 1. *Predictive validity* is a stronger form of validity which requires not only replicative validity, but also the means to predict behaviour not observed yet. This requires that the model and system be equivalent at the next system specification level of 2 which is on an IO function level.

Structural validity is the strongest of the degrees of validity differentiated here. As the name implies it "looks inside" the system and requires that the model and the system be equivalent at a system specification level of 3 (or

### 2.2. FRAMEWORK FOR MODELLING AND SIMULATION

4). This allows the model to not only replicate or/and predict the system's behaviour, but to mimic on a system level (or sub-system/component level) the state transitions of the system.

The term fidelity is often used and it refers to combination of both model validity and model detail. Detail refers to the depth in terms of the number of output variables that the experimental frame requires the system to be probed and is therefore highly dependent on the modelling objectives. It is important to note, though, that high detail alone does not imply high fidelity. High fidelity also requires the modelling relation to hold to the appropriate degree.

### Simulation Relation

As shown, in Figure 2.1, the *Simulation Relation* is a relation between the simulator entity and the model entity of the M&S framework being described. According to Zeigler, a simulator correctly simulates an instance of a model, if, given the object's initial state and input trajectory, the simulator generates the expected output trajectory. Simulator correctness thus requires agreement at, at least, the IO function specification level. If, however, the model was specified at a state transition or coupled component system specification level then, depending on the modellers interest in the detail, the simulator correctness might require agreement at the system state transition or the coupled component levels respectively.

### Modelling As Valid Simplification

The modeller should constantly keep in mind the limited resources of the currently existing simulators. A model might have to be simplified to be simulated within a reasonable time period. The simplified model must still represent the modelled system to the required degree of validity within the chosen experimental frame, though. The detailed (valid for a large set of experimental frames) model is referred to as a *Base Model* and the simplified model as a *Lumped Model*. The lumped model is typically valid for a small set of experimental frames or a single experimental frame, but it is important to note that the lumped model is just as valid within these specific experimental frames as the base model. In Chapter 13 of [15], Zeigler et al. discuss the concept of a morphism for judging the equivalence of base and lumped models with respect to a specific experimental frame, and how to construct such morphisms.

### 2.2.3 Model Characterisation, Validation, Verification and Qualification

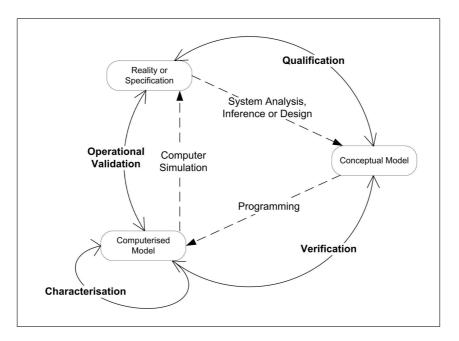

This subsection briefly deals with the *error* in the relations between the entities in the M&S framework. Verification and validation concepts from Zeigler et al.[15] are discussed to address the error in the simulator and model respectively. These concepts are then integrated with the characterisation, validation, verification and qualification cyclical modelling process used by Sargent[29][30] which has already been studied within the GBADS modelling domain.

Zeigler et al. discuss verification as the attempt to test that the simulation relation (discussed earlier) holds between a simulator and a model. The simulation relation in effect establishes error free simulator correctness while verification is the process to evaluate the errors introduced by the process of building the simulator.

Validation, in turn, attempts to test whether the modelling relation (model validity) holds. The modelling relation establishes that an error free model faithfully represents reality to a certain degree of validity within the chosen experimental frame while the validation effort evaluates the faithfulness of the representation taking into account the errors introduced during the modelling process.

Model verification and validation, along with model characterisation and qualification, is a significant part of the modelling process from beginning to end. The modelling process, used by Sargent[29][30], shown in Figure 2.3 is built around these aspects. The process has already been investigated within DPSS's M&S team by Roodt[31] and is reiterated specifically within the GBADS and M&S support domain by Pretorius[1].

The qualification aspect of the modelling process makes the cyclic link between Figure 2.1 and Figure 2.2 taken from Zeigler et al. During the modelling process qualification in effect evaluates whether the chosen experimental frame represents reality in such a way that the outcome measures, and therefore the objectives, are satisfied.

The specific verification and validation techniques and processes are not discussed in this dissertation. The interested reader is referred to [29], in which Sargent continues with validation techniques for each of the above mentioned aspects, and also [31], in which Roodt continues to propose a verification, validation and accreditation (VV&A) process. The viewpoint in the above two references seems to be that model validity may be inferred when there is *failure to reject the model*. Zeigler at al.[15] however follow a more formal approach and attempt to prove validity and simulator correctness in Chapters 12, 13 and 14 of their book.

### 2.2. FRAMEWORK FOR MODELLING AND SIMULATION

Figure 2.3: Model characterisation, validation, verification and qualification within the simplified modelling process (Adapted from [31])

Accreditation is also referred to as certification of a model. This is usually done by a third party (accreditation agent), possibly making use of subject matter experts. According to Roodt[31], the accreditation agent's final assessment may result in:

- Full accreditation—-simulation produces results that are sufficiently credible to support the application,

- limited or conditional accreditation—constraints are placed on how the simulation can be used to support the application,

- modification of the simulation is needed—simulation capabilities are insufficient to support an accreditation decision which requires modifications and subsequent V&V to correct,

- $\bullet$  additional V&V information is needed—requires supplemental V&V, and

- no accreditation the simulation is not fit to support the application.

Sargent [29] is of the opinion that accreditation is most viable (due to cost) when done in parallel with the model development process such that it facilitates the appropriate quality and quantity of V&V efforts during development.

### CHAPTER 2. M&S, PRINCIPLES AND PRACTICE

### 2.2.4 A Taxonomy for Classifying Military Simulation Types

The taxonomy most often used for classifying the different military simulation types is described by Page and Smith[8]. This live, virtual and constructive classification scheme originated from the US DOD during their early simulation efforts. The three classes are officially described as:

- *live simulation* refers to a real simulation involving real people operating real systems.

- *virtual simulation* refers to a simulation involving real people operating simulated systems. Virtual simulations inject human-in-the-loop in a central role by exercising motor control skills (e.g. flying an aeroplane), decision skills (e.g. committing fire control resources to action), or communication skills (e.g. as members of a C4I team).

- constructive simulation refers to a simulation that involves simulated people operating in simulated systems. Real people stimulate (make inputs to) such simulations, but are not involved in determining the outcomes.

The simulation type taxonomy aids the people involved in creating a common understanding of the typical use cases of the simulation which guides the people involved in aligning their efforts in regard to the required experimental frames, potential simulator architectures, simulation logistics, etc.

### 2.2.5 A Simulation Time Management Taxonomy

The synthetic environment has its own notion of time i.e. the *simulation* time according to which the virtual inhabitants play out the action. Simulations and simulators may be distinguished based on their time management strategies. Logical time management requires the simulation to execute every simulated clock tick, stepping the entire system from one state to the next in a deterministic manner. Logical time simulation is also known as, As-Fast-As-Possible (AFAP) simulation as there is no implicit synchronisation of the simulation time with a real world clock. Such a simulation takes as long as is required to simulate any given scenario.

*Real-time* simulation, on the other hand, actively tries to keep its simulation time synchronised with an external real world (wall) clock. A real-time simulation continually *jumps* forward in time as far as is needed to keep executing at real-time. All partaking models and external constructive and

### 2.2. FRAMEWORK FOR MODELLING AND SIMULATION

|          | Logical Time          | Real-Time |

|----------|-----------------------|-----------|

| Locally  | Type 0 (Not possible) | Type 1    |

| Managed  |                       |           |

| Globally | Type 2                | Type 3    |

| Managed  |                       |           |

Table 2.3: A Simulation Time Taxonomy

virtual components must support this *time jump* behaviour for real-time simulation to be successful. The bigger the time jumps, however, the harder it becomes to ensure causality of simulation messages and events within a certain time resolution, until at some point when either real-time execution must be sacrificed or causality is lost along with the credibility of the simulation. A logical time simulation may of course ensure, within performance limits, that its execution is throttled so that it does not exceed real-time. Even in such cases, the differences between logical time and real-time simulation remains in that the former simulation still executes a state transition on each and every simulated clock tick. A logical time simulation that cannot be simulated fast enough to keep up with real-time will fall behind the wall clock.

Time can also be managed either locally or globally across the coupled component models. Global time management implies that there is some explicit time synchronisation mechanism between the coupled components. This is not required for local time management since each component runs at a predefined execution rate. Combining the local/global time dimension with the real-time/logical time dimension results in a *Time Taxonomy* shown in Table 2.3.

A simulation of Type 0 can not be built as there is by definition no mechanism to synchronise the time between the logical time models. Logical time models execute AFAP or apply a best effort to keep to a predefined ratio of real-time. A global mechanism is required to block the execution of models that get ahead of others. Within this time taxonomy, the discrete time simulator discussed in this dissertation, and currently in use, is of type 2. It is a distributed simulator, whose processing nodes each execute AFAP (logical time) and the global synchronisation mechanism tracks node progress and pauses the execution of nodes that get ahead of the others It is worth noting that the previously mentioned simulation type taxonomy is a use case view, while the time taxonomy is an implementation view further down the development cycle of the simulator.

Table 2.3 does however not indicate the *mechanisms* of global time synchronisation. Global time management is further differentiated into conservative and optimistic global time management. Conservative time management is how we intuitively expect the coupled components to behave in that causality violations are strictly avoided. Avoiding causality violations is done by processing the input messages in strict increasing time order which is called the *local causality constraint*.

Optimistic time management, on the other hand, lets a component assume that it is safe to process the events at its inputs although future events may violate the local causality constraint. The object may, however, only operate under this optimistic assumption if it is capable of backtracking its own execution should a message that is older than its current internal time arrive at its input so that causality may be repaired when detected. Optimistic time management ensures that components do not wait unnecessarily for each other or for time advance requests from the simulator. In scenarios where this does not lead to excessive backtracking, such optimistic time management leads to improved simulation performance. Fujimoto experimentally demonstrated the improved performance of optimistic time management in [10] and Zeigler et al. further argues that under typical conditions excessive backtracking does indeed not happen.

## 2.3 Modelling Formalisms and System Specifications

A system specification formalism (or modelling formalism) is a notation with which to articulate the specification of a system to be modelled. Every subclass or type of system has its own modelling fomalism with which to articluate the system specification. Each system subclass implies constraints in terms of description of dynamic behaviour and time management. Zeigler et al. does also distinguish between *basic* and *coupled* system specification formalisms for the spesification of atomic and coupled component models respectively. As mentioned at the onset of this chapter, the system specification formalisms are not discussed in a formal mathematical manner and the interested reader is referred to the work by Zeigler et al. The basic system specification formalisms (basic system subclasses) are introduced to provide insight into the different types of models and their simulators that may be used to instantiate and breathe life into a simulation capability. The coupled extensions to the basic formalisms will be differentiated in the next section.

The basic DTSS is discussed followed by the basic DEVS. The Differen-

### 2.3. MODELLING FORMALISMS AND SYSTEM SPECIFICATIONS 43

tial Equation System Specification (DESS) modelling formalism is a third basic modelling formalism discussed by Zeigler et al. The DESS modelling formalism is not explicitly required for this dissertation and therefore not discussed. Many of the existing GBADS sub-system models do however include sets of differential equations which is currently numerically analysed in discrete time models, but could be articulated using the DESS formalism.

Interconnection between a DTSS and a DEVS is then discussed and the DEVS modelling formalism is finally presented as being universal in the sense that it includes the DTSS modelling formalism, and any other, modelling formalisms. This knowledge further facilitates a common language between M&S groups and allows sensible reuse of models and interconnection of different simulation types. The fact that DTSS specified models may be interfaced to and embedded within a DEVS is also critical to this dissertation. The hybrid DEVS/DTSS simulator proposed to address the research question and discussed in Part III is built upon this knowledge.

### 2.3.1 General Dynamical Systems

A dynamical system has a *time base* that orders all dynamical changes. Dynamical systems may also be specified or described at the various knowledge levels or system specification levels discussed in Section 2.1. At the IO observation frame system specification level—source system knowledge level—the dynamical system my be specified as the structure IO = (T, X, Y), where T is the time base, X is the input values set and Y is the output values set. At the IO behaviour system specification level—data system knowledge level—the I/O relation observation of the dynamical system is specified as the structure  $IORO = (T, X, \Omega, Y, R)$ , where  $\Omega$  is the set of allowable input segments, R is the I/O relation and the rest are as before. The I/O relation, R, is the set of all input and corresponding output segment pairs, for every and all allowable input segments in  $\Omega$ .

At the I/O function system specification level the I/O relation, R, is replaced with a set of functions  $F = \{f_1, f_2, \dots f_i \dots\}$  and the I/O function observation (IOFO) of the system is specified as the structure IOFO = $(T, X, \Omega, Y, F)$ . This allows the correct output segment to be chosen from the set of output segments for a specific input segment given that the system's initial state and in effect which function  $f_i$  to use is known.

At the state transition system specification level the set of functions, F, is replaced with a set of states, Q, a global state transition function,  $\Delta$ , and an output function,  $\Lambda$ . At this level the dynamical system may be specified as  $S = (T, X, \Omega, Y, Q, \Delta, \Lambda)$ . The global transition function,  $\Delta$ , describes the state-to-state transition caused by the input segments. The output function,

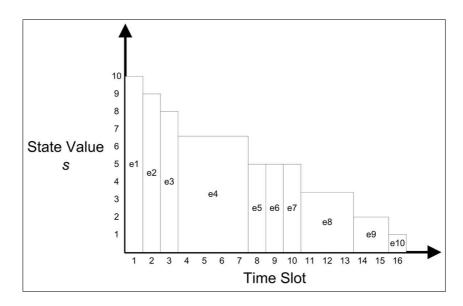

Figure 2.4: Discrete Time System Specification

$\Lambda$ , describes the state-to-observable-output mapping. The output function may be a function of state and input (Mealy-type system) or of only state (Moore-type system).

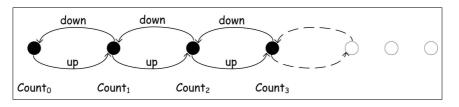

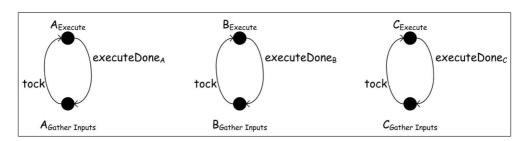

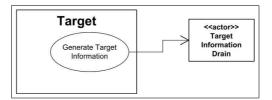

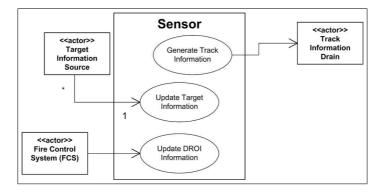

The subclasses of dynamical systems represented in the next two subsections are of similar structure. Certain constraints have however been imposed on the systems. These constraints define the subclass boundaries.

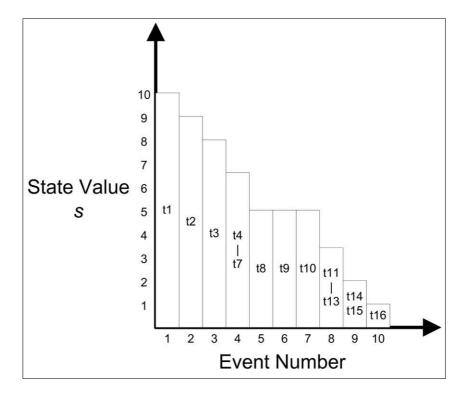

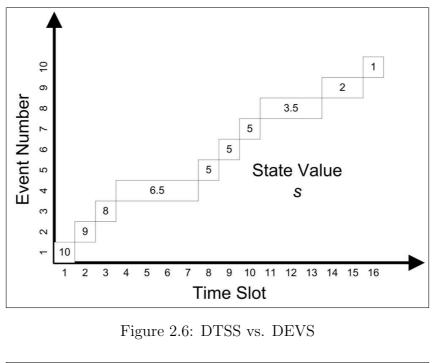

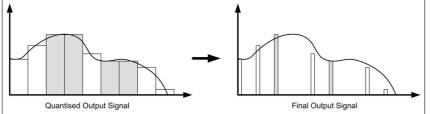

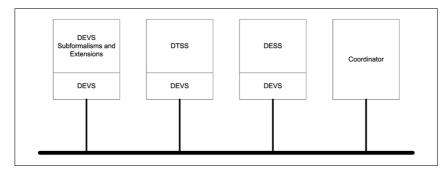

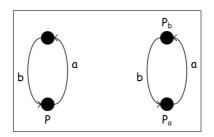

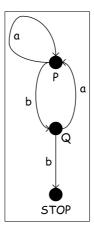

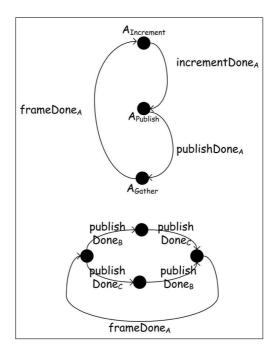

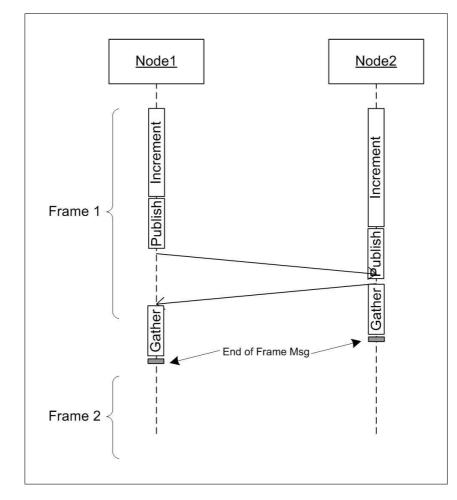

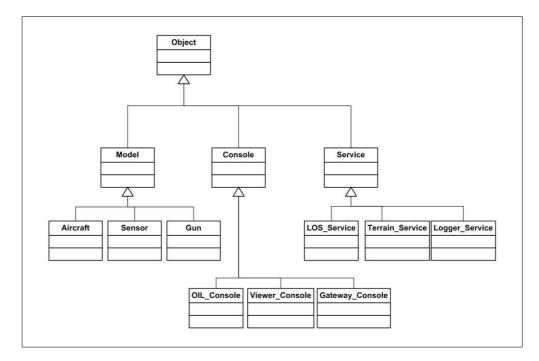

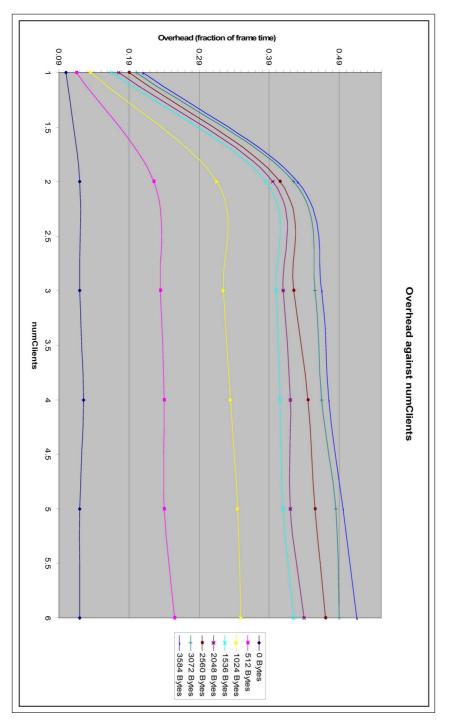

### 2.3.2 The Discrete Time System Specification (DTSS)