The University of Manchester

# COMPUTATION WITH CONTINUOUS MODE CMOS CIRCUITS IN IMAGE PROCESSING AND PROBABILISTIC REASONING

# A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2014

PRZEMYSLAW MROSZCZYK

SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING

# Contents

| Abstract |       |                                                            |    |  |  |

|----------|-------|------------------------------------------------------------|----|--|--|

| D        | eclar | ation                                                      | 7  |  |  |

| С        | opyr  | ight                                                       | 8  |  |  |

|          |       | wledgements                                                | 9  |  |  |

|          |       |                                                            | -  |  |  |

|          |       | r's publications                                           | 10 |  |  |

| 1        | Intr  | roduction                                                  | 11 |  |  |

|          |       | Chapter overview                                           |    |  |  |

|          |       | Reasons for alternative approaches                         |    |  |  |

|          | 1.3   | Alternative ways of information processing                 |    |  |  |

|          |       | 1.3.1 Analogue computers                                   |    |  |  |

|          |       | 1.3.2 Artificial neural networks                           |    |  |  |

|          |       | 1.3.3 Stochastic computers                                 |    |  |  |

|          | 1.4   | Motivations                                                |    |  |  |

|          | 1.5   | Research overview                                          |    |  |  |

|          |       | 1.5.1 Binary image processing                              |    |  |  |

|          | 1.0   | 1.5.2 Bayesian inference.                                  |    |  |  |

|          |       | Contributions                                              |    |  |  |

|          | 1.7   | Thesis structure                                           | 25 |  |  |

| 2        | Cor   | nputation with MOS transistors under parameter variability | 27 |  |  |

|          | 2.1   | Chapter overview                                           | 27 |  |  |

|          | 2.2   |                                                            |    |  |  |

|          |       | 2.2.1 MOS model for hand calculations                      | 29 |  |  |

|          |       | 2.2.2 Switched-current circuits                            |    |  |  |

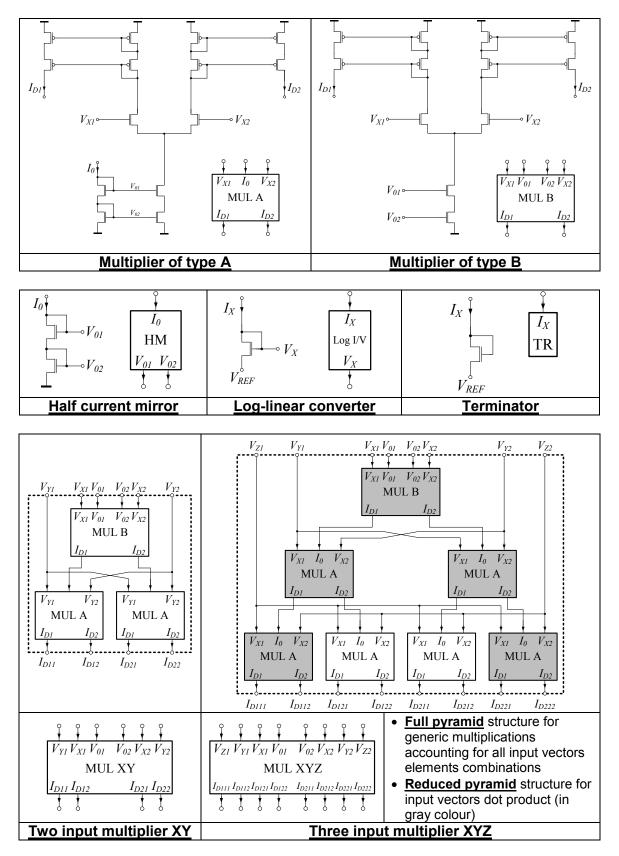

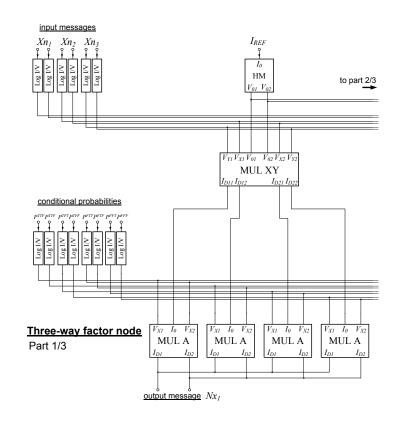

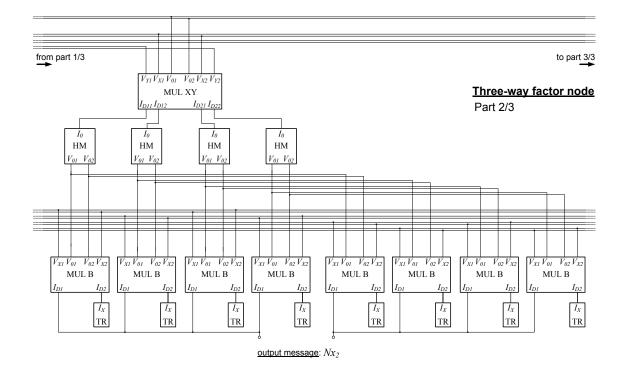

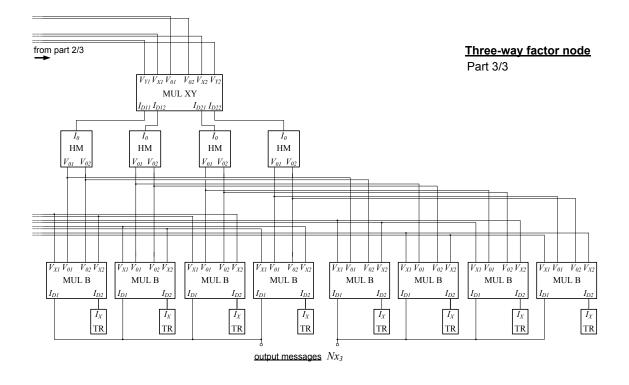

|          |       | 2.2.3 Analogue multipliers                                 |    |  |  |

|          | 2.3   | Parameter variability in CMOS technologies                 | 35 |  |  |

|          |       | 2.3.1 Physical model                                       |    |  |  |

|          |       | 2.3.2 Empirical model                                      |    |  |  |

|          |       | 2.3.3 Variability propagation                              |    |  |  |

|          | 2.4   | Mismatch modelling                                         |    |  |  |

|          |       | 2.4.1 Mismatch MOS model for hand calculations             |    |  |  |

|          |       | 2.4.1.1 Strong inversion and saturation                    |    |  |  |

|          |       | 2.4.1.2 Strong inversion and linear region                 |    |  |  |

|          |       | 2.4.1.3 Weak inversion                                     |    |  |  |

|          |       | 2.4.2 Statistical MOS models for CAD                       |    |  |  |

|          |       | 2.4.3 Extended simplified model                            |    |  |  |

|          | 2.5   | Mismatch scaling                                           |    |  |  |

|          | 2.6   |                                                            |    |  |  |

|          | 2.7   | Mismatch versus temperature                                | 50 |  |  |

|   | 2.8  | Mismatch optimisation                                                                                   | 50  |  |  |

|---|------|---------------------------------------------------------------------------------------------------------|-----|--|--|

|   |      | 2.8.1 Circuit design techniques                                                                         | 50  |  |  |

|   |      | 2.8.2 Layout drawing techniques                                                                         | 51  |  |  |

|   | 2.9  | Conclusions                                                                                             |     |  |  |

| 3 | Cur  | rent-mode analogue multipliers                                                                          | 53  |  |  |

|   | 3.1  | Introduction and chapter overview                                                                       |     |  |  |

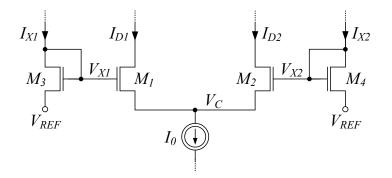

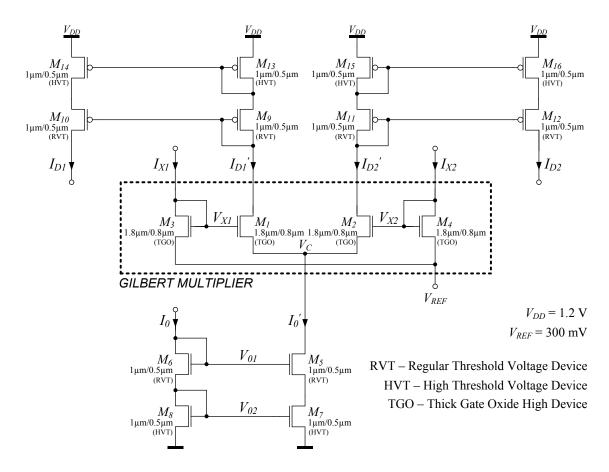

|   |      | Continuous-time Gilbert multiplier                                                                      |     |  |  |

|   |      | 3.2.1 Circuit analysis and realisation                                                                  |     |  |  |

|   |      | 3.2.2 Design issues                                                                                     | 57  |  |  |

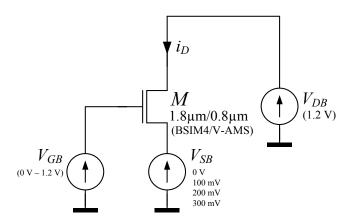

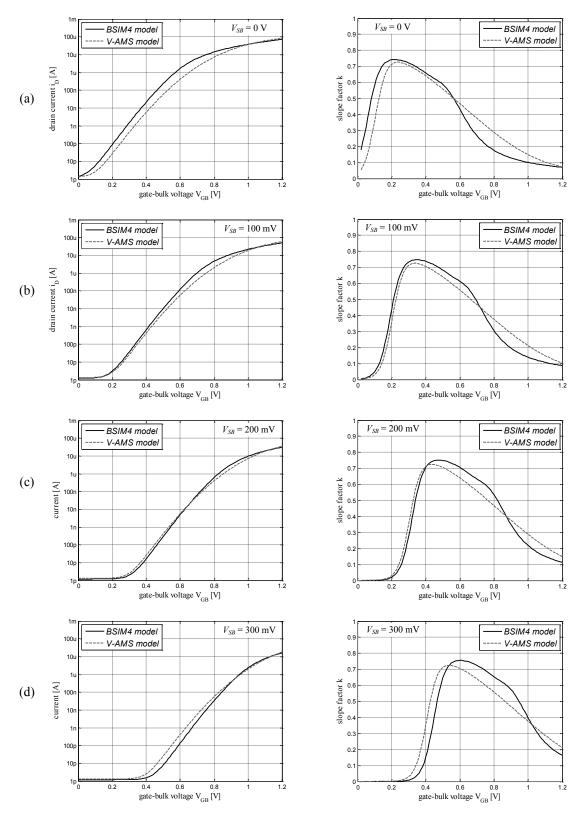

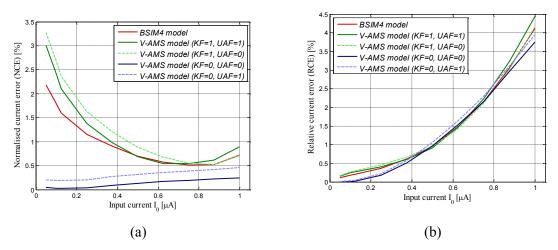

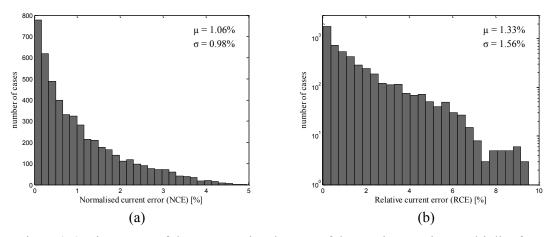

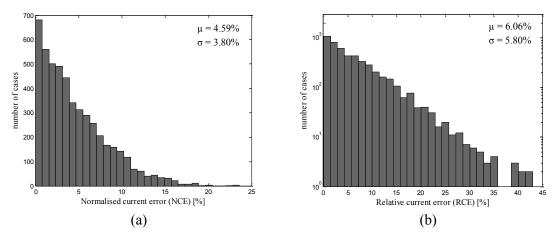

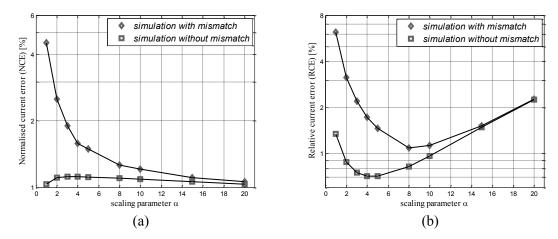

|   |      | 3.2.3 V-AMS MOS model                                                                                   |     |  |  |

|   |      | 3.2.4 Computational errors                                                                              |     |  |  |

|   |      | 3.2.5 Simulation results                                                                                |     |  |  |

|   | 3.3  | Discrete-time Gilbert multiplier                                                                        |     |  |  |

|   |      | 3.3.1 Circuit analysis and realisation                                                                  |     |  |  |

|   |      | 3.3.2 Design issues                                                                                     |     |  |  |

|   | ~ .  | 3.3.3 Simulation results                                                                                |     |  |  |

|   |      | Fixed point digital implementation                                                                      |     |  |  |

|   | 3.5  | Summary and conclusions                                                                                 | 80  |  |  |

| 4 | Dela | Delay lines 8                                                                                           |     |  |  |

|   | 4.1  | Chapter overview                                                                                        |     |  |  |

|   | 4.2  | Introduction                                                                                            |     |  |  |

|   | 4.3  | Circuit operation                                                                                       |     |  |  |

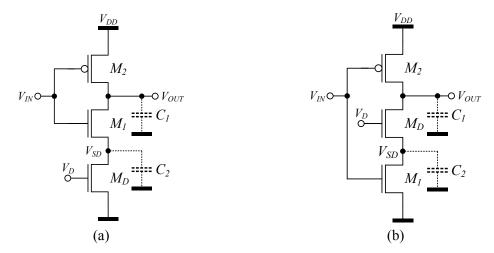

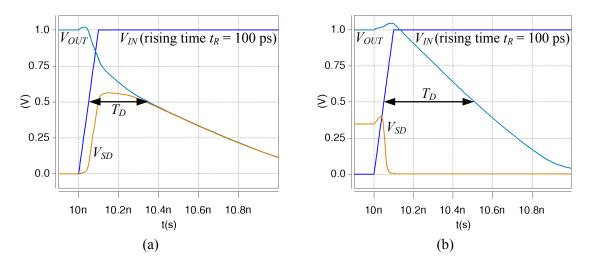

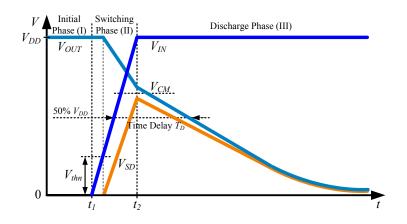

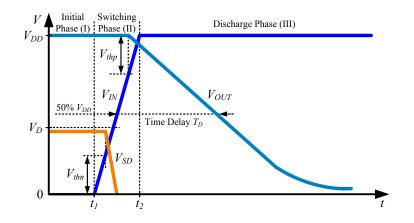

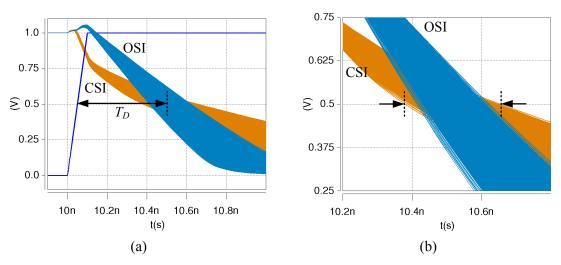

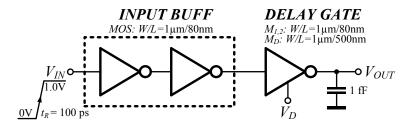

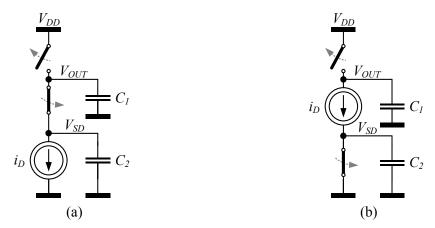

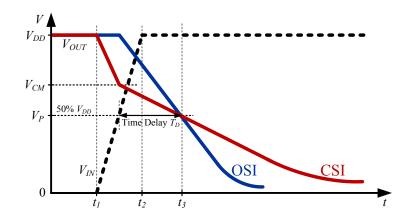

|   |      | 4.3.1 Current starved inverter (CSI)                                                                    |     |  |  |

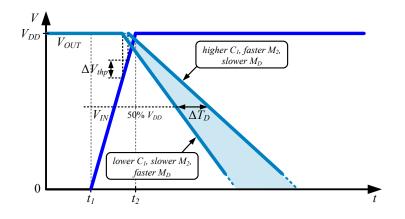

|   |      | 4.3.2 Output split inverter (OSI)                                                                       |     |  |  |

|   | 4.4  | Mismatch analysis                                                                                       |     |  |  |

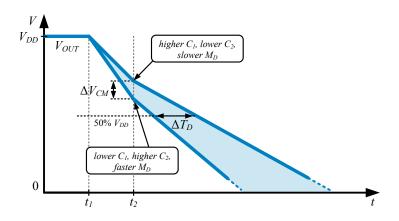

|   |      | 4.4.1 Mismatch in CSI gate                                                                              |     |  |  |

|   |      | 4.4.2 Mismatch in OSI gate                                                                              |     |  |  |

|   |      | 4.4.3 Simplified analytical model                                                                       |     |  |  |

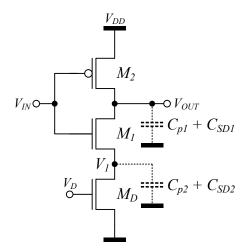

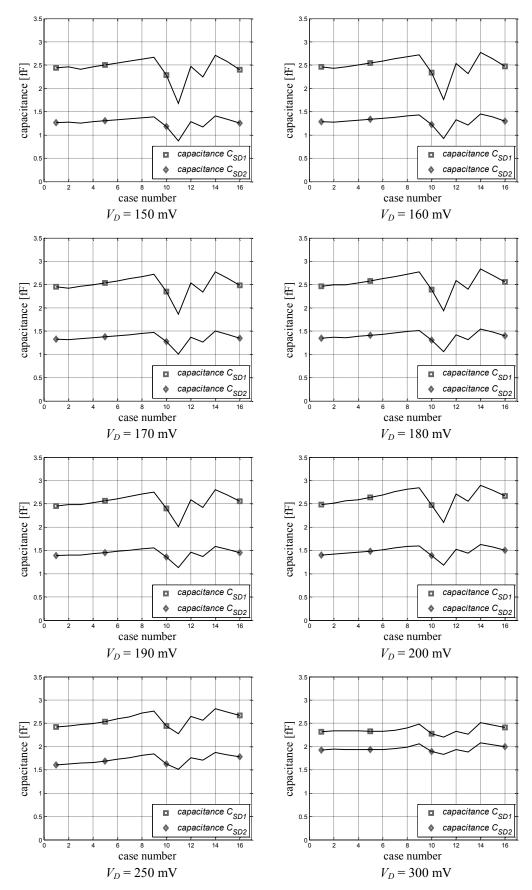

|   |      | 4.4.4 Charge sharing and S/D inherent capacitances                                                      |     |  |  |

|   |      | 4.4.5 Model derivation                                                                                  |     |  |  |

|   |      | <ul><li>4.4.5.1 Mismatch model of a delay gate</li><li>4.4.5.2 Mismatch model of a delay line</li></ul> |     |  |  |

|   |      | 4.4.5.3 Mismatch optimisation                                                                           |     |  |  |

|   | 15   | Chip design and circuit implementation.                                                                 |     |  |  |

|   |      | Experimental results                                                                                    |     |  |  |

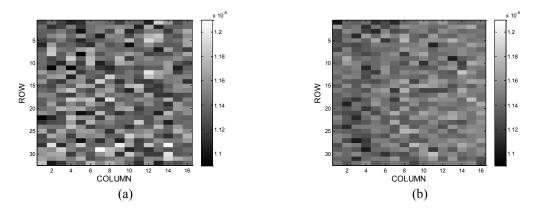

|   | 4.0  | 4.6.1 Callibration                                                                                      |     |  |  |

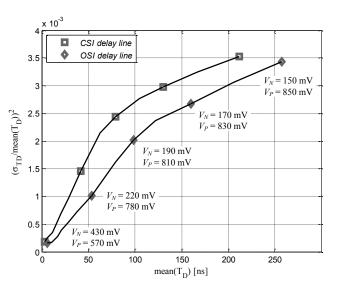

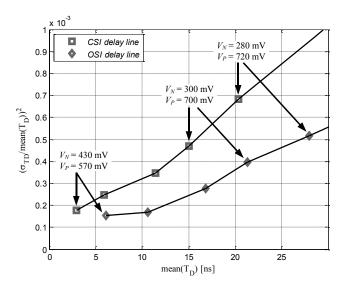

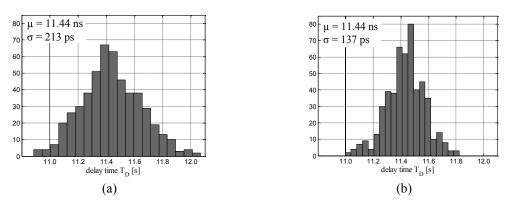

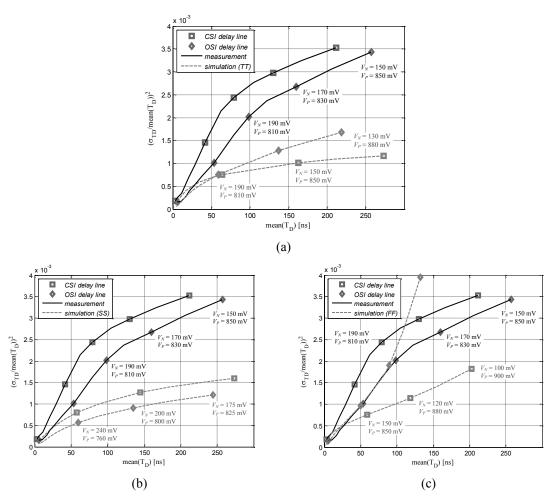

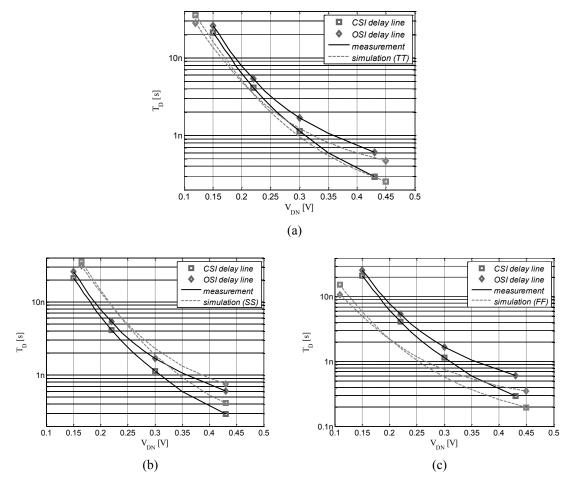

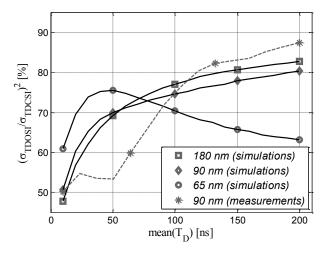

|   |      | 4.6.2 Normalised delay variance                                                                         |     |  |  |

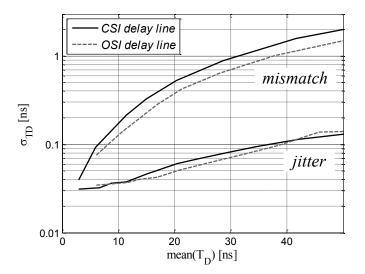

|   |      | 4.6.3 Time jitter                                                                                       |     |  |  |

|   |      | 4.6.4 Simulations versus measurements                                                                   |     |  |  |

|   | 4.7  | Conclusions                                                                                             |     |  |  |

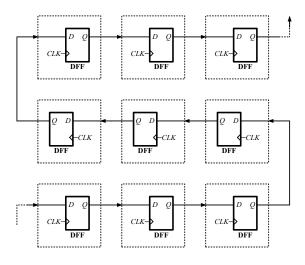

| 5 | Asy  | nchronous CMOS logic array for binary image processing                                                  | 113 |  |  |

|   | 5.1  | Chapter overview                                                                                        | 113 |  |  |

|   |      | Introduction                                                                                            |     |  |  |

|   | 5.2  | 5.2.1 Bio-inspired approach                                                                             |     |  |  |

|   |      | 5.2.2 SIMD paradigm                                                                                     |     |  |  |

|   |      | 5.2.3 Vision chips                                                                                      |     |  |  |

|   |      | 1                                                                                                       |     |  |  |

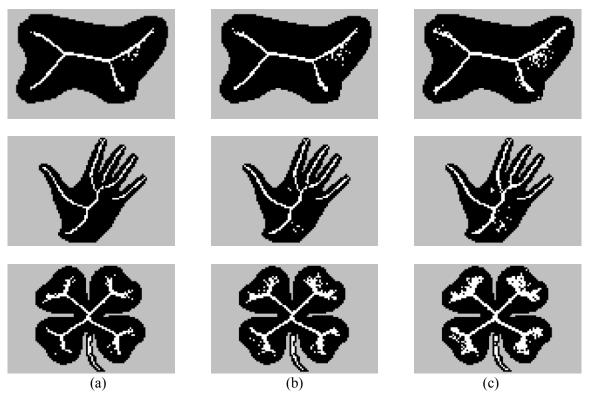

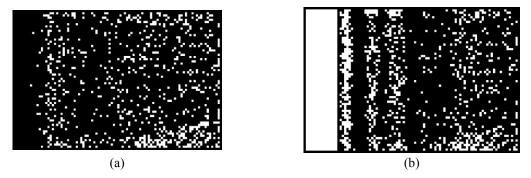

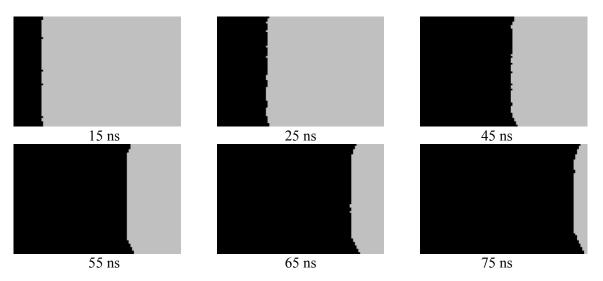

| 5.3   | Wave propagation approach to skeletonization |     |

|-------|----------------------------------------------|-----|

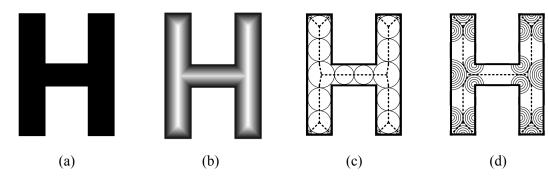

|       | 5.3.1 Skeletonization (background knowledge) |     |

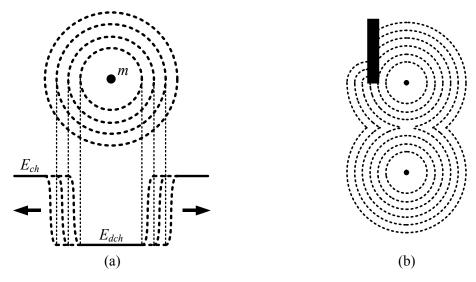

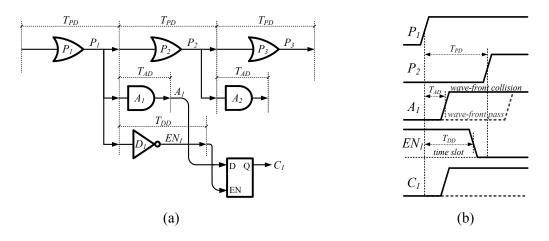

|       | 5.3.2 Trigger-wave propagation concept       |     |

|       | 5.3.3 Hardware realisations                  |     |

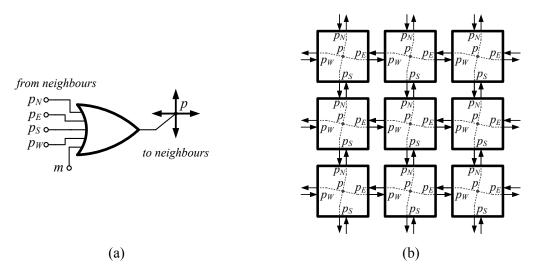

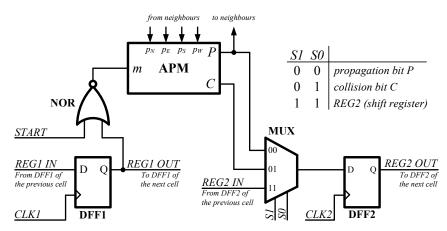

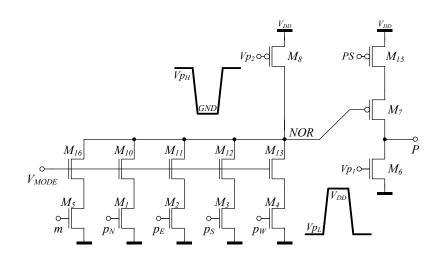

| 5.4   | Circuit design                               |     |

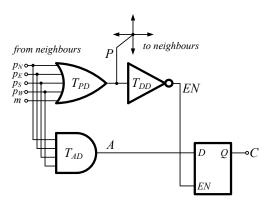

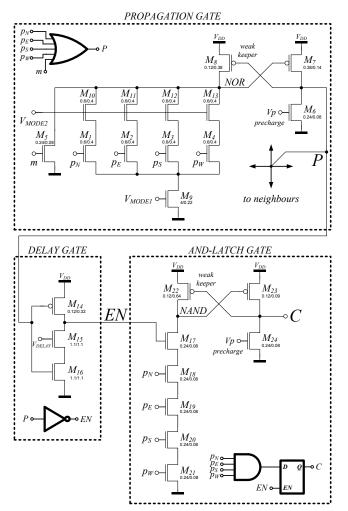

|       | 5.4.1 Propagation gate                       |     |

|       | 5.4.2 Collision-detectig gate                |     |

|       | 5.4.3 CMOS circuit realisation               |     |

|       | 5.4.4 Mismatch optimisation                  |     |

| 5.5   | Chip implementation                          |     |

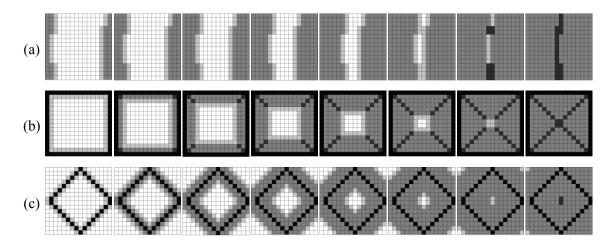

| 5.6   | 5 1                                          |     |

| 5.7   | 1                                            |     |

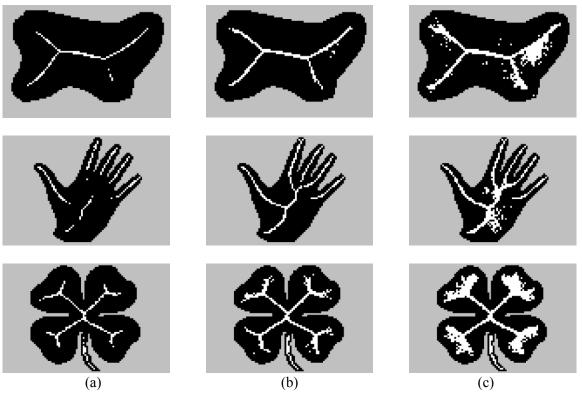

|       | 5.7.1 Result comparison                      |     |

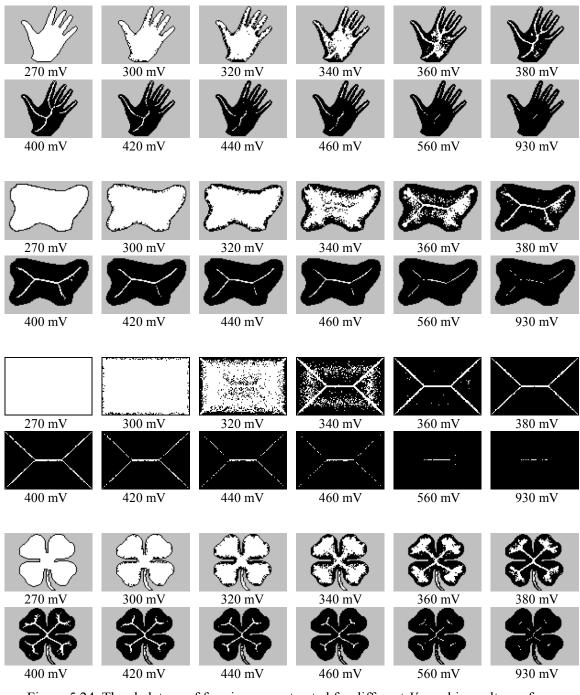

|       | 5.7.2 Delay voltage tuning                   |     |

|       | 5.7.3 Supply voltage variability             |     |

|       | 5.7.4 Temperature variability                |     |

| 5.8   | B Design issues                              |     |

|       | 5.8.1 Power rail ringing                     |     |

|       | 5.8.2 Design asymmetry                       |     |

|       | Performance and power                        |     |

| 5.1   | 0 Design improvements and conclusions        |     |

|       | 5.10.1 Conclusions                           |     |

|       | 5.10.2 Improvements and future work          |     |

| 6 Wa  | ave propagation concept in arbitrary metrics | 152 |

| 6.1   | Chapter overview                             |     |

| 6.2   | Introduction                                 |     |

| 6.3   | Propagation and timing analyses              |     |

| 6.4   | Simplified switched <i>RC</i> model          |     |

| 6.5   | 6 CMOS design and experimental results       |     |

| 6.6   | Conclusions                                  |     |

| 7 Pro | obability and reasoning                      | 162 |

| 7.1   | Introduction and chapter overview            |     |

| 7.2   | 1                                            |     |

| 7.3   |                                              |     |

| 7.4   |                                              |     |

| 7.5   | 5                                            |     |

| 7.6   |                                              |     |

| 7.7   | Conclusions                                  |     |

| 8 VI  | LSI systems for Bayesian inference           | 174 |

| 8.1   |                                              |     |

| 8.2   | 1                                            |     |

| 8.2   |                                              |     |

| 0.5   | 8.3.1 Continuous-time circuits               |     |

|       | 8.3.2 Discrete-time circuits                 |     |

| 8.4   |                                              |     |

|       | Simulations                                  |     |

| (A)   |                                              |     |

|               |             |              | Simulation setup                                 |     |  |  |

|---------------|-------------|--------------|--------------------------------------------------|-----|--|--|

|               | 8.6         |              | Resultsorks in continuous-time analogue circuits |     |  |  |

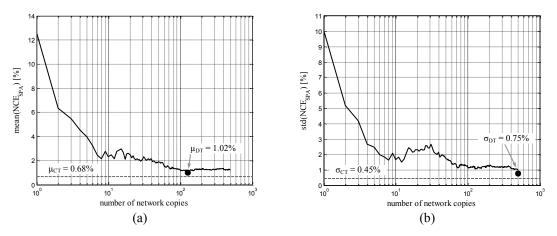

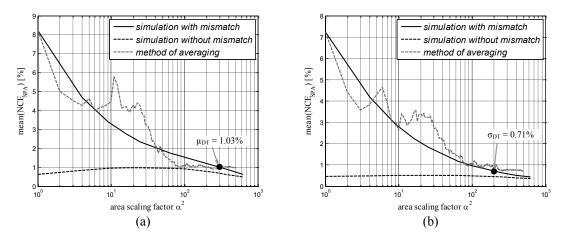

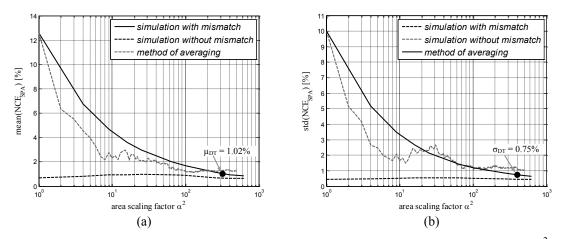

|               | 0.0         |              | Accuracy versus redundancy                       |     |  |  |

|               |             |              | Accuracy versus area                             |     |  |  |

|               |             |              | Convergence in large networks                    |     |  |  |

|               |             |              | Complexity and power scaling                     |     |  |  |

|               | 8.7         |              | rmance of analogue systems                       |     |  |  |

|               | 0.7         |              | Computational efficiency                         |     |  |  |

|               |             | 0./.1<br>872 | Performance of the continuous-time realisation   |     |  |  |

|               |             |              | Performance of the discrete-time realisation     |     |  |  |

|               | 8.8         |              |                                                  |     |  |  |

|               | 0.0         |              | al implementation                                |     |  |  |

|               |             |              | Fixed point arithmetic                           |     |  |  |

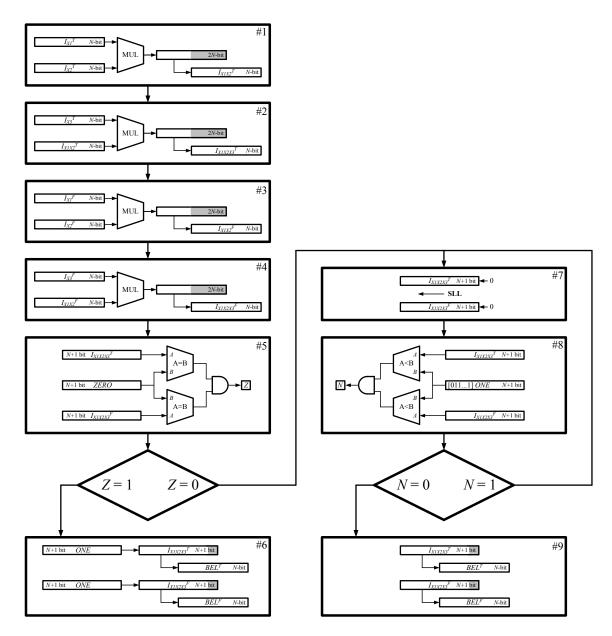

|               |             |              | Hardware realisation                             |     |  |  |

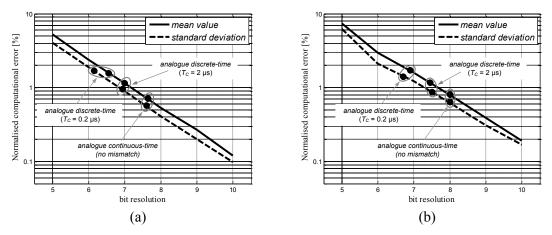

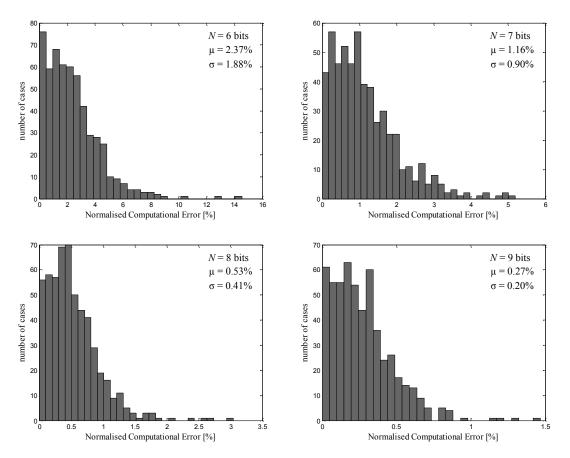

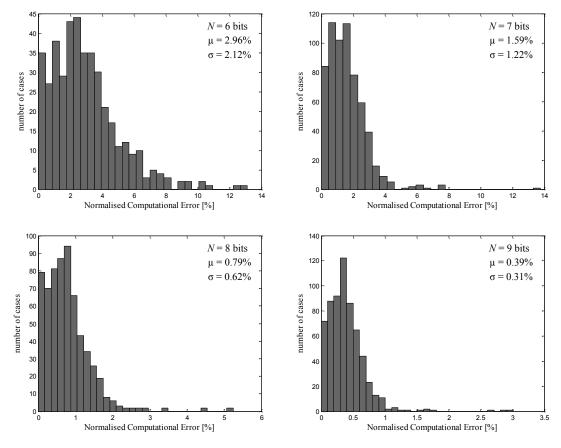

|               |             |              | Computational accuracy                           |     |  |  |

|               |             |              | Digital synthesis and implementation             |     |  |  |

|               | 0.0         |              | Performance of the digital realisation           |     |  |  |

|               | 8.9         |              | rmance comparison                                |     |  |  |

|               |             |              | Analogue implementation                          |     |  |  |

|               |             |              | Digital implementation                           |     |  |  |

|               |             |              | Software implementation for PC                   |     |  |  |

|               | 0.10        |              | Discussion                                       |     |  |  |

|               | 8.10        | Concl        | lusions                                          |     |  |  |

| 9             | Conclusions |              |                                                  | 222 |  |  |

|               | 9.1         | Resea        | Irch summary                                     |     |  |  |

|               |             | 9.1.1        | Binary image processing                          |     |  |  |

|               |             | 9.1.2        | Delay lines                                      |     |  |  |

|               |             | 9.1.3        | Probabilistic reasoning                          |     |  |  |

|               |             | 9.1.4        | Contributions                                    |     |  |  |

|               | 9.2         | Future       | e work                                           |     |  |  |

|               |             | 9.2.1        | Image processing                                 |     |  |  |

|               |             |              | Bayesian inference                               |     |  |  |

|               |             | 9.2.3        | Noise based information processing               |     |  |  |

|               |             | 9.2.4        | Hardware-accelerated network learning            |     |  |  |

| 1(            | ) Ref       | erence       | s                                                | 229 |  |  |

| 10 References |             |              |                                                  |     |  |  |

| 11 Appendix A |             |              |                                                  |     |  |  |

|               | Арр         | bendix       | Α                                                | 246 |  |  |

# Abstract

Computation with Continuous Mode CMOS Circuits in Image Processing and Probabilistic Reasoning A thesis submitted to The University of Manchester for the degree of Doctor of Philosophy Przemyslaw Mroszczyk May, 2014

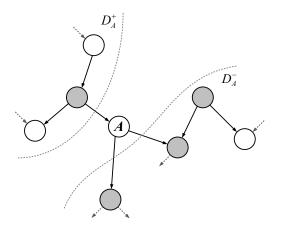

The objective of the research presented in this thesis is to investigate alternative ways of information processing employing asynchronous, data driven, and analogue computation in massively parallel cellular processor arrays, with applications in machine vision and artificial intelligence. The use of cellular processor architectures, with only local neighbourhood connectivity, is considered in VLSI realisations of the trigger-wave propagation in binary image processing, and in Bayesian inference. Design issues, critical in terms of the computational precision and system performance, are extensively analysed, accounting for the non-ideal operation of MOS devices caused by the second order effects, noise and parameter mismatch. In particular, CMOS hardware solutions for two specific tasks: binary image skeletonization and sum-product algorithm for belief propagation in factor graphs, are considered, targeting efficient design in terms of the processing speed, power, area, and computational precision.

The major contributions of this research are in the area of continuous-time and discrete-time CMOS circuit design, with applications in moderate precision analogue and asynchronous computation, accounting for parameter variability. Various analogue and digital circuit realisations, operating in the continuous-time and discrete-time domains, are analysed in theory and verified using combined Matlab-Hspice simulations, providing a versatile framework suitable for custom specific analyses, verification and optimisation of the designed systems. Novel solutions, exhibiting reduced impact of parameter variability on the circuit operation, are presented and applied in the designs of the arithmetic circuits for matrix-vector operations and in the data driven asynchronous processor arrays for binary image processing. Several mismatch optimisation techniques are demonstrated, based on the use of switched-current approach in the design of currentmode Gilbert multiplier circuit, novel biasing scheme in the design of tunable delay gates, and averaging technique applied to the analogue continuous-time circuits realisations of Bayesian networks. The most promising circuit solutions were implemented on the PPATC test chip, fabricated in a standard 90 nm CMOS process, and verified in experiments.

# Declaration

# The University of Manchester PhD Candidate Declaration

Candidate Name: Przemyslaw Mroszczyk Faculty: Engineering and Physical Sciences Thesis Title: Computation with Continuous Mode CMOS Circuits in Image Processing and Probabilistic Reasoning

### Declaration to be completed by the candidate:

I declare that no portion of this work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

Signed:

Date:

# Copyright

The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on Presentation of Theses.

# Acknowledgments

I would like to express my great appreciation to my supervisor Dr. Piotr Dudek for his professional guidance, enthusiastic encouragement and constructive suggestions throughout this research work.

I express my gratitude to my colleagues Dr. Stephen Carey, Dr. Alexey Lopich, Dr. David Barr, Dr. Jayawan Wijekoon, Mr. Bin Wang and Mr. Declan Walsh for their assistance, help and support in this research, and for creating friendly environment.

I would like to extend my thanks to the academic, technical and administrative staff of The University of Manchester for offering me help, resources and assistance, necessary for successful completion of this research.

Finally, I wish to thank my parents (Danuta and Wieslaw) for their strong support, patience and love, and my friends, who greatly contributed to my professional and personal development.

# **Author's Publications**

The work and the results presented in this thesis were in parts subject of the following conference, journal, and poster contributions:

P. Mroszczyk, P. Dudek, "Trigger-Wave Collision Detecting Asynchronous Cellular Logic Array for Fast Image Skeletonization", ISCAS 2012, pp. 2653-2656, May 2012 (Received *Best Student Paper Award*).

P. Mroszczyk, P. Dudek, "Tunable CMOS Delay Gate with Reduced Impact of Fabrication Mismatch on Timing Parameters", NEWCAS 2013, pp. 1-4, Jun. 2013.

P. Mroszczyk, P. Dudek, "Trigger-wave propagation in arbitrary metrics in asynchronous cellular logic arrays", ECCTD 2013, pp. 1-4, Sep. 2013.

P. Mroszczyk, P. Dudek, "The Accuracy and Scalability of Continuous-Time Bayesian Inference in Analogue CMOS Circuits", accepted for ISCAS 2014.

P. Mroszczyk, P. Dudek, "Tunable CMOS Delay Gate with Improved Matching Properties", **IEEE Transactions on Circuits and Systems - I: Regular Papers** (in print), doi:10.1109/TCSI.2014.2312491, 2014.

P. Mroszczyk, P. Dudek, "Asynchronous Cellular Logic Array for Fast and Low-Power Global Binary Image Processing", in preparation for submission to **IEEE Transactions on Circuits and Systems I**.

"Bayesian Inference in Analogue VLSI", UK Neuroinformatics Node, poster presentation, Manchester, UK, Nov. 2011.

"Bayesian Inference in Analogue Networks with Gaussian Noise", Building Bridges to Build Brains, poster presentation, Edinburgh, UK, Nov. 2012.

# **Chapter 1**

# Introduction

### **1.1 Chapter overview**

This chapter discusses reasons for departing from digital computation towards alternative approaches, operating in continuous domains using analogue and various bioinspired ways of information processing. In particular, motivations and key contributions of this research are presented in the field of CMOS hardware design for image processing and probabilistic reasoning tasks. Research summary and the outline of the thesis structure concludes the chapter.

### **1.2 Reasons for alternative approaches**

The application of Boolean logic in solving problems using networks of electromechanical switches, proposed by Claude Elwood Shannon in his Master's dissertation "A Symbolic Analysis of Relay and Switching Circuits" in 1940 [Shannon 38, 40], was one of the major pioneering steps in establishing "digital computing", providing the most reliable and precise way of information encoding and processing ever invented. This work gave foundation for the build of a versatile programmable computing machine (Turing machine), which principles of operation were proposed by Alan Turing [Turing 36] and its particular hardware realisation, known as the von Neumann architecture, was proposed by John von Neumann [von Neumann 45]. Merits of such approach were quickly recognised and electro-mechanical switches were replaced with the best available electronic devices, first valves, and later bipolar and MOS transistors. This began the era of digital computing, the quick development of which, was on one hand propelled by the scientific curiosity and progress in the electronics manufacturing, and on the other, by the political situation in the world, where the applications of new computers, not only in science but also in security and defence, were highly expected. Examples of the most famous constructions from that time are Electronic Numerical Integrator And Computer (ENIAC), built by the scientists from the University of Pennsylvania in 1946, and the Small Scale Experimental Machine ("The Baby") built at the University of Manchester in 1948 as a prototype of a larger computing systems with magnetic data storage [Bowden 53]. In particular, ENIAC could perform about 5000 operations per second with a certain degree of processing parallelism, using several accumulators at the same time for different operations with 10 bit precision. It consumed 150 kW of power and consisted of over 17 000 vacuum tubes, costing an equivalent to 3 million pounds today. Due to the high cost, power consumption and large size, digital computers were solely used for specific scientific and military purposes and access to such devices was rather restricted only to small groups of scientists. The release of the first commercially available programmable 4 bit microprocessor, Intel 4004, by Intel Corporation in 1971, with processing capabilities comparable to ENIAC but consuming only 0.5 W of power [Intel 86], was a milestone achievement in the history of the digital computing. It denoted a new direction for the research and the industry leading to design of cheaper and more power efficient systems based on synchronous digital circuits, where low power consumption and high processing speed could be obtained by transistor size downscaling, and the cost could be reduced by mass production and further MOS process refinement. As a result, MOS technologies evolved, starting from 10 µm down to nearly 10 nm feature size, supported by a highly reliable chip manufacturing processes and a variety of CAD tools for simulation, design and verification of the designed integrated circuits before fabrication.

Due to the long period of development and widespread use of systems based on synchronous digital circuits, such computers could already be called *classical* (term *classical* refers to a typical digital computer based on von Neumann or Harvard architecture, often associated with a single-processor Personal Computers (PCs) executing instructions serially). However, alternative machines, employing different classes of electronic circuits and various ways of information encoding and processing, have always been considered in parallel with the classical solutions. One reason for that, concerning mostly the earliest digital constructions, was the limited processing speed and limited computational capacity of digital systems, unable to solve complex problems required in many practical applications. Another reason was the limited processing efficiency of the digital computers in comparison to the biological nervous systems, inherently dealing with complex tasks while consuming very low power. Therefore, many attempts have been made to mimic the operation of such systems using electronic circuits. In general, the main limitations of digital computers are their high power consumption, low processing speed and large size when compared to the asynchronous or analogue circuit implementations realised in the same technology and dedicated for particular tasks.

For a long time digital computing in CMOS technologies benefitted from the scaling process resulting in improved power efficiency and higher processing speed. In order to build faster and less power consuming computers, practically the same circuit designs, with some minor modifications, could have been used for chip fabrication in the finer technology nodes to achieve the desired effects. The continuous scaling process allowed for implementation of larger circuits on the same chip area, with complexity growing exponentially with time, as suggested by Gordon Moore in 1965 [Moore 65]. This observation, known as Moore's law, became a general scaling rule widely used in science and industry not only to predict the integration level of the future designs but also their speed, power performance, available memory and potential cost. It is obvious, however, that Moore's law is not a generic rule of progress but a self-propelling phenomenon driven by competing corporations trying to maintain reputation and maximise profits. Nonetheless, Moore's law provided a good estimate for parameters of future designs until certain factors, stemming from quantum physics and thermodynamics, started to constrain further performance growth of the CMOS circuits. The main goal of technology feature size miniaturisation is MOS gate capacitance scaling, which on one hand, allows for faster operation but, on the other hand, increases kT/C thermal noise. This, in addition to the reduced supply voltage, affects the operation of digital circuits reducing their statistical reliability. It should be noted that these effects do not constrain the size of a transistor, that can be manufactured, but only suggest to limit either the integration level, or to reduce the clock speed to maintain power dissipation and thermal noise [Kish 2002]. Since device scaling is a very cost-efficient process, the integration level grows exponentially following the Moore's law, however, other measures of performance, such as power and speed have to be compromised in order to meet thermal

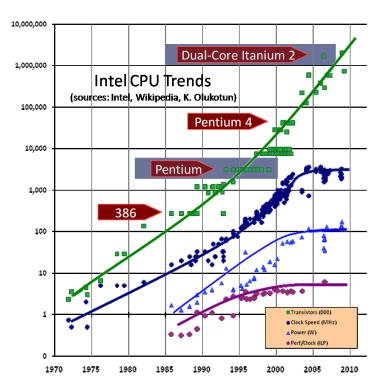

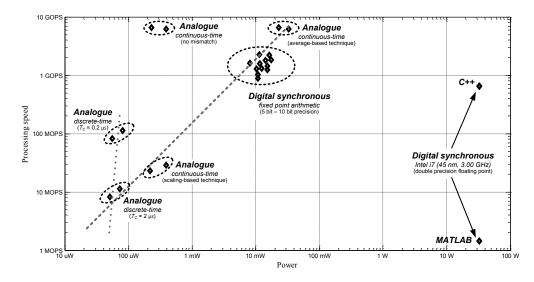

constraints [Gea-Banacloche 2005]. This can be observed in Figure 1.1 showing the scaling trends of Intel processors, where only the number of transistors per chip follows the exponential growth.

Figure 1.1. Scaling trends of Intel chips (green - number of transistors, navy - clock speed, blue - power, magenta - instruction-level parallelism), figure taken from [Shutter 2005].

Further scaling of the CMOS technologies will most probably continue for the next several decades, and will not be quickly replaced by any other known approach on an industrial scale. It is yet too early to assess to what extent novel propositions, based on graphene, single electron, or polymer transistors, will provide satisfactory solutions. At present, classical computing relies on CMOS technology and digital circuits operating close to their thermodynamic limits. Therefore, faster processing is usually attempted by novel programming techniques and better utilisation of the resources using multi core processors. In particular, better integration of the memory and CPU has been suggested to overcome so called *von Neumann architectural bottlenecks* [Backus 78], for example, by employing massively parallel *cellular* processor architectures, with only local or nearest neighbourhood connectivity, associative memories, and processing circuits optimised for particular tasks. Further performance boost is also searched for in the systems using asynchronous and analogue circuits, or even employing other ways of representing and processing information.

## **1.3** Alternative ways of information processing

In the following section more detailed review of the alternative processing methods, such as analogue computers, artificial neural networks and stochastic machines, will be provided. In particular, aspects concerning hardware design challenges and limitations, essential to the research presented in this theses, will be discussed.

### **1.3.1 Analogue computers**

Early realisations of digital computers were not fast and elaborate enough to handle complex mathematical models described by large sets of differential equations. On the other hand, it was observed that many such systems could easily be modelled by analogue circuits with passive and active elements. Since the parameters of the circuits can be tuned, they could inherently solve a set of equations while settling down to the steady state. Such analogue computers were popular even before the invention of the digital machines and used in many areas requiring system modelling and simulations, such as in real time power network simulations [Joetten 85], in nuclear physics experiments [Arbel 64], and in various control applications [Bissell 2004]. Examples of such generic analogue computers used for solving differential equations and system modelling are Newmark (1960, Cambridge, UK) and ELWAT-1 (1967, Wroclaw, Poland). In particular, there were 50 units of ELWAT-1 manufactured by Elwro company in Wroclaw (Poland) between 1967 and 1969 [Sienkiewicz 2009]. Each computer consisted of 19 valve operational amplifiers, 12 computational blocks for summation, differentiation and integration, one multiplier and 4 function generators, and operated with a precision of 0.1% to 5%, displaying the results on an oscilloscope or printing traces on a paper tape. For a long time such analogue computers were competitive with the digital ones in terms of speed and the complexity of the problem, that could be solved. However, relatively low precision, low dynamic range and strong dependency of the circuit parameters on temperature, precluded their use in many applications. Even though the motivations for using analogue circuits in computation and modelling were driven solely by the lack of alternative solutions at that time, or by a low speed and high cost of the early digital computers, the idea was not entirely abandoned after the rapid improvement of the digital computers. It returns as an alternative for classical computers in very complex applications such as bio-inspired processing systems and massively parallel processor arrays.

#### 1.3.2 Artificial neural networks

Biological nervous systems are in many ways similar to electronic circuits, where the information is processed and transmitted between conductive neurons using electric charges. Given the very low power dissipation of the human brain, estimated to be about 20 W [Kish 2011], high complexity, and real time operation, the computational efficiency of such biological computers is much higher than the ones achieved using electronic circuits. One of the characteristic features adopted by nature in nervous systems is the high degree of redundancy in the hardware structure and in the information encoding scheme [von Neumann 52]. Such networks typically consist of a large number of neurons working in parallel to collect, process and exchange information with each other. Redundancy and parallelism assure high reliability of the system and its immunity to parameter fluctuations. This distinguishes them from typical electronic circuits, where failure of one component typically leads to an imminent failure of the whole system. One of the early attempts to improve understanding of the operation of neural networks was done in early 1940s by Warren McCulloch and Walter Pitts, who proposed a very simple mathematical model of neuron operating in a binary mode with Heaviside step activation function, used to the threshold sum of the active input signals [McCulloch 43]. A more elaborate model of perceptron was later proposed by Frank Rosenblatt in 1958 [Rosenblatt 58]. These works, among others, gave foundation for different types of artificial neural networks (ANN), such as multi-layer feed-forward networks and feedback networks as described in [Hecht 90]. Notable types of ANN are Hopfield networks [Hopfield 84] and cellular neural networks (CNN) [Chua 88a, 88b], [Roska 93]. In particular, VLSI implementations of CNN became popular due to their regular two-dimensional structure and only near neighbourhood connectivity between neurons. There are a number of propositions for hardware implementations of such networks, mainly using nonlinear analogue VLSI circuits, operating in continuous and discrete time modes, or specific high performance parallel digital implementations [Kinget 97]. It should be noted that analogue design in this area is very promising since many problems can be solved using dedicated circuits [Mead 89]. Examples of such circuits are single transistor multipliers based on the floating gate technique used as programmable weighted synaptic connections between neurons [Dominguez-Castro 98], rank-order extractors for winner-take-all networks [Hung 2002], and various nonlinear function realisations [Chang 96a].

In analogue networks, information is typically represented by an electric charge measured either as a voltage, when stored on a capacitance, or as a current, when flowing through a conducting element. This is sometimes used to differentiate between circuits operating in the current or voltage mode. However, such classification is rather conventional since the operation of any circuit requires constant transitions between current and voltage domains. [Toumazou 93b].

In biological neural networks, the information is carried by trains of electrical pulses (spikes) where the rate or probability of the pulse occurrence, measured over a period of time, or a correlation between trains of spikes, correspond to the information encoded by the signal. This shows the redundancy of biological systems not only in terms of the hardware but also in terms of the information encoding. Such systems require processing methods different from those used in the conventional electronic circuits [Kinget 97]. Following this approach, a separate class of electronic circuits, dedicated for the Spiking Neural Networks, have been proposed [Maass 2001]. Such circuits combine the processing methods of digital and analogue solutions and operate similarly to the asynchronous circuits, processing discrete signals (e.g. digital pulses) but in continuous time and representing continuous (analogue) values.

### **1.3.3 Stochastic computers**

The probabilistic nature of the signals observed in biological neural networks was an inspiration to the design of specific type of arithmetic machines, considered already in 1960s, as an alternative to the analogue computers [Riberio 67], [Poppelbaum 67], [Gaines 67]. In the design of such stochastic computers it was assumed that the continuous variables could be represented as sequences of random pulses with probability proportional to an analogue value. Simple logic operations performed on such sequences correspond to inherent arithmetic operations on the probabilities. For example, if two random sequences of pulses are generated with probabilities p and q, the logical AND operation on these signals will generate a sequence with probability equal pq [Riberio 67]. Using more complex structures with logic gates, delay elements and memory circuits, different arithmetic operations such as addition, subtraction, multiplication, division, square root, integration and differentiation with respect to time or other variable, can also be realised [Gaines 67].

Stochastic computers operate according to very simple principles, however, their circuit realisations required additional hardware blocks such as generators of random

pulses with controlled probability distribution and signal randomisers. The generators were necessary to convert the analogue input signals to the sequences of random pulses. The randomisers had to be used to restore the statistical properties of the intermediate signals after each processing step [Riberio 67]. Since the computation is based on stochastic processes, the result converges to the expected solution, however, with limited precision depending on the length of the produced sequence. It has been shown that the precision of an analogue value represented by a random pulse string is proportional to the square root of the sequence length. In order to assure precision of 1% the sequence should consist of 10,000 pulses, and this length will have to increase by 100 times if the required precision is 0.1%. Even if longer sequences could be generated, due to the stochastic nature of the process, the probability of unforeseen random disturbances will gradually increase degrading the achievable precision [Poppelbaum 67]. The use of stochastic computers have been suggested in image transformers and artificial neural networks [Petriu 96]. They are promising alternatives to classical computers that could be considered in future designs, where moderate precision is sufficient. The use of modern CMOS technologies may facilitate some solutions to the aforementioned design challenges, seen as unsolvable at the time when the integrated circuits were not widely in use. It should be noted, however, that issues regarding area, power consumption and scalability of such stochastic machines in CMOS need investigation.

The idea of processing continuous random signals (i.e. noise) to evaluate logic functions has been proposed to address the problem of thermal noise in the modern CMOS technologies [Kish 2011]. Such techniques rely on the correlated noise information processing and are immune to the presence of the uncorrelated thermal noise. In principle, the statistical parameters of random orthogonal signals are used to encode logic state. In the processing, electronic circuits such as multipliers, low pass filters and switches, can be used to perform logic operations on the noise signals. Such systems, however, require analogue circuits operating in a very high bandwidth, to attain the processing speed comparable to existing computers and more complex hardware realisations of logic gates. It should be noted that there exist other approaches to stochastic data processing using probabilistic CMOS computers [Korkmaz 2008] or machines going beyond the scope of electronic circuits such as quantum computers [Shor 94]. Due to very specific principles of operation, the application domain of such computers is still limited.

### **1.4 Motivations**

The main motivation for the research presented in this thesis is to address issues and challenges in the design of cellular processor arrays in standard CMOS technologies with applications in fast and power efficient image processing and probabilistic reasoning tasks. In particular, asynchronous and analogue circuits are of the main interest, since they can inherently solve many computationally demanding tasks faster and more efficiently than classical computers.

The work undertaken in this research consists of two parts. The first part considers the use of asynchronous pixel-parallel processor arrays in morphological operations on binary image, supported with the experimental results obtained from the fabricated test chip. The second part considers the use of the continuous-time and discrete-time analogue processor arrays for a particular set of matrix-vector operations required in loopy belief propagation algorithm for approximate inference in Bayesian networks. Aspects, such as processing speed, computational accuracy under fabrication mismatch and efficiency, accounting for power and area requirements, and scalability of such solutions with network size were investigated. In addition to that, equivalent synchronous digital circuits and software solutions on PC, were devised to provide the reference for comparison of the analogue and digital systems in terms of speed, power, area and computational efficiency.

## **1.5 Research overview**

The progress of research work is not predictable and many initial assumptions, ideas and expectations for potentially promising results has to be revised, modified and sometimes abandoned. On the other hand, those unexpectedly encountered obstacles, triggered new ideas and solutions, splitting the research into new branches or even changing its main direction. In order to keep this thesis concise and consistent, some ideas and conclusions, that go slightly off the track, although interesting and certainly valuable, were not included but briefly summarised in the last chapter providing ideas and directions for future work. The outline of the research presented in this thesis indicating its turning points, encountered problems and proposed solutions, is presented further in this section.

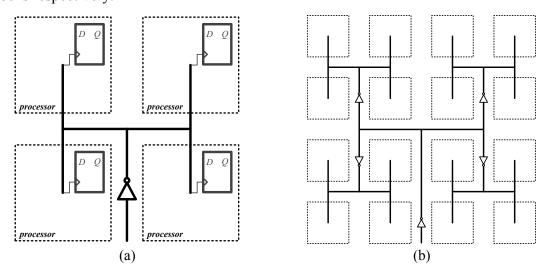

#### 1.5.1 Binary image processing

The idea of binary image processing using trigger-wave propagation concept was initially inspired by the properties of the light-sensitive chemical nonlinear system (a variant of the Belousov-Zhabotinski medium) capable of generating chemical reactions in the form of propagating wave-fronts when stimulated by light [Kuhnert 89], [Krinsky 91]. In literature, such systems are typically realised using asynchronous CMOS cellular processor arrays with applications in morphological image processing task such as geodesic reconstruction, hole filling, etc. [Dudek 2006].

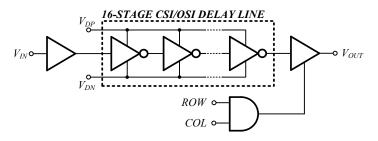

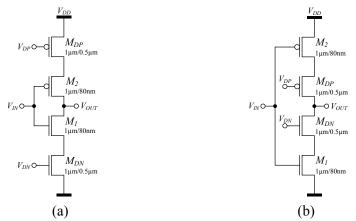

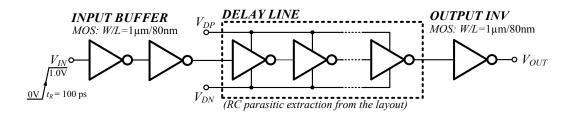

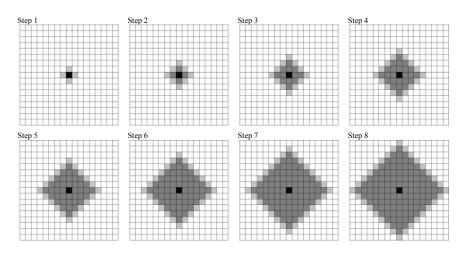

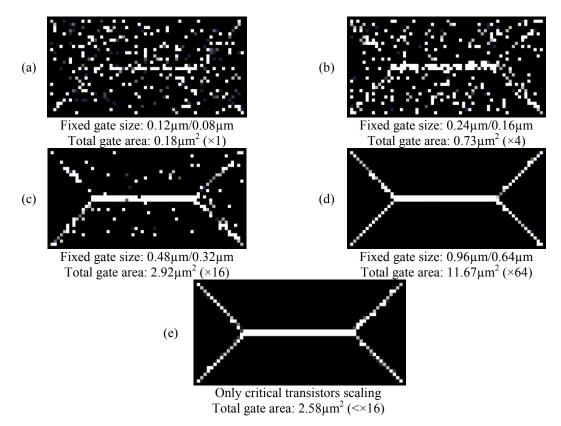

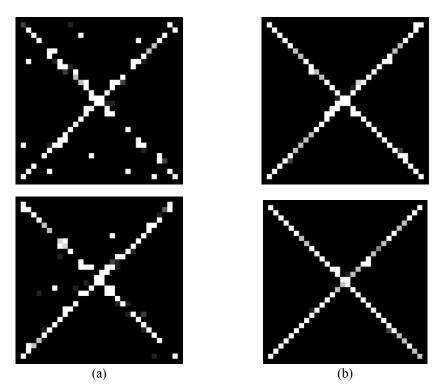

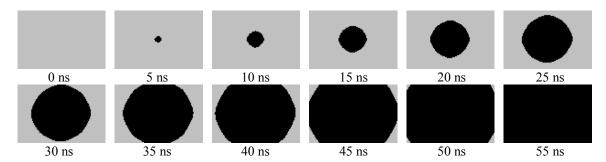

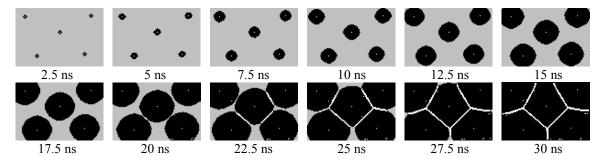

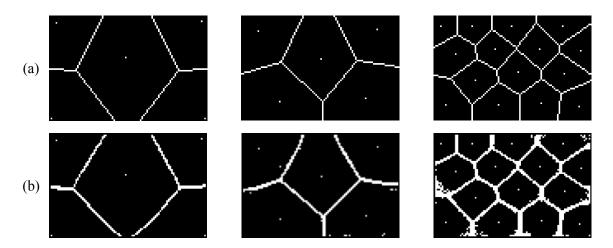

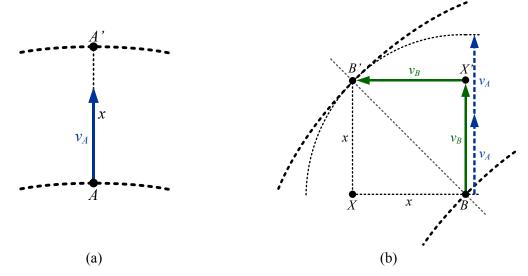

The primary goal of the research was to use such arrays to evaluate skeletons of binary images by implementing a mechanism to detect collisions between the propagating waves. In such a system, it is essential for each processing cell to compute results within a short and precisely defined period of time. Since there is no time reference (e.g. clock signal) available in such asynchronous system, the idea was to implement a simple delay gate generating the required time interval on the arrival of the input data in each cell. By using a simple delay circuit based on a three-transistor current starved inverter, very satisfactory simulation results were obtained. However, when accounting for the parameter variability of MOS transistors, significant problems with the precision of the generated time intervals were observed, affecting the quality of the extracted images. This problem was solved by selective transistor scaling, where only critical transistors in terms of the timing parameters were enlarged. It was also observed that replacing the current limiting transistor with the switching one, in the delay gate circuit, slightly changed the dynamic behaviour of the gate, reducing the impact of the parameter variability on the generated time intervals. Such a gate has the current limiting transistor in between the switching ones *splitting* the output of the inverter, therefore, it is called output split inverter (OSI). The idea was further pursued in isolation from the image processing framework, and eventually evolved into a separate research subject of tunable delay lines with improved matching properties, applicable in delay locked loops, time to digital converters, readout systems for particle detection and neuromorphic circuit design.

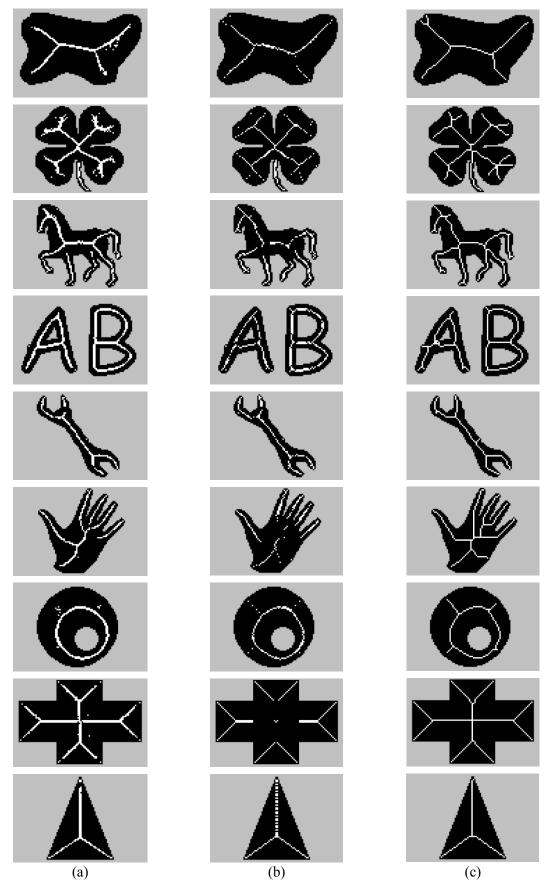

In order to verify and optimise the operation of the designed system, investigate its asynchronous behaviour, timing parameters and dynamic operation, simulations of the actual circuit arrays rather than of a single processing cell were required. It seemed necessary and convenient to provide the inputs and represent the results of the simulations in the form of binary images rather than time dependent signal traces. For this purpose, a separate set of tools was built in Matlab and C++ to communicate with Hspice circuit simulator and visualise the obtained results as a sequence of binary images. This allowed to perform the mismatch optimisation of the array and also aided investigating and solving problems related to current leakage, design asymmetry and initialisation process, not easily detectable at the processing cell level.

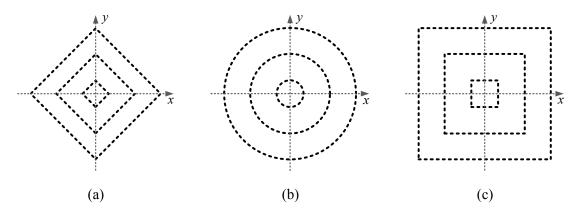

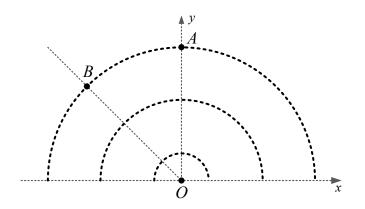

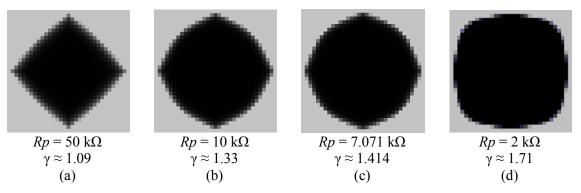

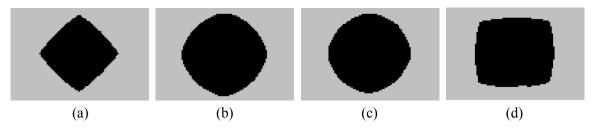

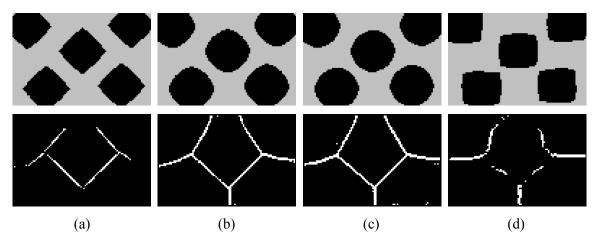

It was also observed that slightly different contours of the waves triggered from a single pixel can be generated depending on the timing parameters of the gate array. The theory behind this was further investigated based on the simplified switched *RC* timing model, generalising the principles of isotropic wave propagation in rectangular arrays in the context of particular distance measure norm. The results of this research were applied in the design of the asynchronous processor array, capable of generating circular propagation waves, significantly improving the quality of the evaluated skeletons and Voronoi diagrams, difficult to implement in synchronous circuits or even in software adaptations of the propagation-based image processing method.

#### **1.5.2 Bayesian inference**

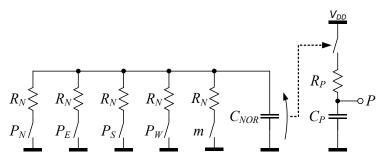

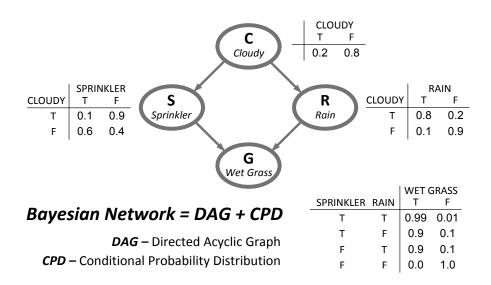

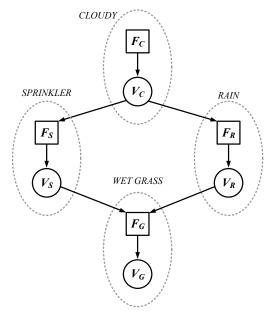

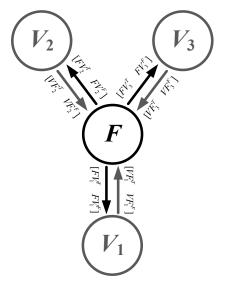

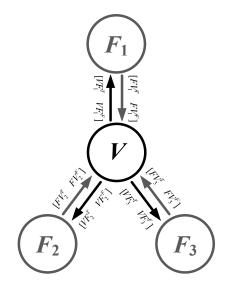

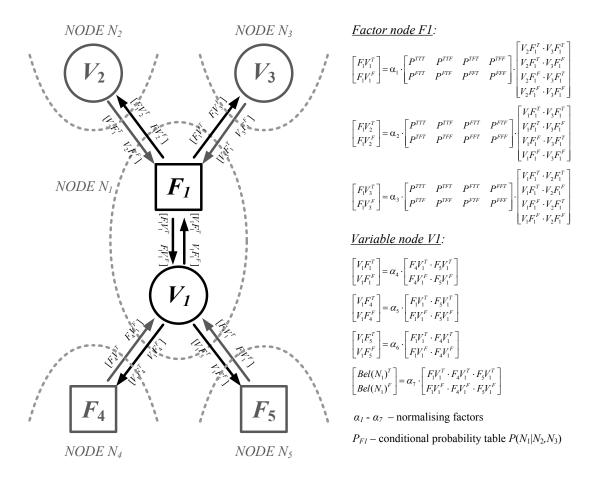

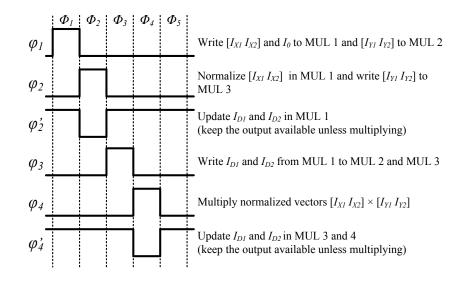

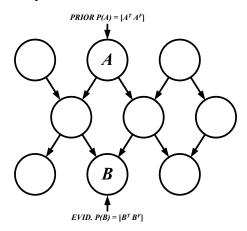

Bayesian inference in networks representing systems with cause-effect relationships is often used in the applications requiring control, decision making, diagnoses and forecasting [Pearl 86, 88], [Jensen 2007]. In general, methods for exact inference are classified as NP-hard problems [Cooper 90], therefore, a lot of attention has been paid to the simplified methods for approximate reasoning such as loopy belief propagation and stochastic sampling [Neapolitan 2004]. In particular, belief propagation, relies on the repetitive information exchange between the nodes, using only locally available data in calculating probabilities. The algorithm performs algebraic operations including matrixvector and vector-vector multiplications on the discrete probability distributions. In order to avoid underflow errors, belief propagation assumes normalisation of the computed probability distributions after each processing step. This, however, requires additional summations and divisions, increasing the computational complexity of the algorithm.

Despite extensive literature concerning principles of Bayesian inference by exact and approximate methods, the area of their hardware implementations is not well explored and limited to only a few publications. The idea of using sum-product algorithm in factor graph implementations in analogue CMOS circuits, for the realisation of loopy belief propagation, was initially proposed in [Kschischang 2001]. This approach was further

followed in [Luckenbill 2002], reporting very low computational accuracy achieved in such circuit realisations, however, relying on circuit simulations of a network with only three nodes and using generic BSIM3 MOS transistor model, not related to any technology. To the best of my knowledge, these are the only practical analogue circuit realisations, apart from several works considering Bayesian inference in spiking neural networks [Corneil 2012] and in digital domain using VLSI [Liang 2011] and field programmable gate arrays (FPGA) [Lin 2010], [Kulesza 2006]. Therefore, the primary motivation of this work was to revise the approach to Bayesian inference in analogue CMOS circuits, and propose a clear formalism in a consistent framework, providing the reference and the foundation for future research in this area.

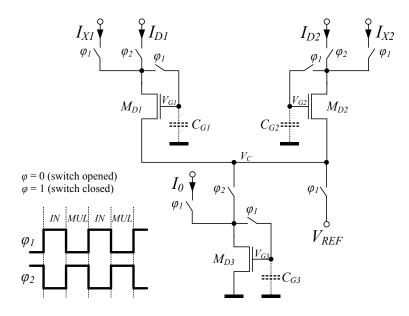

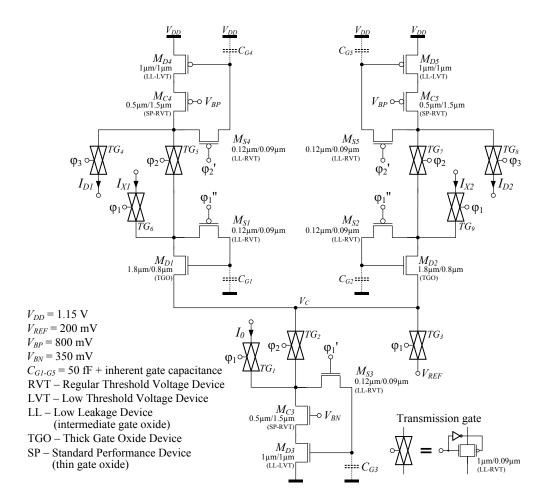

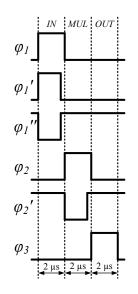

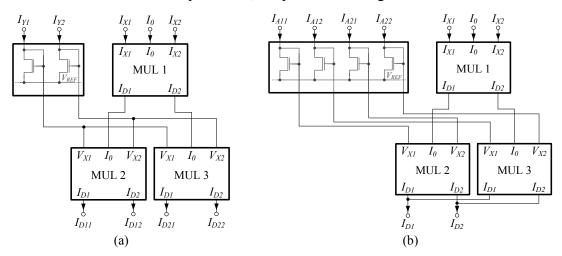

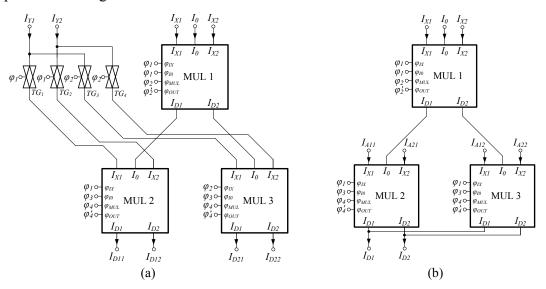

In this thesis, the analogue circuits for arithmetic operations were implemented using CMOS realisation of the Gilbert multiplier, operating in continuous-time and discretetime domains [Toumazou 93b]. The operation of such circuits was thoroughly analysed in theory and verified in simulations using BSIM4 MOS transistor models provided by the foundry. In particular, the operation of the continuous-time multiplier was verified using the author's simplified equivalent model V-AMS, built in Verilog AMS language, to account for second order effects in MOS transistors operating in weak inversion. It was observed that the computational errors result mainly from the channel length modulation effects and from the variable slope factor. These problems were addressed by employing cascode current mirrors, single stage differential pairs (to assure operation in saturation within the limited voltage headroom), and MOS transistors with different threshold voltages, to reduce the leakage currents. The optimised design of the multiplier was used to realise the matrix-vector and vector-vector operations in more complex arithmetic structures, required in the sum product algorithm. Based on that, scaling rules considering circuit complexity and power were derived.

At that stage it was also necessary to develop methods for quick verification of the simulation results and the computational accuracy of the implemented networks. To address this, a separate set of tools for Bayesian inference was built in Matlab. The verification of a particular Bayesian network implemented in analogue circuit, for a given set of input parameters, was performed using scripts for combined Matlab-Hspice simulations, where the inference results obtained from the circuit and software were used to evaluate the computational error. This allowed to further verify the operation and scalability of the circuit realisations of larger networks.

As was initially expected, accounting for the fabrication mismatch of MOS transistors resulted in a significant degradation of the computational accuracy, calling into question any practical use of such circuits. This concluded the preliminary stage of the research giving directions to design of more precise analogue systems for arithmetic operations. It brought attention to the parameter variability issues, setting the next research objective, which was to investigate possible ways of mismatch reduction and optimisation in such analogue circuits.

Several attempts to solve this problem were made, accounting for MOS transistor scaling, network parameters optimisation, redundant design approach and also migration to switched-current (SI) mode. The main disadvantage of the first method, based on enlarging the size of MOS transistors, was a significant increase of the circuit area and settling time. The idea of tuning network parameters to compensate for the parameter mismatch was initially adapted from neural network systems, where inaccuracies of neurons and synapses can be reduced by proper weight adjustment. Unfortunately, this concept failed because of relatively small number of network parameters, as compared to the number of MOS transistors used in the implementation. Another idea, benefiting from the design redundancy was based on the hypothesis that collecting and averaging results from several identical networks (affected by random parameter variability), will generate more precise result. This idea was successful on the simulation level, however, in order to obtain results with acceptable accuracy, large number of uncorrelated network copies were required, practically precluding the use of this technique in CMOS realisations.

Migration to switched-current mode was attempted due to the very high immunity of such circuits to fabrication mismatch reported in literature. It was done based on the observation that the continuous-time Gilbert multiplier can be realised using discrete-time current mirrors The proposed idea was successful and the operation of the SI version of the multiplier, and two Bayesian networks consisting of 5 and 7 nodes were verified in simulations, giving promising results for the computational accuracy, efficiency, and power.

Since the assumed realisation of such systems is fully parallel, each arithmetic operation has its individual hardware block, which leads to a large area occupation. One idea to address this issue is to employ time multiplexing of the resources and serialise the processing flow. Another possibility is to investigate the hardware realisations of stochastic methods for approximate Bayesian inference, such as Gibbs sampling and

stochastic logic sampling. Such methods require less arithmetic operations per node than belief propagation, however, the hardware realisation of the random generators is still an open problem. So far, certain solutions for hardware random bit generators, based on amplified thermal noise [Wee 2001], metastability [Vasyltsov 2008], and analogue chaos generators [Dudek 2003] have been proposed.

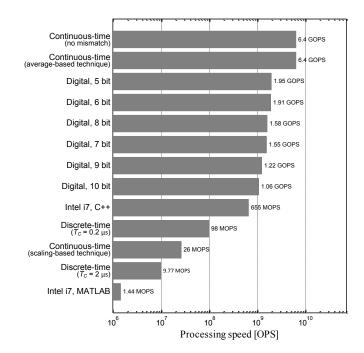

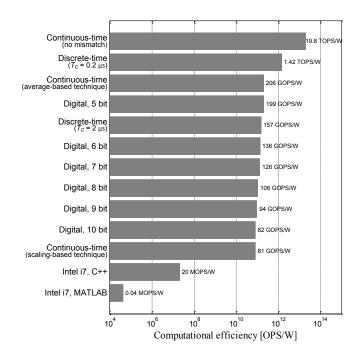

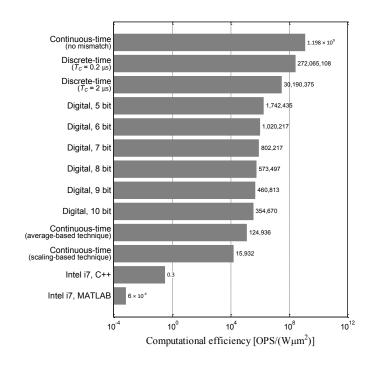

In this research, the results obtained from the continuous-time and discrete-time realisations of Bayesian networks were compared with their equivalent implementations in synchronous digital circuits operating in fixed point arithmetic with different bit precisions from 5 to 10 bits, and with software solutions realised in Matlab and C++. The objective of this comparison was to provide an overview and performance measure of three different approaches to the same problem realised in the same CMOS technology node using, in each case, non-trivial and optimised solutions.

# **1.6 Contributions**

The major contributions of the research presented in this thesis are:

- Analysis and design of the collision detecting layer for trigger-wave propagationbased image processing algorithms in dynamic logic CMOS circuit combining logical AND function and 1 bit memory latch, using only 8 MOS transistors.

- Analysis and design of the propagation gate for trigger-wave propagation-based image processing algorithms with a novel bias scheme allowing for the generation of the circular wave contours, difficult to achieve in software or using generic SIMD processor arrays.

- Analysis and design of a delay gate employing a novel biasing scheme resulting in almost twice better matching properties when compared to the commonly used current starved inverter, with no penalty in terms of power or area.

- Analysis and design of the analogue CMOS discrete-time variant of the Gilbert multiplier, operating in current mode with computational accuracy comparable to its continuous-time equivalent but not affected by parameter mismatch.

- Analysis and design of an optimised digital fixed-point arithmetic circuits for matrixvector operations with applications in probabilistic calculus and other areas requiring computation with normalised data.

- Analysis of the power, area and complexity scaling of the hardware realisations of the factor graphs for belief propagation in analogue circuits.

Development and verification of the mismatch optimisation techniques based on the novel biasing scheme (OSI delay gats), results averaging (Bayesian networks in analogue continuous-time circuits) and switched-current technique (discrete-time current-mode multipliers).

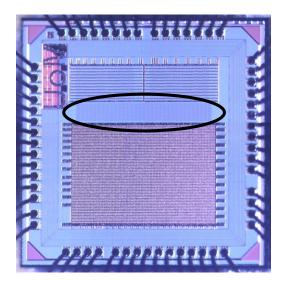

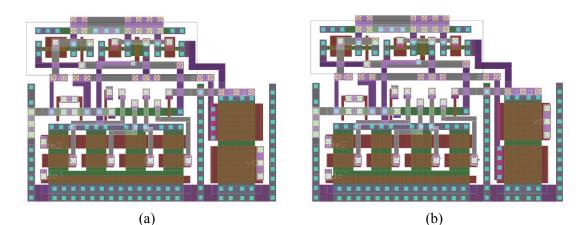

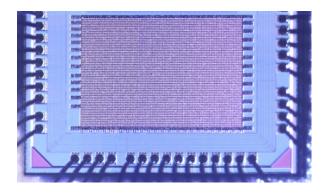

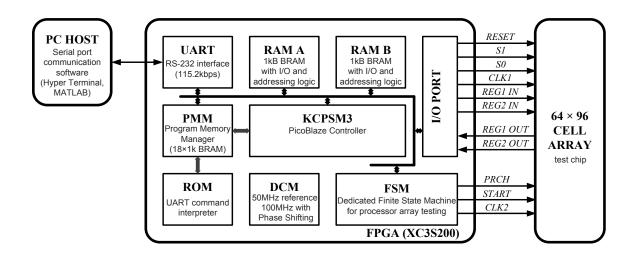

In addition to the undertaken research, the most promising and successful circuit ideas were implemented on a test chip, fabricated using a standard 90 nm CMOS technology available through mini@sic program supervised by EUROPRACTICE. The layout of the PPATC chip (Parallel Processor Arrays Test Chip) was created in the full custom approach. The design was submitted for fabrication in November 2012 and the fabricated chips were received from the foundry in April 2013. The size of the PPATC chip was 1875  $\mu$ m × 1875  $\mu$ m including I/O ring and 64 pads, and accommodated three separate test designs:

- asynchronous logic array for binary image skeletonization and Voronoi tessellation (64 × 96 pixels),

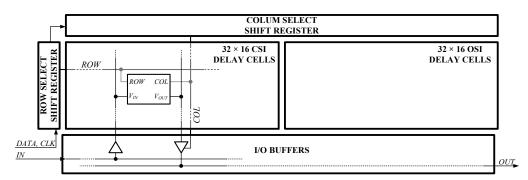

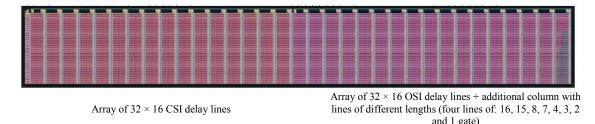

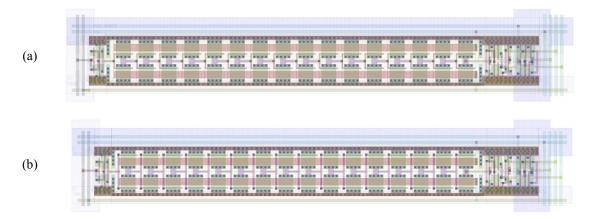

- two arrays of 512 16-stage delay lines each implemented using current starved inverter (CSI) and output-split inverter (OSI) delay gates,

- two analogue processor arrays with various types of memory cells and Gilbert multipliers operating in switched current mode, dedicated for applications in Bayesian inference.

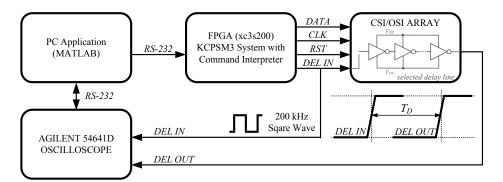

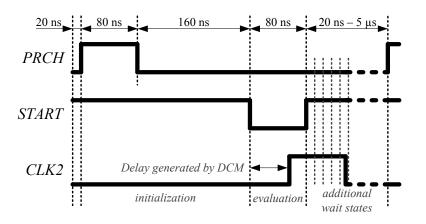

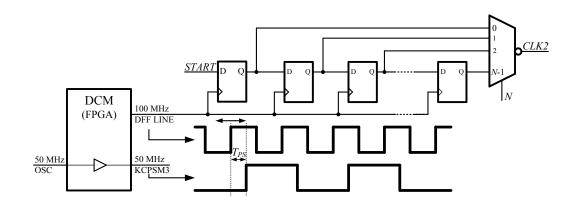

In order to test the fabricated chip, a separate test system based on Xilinx PicoBlaze (Kcpsm3) microcontroller was designed and implemented on a Development Board from Digilent, with Spartan 3 xc3s200 FPGA, operating in a command interpreting mode and providing a communication link between a PC and the PPATC chip. This thesis includes experimental results obtained from tests of the asynchronous logic array for binary image processing and delay line arrays.

### **1.7** Thesis structure

The background knowledge and the literature review concerning the analogue computation in CMOS circuits and a detailed discussion on parameter variability, are presented in Chapter 2. The analysis and design of the continuous-time and discrete-time current-mode analogue multipliers is presented in Chapter 3. The idea, analysis and the

obtained experimental results, concerning the operation of the OSI delay gates with improved matching parameters, are presented in Chapter 4. Chapter 5 provides an introduction to binary image processing based on the trigger-wave propagation concept, presents the proposed idea of detecting collisions, and discusses the obtained simulation and experimental results. Chapter 6 extends this discussion to propagation in arrays operating in different distance measure norms. An introduction to probabilistic reasoning, Bayesian networks and belief propagation is provided in Chapter 7. Various realisations of belief propagation algorithm, in analogue and digital systems, and the corresponding comparative analysis, is provided in Chapter 8. Chapter 9 concludes the thesis and discusses future work. Additional information concerning schematic diagrams and scaling rules of the analogue hardware for Bayesian inference is provided in Appendices A and B.

# **Chapter 2**

# Computation with MOS transistors under parameter variability

# 2.1 Chapter overview

This chapter provides a background knowledge and the literature review on the computation in analogue circuits using MOS transistors and employing their switching capability, nonlinear characteristics and information storing properties. A detailed discussion will concern circuits such as analogue multipliers and switched-current memory cells, used in the realisations of the circuits considered in this research. Since the operation of the analogue and asynchronous circuits is highly determined by the accuracy of the fabricated hardware, the major part of this chapter deals with mismatch analysis, modelling and optimisation, providing foundation for CMOS circuit design discussed in this thesis.

### 2.2 Analogue computation with MOS transistor

The function of MOS transistors in circuits for arithmetic operations is determined by the form of the arguments and the principles of computation employed. In digital domain, the computation on binary numbers is done using logic circuits with MOS transistors operating as switches. In such circuits, the dynamic behaviour of transistors during signal transitions and their nonlinear transfer characteristics, are usually not considered, unless the timing constraints of the designed system are affected. In the analogue computing systems, the continuous arguments are represented by the magnitude of voltage or current, and the arithmetic operations such as addition, subtraction, integration etc., can be realised using linear *RC* circuits with operational amplifiers, where characteristics of MOS transistors are of second importance [Razavi 2001], [Allen 2002]. Such circuits are often used in communication, data converters and analogue signal processing, and are not frequently considered in the realisations of complex computing systems. This is mainly because of the high power and the large area requirements of the operational amplifiers.

In order to reduce the area and power consumption, and to accelerate the processing speed, circuits employing inherent features of MOS transistors (e.g. capacitance of the insulated gate, nonlinear transfer characteristics) are usually considered. In such approach, the mathematical relations between the drain currents and the gate, drain and source voltages, of a MOS transistor, depend on the operating point, and can be used in the realisations of different arithmetic operations, like addition, multiplication, division or log-linear conversion. There are a number of challenges in the design of such circuits, mainly stemming from biasing, dynamic range, noise and fabrication mismatch.

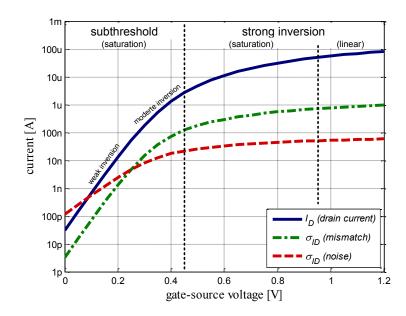

In the literature, fabrication mismatch and noise are often reported as the dominant factors affecting the operation of analogue circuits. Transfer characteristics of a MOS transistor, showing drain current  $I_D$  and the RMS values  $\sigma_{ID}$  (standard deviations) of the noise and the fabrication mismatch versus gate-source voltage, are presented in Figure 2.1. It can be observed that the variability of the drain current, resulting from mismatch, depends on the operation region and is nearly one order of magnitude higher than the variability caused by noise, when operating in strong inversion. In the designs assuming the operation of MOS transistors in weak inversion, both noise and mismatch should be taken into account. In particular, the exponential dependency of the drain current on the gate-source voltage magnifies the impact of parameter mismatch on the circuit performance. Also, a very small drain current in weak inversion approaches the noise level, reducing the dynamic range and degrading signal to noise ratio in the circuit. Nevertheless, the operation in weak inversion is often necessary, since the technology scaling imposes lower supply voltages, which leaves less headroom for the operation in strong inversion. Also, in weak inversion, the approximate exponential transfer characteristics are beneficial in the realisations of some arithmetic operations.

Figure 2.1. Drain current of MOS transistor and the RMS currents related to noise and fabrication mismatch vs. gate-source voltage (simulation results obtained using low-leakage MOS model from a 90 nm CMOS tech. assuming  $W = 1 \mu m$  and  $L = 1 \mu m$ , threshold voltage  $V_{th} = 0.45 V$ , constant drain-source voltage  $V_{DS} = 0.5 V$ , and gate-source voltage swept in range 0 - 1.2 V).

In the following section, an overview of different ideas utilising the inherent features of MOS transistors in the realisation of arithmetic operations in analogue circuits will be presented. In particular, switched-current circuits, advantageous in terms of mismatch immunity and various realisations of analogue multipliers, will be discussed. The discussion will be proceeded by a brief introduction to the simplest MOS transistor model, based on the quadratic law (Spice Level 1), frequently used in analyses and hand calculations. The remainder of this chapter focuses on parameter variability in CMOS technologies, statistical models of MOS transistors, and mismatch optimisation techniques.

### 2.2.1 MOS model for hand calculations

In literature, theoretical analyses of CMOS circuits typically assume the use of the simplest MOS transistor model based on the square-law transfer characteristic, when operating in strong inversion [Shichman 68]. Such model was a sufficient analysis tool for hand calculations and computer simulations (known as Spice Level 1 model), useful in modelling circuits designed in CMOS technologies above 1  $\mu$ m feature size. In its basic form, it considers only four electrical parameters: threshold voltage  $V_{th}$ , current factor  $\beta$ , body effect parameter  $\gamma$ , and channel length modulation  $\lambda$ , which depend on the physical parameters of semiconductors [Allen 2002]. In order to simplify the analyses,

the body effect and the channel length modulation are usually not accounted for in the hand calculations, and that the bulk-source voltage equals zero (i.e. source is electrically connected to bulk). Such model describes the relations between the drain current  $i_D$  and the bias voltages  $v_{GS}$  and  $v_{DS}$  in strong inversion (when  $v_{GS} > V_{th}$ ) in two regions: saturation, when  $v_{DS} \ge v_{GS} - V_{th}$  and linear when  $v_{DS} < v_{GS} - V_{th}$ , and is given by the following equations:

$$i_D = \frac{\beta}{2} (u_{GS} - V_{th})^2$$

, in saturation region where:  $u_{DS} \ge u_{GS} - V_{th}$  (2.1)

$$i_D = \beta \left[ \left( u_{GS} - V_{th} \right) u_{DS} - \frac{u_{DS}^2}{2} \right], \text{ in linear region where: } u_{DS} < u_{GS} - V_{th}$$

(2.2)

The current factor (also called large signal transconductance)  $\beta = \mu C_{ox} W/L$ , depends on the gate oxide capacitance  $C_{ox}$ , carrier mobility  $\mu$  and the device geometry defined by the channel width W and length L.

An extension to this model, accounting for the subthreshold operation in weak inversion, when  $v_{GS} \leq V_{th}$ , assumes the exponential dependency of the drain current on the gate-source voltage according to the equation [Allen 2002], [Mead 89]:

$$i_D = I_{D0} \frac{W}{L} \exp\left(\frac{u_{GS}}{nU_T}\right)$$

(2.3)

where  $I_{D0}$  is a specific current in weak inversion, W and L are the channel width and length respectively,  $U_T = kT/q$  is thermal voltage (equal approximately to 25.85 mV at a room temperature T = 300 K), and n is a subthreshold slope factor, depending on the gate oxide capacitance  $C_{ox}$  and the depletion layer capacitance  $C_{dep}$ , according to relation:  $n = 1 + C_{dep}/C_{ox}$ . In small signal analysis, the slope factor n can be treated as constant and equal to a real number from interval 1 to 3 [Allen 2002]. In general, the slope factor n is in a convoluted relation with  $u_{GS}$ ,  $C_{dep}$  and  $C_{ox}$ , therefore, in a large signal analyses, it should be considered as a function of gate-source voltage, rather than a constant parameter [Toumazou 93b], [Mead 89]. The consequences of this effect will be further investigated in Chapter 3, when discussing the computational errors of CMOS multipliers.

Despite the limited accuracy of this model, equations (2.1) - (2.3) can be used in hand calculations providing results and conclusions useful for further circuit

optimisation, using more precise models such as BSIM (Berkeley Short-channel IGFET Model [Sheu 97]) and dedicated CAD tools.

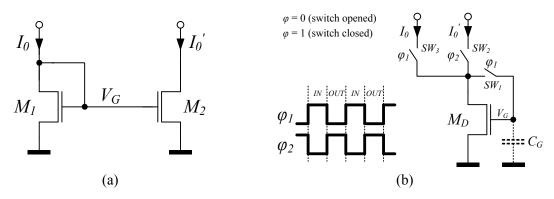

#### 2.2.2 Switched-current circuits

Computation in switched-current circuits typically employs memory cells for information storing and arithmetic operations. In such circuits, the information is represented by a current, which flows to the drain of a diode-connected transistor programming the gate voltage. After that, the gate disconnects from the drain and the transistor operates as a source generating the programmed current. Apart from the information storing purpose, such memory cells can also be used in the realisations of simple current-mode arithmetic operations such as addition, subtraction, multiplication and division by an integer number [Toumazou 93a, 93b].

There are many design challenges reported in the literature related to the realisations of SI circuits, such as charge injection, channel length modulation, gate leakage, noise, capacitive coupling, and parameter mismatch [Wegmann 89], [Daubert 88], [Fiez 91]. They affect the correct operation, accuracy and data retention time. Some of them, e.g. gate leakage, noise and parameter mismatch, are technology dependent and cannot be easily improved. However, effects such as charge injection, channel length modulation and parasitic coupling, can, to some extent, be reduced by using specific circuit solutions and by applying proper design and layout drawing techniques [Guggenbuhl 94], [Yang 90], [Toumazou 90a].

Charge injection is a complex process depending on the size and the driving scheme of the MOS switch connecting the gate and the drain of the information storing transistor [Wegmann 90]. Solutions addressing charge injection problem usually suggest the use of the minimum size switches, redundant dummy switches, individual switching scheme, or the use of additional gate capacitor [Guggenbuhl 94]. In some applications requiring higher precision, more complex structures were proposed including double (master-slave) memory cells [Leenaerts 94], algorithmic memory cells [Toumazou 90a], and S<sup>3</sup>I circuits [Carmona-Galan 2003]. These solutions employ multiple data storing transistors and more complex switching sequences to reduce charge injection errors.

Channel length modulation of the information storing transistor decreases its drainsource resistance, and hence, increases the error, depending on the voltage swing on the output node during transitions between read and write cycles. This can be reduced by employing cascode or regulated cascode memory cells, or by using cells with negative feedback loops and DC servo amplifiers assuring a constant voltage on the analogue bus [Daubert 88], [Toumazou 90b]. Another circuit idea, addressing the charge injection, channel length modulation and signal dependent error cancellation, is based on the S<sup>2</sup>I memory cell [Hughes 93]. Due to its compact structure, requiring only two information storing transistors, and simple switching sequence, such circuit is frequently considered in designs of analogue computing systems [Dudek 2000a].

Circuits based on the SI technique are usually less accurate than their continuoustime or switched-capacitor (SC) equivalents [Chang 96b]. The major disadvantage of the SI approach in current-mode computation is relatively slow operation in comparison to the continuous-time circuits. Especially, when the gate capacitances of the information storing transistors are enlarged (to prevent charge injection errors), time necessary to charge or discharge the gate increases. On the other hand, the realisation of the SI circuits, unlike switched-capacitor solutions, does not require precise linear capacitors nor high supply voltages to assure proper dynamic range [Leenaerts 96]. Most importantly, the correct operation of the switched-current circuits is practically not affected by fabrication mismatch, since the same transistor is used for storing and reading the information. Therefore, SI technique is usually considered in the analogue circuit realisations in standard CMOS technologies [Wegmann 89], [Dudek 2000].

#### 2.2.3 Analogue multipliers

Analogue multipliers in CMOS technologies can be realised in various ways, employing different design strategies and ideas, usually based on the nonlinear characteristics of MOS transistors in continuous-time and discrete-time circuits, operating in switched current (SI) or switched capacitor (SC) modes. Such computational building blocks are used as analogue processing elements in adaptive filters, data converters, mixers and modulators in radio frequency (RF) and communication systems, and in parallel computing in neural networks and analogue processor arrays. In the realisations of analogue multipliers, meeting specific design requirements such as good linearity, wide dynamic range, low noise, high bandwidth and good matching, usually depends on a particular application. For example, in the analogue computation, linearity, dynamic range and parameter mismatch will be more important than noise or bandwidth [Han 98].

In the literature, analogue multipliers are classified depending on the operation range (single, two and four quadrant) and the operation mode, depending on whether the voltage or the current represents the arguments. More generic classification, proposed in this review, differentiates between analogue multipliers based on the principles of signal multiplication. In particular, multiplication utilising variable gain amplifiers, nonlinear characteristics of MOS transistor, floating gate design and charge-based techniques will be discussed.

A multiplication of two analogue signals can be done using an amplifier with a variable gain, controlled by one of the signals, whereas the second one drives its input. There are a number of possible circuit realisations of this idea, however, some of them operate correctly only under the small signal assumption, where the characteristics of the amplifiers remain approximately linear. This often affects the precision and the dynamic range of the circuits, and usually requires differential representation of the signals to eliminate products stemming from nonlinear characteristics, therefore, such structures are mainly considered in RF and communication systems [Han 98].

Structures using MOS transistors operating in strong inversion and linear region, realise analogue multiplication based on the proportion between the drain current and the product of the gate and drain voltages, as shown in equation (2.2) [Shoemaker 91]. An example circuit realisation of such multiplier using two MOS transistors operating in linear region was presented in [Khachab 89]. There are many different possible realisations of such multiplier, based on differential approach with improved accuracy [Coban 95], [Lee 95], [Kub 90], switched capacitor (SC) circuits [Yasumoto 82], [Enomoto 85], and single transistor implementations used in programmable synaptic connections in CNN circuits [Dominguez-Castro 98], [Rodriguez-Vazquez 99], [Carmona-Galan 2003].