# INFORMATION REPRESENTATION ON A UNIVERSAL NEURAL CHIP

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2013

By Francesco Galluppi School of Computer Science

# **Contents**

| Al | bstrac | et      |                                                | 14 |

|----|--------|---------|------------------------------------------------|----|

| De | eclara | ation   |                                                | 15 |

| Co | opyri  | ght     |                                                | 16 |

| A  | cknov  | wledge  | ments                                          | 17 |

| 1  | Intr   | oducti  | on                                             | 18 |

|    | 1.1    | Backg   | ground                                         | 20 |

|    | 1.2    | Motiv   | ration and Research aims                       | 24 |

|    | 1.3    | Contr   | ibutions and Publications                      | 25 |

|    |        | 1.3.1   | Journal Papers                                 | 27 |

|    |        | 1.3.2   | Conference Papers                              | 28 |

|    |        | 1.3.3   | Workshops                                      | 31 |

|    | 1.4    | Thesis  | s outline                                      | 31 |

| 2  | Con    | nputati | ion with Spiking Neurons                       | 33 |

|    | 2.1    | Introd  | luction                                        | 33 |

|    | 2.2    | Bioins  | spired models of neurons and synapses          | 35 |

|    |        | 2.2.1   | Neural Models                                  | 36 |

|    |        | 2.2.2   | Synaptic Models                                | 45 |

|    | 2.3    | Spikin  | ng Models                                      | 49 |

|    |        | 2.3.1   | Biologically inspired models                   | 51 |

|    |        | 2.3.2   | Rank Order Coding                              | 52 |

|    |        | 2.3.3   | Neural Engineering Framework                   | 54 |

|    |        | 2.3.4   | Polychronization                               | 59 |

|    |        | 2.3.5   | Rank order codes and polychronization combined | 61 |

|   | 2.4 | Summ     | nary                                   | 63  |

|---|-----|----------|----------------------------------------|-----|

| 3 | Too | ls for N | Neural Simulation                      | 64  |

|   | 3.1 | Introd   | luction                                | 64  |

|   | 3.2 | Softw    | are Simulators                         | 65  |

|   |     | 3.2.1    | NEURON                                 | 66  |

|   |     | 3.2.2    | GENESIS                                | 66  |

|   |     | 3.2.3    | NEST                                   | 66  |

|   |     | 3.2.4    | Brian                                  | 67  |

|   |     | 3.2.5    | Nengo                                  | 68  |

|   |     | 3.2.6    | Towards a Standard                     | 70  |

|   |     | 3.2.7    | PyNN                                   | 72  |

|   | 3.3 | Simul    | ation on dedicated platforms           | 74  |

|   |     | 3.3.1    | Supercomputers                         | 75  |

|   |     | 3.3.2    | Neuromorphic Hardware                  | 77  |

|   |     | 3.3.3    | Field-Programmable Gate Arrays         | 78  |

|   |     | 3.3.4    | Graphics Processing Units              | 80  |

|   |     | 3.3.5    | Address Event Representation           | 80  |

|   | 3.4 | SpiNN    | Naker                                  | 82  |

|   |     | 3.4.1    | Architecture                           | 83  |

|   |     | 3.4.2    | Hardware Reconfigurability             | 86  |

|   |     | 3.4.3    | Neural Applications                    | 87  |

|   | 3.5 | Summ     | nary                                   | 89  |

| 4 | Con | ıfigurir | ng a universal neural system           | 91  |

|   |     | •        | luction                                | 91  |

|   | 4.2 |          | l to Hardware                          | 92  |

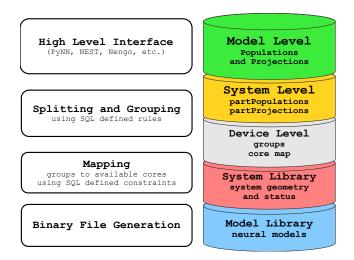

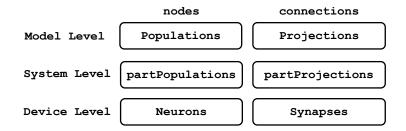

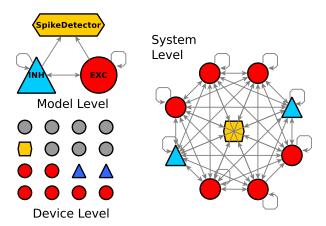

|   |     | 4.2.1    | The mapping approach                   | 93  |

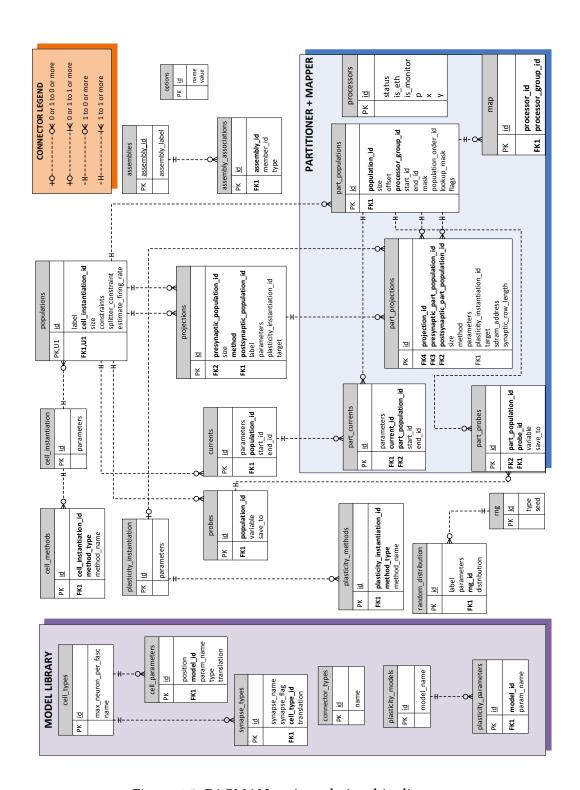

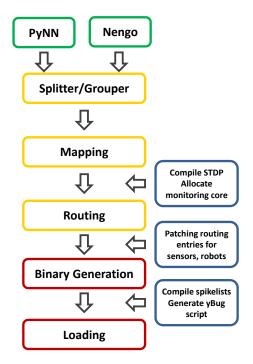

|   |     | 4.2.2    | Partitioning and Configuration Manager | 94  |

|   |     | 4.2.3    | Algorithms                             | 98  |

|   |     | 4.2.4    | Data Representation                    | 98  |

|   |     | 4.2.5    | Design and implementation choices      | 99  |

|   |     | 4.2.6    | Introducing new types                  | 101 |

|   |     | 4.2.7    | Compatible front-ends                  | 102 |

|   | 4.3 | Result   | _                                      | 103 |

|   | 4.4 | PACM     | 1AN for larger systems                 | 109 |

|   |     |          |                                        |     |

| <b>A</b> | Dan        | le anda | or codes and polychronization combined        | 100   |

|----------|------------|---------|-----------------------------------------------|-------|

| 7        | Con        | clusio  | ns                                            | 185   |

|          | 6.4        | Summ    | nary                                          | . 180 |

|          |            | 6.3.2   | Spiking ratSLAM                               |       |

|          |            | 6.3.1   | Simple model of path integration              |       |

|          | 6.3        | Integr  | rating SpiNNaker, NEF and the robot           | . 165 |

|          |            | 6.2.4   | An event-driven configurable platform         | . 164 |

|          |            | 6.2.3   | Results                                       | . 163 |

|          |            | 6.2.2   | Network Description                           | . 158 |

|          |            | 6.2.1   | Hardware setup                                | . 157 |

|          | 6.2        | Visual  | l attentional model using a silicon retina    | . 156 |

|          | 6.1        | Introd  | luction                                       | . 155 |

| 6        | Map        | pping A | AER sensors and robotic actuators             | 155   |

|          | 5.4        | Summ    | nary                                          | . 153 |

|          | <b>5</b> 4 | 5.3.3   | The Neural Engineering Framework on SpiNNaker |       |

|          |            | 5.3.2   | Results                                       |       |

|          |            | 5.3.1   | Encoding/Decoding approach                    |       |

|          | 5.3        |         | d Engineering Framework on SpiNNaker          |       |

|          |            | 5.2.7   | Opening SpiNNaker to PyNN models              |       |

|          |            | 5.2.6   | Profiling the platform                        |       |

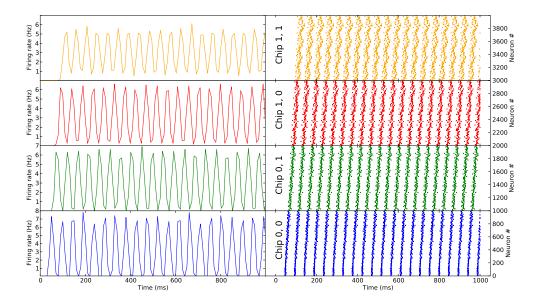

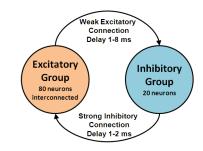

|          |            | 5.2.5   | Oscillatory Network Dynamics                  |       |

|          |            | 5.2.4   | Multimodel simulations                        |       |

|          |            | 5.2.3   | Izhikevich Neuron                             | . 121 |

|          |            | 5.2.2   | LIF Neuron                                    | . 120 |

|          |            | 5.2.1   | The PyNN.SpiNNaker module                     |       |

|          | 5.2        | PyNN    | I and PACMAN                                  | . 118 |

|          | 5.1        | Introd  | luction                                       | . 117 |

| 5        | Map        | ping I  | Different Front-ends                          | 117   |

|          | 4.7        | Summ    | nary                                          | . 115 |

|          | 4.6        |         | oen system                                    |       |

|          | 4.5        |         | iting PACMAN for 48-chip boards               |       |

|          | 1 E        | 1) 0    | ting DACMAN ton 10 chip books                 | 111   |

| В  | Resu  | ılts fro | m simulations with the LIF neuron | 199 |

|----|-------|----------|-----------------------------------|-----|

|    | B.1   | Simula   | tion results with a LIF neuron    | 199 |

|    |       | B.1.1    | Single Neuron Dynamics            | 199 |

|    |       | B.1.2    | Spikes Propagation                | 199 |

|    |       | B.1.3    | Oscillatory Network Activity      | 201 |

| C  | Sup   | plemen   | tary Material                     | 203 |

|    | C.1   | PyNN     | Files                             | 203 |

|    |       | C.1.1    | Chapter 3                         | 203 |

|    |       | C.1.2    | Chapter 4                         | 203 |

|    |       | C.1.3    | Chapter 5                         | 203 |

|    |       | C.1.4    | Chapter 6                         | 204 |

|    | C.2   | Nengo    | Files                             | 204 |

|    |       | C.2.1    | Chapter 3                         | 204 |

|    |       | C.2.2    | Chapter 5                         | 204 |

|    |       | C.2.3    | Chapter 6                         | 204 |

|    | C.3   | Videos   |                                   | 204 |

|    |       | C.3.1    | AER Sensors                       | 204 |

|    |       | C.3.2    | Robot                             | 204 |

|    | C.4   | SpiNNa   | aker Package Documentation        | 205 |

| Bi | bliog | raphy    |                                   | 205 |

Word Count: 43114

# **List of Tables**

| 4.1 | PACMAN Example                                | 97  |

|-----|-----------------------------------------------|-----|

| 4.2 | Revisiting PACMAN for 48-chip boards          | 112 |

| 5.1 | Translation methods for the Izhikevich neuron | 120 |

| 5.2 | Profiling results for 4-chip boards           | 138 |

| 5.3 | Profiling results for 48-chip boards          | 141 |

# **List of Figures**

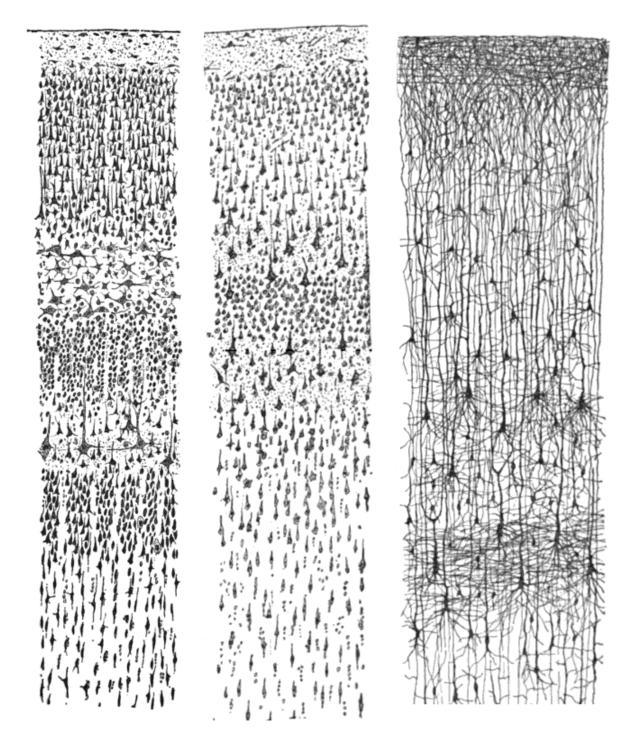

| 1.1  | Three drawings by Santiago Ramon y Cajal, taken from the book             |    |

|------|---------------------------------------------------------------------------|----|

|      | Comparative study of the sensory areas of the human cortex                | 19 |

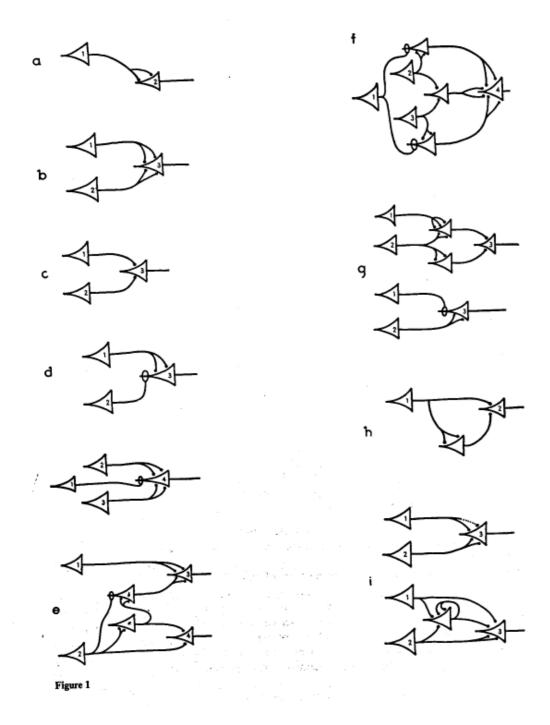

| 1.2  | Neural operations from A logical calculus of the ideas immanent in        |    |

|      | nervous activity [Mcculloch and Pitts, 1943]                              | 21 |

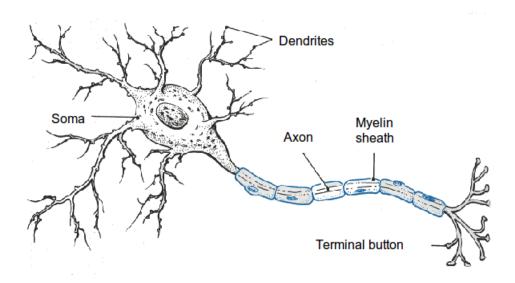

| 2.1  | Neuron structure, from Thompson [1967]                                    | 35 |

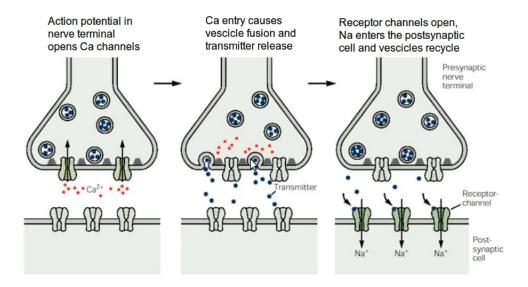

| 2.2  | Signal transmission in a chemical synapses, from Kandel et al. [1991].    | 37 |

| 2.3  | First published intracellular recording of an action potential, from      |    |

|      | Hodgkin and Huxley [1939]                                                 | 38 |

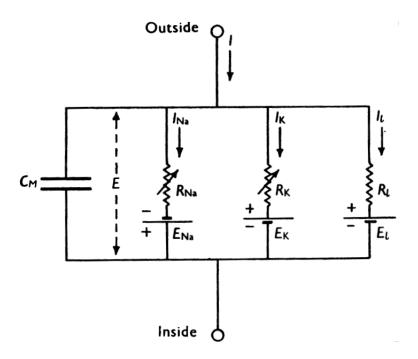

| 2.4  | Circuit equivalent model for the HH neuron, from Hodgkin and Hux-         |    |

|      | ley [1952]                                                                | 39 |

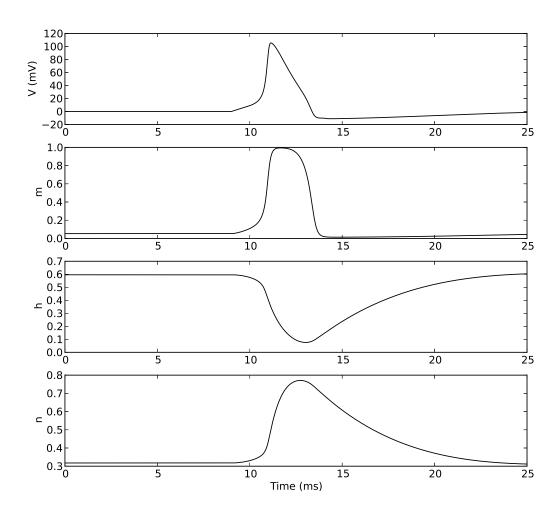

| 2.5  | Activation and deactivation of function n, m, h during the generation     |    |

|      | of an axon potential                                                      | 40 |

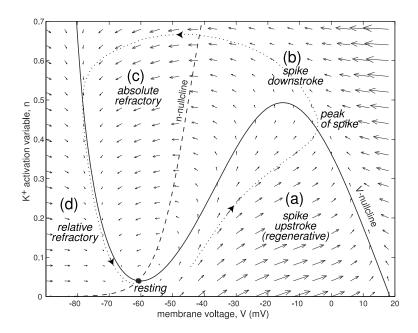

| 2.6  | Phase-plane description of the planer system modelling the resting        |    |

|      | and spiking attractors, from Izhikevich [2006a]                           | 43 |

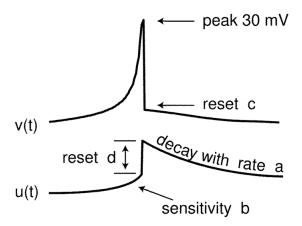

| 2.7  | Graphical representation of the parameters in the Izhikevich model        |    |

|      | from Izhikevich [2006a]                                                   | 44 |

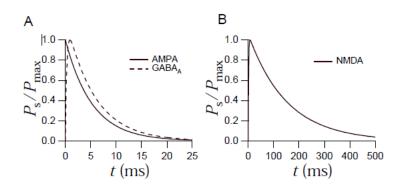

| 2.8  | Synaptic models, from Dayan and Abbott [2001b]                            | 46 |

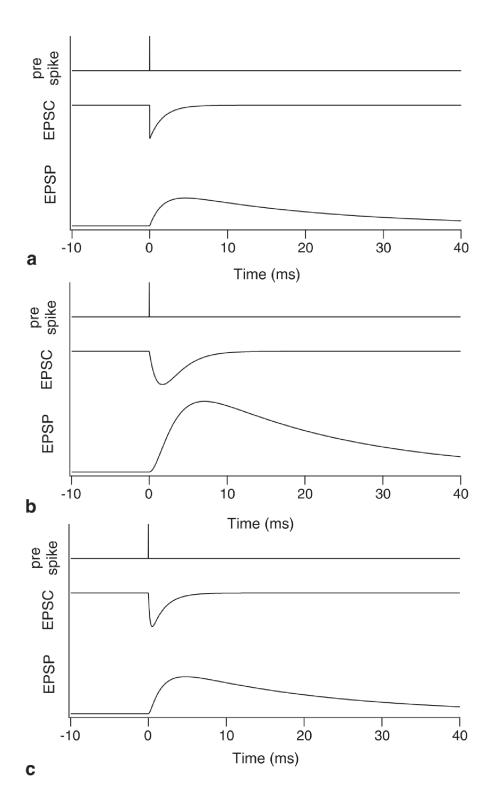

| 2.9  | Synaptic models: first order kinetic decay with an instantaneous rise     |    |

|      | (b) alpha functions (c) difference of two exponentials, after De Schut-   |    |

|      | ter [2009]                                                                | 47 |

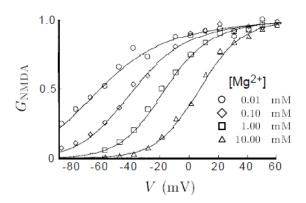

| 2.10 | Variation of conductance with post-synaptic membrane potential in         |    |

|      | NMDA synapses, from Dayan and Abbott [2001b]                              | 49 |

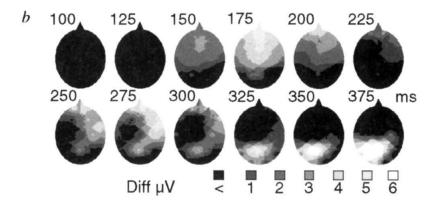

| 2.11 | Speed of processing of the visual system in a recognition task, from Thor | ре |

|      | et al. [1996]                                                             | 50 |

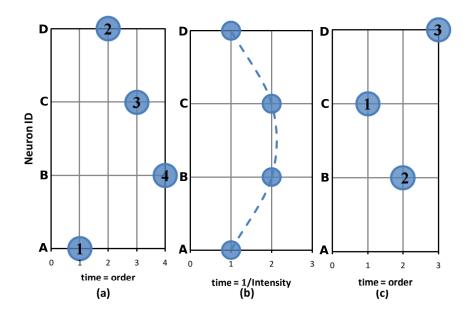

| 2.12 | Rank order codes                                                          | 53 |

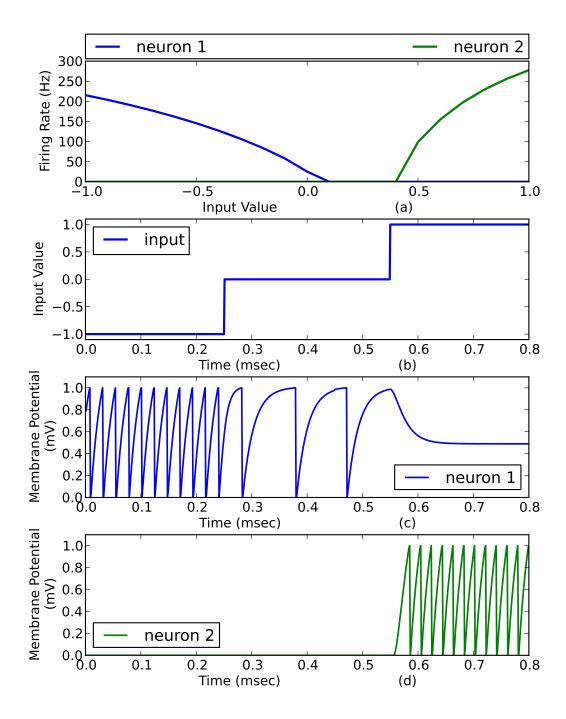

| 2.13 | Tuning curve examples                                                     | 55 |

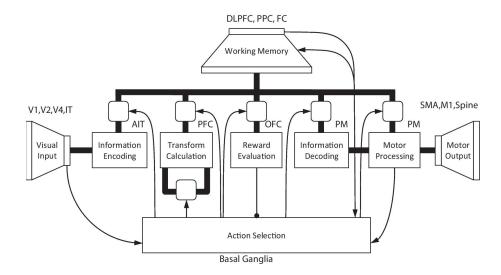

| 2.14 | SPAUN architecture, from Eliasmith et al. [2012]                          | 59 |

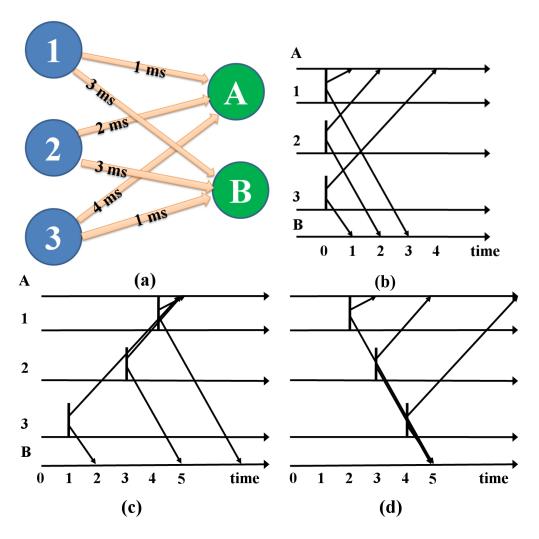

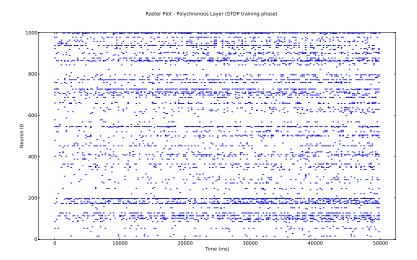

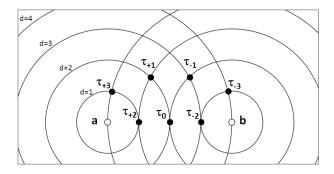

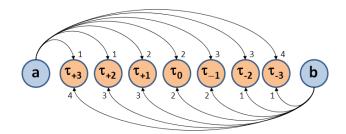

| 2.15 | Polychronization                                                           | 60 |

|------|----------------------------------------------------------------------------|----|

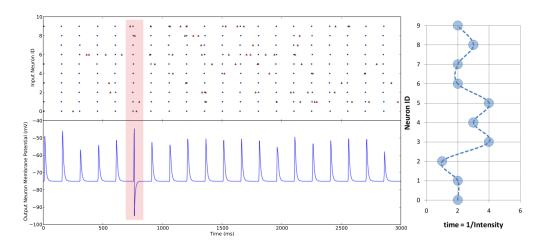

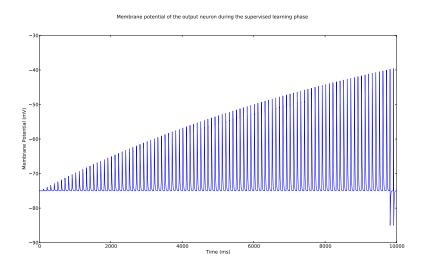

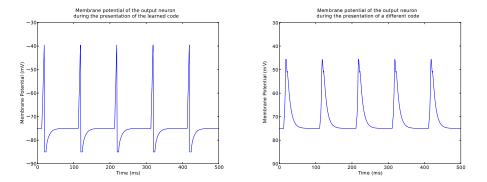

| 2.16 | The output neuron fires only when the learned code is presented            | 62 |

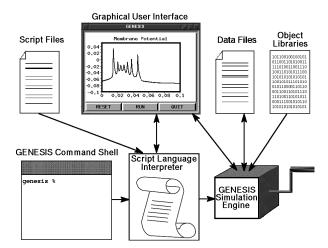

| 3.1  | GENESIS structure, from Bower et al. [1998]                                | 67 |

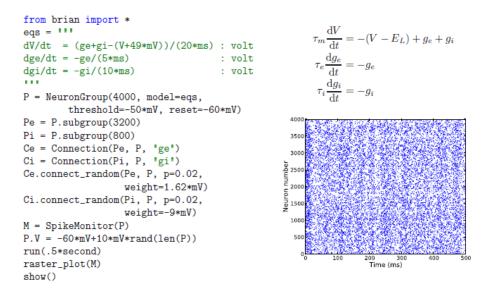

| 3.2  | Example code and execution results from Brian, from Goodman [2008].        | 68 |

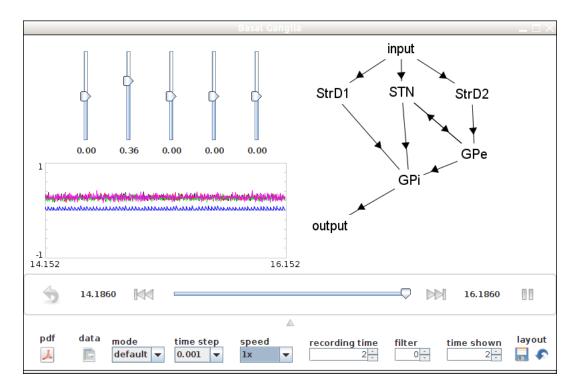

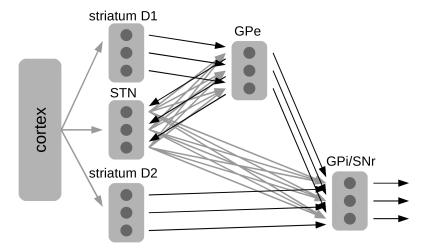

| 3.3  | Example of a basal ganglia network model running in Nengo                  | 69 |

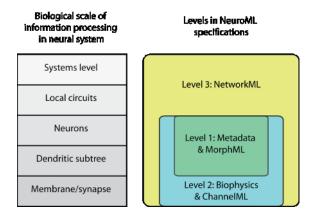

| 3.4  | NeuroML structure, from www.neuroml.org/introduction.php                   | 71 |

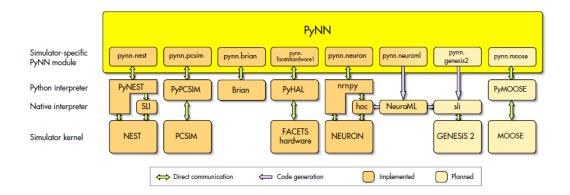

| 3.5  | PyNN Architecture, from Davison et al. [2008]                              | 72 |

| 3.6  | An example of using PyNN, adapted from http://neuralensemble.              |    |

|      | org/trac/PyNN/                                                             | 74 |

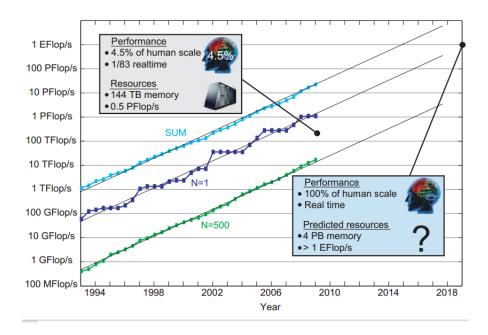

| 3.7  | Estimation for a full-brain, real-time simulation from Ananthanarayanan    | -  |

|      | et al. [2009]                                                              | 76 |

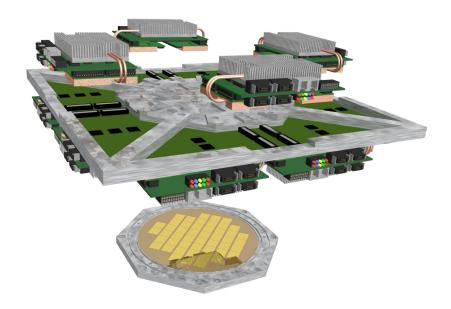

| 3.8  | Design drawing of the BrainScaleS Neural Network Hardware Mod-             |    |

|      | ule from http://brainscales.kip.uni-heidelberg.de/                         | 78 |

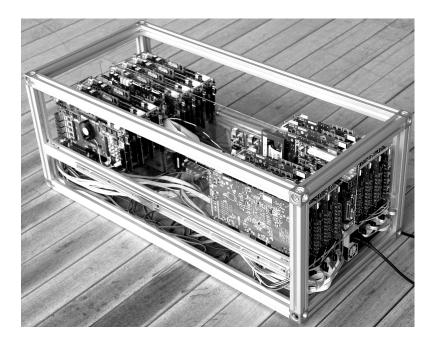

| 3.9  | A 16-FPGA Bluehive system, from Moore et al. [2012]                        | 79 |

| 3.10 | A working CAVIAR prototype asssembled in April 2005 at the CAVIAR          |    |

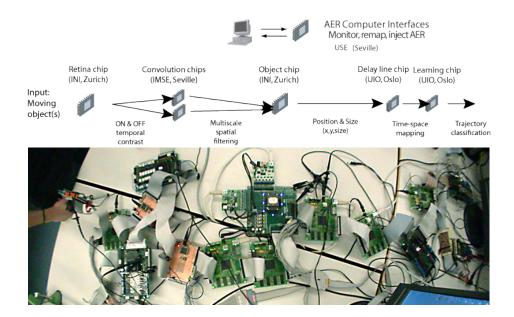

|      | workshop and its schematics, from the project resources website http:      |    |

|      | //www.ini.uzh.ch/~tobi/caviar/                                             | 81 |

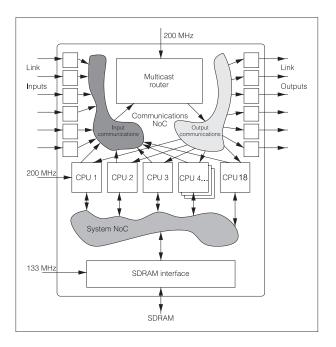

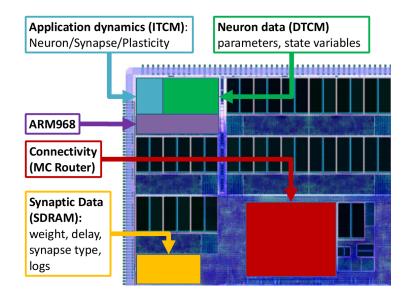

| 3.11 | SpiNNaker chip diagram, after [Plana et al., 2007]. Each SpiNNaker         |    |

|      | chip contains 18 ARM968 cores embedded in a programmable, packet           |    |

|      | based, network on chip. Action potentials are encoded as source-           |    |

|      | based AER packets, and transmitted through a Multicast Router capa-        |    |

|      | ble of handling one packet per clock cycle if unimpeded. Every core        |    |

|      | has a local Tightly-Coupled Memory and access through the System           |    |

|      | NoC to a dedicated DMA controller, used to access a 1 Gbit SDRAM           |    |

|      | within every chip                                                          | 85 |

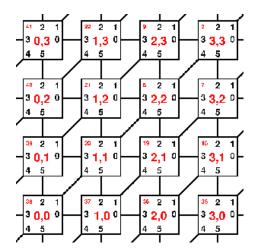

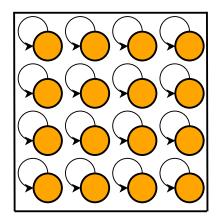

| 3.12 | Inter-chip connectivity for a 4x4 system without wrap-around. Each         |    |

|      | SpiNNaker chip (numbered in red) is connected to its neighbours            |    |

|      | through 6 bidirectional asynchronous links (numbered in black)             | 85 |

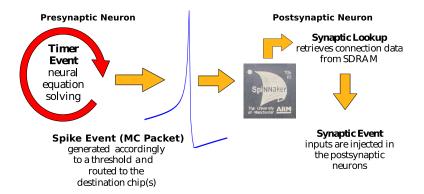

| 3.13 | Neural Simulation Events. Neural equations are solved during a <i>Neu-</i> |    |

|      | ral Event and a Spike Event is produced if a particular condition is       |    |

|      | met. Spikes are encoded as source-based AER packets and are routed         |    |

|      | to their destination cores by the MC routers. On the post-synaptic         |    |

|      | chip synapses are retrieved locally using a source-based lookup to         |    |

|      | access SDRAM; synaptic inputs are then injected into the target neu-       |    |

|      | rons (Synaptic Event)                                                      | 87 |

|      |                                                                            |    |

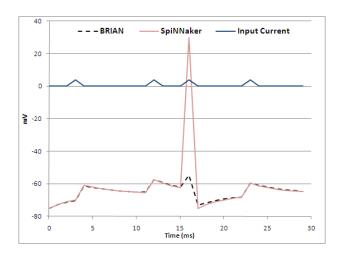

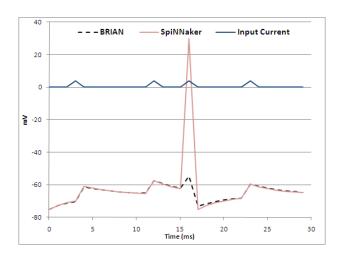

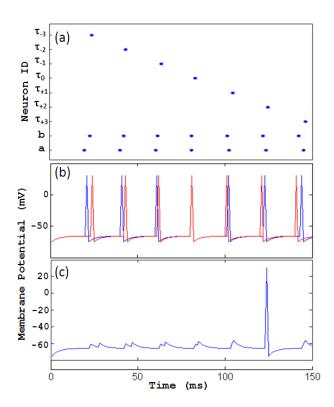

| 3.14 | Single neuron dynamics. The neuron is injected with 4 pulses of           |     |

|------|---------------------------------------------------------------------------|-----|

|      | current                                                                   | 88  |

| 3.15 | Functional blocks on a section of a SpiNNaker Chip                        | 89  |

| 4.1  | Example neural and connection input lists. Explicit modifications are     |     |

|      | required for any change in the network model                              | 93  |

| 4.2  | PACMAN structure                                                          | 95  |

| 4.3  | Hierarchical Approach                                                     | 95  |

| 4.4  | Example network composed of 2 Populations and a Spike Detector            |     |

|      | interconnected                                                            | 96  |

| 4.5  | PACMAN entity-relationship diagram                                        | 100 |

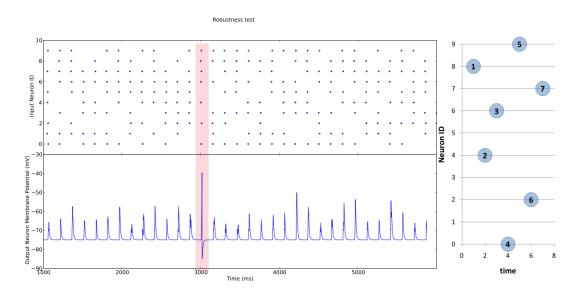

| 4.6  | Example Benchmark Network Dynamics                                        | 106 |

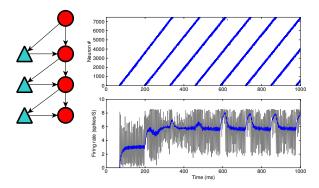

| 4.7  | Results from a synfire chain of 60 nodes of 100+25 neurons each           | 107 |

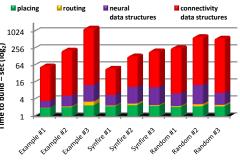

| 4.8  | 2x2 PACMAN performance analysis                                           | 108 |

| 4.9  | Time building results for models run on a 2x2 system                      | 109 |

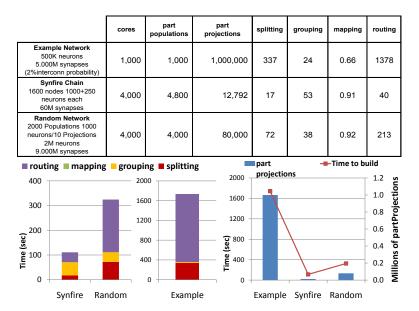

| 4.10 | Results from mapping and routing models on a 16x16 system                 | 110 |

| 4.11 | PACMAN execution flow example                                             | 113 |

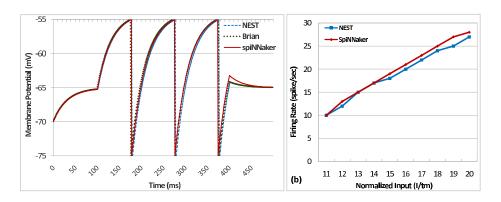

| 5.1  | (a) Results of a single LIF neuron compared with PyNN.nest and            |     |

|      | PyNN.brian (b) Comparison between firing rates                            | 120 |

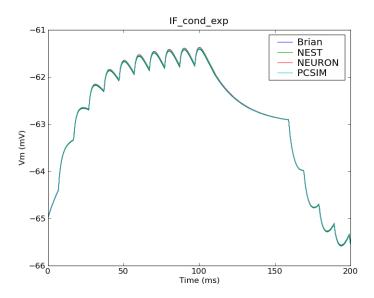

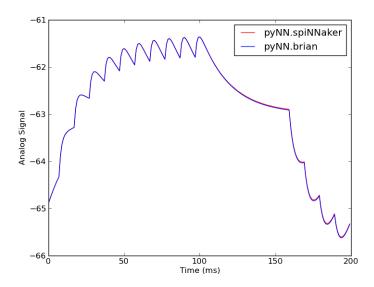

| 5.2  | Conductance-based LIF neuron simulation on SpiNNaker, compared            |     |

|      | to Brian (and to Figure 3.6)                                              | 121 |

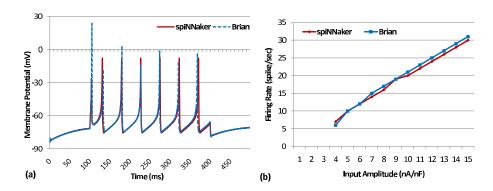

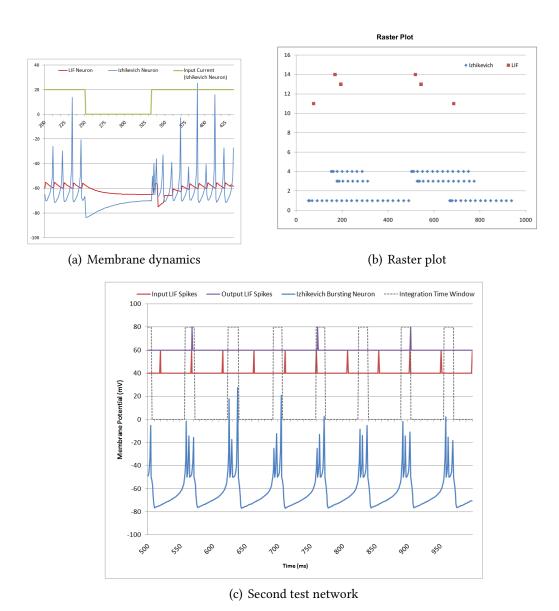

| 5.3  | Results of a single neuron compared with Brian                            | 122 |

| 5.4  | Membrane and network dynamics for simple networks                         | 123 |

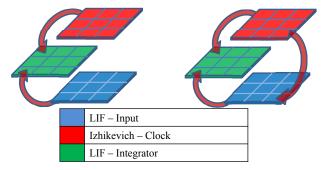

| 5.5  | Multimodel network of neural assemblies: large-scale structure and        |     |

|      | rate plots                                                                | 125 |

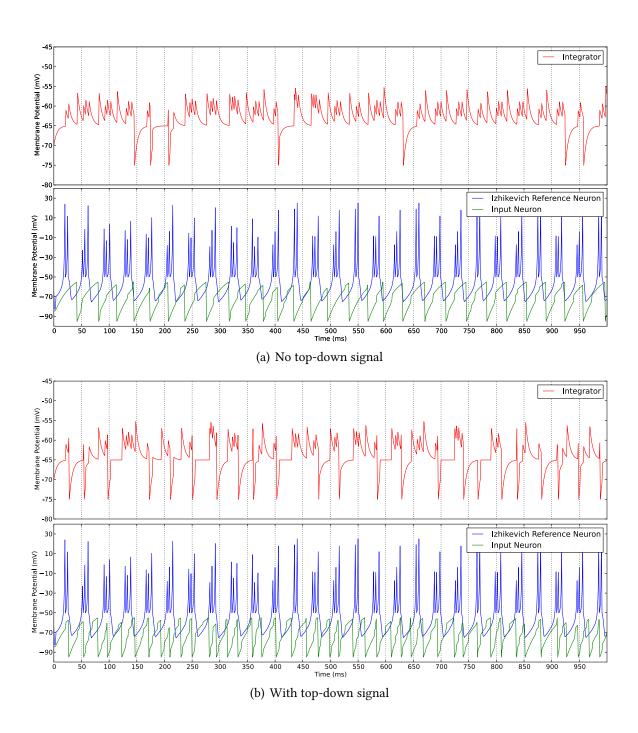

| 5.6  | Activation of a selected triplet of neurons in the mixed-model neural     |     |

|      | assembly network, with and without top-down priming                       | 129 |

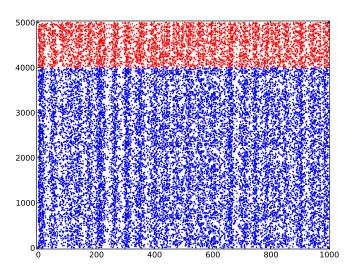

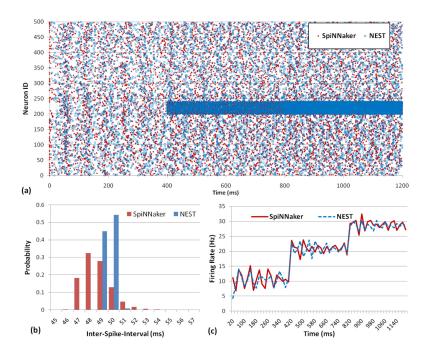

| 5.7  | Simulation with 500 neurons: comparison between NEST and SpiN-            |     |

|      | Naker. (a) Raster Plot for the entire simulation (b) Inter-Spike-Interval |     |

|      | (ISI) Distribution (c) Mean activity rate                                 | 131 |

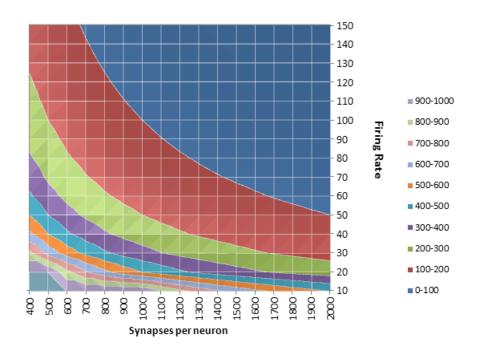

| 5.8  | How many neurons can be modelled on a single core of a SpiNNaker          |     |

|      | chip? Theoretical model                                                   | 132 |

| 5.9  | Synfire chain test on a test chip board                                   | 134 |

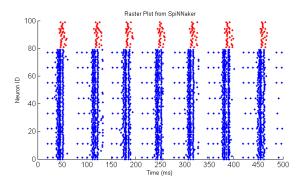

| 5 10 | Raster Plot from the simulation of the synfire chain on 4 chips.          | 135 |

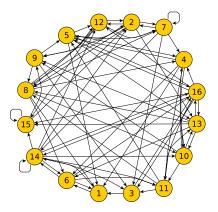

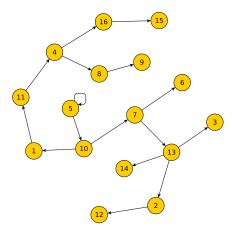

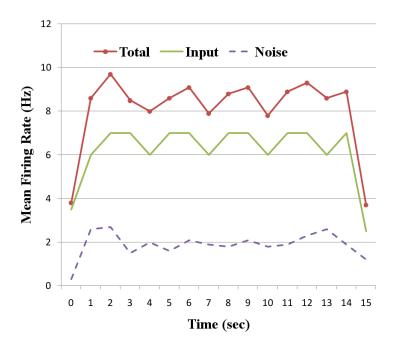

| Experiment 1: 16 populations of a 100 complex neurons each firing              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| at 100 Hz are fully interconnected to 5 other random populations. $$ . $$ .    | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Experiment 2: 16 populations of a 1000 simple neurons each firing at           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1 Hz are fully interconnected to 1 other random population                     | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

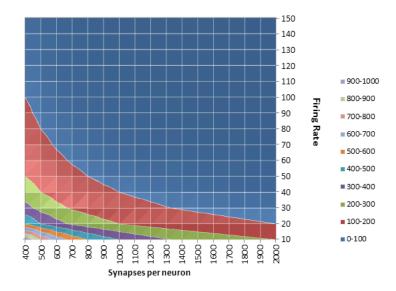

| Number of neurons that can be modelled by each core, measured limit.           | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 48-node SpiNNaker board ( $10^3$ Machine, 864 cores)                           | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

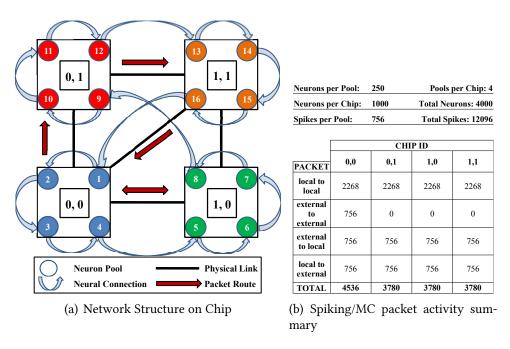

| Example of a single chip containing independent populations, as the            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| model used to test and profile the 48-node boards                              | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

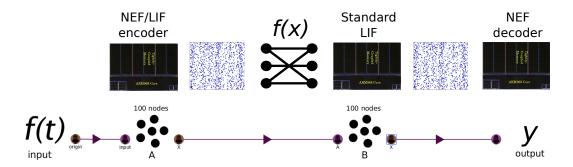

| Approach: Encoding and decoding.                                               | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

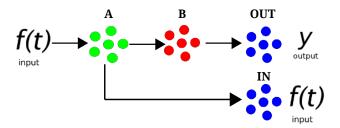

| Structure of the communication channel                                         | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

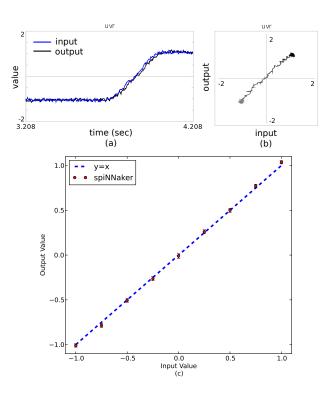

| Representation Principle: Communication channel                                | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

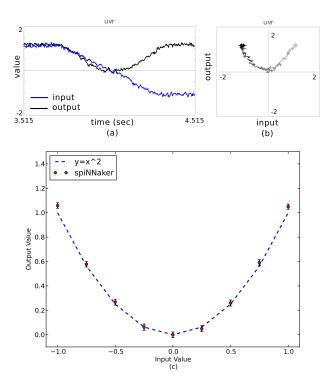

| Transformation Principle: Computing the Square                                 | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

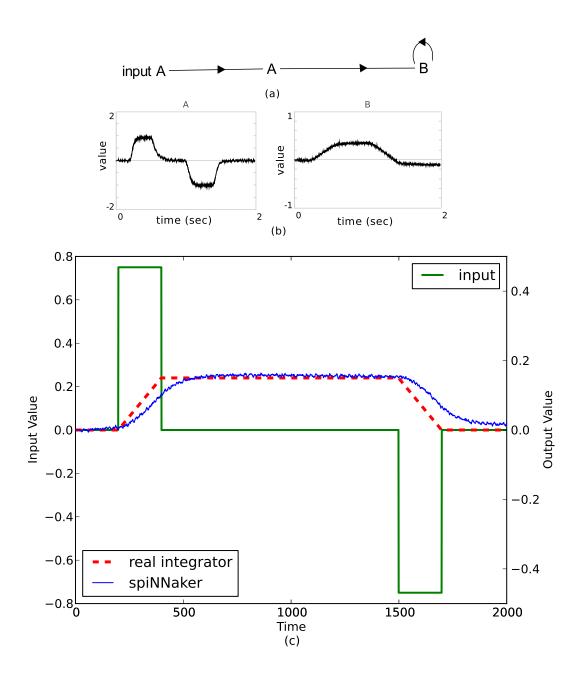

| Dynamics: Neural Integrator                                                    | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

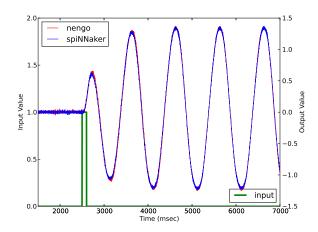

| Cyclic Attractor: Oscillator                                                   | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

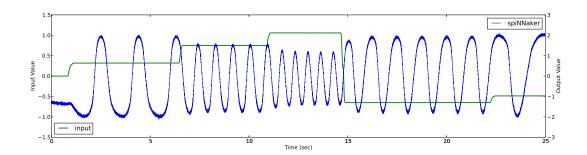

| Non-linear system: Frequency Controlled Oscillator                             | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

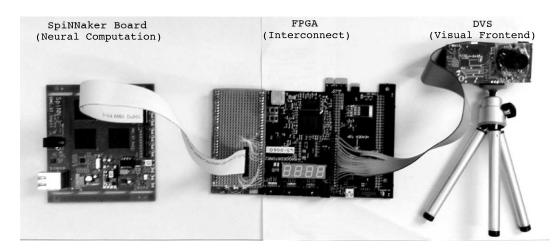

| Overview of the hardware setup: 4 SpiNNaker chips board (left), an             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FPGA translating the AER protocol between the two asynchronous                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| systems (middle) and a DVS Silicon Retina (right)                              | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

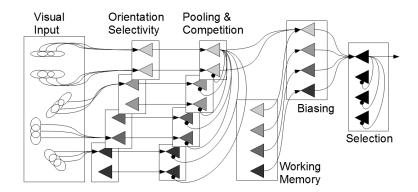

|                                                                                | 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

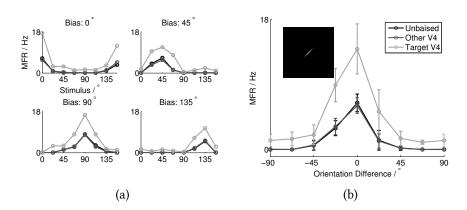

| Experiment I: tuning curves                                                    | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

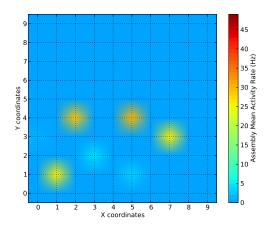

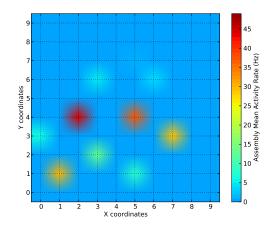

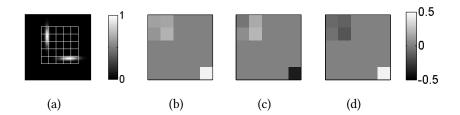

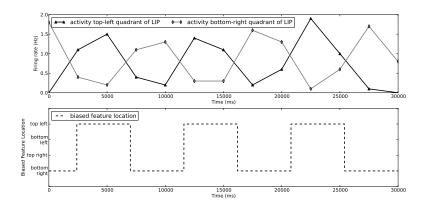

| Experiment II - visual attention task                                          | 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Activity in LIP follows the movements of the biased stimulus                   | 165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

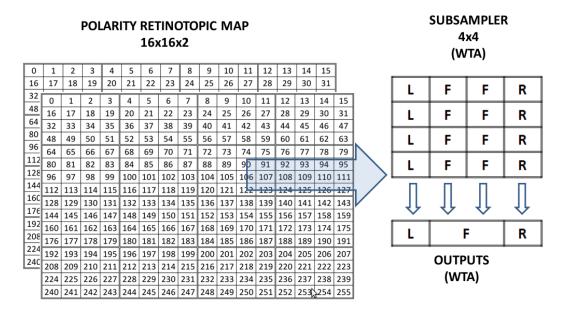

| The Neural Network used. 512 input neurons from the retina feed                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| into a hidden sub-sampler layer, and then to a competitive output              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| layer to give the robot direction                                              | 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

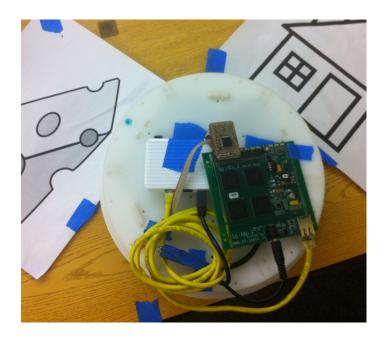

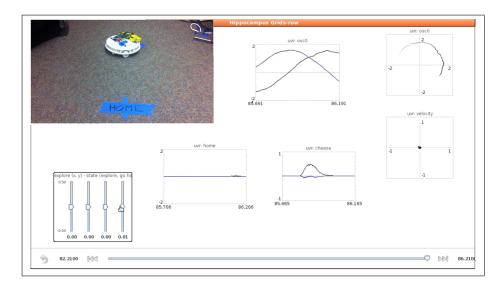

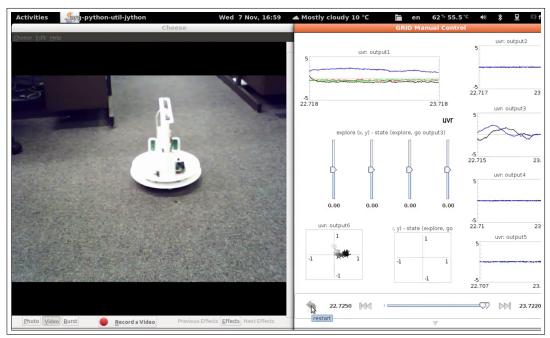

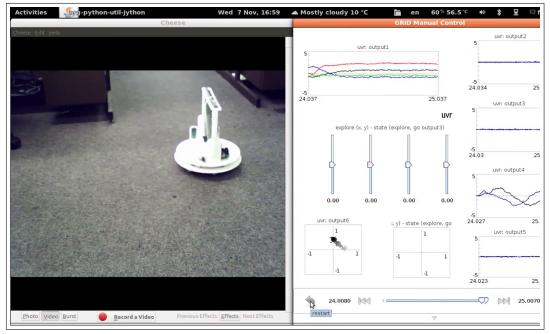

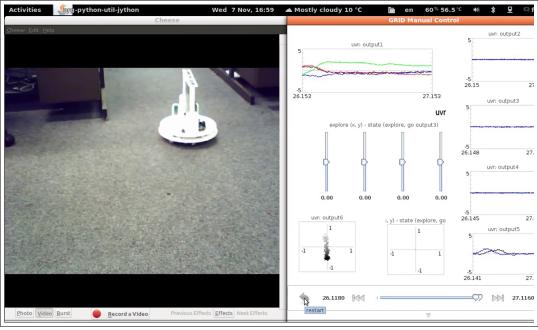

| 4-chip board/OmniBot configuration for the system used in Telluride            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2012                                                                           | 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

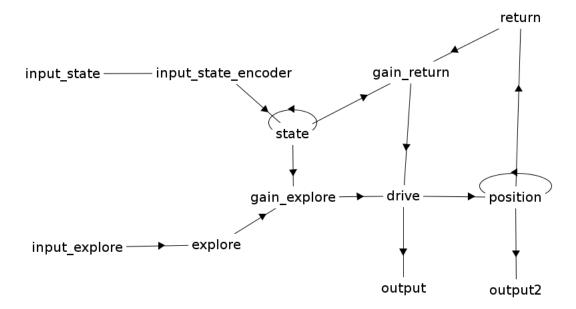

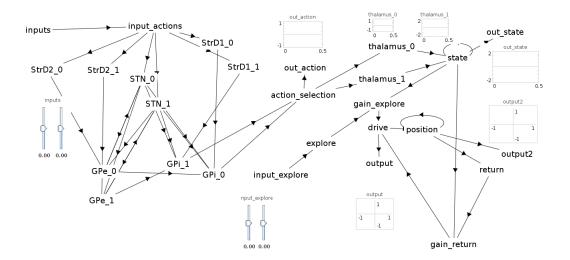

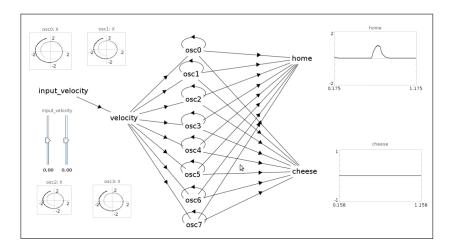

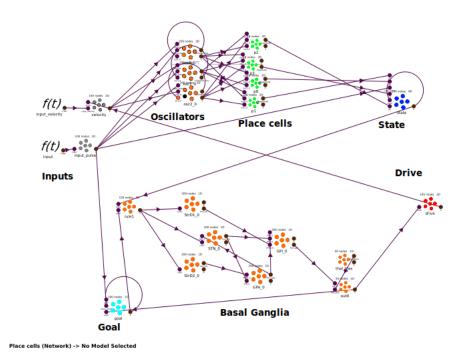

| Nengo network for the return home robot                                        | 169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Basal ganglia model from Stewart et al. [2010b], based on Gurney et al. [2001] | 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

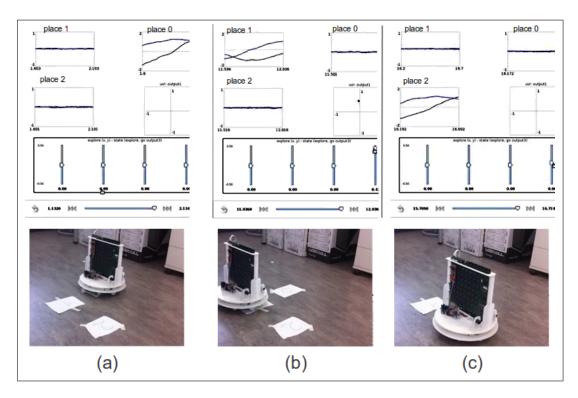

|                                                                                | 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

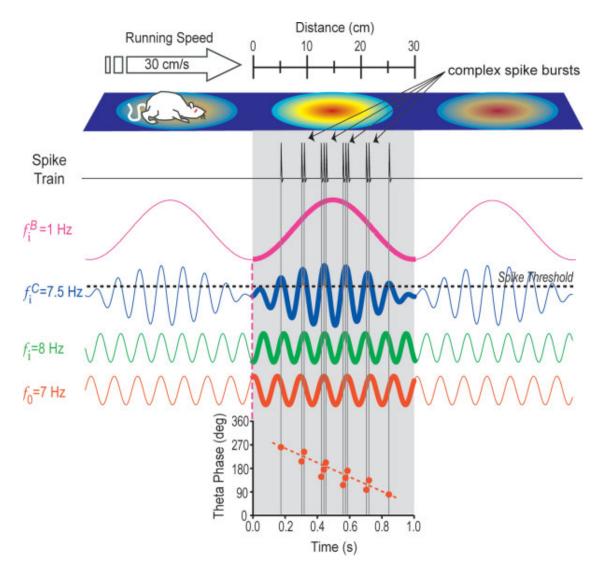

|                                                                                | 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

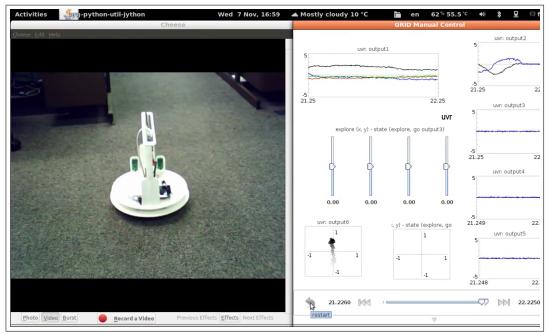

| •                                                                              | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

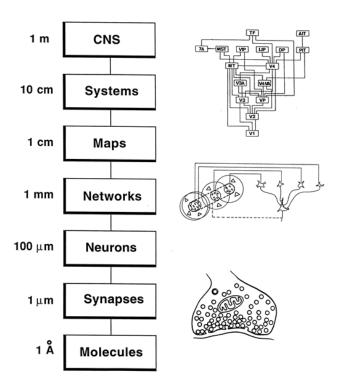

| • •                                                                            | 178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |