# LOW NOISE AMPLIFIERS USING HIGHLY STRAINED InGaAs/InAlAs/InP pHEMT FOR IMPLEMENTATION IN THE SQUARE KILOMETRE ARRAY (SKA)

A thesis submitted to The University of Manchester for the degree of

# **Doctor of Philosophy**

In the Faculty of Engineering and Physical Sciences

2012

**MUAMMAR MOHAMAD ISA**

School of Electrical and Electronic Engineering

# TABLE OF CONTENTS

| TABLE OF CONTENTSii                    |

|----------------------------------------|

| LIST OF TABLESvii                      |

| LIST OF FIGURES AND ILLUSTRATIONS viii |

| LIST OF ABBREVIATIONSxvii              |

| ABSTRACTxxi                            |

| DECLARATIONxxii                        |

| COPYRIGHT STATEMENTxxii                |

| ACKNOWLEDGEMENTSxxiv                   |

| DEDICATIONxxv                          |

| PUBLICATIONSxxvi                       |

| CHAPTER 1 INTRODUCTION1                |

| 1.1 OVERVIEW OF THE SKA1               |

| 1.2 THE CONCEPT OF THE SKA3            |

| 1.3 OBJECTIVES6                        |

| 1.3.1 LNA Specifications6              |

| 1.4 THESIS OUTLINE7                    |

| CHAPTER 2 LITERATURE REVIEW9           |

| 2.1 INTRODUCTION9                      |

| 2.2 HIGH FREQUENCY MATERIALS9          |

| 2.3 LATTICE MATCHED AND PSEUDOMORPHIC MATERIALS14                     |

|-----------------------------------------------------------------------|

| 2.4 HIGH SPEED DEVICES20                                              |

| 2.4.1 N-type Metal Oxide Semiconductor Field Effect Transistor (nMOS) |

| 2.4.2 Metal Semiconductor Field Effect Transistor (MESFET)22          |

| 2.4.3 High Electron Mobility Transistor (HEMT)23                      |

| 2.5 LOW NOISE DEVICE24                                                |

| 2.6 EPITAXIAL STRUCTURES AND ENERGY BAND DIAGRAM OF THE pHEMT         |

| 2.6.1 Metal-Semiconductor Contact                                     |

| 2.6.2 Band Discontinuities31                                          |

| 2.6.3 Quantum Well and 2-DEG33                                        |

| 2.6.4 δ-doped versus Bulk Doped Layers34                              |

| 2.7 PRINCIPLE OF OPERATION36                                          |

| 2.8 DEVICE CHARACTERISATION41                                         |

| 2.8.1 DC Characteristics41                                            |

| 2.8.2 RF Characteristics41                                            |

| 2.9 PARAMETER EXTRACTION42                                            |

| 2.9.1 Transfer Length Method                                          |

| 2.9.2 Ideality Factor and Schottky Barrier Height47                   |

| CHAPTER 3 OPTIMISATION OF INGAAS/INALAS/INP FABRICATION               |

| PROCESS51                                                             |

| 3.1 OPTIMISATION ON GATE RECESS                                                                | 51      |

|------------------------------------------------------------------------------------------------|---------|

| 3.1.1 High Selectivity Wet Etchants                                                            | 51      |

| 3.1.2 Effect of pH Values                                                                      | 57      |

| 3.1.3 Effect of Buffer Solution                                                                | 60      |

| 3.1.4 Etching Time                                                                             | 63      |

| 3.1.5 Etching in the Actual pHEMT Epitaxial Layer                                              | 65      |

| 3.2 THERMAL STABILITY                                                                          | 70      |

| 3.3 SIDE WALL SPACER                                                                           | 74      |

| 3.4 CONCLUSIONS                                                                                | 79      |

| CHAPTER 4 FABRICATION OF NOVEL LOW NOISE<br>BREAKDOWN INGAAS/INALAS/INP PHEMT FOR SKA APPLICAT |         |

| 4.1 INTRODUCTION                                                                               | 81      |

| 4.2 EPITAXIAL LAYER GROWTH                                                                     | 81      |

| 4.3 FABRICATION PROCESS                                                                        | 85      |

| 4.4 DC CHARACTERISTICS                                                                         | 88      |

| 4.5 RF CHARACTERISTICS                                                                         | 95      |

| 4.6 NOISE CHARACTERISTICS                                                                      | 96      |

| 4.7 CONCLUSIONS                                                                                | 97      |

| CHAPTER 5 FABRICATION OF IMPROVED DOUBLE                                                       | δ-DOPED |

| INGAAS/INALAS PHEMTS FOR POWER APPLICATION USIN                                                |         |

| PLATE TECHNOLOGY                                                                               | 98      |

| 5.1 INTRODUCTION                                                                               | 98      |

| 5.2 MATERIAL GROWTH99                                            | 19 |

|------------------------------------------------------------------|----|

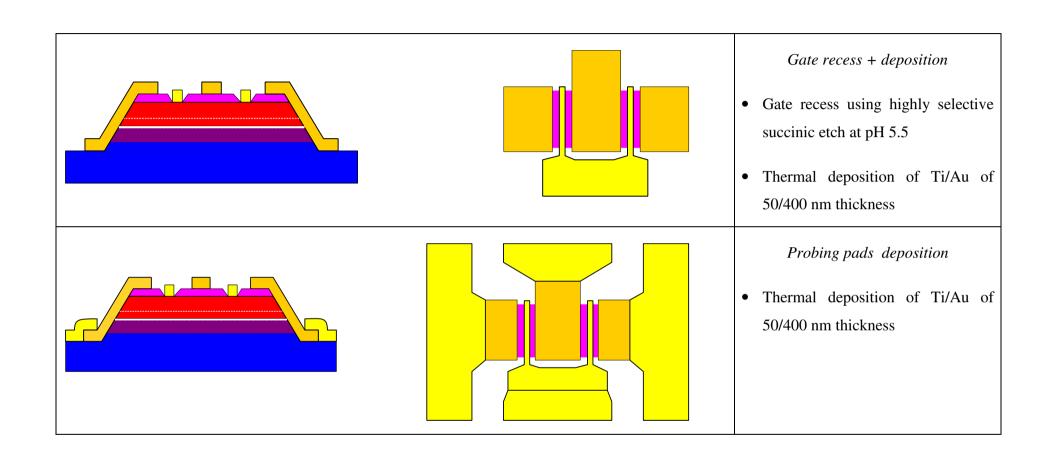

| 5.3 DEVICE FABRICATION102                                        | 12 |

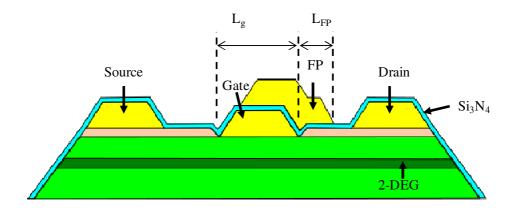

| 5.3.1 Field Plate Design                                         | 13 |

| 5.4 DC AND RF PERFORMANCES10                                     | )4 |

| 5.4.1 Ohmic                                                      | 15 |

| 5.4.2 Schottky and DC characteristic10                           | 15 |

| 5.4.3 RF Performances                                            | 3  |

| 5.5 SUMMARY11                                                    | 5  |

| CHAPTER 6 DEVELOPMENT OF MMIC LNAS FOR SKA RECEIVED              |    |

| 6.1 INTRODUCTION11                                               | 6  |

| 6.2 MMIC AND COPLANAR WAVEGUIDE (CPW)11                          | 7  |

| 6.3 FABRICATION PROCESS11                                        | 8  |

| 6.3.1 MIM Capacitors                                             | 9  |

| 6.3.2 NiCr RESISTOR12                                            | 23 |

| 6.3.3 Spiral Inductor                                            | 28 |

| 6.4 CIRCUIT DESIGN13                                             | 3  |

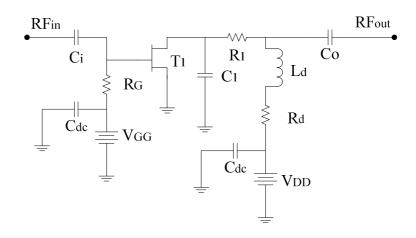

| 6.4.1 Single Stage Single-ended LNA                              | 4  |

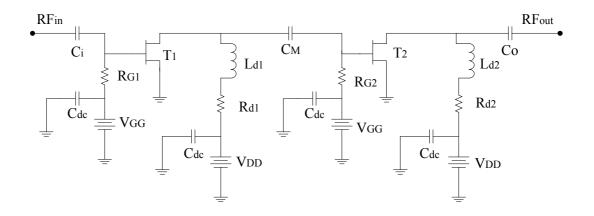

| 6.4.2 Double Stage Single-ended LNA                              | 5  |

| 6.4.2.1 High-gain Double Stages Single-ended MMIC LNA (HG DSLNA) |    |

| 6.4.2.2 Moderate-gain Double Stages Single-ended MMIC LNA        |    |

| (MG-DSLNA)13                                                     | 7  |

| 6.5 FABRICATION OF LNA                                    |

|-----------------------------------------------------------|

| 6.5.1 Mask Design                                         |

| 6.6 S-PARAMETER AND NOISE MEASUREMENT142                  |

| 6.6.1 NF and S-parameters: SSLNA143                       |

| 6.6.2 NF and S-parameters: HG-DSLNA145                    |

| 6.6.3 NF and S-parameters: MG-DSLNA146                    |

| 6.7 LNA PERFORMANCES148                                   |

| 6.8 SUMMARY151                                            |

| CHAPTER 7 CONCLUSIONS AND FUTURE WORK153                  |

| 7.1 CONCLUSIONS                                           |

| 7.2 FUTURE WORK154                                        |

| APPENDIX A: CONVENTIONAL PHEMT PROCESSING STEPS156        |

| APPENDIX B : FABRICATION STEPS FOR CONVENTIONAL PHEMT     |

| DEVICES167                                                |

| APPENDIX C: FABRICATION STEPS FOR FIELD PLATE DEVICES 170 |

| REFERENCES                                                |

# LIST OF TABLES

| Table 2-1 Comparisons between Si and high frequency materials [17-20]                       |

|---------------------------------------------------------------------------------------------|

| Table 2-2 Lattice constant and band gap of common III-V binary and ternary                  |

| compound semiconductors at 300 K [17, 25]                                                   |

| Table 3-1 Final succinic acid compositions                                                  |

| Table 4-1 Hall Measurement data at Room Temperature (300 K) and 77 K                        |

| Table 4-2 Sheet resistances $(R_{sh})$ and Contact residences $(R_C)$ of each sample from   |

| TLM                                                                                         |

| Table 4-3 Microwave biasing for XMBE #109 and VMBE # 2100                                   |

| Table 5-1 Hall Measurements at Room Temperature (300 K) and 77 K for XMBE                   |

| #171 and XMBE #131                                                                          |

| Table 5-2 $R_{sh}$ and $R_c$ from TLM measurement. $R_{sh}$ from Hall measurements are also |

| included                                                                                    |

| Table 5-3 RF biasing for conventional HEMTs and FP HEMTs                                    |

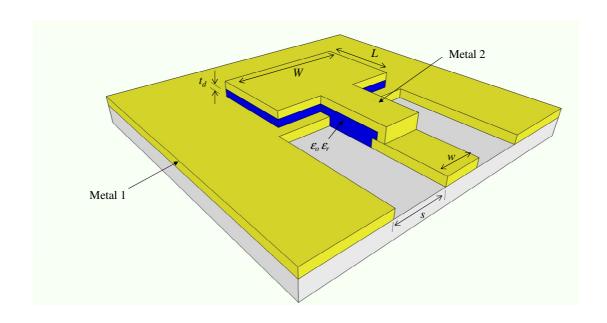

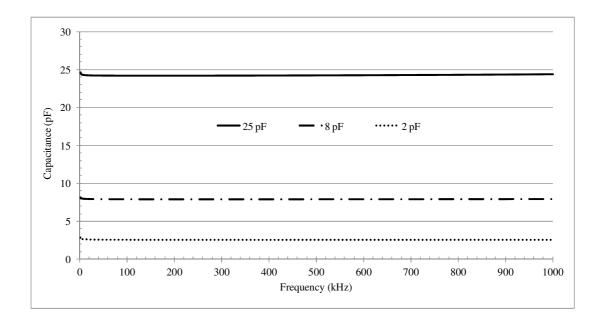

| Table 6-1 Capacitor dimensions at PCM structures                                            |

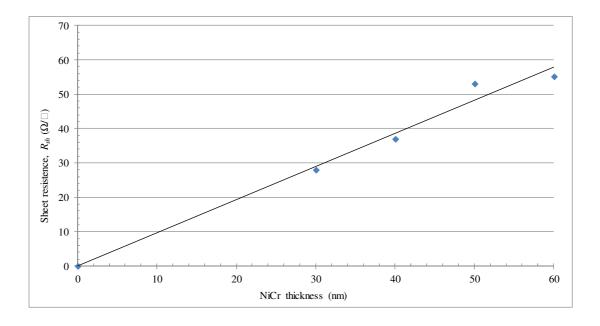

| Table 6-2 The resulting contact resistance, Rc and Rsh from sputtering 50 nm of NiCr        |

|                                                                                             |

| Table 6-3 The resulting average resistance values for PCM resistors                         |

| Table 6-4 Summary of parasitic components in the Inductor's model                           |

| Table 6-5 Table comparing the in-house fabricated LNA with the LNA obtained by              |

| other researchers                                                                           |

# LIST OF FIGURES AND ILLUSTRATIONS

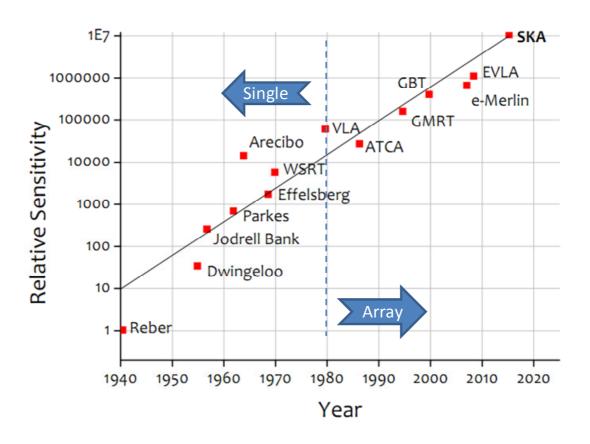

| Figure 1-1 Sensitivity of the SKA with world leading telescopes [4]                      |

|------------------------------------------------------------------------------------------|

| Figure 1-2 An illustration of antenna dislocation [8]4                                   |

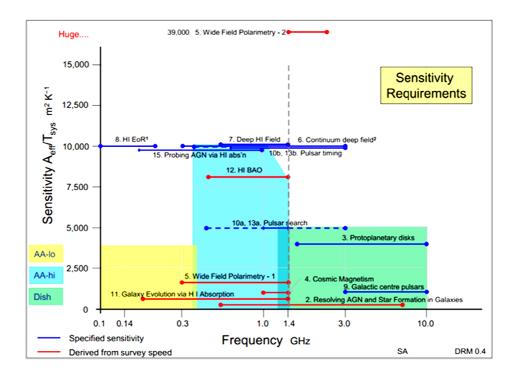

| Figure 1-3 The Sensitivity of the SKA Radio Telescope (AA = Aperture array) [10]. 5      |

| Figure 2-1 Electron mobility at low field strength versus band gap energy for various    |

| semiconductor materials. The line represents electron mobility and energy band gap       |

| levels higher than Si. The second quadrant materials are the most suitable compound      |

| semiconductors for high frequency applications, to replace Si in bulk material (except   |

| GaN because E <sub>g</sub> is high) [15]11                                               |

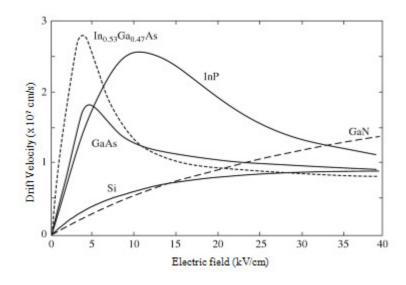

| Figure 2-2 Electron drift velocity of common semiconductor materials at low field        |

| operation [20]                                                                           |

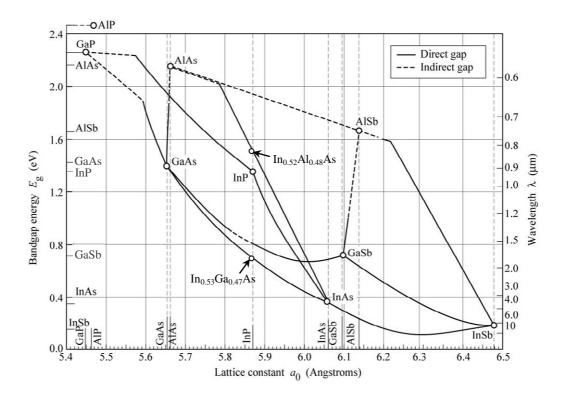

| Figure 2-3 Minimum energy band gap versus lattice constant for various                   |

| semiconductor materials. Shown in the graph is the ternary compound lattice matched      |

| to InP substrate [22]                                                                    |

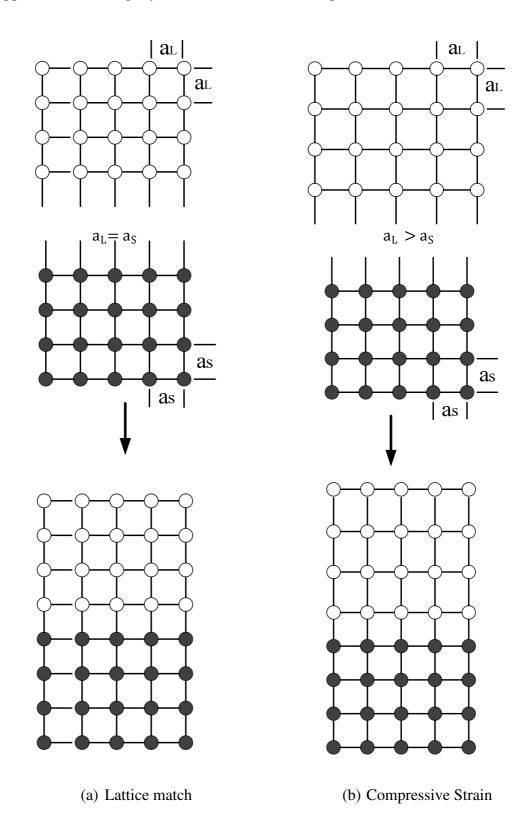

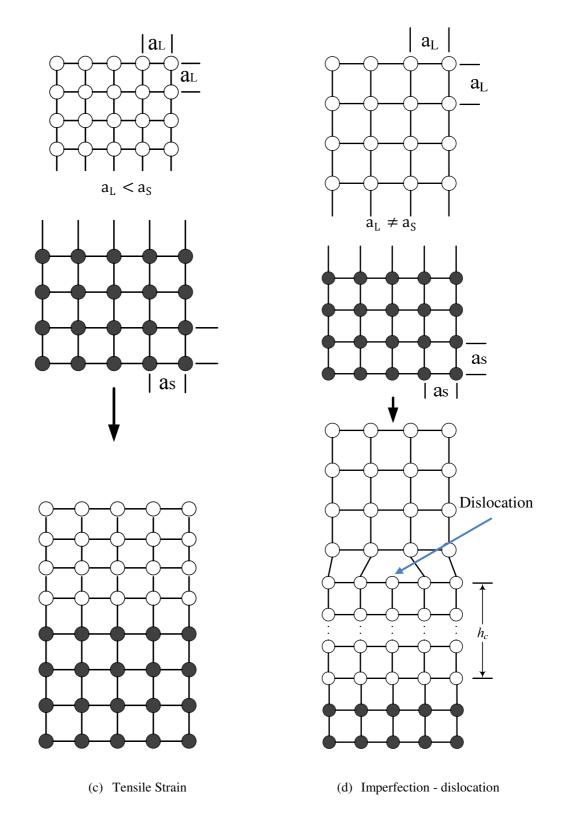

| Figure 2-4 Conceptual formation of lattice match (a), pseudomorphic compressive          |

| strain (b), pseudomorphic tensile strain (c) and lattice mismatched with defects (d). 19 |

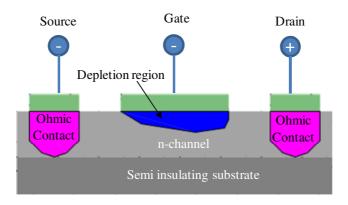

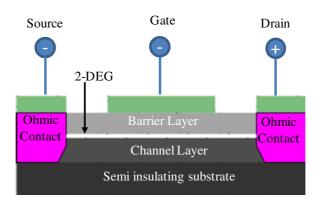

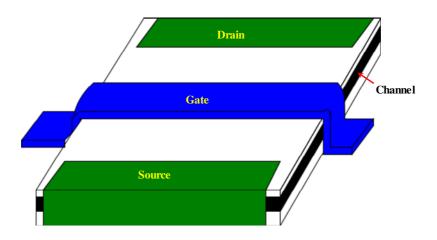

| Figure 2-5 nMOS structure                                                                |

| Figure 2-6 MESFET structure                                                              |

| Figure 2-7 HEMT structure                                                                |

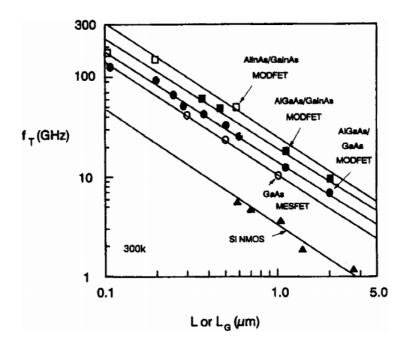

| Figure 2-8 Comparison of $f_T$ versus gate length ( $L_G$ ) of several III-V MESFET and  |

| MODFET devices with Si nMOS devices [35]                                                 |

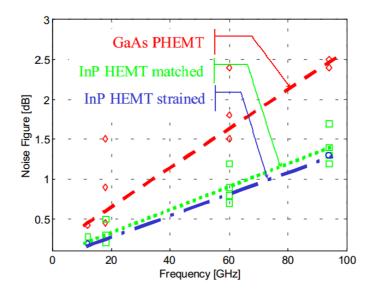

| Figure 2-9 Summary of noise performance for GaAs- and InP-based HEMTs as a               |

| function of operating frequency [37]                                                     |

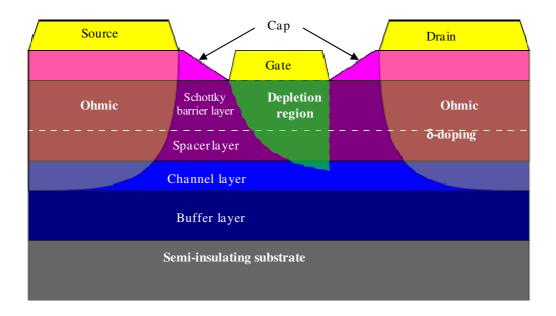

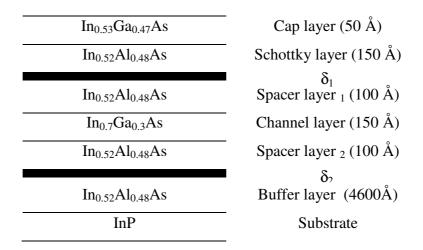

| Figure 2-10 Epitaxial structure for InP-based pHEMT                                      |

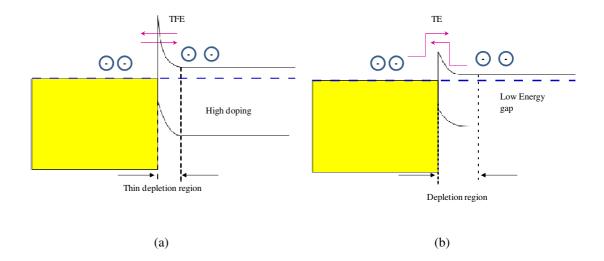

| Figure 2-11 Current conduction at Ohmic contact (a) via TFE in highly doped                       |

|---------------------------------------------------------------------------------------------------|

| semiconductor and (b) via TE at low Schottky barrier interface [35]                               |

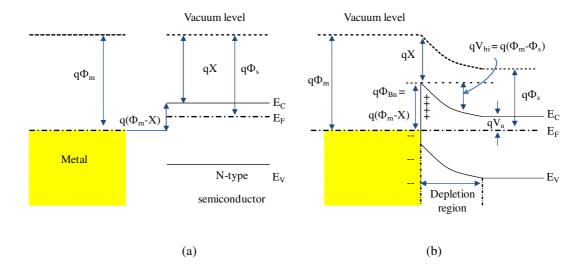

| Figure 2-12 Formation of Schottky contact before (a) and after contact (b) [40] 30                |

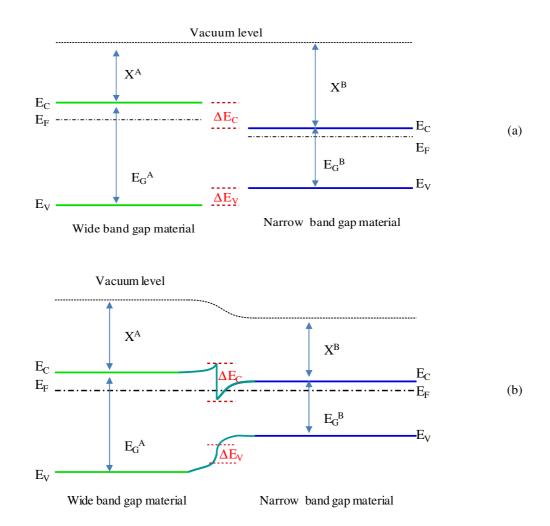

| Figure 2-13 Energy band diagrams of wide and narrow band gap materials; (a) before                |

| and (b) after contact [43]                                                                        |

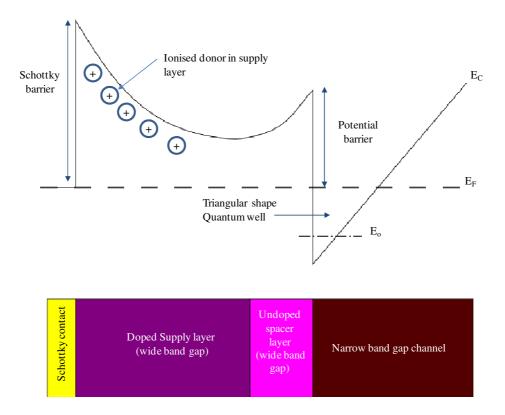

| Figure 2-14 Formation of Quantum Well at in AlGaAs/GaAs hetero-junction 34                        |

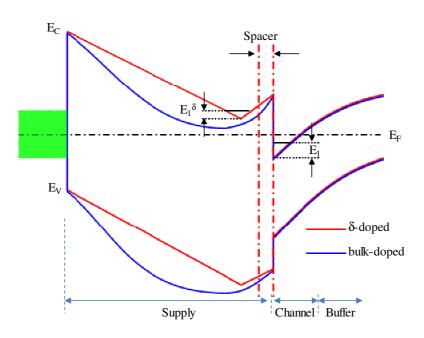

| Figure 2-15 Band diagram and quantised carriers between δ-doped and bulk-doped                    |

| heterostructures resulting similar 2-DEG carrier densities [44]                                   |

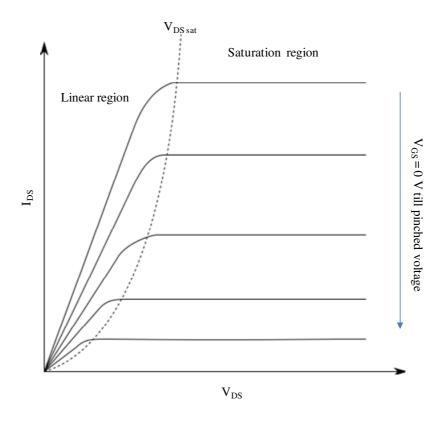

| Figure 2-16 Typical HEMT I-V Characteristic                                                       |

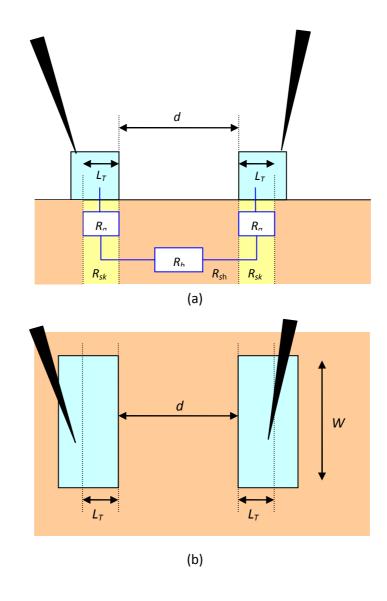

| Figure 2-17 Theory behind TLM structures; (a) side view, and (b) top view                         |

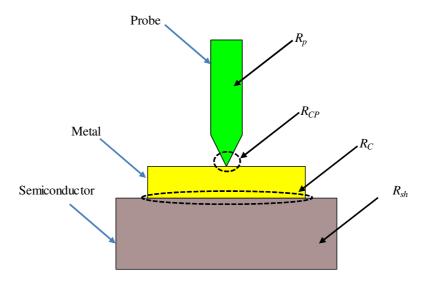

| Figure 2-18 Resistances in a metal-semiconductor contact connected with a probe.                  |

| Black arrows show the resistances and blue arrows are showing the different type of               |

| materials                                                                                         |

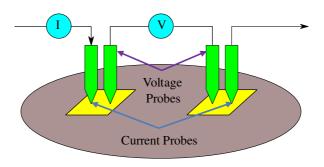

| Figure 2-19 Arrangement of probes in a four-point system between two TLM pads. 45                 |

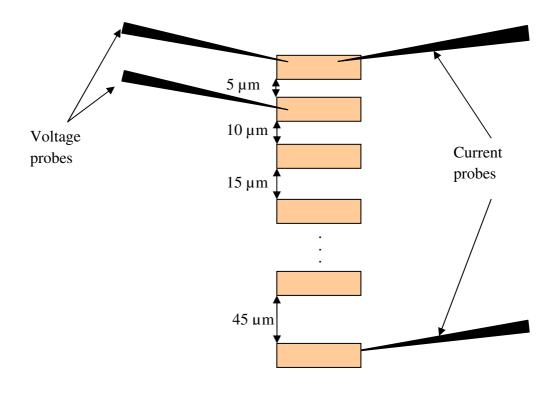

| Figure 2-20 Probing techniques in TLM measurement                                                 |

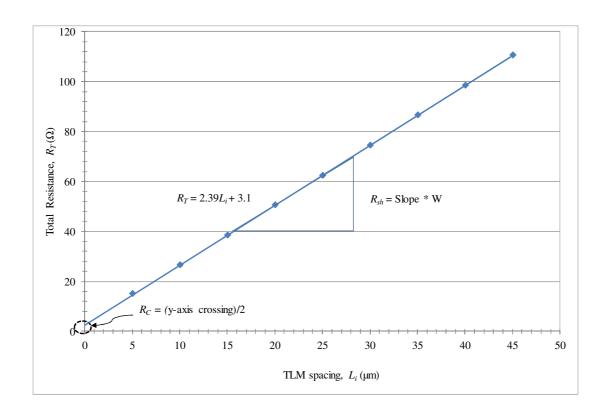

| Figure 2-21 An illustration of the determination of $R_C$ and $R_{sh}$ from TLM measurement       |

| 47                                                                                                |

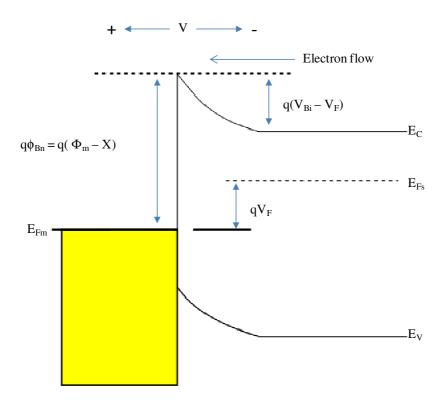

| Figure 2-22 An illustration of a Schottky contact band diagram under forward bias 48              |

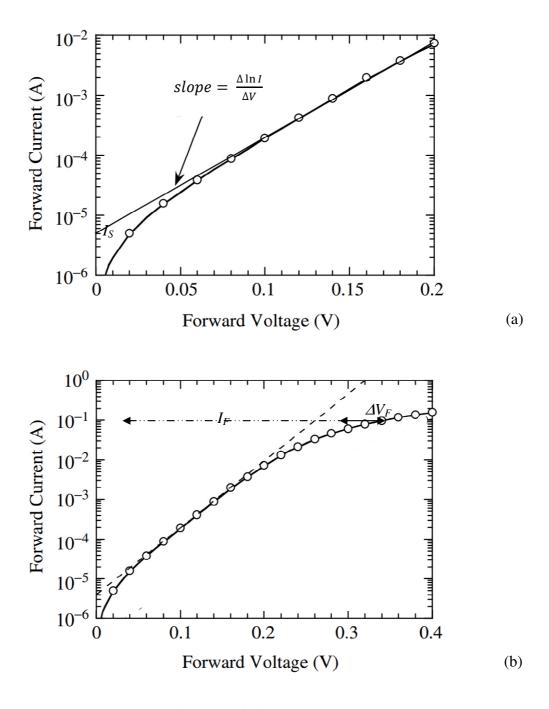

| Figure 2-23 Parameter extraction for (a) ideality factor (n) and barrier height $(\Phi_{Bn})$ and |

| (b) series resistance $(r_s)$ from Schottky forward current characteristic [47] 50                |

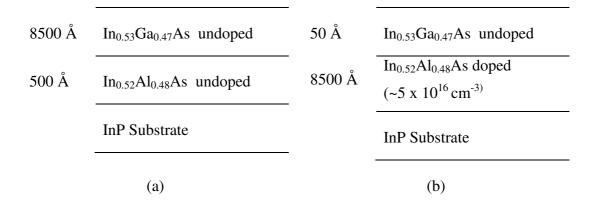

| Figure 3-1 Samples' epitaxial layer used in the experiment (a) Bulk lattice match                 |

| InGaAs VMBE #1593 and (b) Bulk lattice match InAlAs VMBE #1594 (thickness are                     |

| not to scale)53                                                                                   |

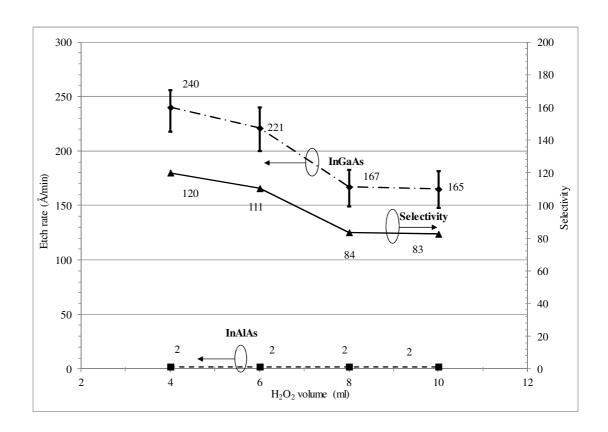

| Figure 3-2 Etch rate of lattice matched InGaAs and InAlAs (dashed lines) and                                           |

|------------------------------------------------------------------------------------------------------------------------|

| selectivity (continuous line) in different $H_2O_2$ composition. (DI volume = 50 ml and                                |

| pH = 6)                                                                                                                |

| Figure 3-3 Etch profile by Talystep Step Profiler (a) InGaAs sample showing 0.01                                       |

| μm/div and (b) InAlAs sample showing 0.004 μm/div                                                                      |

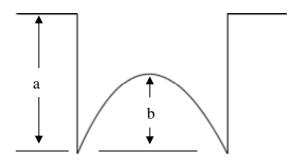

| Figure 3-4 Calculation for percentage of dome profile                                                                  |

| Figure 3-5 Etching profile (dashed lines) and percentage of Dome Effect (solid line)                                   |

| of lattice matched InGaAs (DI volume = 50 ml, pH = 6.0 and etch time = 5 minutes)                                      |

|                                                                                                                        |

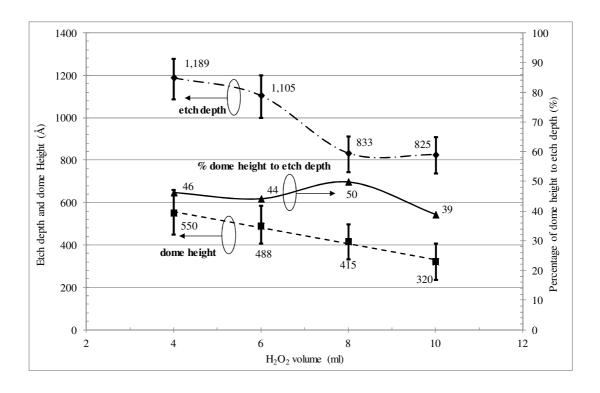

| Figure 3-6 Etch rate (dashed lines) and selectivity (solid line) for lattice match InGaAs                              |

| and InAlAs at different pH values (DI volume = $50 \text{ ml}$ and $H_2O_2$ volume = $8.0 \text{ ml}$ ). $58$          |

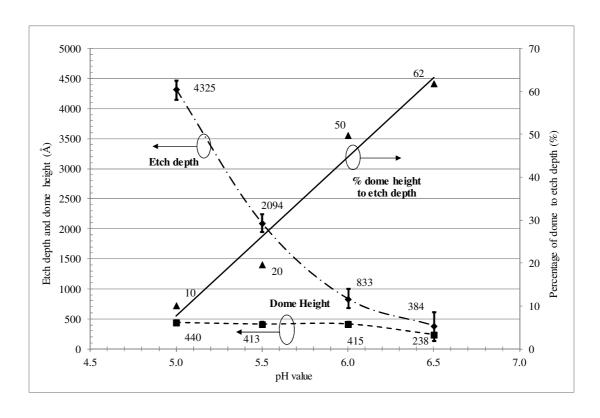

| Figure 3-7 Etch profiles (dashed lines) and Doming Effect (solid line) in InGaAs at                                    |

| different pH values (DI volume = $50 \text{ ml}$ and $H_2O_2$ volume = $8.0 \text{ ml}$ and etch time = $5 \text{ ml}$ |

| minutes)                                                                                                               |

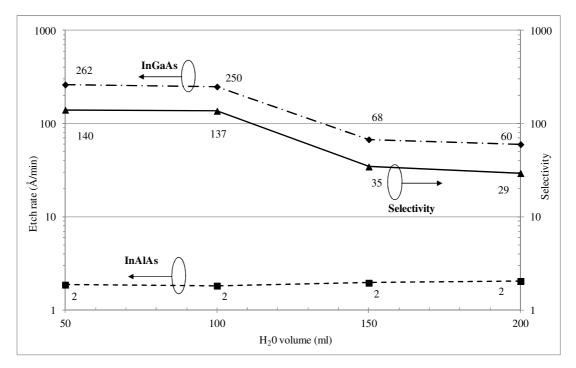

| Figure 3-8 Etch rate (dashed lines) and selectivity (solid line) at different DI water                                 |

| volume61                                                                                                               |

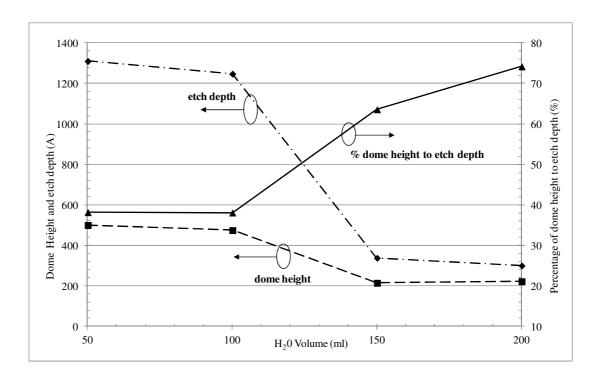

| Figure 3-9 Etch profile (dashed lines) and Dome Effect (solid line) at different                                       |

| deionised water volume (pH=6, $H_2O_2$ volume = 5.0 ml and etch time = 5 minutes) 62                                   |

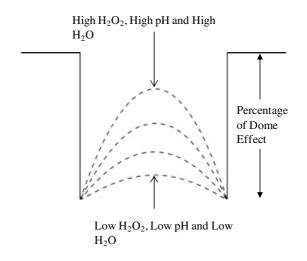

| Figure 3-10 Summary from chemical composition studies                                                                  |

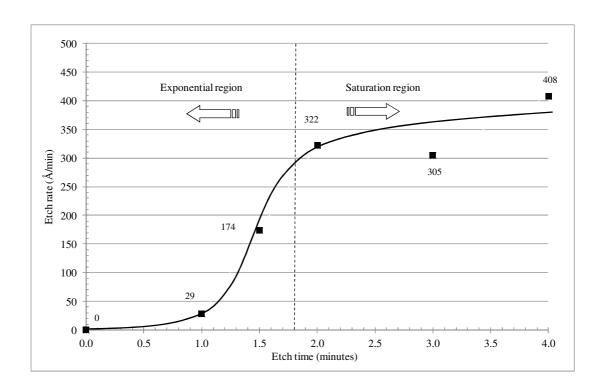

| Figure 3-11 Lattice matched InGaAs etch rate at a different etch time                                                  |

| $(H_2O_2 = 5.0 \text{ ml}, pH = 5.5 \text{ and } H_2O = 50 \text{ ml})$                                                |

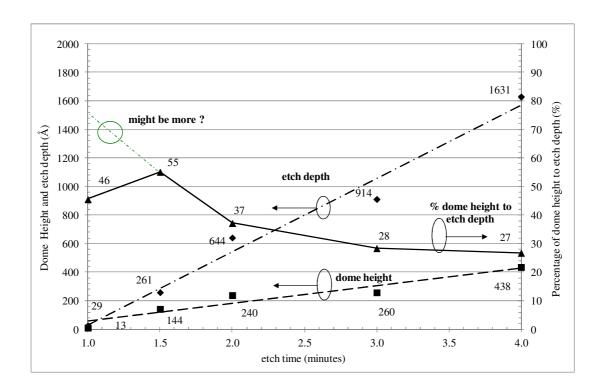

| Figure 3-12 Doming effect at different etch time                                                                       |

| $(H_2O_2 = 5.0 \text{ ml}, pH = 5.5 \text{ and } H_2O = 50 \text{ ml})$                                                |

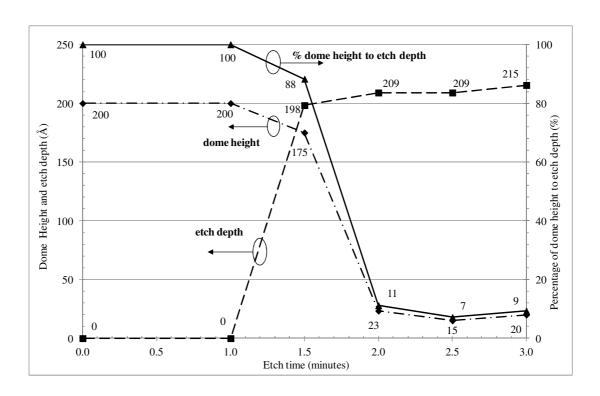

| Figure 3-13 Epitaxial layer for XMBE #170 (thickness not to scale)                                                     |

| Figure 3-14 Doming effects at XMBE#170 samples                                                                         |

| Figure 3-15 Epitaxial layers for XMBE #129 (thickness not to scale)                    |

|----------------------------------------------------------------------------------------|

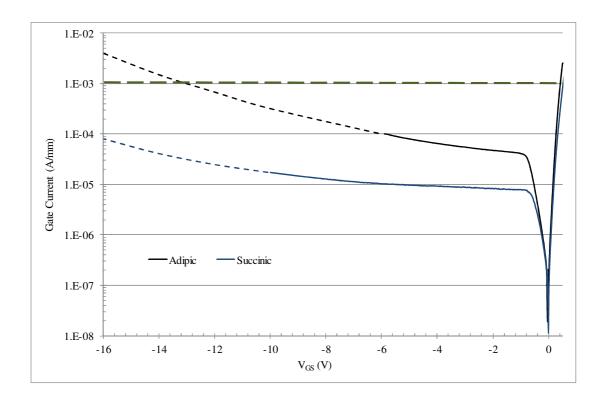

| Figure 3-16 Schottky gate current for XMBE #129 showing Adipic (black line) and        |

| Succinic (blue line) as the gate recess etchant. The dotted black and blue lines       |

| represent the extrapolation of Adipic and Succinic Acid, respectively                  |

| Figure 3-17 Epitaxial layer for XMBE #178 (thickness not to scale)                     |

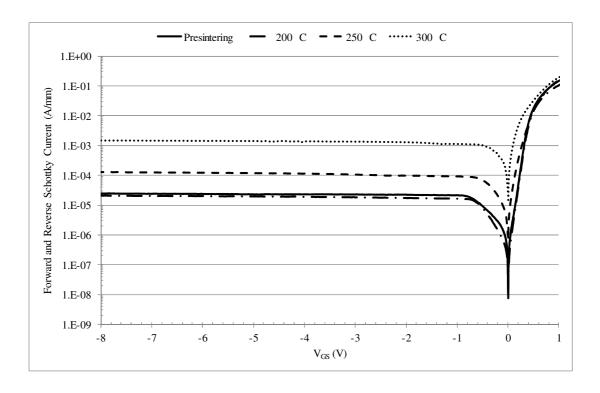

| Figure 3-18 1 x 50 µm gate width sintering studies for 3 minutes succinic etch time 72 |

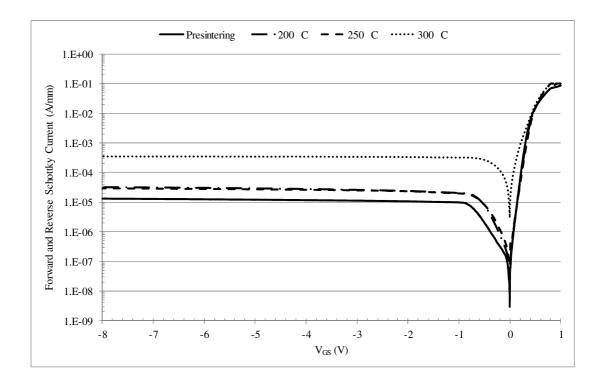

| Figure 3-19 1 x 50 µm gate width sintering studies for 4 minutes succinic etch time 73 |

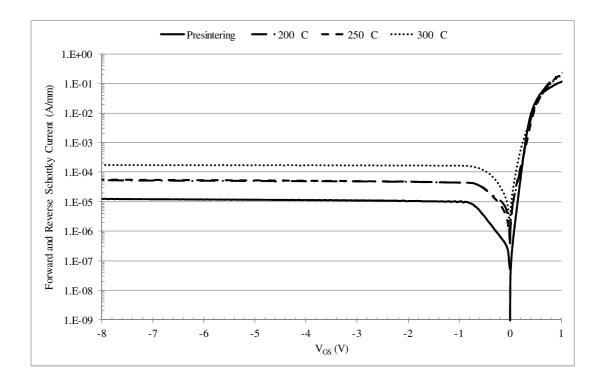

| Figure 3-20 1 x 400 µm gate width sintering studies for 5 minutes succinic etch 74     |

| Figure 3-21 Graphical representation of MESA side wall. The Schottky gate running      |

| up the MESA will in contact with barrow band gap channel layer which complete the      |

| sidewall leakage path [60]75                                                           |

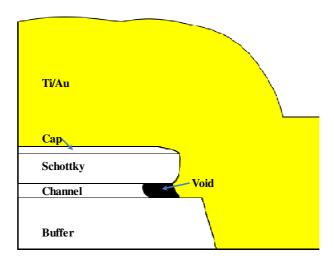

| Figure 3-22 Side wall etch showing the channel cavity isolate the gate from InGaAs     |

| channel [60]                                                                           |

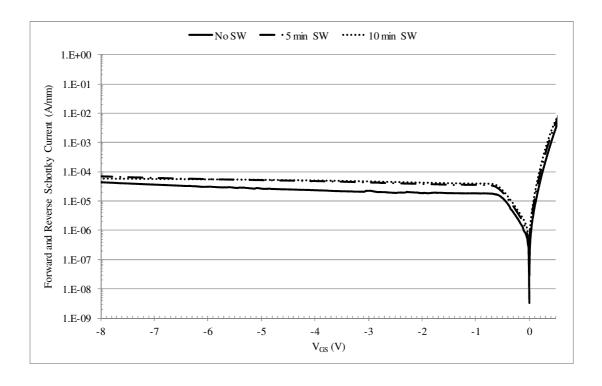

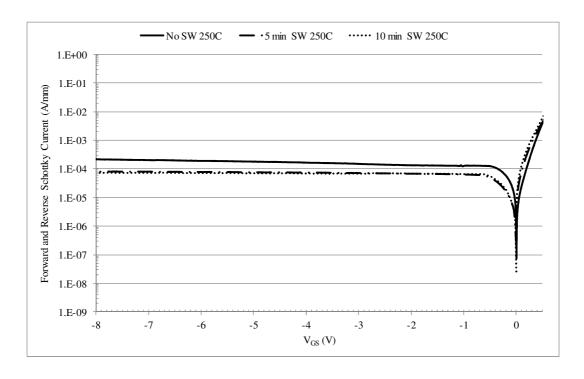

| Figure 3-23 Schottky diode characteristic for 1 x 50 µm gate for all sidewall etch     |

| condition before heat treatment                                                        |

| Figure 3-24 Schottky diode characteristic for 1 x 50 µm gate for all side wall etch    |

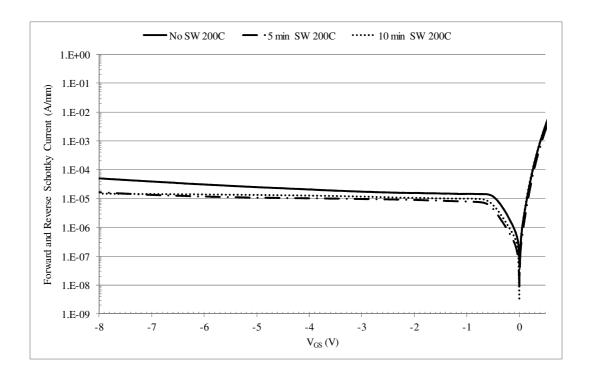

| condition at sintering temperature 200 °C for 5 minutes                                |

| Figure 3-25 Schottky diode characteristic for 1 x 50 µm gate for all side wall etch    |

| condition at sintering temperature 250 °C for 5 minutes                                |

| Figure 4-1 Epitaxial layers for baseline epilayer(XMBE #109) and enhanced epilayer     |

| (VMBE #2100)                                                                           |

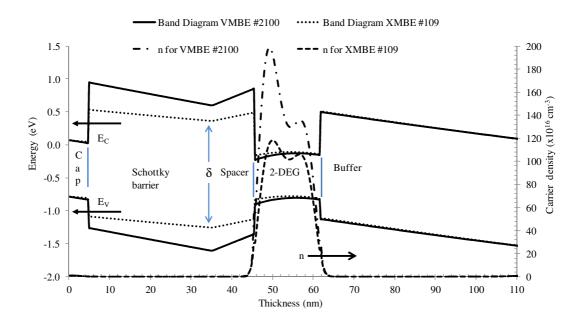

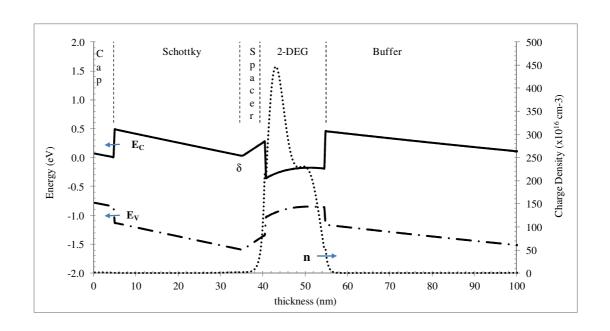

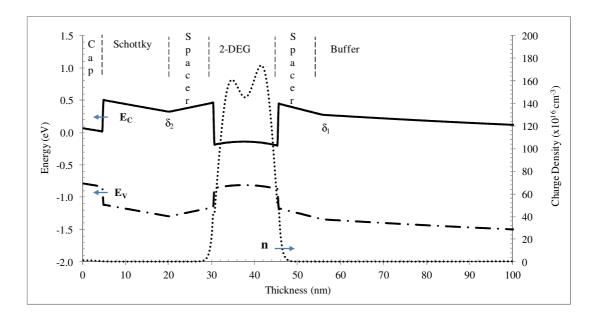

| Figure 4-2 Simulated energy band diagrams and carrier density in channel for both      |

| epilayers. The energy band and carrier density are made overlapped to each other for   |

| comparison purpose                                                                     |

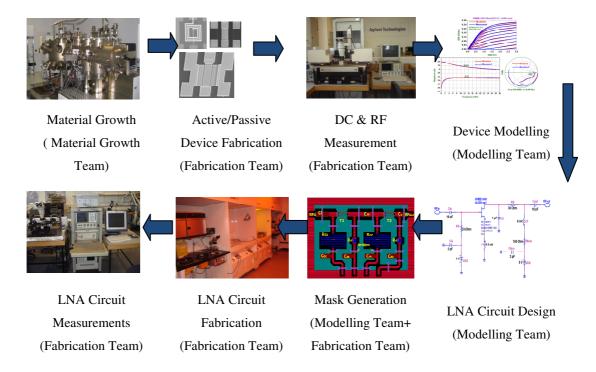

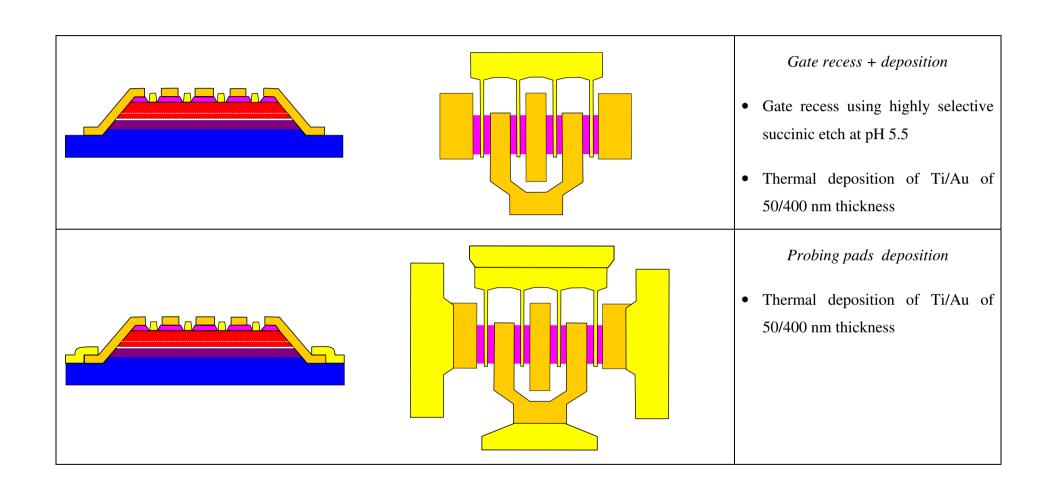

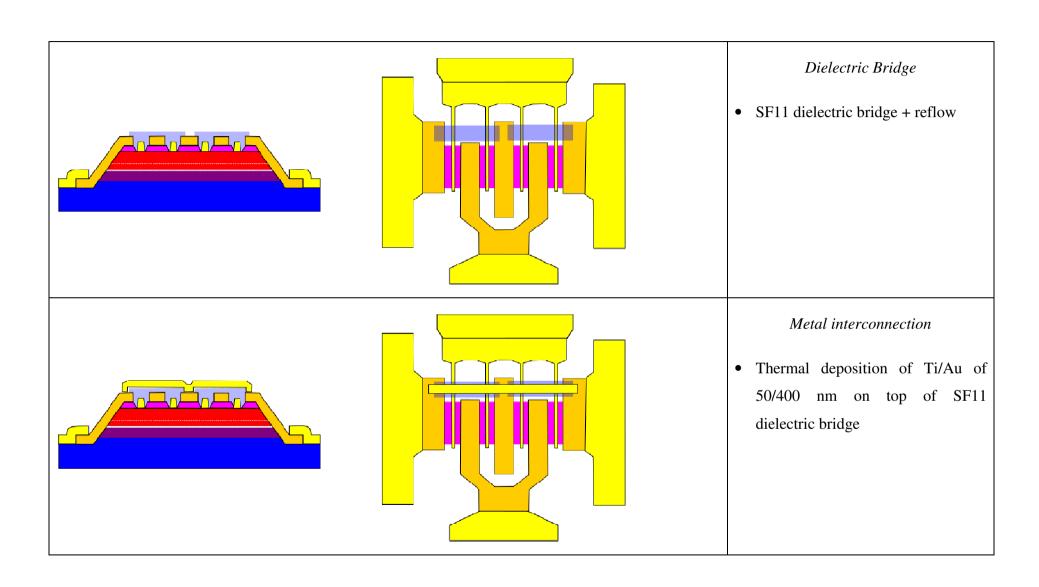

| Figure 4-3 The complete workflow process at the UoM. Shown in the brackets are the                |

|---------------------------------------------------------------------------------------------------|

| sub-group that are responsible for the task                                                       |

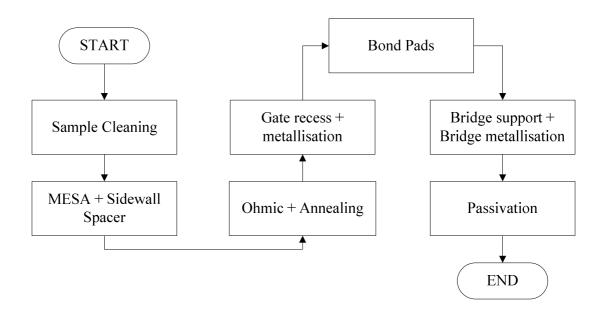

| Figure 4-4 Conventional pHEMT process flow developed at UoM                                       |

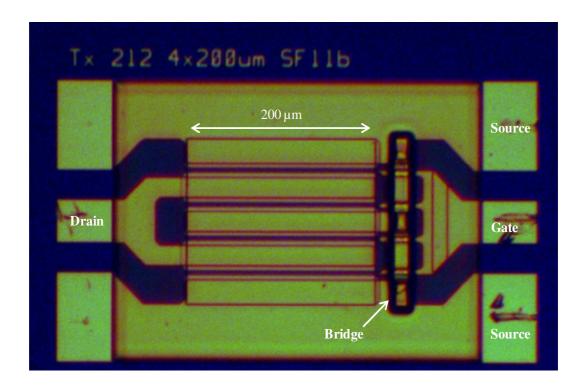

| Figure 4-5 An illustration of a complete bridged 4 x 200 μm device (1 μm gate length)             |

|                                                                                                   |

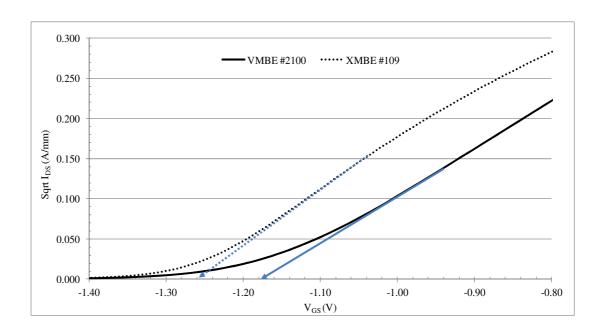

| Figure 4-6 Determination of $V_{th}$ . XMBE #109 = -1.26 V and VMBE #2100 = -1.18 V               |

| 90                                                                                                |

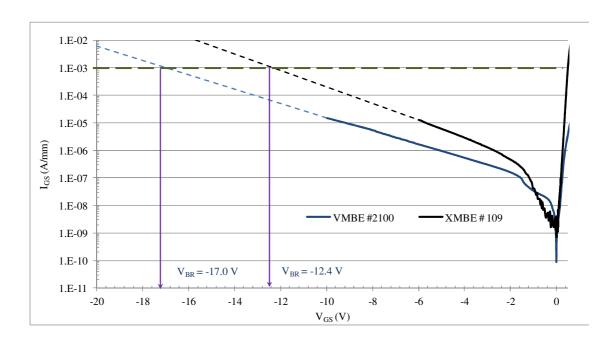

| Figure 4-7 Schottky gate leakage for XMBE #109 (black line) and VMBE #2100                        |

| (blue line). The dotted black and blue lines are the extrapolation for XMBE #109 and              |

| VMBE #2100, respectively Shown in the same figure, the 1 mA/mm breakdown line                     |

| (dotted green line)91                                                                             |

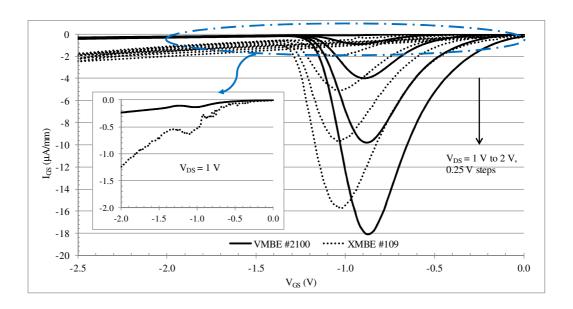

| Figure 4-8 Bell shape curve for both epitaxial structures at $V_{DS} = 1$ to 2 V, steps           |

| 0.25 V. Inset, on-state leakage at $V_{DS} = 1 \text{ V}$                                         |

| Figure 4-9 Transconductance (a) and corresponding $I_{DS}$ curve (b) at $V_{DS} = 1 \text{ V}$ 93 |

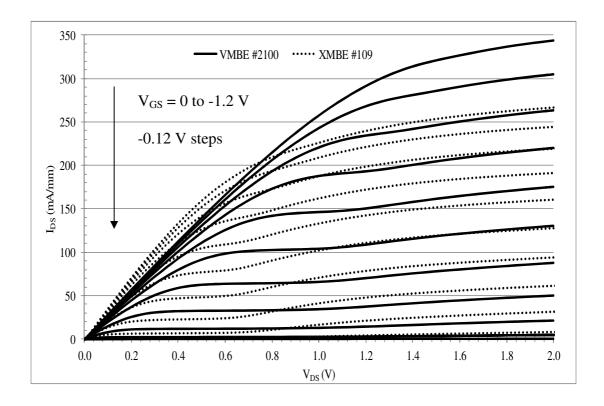

| Figure 4-10 I-V outputs characteristic for both samples. Both devices were biased at              |

| $V_{GS}$ from 0 V to $-1.2$ V with step size of $-0.12$ V (label the curves, which one is 0V      |

| and which one is -1.2V)94                                                                         |

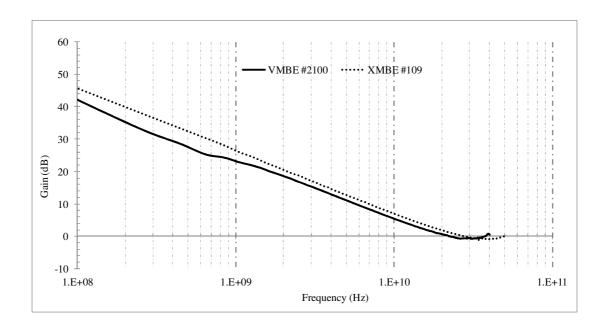

| Figure 4-11 Unity current gain (h21) at $V_{DS} = 1 \text{ V}$                                    |

| Figure 5-1 Epitaxial layer of conventional InGaAs/InAlAs pHEMTs epilayer, XMBE                    |

| #171(thickness not to scale)                                                                      |

| Figure 5-2 Epitaxial layer of improved double δ-doped InGaAs/InAlAs pHEMTs                        |

| epilayer, XMBE #131 (thickness not to scale)                                                      |

| Figure 5-3 Energy band diagram of conventional pHEMTs epilayer, XMBE #171.102                     |

| Figure 5-4 Energy band diagram of improved double δ-doped InGaAs/InAlAs                           |

| pHEMTs epilayer, XMBE #131102                                                                     |

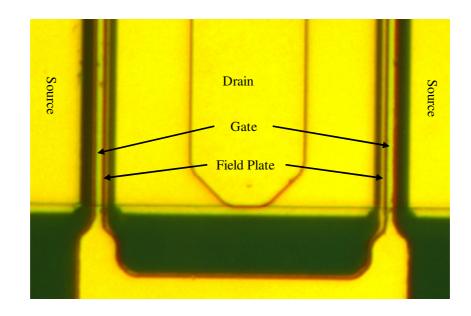

| Figure 5-5 Illustration of dual gate terminal and dual Field Plate structure              |

|-------------------------------------------------------------------------------------------|

| Figure 5-6 Cross section of simplified single gate-FP device                              |

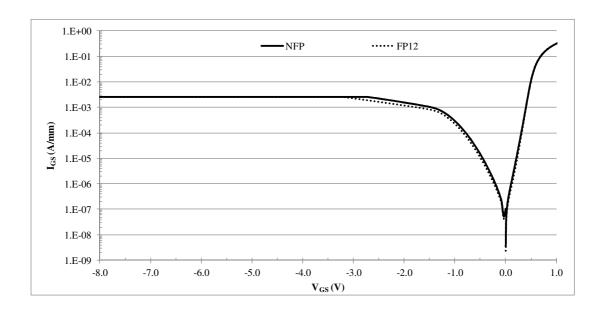

| Figure 5-7 Schottky diode measurements for XMBE #171 showing conventional gate            |

| (NFP) and FP with 1.2 µm extensions (FP12)                                                |

| Figure 5-8 Schottky diode measurements for XMBE #131 showing conventional gate            |

| (NFP) and FP with 1.2 µm extensions (FP12)                                                |

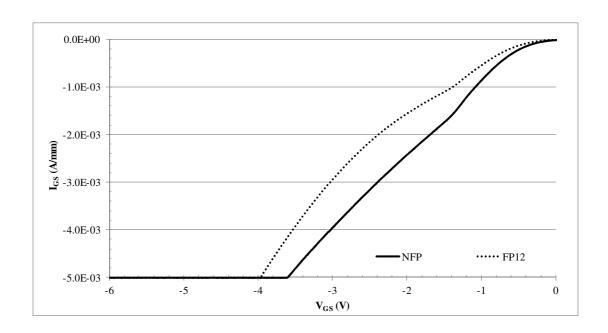

| Figure 5-9 On-state leakage measurement for XMBE #171 showing conventional gate           |

| (NFP) and FP with 1.2 $\mu$ m extensions (FP12) at $V_{DS} = 1 \text{ V}$                 |

| Figure 5-10 On-state leakage measurement for XMBE #131 showing conventional               |

| gate (NFP) and FP with 1.2 $\mu$ m extensions (FP12) at $V_{DS}$ = 1 V. Inset showing the |

| gate leakage due to impact ionisation108                                                  |

| Figure 5-11 Threshold Voltage ( $V_{th}$ ) measurement for XMBE #171 showing              |

| conventional gate (NFP) and FP with 1.2 $\mu$ m extension (FP12) at at $V_{DS}$ = 1 V 109 |

| Figure 5-12 Threshold Voltage ( $V_{th}$ ) measurement for XMBE #131 showing              |

| conventional gate (NFP) and FP with 1.2 $\mu$ m extension (FP12) at $V_{DS}$ = 1 V 109    |

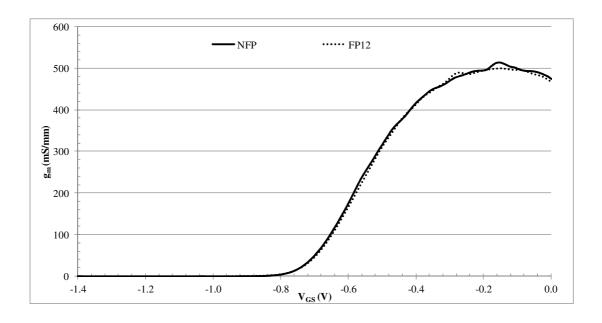

| Figure 5-13 Transconductance $(g_m)$ measurement for XMBE #171 showing                    |

| conventional gate (NFP) and FP with 1.2 µm extension (FP12)                               |

| Figure 5-14 Transconductance $(g_m)$ measurement for XMBE #131 showing                    |

| conventional gate (NFP) and FP with 1.2 µm extension (FP12)                               |

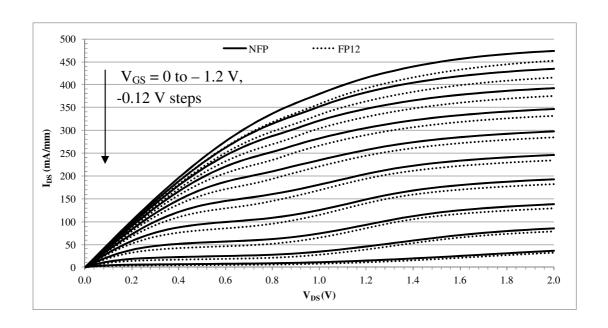

| Figure 5-15 Output current density measurement for XMBE #171 showing                      |

| conventional gate (NFP) and FP with 1.2 µm extension (FP12)                               |

| Figure 5-16 Output current density measurement for XMBE #131 showing                      |

| conventional gate (NFP) and FP with 1.2 µm extension (FP12)                               |

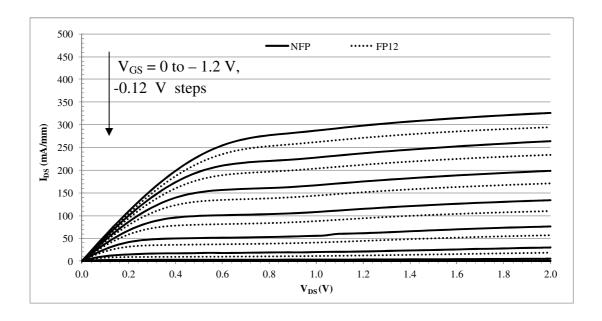

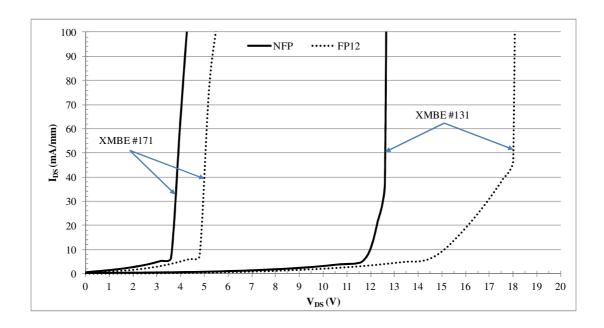

| Figure 5-17 Pinched Off breakdown measurement for XMBE #171 and XMBE #131                 |

| showing conventional gate (NFP) and FP with 1.2 µm extension (FP12) 113                   |

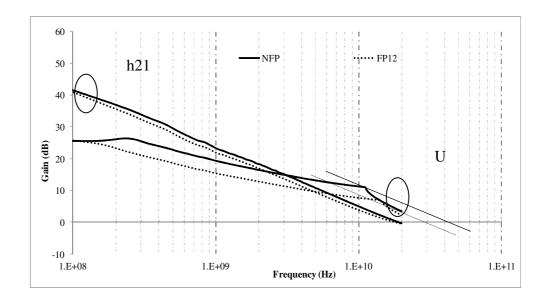

| Figure 5-18 Unity Current Gain (h21) and Unilateral Power Gain (U) measurements                    |

|----------------------------------------------------------------------------------------------------|

| XMBE #171 showing conventional gate (NFP) and FP with 1.2 $\mu m$ extension (FP12)                 |

|                                                                                                    |

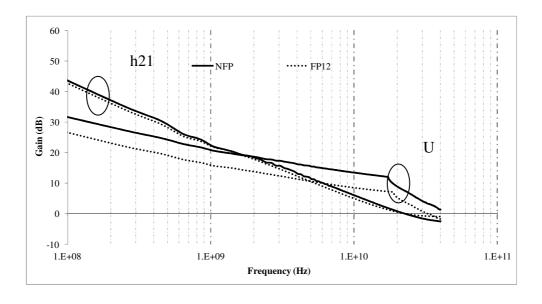

| Figure 5-19 Unity Current Gain (h21) and Unilateral Power Gain (U) measurements\                   |

|                                                                                                    |

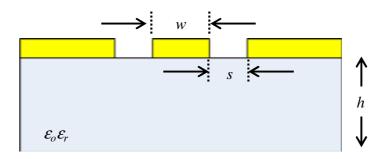

| Figure 6-1 CPW transmission lines dimensions for calculation of the characteristic                 |

| impedance11                                                                                        |

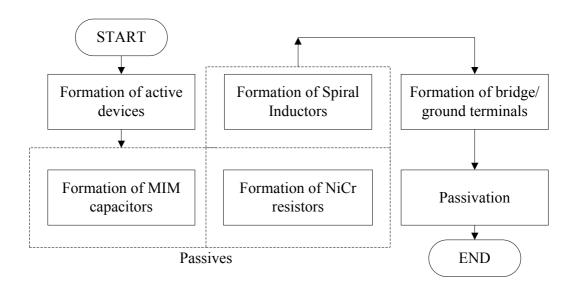

| Figure 6-2 LNA's Process Flow at M&N, UoM                                                          |

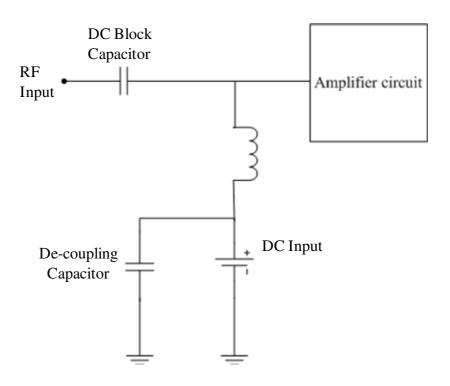

| Figure 6-3 Illustration of DC block and de-coupling capacitors in a RF input matching              |

| circuitry                                                                                          |

| Figure 6-4 Coplanar Wave Guide Metal-Insulator-Metal capacitor                                     |

| Figure 6-5 PCM's C-V measurement result from 1 kHz to 1 MHz frequency using                        |

| Agilent's B1500A Semiconductor Device Analyser                                                     |

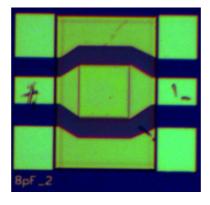

| Figure 6-6 A 8 pF MIM capacitor fabricated at UoM                                                  |

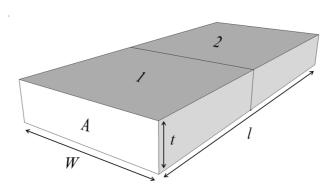

| Figure 6-7 An illustration of a conductor having dimensions $W$ , $l$ and $t$ for the              |

| calculation of its Resistivity $(R)$ and the corresponding 2-dimensional number of                 |

| squares $(l = 2*W)$                                                                                |

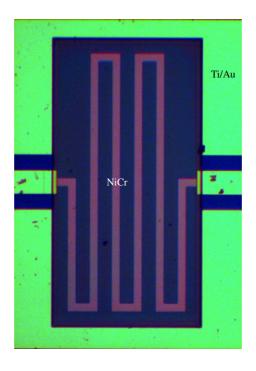

| Figure 6-8 8 k $\Omega$ NiCr resistor by extending the thin film length ( $l$ ) in meandered track |

|                                                                                                    |

| Figure 6-9 Plot of $R_{sh}$ versus thickness for NiCr resistor                                     |

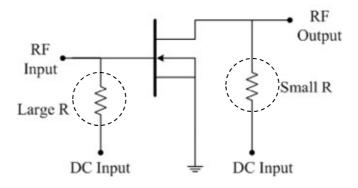

| Figure 6-10 An illustration of the resistor location in a common source amplifier 12               |

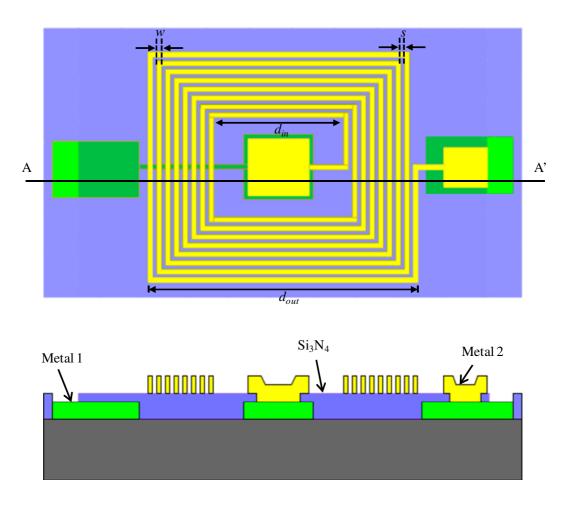

| Figure 6-11 Top and cross view along A-A' line for a square shape MMIC spiral                      |

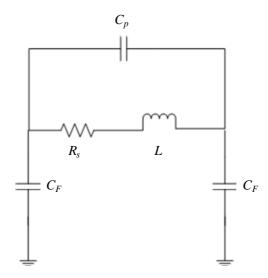

| inductor                                                                                           |

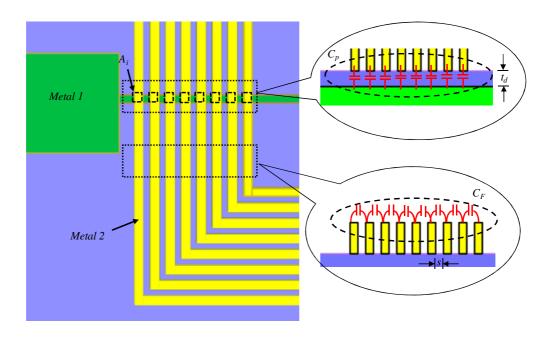

| Figure 6-12 Schematic of equivalent circuit model for spiral inductor                              |

| Figure 6-13 Illustration of $C_p$ and $C_F$                                                        |

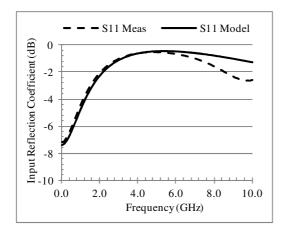

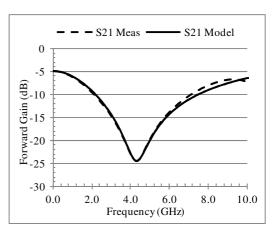

| Figure 6-14 Curve fitting between measured and modelled S-parameters for 14 nH                               |

|--------------------------------------------------------------------------------------------------------------|

| spiral inductor                                                                                              |

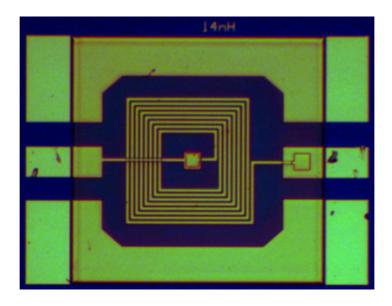

| Figure 6-15 Spiral inductor fabricated at the University of Manchester                                       |

| Figure 6-16 Schematic diagram of SSLNA using 4 x 200 µm InP pHEMTs                                           |

| Figure 6-17 Schematic diagram of HG-DSLNA using 4 x 200 µm InP pHEMTs 136                                    |

| Figure 6-18 Schematic diagram of MG-DSLNA designed using 4 x 200 μm InP                                      |

| pHEMTs137                                                                                                    |

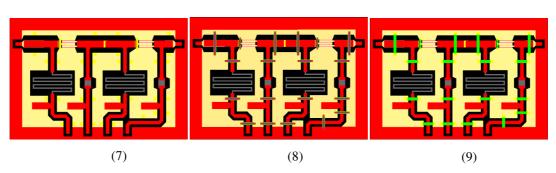

| Figure 6-19 Mask layout for SSLNA (1) MESA, (2) Ohmic, (3) Gate, (4) Metal 1, (5)                            |

| Si <sub>3</sub> N <sub>4</sub> Deposition and etch, (6) NiCr, (7) Metal 2, (8) Dielectric Bridge, (9) Metal  |

| Bridge, (10) Passivation, and (11) Fabricated MMIC SSLNA                                                     |

| Figure 6-20 Mask layout for HG-DSLNA (1) MESA, (2) Ohmic, (3) Gate, (4) Metal                                |

| 1, (5) Si <sub>3</sub> N <sub>4</sub> Deposition and etch, (6) NiCr, (7) Metal 2, (8) Dielectric Bridge, (9) |

| Metal Bridge, (10) Passivation, and (11) Fabricated MMIC HG-DSLNA 140                                        |

| Figure 6-21 Mask layout for MG-DSLNA (1) MESA, (2) Ohmic, (3) Gate, (4) Metal                                |

| 1, (5) Si <sub>3</sub> N <sub>4</sub> Deposition and etch, (6) NiCr, (7) Metal 2, (8) Dielectric Bridge, (9) |

| Metal Bridge, (10) Passivation, and (11) Fabricated MMIC MG-DSLNA 141                                        |

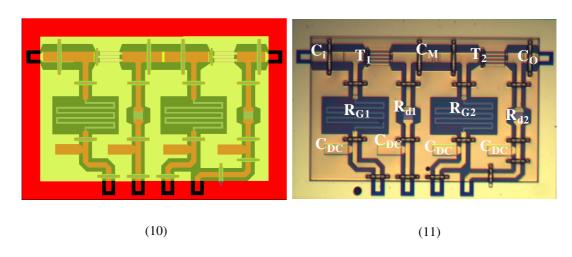

| Figure 6-22 S-parameter and noise measurement setup (a) A complete setup for noise                           |

| figure measurement and (b) A close up calibration standard at two port network using                         |

| CS-5 calibration substrate                                                                                   |

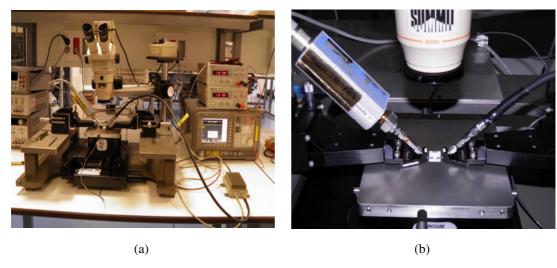

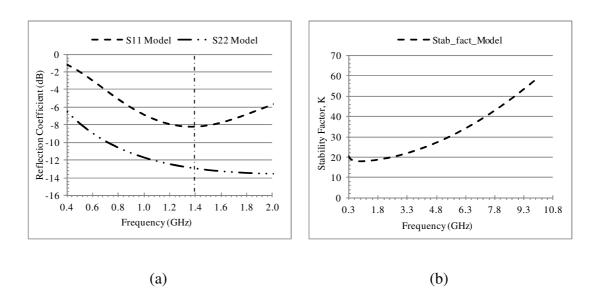

| Figure 6-23 Comparison of measured vs. simulated for SSLNA (a) noise figure (NF)                             |

| against frequency, (b) gain (S21) against frequency (c) and (d) input/output reflection                      |

| coefficient (S11, S22) against frequency, and (e) of Rollet stability factor (K) against                     |

| frequency                                                                                                    |

| Figure 6-24 Comparisons of measured and simulated data for HG-SSLNA (a) noise                                |

| figure (NF) against frequency, (b) gain (S21) against frequency                                              |

| Figure 6-25 Simulated data for HG-DSLNA (a) Input and output reflection coefficient     |

|-----------------------------------------------------------------------------------------|

| (S11 & S22) against frequency, (b) Rollet stability factor (K) against frequency 146    |

| Figure 6-26 Comparisons of simulated and measured data for MG-SSLNA (a) noise           |

| figure (NF) against frequency, (b) gain (S21) against frequency                         |

| Figure 6-27 Simulated data for MG-DSLNA (a) Input and output reflection coefficient     |

| (S11 & S22) against frequency, (b) of Rollet stability factor (K) against frequency 148 |

# LIST OF ABBREVIATIONS

**2-DEG** 2-Dimensional Electron Gas

ADS Advanced Design System

AlGaAs Aluminium Galium Arsenide

**CMOS** Complementary Metal Oxide Semiconductor

**CPW** Coplanar Wave Guide

**CS** Common-Source

**DI water** De-ionised water

**DSLNA** Double Stage Low Noise Amplifier

**DUT** Device Under Test

**e-beam** Electron beam

**EDA** Electronic Design Automation

**FET** Field Effect Transistor

**FP** Field plate

**Ga** Galium

GaAs Galium Arsenide

Ge Germanium

**HEMT** High Electron Mobility Transistor

**HG-DSLNA** High Gain Double Stage Single-ended LNA

IC Integrated Circuit

IC-CAP Integrated Circuit Characterisation and Analysis Program

**InAlAs** Indium Aluminium Arsenide

InGaAs Indium Galium Arsenide

**InP** Indium Phosphide

IPA Isopropanol

**LNA** Low Noise Amplifier

**ISS** Impedance Standard Substrate

M&N Microelectronic & Nanostructures

MBE Molecular Beam Epitaxy

MESFET Metal Semiconductor Field Effect Transistor

MG-DSLNA Moderate Gain Double Stage Single-ended LNA

MIC Microwave Integrated Circuit

MIM Metal-insulator-metal

MMIC Monolithic Microwave Integrated Circuit

MOCVD Metalorganic Chemical Vapour Deposition

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

**NF** Noise Figure

*NF<sub>min</sub>* Minimum Noise Figure

**NiCr** Nickel Chromium or Nichrome

nMOS n-type channel MOS

**PA** Power Amplifier

**PCM** Process Control Module

**pHEMT** pseudomorphic High Electron Mobility Transistor

PMGI Polymethylglutarimide

**QW** Quantum Well

**RA** Radio Astronomy

**RF** Radio Frequency

**RT** Room Temperature

**S-parameter** Scattering parameter

SA Succinic Acid

**S-G-D** Source-Gate-Drain

Si Silicon

**SiGe** Silicon Germanium

**SKA** Square Kilometre Array

**SNR** Signal to Noise Ratio

**SOLT** Short-Open-Load-Thru

SSLNA Single Stage Single-ended LNA

TCR Temperature Coefficient Resistance

TE Thermionic Emission

**TFE** Thermionic Field Emission

**TLM** Transfer Length Method

**UoM** University of Manchester

**UV** Ultraviolet

**VLA** Very Large Array

VNA Vector Network Analyser

### **ABSTRACT**

The University of Manchester

Candidate : Muammar Mohamad Isa Degree : Doctor of Philosophy (PhD)

Title : Low Noise Amplifiers using highly strained InGaAs/InAlAs/InP

pHEMT for implementation in the Square Kilometre Array (SKA)

Date : 17<sup>th</sup> October 2012

The Square Kilometre Array (SKA) is a multibillion and a multinational science project to build the world's largest and most sensitive radio telescope. For a very large field of view, the combined collecting area would be one square kilometre (or 1,000,000 square metre) and spread over more than 3,000 km wide which will require a massive count of antennas (thousands). Each of the antennas contains hundreds of low noise amplifier (LNA) circuits. The antenna arrays are divided into low, medium and high operational frequencies and located at different positions to boost up the telescope's scanning sensitivity.

The objective of this work was to develop and fabricate fully on-chip LNA circuits to meet the stringent requirements for the mid-frequency array from 0.4 GHz to 1.4 GHz of the SKA radio astronomy telescope using Monolithic Microwave Integrated Circuit technology (MMIC). Due to the number of LNA reaching figures of millions, the fabricated circuits were designed with the consideration for low cost fabrication and high reliability in the receiver chain. Therefore, a relaxed optical lithography with  $L_g$  = 1  $\mu$ m was adopted for a high yield fabrication process.

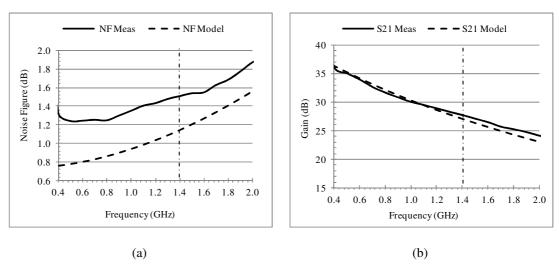

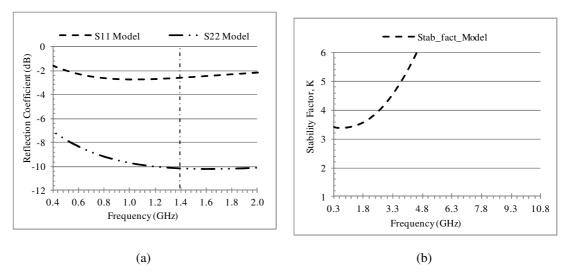

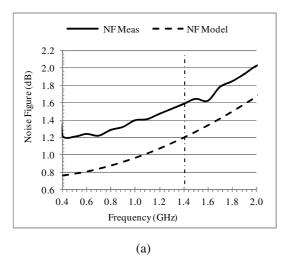

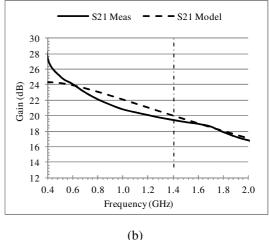

Towards the fulfilment of the device's low noise characteristics, a large number of device designs, fabrication and characterisation of InGaAs/InAlAs/InP pHEMTs were undertaken. These include optimisations at each critical fabrication steps. The device's high breakdown and very low gate leakage characteristics were further improved by a combination of judicious epitaxial growth and manipulation of materials' energy gaps. An attempt to increase the device breakdown voltage was also employed by incorporating Field Plate structure at the gate terminal. This yielded the devices with improvements in the breakdown voltage up to 15 V and very low gate leakage of 1  $\mu$ A/mm, in addition to high transconductance ( $g_m$ ) characteristic. Fully integrated double stage LNA had measured NF varying from 1.2 dB to 1.6 dB from 0.4 GHz to 1.4 GHz, compared with a slightly lower NF obtained from simulation (0.8 dB to 1.1 dB) across the same frequency band.

These are amongst the attractive device properties for the implementation of a fully on-chip MMIC LNA circuits demonstrated in this work. The lower circuit's low noise characteristic has been demonstrated using large gate width geometry pHEMTs, where the system's noise resistance  $(R_n)$  has successfully reduced to a few ohms. The work reported here should facilitate the successful implementation of rugged low noise amplifiers as required by SKA receivers.

### **DECLARATION**

No portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## **COPYRIGHT STATEMENT**

The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

The ownership of certain Copyright, patents, designs, trademarks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy. (http://www.campus.manchester.ac.uk/medialibrary/policies/intellectualproperty.pdff)

.

In any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses.

#### **ACKNOWLEDGEMENTS**

Praise to Allah for endowing me with health, patience, and knowledge throughout the years required to complete this work.

I would like to express my deepest gratitude to my supervisor, Professor Mohamed Missous for his encouragement and extensive guidance in all phases of this research. I am deeply indebted and grateful to the M&N group at The University of Manchester, particularly to Dr. James Sexton, Dr Yan Lai, Mr. Kawa Ian, Mr Malachy Mcgowan and Mr. John Bailey for their useful discussion and substantial assistance in the experimental work throughout this research. I would also like to express my deepest gratitude to Dr. Sanae Boulay for her assistance and help at the beginning of my study.

It is my pleasure to pay tribute to the Professor Giovanni Verzellesi and his team, from the Università di Modena e Reggio Emilia, Italy for the collaborative work on the Field Plate design, which was very beneficial to my research. I also convey my special thanks to Professor Eduardo Artal and his team from the University of Cantabria, Spain, for their great contributions in the measurement of the LNA's noise and S-parameters.

Special thanks to my wife, Mrs. Norhawati Ahmad, who is also my research group colleague, for her dedication, love and persistent confidence in me. I thank her for her selfless encouragement and endless patience throughout my PhD journey.

Finally, I would like to acknowledge my sponsors, the Ministry of Higher Education, Malaysia (MOHE), and Universiti Malaysia Perlis (UniMAP). This research would not have been possible without their financial support.

# **DEDICATION**

To my caring parents.....

To my loving wife.....

To my sovesy children....

## **PUBLICATIONS**

- 1. **M. Mohamad Isa**, Y. Lai, D. Saguatti, M. Missous "Improvement of breakdown voltage in InGaAs/InAlAs/InP pHEMT using band gap engineering and field modulating plate structure" in UK Semiconductor 2012 Conference, The University of Sheffield, 4-5 July 2012

- 2. F. Packeer, **M. Mohamad Isa** and M. Missous "Fabrication and Characterization of Tensile In0.3Al0.7As Barrier and Compressive In0.7Ga0.3As Channel pHEMTs Having Extremely Low Gate Leakage for Low Noise Applications" in UK Semiconductor 2012 Conference, The University of Sheffield, 4-5 July 2012

- 3. W M Jubadi, **M. Mohamad Isa** and M. Missous, "An accurate 2D Physical Model for highly strained InAlAs/InGaAs pHEMTs" in UK Semiconductor 2012 Conference, The University of Sheffield, 4-5 July 2012

- 4. N. Ahmad, **M. Mohamad Isa** and M. Missous, "Modelling, Design and Testing of Novel InGaAs-InAlAs Low Noise Amplifier for Radio Astronomy Applications" in UK Semiconductor 2012 Conference, The University of Sheffield, 4-5 July 2012

- 5. **M. Mohamad Isa**, M. Missous and J. Sexton, "A Large Band gap, High breakdown In0.3Al0.7As-In0.7Ga0.3As pHEMT for low power mobile communications system", Postgraduate Poster Conference and Industrial Advisory Group Meeting, The University of Manchester, 30 Nov 2011.

- 6. N. Ahmad, **M.Mohamad Isa** and M. Missous "Modelling and Design of MMIC Low Noise Amplifier using an in-house InP-based Process", Postgraduate Poster Conference and Industrial Advisory Group Meeting, The University of Manchester, 30 Nov 2011

- 7. **M. Mohamad Isa**, M. Missous, Y. Lai, J. Sexton, and S. Boulay, "Fabrication of Low Noise InAlAs-InGaAs pHEMT for SKA application (300MHz to 2GHz)", in UK Semiconductor 2011 Conference, The University of Sheffield, 6-7 July 2011.

- 8. Y. Lai, **M. Mohamad Isa** and M. Missous, "Pulsed DC characterisation of high breakdown, low leakage InAlAs/InGaAs/InP pHEMTs" in UK Semiconductor 2011 Conference, The University of Sheffield, 6-7 July 2011.

- 9. **M. Mohamad Isa**, N. Ahmad, M. Missous, Y. Lai, J. Sexton, and S. Boulay, "Fabrication of Low Noise InAlAs-InGaAs pHEMT for SKA application (300MHz to 2GHz)", in IMiEJS 2011 Conference, Athlone Institute of Technology (AIT), Ireland, 9-11 June 2011.

- Saguatti, D., Chini, A., Verzellesi, G., Isa, M. M., Ian, K. W., and Missous, M., "Improvement of Breakdown and DC-to-Pulse Dispersion Properties in Field-Plated InGaAs-InAlAs pHEMTs", International Conference on Indium Phosphide & Related Materials (IPRM), 22 26 May, 2011 Berlin, Germany, pp. 84-86.

- 11. **M. Mohamad Isa,** D. Saguatti, G. Verzellesi, A. Chini, K.W. Ian, M. Missous, "*Fabrication of novel high frequency and high breakdown InAlAs-InGaAs pHEMTs*," in 8th International Conference on Advanced Semiconductor Devices & Microsystems (ASDAM), 2010, 25 27 Oct. 2010, pp. 41-44.

- 12. **M. Mohamad Isa,** D. Saguatti, G. Verzellesi, A. Chini, K.W. Ian, M. Missous, "Novel high frequency and high breakdown InAlAs-InGaAs pHEMTs for low noise and high power applications", in UK Semiconductor 2010 Conference, The University of Sheffield, 7-8 July 2010.

- 13. D. Saguatti, **M. Mohamad Isa,** K. W. Ian, and M. Missous, . " *InAlAs-InGaAs pHEMT TCAD Simulation and Optimization*", in UK Semiconductor 2010 Conference, The University of Sheffield, 7-8 July 2010.

- 14. Saguatti, D., Chini, A., Verzellesi, G., Isa, M. M., Ian, K. W., and Missous, M., "TCAD optimization of field-plated InAlAs-InGaAs HEMTs", International Conference on Indium Phosphide & Related Materials (IPRM), 31 May 4 June 2010. Takamatsu Symbol Tower, Kagawa, Japan, pp. 1-3.

# **CHAPTER 1**

#### INTRODUCTION

#### 1.1 OVERVIEW OF THE SKA

Over the last few decades, the desire to learn more about our solar system, and more fundamentally, how the universe began, led to the launch of large astronomy projects and deep space probes. Although these missions have yielded important scientific discoveries and improved our understanding of the cosmos, they have not explored the most fundamental questions about the universe. These include: understanding dark energy, general relativity in extreme conditions, and how the universe was shaped into its current form; from immediately after the big bang to the present day.

The rapid advancement in technology has provided the means for space exploration equipment to deliver more meaningful data about the cosmos than ever before, of which the Square Kilometre Array (SKA) is one example. The project is destined to be a multibillion dollar, multinational science project, for establishing the world's largest and most sensitive radio telescope [1]. Work has already started in the science, engineering and associated industries to drive the development of technology in antennas, signal transport, signal processing, software and computing.

Central to the concept of the SKA is a deep understanding of the sensitivity of a radio telescope. The sensitivity (S) of a telescope is dependent on its effective collecting area  $(A_{eff})$  and the receiver equivalent system temperature  $(T_{sys})$  [2]:

$$S = \frac{A_{eff}}{T_{svs}}$$

Equation 1-1

From Equation 1-1, the sensitivity of a Radio Telescope system is directly proportional to the system's effective collecting area. The equation also shows that the sensitivity can be improved if the system is operated at low temperature.

Since the radio signals originating from cosmic sources are very faint in nature, astronomers require a highly sensitive and physically large telescope in order for the very small signals to be detected. However, building such a large telescope receiver is impractical. The most practical way to increase the sensitivity is by arranging a number of smaller-sized receivers in an array, which synthesises a larger telescope receiver.

The shift from a single dish to arrays of receiver dishes began in 1980 with the implementation of the Very Large Array (VLA) radio astronomy telescope. The VLA system consists of 27 independent antennas with each dish having a diameter of 25 metres. The antennas are arrayed along the three arms of a Y-shape, with each arm measuring 21 km in length [3].

Figure 1-1 Sensitivity of the SKA with world leading telescopes [4]

Over the years, more radio telescopes were built using the similar concept of arrays of receivers with a larger collection area for greater sensitivity. Figure 1-1 illustrates various types of radio telescope and the transition from a single large parabolic dish to an array of smaller dishes. The projection ends with the SKA, which is expected to have a relative sensitivity one hundred times better than the best of the existing radio interferometers today.

Another alternative to increase the system sensitivity is by lowering the system noise temperature (refer Equation 1-1). It is anticipated that the SKA will have a lower noise temperature by cryogenically cooled the receiver modules [5], where the individual sensitivity of each receiver subsystem associated with few thousands Low Noise Amplifiers (LNAs) can be maximised. When the LNAs are cryogenically cooled, the circuit low noise characteristics can be improved to a greater extend and consequently increasing the system sensitivity.

Since large numbers of LNAs are needed (several thousands), considering the cost and complexity of the cryogenic cooled system (which is another extension of greater challenge), the Room Temperature (RT) application is then considered. Therefore, the focus of this SKA project, for the reason mentioned above, is assessed with respect to its RT application [6].

#### 1.2 THE CONCEPT OF THE SKA

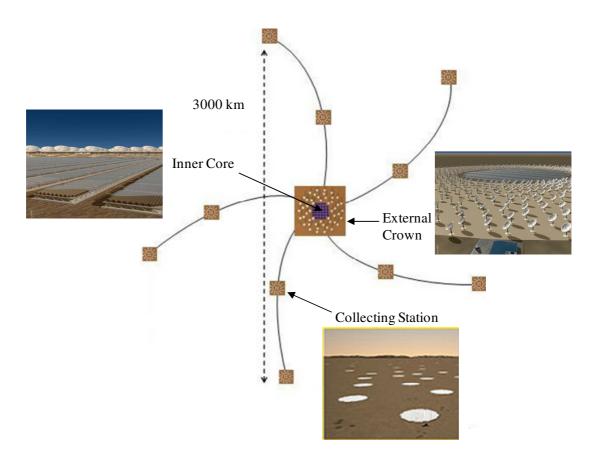

At present, the complete bandwidth of the SKA ranges from 70 MHz to 10 GHz [7]. To achieve such a wide bandwidth, a massive collecting area that still maintains a high signal to noise ratio (SNR) is achieved by arrays of antennas. These antennas will be arranged in a spiral shape and are distributed in three regions with a diameter extending to 3000 km [8, 9], as shown in Figure 1-2.

Figure 1-2 An illustration of antenna dislocation [8]

The spiral core will be formed by two topologies of antennas that become half of the collecting area. The core will be smaller in diameter and will contain a dense of aperture arrays for low frequency radio-signals, and will be surrounded by parabolic dishes, which are used for high frequency radio-signals. Even though the resolution will be sacrificed when the aperture arrays are close to each other, this arrangement will capture characteristic information, such as object brightness and temperature. The planar arrays are fixed but they can be steered electronically, whereas the parabolic dishes can be moved mechanically to cover the entire horizon.

Along the spiral arms, several stations are located extending out to 150 km. Each station will contain hundreds of dense aperture arrays for medium frequency radio signals.

The outer region of the SKA will cover a large area between 180 km to 3000 km. This region will include five spiral arms along with aperture arrays that are

combined into stations. There will be an increase in separation of the stations in the outer region of the spiral arms

As briefly described in the above, the SKA will use three different types of antenna across the frequency bandwidth - high frequency dishes for 1.2 to 10 GHz, mid frequency aperture array from 0.4 to 1.4 GHz, and low frequency aperture array from 70 to 450 MHz [10]. Figure 1-3 illustrates the separation and the key observations for each frequency region.

Figure 1-3 The Sensitivity of the SKA Radio Telescope (AA = Aperture array) [10]

The stringent requirement of the SKA for a wide field of view and large collecting area demands a high linearity, low power dissipation, and low-noise phased-array receiving block. In order to amplify the weak signals received by the antenna, a low noise amplifier (LNA) is placed at each receiver end and transfers the signal to the remaining receiving circuits to fulfil the SKA requirements. The large number of receivers adds a significant cost consideration to the design of the unit element to keep the budget under control.

Moreover, cooling of the receiver modules in order to improve their noise temperature has not been fully explored, as the running costs of cooling such a massive collector array would most likely make the cryogenic methods an economically unfeasible option. For this reason the technology being developed for the SKA is being assessed in respect of its room temperature operating properties [11].

Therefore, in this project, the aim is to develop the front-end system using a novel InP-based pseudomorphic High Electron Mobility Transistor (pHEMT) technology for the design and fabrication of LNAs, optimised in the band 0.4 - 1.4 GHz in meeting the mid frequency performance requirements of the SKA in terms of performance, cost and power budget.

## 1.3 OBJECTIVES

The key objective of this work focuses on the development of Indium Galium Arsenide/Indium Aluminium Arsenide/Indium Phosphide (InGaAs/InAlAs/InP) devices for low noise applications at radio frequencies. The adaptation of band-gap engineering in conjunction with low cost I-line optical photolithography is the prime focus in achieving low noise devices. This is an alternative to highly scaled and sophisticated technologies such as nano-scaled Complementary Metal Oxide Semiconductor (CMOS), which involves more complicated steps and not cost effective with respect to this application. In terms of manufacturability, the requirements for the optical lithography method adopted in this work are less stringent (in terms of feature sizes and mask costs) than deep Ultraviolet (UV) lithography, especially those used in Si technology. Several types of LNA circuits, which employed this technology will be presented here as proof of the suitability of the technology and also to provide a starting point for future applications in microwave communication systems. The LNA design specifications are detailed in the following section.

# 1.3.1 LNA Specifications

All the work presented in this thesis converged into one purpose, which is to obtain a very low Noise Figure (*NF*) amplifiers operating at Room Temperature (RT) using the 1 µm highly strained channel based on InGaAs/InAlAs/InP pHEMT technology

developed at the University of Manchester (UoM). The large gate peripheries are advantageous from the perspective of manufacturing cost and throughput where expensive electron-beam (e-beam) lithography can certainly be avoided.

The LNAs in this project are determined to operate in the mid frequency range (0.4 GHz to 1.4 GHz) of the SKA. The same frequency band has also found its application in medium frequency commercial applications such as Global Positioning System (GPS) and mobile communication.

The paramount importance in terms of specification in the design is the *NF*. The *NF* of the project is set to be less than 1 dB over the chosen frequency bandwidth. However, in the final SKA specification, the *NF* is further tightened to a lower value of 0.5 dB. The lower *NF* is highly desirable for the system as a whole, where low *NF* will only need smaller and consequently cost effective collection area.

The amplifiers must also be unconditionally stable over the entire operational bandwidth. Given that the oscillation is knowingly common in high gain circuit [12], the gain of the circuit is determined to be in modest value of about 25 dB to 35 dB.

Furthermore, the amplifier is configured to consume power of less than 150 mW. The commonly used load impedance of  $50 \Omega$  is dedicated for the circuit to facilitate the interfacing with the measurement tools and integration with other components in the system.

#### 1.4 THESIS OUTLINE

Chapter 2 begins with an elaborative study of semiconductor materials suitable for high frequency operation, leading to in-depth discussions concerning appropriate devices for the advanced materials discussed. The discussion continues with an extensive study of the physics and operation of the devices. At the end of the chapter, some important physical parameter extraction methods are highlighted, as these methods are used throughout this work.

**Chapter 3** discusses the performed optimisation steps of the in-house pHEMT's fabrication steps. The task begins with the development of an optimal gate recess

recipe using highly selective succinic acid etchant for highly uniform Schottky contacts. The results from this study are then used for the design of the gate-to-channel isolation technique to minimise the gate leakage current of the device. In addition, a thermal stability study is performed to investigate the reliability of the device during high temperature processing.

**Chapter 4** presents the fabrication and characterisation of a novel low-leakage high-breakdown InGaAs/InAlAs/InP pHEMT, which is targeted for implementation in the LNA design as described in **Chapter 6**. To complete the discussion, comprehensive comparisons are made with other published device data prepared for the same purpose.

**Chapter 5** highlights the adaptation of a field plate structure to improve the device breakdown voltage, which is beneficial for low noise high power applications. For comparison, the DC and RF characteristics of the device are evaluated with respect to the conventional narrow band gap channel InGaAs/InAlAs/InP device.

**Chapter 6** provides the full description of the fabrication process of three LNA circuits utilising the low noise device detailed in **Chapter 4**. At the beginning of the chapter, the fabrication and characterisation of passive devices are described, including out of target passives which caused a mismatch in the circuit's noise performance.

**Chapter 7** summarises the work discussed in this project, stressing the potential from the project and the consequent suitability of the developed devices and LNA circuits to meet the requirements of the SKA. Finally, some additional work is suggested for further improvement and extension from the findings in this thesis.

# **CHAPTER 2**

# LITERATURE REVIEW

#### 2.1 INTRODUCTION

Lower cost and higher levels of integration have undoubtedly allowed Silicon (Si) technologies to become the workhorse of semiconductor material in the digital Integrated Circuit (IC) prime markets in the electronic age. This unrivalled status is mostly due to its superior chemical and electrical characteristics. However, due to Si low intrinsic mobility, other materials are more suitable for future high-speed and low-power applications at high frequencies. For example, III-V materials are having significantly higher intrinsic mobility and can substitute Si as a promising solution for high speed applications. III-V materials can also be designed into suitable device structures by means of adapting similar processing techniques used in Si technology such as lithography and etching [13]. In this regard, III-Vs are considered far more practical than other non-Si materials for future high-speed applications. Indeed, both Galium Arsenide (GaAs) and Indium Galium Arsenide (InGaAs) materials are possible future candidates in the post sub-22 nm node CMOS [14].

This chapter will highlight the properties and operational principles of suitable devices for high speed, low noise applications, derived from III-V materials. Several important parameter extraction methods are also included at the end of the chapter.

#### 2.2 HIGH FREQUENCY MATERIALS

III-V compounds have a number of desirable material characteristics which make them superior to Si in high-frequency applications. The primary characteristic is high carrier electron mobility. This contributes to making the materials very responsive to rapid changes in applied electric fields. Furthermore, since the mobility of electrons far exceeds that of the holes, electrons are invariably used in high frequency devices. Another useful property of III-V compounds is the higher band gap energy compared to Si, allowing the synthesis of insulating and semi-insulating materials that are essential in high frequency circuits. The rich variety of available materials also allow for lower band gap materials with superior transport characteristics and very high mobilities.

However, for a low band gap material, there are a large number of carriers that have sufficient thermal energy to overcome the metal-semiconductor junction barrier, resulting in higher leakage devices when compared with Si. On the other hand, the band gap should not exceed to a greater extent as it may require high thermal energy to turn ON the device. Nevertheless, a suitable combination of small and large band gap materials can be chosen so that the leakage or the required thermal energy does not become a concern.

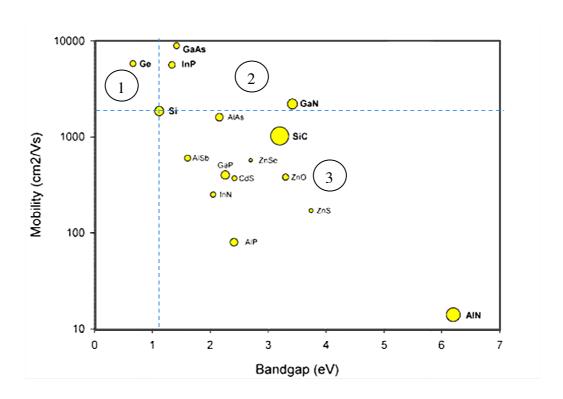

Figure 2-1 shows the low field electron mobility versus energy band gap for common semiconductors. The semiconductors consist of elemental (Ge and Si) and compound semiconductors (binary compounds such as II-VI and III-V group elements). In the diagram, most of the direct and low band gap materials are located in the first quadrant and have electron mobility higher than that of Si. However, as mentioned above, they are not always the favourable candidates due to their lower energy gap as they lead to leakier device characteristics. The materials in the third quadrant have a higher energy gap than that of Si, but are not good candidates for active channels, since the electron mobility is so much lower than in Si. This characteristic leaves two materials in the second quadrant, where the electron mobility and band gap energy are higher than those of Si. The two compound semiconductors are the GaAs and InP. Both are binary alloys formed from group III and group V element semiconductors. The characteristics of Si, GaAs and InP are shown in Table 2-1. Included in the table are the electrical properties of the high mobility InP-based ternary compound, In<sub>0.53</sub>Ga<sub>0.47</sub>As, the importance of which will be detailed later.

Figure 2-1 Electron mobility at low field strength versus band gap energy for various semiconductor materials. The line represents electron mobility and energy band gap levels higher than Si. The second quadrant materials are the most suitable compound semiconductors for high frequency applications, to replace Si in bulk material (except GaN because E<sub>g</sub> is high) [15].

By referring to Table 2-1, the energy band gaps for GaAs and InP (1.42 eV and 1.35 eV respectively) are higher than that of Si. Even though this value is higher than Si, it is still sufficiently small when compared to other semiconductor materials; therefore, electrons are easily excited into the conduction band for effective device conduction. Referring to carrier mobility, InP has an electron mobility three times higher than that of Si, whereas GaAs has a mobility that is almost six times higher than Si. There are many advantages associated with this high carrier mobility. For instance, when considering low noise applications in higher mobility materials, the random noise events resulting from carrier collisions within the lattice are less significant relative to the drift current produced by the carriers [16].

Table 2-1 Comparisons between Si and high frequency materials [17-20].

| Characteristics                                     | Si    | GaAs  | InP   | In <sub>0.53</sub> Ga <sub>0.47</sub> As |

|-----------------------------------------------------|-------|-------|-------|------------------------------------------|

| Lattice Constant (Å)                                | 5.431 | 5.653 | 5.869 | 5.869                                    |

| Band gap (eV)                                       | 1.12  | 1.42  | 1.35  | 0.71                                     |

| Electron Saturation velocity (10 <sup>7</sup> cm/s) | 1.0   | 1.0   | 1.3   | 0.7                                      |

| Electron mobility at 300 K (cm <sup>2</sup> /V.s)   | 1,500 | 8,500 | 4,500 | 12,000                                   |

| Hole mobility at 300 K (cm <sup>2</sup> /V.s)       | 400   | 400   | 150   | 300                                      |

| Critical breakdown field (MV/cm)                    | 0.3   | 0.4   | 0.5   | 0.2                                      |

| Relative dielectric constant                        | 11.8  | 12.8  | 12.5  | 13.8                                     |

However, compared to GaAs and InP, an even higher electron mobility can be achieved from In<sub>0.53</sub>Ga<sub>0.47</sub>As which is lattice matched to InP. Even though the energy gap is less than Si, the high carriers' thermal excitation from valance band to conduction band is compensated by this superior electron mobility property. Through the advancement in epitaxial growth, this material (or other materials lattice matched to InP) can be grown on top of an InP substrate, therefore this compound is sometimes called InP-based material. Further discussion of this material is shown in subsequent sections.

Above all, when compared to the Si-based devices, these materials are determined to have more current gain, mainly due to their high electron mobility; if the same input voltage is applied, higher output current can flow from these materials and consequently higher gain can be achieved.

Furthermore, the high electron mobility property implies that the carriers can navigate through the device geometry in a very short transit time, thereby promoting its high frequency application. A high carrier velocity will allow the device to be responsive to high frequency excitation. A comparison of carrier drift velocity versus applied electric field between Si, GaAs, InP and In<sub>0.53</sub>Ga<sub>0.47</sub>As is shown in Figure 2-2. In low field-strength operation, Si is shown to have the lowest drift velocity whereas In<sub>0.53</sub>Ga<sub>0.47</sub>As is illustrated to have the highest. However, at high field operation, the carrier velocity for GaAs, InP and In<sub>0.53</sub>Ga<sub>0.47</sub>As drop to values that are comparable to the Si saturation velocity. The saturation velocities of undoped materials are also shown in Table 2-1.

Figure 2-2 Electron drift velocity of common semiconductor materials at low field operation [20]

This phenomenon occurs because in GaAs, InP and In<sub>0.53</sub>Ga<sub>0.47</sub>As materials, there exist more than one local minima in the energy band gap. Most of the time (at low electric field-strengths), the electron will occupy the first local minima; at that point the electrons have a low effective mass and therefore high mobility. However, when the applied electric field is increased to about 3.2 kV/cm, the electron will have sufficient energy to occupy the second minima. At the second minima, the electrons will have higher effective mass and will have lost their high mobility property. As the electric field is increased further, more electrons will occupy this low mobility region and their velocity will continue to decrease until a point where all the electrons completely occupy the second local minima. At this point, the drift velocity will level off as shown in Figure 2-2.

Notwithstanding the above advantages, both materials do have drawbacks. In general, Si is a more cost effective material in fabrication processes, is a more mature technology and has better device characterisation and understanding. In production lines, the yield in Si processing has been increased repeatedly, along with improvements in material reliability. It should be noted that Si, with its inherent advantage of exceptional native oxide (SiO<sub>2</sub>), makes the devices significantly more stable.

At present, Silicon-Germanium (SiGe) heterostructures with Si are a topic of significant research interest in order to cater the low carrier mobility, which closely related to the Si properties. The emerging new material has offered the possibility to extend the reach of Si technology into areas of high mobility - high speed applications which were dominated by the III–V devices. This technology has offered many advantages associated with heterostructures, in addition to largely compatible with standard Si IC processing techniques [21].

For the III-V material type, comparing between GaAs and InP-based compounds such as InGaAs and InAlAs, the advantages of InGaAs-InAlAs over GaAs are less perceptible due to issues such as non-optimum material characteristics, buffer layer and substrate quality problems. There are also additional technical issues related to the low energy gap of the InGaAs channel and low barrier height of InAlAs Schottky gates. Consequently, more electrons are thermally excited over the rather low Schottky barrier and this leads to an increase in gate leakage current [16].

## 2.3 LATTICE MATCHED AND PSEUDOMORPHIC MATERIALS

Over the years, much work has been carried out and a number of material systems have been extensively studied as alternatives to bulk GaAs. One important discovery concerns the manipulation of energy bands by band gap engineering. Here, the idea of combining multiple unequal energy gaps is often advantageous to the electrical properties used in many solid-state device applications. It is realised by growing layers of similar crystalline structure on top of each other by means of Molecular Beam Epitaxy (MBE) or Metalorganic Chemical Vapour Deposition (MOCVD). The interface that occurs between them is called a heterojunction. Multiple

heterojunctions combined in one structure are called heterostructures. This has lead to the emergence of a new class of high-speed devices, that a high quality junction between semiconductors of different band gaps can be formed.

At this point, the quality of the semiconductor depends on the materials' lattice constant ( $a_0$ ). The lattice constant is defined as the distance between the unit-cell of the periodic crystal. A lattice matched structure is formed when two different materials with nearly the same lattice properties are grown on top of each other. Therefore, the quality of the resulting structure greatly depends on the quality of the matching between the two lattice constants [16].

Figure 2-3 Minimum energy band gap versus lattice constant for various semiconductor materials.

Shown in the graph is the ternary compound lattice matched to InP substrate [22]

Figure 2-3 shows the energy band gap  $(E_g)$  versus lattice constant for various semiconductor materials that are of interest to the work presented here. Illustrated in the figure are the ternary compound semiconductor materials that are lattice matched to GaAs and InP substrates. For example,  $Al_xGa_{(1-x)}As$  is lattice match with GaAs irrespective of the specific mole fractions, whereas  $In_xGa_{(1-x)}As$  and  $In_xAl_{(1-x)}As$  are

lattice matched with InP only at a single fixed mole fraction ( $x \sim 0.52$ ). An approximation of the ternary's lattice constant and energy band gap can be calculated using Vegard's Law [23, 24], where x is the mole fraction and AZ and BZ are the binary compound lattice constant and band gap values.

$$a_{alloy}$$

= $x$ AZ+ $(1-x)$ BZ Equation 2-1

The lattice constant and band-gap energy for GaAs and InP-based materials are tabulated in Table 2-2 [17, 25]. One can identify immediately the various energy gaps between those materials. Clearly, few pairs of semiconductors have a near-equal lattice constant.

Table 2-2 Lattice constant and band gap of common III-V binary and ternary compound semiconductors at 300 K [17, 25]

| Alloy                                    | Lattice constant, $a_{\theta}(\mathring{A})$ | Band gap, E <sub>g</sub> (eV) |

|------------------------------------------|----------------------------------------------|-------------------------------|

| GaAs                                     | 5.653                                        | 1.42                          |

| AlAs                                     | 5.660                                        | 2.16                          |

| InAs                                     | 6.058                                        | 0.37                          |

| InP                                      | 5.869                                        | 1.35                          |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As | 5.869                                        | 0.76                          |

| In <sub>0.52</sub> Al <sub>0.48</sub> As | 5.869                                        | 1.48                          |

For nearly equal lattice constant materials, the atoms at the hetero-interface have to slightly adjust their positions in order for them to conserve the geometry of the lattice. The adjustments of the atomic position will result in a small strain at the interface. The strain  $(\varepsilon)$  at the semiconductor interface is defined in Equation 2-2. Here,  $a_L$  is the lattice constant for the overlay semiconductor and  $a_S$  is the lattice constant of the baseline semiconductor.

$$\varepsilon = \frac{(a_L - a_S)}{a_S}$$

Equation 2-2

However, when lattice matching is not adequate, this strain exceeds a certain critical value and therefore, the crystal lattice cannot hold the excessive force. This will then result in crystal dislocations. The crystal imperfections will propagate through many crystalline layers producing crystal dislocations in the lattice. These defects will invariably trap carriers, which will limit their mobility. They can also become recombination centres, which shorten the carriers' lifetimes. The overall effects result in very poor device properties.

Nevertheless, high quality crystal growth from two mismatched lattices can still be achieved with careful processing through advancements in crystal growth technologies such as MBE and MOCVD [26-28]. The strain can be tolerated by growing thin mismatched epitaxial layers on top of each other. However, as the strain energy increases with the thickness of the strained layer, the overlay layer must be grown below a critical thickness before dislocations can occur [29, 30]. This critical thickness ( $h_c$ ) is defined as:

$$h_c = \frac{a_s}{2\varepsilon}$$

Equation 2-3

To compensate for this difference, the resultant layer will be under strain. This new layer is known as 'pseudomorphic' since it is physically modified from the original crystal structure and consequently its physical properties are changed. This is beneficial in the manipulation of the semiconductors' mole fraction for combining either wider or narrower semiconductor materials. The significance of these material mixes will become clearer shortly.

Figure 2-4 shows the crystal formation as above. In figure (a),  $a_L$  is lattice matched with  $a_S$ , and hence the over-layer and base material atoms at the crystal interface are not required to adjust their positions relative to each other.

Figures (b) and (c) show the pseudomorphic crystal structure under compressive and tensile strains respectively. When  $a_L$  is larger than  $a_S$ , the resultant relaxed material is under compressive strain whereas the atoms are under tensile strain when  $a_L$  is smaller than  $a_S$ . Above the critical thickness, the excessive strain energy is released

by the formation of dislocations where some of the bonds are missing or extra bonds appear. The resulting crystal defects are shown in figure (d).

Figure 2-4 Conceptual formation of lattice match (a), pseudomorphic compressive strain (b), pseudomorphic tensile strain (c) and lattice mismatched with defects (d)

#### 2.4 HIGH SPEED DEVICES

In previous sections, semiconductor materials suitable for high frequency applications have been identified, and the focus has primarily been on GaAs and InGaAs-InAlAs compounds from which high-speed devices have been realised. This section summarises the historical trend in high-speed devices beginning with a brief introduction of the device structure and high-speed limitations of the Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET). Next, the Metal Semiconductor Field Effect Transistor (MESFET), which over the years has been refined, resulting in devices that are more outstanding. Finally, the ultimate device in high frequency device applications, the High Electron Mobility Transistor (HEMT) is described.

In most semiconductor materials, the hole mobility is relatively poor when compared to that of the electron. For this reason, most high-speed devices use electrons as the charge carriers. Thus, the use of n-type channel in MOS (nMOS), and an electron-rich channel in MESFET and HEMT device architectures are required. These are the three terminal device that uses the induced electric field from a gate voltage to control the shape and consequently the conductivity in the channel. All of these devices are referred to Field Effect Transistors (FETs).

## 2.4.1 N-type Metal Oxide Semiconductor Field Effect Transistor (nMOS)

In an nMOS device (see Figure 2-5), the gate terminal is biased to a positive potential with respect to the p-type substrate. The positive charges at the gate terminal will repel the majority holes, and create a depletion region near the gate oxide surface. At the same time, some minority electrons are also attracted to the surface, but at low gate potentials, the accumulation of the electrons is not sufficient to cause current conduction.

Figure 2-5 nMOS structure

As the gate voltage is increased, a dense inversion layer of electrons is formed under the oxide surface. When the gate potential reaches a threshold voltage  $(V_{th})$ , an inversion layer of electron-rich conduction channel will be formed and allow current conduction between the source and drain terminals of the MOSFET.

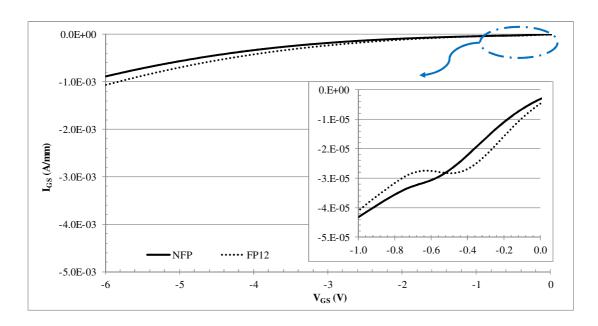

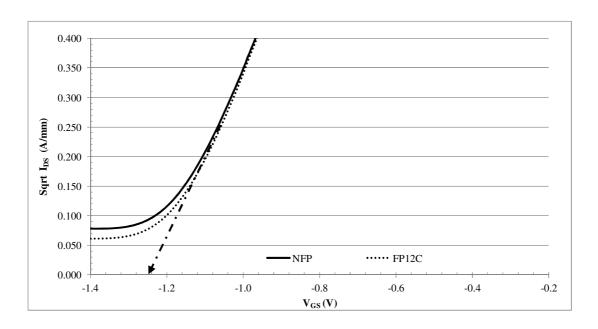

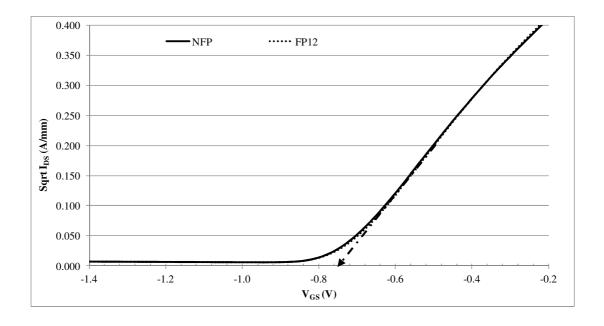

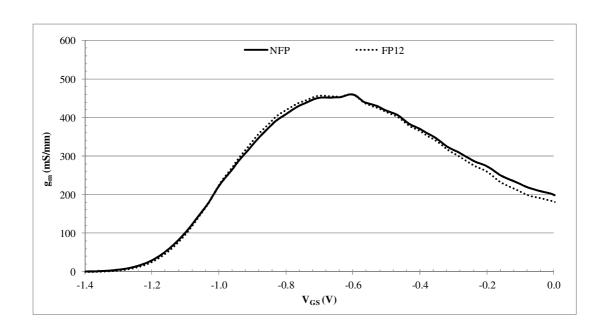

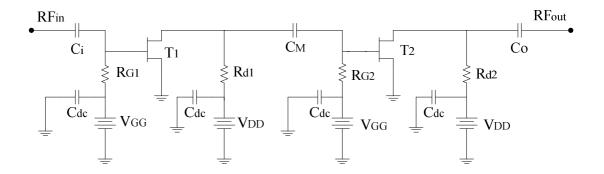

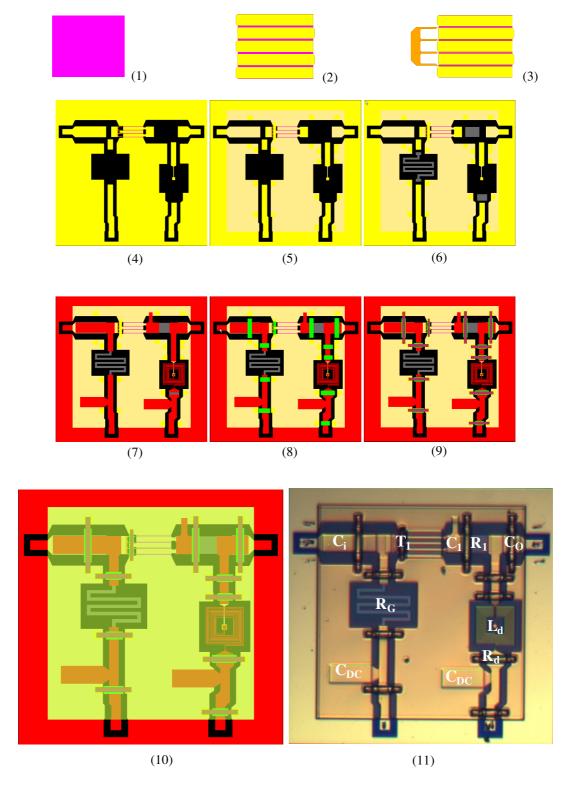

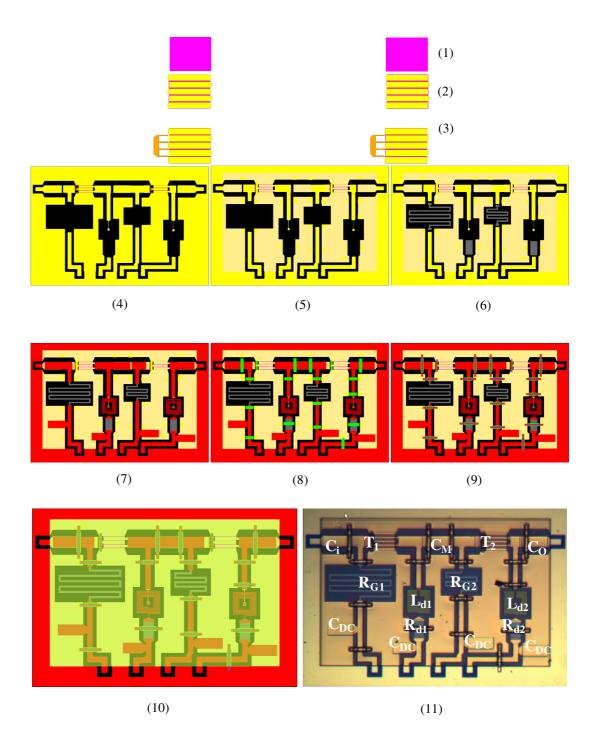

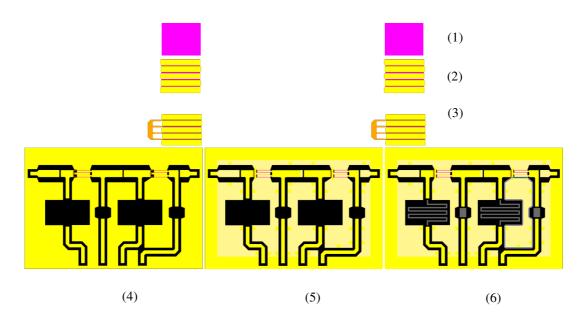

However, the low carrier mobility in Si inherently limits the device application in ultra high frequency operation. For this reason, and for micron-sized devices, the cut-off frequency of these devices is only in the order of 1 to 3 GHz [31]. Deeply scaled MOS devices (gate length of 35 nm or less) reach cut-off frequencies of ~200 to 300 GHz. That is the reason why the micron scale Si MOSFET is widely used in lower frequency electronic circuits.